【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成27年4月9日(2015.4.9)

【公開番号】特開2014-192825(P2014-192825A)

【公開日】平成26年10月6日(2014.10.6)

【年通号数】公開・登録公報2014-055

【出願番号】特願2013-68636(P2013-68636)

【国際特許分類】

|        |        |           |

|--------|--------|-----------|

| H 04 N | 5/374  | (2011.01) |

| H 01 L | 29/786 | (2006.01) |

| H 01 L | 27/146 | (2006.01) |

| H 01 L | 27/144 | (2006.01) |

| H 04 N | 5/32   | (2006.01) |

【F I】

|        |       |         |

|--------|-------|---------|

| H 04 N | 5/335 | 7 4 0   |

| H 01 L | 29/78 | 6 1 7 N |

| H 01 L | 29/78 | 6 1 7 T |

| H 01 L | 29/78 | 6 1 8 B |

| H 01 L | 27/14 | C       |

| H 01 L | 27/14 | K       |

| H 04 N | 5/32  |         |

【手続補正書】

【提出日】平成27年2月18日(2015.2.18)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0024

【補正方法】変更

【補正の内容】

【0024】

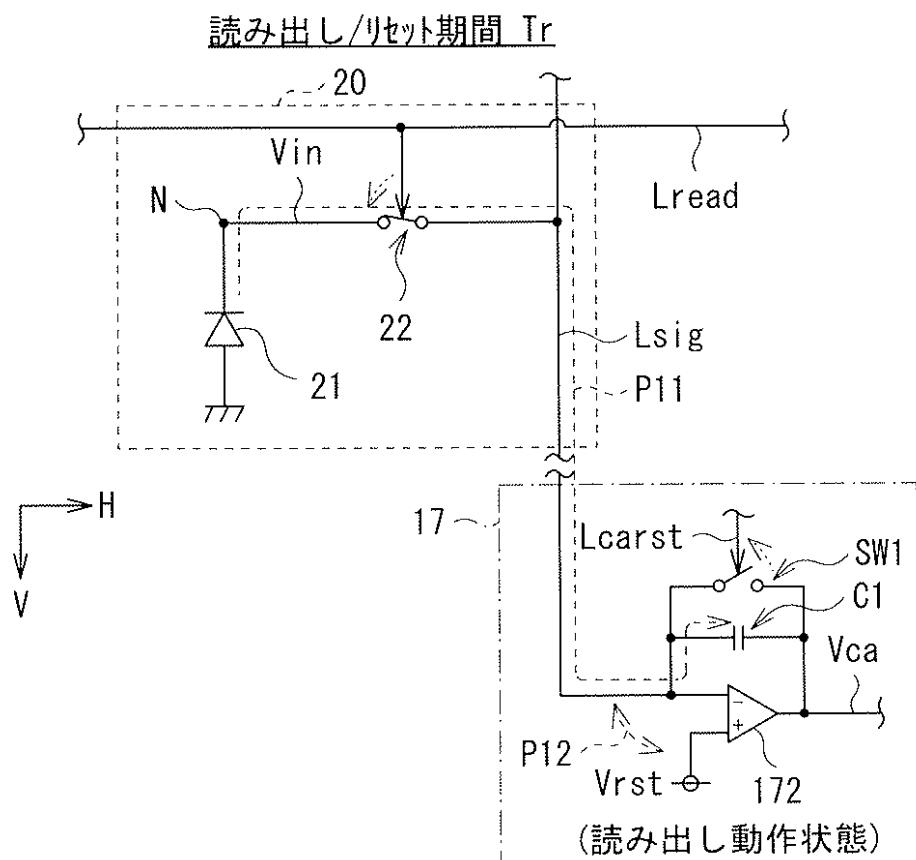

本実施の形態では、画素20の回路構成において、例えば第1ゲート電極220Aが読み出し制御線L read1に接続され、第2ゲート電極220Bが読み出し制御線L read2に接続されている。このような構成において、第1ゲート電極220Aおよび第2ゲート電極220Bは別々に電圧制御される。具体的には、第1ゲート電極220Aへ印加される電圧は、例えばシステム制御部16および行走査部13により制御され、第2ゲート電極220Bへ印加される電圧は、例えばバイアス電圧制御部18により制御される。これにより、第1ゲート電極220Aには、行走査信号に相当するパルス電圧Vg(第1の電圧)が印加され、第2ゲート電極220Bには、バイアス電圧Vtg(第2の電圧)が印加される。尚、ここでは、パルス電圧が印加される第1ゲート電極220Aを下側(半導体層226よりも下方)に配置し、バイアス電圧が印加される第2ゲート電極220Bを上側(半導体層226よりも上方)に配置しているが、上下逆の構造であってもよい。トランジスタ22のソース(ソース・ドレイン電極228)は、例えば信号線Lsigに接続されており、ドレイン(ソース・ドレイン電極228)は、例えば光電変換素子21のカソードに蓄積ノードNを介して接続されている。また、光電変換素子21のアノードは、ここではグランドに接続(接地)されている。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0040

【補正方法】変更

## 【補正の内容】

## 【0040】

図6Aは、バイアス電圧制御部18の機能構成を、読み出し制御線L read2と共に表したものである。尚、図6Aでは、画素部11に画素行毎に接続される読み出し制御線L read2のうち、上から3行分の読み出し制御線L read2(1)～L read2(3)を例示している。バイアス電圧制御部18は、例えばFPGA(field-programmable gate array)制御部180と、D/Aコンバータ181と、LDO(Low Drop Out)レギュレータ182とを備える。バイアス電圧制御部18では、FPGA制御部180において、バイアス電圧V<sub>tg</sub>の電圧値および切り替えタイミング等が設定される。例えば、図6Bに示したように、バイアス電圧V<sub>tg</sub>の電圧値p<sub>1</sub>、p<sub>2</sub>、p<sub>3</sub>、p<sub>4</sub>と、各電圧値の切り替えタイミングt<sub>1</sub>、t<sub>2</sub>、t<sub>3</sub>が設定される。

## 【手続補正3】

## 【補正対象書類名】明細書

## 【補正対象項目名】0056

## 【補正方法】変更

## 【補正の内容】

## 【0056】

図9に、低温多結晶シリコンを用いたトランジスタ22へX線を照射した場合の、ゲート電圧(V<sub>g</sub>)に対するドレイン電流(I<sub>d</sub>)の関係(電流電圧特性)について示す。このように、放射線を照射した場合、その照射量が、0 Gy, 54 Gy, 79 Gy, 104 Gy, 129 Gy, 154 Gy, 254 Gy, 354 Gyと増大するに従って、閾値電圧V<sub>th</sub>が負側にシフトすることがわかる。また、照射量が増すに従って、S(サブスレッショルドスウェーブ)値も悪化している。加えて、この閾値電圧V<sub>th</sub>のシフト量の増加は、オフ電流およびオン電流の変化を引き起こす。例えば、オフ電流が増して電流リークが生じたり、オン電流が減少して読み出し不能になる等、トランジスタの信頼性を維持することが困難となる。このように、特に低温多結晶ポリシリコンを用いた放射線撮像装置では、被曝によってトランジスタ22の閾値電圧V<sub>th</sub>が負側へシフトし、これが信頼性低下の要因となっている。そこで、本実施の形態では、以下のような閾値電圧V<sub>th</sub>のシフト量を考慮した補正(キャリブレーション)がなされる。

## 【手続補正4】

## 【補正対象書類名】明細書

## 【補正対象項目名】0069

## 【補正方法】変更

## 【補正の内容】

## 【0069】

以上のように本実施の形態では、各画素20からの信号電荷の読み出しの際、トランジスタ22の第1ゲート電極220Aにパルス電圧V<sub>g</sub>を、第2ゲート電極220Bにバイアス電圧V<sub>tg</sub>がそれぞれ印加され、トランジスタのオン・オフ制御がなされる。このとき、所定のタイミングにおいて、バイアス電圧制御部18が、バイアス電圧V<sub>tg</sub>を、トランジスタ22の閾値電圧V<sub>th</sub>のシフト量に応じて補正する。これにより、トランジスタの閾値電圧のシフトによる影響を緩和して高信頼性を実現することが可能となる。

## 【手続補正5】

## 【補正対象書類名】明細書

## 【補正対象項目名】0076

## 【補正方法】変更

## 【補正の内容】

## 【0076】

図15は、本変形例のバイアス電圧制御部18Aの機能構成をシステム制御部16と共に表したものである。このように、本変形例では、バイアス電圧制御部18Aが、読み出し制御線L read2にいわゆる共通接点cを有するスイッチ(スイッチSW12)が設けら

れている。このスイッチ SW12 は、共通接点 c と、2 つの接点 a, b を有する切り替えスイッチであり、これにより、バイアス電圧制御部 18A から 2 値の電圧値を逐一的に出力できるようになっている。例えば、バイアス電圧制御部 18A は、バイアス電圧 V<sub>tg</sub> の電圧値を生成する回路部 18a1 と、読み出し / リセット期間中に印加する電圧値を生成する回路部 18a2 を有しており、これらの回路部 18a1, 18a2 は FPGA 制御部 180 によって制御される。回路部 18a1 はスイッチ SW12 の接点 a に、回路部 18a2 はスイッチ SW12 の接点 b に、それぞれ接続されている。尚、スイッチ SW12 の切り替えは、図示しない制御信号によってなされ、例えば、通常時（スイッチ SW12 のオフ時）は接点 a につながり、動作時（スイッチ SW12 のオン時）には接点 b につながるようになっている。

【手続補正 6】

【補正対象書類名】明細書

【補正対象項目名】0081

【補正方法】変更

【補正の内容】

【0081】

但し、本変形例では、画素 20B が、2 つのトランジスタ 22（トランジスタ 22B1, 22B2）を有している。これら 2 つのトランジスタ 22B1, 22B2 は、互いに直列に接続されている（一方のソースまたはドレインと他方のソースまたはドレインとが電気的に接続されている。または、後述するように半導体層 226 が一体的に連結して形成されている。）。また、各トランジスタ 22B1, 22B2 における一方のゲートが読み出し制御線 L<sub>read1</sub> に接続され、他方のゲートが読み出し制御線 L<sub>read2</sub> に接続されている。

【手続補正 7】

【補正対象書類名】明細書

【補正対象項目名】0084

【補正方法】変更

【補正の内容】

【0084】

<変形例 5, 6 >

図 19 は、変形例 5 に係る画素（画素 20C）の回路構成を、以下説明する列選択部 17B の回路構成例とともに表したものである。また、図 20 は、変形例 6 に係る画素（画素 20D）の回路構成を、列選択部 17B の回路構成例とともに表したものである。これらの変形例 5, 6 に係る画素 20C, 20D はそれぞれ、これまで説明した画素 20, 20A, 20B とは異なり、いわゆるアクティブ型の画素回路を有している。

【手続補正 8】

【補正対象書類名】明細書

【補正対象項目名】0087

【補正方法】変更

【補正の内容】

【0087】

また、これらの変形例 5, 6 において列選択部 17B は、前述した列選択部 17 において、チャージアンプ 172、容量素子 C1 およびスイッチ SW1 に代わりに、定電流源 171 およびアンプ 176 を設けたものとなっている。アンプ 176 では、正側の入力端子には信号線 L<sub>sig</sub> が接続されると共に、負側の入力端子と出力端子とが互いに接続され、ボルテージフォロワ回路が形成されている。尚、信号線 L<sub>sig</sub> の一端側には定電流源 171 の一方の端子が接続され、この定電流源 171 の他方の端子には電源 V<sub>SS</sub> が接続されている。

【手続補正 9】

【補正対象書類名】明細書

【補正対象項目名】 0 0 8 8

【補正方法】 変更

【補正の内容】

【0 0 8 8】

<変形例7, 8>

図21Aおよび図21Bはそれぞれ、変形例7, 8に係る撮像部11の概略構成を模式的に表したものである。上記実施の形態の撮像装置1が、放射線撮像装置である場合には、撮像部11は、これらの変形例7, 8のいずれかの構成を有している。

【手続補正10】

【補正対象書類名】 図面

【補正対象項目名】 図7B

【補正方法】 変更

【補正の内容】

【図7B】