## (12) 发明专利

(10) 授权公告号 CN 109508306 B

(45) 授权公告日 2023.11.10

(21) 申请号 201810908900.4

(74) 专利代理机构 华进联合专利商标代理有限公司 44224

(22) 申请日 2018.08.10

专利代理人 刘培培 黄隶凡

(65) 同一申请的已公布的文献号

申请公布号 CN 109508306 A

(51) Int.CI.

(43) 申请公布日 2019.03.22

G06F 13/16 (2006.01)

(30) 优先权数据

62/558,726 2017.09.14 US

(56) 对比文件

62/558,732 2017.09.14 US

CN 102084428 A, 2011.06.01

62/558,741 2017.09.14 US

CN 106471474 A, 2017.03.01

15/821,688 2017.11.22 US

US 2010169603 A1, 2010.07.01

(73) 专利权人 三星电子株式会社

US 2014075135 A1, 2014.03.13

地址 韩国京畿道水原市灵通区三星路129

号

US 2015149735 A1, 2015.05.28

(72) 发明人 克里希纳·T·马拉迪 郑宏忠

US 2016070483 A1, 2016.03.10

US 2016085465 A1, 2016.03.24

US 2017255390 A1, 2017.09.07

US 5396641 A, 1995.03.07

审查员 朱江

权利要求书3页 说明书15页 附图10页

(54) 发明名称

高带宽存储系统

(57) 摘要

一种高带宽存储(HBM)系统包括高带宽存储装置及逻辑电路。所述逻辑电路包括耦合到主机装置的第一接口及耦合到所述高带宽存储装置的第二接口。所述逻辑电路通过所述第一接口从所述主机装置接收第一命令并将所接收的第一命令转换成第一存储器内处理(PIM)命令，所述第一存储器内处理命令通过所述第二接口发送到所述高带宽存储装置。所述第一存储器内处理命令的完成具有确定的延迟。所述逻辑电路还通过所述第一接口从所述主机装置接收第二命令并将所接收的第二命令转换成第二存储器内处理命令，所述第二存储器内处理命令通过所述第二接口发送到所述高带宽存储装置。所述第二存储器内处理命令的完成具有不确定的延迟。

1. 一种高带宽存储系统,其特征在于,包括:

高带宽存储装置;以及

逻辑电路,包括能够耦合到主机装置的第一接口及耦合到所述高带宽存储装置的第二接口,所述逻辑电路能够通过所述第一接口从所述主机装置接收第一命令并将所接收的所述第一命令转换成第一存储器内处理命令,所述第一存储器内处理命令通过所述第二接口发送到所述高带宽存储装置,所述第一存储器内处理命令的完成具有确定的延迟,且所述逻辑电路还能够通过所述第一接口从所述主机装置接收第二命令并将所接收的所述第二命令转换成第二存储器内处理命令,所述第二存储器内处理命令通过所述第二接口发送到所述高带宽存储装置,所述第二存储器内处理命令的完成具有不确定的延迟。

2. 根据权利要求1所述的高带宽存储系统,其特征在于,响应于从所述主机装置接收到所述第一命令,所述逻辑电路控制所述高带宽存储装置对所述高带宽存储装置的信道中的至少一个所选择存储体进行预充电。

3. 根据权利要求1所述的高带宽存储系统,其特征在于,所述逻辑电路从所述主机装置接收到所述第一命令的时刻与所述高带宽存储系统准备好从所述主机装置接收另一命令的时刻之间的时间是确定的。

4. 根据权利要求3所述的高带宽存储系统,其特征在于,所述第一接口包括命令/地址总线及数据总线,

其中所述逻辑电路通过所述命令/地址总线接收所述第一命令,且

其中所述逻辑电路通过所述数据总线接收与所述第一命令对应的第一命令分组。

5. 根据权利要求4所述的高带宽存储系统,其特征在于,还包括能够耦合在所述逻辑电路与所述主机装置之间的事务总线,且

其中当所述第二存储器内处理命令已完成时,所述逻辑电路通过所述事务总线向所述主机装置发送指示。

6. 根据权利要求5所述的高带宽存储系统,其特征在于,当所述高带宽存储系统准备好从所述主机装置接收另一命令时,所述逻辑电路通过所述命令/地址总线从所述主机装置接收第三命令,且

其中通过所述数据总线从所述逻辑电路向所述主机装置输出与所述第三命令对应的响应。

7. 根据权利要求4所述的高带宽存储系统,其特征在于,所述系统还包括位于所述逻辑电路与所述主机装置之间的事务总线,

其中所述逻辑电路通过所述命令/地址总线从所述主机装置接收所述第二命令,

其中所述逻辑电路通过数据总线从所述主机装置接收与所述第二命令对应的第二命令分组,且

其中当所述第二存储器内处理命令已完成时,所述逻辑电路通过所述事务总线向所述主机装置发送指示。

8. 一种高带宽存储系统,其特征在于,包括:

高带宽存储装置;以及

逻辑电路,包括第一接口、第二接口及事务总线,所述第一接口包括能够耦合到主机装置的命令/地址总线及能够耦合到所述主机装置的数据总线,所述第二接口耦合到所述高

带宽存储装置，所述事务总线能够耦合到主机装置，所述逻辑电路能够通过所述第一接口从所述主机装置接收第一命令并将所接收的所述第一命令转换成第一存储器内处理命令，所述第一存储器内处理命令通过所述第二接口发送到所述高带宽存储装置，所述第一存储器内处理命令的完成具有不确定的延迟，且当所述第一存储器内处理命令已完成时，所述逻辑电路通过所述事务总线向所述主机装置发送指示。

9. 根据权利要求8所述的高带宽存储系统，其特征在于，所述逻辑电路通过所述数据总线从所述主机装置接收与所述第一命令对应的第一命令分组，且

其中从所述主机装置接收到所述第一命令的时刻与所述高带宽存储系统准备好从所述主机装置接收另一命令的时刻之间的时间是不确定的。

10. 根据权利要求9所述的高带宽存储系统，其特征在于，在所述第一命令之后，所述逻辑电路通过所述命令/地址总线从所述主机装置接收第二命令，且

其中通过所述数据总线从所述逻辑电路向所述主机装置输出与所述第二命令对应的输出。

11. 根据权利要求10所述的高带宽存储系统，其特征在于，所述逻辑电路还能够通过所述第一接口从所述主机装置接收第三命令并将所接收的所述第三命令转换成第二存储器内处理命令，所述第二存储器内处理命令通过所述第二接口发送到所述高带宽存储装置，所述第二存储器内处理命令的完成具有确定的延迟。

12. 根据权利要求11所述的高带宽存储系统，其特征在于，响应于从所述主机装置接收到所述第三命令，所述逻辑电路控制所述高带宽存储装置对所述高带宽存储装置的信道中的至少一个所选择存储体进行预充电。

13. 根据权利要求12所述的高带宽存储系统，其特征在于，所述逻辑电路从所述主机装置接收第四命令，且

其中所述逻辑电路从所述主机装置接收到所述第四命令的时刻与所述高带宽存储系统准备好从所述主机装置接收另一命令的时刻之间的时间是确定的。

14. 根据权利要求13所述的高带宽存储系统，其特征在于，通过所述命令/地址总线接收所述第四命令，且

其中通过所述数据总线接收与所述第四命令对应的第四命令分组。

15. 一种高带宽存储系统，其特征在于，包括：

高带宽存储装置，能够执行存储器内处理功能；以及

逻辑电路，包括第一接口、第二接口及事务总线，所述第一接口包括能够耦合到主机装置的命令/地址总线及能够耦合到所述主机装置的数据总线，所述第二接口耦合到所述高带宽存储装置，所述事务总线能够耦合到所述主机装置，所述逻辑电路能够通过所述第一接口从所述主机装置接收第一命令并将所接收的所述第一命令转换成通过所述第二接口发送到所述高带宽存储装置以进行存储器内处理的第一命令，所述第一命令的完成具有确定的延迟，且所述逻辑电路还能够通过所述第一接口从所述主机装置接收第二命令并将所接收的所述第二命令转换成通过所述第二接口发送到所述高带宽存储装置以进行存储器内处理的第二命令，所述第二命令的完成具有不确定的延迟。

16. 根据权利要求15所述的高带宽存储系统，其特征在于，响应于从所述主机装置接收到所述第一命令，所述逻辑电路控制所述高带宽存储装置对所述高带宽存储装置的信道中

的至少一个所选择存储体进行预充电。

17. 根据权利要求15所述的高带宽存储系统，其特征在于，所述逻辑电路从所述主机装置接收到第三命令的时刻与所述高带宽存储系统准备好从所述主机装置接收另一命令的时刻之间的时间是确定的。

18. 根据权利要求17所述的高带宽存储系统，其特征在于，通过所述命令/地址总线接收所述第一命令，且

其中通过所述数据总线接收与所述第一命令对应的第一命令分组。

19. 根据权利要求18所述的高带宽存储系统，其特征在于，所述逻辑电路通过所述命令/地址总线从所述主机装置接收所述第二命令，

其中所述逻辑电路通过所述数据总线从所述主机装置接收与所述第二命令对应的第二命令分组，且

其中当存储器内处理的所述第二命令已完成时，所述逻辑电路通过所述事务总线向所述主机装置发送指示。

20. 根据权利要求19所述的高带宽存储系统，其特征在于，所述逻辑电路通过所述命令/地址总线从所述主机装置接收第三命令，且

其中通过所述数据总线从所述逻辑电路向所述主机装置输出与所述第三命令对应的输出。

## 高带宽存储系统

[0001] [相关申请的交叉参考]

[0002] 本专利申请主张在2017年9月14日提出申请的美国临时专利申请第62/558,726号的优先权、在2017年9月14日提出申请的临时专利申请第62/558,732号的优先权以及在2017年9月14日提出申请的临时专利申请第62/558,741号的优先权，所述各临时专利申请的公开内容全文并入本申请供参考。

### 技术领域

[0003] 本文所公开的主题大体来说涉及高带宽存储(HBM)系统，且更具体来说，涉及一种能够在存储器操作中进行确定的处理及不确定的处理以与主机装置接口的系统及协议。

### 背景技术

[0004] 新兴应用(比如，深度神经网络)使用大规模的计算及存储能力来对不同的数据集进行训练并以高的准确性进行学习。此外，随着应用(比如，高性能计算(high-performance computing, HPC)、图形算法等)变为数据及计算密集型的，能量效率及低延迟成为关键特性。存储器内处理(processing in memory, PIM)能够通过在动态随机存取存储器(dynamic random access memory, DRAM)逻辑裸片上排程复杂的操作来解决这些挑战，从而以较低功率技术进程提供额外的计算能力，且还更靠近数据所在的位置。

### 发明内容

[0005] 一个示例性实施例提供一种高带宽存储(high-bandwidth memory, HBM)系统，所述高带宽存储系统可包括高带宽存储装置以及逻辑电路。所述逻辑电路可包括能够耦合到主机装置的第一接口及耦合到所述高带宽存储装置的第二接口，其中所述逻辑电路可能够通过所述第一接口从所述主机装置接收第一命令并将所接收的所述第一命令转换成第一存储器内处理(PIM)命令，所述第一存储器内处理命令通过所述第二接口发送到所述高带宽存储装置，其中所述第一存储器内处理命令的完成可具有确定的延迟。所述逻辑电路还可通过所述第一接口从所述主机装置接收第二命令并将所接收的所述第二命令转换成第二存储器内处理命令，所述第二存储器内处理命令通过所述第二接口发送到所述高带宽存储装置，其中所述第二存储器内处理命令的完成可具有不确定的延迟。响应于从所述主机装置接收到所述第一命令，所述逻辑电路可控制所述高带宽存储装置对所述高带宽存储装置的信道中的至少一个所选择存储体进行预充电。所述逻辑电路从所述主机装置接收到所述第一命令的时刻与所述高带宽存储系统准备好从所述主机装置接收另一命令的时刻之间的时间可为确定的。

[0006] 另一个示例性实施例提供一种高带宽存储(HBM)系统，所述高带宽存储系统可包括高带宽存储装置以及逻辑电路。所述逻辑电路可包括第一接口、第二接口及事务总线，所述第一接口包括能够耦合到主机装置的命令/地址总线及能够耦合到所述主机装置的数据总线，所述第二接口耦合到所述高带宽存储装置，所述事务总线能够耦合到主机装置。所述

逻辑电路可能能够通过所述第一接口从所述主机装置接收第一命令并将所接收的所述第一命令转换成第一存储器内处理(PIM)命令,所述第一存储器内处理命令通过所述第二接口发送到所述高带宽存储装置,其中所述第一存储器内处理命令的完成可具有不确定的延迟。当所述第一存储器内处理命令已完成时,所述逻辑电路可通过所述事务总线向所述主机装置发送指示。所述逻辑电路通过所述数据总线从所述主机装置接收与所述第一命令对应的第一命令分组,且从所述主机装置接收到所述第一命令的时刻与所述高带宽存储系统准备好从所述主机装置接收另一命令的时刻之间的时间可为不确定的。

[0007] 再一个示例性实施例提供一种高带宽存储(HBM)系统,所述高带宽存储系统可包括高带宽存储装置以及逻辑电路。所述高带宽存储装置可执行存储器内处理(PIM)功能。所述逻辑电路可包括第一接口、第二接口及事务总线,所述第一接口包括能够耦合到主机装置的命令/地址总线及能够耦合到所述主机装置的数据总线,所述第二接口耦合到所述高带宽存储装置,所述事务总线能够耦合到主机装置。所述逻辑电路可通过所述第一接口从所述主机装置接收第一命令并将所接收的所述第一命令转换成通过所述第二接口发送到所述高带宽存储装置以进行存储器内处理的第一命令,其中所述第一命令的完成可具有确定的延迟。所述逻辑电路还可能能够通过所述第一接口从所述主机装置接收第二命令并将所接收的所述第二命令转换成通过所述第二接口发送到所述高带宽存储装置的以进行存储器内处理第二命令,其中所述第二命令的完成可具有不确定的延迟。

## 附图说明

[0008] 在以下部分中,将参照各图中所示的示例性实施例来阐述本文所公开的主题的各个方面,在各图中:

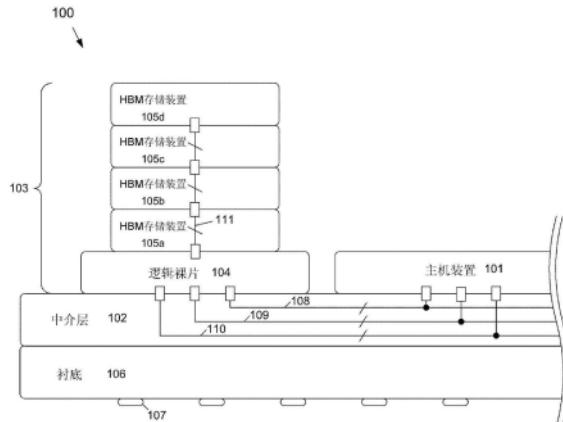

[0009] 图1绘示根据本文所公开主题的高带宽存储器内处理(HBM+)系统的示例性实施例的一部分的剖视图;

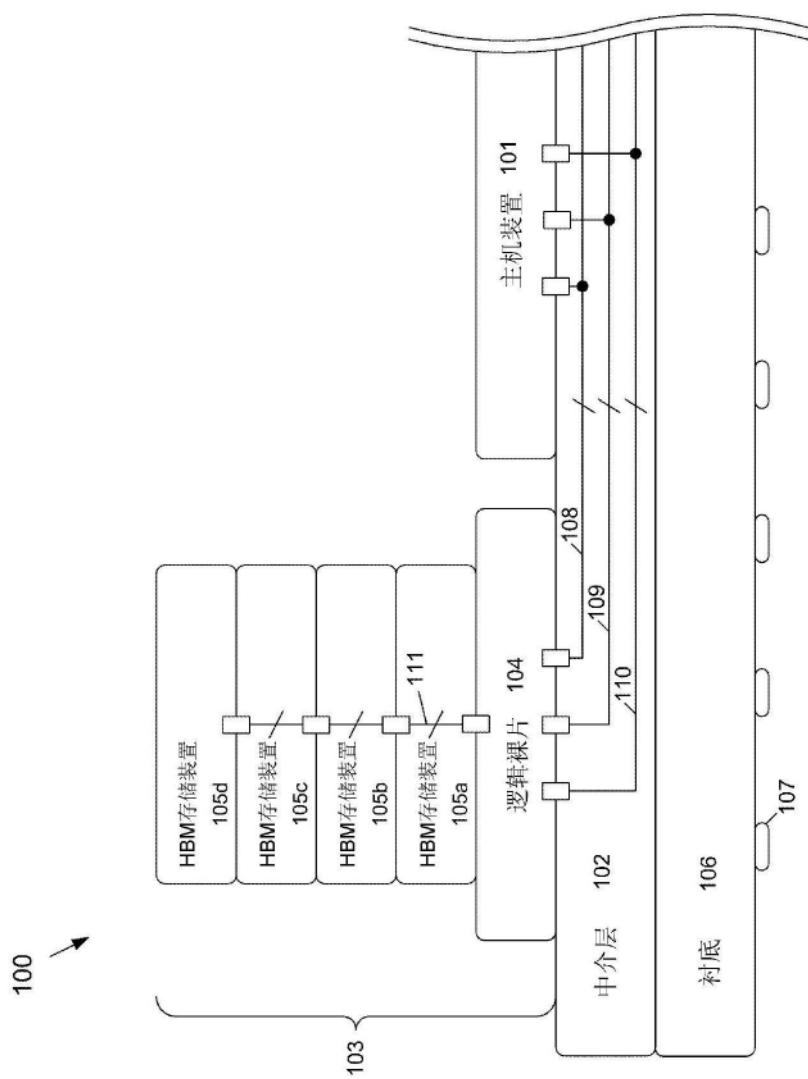

[0010] 图2绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议命令的概括时序型图;

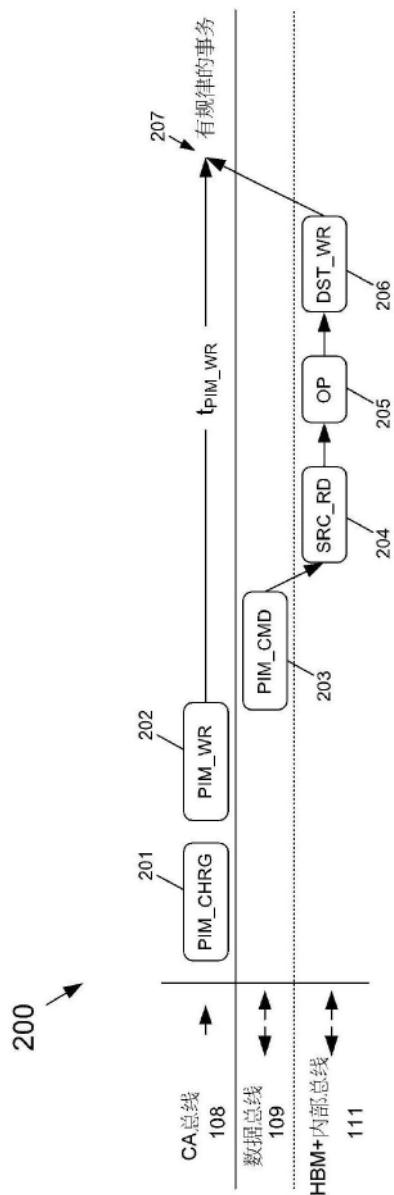

[0011] 图3绘示根据本文所公开主题的PIM\_CMD命令的内容的示例性配置方式;

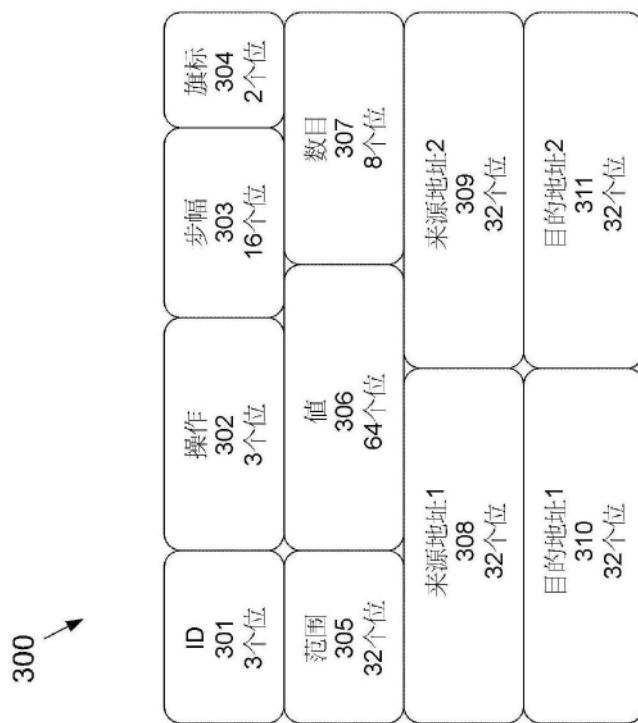

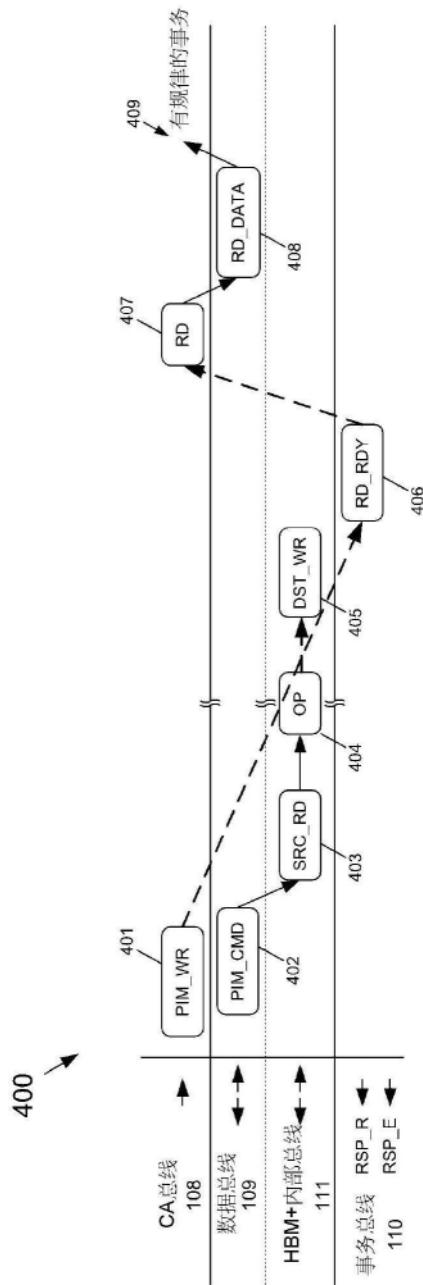

[0012] 图4绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议命令的概括时序型图;

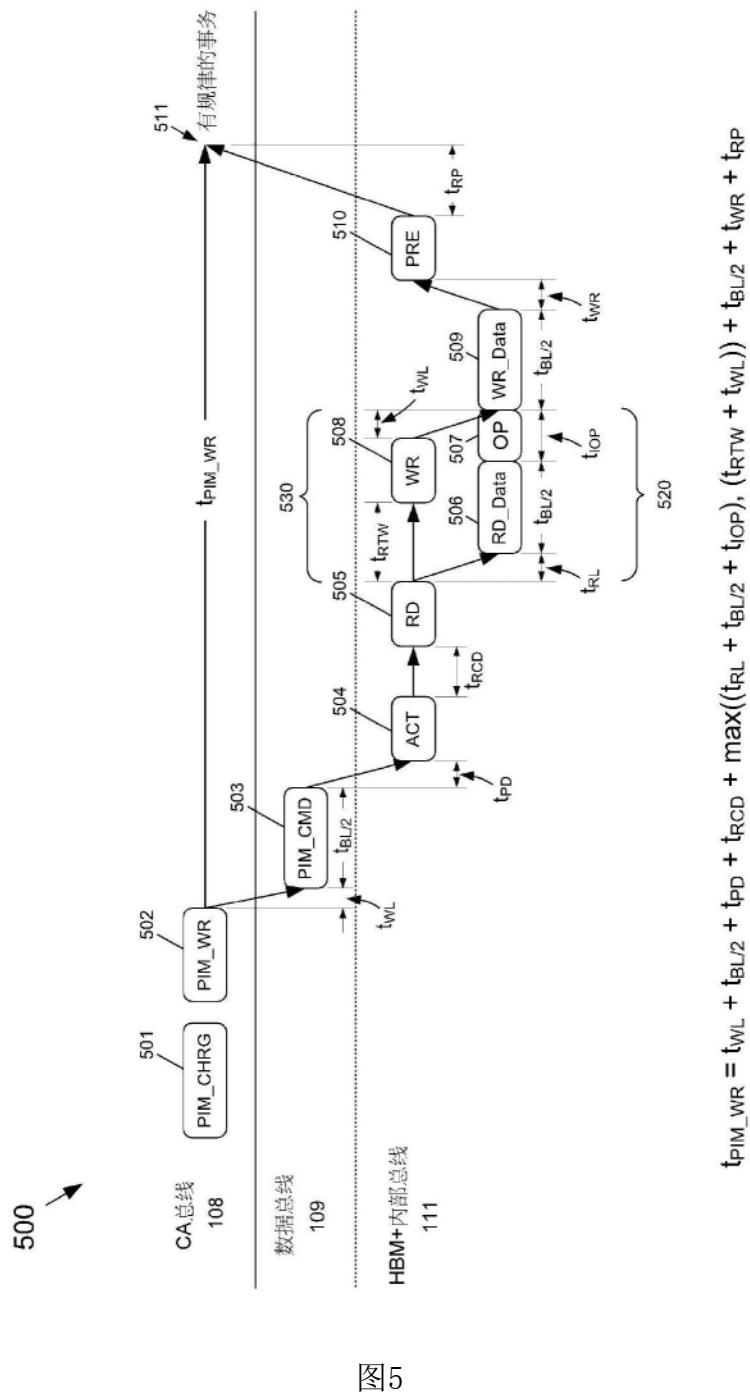

[0013] 图5绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议存储器内处理命令的时序型图,其中存储器内处理操作是针对单个地址进行或者针对高带宽存储器内处理装置中的同一行进行;

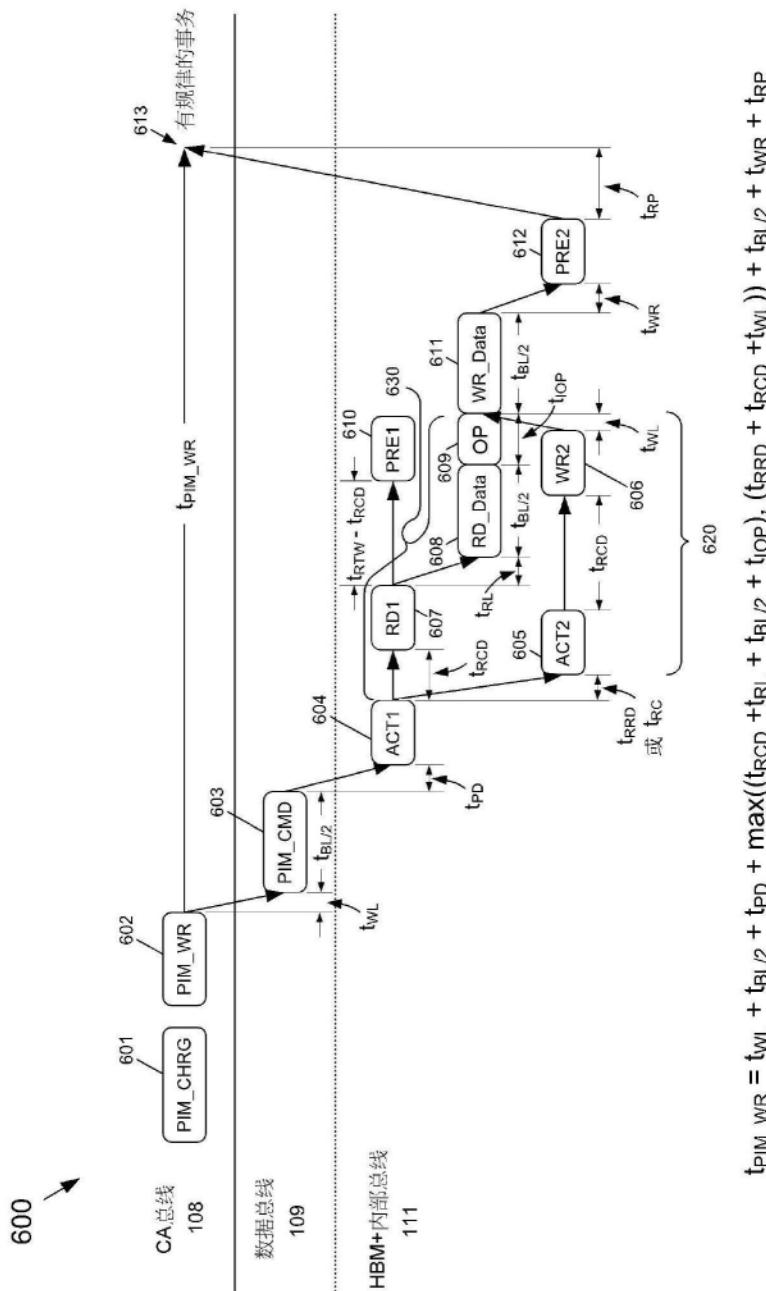

[0014] 图6绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议存储器内处理命令的时序型图,其中存储器内处理操作在同一信道中的各存储体内进行;

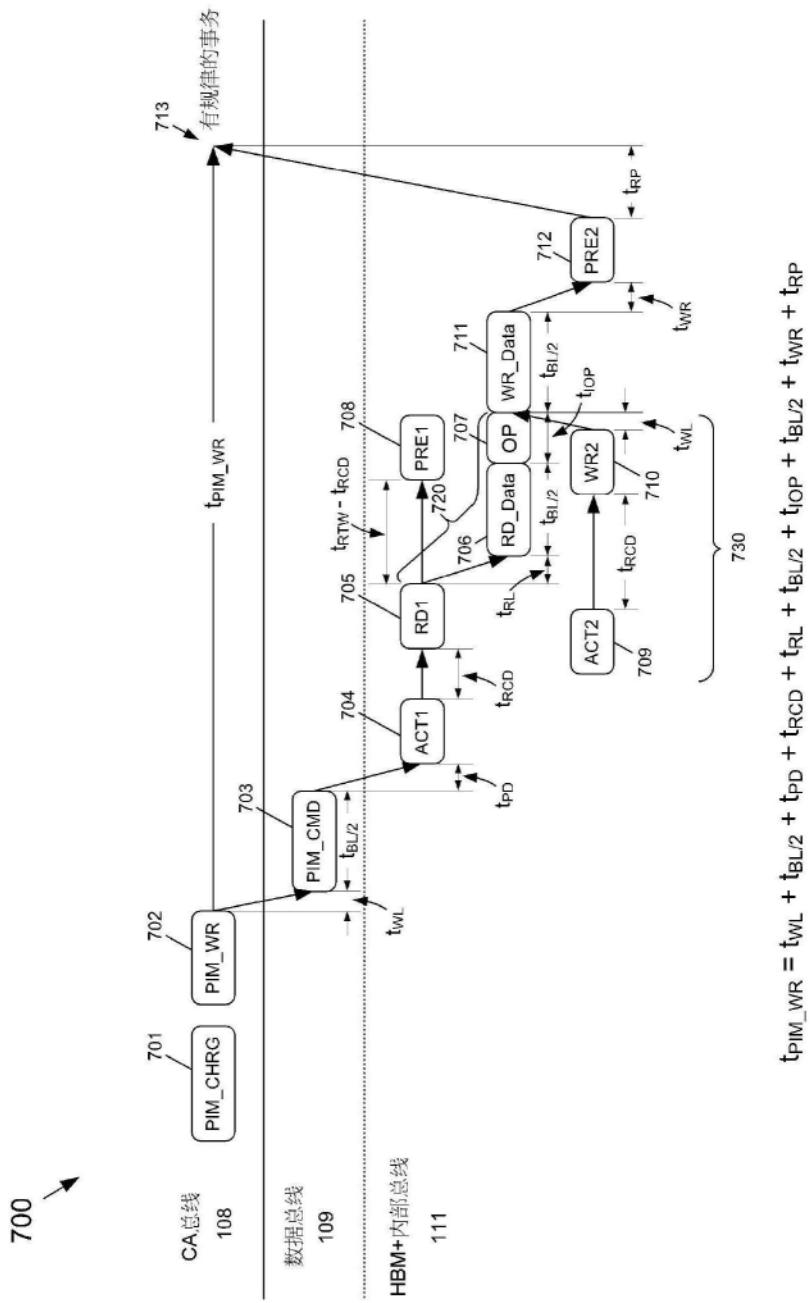

[0015] 图7绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议存储器内处理命令的时序型图,其中存储器内处理操作在不同的信道中进行;

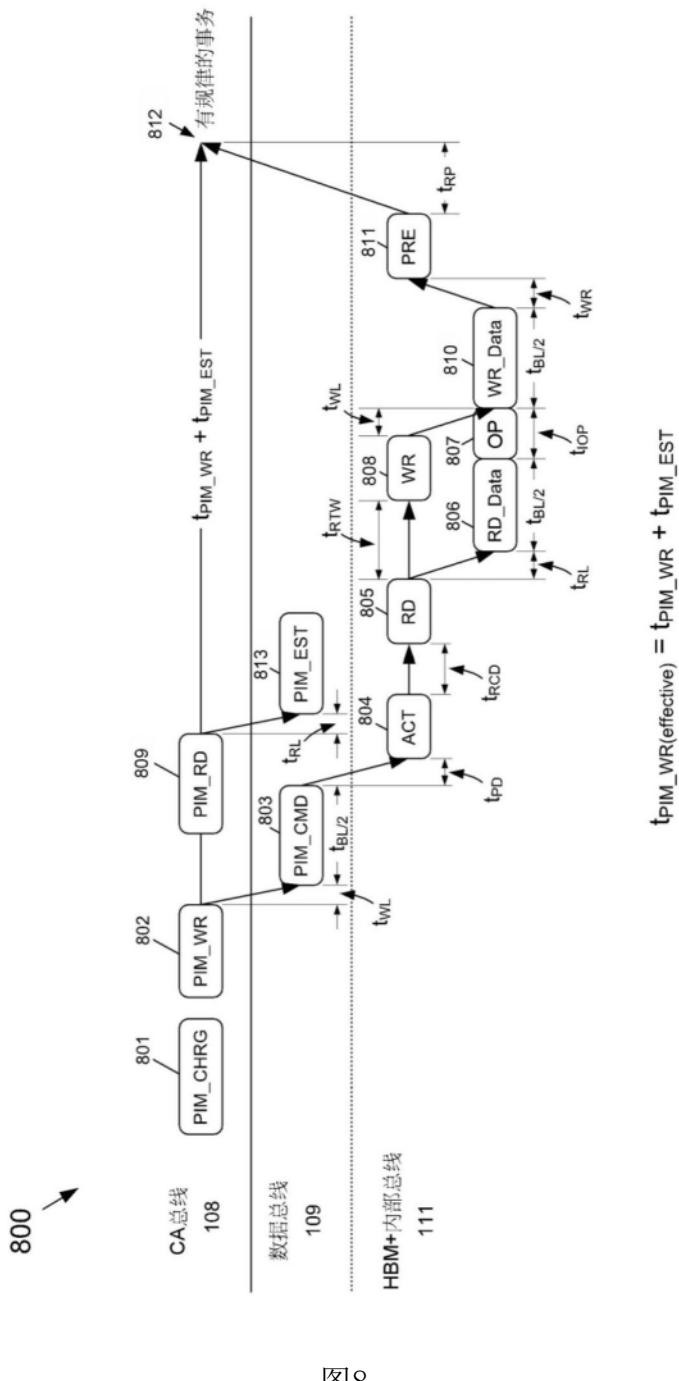

[0016] 图8绘示根据本文所公开主题的示例性两步式高带宽存储器内处理协议存储器内处理命令的时序型图,其中高带宽存储器内处理堆叠提供关于存储器内处理命令将何时完成的时间估计;

[0017] 图9绘示根据本文所公开主题的示例性两步式高带宽存储器内处理协议存储器内

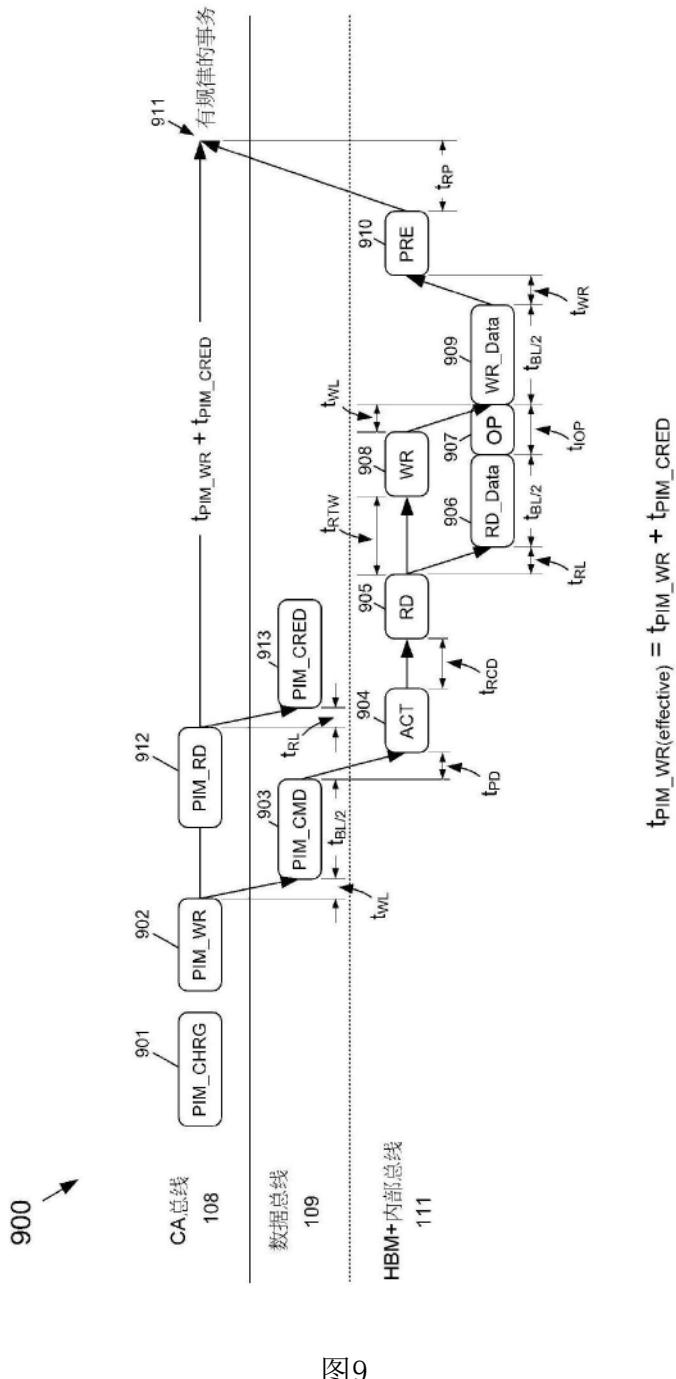

处理命令的时序型图,其中高带宽存储器内处理堆叠提供关于存储器内处理命令将何时完成的基于信用值的指示(credit-based indication);

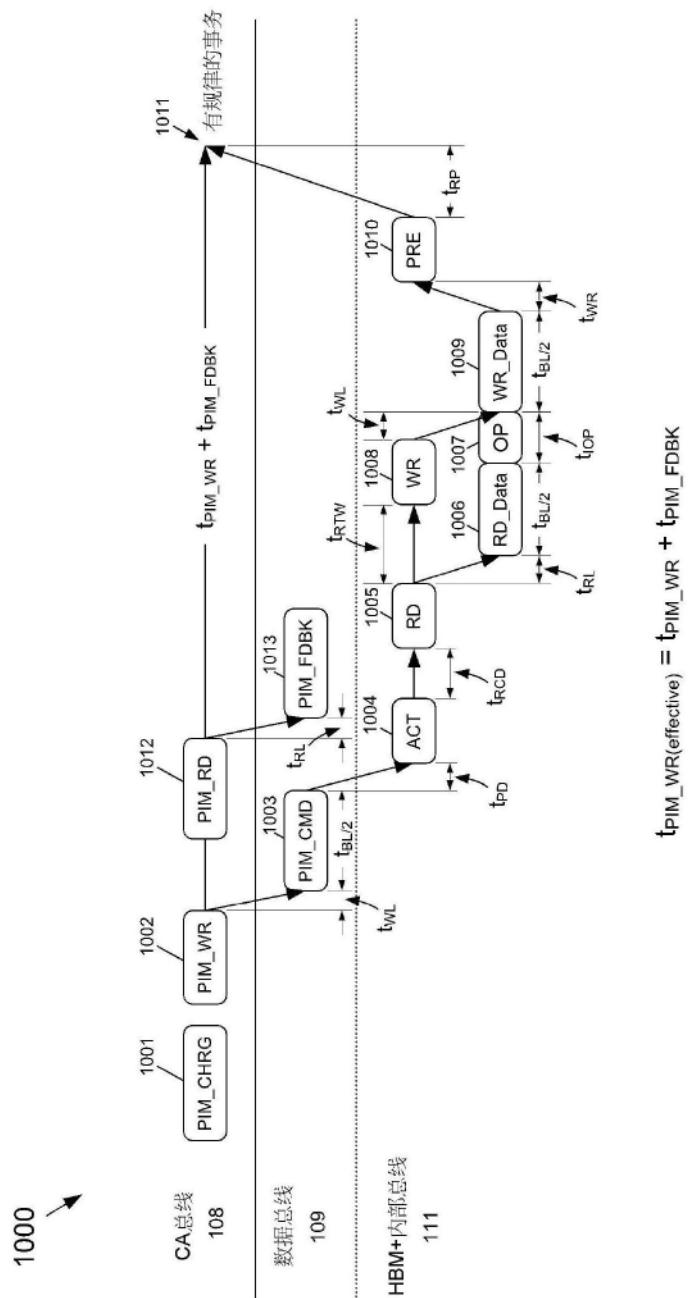

[0018] 图10绘示根据本文所公开主题的示例性两步式高带宽存储器内处理协议存储器内处理命令的时序型图,其中高带宽存储器内处理堆叠提供关于存储器内处理命令将何时完成的基于反馈的指示。

[0019] [符号的说明]

[0020] 100:高带宽存储器内处理系统;

[0021] 101:主机处理装置/主机装置;

[0022] 102:中介层;

[0023] 103:高带宽存储器内处理堆叠/堆叠;

[0024] 104:逻辑裸片/高带宽存储器内处理装置;

[0025] 105a、105b、105c、105d:高带宽存储器内处理存储装置;

[0026] 106:衬底;

[0027] 107:端子;

[0028] 108:命令/地址总线;

[0029] 109:数据总线;

[0030] 110:事务总线;

[0031] 111:高带宽存储器内处理内部总线;

[0032] 200、400、500、600、700、800、900、1000:时序型图;

[0033] 201、202、203、204、205、206、207、401、402、403、404、405、406、407、408、409、501、502、503、504、505、506、507、508、509、510、511、601、602、603、604、605、606、607、608、609、610、611、612、613、701、702、703、704、705、706、707、708、709、710、711、712、713、801、802、803、804、805、806、807、808、809、810、811、812、813、901、902、903、904、905、906、907、908、909、910、911、912、913、1001、1002、1003、1004、1005、1006、1007、1008、1009、1010、1011、1012、1013:操作;

[0034] 300:PIM\_CMD命令;

[0035] 301:ID字段;

[0036] 302:操作字段;

[0037] 303:步幅字段;

[0038] 304:旗标字段;

[0039] 305:范围字段;

[0040] 306:值字段;

[0041] 307:数目字段;

[0042] 308:来源地址1字段;

[0043] 309:来源地址2字段;

[0044] 310:目的地址1字段;

[0045] 311:目的地址2字段;

[0046] 520、530:路径/并行路径;

[0047] 620:路径/并行路径/第一并行路径;

- [0048] 630:路径/第二并行路径;

- [0049] 720:第一并行路径;

- [0050] 730:第二并行路径;

- [0051] ACT、ACT1、ACT2:激活命令;

- [0052] OP:存储器内处理操作/存储器内处理命令/存储器内处理;

- [0053] PIM\_CMD、PIM\_WR、PIM\_CMD、DST\_WR、PIM\_RD:命令;

- [0054] PIM\_EST、PIM\_CRED、PIM\_FDBK:响应;

- [0055] PRE、PRE1、PRE2:预充电命令;

- [0056] RD、RD1:读取命令;

- [0057] RD\_Data、RD\_DATA:读取数据;

- [0058] RD\_RDY:读取就绪命令;

- [0059] RSP\_E:事务误差信号;

- [0060] RSP\_R:事务响应信号;

- [0061] SRC\_RD:来源读取命令;

- [0062]  $t_{BL/2}$ :突发长度延迟/延迟/突发延迟;

- [0063]  $t_{IOP}$ 、 $t_{RC}$ 、 $t_{RL}$ 、 $t_{RRD}$ 、 $t_{RTW}$ :延迟;

- [0064]  $t_{PD}$ :传播延时/传播延时延迟/时间延迟;

- [0065]  $t_{PIM\_CRED}$ :整数个信用值;

- [0066]  $t_{PIM\_EST}$ :时间估计值;

- [0067]  $t_{PIM\_FDBK}$ :信息;

- [0068]  $t_{PIM\_WR}$ :时序/时间;

- [0069]  $t_{RCD}$ :激活延迟/延迟;

- [0070]  $t_{RP}$ :预充电延迟/延迟;

- [0071]  $t_{WL}$ :延迟/写入时间延迟/时间延时;

- [0072]  $t_{WR}$ :恢复时间延迟/延迟;

- [0073] WR、WR2:写入命令;

- [0074] WR\_Data:写入数据。

## 具体实施方式

[0075] 在以下详细说明中,阐述许多具体细节来提供对公开内容的透彻理解。然而,所属领域中的技术人员应理解,无需这些具体细节也可实践所公开的各个方面。在其他情形中,未详细阐述众所周知的方法、流程、组件及电路,以免使本文所公开的主题模糊不清。

[0076] 本说明书通篇中所提及的“一个实施例 (one embodiment)”或“实施例 (an embodiment)”意指结合所述实施例所阐述的特定特征、结构或特性可包括于本文所公开的至少一个实施例中。因此,在本说明书通篇中各处出现的短语“在一个实施例中 (in one embodiment)”或“在实施例中 (in an embodiment)”或者“根据一个实施例 (according to one embodiment)”(或具有相似含义的其他短语)可能未必皆指同一实施例。此外,在一个或多个实施例中,特定特征、结构或特性可采用任何合适的方式进行组合。就此而言,本文所用的词“示例性(exemplary)”意指“用作实例、例子或例示”。本文被阐述为“示例性”的任

何实施例不应被视为与其他实施例相比必定是优选的或有利的。另外,根据本文中的论述的上下文而定,单数用语可包括对应的复数形式且复数用语可包括对应的单数形式。还应注意,本文中所示及所论述的各个图(包括组件图)仅是出于例示目的,而并非按比例绘示。相似地,示出各种波形及时序图仅是用于例示目的。举例来说,为清晰起见,可相对于其他元件夸大元件中的一些元件的尺寸。另外,在适当情况下,在各个图中重复使用参考编号来指示对应的元件和/或类似元件。

[0077] 本文所用术语仅是用于阐述特定示例性实施例的目的,而非旨在限制所主张的主题。除非上下文另外清楚地指明,否则本文所用单数形式“一(a、an)”及“所述(the)”旨在也包括复数形式。还应理解,当在本说明书中使用用语“包括(comprises和/或comprising)”时,是指明所陈述特征、整数、步骤、操作、元件和/或组件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、组件和/或其群组的存在或添加。本文所用用语“第一(first)”、“第二(second)”等被用作位于所述用语后面的名词的标签,且除非明确定义,否则所述用语并不隐含着任何类型的排序(例如,空间、时间、逻辑等)。此外,在两个或更多个图中可使用相同的参考编号来指代具有相同或相似的功能的部件、组件、区块、电路、单元或模块。然而,这种用法仅是为了使例示简洁且易于论述起见;所述用法并不隐含着这种组件或单元的构造细节或架构细节在所有实施例中是相同的或者这些通常提及的部件/模块是实施本文中所公开特定实施例的教示内容的唯一方式。

[0078] 除非另外定义,否则本文所用所有用语(包括技术及科学用语)的意义均与本主题所属领域中的一般技术人员所通常理解的意义相同。还应理解,用语(例如在常用词典中所定义的用语)应被解释为具有与其在相关技术的上下文中的含义一致的含义,且除非在本文中明确定义,否则不应将其解释为具有理想化或过于正式的意义。

[0079] 本文所公开主题涉及一种用于高带宽存储器内处理(high bandwidth PIM,HBM+)系统的准同步接口协议。也就是说,本文所公开主题在高带宽存储器内处理系统与主机装置之间提供一种包括确定的延迟及不确定的延迟两种延迟的接口;由此,提供准同步接口协议。通过本文所公开的准同步协议进行的通信可与一个或多个时钟信号同步,但与特定操作(例如存储器内处理操作)的完成相关联的特定延迟可具有确定的延迟或不确定的延迟。可提供确定的延迟的存储器内处理操作可使用一步式高带宽存储器内处理协议实行,而可提供不确定的延迟的存储器内处理操作可使用两步式高带宽存储器内处理协议实行。

[0080] 图1绘示根据本文所公开主题的高带宽存储器内处理系统100的示例性实施例的一部分的剖视图。高带宽存储器内处理系统100可包括主机处理装置(主机装置)101、中介层(interposer)102及高带宽存储器内处理堆叠103。高带宽存储器内处理堆叠103可包括逻辑电路或裸片104以及排列在逻辑裸片104的顶表面上的多个高带宽存储器内处理存储装置105a到105d。主机装置101及高带宽存储器内处理堆叠103可被固定到中介层102的顶表面。

[0081] 在一个实施例中,主机装置101可为但不限于中央处理器(central processing unit,CPU)、图形处理单元(graphics processing unit,GPU)、图形加速器(graphics accelerator)或现场可编程门阵列(Field Programmable Gate Array,FPGA)。

[0082] 高带宽存储器内处理存储装置105a到105d可被划分成两个信道,其中每个信道可存在16个存储体。高带宽存储器内处理存储装置105a到105d中的一者或者还可包括存储

器内处理功能及有规律的数据存储功能,例如传统的读取及写入操作。高带宽存储器内处理存储装置105a到105d可比主机装置101更高效地提供在高带宽存储器内处理存储装置中提供的存储器内处理功能。逻辑裸片104可包括用于控制高带宽存储器内处理存储装置105a到105d中的存储器内功能的逻辑功能。高带宽存储器内处理内部总线111将逻辑裸片104连接到高带宽存储器内处理存储装置105a到105d中的每一者。高带宽存储器内处理内部总线111可包括多条地址线、多条命令线、多条数据线和/或一条或多条其他信号线。应理解,尽管在高带宽存储器内处理堆叠103中示出仅四个高带宽存储器内处理存储装置105a到105d,然而任何数目的高带宽存储器内处理存储装置105a到105d均可形成高带宽存储器内处理堆叠103。另外,即使在图1中绘示了高带宽存储器内处理系统100的仅一部分,然而应理解,可存在可贴合到中介层102的顶表面的额外的高带宽存储器内处理堆叠103。

[0083] 中介层102可固定到衬底106的顶表面。衬底106可包括端子107,端子107可用来提供与其他装置(图中未示出)的电连接。除了为主机装置101及高带宽存储器内处理堆叠103提供结构基础之外,中介层102还在主机装置101与高带宽存储器内处理堆叠103之间提供电连接。在一个实施例中,中介层102可包括电耦合在主机装置与高带宽存储器内处理堆叠103之间的命令/地址(command/address,CA)总线108、数据总线109及事务总线110。应理解,中介层102可包括图中未示出的另外的电连接。

[0084] 命令/地址总线108、数据总线109、及事务总线110中的每一者可包括多条线和/或多个位。在一个实施例中,事务总线110可包含事务响应信号RSP\_R及事务误差信号RSP\_E。命令/地址总线108、数据总线109及事务总线110可采用同步型方式在高带宽存储器内处理系统100内运行。也就是说,命令/地址总线108、数据总线109及事务总线110与一个或多个时钟信号同步运行。

[0085] 在一个实施例中,对于其中命令或事务的发出与响应的输出之间的时间(无论是基于有规律的数据存储功能和/或存储器内处理功能)或者高带宽存储器内处理堆叠103对另一个命令或事务作好准备的时刻是确定的情形,高带宽存储器内处理系统100可包括用于在主机装置101与高带宽存储器内处理堆叠103之间传送命令及数据的一步式高带宽存储器内处理协议。对于其中命令或事务的发出与响应的输出之间的时间(无论是基于有规律的数据存储功能和/或存储器内处理功能)或者高带宽存储器内处理堆叠103对另一个命令或事务做好准备的时刻是不确定的情形,高带宽存储器内处理系统100还可包括用于在主机装置101与高带宽存储器内处理堆叠103之间传送命令及数据的两步式高带宽存储器内处理协议。本文所用用语“准同步接口”意指供确定的通信及不确定的通信两者或事务通过的接口。

[0086] 一步式高带宽存储器内处理协议一般旨在用于其中主机装置101不等待结果的相对有规律的数据存储及简单存储器内处理操作。也就是说,命令的发出与响应的输出之间的时间或延迟是确定的,使得主机装置101可在命令的发出与响应的输出之间临时执行其他操作。作为另外一种选择,主机装置101可被排程成在确定的延迟结束时恢复有规律的事务。典型地,简单存储器内处理操作包括一个或两个来源地址和/或目的地址,且不包括步幅参数(stride parameter)。

[0087] 两步式高带宽存储器内处理协议一般旨在用于其中主机装置101可等待结果的更复杂的存储器内处理操作,例如但不限于许多来源地址和/或目的地址、矩阵操作、包括步

幅的操作。命令的发出与响应的输出之间的时间或延迟是不确定的,使得主机装置101可在命令的发出与响应的输出之间或者在命令的发出与高带宽存储器内处理堆叠103准备好接收另一命令或事务的时刻之间临时执行其他操作。表2阐述了一些示例性高带宽存储器内处理存储器内处理命令类别及时序估计。

[0088] 图2绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议命令的概括时序型图200。应理解,时序型图200并非按比例绘示且仅旨在绘示示例性存储器内处理命令的一步式高带宽存储器内处理协议的相对顺序。时序型图200包括与不同的总线相关联的箭头以大体表示特定总线的单向性质或双向性质。具体来说,从左指向右的箭头表示从主机装置101发送到高带宽存储器内处理堆叠103的通信、事务或信号,而从右指向左的箭头表示从高带宽存储器内处理堆叠103发送到主机装置101的通信、事务或信号。在本文所公开的所有时序型图中,被表示为通过高带宽存储器内处理内部总线111发生的事务及操作对位于高带宽存储器内处理堆叠103外部的装置而言是不可见的。

[0089] 在图2中的201处,主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令,逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电,并锁定所述一个或多个所选择信道中的相关存储体以保证相关存储体对主机装置101以及即将到来的PIM\_CMD命令的所有权。紧接在PIM\_CHRG命令之后,主机装置101通过命令/地址总线108在202处发出PIM\_WR命令。表1阐述了PIM\_CHRG命令及PIM\_WR命令的示例性物理信号参数。

[0090] 表1.PIM\_CHRG命令及PIM\_WR命令的示例性物理信号参数。

| [0091] | 功能       | CKE_0 |      | R[0] | R[1] | R[2] | R[3] | R[4] | R[5] |

|--------|----------|-------|------|------|------|------|------|------|------|

|        |          | 前一循环  | 当前循环 |      |      |      |      |      |      |

|        | PIM_CHRG | H     | H    | H    | L    | H    | X    | X    | X    |

|        | PIM_WR   | H     | H    | L    | L    | L    | X    | X    | X    |

[0092] 在表1中,在顶部示出基于当前的电子器件工程联合委员会(Joint Electron Device Engineering Council, JEDEC)标准的示例性引脚标识。“H”表示高逻辑电压电平,且“L”表示低逻辑电压电平。“X”表示“不用理会(do not care)”逻辑电压电平。

[0093] 图3绘示根据本文所公开主题的PIM\_CMD命令300的内容的示例性配置方式。PIM\_CMD含有实际存储器内处理命令,且是通过数据总线109发送而非通过命令/地址总线108发送。逻辑裸片104对PIM\_CMD进行解码并在高带宽存储器内处理堆叠103内部发出命令以完成PIM\_CMD命令中所含有的存储器内处理操作。在一个实施例中,尽管并非所有存储器内处理命令均可使用PIM\_CMD的所有字段,然而PIM\_CMD具有固定大小或长度。

[0094] 如图3中所绘示的示例性配置方式中所示,PIM\_CMD命令300可包括ID字段301、操作字段302、步幅字段303、旗标字段304、范围字段305、值字段306、数目字段307、来源地址1字段308、来源地址2字段309、目的地址1字段310及目的地址2字段311。在一个实施例中, ID字段301可包括三个位,且操作字段302可包括三个位。步幅字段303可包括16个位。旗标字段304可包括两个位,且范围字段305可包括32个位。值字段306可包括64个位。数目字段307可包括八个位。来源地址1字段308可包括32个位,且来源地址2字段309可包括32个位。目的

地址1字段310可包括32个位,且目的地址2字段311可包括32个位。也可能存在其他的和/或额外的字段、字段配置方式和/或字段大小。

[0095] 返回图2,在202处通过命令/地址总线108发送的PIM\_WR命令用于在203处通过数据总线109发送PIM\_CMD。在一个实施例中,在数据总线109上出现PIM\_CMD命令可紧接在在命令/地址总线108上出现PIM\_WR命令之后。在另一个实施例中,在数据总线109上出现PIM\_CMD命令可与在命令/地址总线108上出现PIM\_WR命令至少局部地同时发生。

[0096] 响应于PIM\_CMD,此概括说明中的逻辑裸片104通过高带宽存储器内处理内部总线111在204处发送来源读取命令SRC\_RD以读取将作为PIM\_CMD中所包含存储器内处理操作的来源的数据。对此实例来说,在205处执行存储器内处理操作OP。在206处使用逻辑裸片104已发送的DST\_WR命令将存储器内处理操作的结果写入到目的地址。在207处,存储器内处理操作已完成,且高带宽存储器内处理堆叠103准备好从主机装置101接收另外的有规律的操作、存储器内处理操作和/或其他事务。

[0097] 图2中所绘示的一步式高带宽存储器内处理协议的时序是确定的;因此,在202处发出PIM\_WR命令的时刻与高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令和/或事务(即,恢复有规律的事务)的时刻之间的时间在图2中被表示为 $t_{PIM\_WR}$ 。也就是说,时序 $t_{PIM\_WR}$ 可被视为在可由主机装置101向高带宽存储器内处理堆叠103中的同一信道/存储体发出新命令或事务之前的最短时间。为表示一步式高带宽存储器内处理协议的时序的确定性性质,图2中所表示的各个命令、事务及响应之间的箭头被示出为实线箭头。图5至图7分别绘示多个不同的确定性时序情景的时序型图。

[0098] 图4绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议命令的概括时序型图400。应理解,时序型图400并非按比例绘示且仅旨在绘示示例性存储器内处理命令的两步式高带宽存储器内处理协议的相对顺序。与图2所示时序型图200相似,时序型图400包括与不同的总线相关联的箭头以大体表示特定总线的单向性质或双向性质。

[0099] 在图4中,主机装置101通过命令/地址总线108发出PIM\_CHRG命令,此在图4中出于空间考虑而未示出。如同一步式高带宽存储器内处理协议一样,PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令,逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电,并锁定整个高带宽存储器内处理堆叠103以保证堆叠103对主机装置101的所有权。紧接在PIM\_CHRG命令(同样未示出)之后,在401处主机装置101通过命令/地址总线108发出PIM\_WR命令。在402处,主机装置101在数据总线109上发出PIM\_CMD。

[0100] 响应于PIM\_CMD,逻辑裸片104通过高带宽存储器内处理内部总线111在403处发送来源读取命令SRC\_RD以读取PIM\_CMD中所表示的操作的来源数据。在404处执行存储器内处理操作OP。在405处使用DST\_WR命令将存储器内处理操作的结果写入到目的地址。对于图4中所绘示的示例性时序来说,在406处,逻辑裸片104通过事务总线110向主机装置101发送读取就绪命令RD\_RDY。在407处,主机装置101通过命令/地址总线108发送读取命令RD。在408处,逻辑裸片104通过数据总线109输出读取数据RD\_DATA,且在409处,主机装置101可产生有规律的操作及事务。对于一些两步式高带宽存储器内处理协议存储器内处理命令来说,逻辑裸片104不向主机装置101发送读取就绪命令RD\_RDY,而是向主机装置101发送关于存储器内处理操作何时可完成的指示以使主机装置101可临时对其他操作进行排程。结合

图8至图10阐述发送这种指示的逻辑裸片104的一些示例性情景。

[0101] 与一步式高带宽存储器内处理协议相比,两步式高带宽存储器内处理协议具有不确定的时序特性,这是由于存储器内处理操作OP对两步式高带宽存储器内处理协议而言一般更复杂且可根据存储器内处理操作而花费不确定的时间量。举例来说,将对100x 100矩阵执行的矩阵转置存储器内处理操作可比对10x 10矩阵进行的相同的矩阵转置存储器内处理操作花费更长时间,即使存储器内处理转置操作在这两种情形中是相同的操作。为表示与两步式高带宽存储器内处理操作相关联的时序一般是不确定的,图4中在命令与响应之间表示的箭头中的一些箭头被示出为粗的虚线箭头。举例来说,401处的PIM\_WR命令与406处的RD\_RDY响应之间的箭头以及406处的RD\_RDY响应与407处的RD命令之间的箭头被示出为粗的虚线箭头以表示两步式高带宽存储器内处理协议的不确定的性质。所述不确定的性质还由404处的存储器内处理OP与405处的DST\_WR响应之间的粗的虚线箭头表示。

[0102] 表2阐述了一些示例性HBM+PIM命令类别及时序估计。

| [0103] | #  | 类别    | 功能实例     | 投影 $t_{IOp}$<br>(循环) | 操作类型  |

|--------|----|-------|----------|----------------------|-------|

|        | 1. | 数据原子性 | 读取-修改-写入 | 1                    | 寄存器复制 |

|        |    |      |                                           |      |              |

|--------|----|------|-------------------------------------------|------|--------------|

| [0104] | 2. | 数据复制 | 测试及设定                                     | 2    | 寄存器比较<br>+复制 |

|        |    |      | 比较及交换 (CAS)                               | 2    | 寄存器比较<br>+复制 |

|        |    |      | 递增                                        | 1    | 寄存器 ALU      |

| 3.     | 3. | 数据重塑 | 存储器复制                                     | 1    | 寄存器复制        |

|        |    |      | 存储器设定                                     | 1    | 寄存器复制        |

| 4.     | 4. | 数据简化 | 转置、打包/解包<br>(Pack/unpack)、交换              | 规定协议 | 多次复制         |

|        |    |      | 种群计数 (Popcount)、<br>累加、逐位运算、求和、<br>最小化、点积 |      | 多次复制、<br>ALU |

|        | 5. | 特定功能 | 映射功能、散列、图案<br>匹配                          | 规定协议 | 多次复制、<br>ALU |

[0105] 从主机装置101的角度来看,一步式高带宽存储器内处理协议的确定性性质可被视为提供基于主机的命令排程协议。举例来说,图5绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议存储器内处理命令的时序型图500,其中存储器内处理操作是针对单个地址进行或者针对高带宽存储器内处理装置中的同一行进行。应理解,时序型图500并非按比例绘示且仅旨在绘示针对单个地址进行或者针对高带宽存储器内处理装置中的同一行进行的示例性存储器内处理操作的一步式高带宽存储器内处理协议的相对顺序。

[0106] 在501处,主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令,逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电,并锁定所述一个或多个所选择

信道中的相关存储体以保证在存储器内处理操作期间对主机装置101的所有权。紧接着在PIM\_CHRG命令之后，主机装置101通过命令/地址总线108在502处发出PIM\_WR命令。在503处，主机装置101通过数据总线109发送PIM\_CMD。在此实例中，将PIM\_CMD视为使高带宽存储器内处理装置104中的存储器位置中的值递增的命令。PIM\_WR命令与PIM\_CMD命令之间的时间延时是 $t_{WL}$ ，即，在发送PIM\_WR命令与发送PIM\_CMD命令之间必须等待的写入时间延迟。对双倍数据速率(double data rate, DDR)高带宽存储装置而言，PIM\_CMD命令花费突发长度延迟 $t_{BL/2}$ 。

[0107] 逻辑裸片104对PIM\_CMD进行解码并通过高带宽存储器内处理内部总线111在504处向高带宽存储器内处理堆叠103发出ACT命令将存在传播延时 $t_{PD}$ 所选择行的激活延迟是 $t_{RCD}$ 。在505处，逻辑裸片104发出读取命令RD来加载所选择的来源数据。沿路径520读取所选择数据的延迟是 $t_{RL}$ 。在506处，以延迟 $t_{BL/2}$ 来读取所选择的来源数据。在507处，以延迟 $t_{IOP}$ 来执行存储器内处理操作OP。在此实例中，存储器内处理操作OP是对位于高带宽存储器内处理装置104中的存储位置中的值进行递增，这是相对不复杂的存储器内处理操作。

[0108] 在图5中由530表示的并行路径中，由于将在507处在存储器内处理命令OP结束时将数据回写到存储器，因此逻辑裸片104在延迟 $t_{RTW}$ 之后在508处发出写入命令WR。与写入命令WR相关联的延迟是 $t_{WL}$ 。在一个实施例中，逻辑裸片104在508处确定恰当的时间来发送写入命令WR，以使时序是正确的，从而在509处写入所得数据。

[0109] 在509处，响应于写入命令WR，以突发长度延迟 $t_{BL/2}$ 将存储器内处理操作OP的结果回写到存储器。在将结果回写到存储器之后的恢复时间延迟是 $t_{WR}$ 。在510处，逻辑裸片104针对已被写入所述结果的行发出预充电命令PRE，且接着在主机装置101可在511处向高带宽存储器内处理堆叠103发出另一事务和/或另一些命令之前出现预充电延迟 $t_{RP}$ 。

[0110] 因此，对其中存储器内处理操作是针对单个地址进行或者针对高带宽存储器内处理装置中的同一行进行的这一情景而言，在502处发出PIM\_WR命令的时刻与在511处高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令和/或事务的时刻之间的时间 $t_{PIM\_WR}$ 被确定为 $t_{PIM\_WR} = t_{WL} + t_{BL/2} + t_{PD} + t_{RCD} + \max((t_{RL} + t_{BL/2} + t_{IOP}), (t_{RTW} + t_{WL})) + t_{BL/2} + t_{WR} + t_{RP}$ ，其中使用图5中路径520与路径530之间的最大延迟来定义 $t_{PIM\_WR}$ 。路径520的延迟是 $(t_{RL} + t_{BL/2} + t_{IOP})$ ，而路径530的延迟是 $(t_{RTW} + t_{WL})$ 。

[0111] 在图6中绘示了也可被视为提供基于主机的命令排程协议的另一种一步式高带宽存储器内处理协议情景。具体来说，图6绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议存储器内处理命令的时序型图600，其中存储器内处理操作在同一信道中的存储体内进行。应理解，时序型图600并非按比例绘示且仅旨在绘示针对同一信道中的存储体进行的示例性存储器内处理操作的一步式高带宽存储器内处理协议的相对顺序。

[0112] 在601处，主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令，逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电，并锁定所述一个或多个所选择信道中的相关存储体以保证在存储器内处理操作期间对主机装置101的所有权。紧接着在PIM\_CHRG命令之后，主机装置101通过命令/地址总线108在602处发出PIM\_WR命令。在603处，主机装置101通过数据总线109发送PIM\_CMD。在此实例中，将PIM\_CMD视为将存储位置B设定成与存储位置A相等的命令，其中位置A及位置B处于高带宽存储器内处理装置104中同

一信道中的存储体内。PIM\_WR命令与PIM\_CMD命令之间的写入时间延迟是 $t_{WL}$ 。对双倍数据速率高带宽存储装置而言，PIM\_CMD命令花费突发延迟 $t_{BL/2}$ 。

[0113] 响应于603处的PIM\_CMD，逻辑裸片104在604处通过高带宽存储器内处理内部总线111向高带宽存储器内处理堆叠103发送激活命令ACT1以激活第一来源数据地址(即，位置A)。逻辑裸片104对PIM\_CMD进行解码且接着在604处发出ACT1命令的传播延时延迟是 $t_{PD}$ 。

[0114] 在第一并行路径620中，逻辑裸片104在605处发出激活命令ACT2以激活第二来源数据地址(即，位置B)。发出ACT1命令与发出ACT2命令之间的延迟是 $t_{RRD}$ 或 $t_{RC}$ 。如果存储器内处理操作是在两个不同的存储体之间进行，则延迟(一般来说)将为 $t_{RRD}$ 。(应注意，如果来源地址与目的地址位于处于同一存储体群组内的两个不同的存储体之间，则延迟将为 $t_{RRDL}$ ；然而，如果来源地址与目的地址位于处于不同的存储体群组中的两个不同的存储体中，则延迟将为 $t_{RRDF}$ 。)如果存储器内处理操作处于同一存储体内，则延迟将为 $t_{RC}$ 。在此并行路径620中，在逻辑裸片104在606处发出写入命令WR2之前也存在延迟 $t_{RCD}$ ，且在写入命令WR2之后将存在延迟 $t_{WL}$ 。

[0115] 在第二并行路径630中，响应于激活命令ACT1，逻辑裸片104在607处发出读取命令RD1。在激活命令ACT1之后及在读取命令RD1之前存在延迟 $t_{RCD}$ 。在发出读取命令RD1的时间与608的读取数据RD\_Data操作之间存在延迟 $t_{RL}$ 。在608处以突发长度延迟 $t_{BL/2}$ 来读取数据。在609处，以延迟 $t_{IOP}$ 来执行存储器内处理操作OP。

[0116] 为写入从存储器内处理操作OP得到的数据，在逻辑裸片104的读取命令RD1之后到在610处发出预充电命令PRE1之间存在延迟 $t_{RTW} - t_{RCD}$ 。在611处，响应于写入命令WR2，以延迟 $t_{BL/2}$ 将存储器内处理操作OP的结果回写到存储器。在将结果回写到存储器之后的恢复时间延迟是 $t_{WR}$ 。在612处，逻辑裸片104针对已被写入所述结果的行发出预充电命令PRE2以进行恢复，且接着在主机装置101可在613处向高带宽存储器内处理堆叠103发出另一些事务和/或另一些命令之前出现延迟 $t_{RP}$ 。

[0117] 因此，对其中存储器内处理操作是针对同一信道中的存储体进行的这一情景而言，在602处发出PIM\_WR命令的时刻与在613处高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令的时刻之间的时间 $t_{PIM\_WR}$ 被确定为

[0118]  $t_{PIM\_WR} = t_{WL} + t_{BL/2} + t_{PD} + \max((t_{RCD} + t_{RL} + t_{BL/2} + t_{IOP}), (t_{RRD} + t_{RCD} + t_{WL})) + t_{BL/2} + t_{WL} + t_{RP}$ ，其中使用图6中路径620与路径630之间的最大延迟来定义 $t_{PIM\_WR}$ 。路径620的延迟是 $(t_{RCD} + t_{BL/2} + t_{IOP})$ ，而路径630的延迟是 $(t_{RRD} + t_{RCD} + t_{WL})$ 。

[0119] 在图7中绘示了也可被视为提供基于主机的命令排程协议的再一种一步式高带宽存储器内处理协议情景。具体来说，图7绘示根据本文所公开主题的示例性一步式高带宽存储器内处理协议存储器内处理命令的时序型图700，其中存储器内处理操作在不同的信道中进行。应理解，时序型图700并非按比例绘示且仅旨在绘示在不同的信道中进行的示例性存储器内处理操作的一步式高带宽存储器内处理协议的相对顺序。

[0120] 在701处，主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令，逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电，并锁定所述一个或多个所选择信道中的相关存储体以保证相关存储体在存储器内处理操作期间对主机装置101的所有权。紧接着在PIM\_CHRG命令之后，主机装置101通过命令/地址总线108在702处发出PIM\_WR命

令。主机装置101在703处通过数据总线109发送PIM\_CMD。PIM\_WR命令与PIM\_CMD命令之间的时间延迟是 $t_{WL}$ ,即,在发送PIM\_WR命令与发送PIM\_CMD命令之间必须等待的时间。对双倍数据速率高带宽存储装置而言,PIM\_CMD命令具有突发长度延迟 $t_{BL/2}$ 。

[0121] 响应于703处的PIM\_CMD,逻辑裸片104在704处通过高带宽存储器内处理内部总线111向高带宽存储器内处理堆叠103发送激活命令ACT1。逻辑裸片104对PIM\_CMD进行解码且接着在704处发出ACT1命令的时间延迟是 $t_{PD}$ 。在延迟 $t_{RCD}$ 后,逻辑裸片104在705处发出读取命令RD1。在第一并行路径720中,在以突发长度延迟 $t_{BL/2}$ 在706处读取数据RD\_Data之前,存在延迟 $t_{RL}$ 。在707处以延迟 $t_{IOP}$ 来执行存储器内处理操作OP。为写入从存储器内处理操作OP得到的数据,在逻辑裸片104在705处的读取命令RD1之后到在708处发出预充电命令PRE1之间存在延迟 $t_{RTW} - t_{RCD}$ 。

[0122] 在第二并行路径730中,逻辑裸片104在709处发出激活命令ACT2。在其中存储器内处理操作是在不同的信道中进行的情形中,就逻辑裸片104何时发出激活命令ACT2而言不存在限制条件。在逻辑裸片104在710处发出写入命令WR2之前存在延迟 $t_{RCD}$ 。在发出写入命令WR2的时间直到在711处已写入数据WR\_Data之间存在延迟 $t_{WL}$ 。在711处以突发长度延迟 $t_{BL/2}$ 来写入数据。在逻辑裸片104在712处针对已被写入所述结果的行发出预充电命令PRE2以进行恢复之前存在延迟 $t_{WR}$ ,且接着在主机装置101可在713处向高带宽存储器内处理堆叠103发出另一事务和/或另一些命令之前出现延迟 $t_{RP}$ 。

[0123] 因此,对其中存储器内处理操作是在不同的信道中进行的这一情景而言,在702处发出PIM\_WR命令的时刻与在713处高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令的时刻之间的时间 $t_{PIM\_WR}$ 被确定为

$$[0124] \quad t_{PIM\_WR} = t_{WL} + t_{BL/2} + t_{PD} + t_{RCD} + t_{RL} + t_{BL/2} + t_{IOP} + t_{BL/2} + t_{WR} + t_{RP}.$$

[0125] 图8至图10绘示示例性两步式高带宽存储器内处理协议存储器内处理命令的时序型图,其中存储器内处理操作比图5至图7中所考虑的一步式高带宽存储器内处理协议命令更复杂,且因此,所述存储器内处理操作的完成具有总体不确定的时序。因此,一些两步式高带宽存储器内处理协议存储器内处理命令可被视为提供基于客户机的命令排程协议,且高带宽存储器内处理堆叠可提供关于存储器内处理命令何时可完成的指示,以考虑到一些两步式高带宽存储器内处理协议存储器内处理命令的不确定性性质。就此来说,逻辑裸片104可向主机装置101提供关于复杂的存储器内处理命令的完成时间的指示。

[0126] 在一个实施例中,关于有效时间的指示可包括时间估计。在另一个实施例中,关于有效时间的指示可包括基于信用值的值。在再一个实施例中,关于有效时间的指示可包括基于重试的反馈(retry-based feedback),其中主机装置101被给予关于何时轮询高带宽存储器内处理堆叠以查看存储器内处理操作是否已完成的指示。被提供到主机装置101的关于存储器内处理命令的完成时间的指示可基于以下或者可从以下来预测(但并非仅限于以下):自动日志的内容、历史统计信息、所计算估计值、正在进行的讯务和/或存储器内处理操作的最大边界。

[0127] 应注意,在以下图8至图10的时序型图中绘示的两步式高带宽存储器内处理协议存储器内处理命令不使用图1中所绘示的事务总线110。而是,图8至图10中所绘示的两步式高带宽存储器内处理协议存储器内处理命令利用命令/地址总线108、数据总线109及高带宽存储器内处理内部总线111来向主机装置101提供关于存储器内处理命令完成所需的有

效时间的指示。

[0128] 图8绘示根据本文所公开主题的示例性两步式高带宽存储器内处理协议存储器内处理命令的时序型图800,其中高带宽存储器内处理堆叠103提供关于存储器内处理命令将何时完成的时间估计。应理解,时序型图800并非按比例绘示且仅旨在绘示在高带宽存储器内处理堆叠提供关于示例性存储器内处理操作将何时完成的时间估计时两步式高带宽存储器内处理协议的相对顺序。

[0129] 在801处,主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令,逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电,并锁定高带宽存储器内处理堆叠103以保证高带宽存储器内处理堆叠在存储器内处理操作期间对主机装置101的所有权。紧接在PIM\_CHRG命令之后,主机装置101通过命令/地址总线108在802处发出PIM\_WR命令。主机装置101在803处通过数据总线109发送PIM\_CMD。PIM\_WR命令与PIM\_CMD命令之间的时间延迟是 $t_{WL}$ 。对双倍数据速率高带宽存储装置而言,PIM\_CMD命令花费突发长度延迟 $t_{BL/2}$ 。

[0130] 响应于803处的PIM\_CMD,逻辑裸片104在804处通过高带宽存储器内处理内部总线111向高带宽存储器内处理堆叠103发送激活命令ACT。逻辑裸片104对PIM\_CMD进行解码且接着在804处发出ACT命令的时间延迟是 $t_{PD}$ 。在延迟 $t_{RCD}$ 后,逻辑裸片104在805处发出读取命令RD。在以突发长度延迟 $t_{BL/2}$ 在806处读取数据RD\_Data之前,存在延迟 $t_{RL}$ 。以延迟 $t_{TOP}$ 在807处执行存储器内处理操作OP;然而,由于存储器内处理操作OP是复杂的,因此与存储器内处理操作OP相关联的延迟是不确定的。

[0131] 逻辑裸片104还在805处发出读取命令RD之后经过延迟 $t_{RTW}$ 后、但在807处已完成存储器内处理操作OP之前,在808处发出写入命令WR。存储器内处理操作OP的结果在发出写入命令WR之后经过延迟 $t_{WL}$ 后在810处被写入到存储器。在811处,逻辑裸片104发出具有延迟 $t_{WR}$ 的预充电命令PRE。接着在812处在主机装置101可向高带宽存储器内处理堆叠103发出另一事务和/或另一些命令之前出现延迟 $t_{RP}$ 。

[0132] 尽管在时序型图800中所绘示的事务中许多事务可为确定性的,然而整个事务的总体时序是不确定的。为考虑到在807处的存储器内处理操作OP的不确定的延迟,主机装置101在809处通过命令/地址总线108发出PIM\_RD命令。在逻辑裸片104以PIM\_EST响应在813处作出响应之前将存在延迟 $t_{RL}$ 。在此实施例中,PIM\_EST响应可包括指示807处的存储器内处理操作OP将完成的时间的时间估计值。在一个实施例中,时间估计值可以时间为单位。在另一个实施例中,时间估计值可以时钟循环为单位。

[0133] 因此,在802处发出PIM\_WR命令的时刻与在812处高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令的时刻之间的有效时间 $t_{PIM\_WR(effective)}$ 被确定为 $t_{PIM\_WR(effective)} = t_{PIM\_WR} + t_{PIM\_EST}$ ,其中 $t_{PIM\_WR}$ 表示存储器内处理操作的完成时间的确定性部分,且 $t_{PIM\_EST}$ 表示存储器内处理操作的完成时间的不确定性部分的时间估计值。图9绘示根据本文所公开主题的示例性两步式高带宽存储器内处理协议存储器内处理命令的时序型图900,其中高带宽存储器内处理堆叠103提供关于存储器内处理命令将何时完成的基于信用值的指示。应理解,时序型图900并非按比例绘示且仅旨在绘示在高带宽存储器内处理堆叠提供关于示例性存储器内处理操作将何时完成的基于信用值的指示时两步式高带宽存储器内处理协议的相对顺序。

[0134] 在901处,主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令,逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电,并锁定高带宽存储器内处理堆叠103以保证高带宽存储器内处理堆叠在存储器内处理操作期间对主机装置101的所有权。紧接在PIM\_CHRG命令之后,主机装置101通过命令/地址总线108在902处发出PIM\_WR命令。主机装置101在903处通过数据总线109发送PIM\_CMD。PIM\_WR命令与PIM\_CMD命令之间的时间延迟是 $t_{WL}$ 。对双倍数据速率高带宽存储装置而言,PIM\_CMD命令花费突发长度延迟 $t_{BL/2}$ 。

[0135] 响应于903处的PIM\_CMD,逻辑裸片104在904处通过高带宽存储器内处理内部总线111向高带宽存储器内处理堆叠103发送激活命令ACT。逻辑裸片104对PIM\_CMD进行解码且接着在904处发出ACT命令的时间延迟是 $t_{PD}$ 。在延迟 $t_{RCD}$ 后,逻辑裸片104在905处发出读取命令RD。在以突发长度延迟 $t_{BL/2}$ 在906处读取数据RD\_Data之前,存在延迟 $t_{RL}$ 。以延迟 $t_{IOP}$ 在907处执行存储器内处理操作OP;然而,由于存储器内处理操作OP是复杂的,因此与存储器内处理操作OP相关联的延迟是不确定的。

[0136] 逻辑裸片104还在905处发出读取命令RD之后经过延迟 $t_{RTW}$ 后、但在907处已完成存储器内处理操作OP之前,在908处发出写入命令WR。存储器内处理操作OP的结果在发出写入命令WR之后经过延迟 $t_{WL}$ 后在909处被写入到存储器。在910处,逻辑裸片104发出具有延迟 $t_{WR}$ 的预充电命令PRE。接着在911处在主机装置101可向高带宽存储器内处理堆叠103发出另一事务和/或另一些命令之前出现延迟 $t_{RP}$ 。

[0137] 即使在时序型图900中所绘示的事务中许多事务可为确定性的,整个事务的总体时序也是不确定的。为考虑到在907处的存储器内处理操作OP的不确定的延迟,主机装置101在912处通过命令/地址总线108发出PIM\_RD命令。在逻辑裸片104以PIM\_CRED响应在913处作出响应之前将存在延迟 $t_{RL}$ 。在此实施例中,PIM\_CRED响应可包括与可被主机装置101用作节流机制(throttling mechanism)的信用值的数目有关的信息。举例来说,如果PIM\_CRED响应指示主机装置101具有大于零的整数个信用值,则主机装置101可继续向高带宽存储器内处理堆叠103发出命令和/或事务直到主机装置101没有任何信用值留下为止。

[0138] 因此,在902处发出PIM\_WR命令的时刻与在911处高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令的时刻之间的有效时间 $t_{PIM\_WR(effective)}$ 被确定为

$$[0139] t_{PIM\_WR(effective)} = t_{PIM\_WR} + t_{PIM\_CRED},$$

[0140] 其中 $t_{PIM\_WR}$ 表示存储器内处理操作的完成时间的确定性部分,且 $t_{PIM\_CRED}$ 表示大于零的整数个信用值,主机装置101可继续向高带宽存储器内处理堆叠103发出命令和/或事务直到主机装置101没有任何信用值留下为止。

[0141] 图10绘示根据本文所公开主题的示例性两步式高带宽存储器内处理协议存储器内处理命令的时序型图1000,其中高带宽存储器内处理堆叠103提供关于存储器内处理命令将何时完成的基于反馈的指示。应理解,时序型图1000并非按比例绘示且仅旨在绘示在高带宽存储器内处理堆叠提供关于存储器内处理操作将何时完成的基于反馈的指示时两步式高带宽存储器内处理协议的相对顺序。

[0142] 在1001处,主机装置101通过命令/地址总线108发出PIM\_CHRG命令。PIM\_CHRG命令包括不久将要发出的PIM\_CMD的存储体及信道身份信息。响应于PIM\_CHRG命令,逻辑裸片104对一个或多个所选择信道中的相关存储体进行预充电,并锁定高带宽存储器内处理堆

叠103以保证高带宽存储器内处理堆叠在存储器内处理操作期间对主机装置101的所有权。紧接在PIM\_CHRG命令之后，主机装置101通过命令/地址总线108在1002处发出PIM\_WR命令。主机装置101在1003处通过数据总线109发送PIM\_CMD。PIM\_WR命令与PIM\_CMD命令之间的时间延迟是 $t_{WL}$ 。对双倍数据速率高带宽存储装置而言，PIM\_CMD命令花费突发长度延迟 $t_{BL/2}$ 。

[0143] 响应于1003处的PIM\_CMD，逻辑裸片104在1004处通过高带宽存储器内处理内部总线111向高带宽存储器内处理堆叠103发送激活命令ACT。逻辑裸片104对PIM\_CMD进行解码且接着在1004处发出ACT命令的时间延迟是 $t_{PD}$ 。在延迟 $t_{RCD}$ 后，逻辑裸片104在1005处发出读取命令RD。在以突发长度延迟 $t_{BL/2}$ 在1006处读取数据RD\_Data之前，存在延迟 $t_{RL}$ 。以延迟 $t_{IOP}$ 在1007处执行存储器内处理操作OP；然而，由于存储器内处理操作OP是复杂的，因此与存储器内处理操作OP相关联的延迟是不确定的。

[0144] 逻辑裸片104还在1005处发出读取命令RD之后经过延迟 $t_{RTW}$ 后、但在1007处已完成存储器内处理操作OP之前，在1008处发出写入命令WR。存储器内处理操作OP的结果在发出写入命令WR之后经过延迟 $t_{WL}$ 后在1009处被写入到存储器。在1010处，逻辑裸片104发出具有延迟 $t_{WR}$ 的预充电命令PRE。接着在1011处在主机装置101可向高带宽存储器内处理堆叠103发出另一事务和/或另一些命令之前出现延迟 $t_{RP}$ 。

[0145] 在时序型图1000中所绘示的事务中许多事务可为确定性的，然而整个事务的总体时序是不确定的。为考虑到在1007处的存储器内处理操作OP的不确定的延迟，主机装置101在1012处通过命令/地址总线108发出PIM\_RD命令。在逻辑裸片104以PIM\_FDBK响应在1013处作出响应之前将存在延迟 $t_{RL}$ 。在此实施例中，PIM\_FDBK响应可包括与在主机装置101轮询高带宽存储器内处理堆叠103以判断存储器内处理操作是否已完成之前的时间段有关的信息。主机装置101可在返回对高带宽存储器内处理堆叠103进行轮询之前使用反馈信息进行排程及执行其他操作。

[0146] 因此，在1002处发出PIM\_WR命令的时刻与在1011处高带宽存储器内处理堆叠103准备好从主机装置101接收另一命令的时刻之间的有效时间 $t_{PIM\_WR(effective)}$ 被确定为

$$[0147] t_{PIM\_WR(effective)} = t_{PIM\_WR} + t_{PIM\_FBDBK},$$

[0148] 其中 $t_{PIM\_WR}$ 表示存储器内处理操作的完成时间的确定性部分，且 $t_{PIM\_FBDBK}$ 表示与在主机装置101轮询高带宽存储器内处理堆叠103以判断存储器内处理操作是否已完成之前的时间段有关的信息。

[0149] 如所属领域中的技术人员将认识到，可在各种各样的应用中对本文所述创新概念进行修改及变化。因此，所主张主题的范围不应仅限于以上所论述的任何具体示例性教示内容，而是由以上权利要求书来界定。

图1

图2

图3

图6

图7

图8

图9

图 10