【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成19年2月15日(2007.2.15)

【公開番号】特開2005-191447(P2005-191447A)

【公開日】平成17年7月14日(2005.7.14)

【年通号数】公開・登録公報2005-027

【出願番号】特願2003-433851(P2003-433851)

【国際特許分類】

H 01 L 23/12 (2006.01)

H 01 L 21/60 (2006.01)

【F I】

H 01 L 23/12 E

H 01 L 21/60 301N

H 01 L 23/12 F

【手続補正書】

【提出日】平成18年12月25日(2006.12.25)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

第1主面と、前記第1主面と対向する第1裏面と、前記第1主面に設けられたチップ搭載領域と、前記チップ搭載領域の周囲に設けられ、かつ電源電位または接地電位が供給される複数の第1ボンディング電極と、前記第1ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられ、かつ信号が入力または出力される複数の第2ボンディング電極とを含む配線基板と、

第2主面と、前記第2主面と対向する第2裏面と、前記第2主面に設けられ、かつ前記第2主面の外周に沿って設けられた複数の第1電極と、前記第2主面に設けられ、かつ前記複数の第1電極よりも内側に設けられた複数の第2電極とを含み、前記第2裏面が前記チップ搭載領域と対向するように前記配線基板に搭載された半導体チップと、

前記複数の第1ボンディング電極と前記複数の第1電極をそれぞれ電気的に接続する複数の第1ワイヤと、前記複数の第2ボンディング電極と前記複数の第2電極をそれぞれ電気的に接続する複数の第2ワイヤとを有し、

前記第1電極と前記第2電極は、前記半導体チップの外周に沿った方向で互い違いに配置され、

前記第1電極の外形サイズは、前記第2電極の外形サイズよりも大きいことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記第1ワイヤの径は、前記第2ワイヤの径よりも太いことを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置において、

前記第1電極に電気的に接続される第1ワイヤの数は、前記第2電極に電気的に接続される第2ワイヤの数よりも多いことを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置において、

前記半導体チップの前記第2主面に設けられ、かつ前記複数の第2電極よりも内側の領域には複数の電源回路セルおよび複数の入出力回路セルが設けられ、

前記電源回路セルと前記第1電極を電気的に接続する第1配線の幅は、前記入出力回路セルと前記第2電極を電気的に接続する第2配線の幅よりも太いことを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置において、

前記電源回路セルおよび前記入出力回路セルのそれぞれは、バッファ回路、静電破壊保護回路、プリバッファ回路、レベルシフト回路、および論理回路から形成されていることを特徴とする半導体装置。

【請求項6】

請求項4記載の半導体装置において、

前記電源回路セルは、前記接地電位が供給される第1電源回路セルと、外部電源電位が供給される第2電源回路セルを有することを特徴とする半導体装置。

【請求項7】

請求項6記載の半導体装置において、

前記電源回路セルは、更に、内部電源電位が供給される第3電源回路セルを有することを特徴とする半導体装置。

【請求項8】

請求項7記載の半導体装置において、

前記第3電源回路セル上には、第3電極が形成されていることを特徴とする半導体装置。

。

【請求項9】

請求項8記載の半導体装置において、

前記複数の第1ポンディング電極は、前記接地電位が供給され、かつ前記チップ搭載領域の周囲にリング状に形成された第3ポンディング電極と、外部電源電位が供給され、かつ前記第3ポンディング電極よりも前記チップ搭載領域から遠い位置にリング状に形成された第4ポンディング電極を有することを特徴とする半導体装置。

【請求項10】

請求項9記載の半導体装置において、

前記複数の第1ポンディング電極は、更に、前記内部電源電位が供給され、かつ前記第3ポンディング電極と前記第4ポンディング電極との間にリング状に形成された第5ポンディング電極を有することを特徴とする半導体装置。

【請求項11】

請求項10記載の半導体装置において、

前記第3電極は、前記第5ポンディング電極とそれ電気的に接続されていることを特徴とする半導体装置。

【請求項12】

請求項1記載の半導体装置において、

前記複数の第2ポンディング電極は、前記複数の第1ポンディング電極よりも前記チップ搭載領域から遠い位置に設けられた複数の第6ポンディング電極と、前記複数の第6ポンディング電極よりも前記チップ搭載領域から遠い位置に設けられた複数の第7ポンディング電極を有することを特徴とする半導体装置。

【請求項13】

請求項12記載の半導体装置において、

前記複数の第1電極は、クロック信号を入力または出力する複数の第4電極を有し、前記複数の第4電極は、前記複数の第6ポンディング電極と前記複数の第2ワイヤ介してそれ電気的に接続されていることを特徴とする半導体装置。

【請求項14】

請求項1記載の半導体装置において、

前記配線基板の前記第1裏面には、複数のはんだボールが設けられ、

前記複数のはんだボールは、前記複数の第1ポンディング電極および前記複数の第2ポンディング電極と複数の配線層を介してそれぞれ電気的に接続されていることを特徴とする半導体装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】発明の名称

【補正方法】変更

【補正の内容】

【発明の名称】半導体装置

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0029

【補正方法】変更

【補正の内容】

【0029】

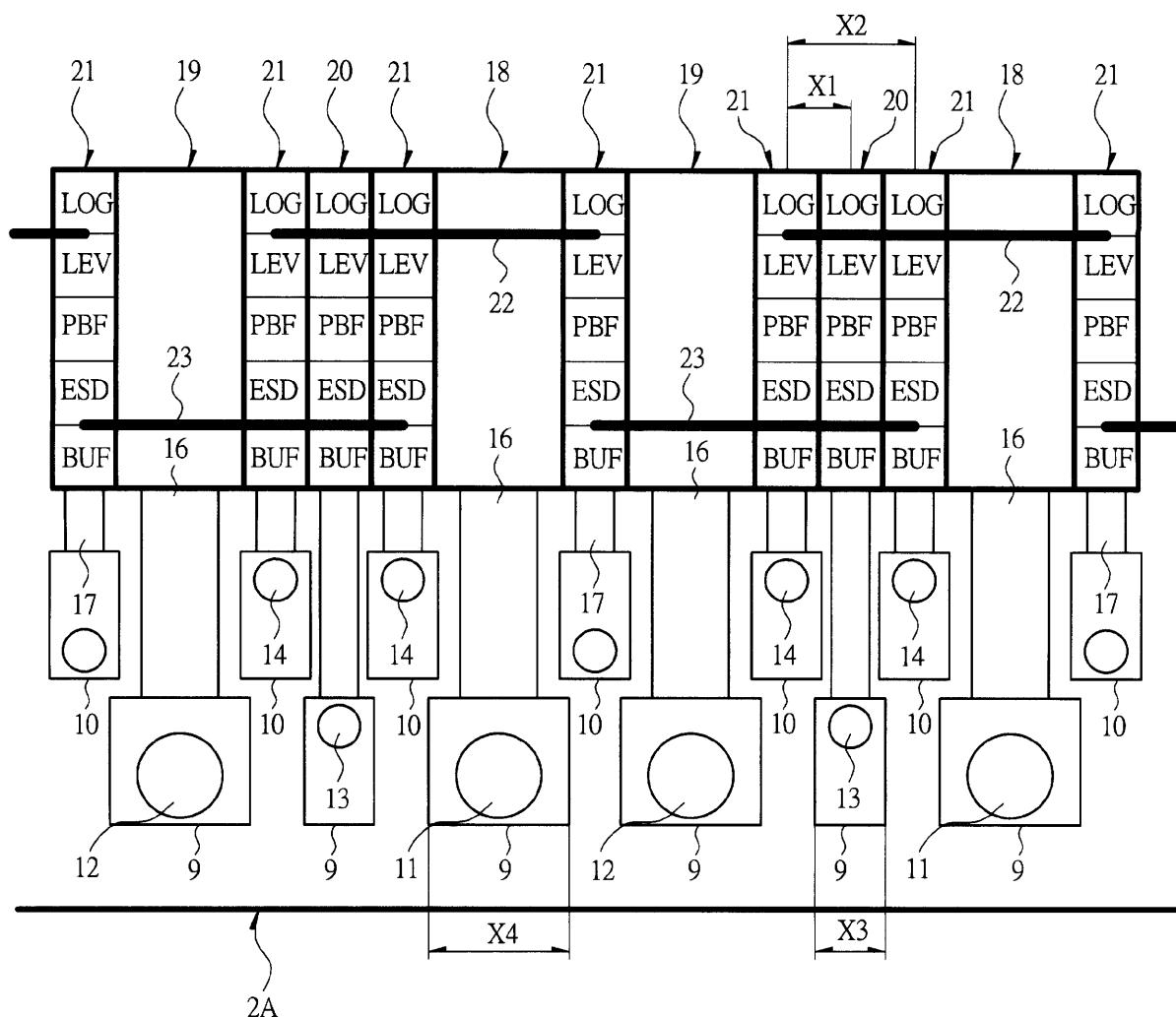

前述したように、本実施の形態1では、ポンディングパッド9とポンディングパッド10とは、チップ2の正面の外周に沿った方向で互い違いに配置されており、隣り合うポンディングパッド9間には配線が配置されていないことから、図6に示すように、電源系のポンディングパッド9の幅X4は、ポンディングパッド10の幅X3より大きく確保することができ、たとえば約100μmとすることができます。その結果、図6～図8に示すように、本実施の形態1においては電源系のポンディングパッド9と接続するワイヤ11、12の径を他のワイヤ13、14の径より大きくすることができます。本実施の形態1では、ワイヤ13、14の径が20μmであるのに対して、ワイヤ11、12の径を30μmにできることを例示できる。その結果、ワイヤ11、12におけるインピーダンスを低減できるので、上記配線16で増加したインピーダンスをワイヤ11、12の低抵抗化により相殺することが可能となる。すなわち、電源回路セル18、19と電気的に接続する配線16、ポンディングパッド9およびワイヤ11、12の総合的なインピーダンスを低減できるので、チップ2内に形成されたロジックICの動作の高速化またはASICの多機能化を実現することが可能となる。

【手続補正4】

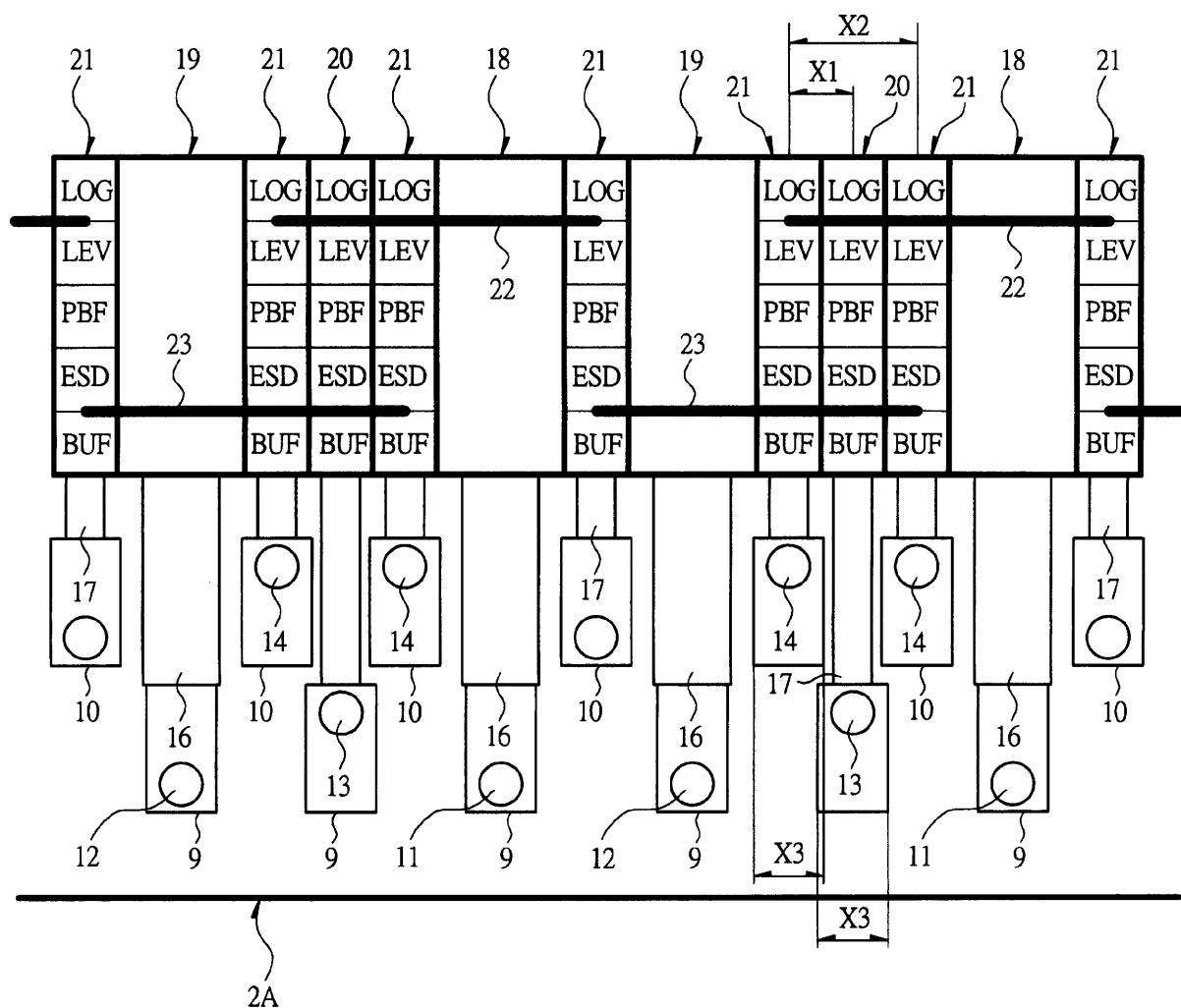

【補正対象書類名】図面

【補正対象項目名】図4

【補正方法】変更

【補正の内容】

【図4】

図4

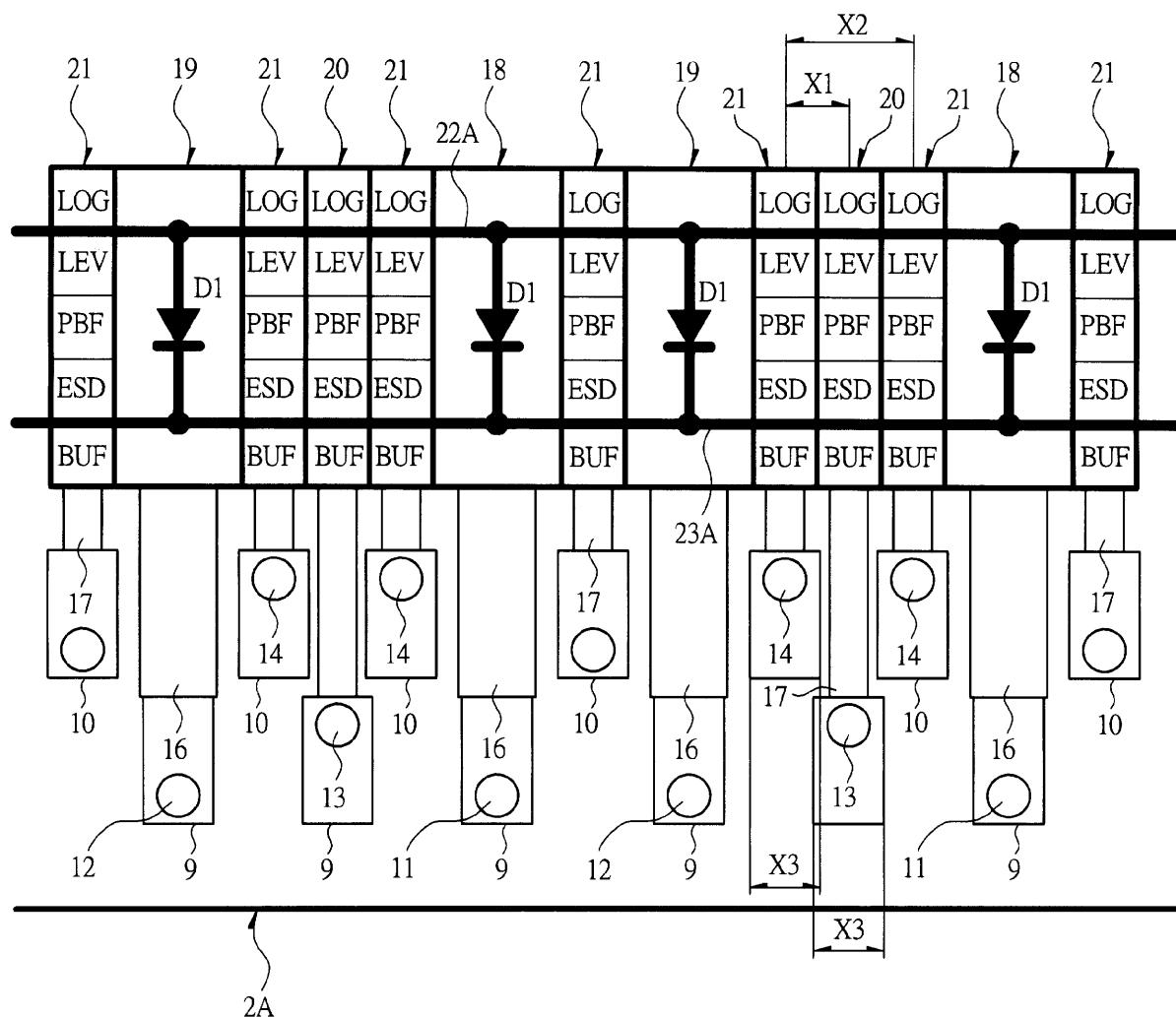

【手続補正5】

【補正対象書類名】図面

【補正対象項目名】図5

【補正方法】変更

【補正の内容】

【図5】

図 5

【手続補正6】

【補正対象書類名】図面

【補正対象項目名】図6

【補正方法】変更

【補正の内容】

【図6】

図6

9 : ボンディングパッド(電極, 第1電極)

10 : ボンディングパッド(電極, 第2電極)

11,12 : ワイヤ(第1ワイヤ)

13,14 : ワイヤ(第2ワイヤ)