# UK Patent Application (19) GB (11) 2 163 627 A

(43) Application published 26 Feb 1986

- (21) Application No 8521222

- (22) Date of filing 23 Aug 1985

- (30) Priority data

- (31) 8421500

- (32) 24 Aug 1984

- (33) GB

- (71) Applicant

81 Newgate Street, London EC1A 7AJ

British Telecommunications plc (United Kingdom),

- (72) Inventor

- **Peter Michael Attkins**

- (74) Agent and/or Address for Service Kevin John Purell, Intellectual Property Unit, Room 1304, 151 Gower Street, London WC1E 6BA

- (51) INT CL4 H03K 3/84 G01R 31/02 G06F 7/58 H04M 3/34

- (52) Domestic classification **H4P EUM**

- (56) Documents cited GB A 2131183

G4D AJ

(58) Field of search

H4P

G4D

G<sub>1</sub>V

### (54) Error generator

(57) The output of a pseudo-random sequence generator (SR,X1) is fed to a comparator (CP1, M1) which produces an output when a selected number of bits of the generator output matches a comparison word (from CR1); the number of bits selected (by MR1) determines the error rate. Correlation problems are reduced by changing the comparison word (eg. by loading latch CR1 from counter LC incremented at clock rate) each time a match is found.

3B 2 163 627 A

Fig.9.

65

# **SPECIFICATION**

# **Error generation**

| 5  | There are various types of random and pseudo random error generator principles. For example, a white noise source connected to a variable threshold comparator and sampling circuit will produce an output signal with probability altered by the threshold level. This type of                                                                                                                                                                                                                                                                                                         | 5  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10 | generator has many failings such as; small noise power changes caused by temperature etc. will have a considerable effect on the error probability; the noise power bandwidth and comparator bandwidth must be many times greater than the sampling frequency—if this is not attained then there will be correlation between consecutive samples and the output signal will reflect this deficiency.                                                                                                                                                                                    | 10 |

| 15 | The most consistent and predictable error generators are based on digital techniques, ideally using random number generation. A realistic approach is to generate a long pseudo random sequence and use a digital word detector.  Assume that the generator consists of an n-bit shift register with feedback, and a w-bit word detector produces an output whenever a specified word appears in the output sequence.                                                                                                                                                                   | 15 |

| 20 | The generator will produce 2 <sup>n</sup> -1 unique words of n-bits (with exclusive OR feedback all zeros is illegal and with exclusive NOR feedback all ones is illegal). This is true for certain tap configurations only-some combinations will produce far fewer words. The word detector can 'look' for any w-bit word in the sequence except the illegal word therefore it is better to make w <n a="" avoid="" situation.<="" such="" td="" to=""><td>20</td></n>                                                                                                                | 20 |

| 25 | The probability of a w-bit word being detected is slightly greater than 2 w because there are only 2n-1words and not 2n. The difference depends on the actual value of n. An obvious limitation to this generator is that the probability values obtainable are in powers of 2 and not infinitely variable. In practice, however, there is normally more than enough resolution. This method of error generation does produce the correct probability, but the nature of error                                                                                                          | 25 |

| 30 | distribution along the length of pseudorandom sequence is sequence related. For a given w-bit word the output sequence from the detector may be charged by altering the generator, for example by changing n or just changing the other shift resistor tap/taps and the word order will change. Similarly an exclusive NOR feedback would give a different distribution from exclusive OR. This is irrelvant if the distribution is reasonable anyway, but certain configurations may result in the output signals being bunched together and ten a long gap until the pattern repeats, | 30 |

| 35 | especially when w approaches n. Closer examination of a typical PRBSG will reveal another shortcoming of this type of error generator and that is of inter-word correlation similar to bandwidth limitation in a noise source based design. A PRBSG has word correlation at an interval of $2^m-n-1$ (a maximal length                                                                                                                                                                                                                                                                  | 35 |

| 40 | sequence)—this is ONLY for a one bit word though. If we use more than one bit there may be correlation over a much shorter interval. If, for example, the feedback is an EXCLUSIVE OR of shift register taps 28 and 31, the sequence is very long, but correlation will occur at intervals of Tap 28+1, Tap 31+1, Tap 31—Tap 28 because each new bit entering the shift register is related to bits 28 and 31 further down. It causes an unwanted distribution of output signals which gets worse as w increases from 2.                                                                | 40 |

| 45 | An error generator of this type is described in CCITT Study Group XVII Document No: 18, Annex 1 (14 July 1982). This uses a 31-bit register with exclusive or feedback from taps 28 and 31; a w-bit word detector produces an error output when taps 12 to (11+w) are all "1". This error generator attempts to circumvent the problem of correlation by sub-sampling the PRBSG at a ratio of 1:32. This is achieved by clocking the generator 32 times between each                                                                                                                    | 45 |

| 50 | test by the word detector thereby removing all correlations $<$ 32. In practical terms the shift register clock is 2.048MHz while the sampling/data rate is 64KHz. The feedback taps used (Taps 28 and 31) produce a maximal length pseudo random binary sequence of length $2^{31}-1$ bits or approximately $2.1\times10^9$ bits before a repeat of the sequence. The sub-sampling rate cannot be a submultiple of the pattern length due to the $-1$ term in                                                                                                                          | 50 |

| 55 | 2°-1 so the actual sub-sampled pattern would repeat approximately:  32×2.1×10° bits at 2.048Mbit/s (each pattern is 'short' bu 1 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55 |

|    | 32 (sub-sampling rate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 60 | which is the same length as the original pattern of 2.1×10° bits or a repetition once every                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60 |

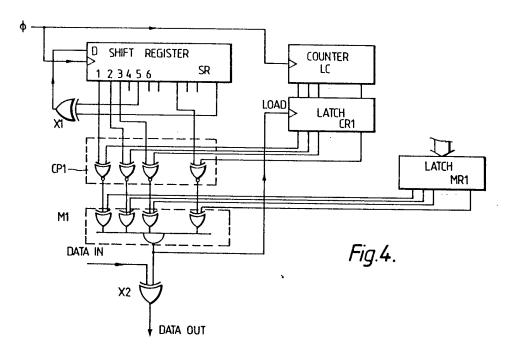

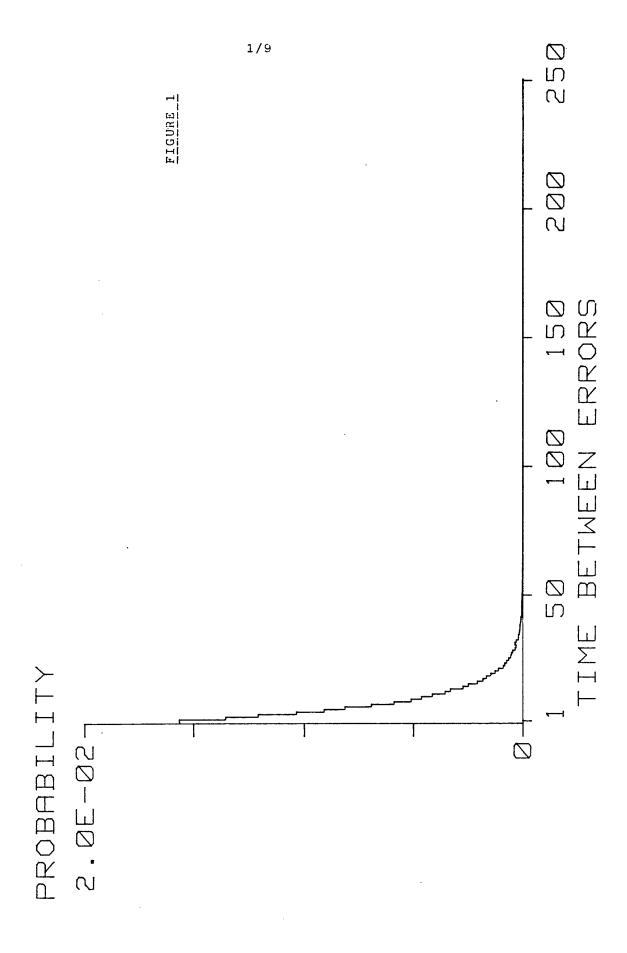

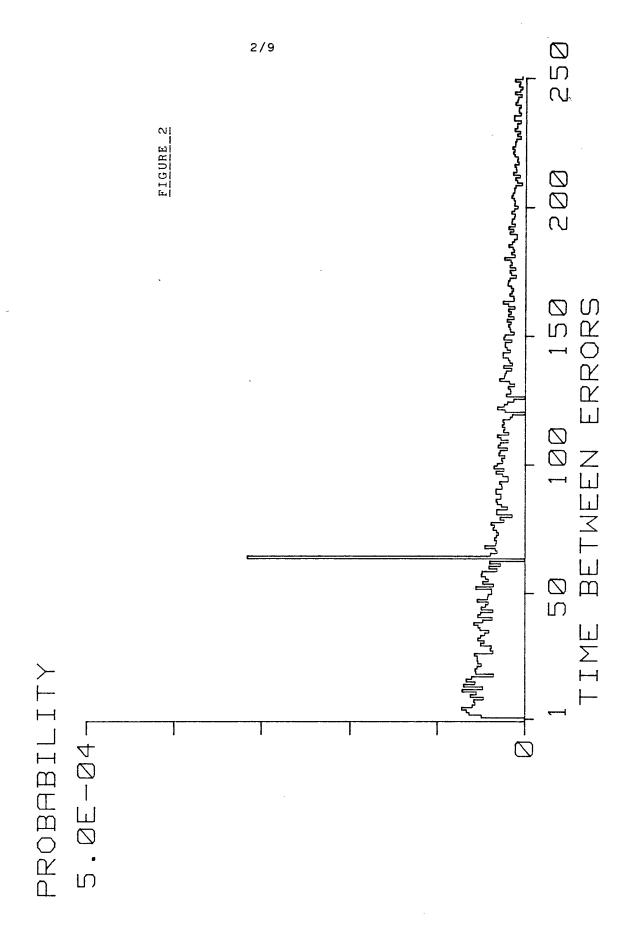

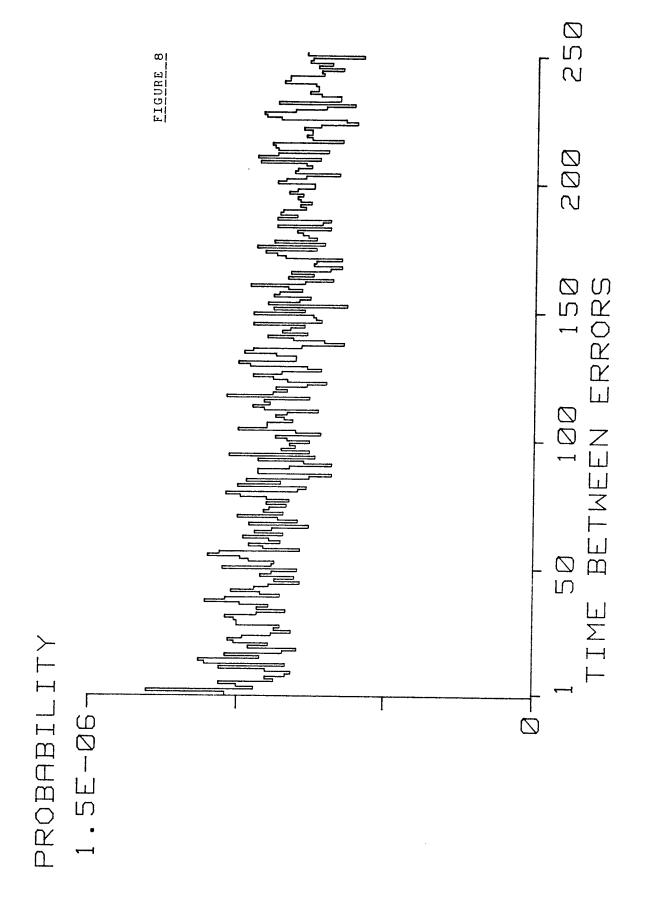

Unfortunately this sub-sampling only shifts the correlation intervals instead of eliminating them. Computer simulation of this error generator has been carried out and results are shown in Figs. 1 to 3 for an order w of 3, 7 and 10 respectively, the probability p of an interval of the

65 samples between errors being plotted against the. Further data are set out below:

32812.5 seconds (9 hours approximately).

|    |                                                       | •                                                                                                  |                                                                       |                                                          |                                                                |                                                                                                                                           |    |

|----|-------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | Fig Order                                             | (w) Error Rate                                                                                     | Equivalent<br>duration of<br>test at<br>64kbit/s<br>(seconds)         | Total<br>Errors                                          | % of errors beyond tbe=250                                     | ·                                                                                                                                         | 5  |

| 10 | 1 3<br>2 7<br>3 10                                    | 120×10 <sup>-3</sup><br>7.8×10 <sup>-3</sup><br>0.97×10 <sup>-3</sup>                              | 13<br>20<br>161                                                       | 100,000<br>10,000<br>10,000                              |                                                                | •                                                                                                                                         | 10 |

| 15 | and less impo                                         | bserved that the out<br>ortant problems at h<br>an interval of the the                             | igher intervals                                                       | ajor correlat<br>. If P(tbe) is                          | tion problem<br>the probab                                     | s at intervals 63 and 64 bility of consecutive errors                                                                                     | 15 |

| 20 | P(63)-<br>P(64)>P(x)                                  | O for all values of error has occurred no error will occur where x ≠ 63 and x all values of ORDER  | it is certain th<br>63 samples la<br>is 'near' to 6                   | at<br>ater                                               |                                                                |                                                                                                                                           | 20 |

| 25 | For ORDER>                                            | 3:P(64) is 4 to 6 perror rate or there percent chance of produced 64 bits a error. This is clearly | ercent of the<br>is roughly a 5<br>an error being<br>after the previo |                                                          |                                                                |                                                                                                                                           | 25 |

| 30 | The relatio                                           | the error generation                                                                               | n method.<br>probability/ra                                           | tes and equestern is as                                  | uivalent mea<br>follows:                                       | n-time-between-errors for                                                                                                                 | 30 |

| 35 | Error rate:                                           | ability (approximately                                                                             |                                                                       | 1000                                                     |                                                                |                                                                                                                                           | 35 |

| 40 | would be ve<br>difference th                          | ery like having a pusl<br>nough is that the ger<br>s) later—the ear woul                           | n-switch to ge<br>nerator will, ab<br>ld detect this                  | nerate a si<br>out 5 perc<br>as a single                 | ngle error of<br>ent of the ti<br>disturbance                  | rrors would be 16s and this ccasionally. One important me, produce a second error of greater magnitude than bound worse than it should as | 40 |

| 45 | some of the indeed they (byte derive                  | time the double err<br>should be. Any tran<br>d systems such as F<br>raming information w          | ors will be co<br>smission syst<br>PCM) could be<br>vill not respon   | nsidered, b<br>em with da<br>affected b<br>d to a give   | y the listene<br>ta structure<br>y the proble<br>n error in th | ound worse than it should as er, to be single errors as at a sub-multiple of 64 am at P(64) and any system are same manner as it would    | 45 |

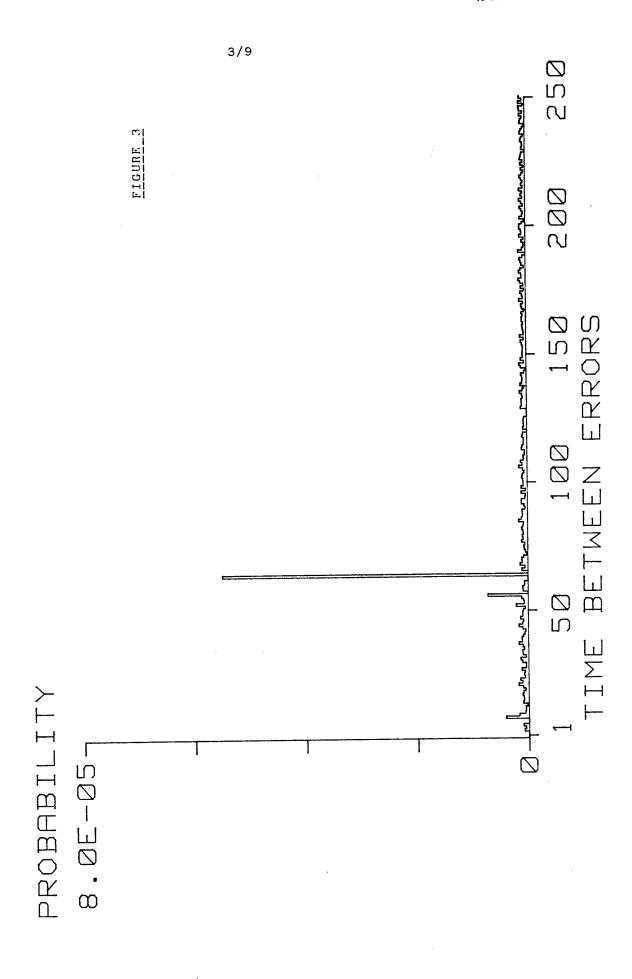

| 50 | systems who better meas According                     | nich deliberately response the performance the to the present inverse a pseudo-random se           | ond very favor<br>an they would<br>ntion there is<br>quence genera    | urably to th<br>I otherwise<br>provided a<br>ator (SR.X1 | ne error inject<br>variable pro<br>) and detect                | be to build transmission of the total and thereby give a bability error generator for means (CP1, CP2) ar-                                | 50 |

| 55 | ranged to e<br>output upor<br>modification            | xamine a selected no<br>recognition that the<br>means (LC, CR1, C<br>word.                         | umber of bits<br>use bits corres<br>R2) operable,                     | of the gene<br>spond to a<br>following e                 | erated seque<br>comparison<br>ach such re                      | ence and to produce an word, characterised by cognition, to change the d, by way of example, with                                         | 55 |

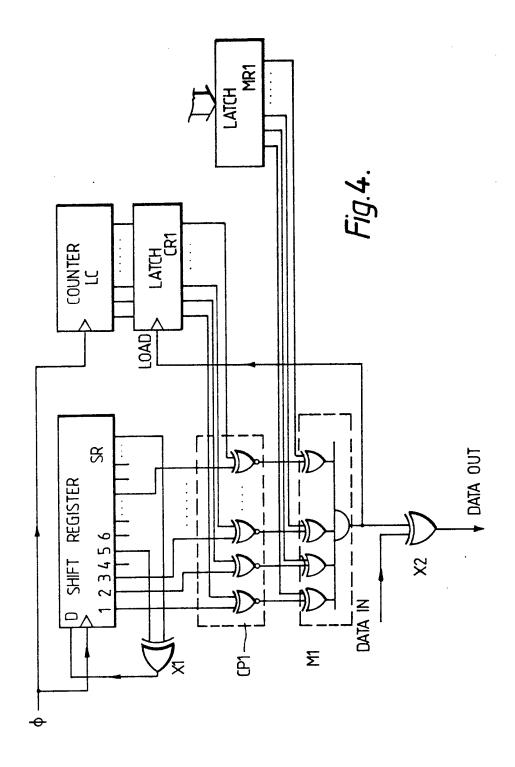

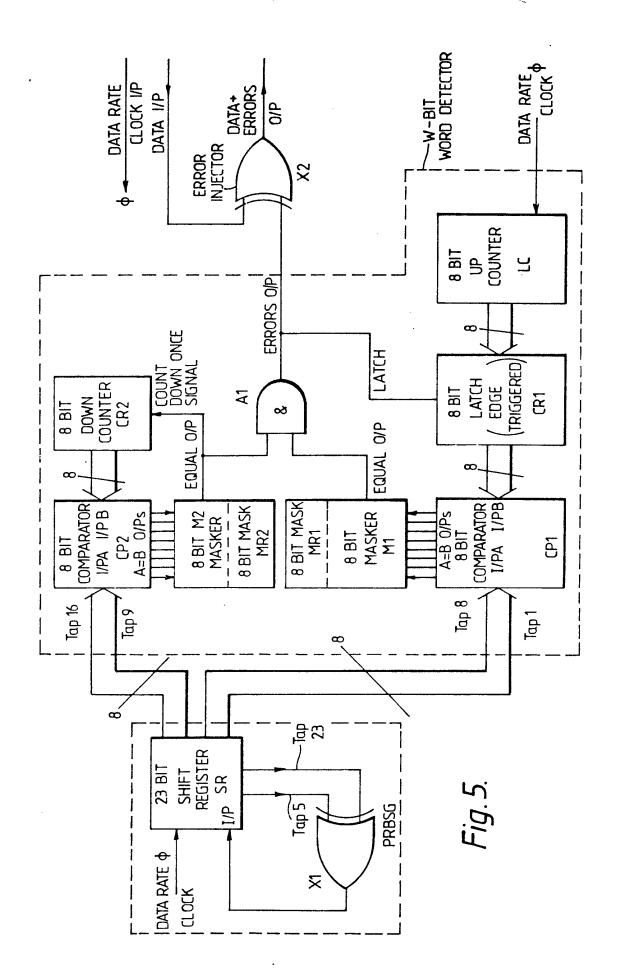

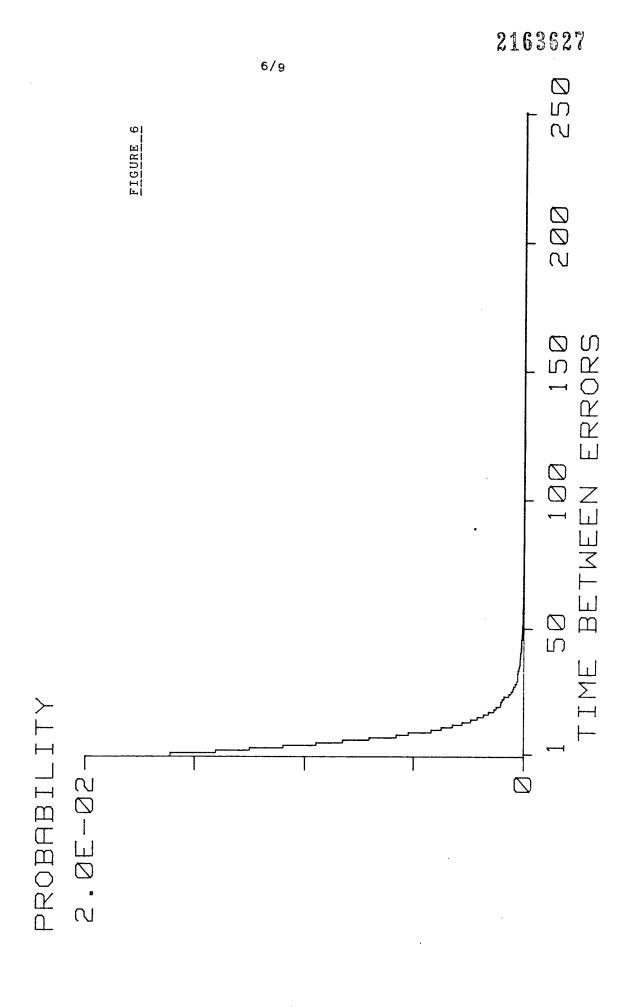

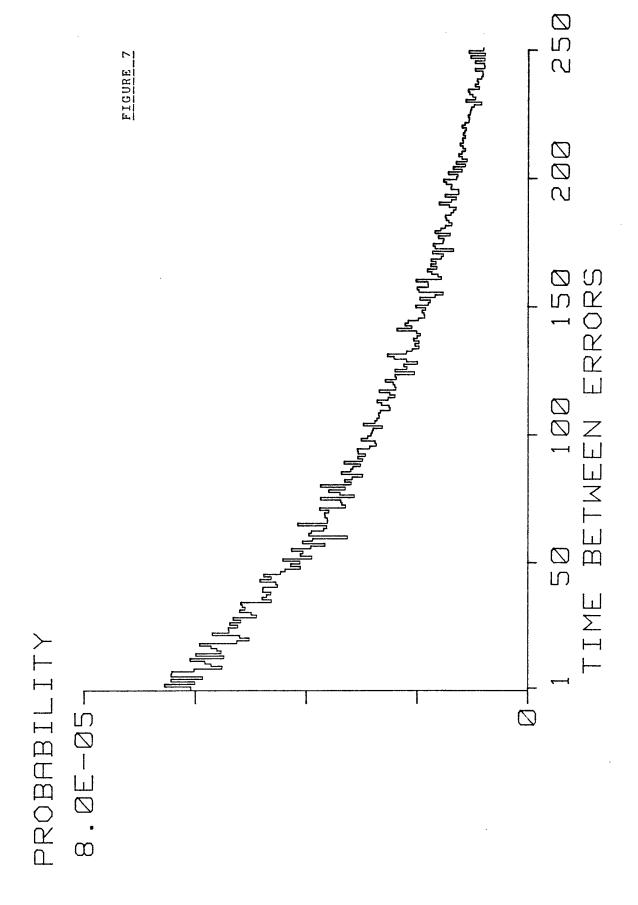

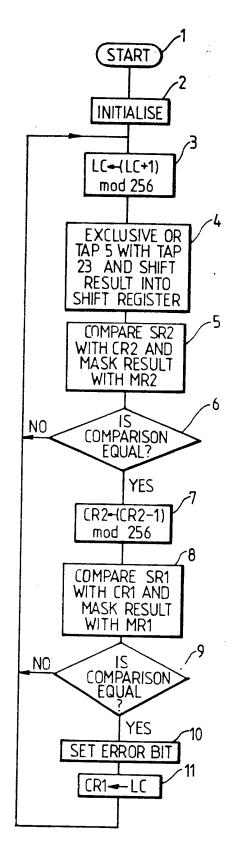

| 60 | reference to Figures 1 Figures 4 invention; Figures 6 | the accompanying to 3 are graphs illustrand 5 are block dia                                        | drawings, in v<br>strating the pe<br>grams of two<br>strating the pe  | vhich:<br>erformance<br>alternative<br>erformance        | of a known<br>error generation                                 | error generator;<br>ators according to the<br>rator of Fig. 5; and                                                                        | 60 |

| 6  | Figure 9                                              | is a flowchart illustra                                                                            | iting a third er<br>random binary                                     | nbodiment<br>/ seauence                                  | of the inver                                                   | ntion.<br>s formed by a shift register<br>3, giving a pattern length of                                                                   | 65 |

60

65

5

10

15

20

25

30

35

40

45

more than 8 million bits. The register is loaded initially (by means not shown) with a non-zero number to ensure proper startup. The first W taps are used in conjunction with a w-bit word detector where w is less than or equal to W. The errors output are injected into the incoming data stream with an exclusive OR gate X2.

It is the implementation of the w-bit word detector that controls the performance of the error generator with regard to distribution of time between errors, the problems with conventional generators having been shown already. In Fig. 4, the W bits are compared bit by bit in comparator CP1 with a comparison word stored in a latch CR1. The outputs of the comparator are fed to a masker M1 in which the first w bits are AND-ed to form the output; the remainder if any being forced to 1 by the output of a latch MR1 by presetting appropriate bits of the

This generator does not even attempt to employ sub-sampling techniques, instead, the w-bit word detector uses a variable word for its comparison. Conventional generators use a fixed word—the actual word will affect the error distribution, but any fixed word produces an un- wanted distribution similar to the graphs shown in Figs. 1 to 3 (this used 'all ones' as the word). Using a variable word overcomes the correlation problem providing that the word is not directly related to the sequence. The word is charged each time the w-bit word detector produces an output, the new word being stored in the latch CR1 and is the value of a modulo 256 counter LC clocked by the data rate clock  $\phi$ .

Fig. 5 shows a modified version, in which the word detector examines up to 16 bits (ie. W=16). The lower 8 bits are dealt with in the same way as in Fig. 4, whilst the upper 8 are compared in comparator CP2 with a separate comparison word from an 8-bit modulo 256 down counter CR2, decremented by the equal output of the comparator. The comparator output is masked by masker M2 and mask register MR2 and the output combined with that of MR1 in an 55 AND gate A1.

The error rate selection is controlled by the mask registers MR2, MR1 eg:

| 30 | ORDER | MR2      | MR1      | COMMENT                 |

|----|-------|----------|----------|-------------------------|

| 00 | 1     | 0000000  | 00000001 | Look at tap 1 only      |

|    | 13    | 00011111 | 11111111 | Look at tap 1 to tap 13 |

Note however that the bits set do not have to be consecutive; any pattern can be used provided the total number of bits set to 1 is w.

These values are used by the 8-bit maskers to select only the required taps for the selected ORDER. A 'zero' mask bit means—assume the corresponding tap was equal to the compare register bit value (ignore it). A 'one' means pass the comparator value to the equal detector in 40 the masker. Note that this is the reverse convention to that employed in Fig. 4. Thus if w is less than or equal to 8, then operation is identical to that of Fig. 4; if w is greater than 8 then the upper half of the detector is used. The upper EQUAL O/P will detect w-8 bits from the PRBSG (the detector always 'looks' at tap 1 to tap w) and when equality is found then the upper 8-bit word is decremented by one. Obviously to produce an error output both halves of the word detector must be presented with their correct words simultaneously.

Computer generated results for the arrangement of Figs. 5 are shown in Fig. 6 to 8 (Figs. 6 and 7 are also valid for the version of Fig. 4, of course). Further data are as follows:

| 50 | Fig | Order (w) | Equivalent<br>Error Rate | duration of<br>test at<br>64kbit/s<br>(seconds) | Total<br>Errors | % of errors beyond tbe=250 |

|----|-----|-----------|--------------------------|-------------------------------------------------|-----------------|----------------------------|

| 55 | 6   | 3         | 120×10 <sup>3</sup>      | 13                                              | 10,000          | 0                          |

|    | 7   | 7         | 7.9×10 <sup>3</sup>      | 198                                             | 10,000          | 14                         |

|    | 8   | 10        | 0.97×10 <sup>3</sup>     | 1610                                            | 10,000          | 78                         |

It will be observed that there are *no* zero probability points, and that there are no longer any excessively high probability points. Fig. 8 shows a wider variation than the others but this is due to the low error rate in relation to the duration of the test and would also be seen for a true random sequence. It is found that the graph "smoothes" as the test is continued.

It should also be noted that the vertical scales of the graphs of Figs. 6 to 8 are different from

60

65

those of Figs. 1 to 3. Interestingly, the differences between the two sets of results cannot be discerned using a spectrum analyser. As well as the substantial improvement in probability distribution, the generators described also have the advantage, compared with generators using sub-sampling, of not requiring logic operating at rates in excess of the data clock rate. Whilst this would be of importance in the 5 hardware versions described only in the case of extremely high data rates, it is significant for the microprocessor based version described below. Using a Motorola 68000 microprocessor with an 8 MHz processor clock, programmed in machine code, it has been found that it is possible to achieve real-time error generation for 64kbit/s data. Were sub-sampling employed, 10 10 this would not be possible. A microprocessor-based version has also been implemented on an 8-bit Intel 8051 microcontroller chip. The prime requirement was for speed of execution as the application was a 16kbit/s error injector. The microcontroller will produce errors at 32kbit/s, but it is insufficiently fast for 64kbit/s. All practical tests (to conform the simulation) were performed at 16kbit/s. A flowchart 15 15 for this implementation is shown in Fig. 9. This uses the same algorithm as embodied in the hardware version of Fig. 5. The same references are used to refer to the CPU registers (or memory locations) as were used to refer to the register of Fig. 5. The 23-bit shift registers BR is represented by three 8-bit registers as follows: 20 20 SR1:-tap 1 -tap 8 SR2:-tap 9 -tap 15 SR3:-tap 16-tap 24 Only those steps of the flowchart which are not self-explanatory are discussed below 25 25 2 Initialise: Set SR1=5; SR2=SR3=0 CR1=CR2=0 LC=030 Mask registers filled with N ones 30 starting from the l.s.b of MR1 3 The loop counter is incremented. When listening to speech over a 64kbit/s transmission system a single error may be noticed; 35 35 however, there is little point in using an error generator with an order greater than 20 because it would approximate single errors. **CLAIMS** 1. A variable probability error generator comprising a pseudo-random sequence generator 40 (SR,X1) and detector means (CP1, CP2) arranged to examine a selected number of bits of the 40 generated sequence and to produce an output upon recognition that those bits correspond to a comparison word, characterised by modification means (LC, CR1, CR2) operable, following each such recognition, to change the comparison word. 2. An error generator according to claim 1 characterised in that the detector means is 45 arranged to examine the selected number of consecutivie bits of the generated sequence. 45 3. An error generator according to Claim 2 characterised in that the detector means is arranged, for each bit of the generated sequence, to examine that bit and the appropriate number of succeeding bits. 4. An error generator according to claim 2 or claim 3 characterised in that the modification 50 means is arranged, upon such recognition, to make the comparison word, considered as a binary 50 number, is made equal to the number of comparisons, counted modulo-sw, where w is the selected number of bits, which have occurred since an arbitary datum point. 5. An error generator substantially as herein described with reference to the accompanying

drawings.