RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 493 526**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 81 20694**

(54) Dispositif permettant le comptage de cycles Doppler fractionnels et procédé de mesure de fréquence associé.

(51) Classification internationale (Int. Cl. 3). G 01 R 23/00; G 01 C 21/00; G 01 S 1/02.

(22) Date de dépôt ..... 4 novembre 1981.

(33) (32) (31) Priorité revendiquée : EUA, 5 novembre 1980, n° 204,097.

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 18 du 7-5-1982.

(71) Déposant : Société dite : MOTOROLA, INC., résidant aux EUA.

(72) Invention de : Howard L. Kennedy.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Cabinet Beau de Loménie,

55, rue d'Amsterdam, 75008 Paris.

La présente invention concerne un dispositif permettant le comptage de cycles Doppler fractionnels ainsi qu'un procédé de mesure de fréquence associé.

Dans les équipements de mesure de fréquence Doppler utilisés dans les systèmes de navigation, il est essentiel d'obtenir des mesures précises donnant une indication exacte de tous les cycles Doppler partiels présents dans la mesure. Certains dispositifs de la technique antérieure utilisent des techniques de multiplication analogiques appliquées au signal d'entrée ou à une combinaison de plusieurs signaux d'entrée afin d'augmenter la résolution de la mesure Doppler avant la mise sous forme numérique de la mesure. Une autre technique permettant de faire des mesures précises de cycles Doppler partiels est mise en oeuvre dans la demande de brevet des Etats-Unis d'Amérique n° 025 260 déposée par Stulting et al sous le titre "Method and Apparatus For Measuring Received Doppler Cycles For a Specified Period of Time" et cédée à la demanderesse. La technique qui est alors utilisée consiste à compter aussi bien les cycles complets que les cycles partiels du signal d'entrée Doppler en utilisant un compteur dont les impulsions d'horloge valent de nombreuses fois la fréquence Doppler attendue. On compare le comptage des cycles partiels au comptage des cycles complets pour une même période et on détermine par le calcul la valeur de comptage fractionnelle.

Les dispositifs de la technique antérieure introduisent une complexité élevée dans leurs circuits et, ou bien, nécessitent des compteurs permettant de répondre à des impulsions d'horloge de très haute fréquence.

L'invention n'exige pas l'utilisation d'un compteur d'intervalles de temps et, par suite, les calculs permettant de déterminer la valeur de comptage fractionnelle des cycles Doppler sont beaucoup plus simples. Au contraire, un oscillateur à commande de tension travaille à un multiple de la fréquence Doppler et il est utilisé un compteur Doppler qui présente un surcroît de capacité pour la fréquence plus élevée. Le comptage des cycles Doppler fractionnels à un degré de résolution adéquat est réalisé sans que la complexité du dispositif soit notablement accrue et au prix de l'utilisation

d'un petit nombre seulement de pièces d'un coût réduit. Lorsqu'un tel dispositif de comptage Doppler est utilisé dans un système de localisation de position tel que le "Navy Navigational Satellite System (TRANSIT)", la précision du système de localisation de position en est fortement accrue.

C'est donc un objet de l'invention d'utiliser un oscillateur à commande de tension dans une boucle de verrouillage de phase qui fonctionne à un multiple de la fréquence Doppler, afin d'ainsi améliorer la précision du comptage sans utiliser un compteur d'intervalles de temps de haute fréquence pour compter les cycles fractionnels.

Un autre objet de l'invention est de verrouiller un oscillateur à commande de tension sur un multiple de la fréquence Doppler à l'aide d'une boucle de verrouillage de phase. La fréquence supérieure est ensuite comptée par un compteur Doppler présentant une capacité supplémentaire vis-à-vis des hautes fréquences de manière à traiter la fréquence d'entrée supérieure.

La description suivante, conçue à titre d'illustration de l'invention, vise à donner une meilleure compréhension de ses caractéristiques et avantages; elle s'appuie sur les dessins annexés, parmi lesquels :

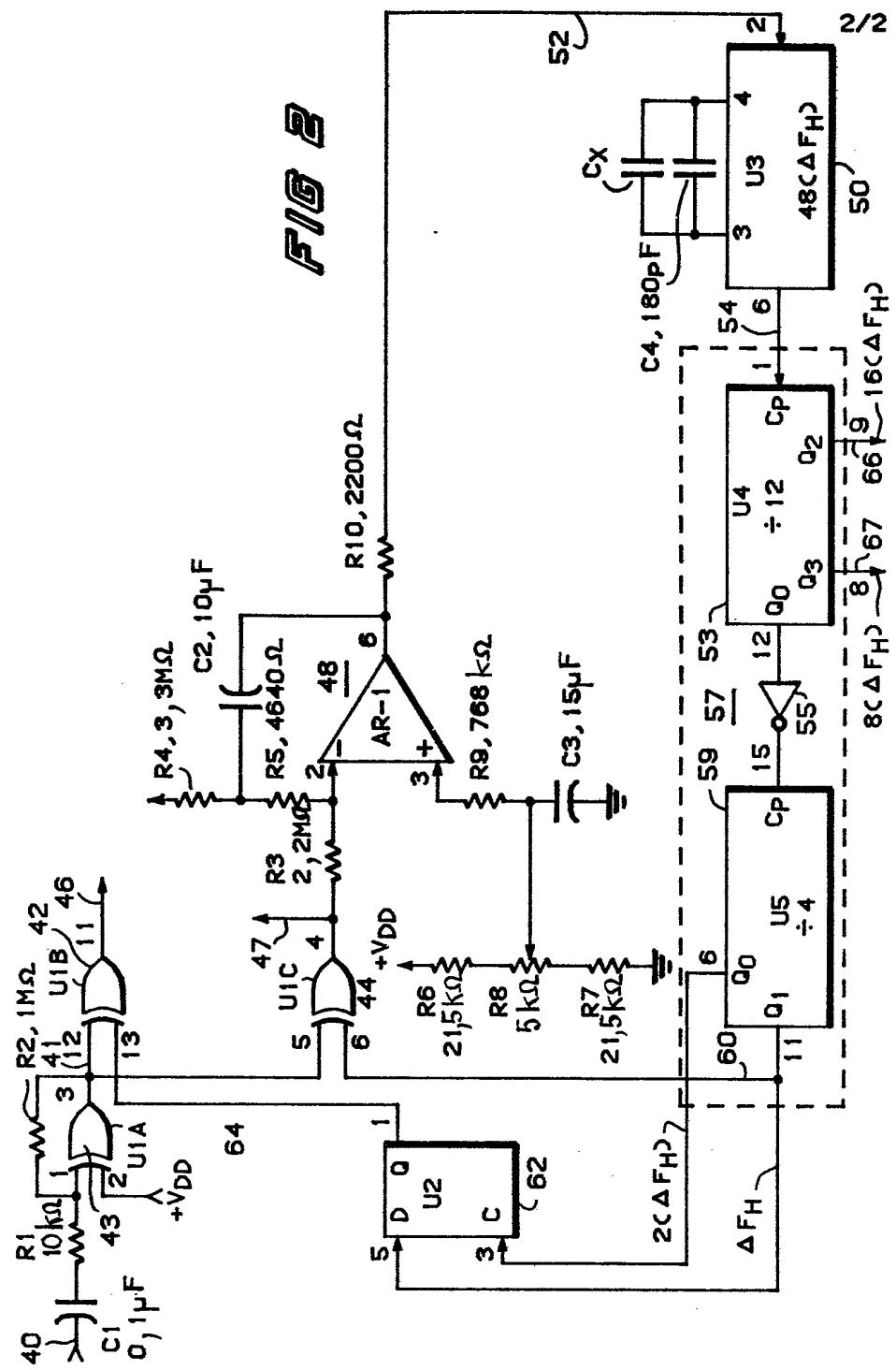

- la figure 1 est un schéma de principe général d'un dispositif utilisant un oscillateur à commande de tension verrouillé sur une fréquence qui est un multiple d'une fréquence Doppler; et

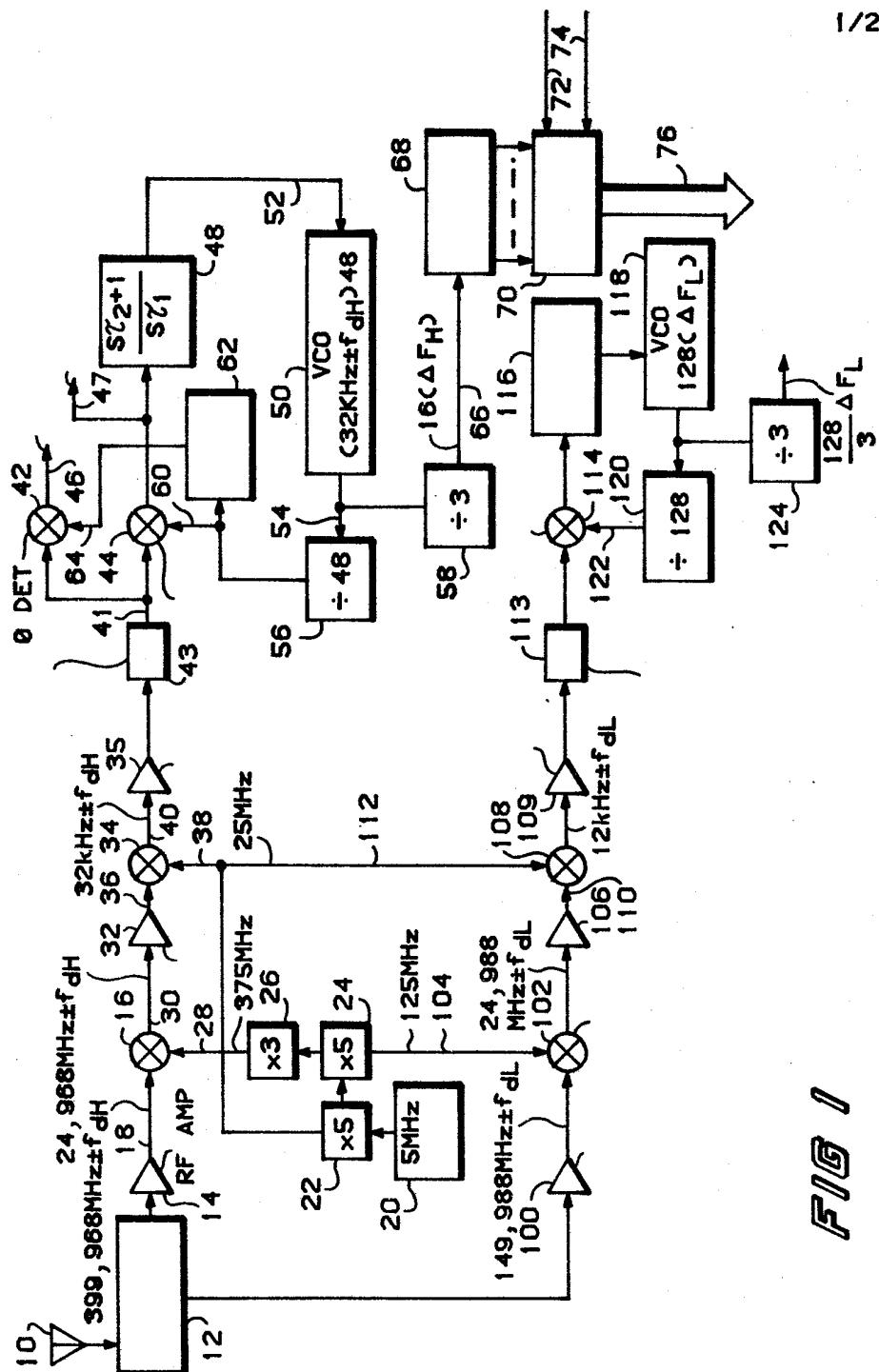

- la figure 2 est un schéma logique plus détaillé de la boucle de verrouillage de phase comportant l'oscillateur à commande de tension du schéma de principe de la figure 1.

Le qualificatif "Doppler", tel qu'il est utilisé dans la présente description, peut signifier une fréquence de bande de base plus ou moins la fréquence Doppler (ou la différence entre la fréquence de référence d'un récepteur et la fréquence reçue), ou bien simplement la fréquence Doppler  $f_d$ . La première définition contient un terme de fréquence continu.

La figure 1 est un schéma de principe d'un récepteur de navigation utilisant l'invention. Naturellement, l'invention peut être utilisée à chaque fois qu'un comptage de cycle ou une mesure

de fréquence doit être obtenu à partir d'un signal de fréquence variable. Une antenne 10 alimente un séparateur de fréquence 12. Le séparateur 12 produit un signal de canal de bande élevée et un signal de canal de bande basse. Le canal de bande élevée est amplifié 5 dans un amplificateur de haute fréquence 14, le signal de sortie de fréquence de l'amplificateur 14 étant de  $399,968 \text{ MHz} \pm f_{DH}$  (fréquence Doppler). Le signal est envoyé à un mélangeur 16 via une borne 18. Un oscillateur de 5 MHz, désigné par la référence 20, alimente des 10 multiplicateurs par cinq, désignés par les références 22 et 24, et le multiplicateur par cinq 24 alimente un multiplicateur par trois, désigné par la référence 26, afin de fournir un signal d'entrée de 375 MHz au mélangeur 16 par une borne 28. Le signal de sortie du mélangeur 16 apparaît sur une borne 30 sous la forme d'un signal de  $24,968 \text{ MHz} \pm f_{DH}$ . Ce signal est envoyé à un amplificateur 32 de fréquence intermédiaire, puis est appliqué à un mélangeur 34 via une 15 borne d'entrée 36. Le signal de sortie du multiplicateur par cinq 22 est envoyé à une borne d'entrée 38 du mélangeur 34, et le signal de sortie du mélangeur 34 est un signal ( $\Delta F_H$ ) de  $32 \text{ kHz} \pm f_{DH}$  apparaissant sur la borne 40, où  $f_{DH}$  est la fréquence Doppler. Ce signal est 20 envoyé à une entrée d'un amplificateur 35 de fréquence intermédiaire dont le signal de sortie est envoyé à un limiteur 43. Le limiteur 43 est un limiteur ou convertisseur de niveau qui transforme le niveau de signal venant du récepteur en niveaux logiques qui sont compatibles avec les circuits de la boucle de verrouillage de phase de l'invention. 25 Le signal est envoyé, via le limiteur 43, à des détecteurs de phase 42 et 44 via la ligne 41. Le signal de sortie du détecteur de phase 42 constitue un signal de sortie en cosinus du signal d'entrée modulé en phase et est appliqué à une borne 46. Ce signal de sortie fournit une indication de verrouillage de phase et permet le rétablissement 30 du signal d'horloge de données du dispositif. Le signal de sortie du détecteur de phase 44, c'est-à-dire le signal de sortie en sinus, est appliqué à un filtre 48, qui est un filtre du type  $(sT_2 + 1)/sT_1$ . Le filtre 48 peut être un filtre en boucle passif ou actif. Le signal de sortie du filtre 48 est appliqué à un oscillateur à com- 35 mande de tension 50 via une borne d'entrée 52. L'oscillateur 50 est conçu pour répondre au signal d'entrée 52 de manière linéaire sur l'intervalle attendu des fréquences Doppler nécessaires pour le

dispositif, soit, dans ce cas, de 1056 kHz à 2016 kHz environ. Ceci est vrai parce que, dans le mode de réalisation préféré de l'invention présenté sur la figure 1, l'oscillateur à commande de tension 50 fonctionne à 48 fois la fréquence Doppler  $\Delta F_H$ . Le signal de sortie de l'oscillateur à commande de tension 50 est envoyé à un diviseur de fréquence 56 qui divise le signal par 48 et à un diviseur de fréquence 58 qui divise la fréquence par trois. Le signal de sortie du diviseur de fréquence 56 est envoyé à une entrée 60 du détecteur de phase 44. Ceci ferme la boucle en sinus. Le signal de sortie du diviseur 56 est également envoyé, via un déphasage de  $90^\circ$  désigné par la référence 62, à une entrée 64 du comparateur de phase 42. Ceci referme la boucle en cosinus de la boucle de verrouillage de phase. Le signal de sortie 54 de l'oscillateur à commande de tension 50 est divisé dans le diviseur de fréquence 58 de manière que le signal de sortie présent sur la borne 66 vaille 16 fois la fréquence Doppler. Ce signal est envoyé à un compteur 68 qui est conçu de manière à ne pas déborder plus d'une fois durant chaque durée de bit du dispositif. Le signal de sortie en parallèle du compteur 68 est envoyé à des moyens de verrouillage 70. Les moyens de verrouillage 70 sont commandés par un signal d'échantillonage de bit appliqué à l'entrée 72 et un signal d'échantillonage de lecture appliqué à l'entrée 74. Le signal de sortie des moyens de verrouillage 70 est appliqué à la ligne omnibus 76 pour être délivrée à un processeur du dispositif qui détermine la fréquence Doppler de chaque échantillon.

Le séparateur de fréquence 12 alimente également un amplificateur 100 de haute fréquence. Le séparateur de fréquence 12 alimente également un amplificateur 100 de haute fréquence. Le signal de sortie de l'amplificateur 100 du mode de réalisation préféré de l'invention représenté sur la figure 1 est de  $149,988 \text{ MHz} \pm f_{dL}$ . Ce signal est envoyé à un mélangeur 102 dans lequel il est mélangé avec un signal de 125 MHz venant du multiplicateur par cinq 24, dont un signal d'entrée est appliqué au mélangeur 102 via une borne d'entrée 104. Le signal de sortie du mélangeur 102 est de  $24,988 \text{ MHz} \pm f_{dL}$ . Ce signal est envoyé à un amplificateur 106 de fréquence intermédiaire, puis à un mélangeur 108 via une borne d'entrée 110.

Une autre borne d'entrée 112 du mélangeur 108 reçoit un signal d'oscillateur local de 25 MHz en provenance du multiplicateur par cinq 22. Le signal de sortie du mélangeur 108 est un signal ( $\Delta F_L$ ) de 12 kHz  $\pm f_{dL}$ . Ce signal est appliqué, via un amplificateur 109 de fréquence intermédiaire et un convertisseur de niveau 113, à un comparateur de phase 114, puis à un filtre 116 qui commande un oscillateur à commande de tension 118. L'oscillateur 118 est conçu pour fonctionner à 128 fois la fréquence Doppler. Le signal de sortie de l'oscillateur à commande de tension 118 est envoyé dans un diviseur de fréquence 120 qui divise par 128 le signal venant de l'oscillateur à commande de tension 118. Le signal ainsi divisé est ensuite envoyé au détecteur de phase 114 via une borne 122. Ceci referme la boucle de verrouillage de phase du canal bas. Le signal de sortie de l'oscillateur à commande de tension 118 est également envoyé à un circuit de division par trois désigné par la référence 124 et produit un signal Doppler de canal bas défini par 128/3 fois la fréquence Doppler. Chacun des signaux  $\Delta F_H$  et  $\Delta F_L$  contient un terme continu de fréquence de -80 ppm. Dans le système de navigation dans lequel le circuit est utilisé, cette fréquence continue ou de décalage sert à empêcher que  $\Delta F$  ne soit négatif. Le compteur et les moyens de verrouillage (68 et 70) du canal de haute fréquence devraient être simplement reproduits, avec la gamme de comptage appropriée, dans le canal de basse fréquence. Ils ont été omis pour ne pas compliquer le dessin du canal de haute fréquence.

Une forme de réalisation détaillée de la boucle de verrouillage de phase, du compteur et des moyens de verrouillage du canal haut de la figure 1 est présentée sur la figure 2. Un circuit analogue pourrait être utilisé pour le canal de basse fréquence. Lorsque des numéros de référence identiques sont utilisés sur les figures 1 et 2, il s'agit d'éléments équivalents. Le signal de sortie du mélangeur 34 (voir figure 1) sur la ligne 40 est envoyé à une porte OU exclusif 43 (désignée également par la référence U1A) via un condensateur C1 et une résistance R1 (de valeurs respectives 0,1  $\mu F$  et 10 k $\Omega$ ). Le signal de sortie de la porte OU exclusif 43 est renvoyé à la même entrée par l'intermédiaire d'une résistance R<sub>2</sub> (1 M $\Omega$ ). Une deuxième entrée de la porte OU exclusif 43 est connectée

à une source de tension de référence  $+V_{DD}$  et, ainsi câblée, la porte OU exclusif 43 fait fonction de convertisseur de niveau. Le signal de sortie du convertisseur de niveau 43 apparaît sur la ligne 41 et constitue un signal d'entrée pour le détecteur de phase en cosinus 42 (désigné en outre par la référence U1B) et un signal d'entrée pour le détecteur de phase en sinus 44 (désigné en outre par la référence U1C). Le signal de sortie du détecteur de phase en cosinus 42 apparaît sur la ligne 46 et peut être utilisé de manière que ce dernier serve de détecteur d'amplitude cohérente produisant une indication de verrouillage de phase et le rétablissement du signal d'horloge de données. Le détecteur de phase en sinus 44 produit un signal de sortie sur la ligne 47 qui peut être utilisé à des fins de rétablissement de données. La résistance R3 ( $2,2 \text{ M}\Omega$ ) fournit ce signal à une entrée d'un amplificateur opérationnel 48, lequel comporte un amplificateur AR1, un condensateur de réaction C2 de  $10 \mu\text{F}$ , des résistances R4, R5, R6, R7, R8 et R9, et un condensateur C3 (respectivement  $3,3 \text{ M}\Omega$ ,  $4640 \text{ }\Omega$ ,  $21,5 \text{ k}\Omega$ ,  $5\text{k}\Omega$ ,  $21,5 \text{ k}\Omega$  et  $768 \text{ k}\Omega$ , et  $15 \mu\text{F}$ ). Le potentiomètre R8 est connecté à la terre par l'intermédiaire de R7 et est connecté à la tension  $V_{DD}$  par l'intermédiaire de R6. Le curseur du potentiomètre R8 est connecté à la jonction de C3 et R9 de manière à produire un niveau de polarisation continu pour l'entrée positive de l'amplificateur opérationnel AR1, puisque l'autre borne de R9 est connectée à la broche d'entrée 3 de AR1. La sortie de AR1 est connectée à une résistance R10 de  $2200 \text{ }\Omega$  et un condensateur C2 de  $10 \mu\text{F}$ ; l'autre extrémité de C2 est connectée via la résistance R5 à l'entrée de polarité négative de AR1. Ceci fournit une branche de réaction pour AR1, et l'on choisit les valeurs des résistances et des condensateurs d'accompagnement de manière à constituer un filtre actif passe-bas. Le signal de sortie est transmis via la résistance R10 à l'entrée de l'oscillateur à commande de tension 50 (désigné en outre par la référence U3) sur la ligne 52. Un condensateur C4, d'une capacité de  $180 \mu\text{F}$ , et un condensateur  $C_X$  sont connectés en parallèle sur les broches 3 et 4 de l'oscillateur à commande de tension 50 afin de produire une commande de fréquence nominale dans le circuit intégré. On choisit  $C_X$  de manière à permettre un fonctionnement approprié en fréquence de l'oscillateur 50 lors de l'essai du circuit. La sortie ( $Q_0$ ) de l'oscillateur à commande de

tension 50 est connectée par la ligne 54 à l'entrée ( $C_p$ ) d'un circuit U4 de division par douze. Un signal de sortie 16 ( $\Delta F_H$ ), venant de la sortie  $Q_2$  du circuit U4 de division par douze, apparaît sur la broche 9 via la ligne 66. Un autre signal de sortie 8 ( $F_H$ ) de U4 (borne  $Q_3$ ) apparaît sur la broche 8, c'est-à-dire la ligne 67. Un troisième signal de sortie de U4 apparaît sur la sortie  $Q_0$  correspondant à la broche 12 et est envoyé, via un inverseur 55, à une entrée ( $C_p$ ) d'un circuit U5 de division par quatre, au niveau d'une broche 15. (Les diviseurs U4 et U5 sont en outre désignés par les références 53 et 59). Ensemble, les diviseurs 53 et 59 constituent un diviseur par 48, désigné par la référence 57. Naturellement, on peut choisir le diviseur 57 de manière à obtenir un facteur de division N quelconque approprié. Un premier signal de sortie 2( $\Delta F_H$ ) de U5 apparaît sur la broche 6 (sortie  $Q_0$ ) et est envoyé à la broche 3 (entrée C) du déphasage à bascule de type D 62 (désigné également par la référence U2). Un autre signal de sortie  $\Delta F_H$  venant du diviseur par quatre, désigné conjointement par les références U5 et 59, est envoyé de la broche 11 (sortie  $Q_1$ ) à la broche 6 du détecteur de phase 44 constitué par la porte OU exclusif et à la broche 5, c'est-à-dire l'entrée D, du déphasage 62 de type bascule. La sortie  $Q_1$  associée à la broche 1, de la bascule 62 est connectée au détecteur de phase en cosinus 42, formé de la porte OU exclusif, via la ligne 64.

En fonctionnement, le convertisseur de niveau ou porte OU exclusif 43 sert à déplacer les niveaux de sortie du récepteur sur le niveau demandé par les comparateurs de phase. Le signal de sortie du convertisseur de niveau 43 est envoyé à une entrée du détecteur de phase en cosinus 42. L'autre entrée du détecteur de phase 42 vient de la bascule 62 constituant un déphasage de  $90^\circ$ . Le signal de sortie du détecteur de phase 42 fournit un indication de verrouillage de phase et un signal approprié au rétablissement du signal d'horloge de données après un traitement ultérieur. La sortie du convertisseur de niveau 43 alimente également une entrée de la porte OU exclusif 44 (détecteur de phase en sinus). Le signal venant du détecteur de phase en sinus 44 subit l'effet du filtre actif 48 afin de produire sur la ligne 52 un signal continu, qui

est un signal continu proportionnel à l'erreur de phase existant entre les signaux des lignes 41 et 60. Ce signal sert à commander la fréquence de l'oscillateur 50, qui peut être un oscillateur à commande de tension et, parce que l'oscillateur à commande de tension 50 est suivi par un compteur ou diviseur, 57, par 48, la fréquence de l'oscillateur à commande de tension 50 vaut 48 fois la fréquence Doppler. Ce signal, c'est-à-dire  $48(\Delta F_H)$  apparaît sur la ligne 54 du niveau de l'entrée du diviseur 53. La sortie  $Q_2$  correspondant à la broche 9 du diviseur 53 porte la fréquence d'entrée de la ligne 54 divisée par trois. Ceci signifie que le signal de la ligne 66 venant du diviseur 53 est un signal qui vaut  $16(\Delta F_H)$ . Un signal de sortie, divisé par six, du diviseur 53 apparaît sur la broche 8 ( $Q_3$ ) et vaut  $8(\Delta F_H)$ . La sortie  $Q_0$  du diviseur 53 via la broche 12 porte la fréquence d'entrée divisée par douze, qui vaut  $4(\Delta F_H)$ . L'inverseur 50 ne sert qu'au traitement des différences de polarité entre le diviseur 53 et le diviseur 59. Le circuit 59 est un circuit de division par quatre qui produit la fréquence Doppler à sa sortie, via  $Q_1$ , c'est-à-dire la broche 11, c'est-à-dire la ligne 60. La sortie  $Q_0$  associée à la broche 6 porte une fréquence de  $2(\Delta F_H)$  et cette fréquence est utilisée pour alimenter le déphasage 62 par sa broche 3, (correspondant à l'entrée d'horloge). La sortie  $Q$  associée à la broche 1 du déphasage 62 alimente l'entrée par la broche 13 du détecteur de phase en cosinus 42.

On peut alors voir que le signal de sortie  $16(\Delta F_H)$  de la ligne 66 venant du diviseur 53 par douze peut être utilisé dans le compteur 68 (voir figure 1) et que la résolution qui peut être obtenue sur la base du comptage de ce signal est 16 fois plus précise que ne serait le comptage de la fréquence Doppler elle-même. Dans ce dispositif, une valeur de comptage Doppler représente un changement de trois quart de mètre en intervalle incliné, de sorte que, si l'on reçoit ou traite la fréquence Doppler à 16 fois la fréquence réelle, on peut obtenir une résolution d'intervalle de  $3/64$  de mètre dans le mode de réalisation présenté.

Les parties qui ont été utilisées pour construire le circuit de la figure 2 sont indiquées ci-dessus.

Les portes OU exclusif 43, 42 et 44 sont des éléments désignés par la référence "MC14070BAL".

La bascule 62 est un élément de référence "MC14013BAL".

L'oscillateur à commande de tension 50 fait partie

5 d'un élément de référence "MC4324L".

Le diviseur 53 par douze est un élément de référence

"SN54LS92J".

Le diviseur 59 par quatre est un élément de référence

"MC14029BAL".

10 L'amplificateur opérationnel AR1 est un élément de

référence "CA3140".

Tous les éléments dont la référence commence par "MC"

et "SN" sont produits par la société des Etats-Unis d'Amérique Motorola

Inc, tandis que l'amplificateur opérationnel AR1 de référence "CA3140"

15 est produit par la Société des Etats-Unis d'Amérique RCA Corporation.

On notera que les valeurs numériques des composants

résistifs et capacitifs sont données à titre d'exemple.

On voit que, en utilisant le dispositif de l'invention

tel que décrit ci-dessus, il est possible d'utiliser des multiples

20 de la fréquence Doppler à des fins de comptage de manière à augmenter

la résolution du dispositif. Naturellement, il apparaîtra clairement

à l'homme de l'art que des facteurs multiplicatifs autres que

ceux indiqués ci-dessus peuvent être utilisés et que divers points

de prise intermédiaire des diviseurs peuvent être utilisés à des

25 fins relatives au comptage Doppler.

Bien entendu, l'homme de l'art sera en mesure d'imaginer,

à partir du dispositif et du procédé dont la description vient

d'être donnée à titre simplement illustratif et nullement limitatif,

diverses autres variantes et modifications ne sortant pas du cadre

30 de l'invention.

REVENDICATIONS

1. Dispositif permettant de mesurer des valeurs de comptage de cycles d'un signal inconnu de fréquence variable, comprenant une boucle de verrouillage de phase qui possède un détecteur de phase (44), le détecteur de phase (44) ayant au moins 5 une borne de sortie (47) et une borne d'entrée (41, 60), et un oscillateur commandé (50) ayant au moins une borne de signal de sortie (54), le dispositif étant caractérisé par :

- un circuit (56) de division par un facteur N ayant une borne d'entrée (54) et une borne de sortie (60), la borne 10 d'entrée (54) du diviseur (56) étant connectée à la borne de sortie de l'oscillateur commandé (50), la borne de sortie du diviseur (56) étant connectée à l'une (60) de deux bornes d'entrée du détecteur de phase (44); et

- un compteur (68) ayant une borne d'entrée (66) et 15 plusieurs bornes de sortie, la borne d'entrée (66) du compteur étant connectée à la borne de sortie de l'oscillateur commandé (50), les bornes de sortie étant destinées à produire un signal de sortie représentatif d'un multiple de la valeur de comptage de cycles de la fréquence variable inconnue, ledit multiple étant égal à N.

2. Dispositif permettant de mesurer des valeurs de comptage de cycles d'un signal de fréquence inconnue dans les limites d'un laps de temps prédéterminé, le dispositif étant caractérisé par :

- une boucle de verrouillage de phase, ladite boucle comprenant en outre :

- 25 un détecteur de phase (44) ayant une première entrée (41) et une deuxième entrée (60) ainsi qu'une sortie (47), ledit signal inconnu étant envoyé à la première entrée (41) du détecteur de phase;

- un filtre en boucle (48) ayant une entrée (47) et 30 une sortie (52), la sortie (47) du détecteur de phase (44) étant connectée à l'entrée du filtre (48);

- un oscillateur commandé ayant une entrée (52) et une sortie (54), la sortie (52) du filtre (48) étant connectée à l'entrée (52) de l'oscillateur commandé (50);

- 35 et

- un circuit (56) de division par un facteur N ayant une entrée (54) et au moins une sortie (60), la sortie de l'oscillateur commandé (50) étant connectée à l'entrée du circuit (56) de division par un facteur N et à une borne de sortie (66) de multiplication par un facteur N de la boucle de verrouillage de phase, la sortie du circuit (56) de division par un facteur N étant connectée à la deuxième entrée (60) du détecteur de phase (44); et

- 10           un moyen (68) permettant de compter des cycles d'un signal sur ladite borne de sortie (66) de multiplication par un facteur N de la fréquence pendant ledit laps de temps prédéterminé.

3.           Dispositif selon la revendication 2, caractérisé en ce que la boucle de verrouillage de phase comporte en outre :

- 15           un autre détecteur de phase (42) ayant une première entrée (41) et une deuxième entrée (64) ainsi qu'une sortie (46);

un déphasageur (62) ayant au moins une entrée (60) et une sortie (64), la sortie du déphasageur (62) étant connectée à la deuxième entrée (64) dudit autre détecteur de phase (42), ledit autre détecteur de phase (42), ladite entrée (60) du déphasageur (62) étant connectée à ladite sortie (60) du circuit (56) de division par un facteur N; et

- 20           un moyen (46) servant à indiquer le verrouillage de phase, ledit moyen d'indication étant connecté à la sortie (46) et répondant à un signal de ladite sortie (46) du deuxième détecteur de phase (42).

- 25           Dispositif selon la revendication 2 ou 3, caractérisé en ce qu'il comprend en outre : un moyen (68) permettant de déterminer une fréquence du signal connu sur la base desdits cycles comptés, du laps de temps prédéterminé et du facteur N.

- 30           Procédé de mesure de la fréquence d'un signal inconnu de fréquence variable utilisant une boucle de verrouillage de phase, caractérisé en ce qu'il comprend les opérations suivantes :

- 35           diviser un signal de sortie (54) d'un oscillateur commandé (50) de la boucle de verrouillage de phase par un nombre

- entier prédéterminé N dans un circuit (56) diviseur de fréquence;

comparer les phases d'un signal de sortie du circuit (56)

diviseur de fréquence et du signal inconnu dans un détecteur de fré-

quence (44) de la boucle de verrouillage de phase;

- 5 éliminer par filtrage les composantes de haute fré-

quence d'un signal de sortie dudit détecteur de phase (44);

commander en fréquence ledit signal de sortie (54)

de l'oscillateur commandé (50) au moyen du signal de sortie filtré

du détecteur de phase (44) de façon que la fréquence du signal de

10 sortie de l'oscillateur commandé (50) soit un multiple d'ordre N dudit

signal inconnu, ledit ordre de multiplication N étant ledit nombre

entier prédéterminé N; et

compter le signal de sortie de l'oscillateur commandé (50)

sur une période de temps prédéterminée afin de déterminer un nombre

15 de cycles du signal de sortie de l'oscillateur commandé (50) se pro-

duisant dans ladite période de temps prédéterminée.

6. Procédé selon la revendication 5, caractérisé en outre

par l'opération suivante :

calculer une fréquence entière et fractionnelle du

20 signal inconnu en utilisant ledit nombre compté de cycles, le nombre

entier prédéterminé N et ledit intervalle de temps prédéterminé.

*F/G /*