(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 102 49 869 B4 2006.08.31

(12)

## Patentschrift

(21) Aktenzeichen: **102 49 869.5**

(22) Anmelddatum: **25.10.2002**

(43) Offenlegungstag: **15.05.2003**

(45) Veröffentlichungstag

der Patenterteilung: **31.08.2006**

(51) Int Cl.<sup>8</sup>: **G11C 11/14 (2006.01)**

**G11C 11/15 (2006.01)**

**G11C 5/06 (2006.01)**

**G11C 5/14 (2006.01)**

**G11C 7/02 (2006.01)**

**G11C 7/24 (2006.01)**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (30) Unionspriorität:<br>2001/327690 25.10.2001 JP<br>2002/070583 14.03.2002 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IEEE<br>International Solid-State Circuits Conference,<br>7-9 Feb. 2000, 130-131;<br>Naji, P.K.; Durlam, M.; Tehrani, S.; Calder, J.;<br>DeHerrera, M.F.: "A 256 kb 3.0 V 1T1MTJ nonvolatile magnetoresistive RAM". IEEE International Solid-State Circuits Conference, 5-7 Feb. 2001, 122-123, 438;<br>Petschauer, R.: "Engineering aspects of magnetic film memories". IEEE Transactions on Magnetics, Bd. 1, Nr. 3, Sept. 1965, 185-192;<br>Wang, Z.G.; Mapps, D.J.; He, L.N.; Clegg, W.W.;<br>Wilton, D.T.; Robinson, P.; Nakamura, Y.:<br>"Feasibility of ultra-dense spin-tunneling random access memory". IEEE Transactions on Magnetics,<br>Bd. 33, Nr. 6, Nov. 1997, 4498-4512;<br>Brown, J.L.; Pohm, A.V.; Mundon, S.A.; Sinclair,<br>R.A.; Cooper, D.K.; Black, W.C.; Dupuis, T.J.;<br>Daughton, J.M.: "One Megabit Memory Chip Using Giant Magnetoresistive Memory Cells".<br>Nonvolatile<br>Memory Technology Review, 1993, 22-24 Juni<br>1993,<br>50-53; |

| (73) Patentinhaber:<br><b>Mitsubishi Denki K.K., Tokio, JP</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (74) Vertreter:<br><b>PRÜFER &amp; PARTNER GbR, 81545 München</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (72) Erfinder:<br><b>Hidaka, Hideto, Tokio, JP</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:<br>DE 102 28 560 A1<br>DE 100 53 965 A1<br>DE 15 24 770 A<br>Scheuerlein, R.; Gallagher, W.; Parkin, S.;<br>Lee, A.; Ray, S.; Robertazzi, R.; Reohr, W.: "A 10ns read and write non-volatile memory array using a magnetic tunnel junction and FET switch in each cell". IEEE International Solid-State Circuits Conference, 7-9 Feb. 2000, 128-129;<br>Durlam, M.; Naji, P.; DeHerrera, M.; Tehrani, S.;<br>Kerszykowski, G.; Kyler, K.: "Nonvolatile RAM based on magnetic tunnel junction elements". |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

(54) Bezeichnung: **Magnetische Dünnfilmspeichervorrichtung zum Durchführen eines Datenschreibvorgangs durch Anlegen eines Magnetfelds**

(57) Hauptanspruch: Magnetische Dünnfilmspeichervorrichtung mit einem Speicherfeld (2) mit einer Mehrzahl von darin angeordneten Speicherzellen (MC) zum magnetischen Datenspeichern, wobei jede Speicherzelle einen magnetischen Speicherabschnitt (TMR) aufweist mit einem elektrischen Widerstandswert, der sich entsprechend einer Magnetisierungsrichtung ändert, die durch Anlegen eines vorgeschriebenen Magnetfelds überschrieben werden kann; einer peripheren Schaltung (5, 5#), die in einem an das Speicherfeld angrenzenden Bereich bereitgestellt ist, zum Durchführen eines Datenlesebetriebs und eines Datenschreibbetriebs aus dem bzw. in das Speicherfeld; und

einer ersten und einer zweiten Stromversorgungsleitung (PL, GL) zum Zuführen einer Betriebsspannung (Vcc, GND) zu der peripheren Schaltung; wobei die erste und die zweite Versorgungsleitung so angeordnet sind, dass ein durch einen durch die erste Versorgungsleitung fließenden Strom erzeugtes Magnetfeld und ein durch einen durch die zweite Versorgungsleitung fließenden Strom erzeugtes Magnetfeld einander in dem Speicherfeld gegenseitig aufheben.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich allgemein auf eine magnetische Dünnfilm-Speichervorrichtung. Insbesondere bezieht sich die vorliegende Erfindung auf einen Direktzugriffspeicher (RAM) mit Speicherzellen mit einem magnetischen Tunnelübergang (MTJ).

## Stand der Technik

**[0002]** Eine MRAM-Vorrichtung (Magnetic Random Access Memory = Magnetischer Direktzugriffspeicher) hat als eine Speichervorrichtung, die in der Lage ist, mit geringem Leistungsverbrauch Daten auf nicht-flüchtige Weise zu speichern, Aufmerksamkeit auf sich gezogen. Die MRAM-Vorrichtung ist eine Speichervorrichtung, die in der Lage ist, unter Verwendung einer Mehrzahl von magnetischen Dünnfilmelementen, die in einer integrierten Halbleiterschaltung ausgebildet sind, Daten auf nicht-flüchtige Weise zu speichern und auf jedes dieser magnetischen Dünnfilmelemente einen Direktzugriff durchzuführen.

**[0003]** Insbesondere zeigen jüngere Ankündigungen, dass die Verwendung magnetischer Dünnfilmelemente mit einem magnetischen Tunnelübergang MTJ (Magnetic Tunnel Junction) als Speicherzelle die Leistungsfähigkeit einer MRAM-Vorrichtung beträchtlich verbessert. Die MRAM-Vorrichtung, die Speicherzellen mit einem magnetischen Tunnelübergang beinhaltet, ist in der technischen Literatur veröffentlicht wie z.B. in "A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell", ISSCC Digest of Technical Papers, TA7.2, Februar 2000, "Nonvolatile RAM based on Magnetic Tunnel Junction Elements", ISSCC Digest of Technical Papers, TA7.3, Februar 2000, und "A 256kb 3.0V 1T1MTJ Nonvolatile Magneto resistive RAM", ISSCC Digest of Technical Papers, TA7.6, Februar 2001.

**[0004]** In der Veröffentlichung "Engineering Aspects of Magnetic Film Memories", IEEE Transactions on Magnetics, Vol. MAG-1, No. 3, September 1965 werden Magnetfilmspeicher mit destruktiver Auslese und nichtdestruktiver Auslese beschrieben. Dabei wird darauf hingewiesen, dass eine Speicherzelle durch ein transversales Feld beeinflusst wird, welches beim Betrieb einer benachbarten Wortleitung auftritt.

**[0005]** In "Feasability of Ultra-Dense Spin-Tunneling Random Access Memory", IEEE Transactions on Magnetics, Vol. 33, No. 6, November 1997 werden die Ergebnisse von FEM-Simulationen des Verhaltens von STrams beschrieben. Weiterhin wird ein Design vorgestellt, bei dem durch laterales Anbringen eines Materials hoher Permeabilität an den Wort- und Bitleitungen das Übersprechen verringert wird, da der magnetische Fluss geschlossen wird.

**[0006]** Brown et al. beschreiben in "One Megabit Memory Chip Using Giant Magnetoresistive Memory Cells", Nonvolatile Memory Technology Review, Juni 1993, Seite 50-53 einen 1-Megabit-Speicherchip, bei dem für die Speicherzellen GMR-Materialien verwendet werden. Um beim Anschalten des Wortleitungsstroms auftretenden Störungen zu begrenzen, ist die Rückseite des Chips mit Gold beschichtet.

**[0007]** DE 1524 770 A offenbart einen magnetischen Dünnenschichtspeicher, bei dem ein notwendiger Worttreibstrom dadurch reduziert wird, dass eine außerhalb der beiden Magnetschichtelemente angeordnete zusätzliche magnetfelderzeugende Leiteranordnung ein Vorspannungsfeld an die Speicherzellen entlang einer harten Achse angelegt wird. Dabei wird durch die Verwendung einer Magnetflußkopplung in der harten Achse eine Verringerung des Streuflusses in Richtung der Bitleitungen ermöglicht.

**[0008]** Die ältere Anmeldung DE 102 28 560 derselben Anmelderin beschreibt eine Dünnfilmmagnetspeichervorrichtung mit einer Datenlesestromeinstellungsfunktion. Unter anderem wird eine Dünnfilmmagnetspeichervorrichtung mit Dummyspeicherzellen offenbart, welche einen Dummymagnetspeicherbereich mit einem elektrischen Zwischenwiderstandswert und ein Dummyzugriffselement, das elektrisch mit dem Dummymagnetspeicherbereich in Reihe geschaltet ist, enthalten.

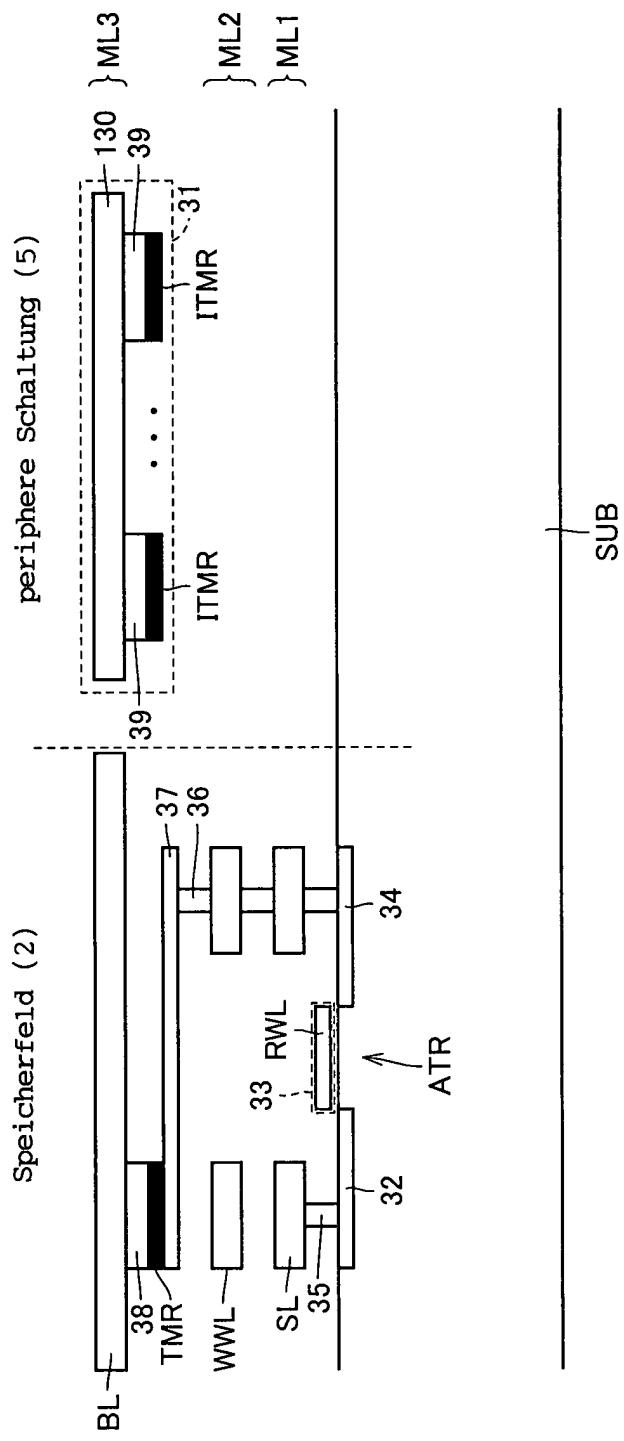

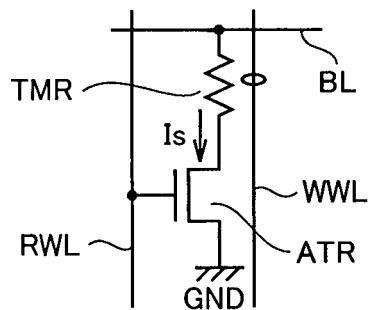

**[0009]** **Fig. 39** ist eine schematische Darstellung des Aufbaus einer Speicherzelle mit magnetischem Tunnelübergang (im Folgenden gelegentlich einfach als "MTJ-Speicherzelle" bezeichnet). Wie in **Fig. 39** dargestellt beinhaltet eine MTJ-Speicherzelle ein magnetoresistives Tunnelelement TMR, dessen elektrischer Widerstand sich entsprechend dem Speicherdatenpegel ändert, und ein Zugriffselement ATR zum Bilden eines Pfads für einen Lesestrom  $I_s$ , der bei dem Datenlesevorgang durch das magnetoresistive Tunnelelement TMR fließt. Da typischerweise ein Feldeffekttransistor als Zugriffselement ATR verwendet wird, wird das Zugriffselement ATR im Folgenden gelegentlich als Zugriffstransistor bezeichnet. Der Zugriffstransistor ATR ist zwischen dem magnetoresistiven Tunnelelement TMR und einer feste Spannung (Massespannung GND) geschaltet.

**[0010]** Für die MTJ-Speicherzelle sind eine Schreibwortleitung WWL (Write Word Line) für den Datenschreibbetrieb, eine Lesewortleitung RWL (Read Word Line) für den Datenlesebetrieb und eine Bitleitung BL (Bit Line) bereitgestellt. Die Bitleitung BL dient im Datenlesebetrieb und im Datenschreibbetrieb als Datenleitung zum Übertragen eines elektrischen Signals entsprechend dem Speicherdatenpegel.

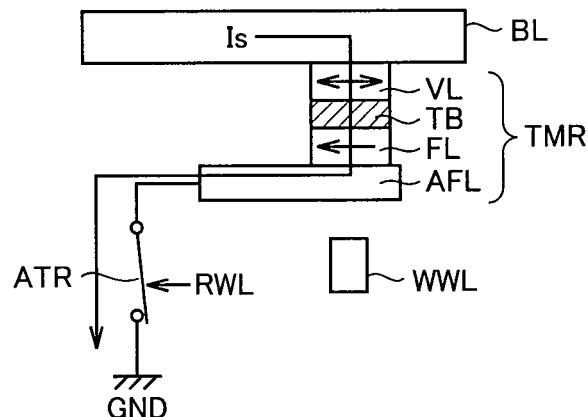

**[0011]** Fig. 40 ist eine konzeptionelle Darstellung, die den Datenlesebetrieb aus der MTJ-Speicherzelle veranschaulicht. Wie in Fig. 40 dargestellt beinhaltet das magnetoresistive Tunnelement TMR eine Schicht aus einem ferromagnetischen Material FL mit einer festen Magnetisierungsrichtung (im folgenden gelegentlich einfach als "feste magnetische Schicht" bezeichnet), eine Schicht aus einem ferromagnetischen Material VL, die in einer Richtung magnetisiert ist, die einem von außen angelegten Magnetfeld entspricht (im folgenden gelegentlich einfach als "freie magnetische Schicht" bezeichnet), und eine antiferromagnetische Materialschicht AFL zum Fixieren der Magnetisierungsrichtung der festen magnetischen Schicht FL. Zwischen der festen magnetischen Schicht FL und der freien magnetischen Schicht VL ist eine Tunnelbarriere (Tunnelschicht) TB aus einer Isolierschicht ausgebildet. Entsprechend dem Speicherdatenpegel ist die freie magnetische Schicht VL entweder in dieselbe (parallele) Richtung magnetisiert wie die feste magnetische Schicht FL oder in die entgegengesetzte (antiparallele) Richtung. Die feste magnetische Schicht FL, die Tunnelbarriere TB und die freie magnetische Schicht VL bilden einen magnetischen Tunnelübergang MTJ.

**[0012]** Beim Datenlesebetrieb wird der Zugriffstransistor ATR als Reaktion auf eine Aktivierung der Lesewortleitung RWL eingeschaltet. Dadurch kann ein Lesestrom  $I_s$  durch einen Strompfad fließen, der durch die Bitleitung BL, das magnetoresistive Tunnelelement TMR, den Zugriffstransistor ATR und die Massespannung GND gebildet wird.

**[0013]** Der elektrische Widerstandswert des magnetoresistiven Tunnelements TMR ändert sich entsprechend der Beziehung zwischen den Magnetisierungsrichtungen der festen magnetischen Schicht FL und der freien magnetischen Schicht VL. Genauer gesagt: Wenn die feste magnetische Schicht FL und die freie magnetische Schicht VL dieselbe (parallele) Magnetisierungsrichtung aufweisen, hat das magnetoresistive Tunnelement TMR einen geringeren elektrischen Widerstandswert als in dem Fall, in dem sie entgegengesetzte (antiparallele) Magnetisierungsrichtungen aufweisen.

**[0014]** Wenn die freie magnetischen Schicht VL in der dem Speicherdatenpegel entsprechenden Richtung magnetisiert ist, variiert dementsprechend eine durch den Lesestrom  $I_s$  in dem magnetoresistiven Tunnelement TMR erzeugte Spannungsänderung entsprechend dem Speicherdatenpegel. Daher kann durch Aufladen der Bitleitung BL auf eine vorgesehene Spannung und anschließendes Zuführen des Lesestroms  $I_s$  zu dem magnetoresistiven Tunnelement TMR der Speicherdatenwert in der MTJ-Speicherzelle durch Erfassen der Spannung auf der Bitleitung BL gelesen werden.

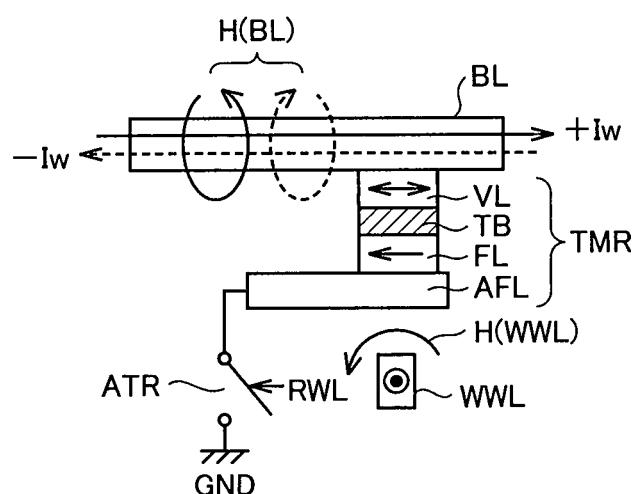

**[0015]** Fig. 41 ist eine konzeptionelle Darstellung, die den Datenschreibbetrieb in die MTJ-Speicherzelle veranschaulicht. Wie in Fig. 41 dargestellt wird in dem Datenschreibbetrieb die Lesewortleitung RWL deaktiviert und der Zugriffstransistor ATR ausgeschaltet. In diesem Zustand wird der Schreibwortleitung WWL und der Bitleitung BL ein Datenschreibstrom zum Magnetisieren der freien magnetischen Schicht VL in der dem Schreibdatenpegel entsprechenden Richtung zugeführt. Die Magnetisierungsrichtung der freien magnetischen Schicht VL wird durch die Kombination der Richtungen der Datenschreibströme festgelegt, die durch die Schreibwortleitung WWL und die Bitleitung BL fließen.

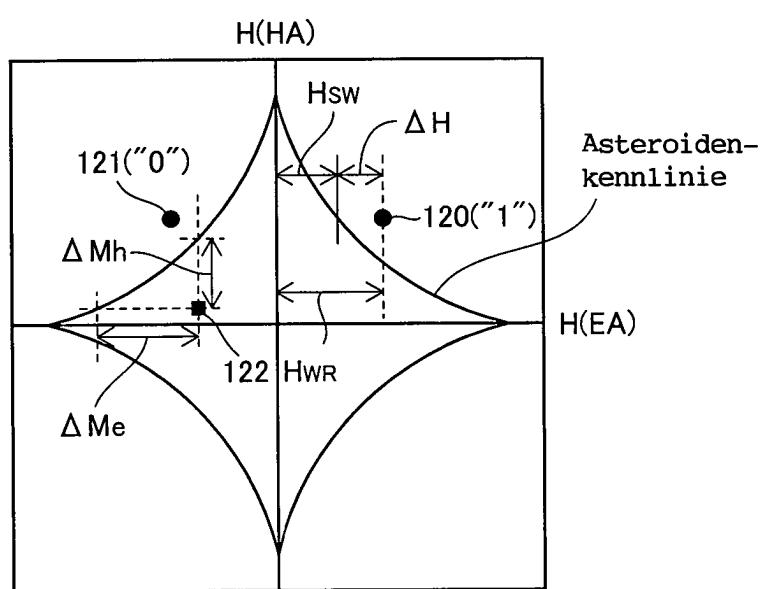

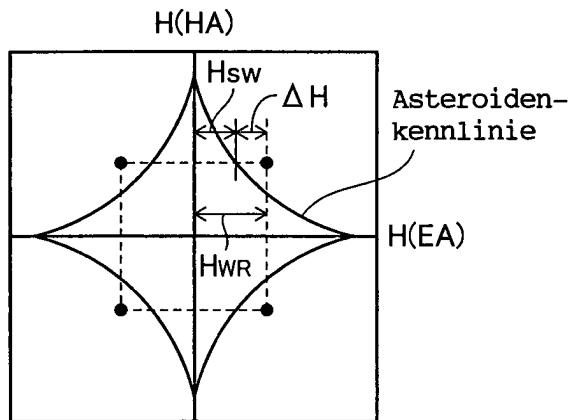

**[0016]** Fig. 42 ist eine konzeptionelle Darstellung zur Erläuterung des Zusammenhangs zwischen dem Datenschreibstrom und der Magnetisierungsrichtung des magnetoresistiven Tunnelements TMR beim Datenschreibbetrieb in die MTJ-Speicherzelle. In Fig. 42 bezeichnet die Abszisse  $H(EA)$  ein Magnetfeld, das an die freie magnetische Schicht VL des magnetoresistiven Tunnelements TMR in der leicht zu magnetisierenden Richtung (EA) angelegt ist. Die Ordinate  $H(HA)$  bezeichnet ein Magnetfeld, das an die freie magnetische Schicht VL in der schwer zu magnetisierenden Richtung (HA) angelegt ist. Die Magnetfelder  $H(EA)$  und  $H(HA)$  entsprechen jeweils zwei Magnetfeldern, die durch die in der Bitleitung BL und in der Schreibwortleitung WWL fließenden Ströme erzeugt werden.

**[0017]** In der MTJ-Speicherzelle ist die feste magnetische Schicht FL in der festen Richtung in der leicht zu magnetisierenden Achse der freien magnetischen Schicht VL magnetisiert. Die freie magnetische Schicht VL ist entsprechend dem Speicherdatenpegel ("1" bzw. "0") entweder in dieselbe (parallele) Richtung in der leicht zu magnetisierenden Achse magnetisiert wie die feste magnetische Schicht FL oder in die entgegengesetzte (antiparallele) Richtung. Im Folgenden bezeichnen  $R_1$  und  $R_0$  (mit  $R_1 > R_0$ ) die elektrischen Widerstandswerte des magnetoresistiven Tunnelements TMR, die jeweils den zwei Magnetisierungsrichtungen der freien magnetischen Schicht VL entsprechen.

**[0018]** Die MTJ-Speicherzelle ist somit in der Lage, entsprechend den zwei Magnetisierungsrichtungen der freien magnetischen Schicht VL 1-Bit-Daten ("1" bzw. "0") zu speichern.

**[0019]** Die Magnetisierungsrichtung der freien magnetischen Schicht VL kann nur dann neu geschrieben werden, wenn die Summe der angelegten Magnetfelder  $H(EA)$  und  $H(HA)$  den Bereich außerhalb der in Fig. 42 dargestellten Asteroidenkennlinie erreicht. Anders ausgedrückt: Die Magnetisierungsrichtung der freien magnetischen Schicht VL ändert sich nicht, wenn ein angelegtes Datenschreibmagnetfeld dem

Bereich innerhalb der Asteroidenkennlinie entspricht.

**[0020]** Wie aus der Asteroidenkennlinie ersichtlich, ermöglicht das Anlegen eines Magnetfelds in der schwer zu magnetisierenden Richtung an die freie magnetische Schicht VL eine Verringerung eines Magnetisierungsschwellwerts, der zum Ändern der Magnetisierungsrichtung in der leicht zu magnetisierenden Richtung erforderlich ist.

**[0021]** Wenn der Schreibarbeitspunkt wie in dem in **Fig. 42** dargestellten Beispiel festgelegt ist, muss ein Datenschreibmagnetfeld in der leicht zu magnetisierenden Richtung, um geschrieben zu werden, in der MTJ-Speicherzelle eine Stärke  $H_{WR}$  haben. Anders ausgedrückt wird der Wert des Datenschreibstroms, der der Bitleitung BL bzw. der Schreibwortleitung WWL zugeführt werden soll, so festgelegt, dass das Datenschreibmagnetfeld  $H_{WR}$  erzeugt wird. Im allgemeinen ist das Datenschreibmagnetfeld  $H_{WR}$  definiert als die Summe einer Schalmagnetfeldstärke  $H_{SW}$ , die zum Schalten der Magnetisierungsrichtung erforderlich ist, und einem Rand  $\Delta H$ . Das Datenschreibmagnetfeld  $H_{WR}$  ist somit definiert als  $H_{WR} = H_{SW} + \Delta H$ .

**[0022]** Um den Speicherdatenwert der MTJ-Speicherzelle, d.h. die Magnetisierungsrichtung des magnetoresistiven Tunnelelements TMR zu überschreiben, muss sowohl an die Schreibwortleitung WWL als auch an die Bitleitung BL ein Datenschreibstrom mit mindestens einem vorhergesehenen Pegel zugeführt werden. Die freie magnetische Schicht VL in dem magnetoresistiven Tunnelement TMR wird somit entsprechend der Richtung des Datenschreibmagnetfelds in der leicht zu magnetisierenden Achse (EA) entweder in dieselbe (parallele) oder in die entgegengesetzte (antiparallele) Richtung magnetisiert wie die feste magnetische Schicht FL. Die in das magnetoresistive Tunnelement TMR geschriebene Magnetisierungsrichtung, d.h. der Speicherdatenwert der MTJ-Speicherzelle, wird auf nichtflüchtige Weise gehalten, bis ein anderer Datenschreibvorgang durchgeführt wird.

**[0023]** Wie oben beschrieben ändert sich der elektrische Widerstandswert des magnetoresistiven Tunnelements TMR entsprechend der Magnetisierungsrichtung, die durch ein angelegtes Datenschreibmagnetfeld überschrieben werden kann. Dementsprechend kann ein nichtflüchtiges Datenspeichern verwirklicht werden, indem jeweils die zwei Magnetisierungsrichtungen der freien magnetischen Schicht VL in dem magnetoresistiven Tunnelement TMR als Speicherdatenpegel ("0" bzw. "1") verwendet werden.

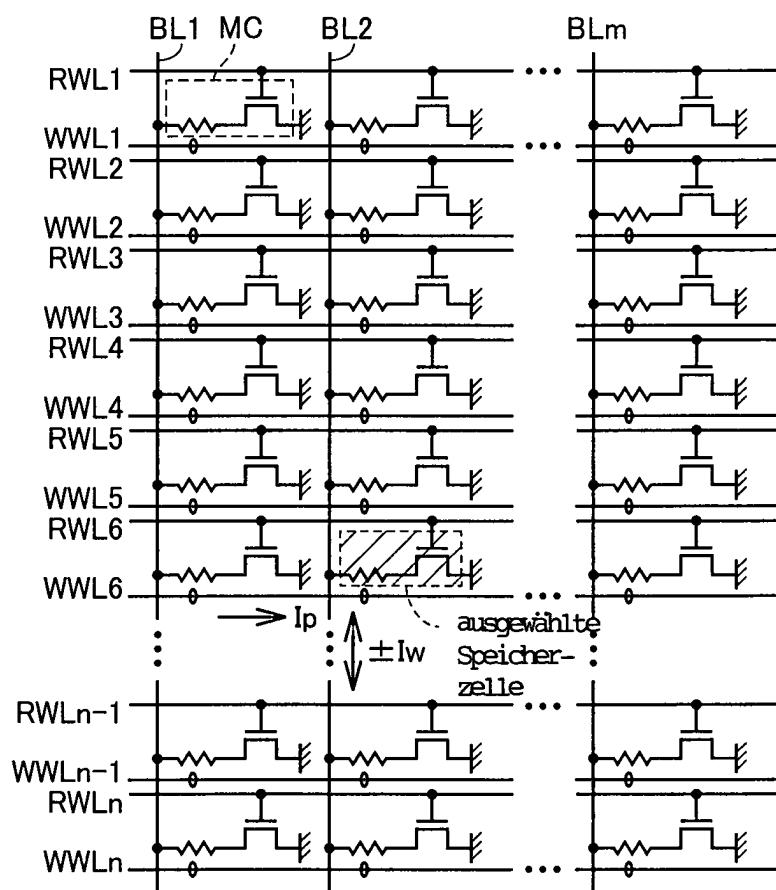

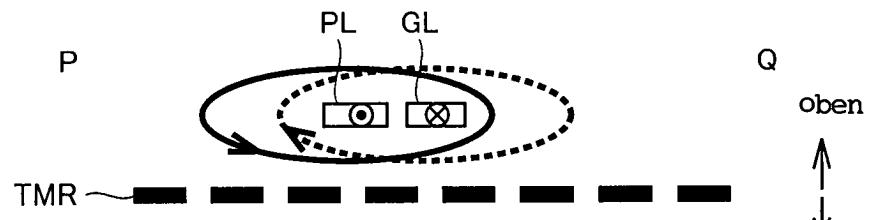

**[0024]** **Fig. 43** ist eine konzeptionelle Darstellung, die den Feldaufbau der in integrierter Weise in einer Matrix angeordneten MTJ-Speicherzellen zeigt. Wie in **Fig. 43** dargestellt, sind die MTJ-Speicherzellen in

n Zeilen und m Spalten angeordnet (wobei n, m natürliche Zahlen sind). Wie oben beschrieben müssen für jede MTJ-Speicherzelle eine Bitleitung BL, eine Schreibwortleitung WWL und eine Lesewortleitung RWL bereitgestellt sein.

**[0025]** Im Datenschreibbetrieb wird einer Schreibwortleitung WWL und einer Bitleitung BL, die der ausgewählten Speicherzelle entsprechen, ein vorgesehener Datenschreibstrom zugeführt. Wenn z.B. Daten in die in **Fig. 43** schraffiert dargestellte MTJ-Speicherzelle geschrieben werden sollen, wird der Schreibwortleitung WWL6 ein Datenschreibstrom  $I_p$  in der Zeilenrichtung zugeführt und der Bitleitung BL2 ein Datenschreibstrom  $I_w$  in der Spaltenrichtung. Dementsprechend empfängt die ausgewählte MTJ-Speicherzelle sowohl ein Datenschreibmagnetfeld  $H(EA)$  in der leicht zu magnetisierenden Richtung als auch ein Datenschreibmagnetfeld  $H(HA)$  in der schwer zu magnetisierenden Richtung jenseits des in **Fig. 42** dargestellten Schalmagnetfelds  $H_{SW}$ . Demzufolge wird die freie magnetische Schicht VL in der dem Schreibdatenpegel entsprechenden Richtung magnetisiert.

**[0026]** Andererseits empfangen die nicht ausgewählten Speicherzellen, die in derselben Speicherzellenzeile bzw. in derselben Speicherzellenspalte angeordnet sind wie die ausgewählte Speicherzelle, (in dem in **Fig. 43** dargestellten Beispiel die nicht ausgewählten Speicherzellen, die der Schreibwortleitung WWL6 entsprechen und die nicht ausgewählten Speicherzellen, die der Bitleitung BL2 entsprechen) nur entweder das Datenschreibmagnetfeld  $H(EA)$  in der leicht zu magnetisierenden Richtung oder das Datenschreibmagnetfeld  $H(HA)$  in der schwer zu magnetisierenden Richtung jenseits des Schalmagnetfelds  $H_{SW}$ . In diesen Speicherzellen wird die Magnetisierungsrichtung der freien magnetischen Schicht VL nicht überschrieben. Anders ausgedrückt wird theoretisch kein Datenschreibbetrieb durchgeführt.

**[0027]** Wenn jedoch an die oben genannten nicht ausgewählten Speicherzellen eine magnetische Störung jeweils in der anderen Richtung angelegt wird, können Daten fehlerhafterweise in sie geschrieben werden.

**[0028]** Ein typisches Beispiel für eine solche magnetische Störung ist ein Magnetfeld, das durch einen Strom erzeugt wird, der durch eine Spannungsversorgungsleitung und eine Masseleitung fließt, um den peripheren Schaltungen zum Durchführen des Datenlesebetriebs aus dem Speicherfeld und des Datenschreibbetriebs in das Datenfeld eine Betriebsspannung zuzuführen. Der durch die Versorgungsleitung und die Masseleitung fließende Strom erreicht während des Betriebs der peripheren Schaltungen leicht eine Spitze. Daher hat die magnetische Störung von diesen Versorgungsleitungen ei-

nen gewissen Intensitätspegel.

**[0029]** Besonders zur verbesserten Integration können diese Versorgungsleitungen nahe bei dem Speicherfeld bereitgestellt sein, d.h. nahe bei den magnetoresistiven Tunnelementen TMR. In diesem Fall kann die magnetische Störung von der Versorgungsleitung einen verringerten Betriebsspielraum und fehlerhaftes Schreiben bewirken. Daher müssen solche Probleme auf irgendeine Weise verhindert werden.

### Aufgabenstellung

**[0030]** Die Aufgabe der vorliegenden Erfindung besteht darin, durch Unterdrückung der Einflüsse magnetischer Störungen von den für periphere Schaltungen bereitgestellten Versorgungsleitungen und Ähnlichem, insbesondere der magnetischen Störungen von einer Spannungsversorgungsleitung und einer Masseleitung, einen stabilen Betrieb einer magnetischen Dünnfilmspeicherung zu ermöglichen.

**[0031]** Die Aufgabe wird gelöst durch eine magnetische Dünnfilmspeichervorrichtung gemäß Anspruch 1, 7, 8, 9, 11, 12, 17, 18, bzw. 19. Weiterbildungen der Erfindung sind in den Unteransprüchen gekennzeichnet.

**[0032]** Dementsprechend liegt ein Hauptvorteil der vorliegenden Erfindung in Folgendem: da die durch die erste und zweite Versorgungsleitung erzeugten Magnetfelder sich in dem Speicherfeld gegenseitig aufheben, kann ein fehlerhaftes Schreiben und ein verringrigerter Betriebsspielraum, die durch die magnetischen Störungen von den Versorgungsleitungen bewirkt werden, verhindert werden, wodurch ein stabiler Betrieb erreicht wird.

**[0033]** Die magnetischen Störungen von den Versorgungsleitungen können an das Speicherfeld in der leicht zu magnetisierenden Richtung der magnetischen Speicherabschnitte (magnetoresistiven Tunnelemente) angelegt werden. Das unterdrückt die magnetische Störung in der schwer zu magnetisierenden Richtung in der Gruppe nicht ausgewählter Speicherzellen der ausgewählten Spalte, wodurch ein fehlerhaftes Schreiben verhindert wird, dass durch von den Versorgungsleitungen im Datenschreibbetrieb erzeugten magnetischen Störungen bewirkt wird. Auch in einem anderen Betrieb als in dem Datenschreibbetrieb werden keine Störung, die die Magnetisierungsrichtung der magnetischen Speicherabschnitte (der magnetoresistiven Tunnelemente) drehen, an die Speicherzellen angelegt. Das verhindert eine Verringerung des Lesebetriebsspielraums, die durch magnetische Störungen von den Versorgungsleitungen bewirkt wird.

**[0034]** Die magnetische Störung von jeder Versorgungsleitung hat eine Spitzenstärke, die in der am

nächst zu der Versorgungsleitung angeordneten Speicherzelle kleiner ist als ein vorgesehener Wert, und der vorgesehene Wert wird im Hinblick auf die Magnetisierungseigenschaften der Speicherzellen festgelegt. Demzufolge wird die Betriebsstabilität durch magnetische Störungen von den Versorgungsleitungen nicht beeinträchtigt.

**[0035]** Der Entkopplungskondensator, der einen Spitzenstrom empfängt, ist in einem Bereich der Versorgungsleitung bereitgestellt, der nicht ein Bereich nahe dem Speicherfeld ist. Eine solche effiziente Anordnung des Entkopplungskondensators ermöglicht die Unterdrückung von magnetischen Störungen von den Versorgungsleitungen.

**[0036]** Weiterhin verhindern die magnetoresistiven Dummyelemente, die an dem Ende des Speicherfelds bereitgestellt sind, dass das magnetische Feld am Ende des Speicherfelds diskontinuierlich wird. Daher wird der Betriebsspielraum der Speicherzellen, die in dem Endbereich des Speicherfelds angeordnet sind, nicht beeinträchtigt.

**[0037]** Das Induktivitätselement kann unter der Verwendung eines magnetischen Elements ausgebildet sein, das gleichzeitig mit den Speicherzellen in dem Herstellungsprozess für die Speicherzellen hergestellt werden kann. Demzufolge kann das Induktivitätselement hergestellt werden, ohne die Anzahl von Schritten in dem Herstellungsprozess zu vergrößern.

**[0038]** Eine magnetische Störung von der ersten Verdrahtung (die einem Leckmagnetfeld des Schreibmagnetfelds entspricht) und eine magnetische Störung von der zweiten Verdrahtung, die in dem Pfad des Schreibstroms enthalten sind, heben einander in den nicht ausgewählten Speicherzellen gegenseitig auf. Das verringert die magnetischen Störungen in den nicht ausgewählten Speicherzellen und verbessert dadurch die Betriebszuverlässigkeit der magnetischen Dünnfilmspeichervorrichtung.

**[0039]** Wenn die Speicherzellen in eine Mehrzahl von Bänke aufgeteilt sind, die im Datenschreibbetrieb selektiv beschrieben werden (d.h. die Mehrzahl von Bänken wird nicht gleichzeitig für den Datenschreibbetrieb ausgewählt), wird verhindert, dass im Datenschreibbetrieb in dem nicht ausgewählten Speicherzellen fehlerhaftes Schreiben erfolgt. Demzufolge wird die Betriebszuverlässigkeit der magnetischen Dünnfilmspeichervorrichtung verbessert.

**[0040]** Die nicht ausgewählten Speicherzellen, die nahe der ausgewählten Speicherzelle angeordnet sind, unterliegen am ehesten dem fehlerhaften Schreiben von Daten. Daher erstreckt sich eine andere Verdrahtung als die Schreibleitungen, die am nächsten zu den Speicherzellen angeordnet ist, in eine solche Richtung, dass die nächstliegende Ver-

drahtung auf dieser nicht ausgewählten Speicherzellen eine magnetische Störung anlegt, die dieselbe Richtung hat wie die eines relativ großen Restabstands für fehlerhaftes Schreiben. Das verhindert, dass im Datenschreibbetrieb ein fehlerhaftes Schreiben in die nicht ausgewählten Speicherzellen auftritt, wodurch die Betriebszuverlässigkeit der magnetischen Dünnfilmspeichervorrichtung verbessert wird.

**[0041]** Wie oben beschrieben werden die nahe an der ausgewählten Speicherzelle angeordneten nicht ausgewählten Speicherzellen am ehesten einem fehlerhaften Schreiben von Daten unterliegen. Daher erstreckt sich eine Versorgungsleitung, die einen relativ großen Strom empfängt, in eine solche Richtung, XXX.

#### Ausführungsbeispiel

**[0042]** Weitere Merkmale und Zweckmäßigkeitkeiten der Erfindung ergeben sich aus der Beschreibung von Ausführungsbeispielen anhand der beigefügten Zeichnungen. Von den Figuren zeigen:

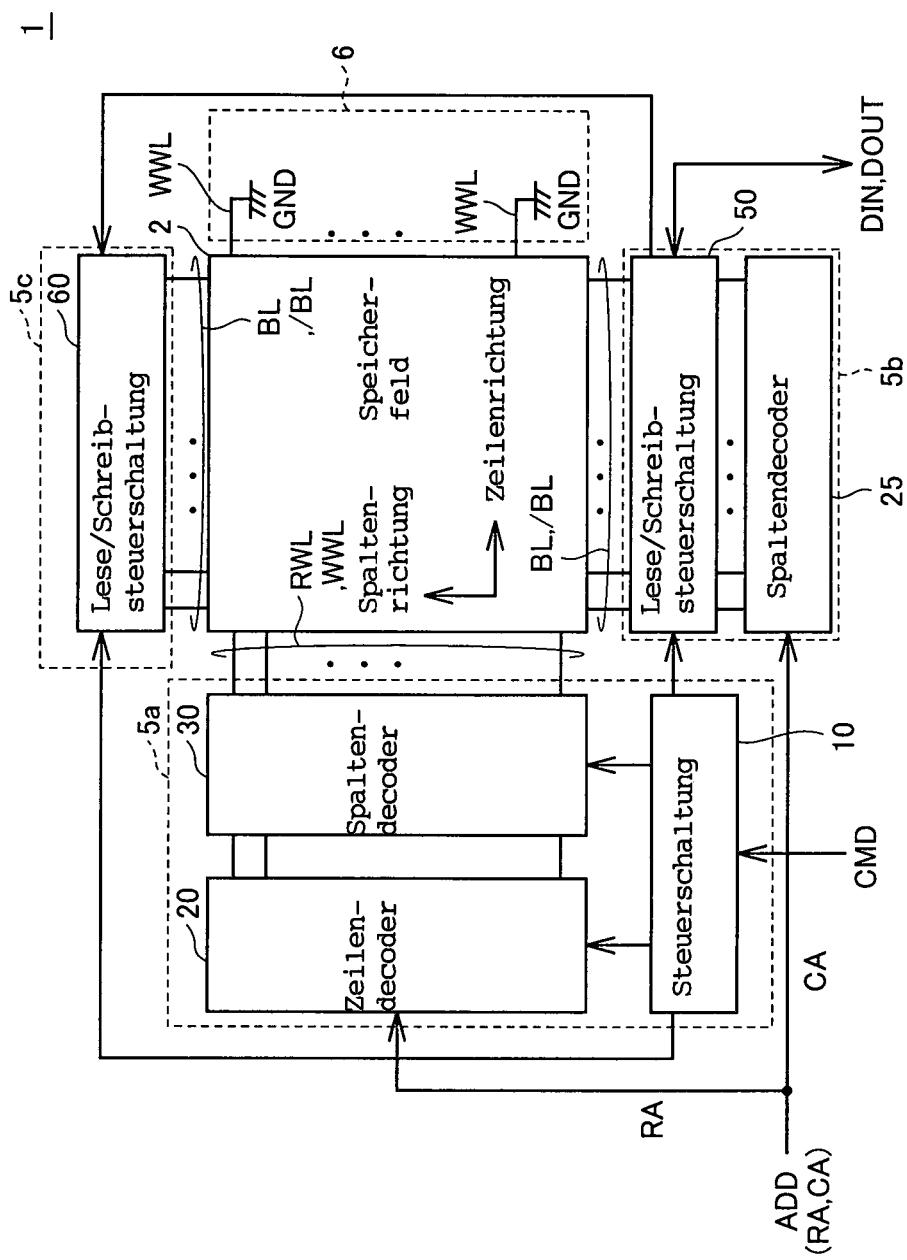

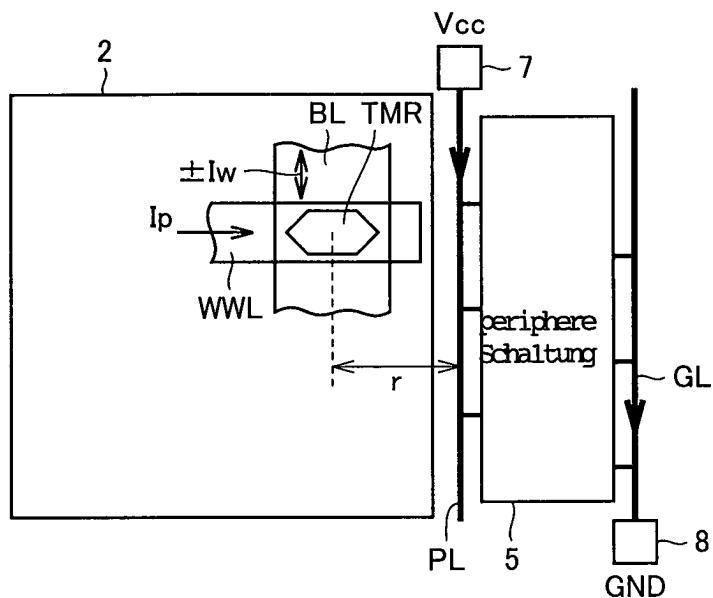

**[0043]** [Fig. 1](#) ein schematisches Blockdiagramm, das den Gesamtaufbau einer MRAM-Vorrichtung nach einer ersten Ausführungsform der vorliegenden Erfindung zeigt;

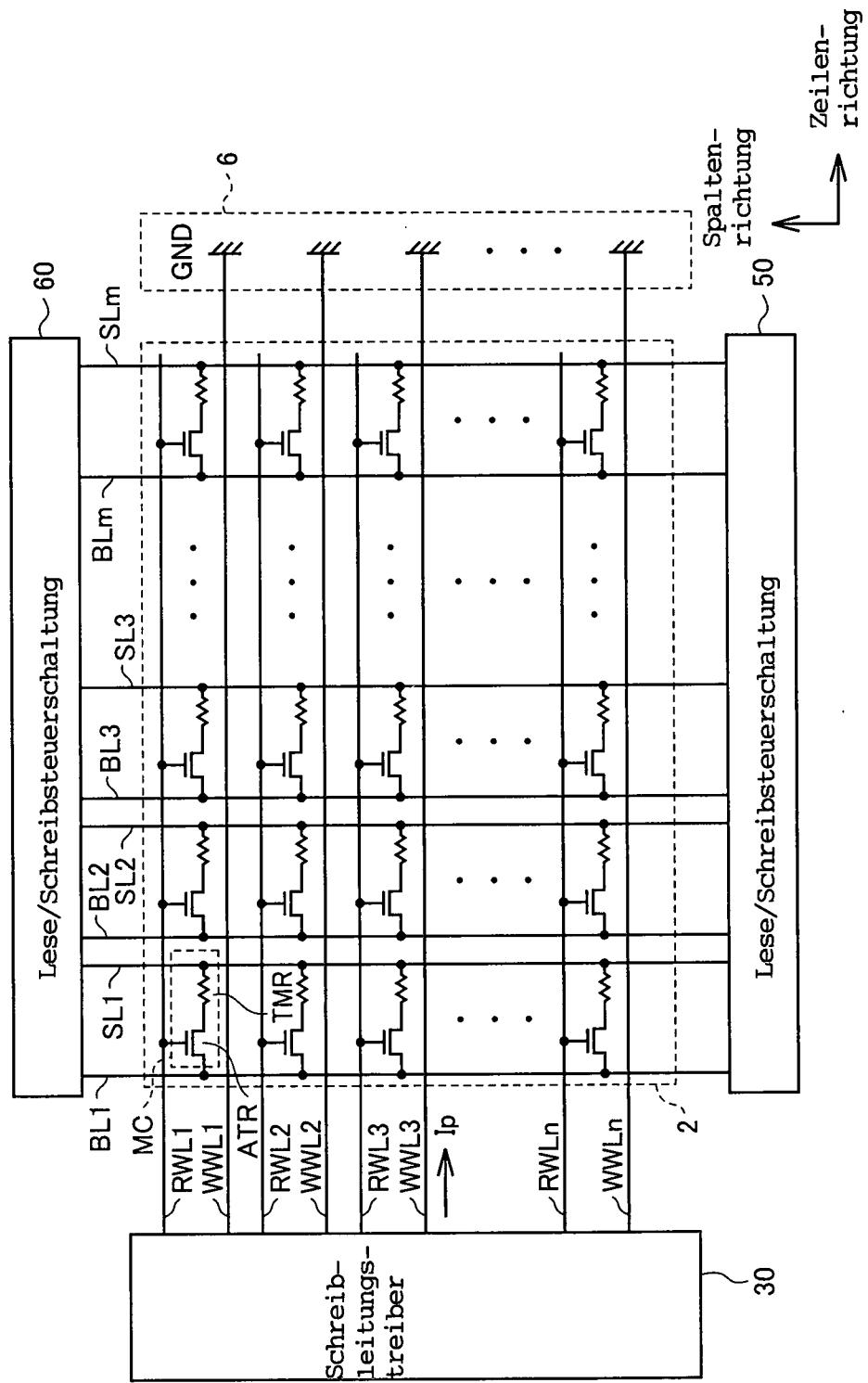

**[0044]** [Fig. 2](#) ein Schaltbild, das ein Beispiel für den Aufbau eines in [Fig. 1](#) dargestellte Speicherfeld zeigt;

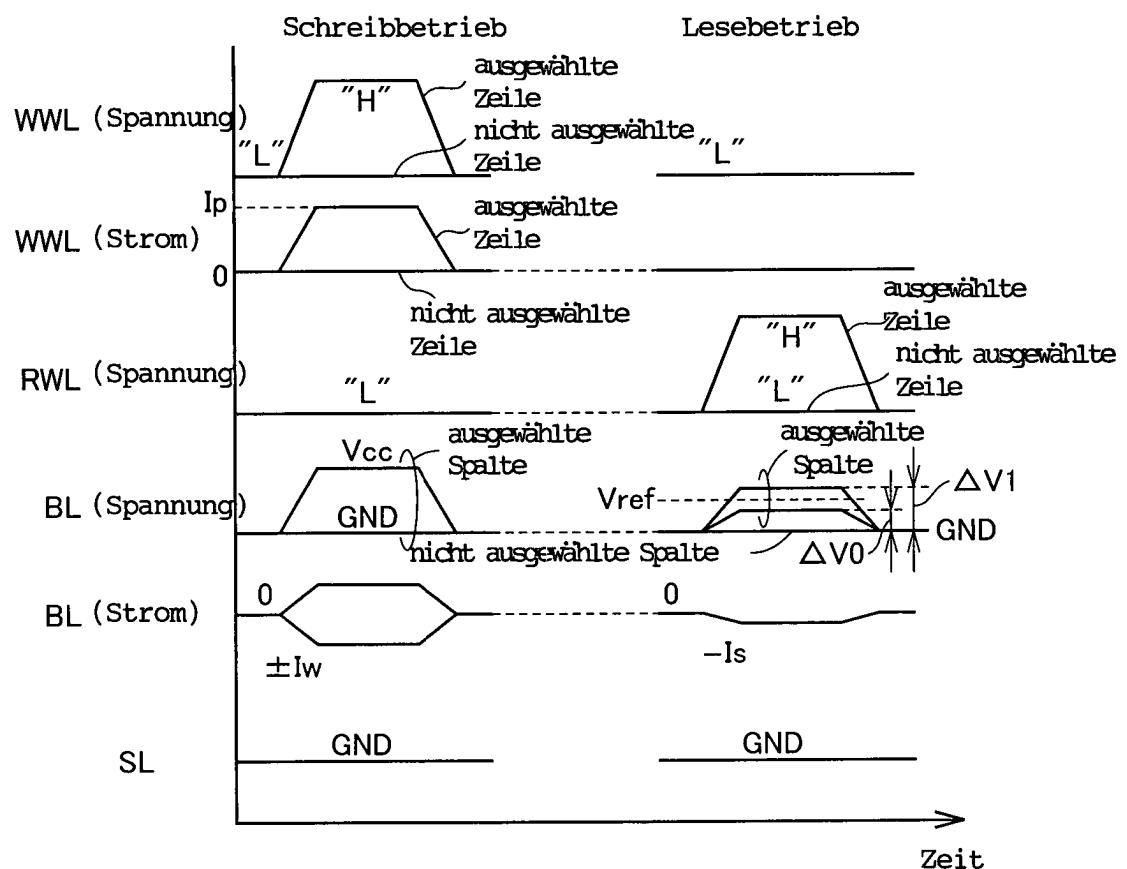

**[0045]** [Fig. 3](#) ein Zeitverlaufsdiagramm, das einen Datenschreibvorgang in die Speicherzelle und einen Datenlesevorgang aus der Speicherzelle veranschaulicht;

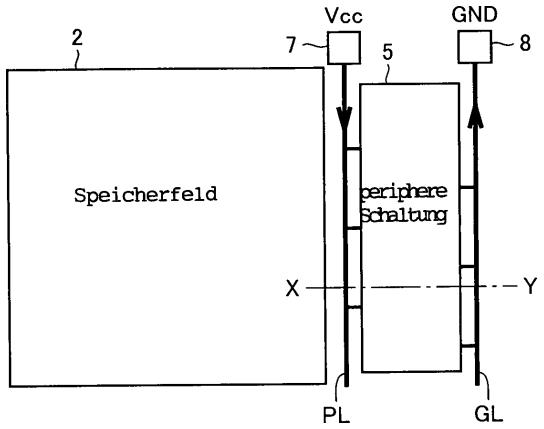

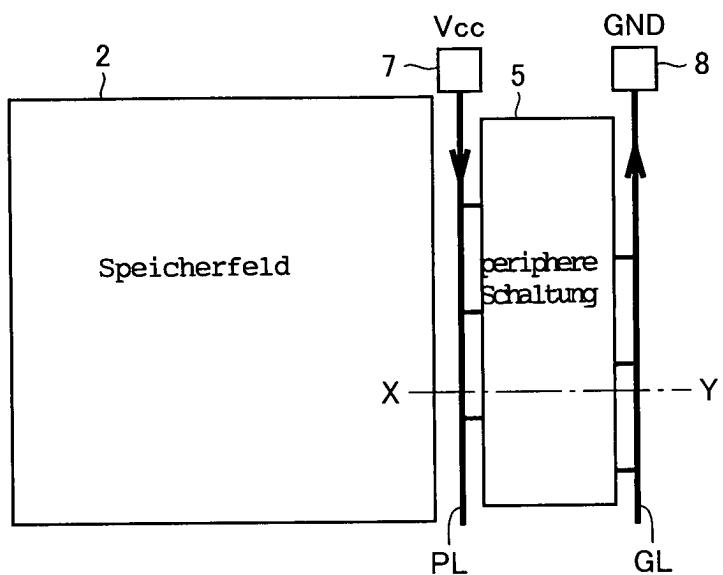

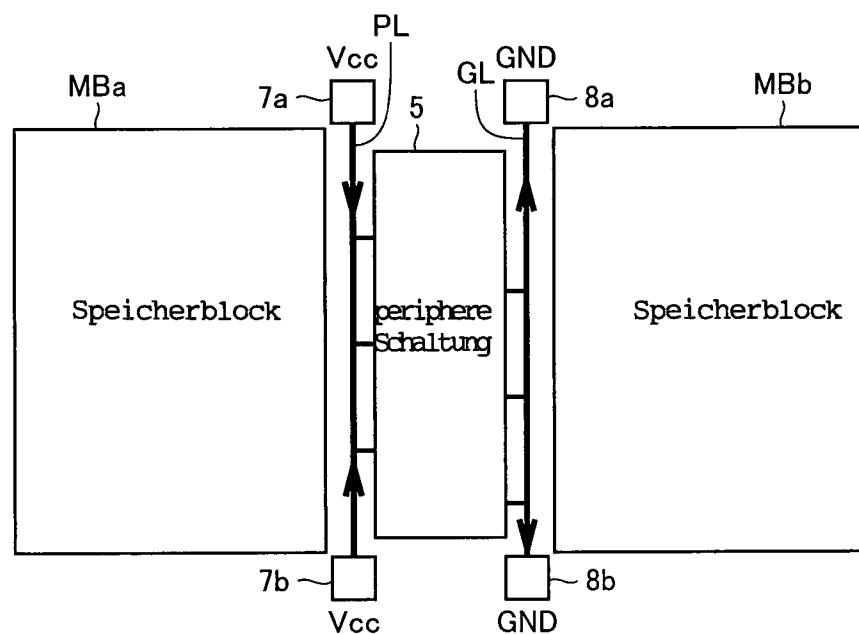

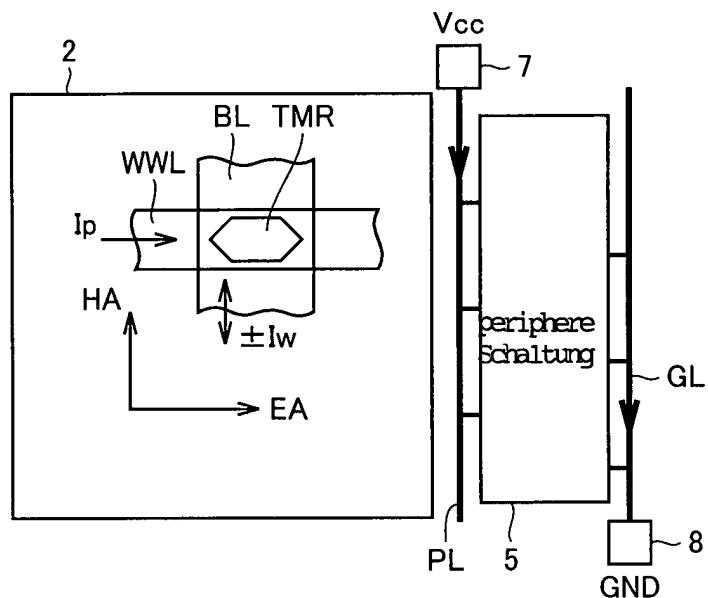

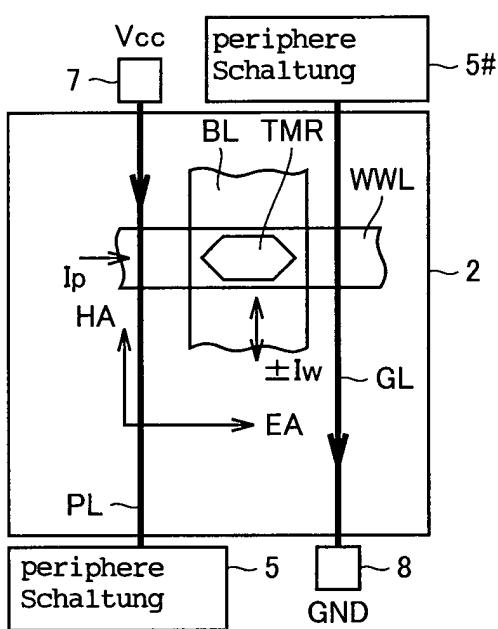

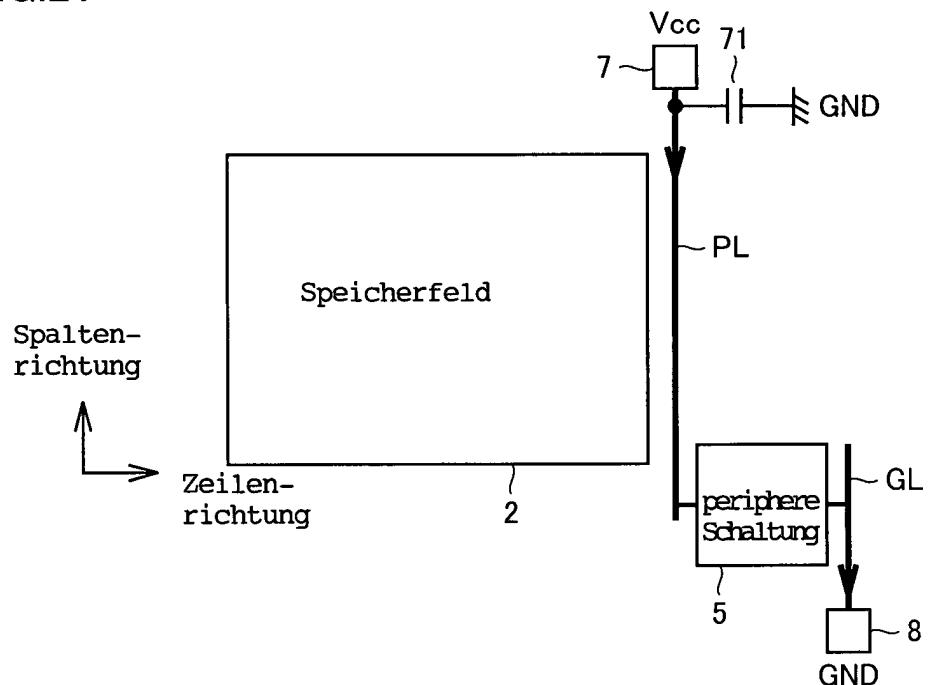

**[0046]** [Fig. 4](#) ein Blockdiagramm, das die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer ersten Ausführungsform der vorliegenden Erfindung zeigt;

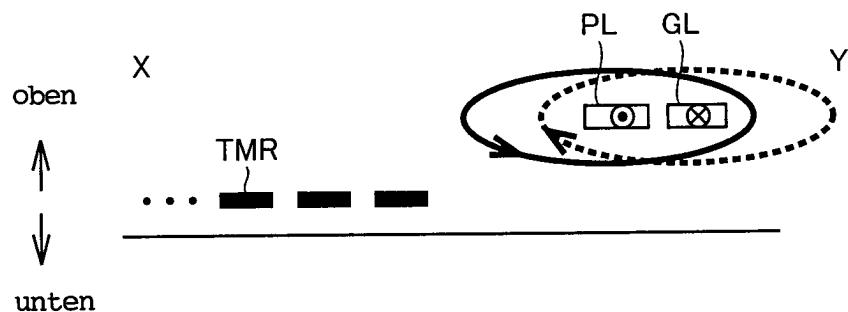

**[0047]** [Fig. 5](#) einen Querschnitt entlang der in [Fig. 4](#) dargestellten Linie X-Y, der ein erstes Beispiel für die Anordnung der Versorgungsleitungen nach der ersten Ausführungsform zeigt;

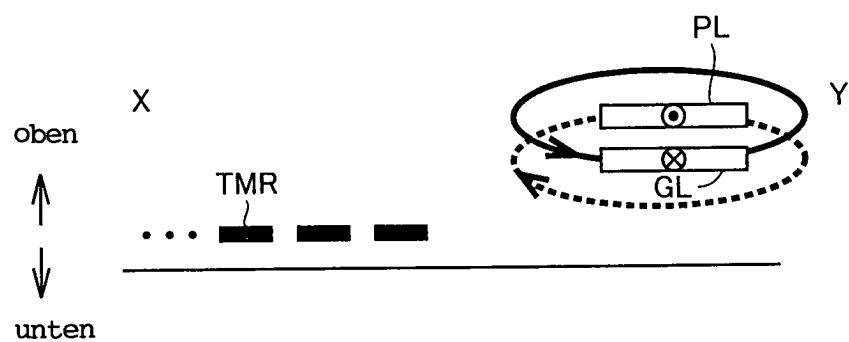

**[0048]** [Fig. 6](#) einen Querschnitt entlang der in [Fig. 4](#) dargestellten Linie X-Y, der ein zweites Beispiel für die Anordnung der Versorgungsleitungen nach der ersten Ausführungsform zeigt;

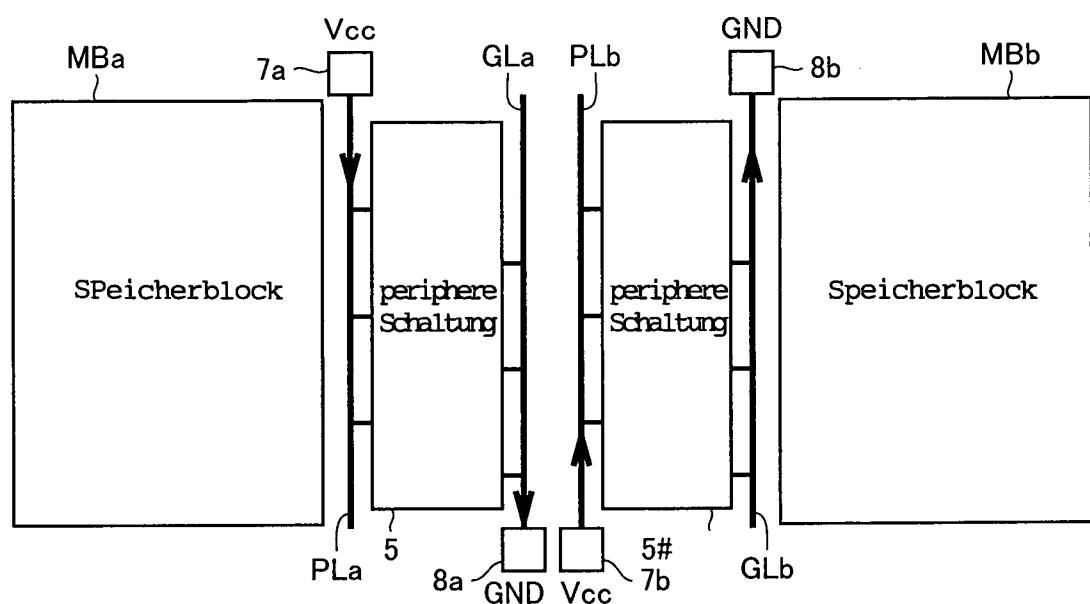

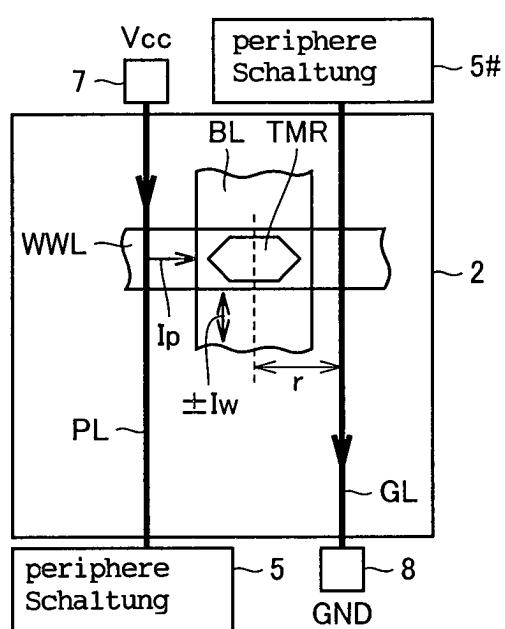

**[0049]** [Fig. 7](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer ersten Abwandlung der ersten Ausführungsform zeigt;

**[0050]** [Fig. 8](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung der Versorgungsleitungen

für periphere Schaltungen nach der ersten Abwandlung der ersten Ausführungsform zeigt;

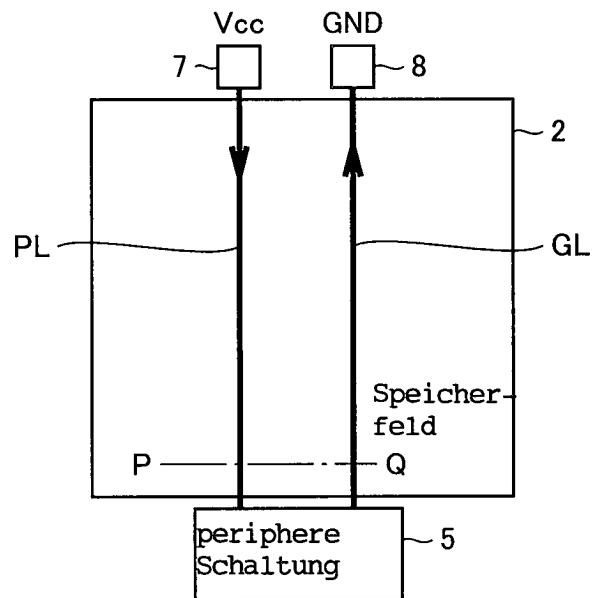

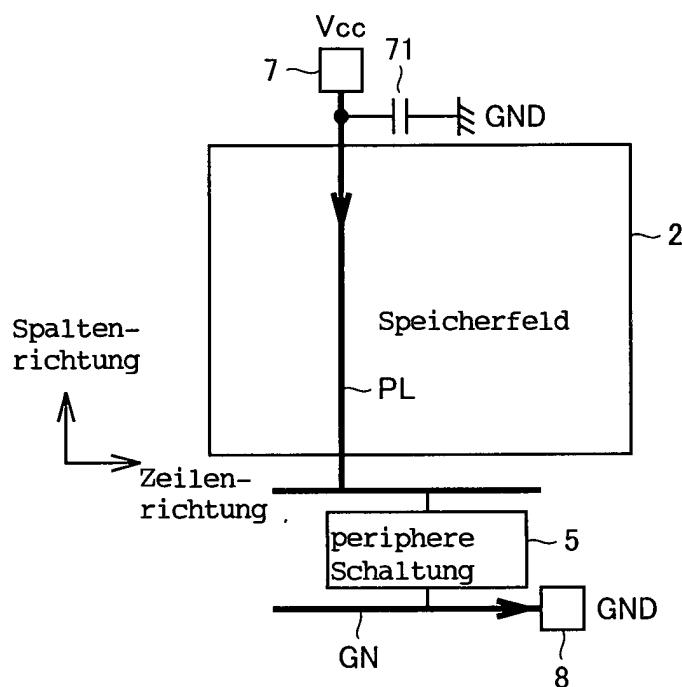

**[0051]** [Fig. 9](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer zweiten Abwandlung der ersten Ausführungsform zeigt;

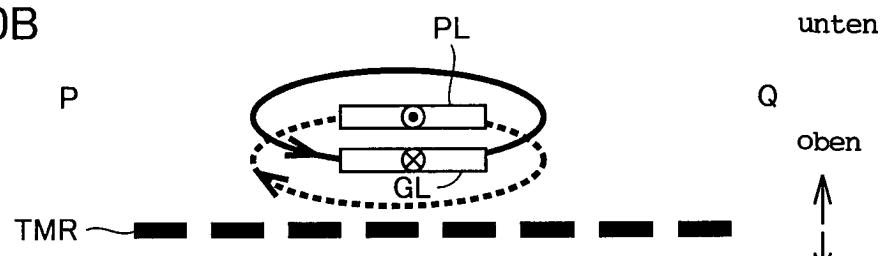

**[0052]** [Fig. 10A-C](#) Querschnitte entlang der in [Fig. 9](#) dargestellten Linie P-Q, die das erste Beispiel für die Anordnung der Versorgungsleitungen nach der zweiten Abwandlung der ersten Ausführungsform zeigen;

**[0053]** [Fig. 11](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer zweiten Abwandlung der ersten Ausführungsform zeigt;

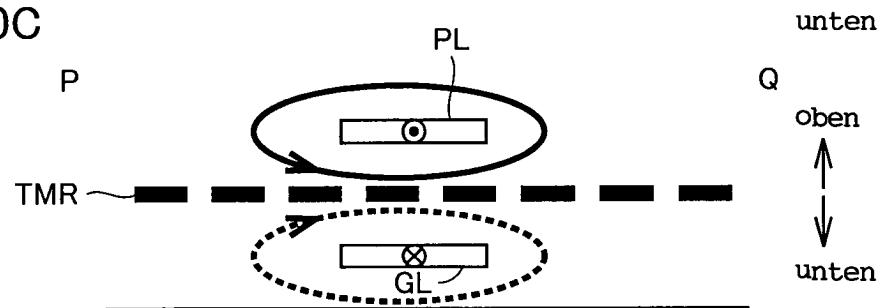

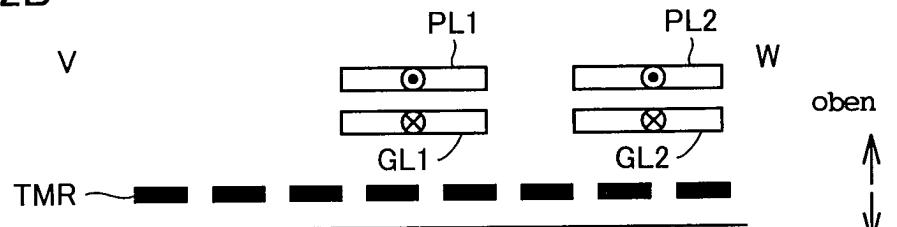

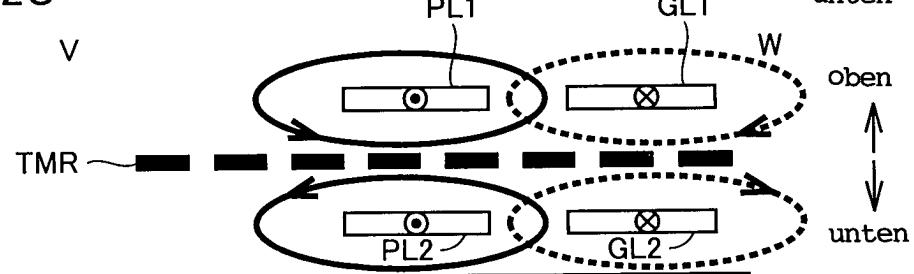

**[0054]** [Fig. 12A-C](#) Querschnitte entlang der in [Fig. 11](#) dargestellten Linie V-W, die das zweite Beispiel für die Anordnung der Versorgungsleitungen nach der zweiten Abwandlung der ersten Ausführungsform zeigen;

**[0055]** [Fig. 13](#) ein Blockdiagramm, das ein Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer dritten Abwandlung der ersten Ausführungsform zeigt;

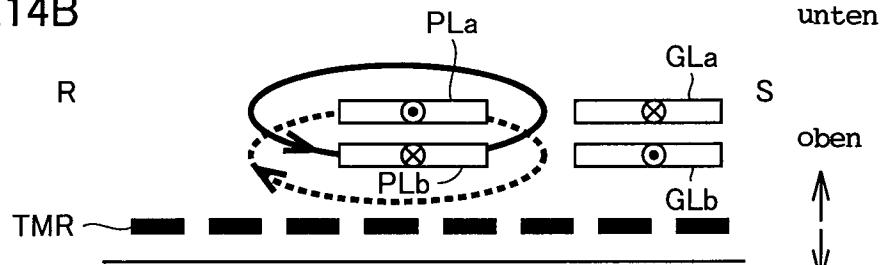

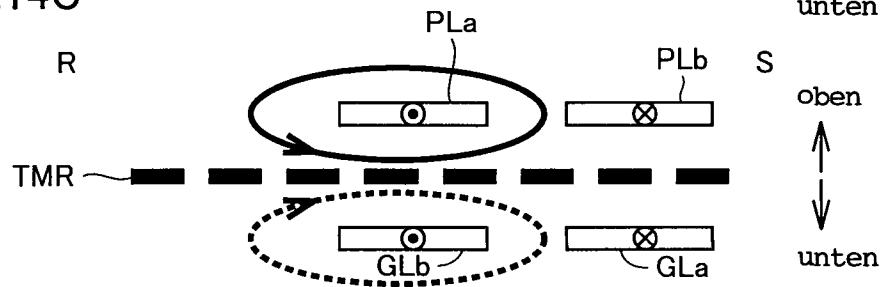

**[0056]** [Fig. 14A-C](#) Querschnitte entlang der in [Fig. 13](#) dargestellten Linie R-S, die das Beispiel für die Anordnung der Versorgungsleitungen nach der dritten Abwandlung der ersten Ausführungsform zeigen;

**[0057]** [Fig. 15](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer zweiten Ausführungsform der vorliegenden Erfindung zeigt;

**[0058]** [Fig. 16](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach der zweiten Ausführungsform zeigt;

**[0059]** [Fig. 17](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer Abwandlung der zweiten Ausführungsform zeigt;

**[0060]** [Fig. 18](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach der Abwandlung der zweiten Ausführungsform zeigt;

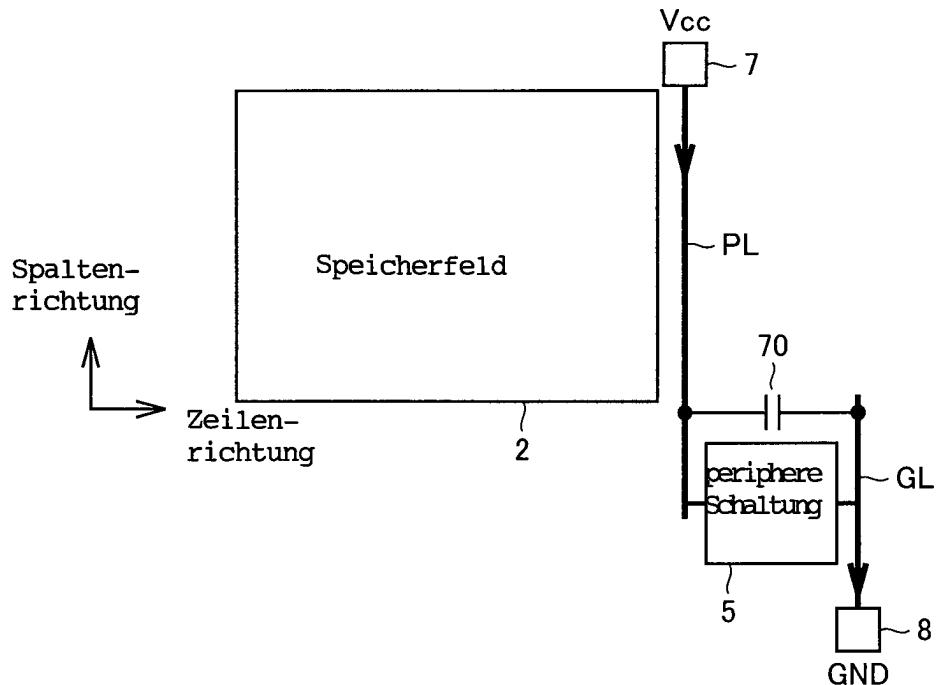

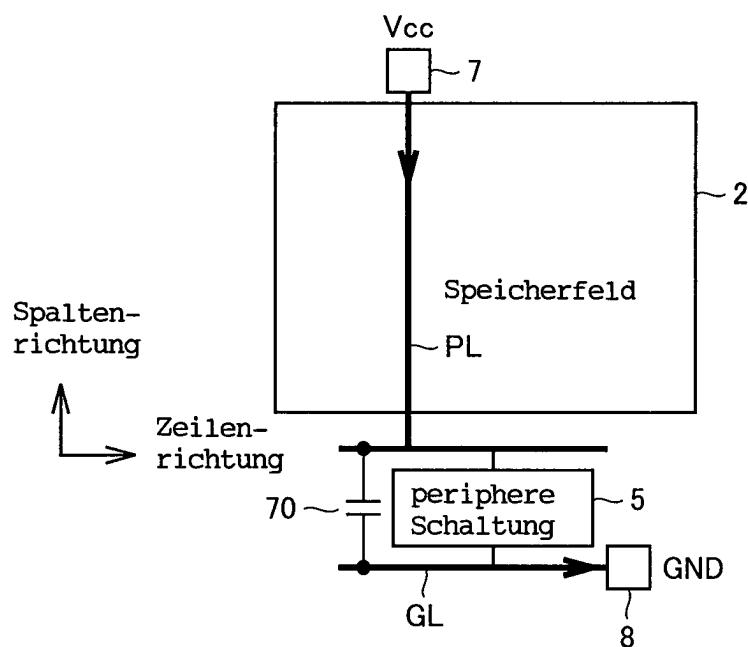

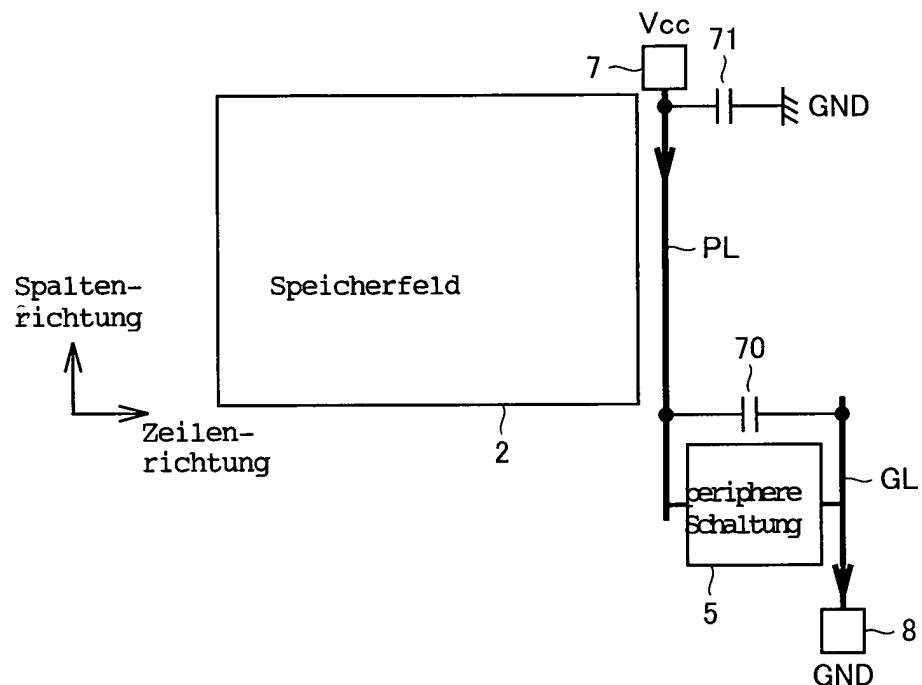

**[0061]** [Fig. 19](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung eines Entkopplungskondensators nach einer dritten Ausführungsform der vorliegenden Erfindung zeigt;

[0062] [Fig. 20](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung des Entkopplungskondensators nach der dritten Ausführungsform zeigt;

[0063] [Fig. 21](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung eines Entkopplungskondensators nach einer ersten Abwandlung der dritten Ausführungsform zeigt;

[0064] [Fig. 22](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung des Entkopplungskondensators nach der ersten Abwandlung der dritten Ausführungsform zeigt;

[0065] [Fig. 23](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung von Entkopplungskondensatoren nach einer zweiten Abwandlung der dritten Ausführungsform zeigt;

[0066] [Fig. 24](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung der Entkopplungskondensatoren nach der zweiten Abwandlung der dritten Ausführungsform zeigt;

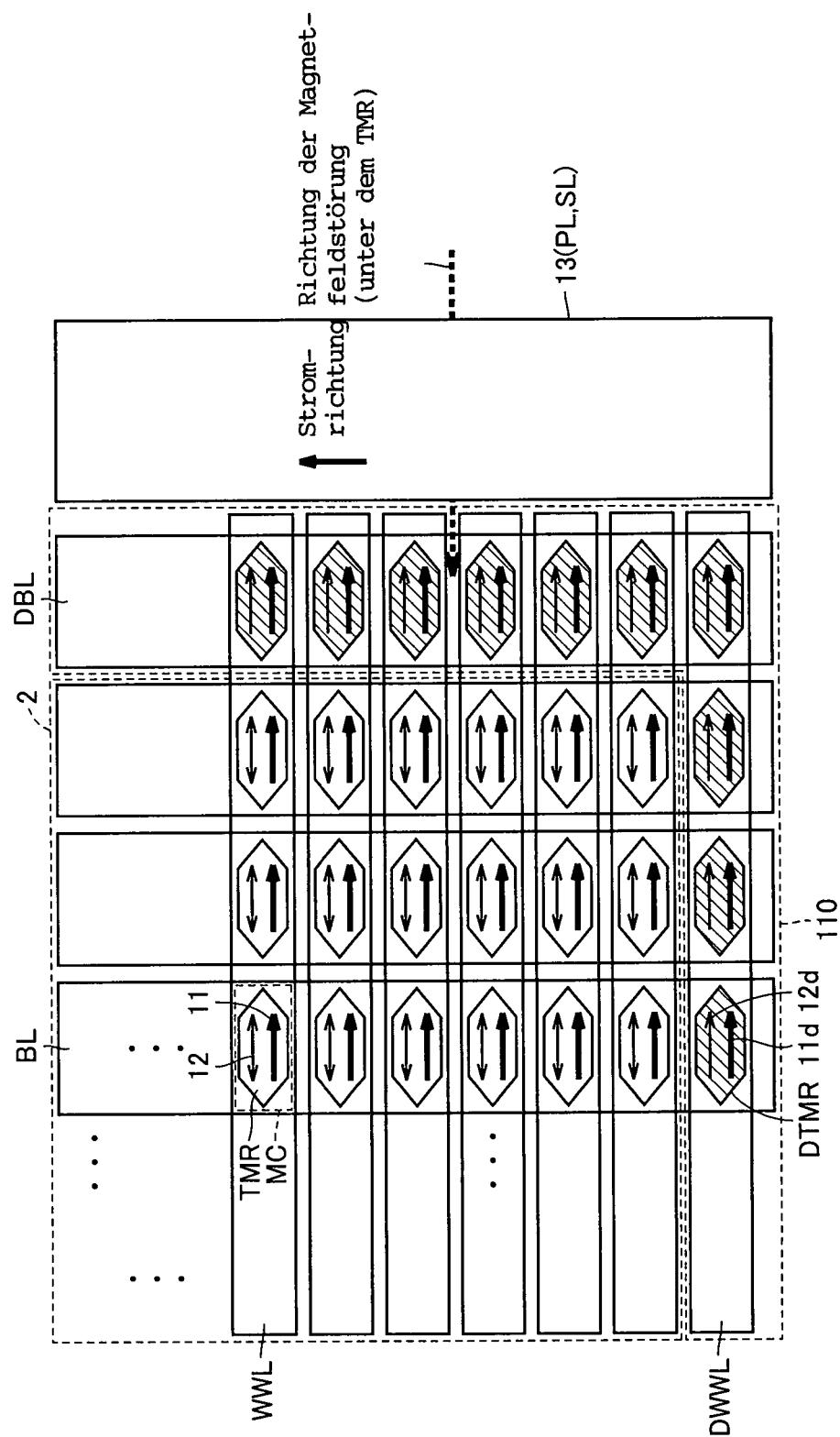

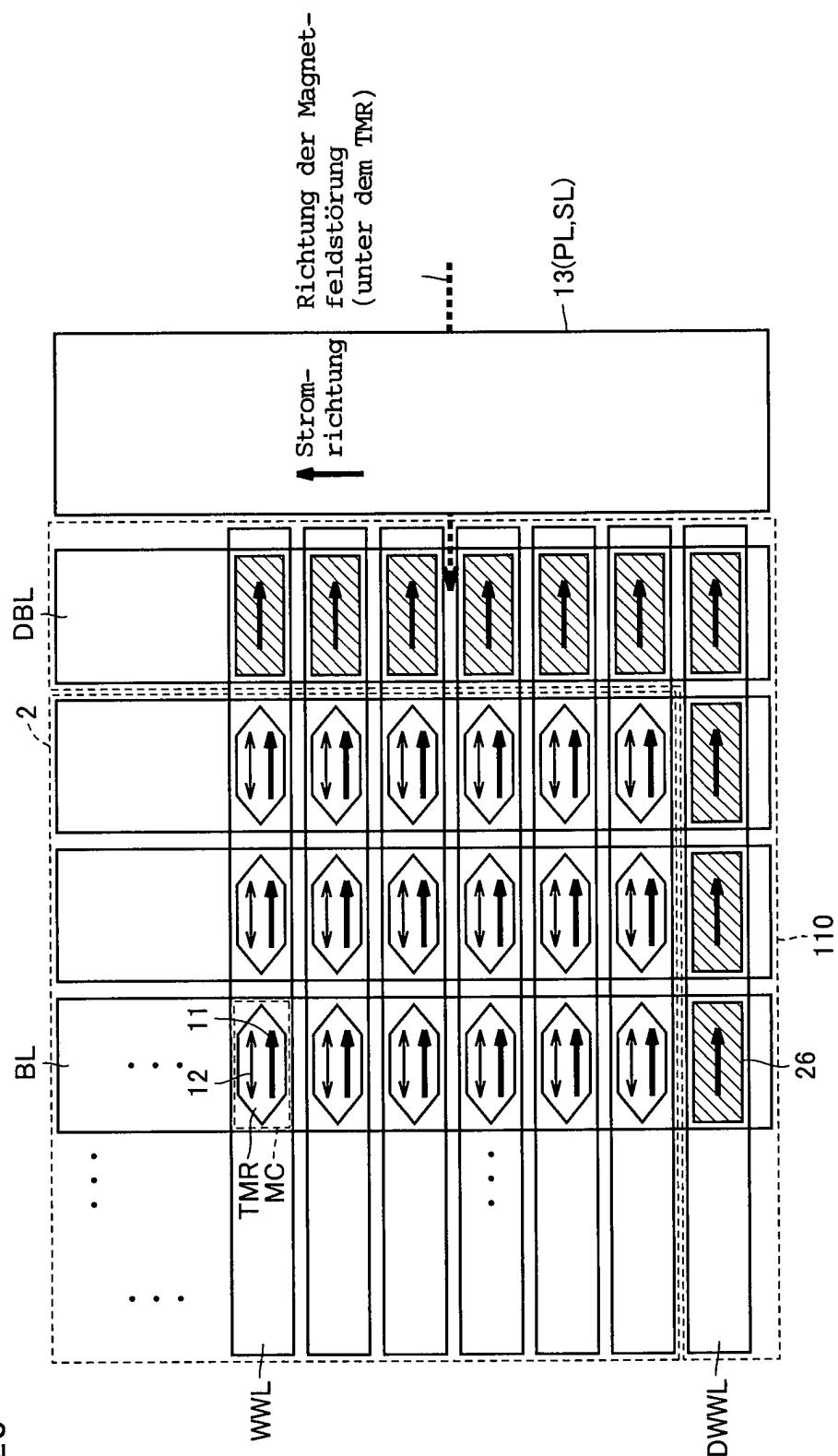

[0067] [Fig. 25](#) eine konzeptionelle Darstellung, die den Aufbau in der Umgebung eines Speicherfelds nach einer vierten Ausführungsform der vorliegenden Erfindung zeigt;

[0068] [Fig. 26](#) eine konzeptionelle Darstellung, die den Aufbau in der Umgebung eines Speicherfelds nach einer Abwandlung der vierten Ausführungsform zeigt;

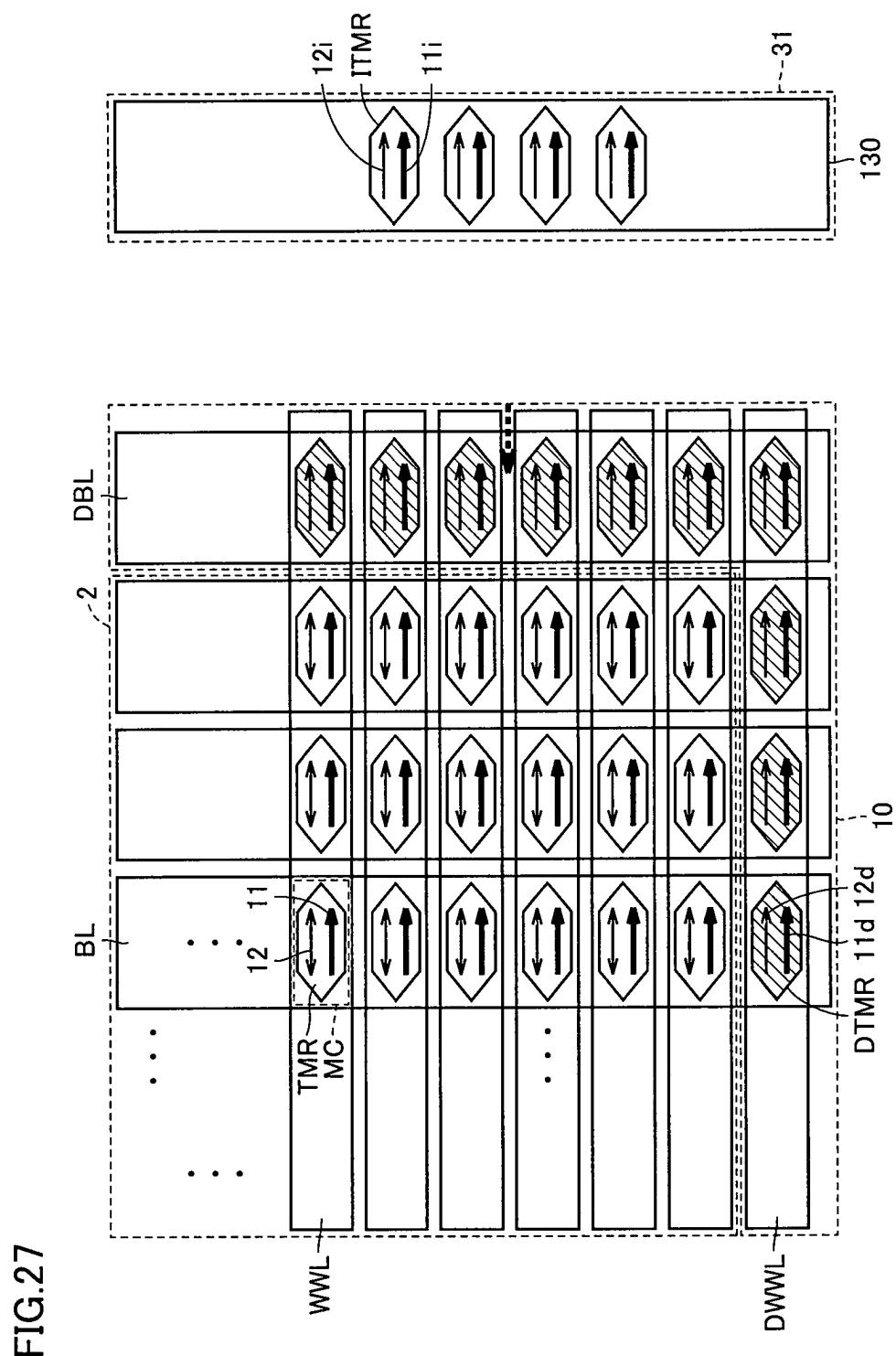

[0069] [Fig. 27](#) eine konzeptionelle Darstellung, die den Aufbau in der Umgebung eines Speicherfelds nach einer fünften Ausführungsform der vorliegenden Erfindung zeigt;

[0070] [Fig. 28](#) einen Querschnitt, der den Aufbau eines in [Fig. 27](#) dargestellten Induktivitätselementes veranschaulicht;

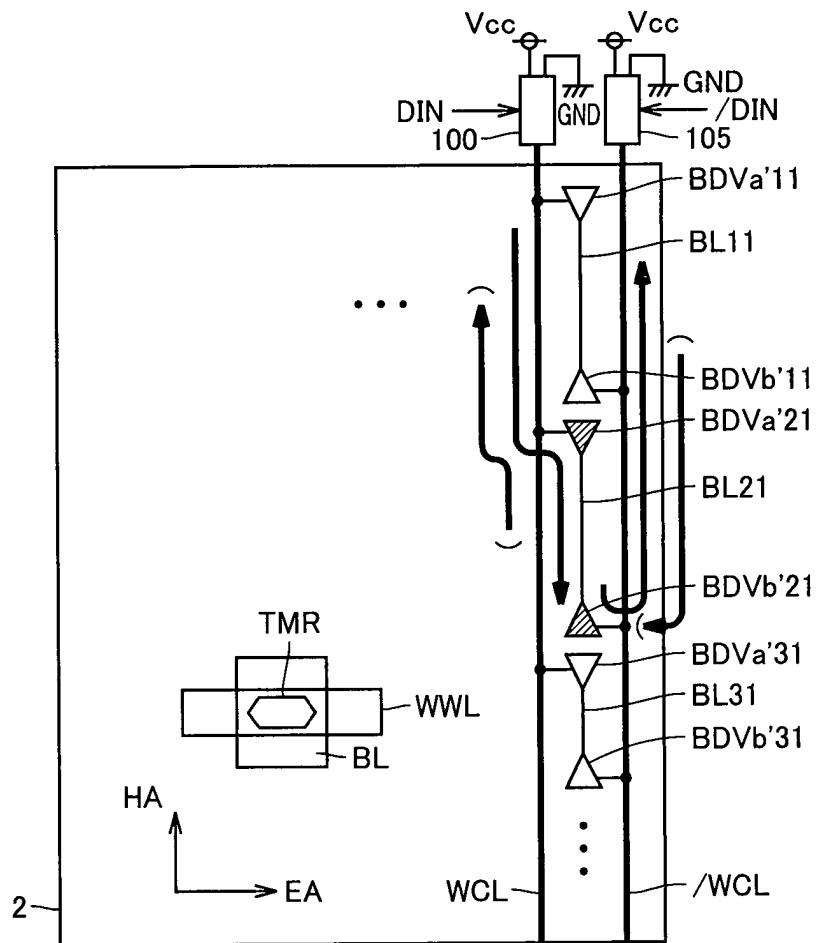

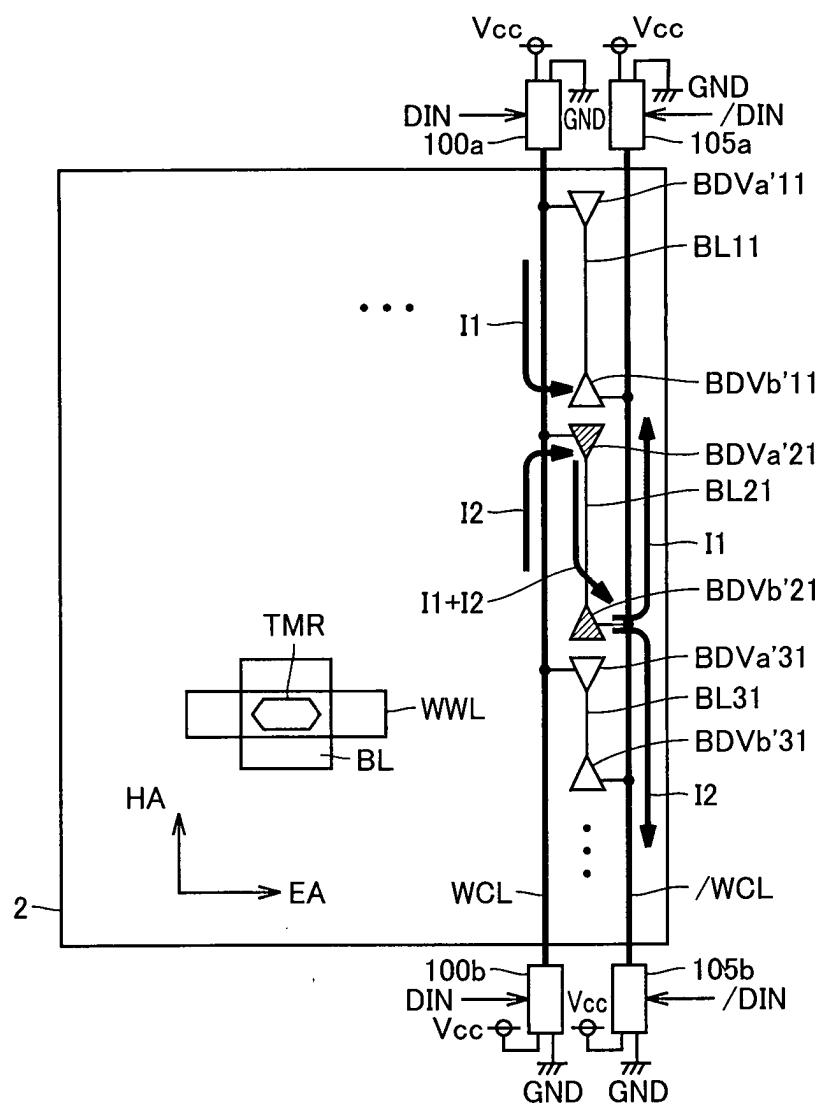

[0071] [Fig. 29](#) eine konzeptionelle Darstellung, die die Anordnung von Bitleitungen und Versorgungsleitungen nach einer sechsten Ausführungsform der vorliegenden Erfindung zeigt;

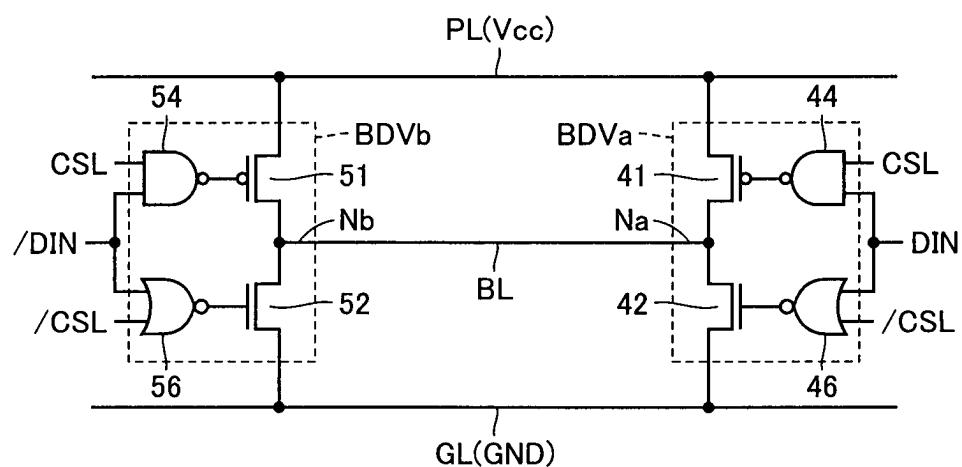

[0072] [Fig. 30](#) ein Schaltbild, das den Aufbau der in [Fig. 29](#) dargestellten Bitleitungstreiber zeigt;

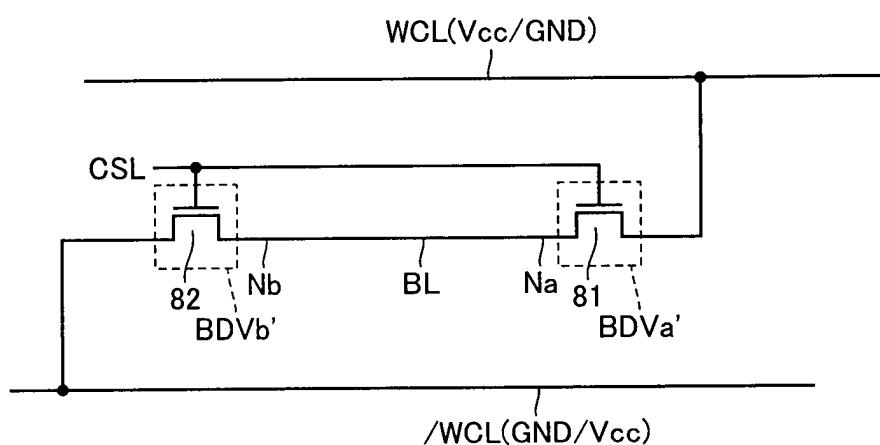

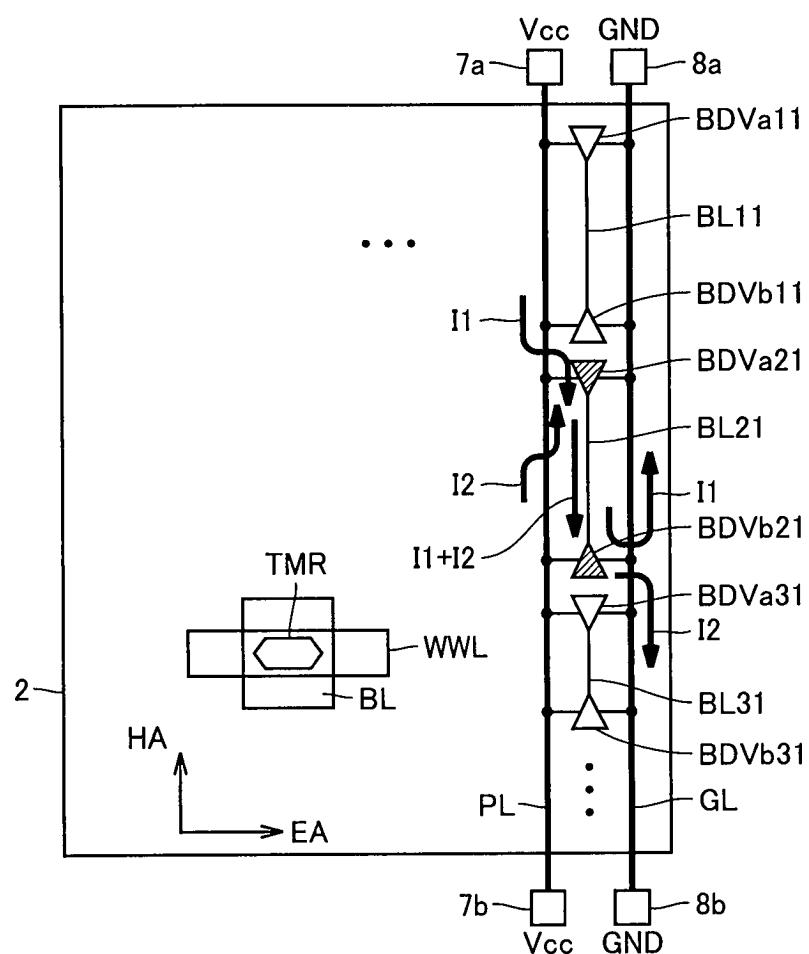

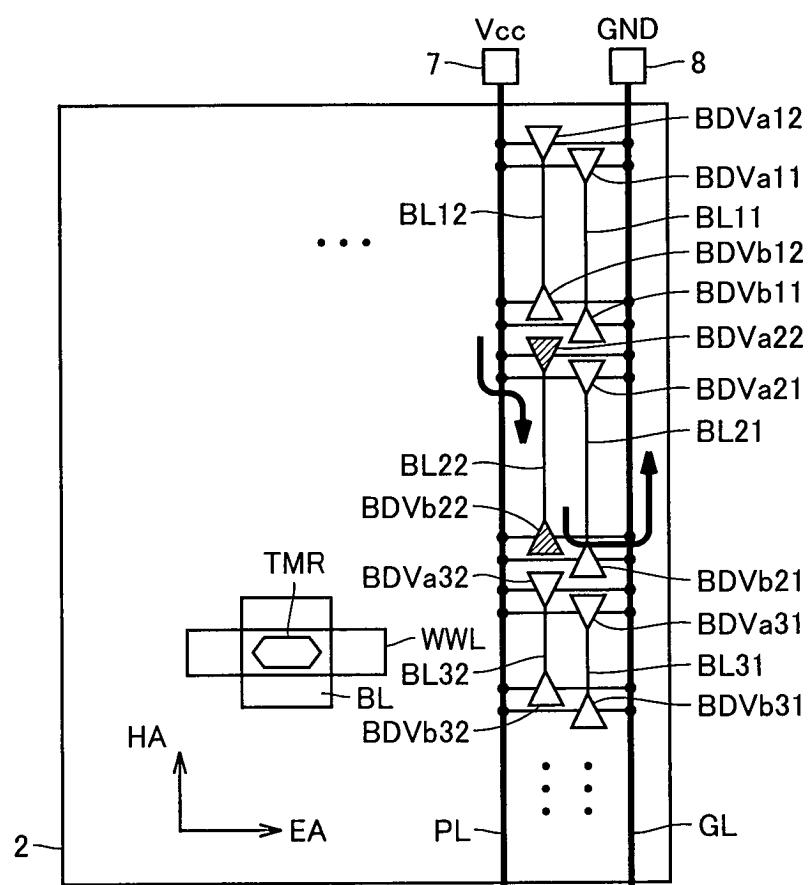

[0073] [Fig. 31](#) eine konzeptionelle Darstellung, die die Anordnung von Bitleitungen und Versorgungsleitungen nach einer ersten Abänderung der sechsten Ausführungsform zeigt;

[0074] [Fig. 32](#) ein Schaltbild, das den Aufbau der in [Fig. 31](#) dargestellten Bitleitungstreiber zeigt;

[0075] [Fig. 33](#) eine konzeptionelle Darstellung, die

die Anordnung von Bitleitungen und Versorgungsleitungen nach einer zweiten Abänderung der sechsten Ausführungsform zeigt;

[0076] [Fig. 34](#) eine konzeptionelle Darstellung, die die Anordnung von Bitleitungen und Versorgungsleitungen nach einer dritten Abänderung der sechsten Ausführungsform zeigt;

[0077] [Fig. 35](#) eine konzeptionelle Darstellung, die die Anordnung von Bitleitungen und Versorgungsleitungen nach einer vierten Abänderung der sechsten Ausführungsform zeigt;

[0078] [Fig. 36](#) ein Blockdiagramm, das ein erstes Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach einer siebten Ausführungsform der vorliegenden Erfindung zeigt;

[0079] [Fig. 37](#) ein Blockdiagramm, das ein zweites Beispiel für die Anordnung der Versorgungsleitungen für periphere Schaltungen nach der siebten Ausführungsform zeigt;

[0080] [Fig. 38](#) eine konzeptionelle Darstellung, die Störungen zeigt, die beständig an die nicht ausgewählten Speicherzellen angelegt sind, und die die Anordnung der Verdrahtungen nach einer achten Ausführungsform der vorliegenden Erfindung veranschaulicht;

[0081] [Fig. 39](#) eine schematische Darstellung des Aufbaus einer MTJ-Speicherzelle;

[0082] [Fig. 40](#) eine konzeptionelle Darstellung, die den Datenlesebetrieb aus der MTJ-Speicherzelle veranschaulicht;

[0083] [Fig. 41](#) eine konzeptionelle Darstellung, die den Datenschreibbetrieb in die MTJ-Speicherzelle veranschaulicht;

[0084] [Fig. 42](#) eine konzeptionelle Darstellung, die den Zusammenhang zwischen einem Datenschreibstrom und der Magnetisierungsrichtung eines magnetoresistiven Tunnellements im Datenschreibbetrieb in die MTJ-Speicherzelle veranschaulicht;

[0085] [Fig. 43](#) eine konzeptionelle Darstellung, die den Feldaufbau der in integrierter Weise in einer Matrix angeordneten MTJ-Speicherzellen zeigt.

[0086] Im Folgenden werden mit Bezug auf die Figuren Ausführungsformen der vorliegenden Erfindung detailliert beschrieben. In den Figuren bezeichnen dabei gleiche Bezugszeichen gleiche oder entsprechende Abschnitte.

[0087] Mit Bezug auf [Fig. 1](#) führt eine MRAM-Vorrichtung 1 gemäß einer Ausführungsform der vorlie-

genden Erfindung entsprechend einem externen Steuersignal CMD und einem externen Adresssignal ADD einen wahlfreien Zugriff durch, um Schreibdaten DIN zu empfangen bzw. Ausgabedaten DOUT auszugeben.

**[0088]** Die MRAM-Vorrichtung 1 beinhaltet ein Speicherfeld 2 mit einer Mehrzahl von MTJ-Speicherzellen, die in einer Matrix angeordnet sind, und peripheren Schaltungen 5a, 5b, 5c zum Durchführen von Lese- und Schreibvorgängen aus dem bzw. in das Speicherfeld 2. Die peripheren Schaltungen 5a, 5b, 5c sind in einem Bereich um das Speicherfeld 2 herum bereitgestellt. Im Folgenden werden die peripheren Schaltungen 5a, 5b, 5c gelegentlich allgemein als "periphere Schaltung 5" oder "periphere Schaltung 5#" bezeichnet.

**[0089]** Eine Mehrzahl von Schreibwortleitungen WWL und eine Mehrzahl von Lesewortleitungen RWL sind entsprechend den MTJ-Speicherzellenzeilen (im Folgenden gelegentlich einfach als "Speicherzellenzeilen" bezeichnet) angeordnet. Eine Mehrzahl von Bitleitungen BL ist entsprechend den MTJ-Speicherzellenspalten (im Folgenden gelegentlich einfach als "Speicherzellenspalten" bezeichnet) angeordnet. Der genaue Aufbau des Speicherfelds wird weiter unten detailliert beschrieben.

**[0090]** Die periphere Schaltung 5 beinhaltet eine Steuerschaltung 10, einen Zeilendecoder 20, einen Spaltendecoder 25, einen Wortleitungstreiber 30 und Lese/Schreibsteuerschaltungen 50 und 60. All diese Elemente sind in dem Bereich um das Speicherfeld 2 herum bereitgestellt. Es sei angemerkt, dass die Anordnung der peripheren Schaltung 5 nicht auf die in [Fig. 1](#) dargestellte Anordnung beschränkt ist.

**[0091]** Die Steuerschaltung 10 steuert den Gesamtbetrieb der MRAM-Vorrichtung 1, um entsprechend dem Steuersignal CMD einen vorgesehenen Vorgang durchzuführen. Der Zeilendecoder 20 wählt entsprechend einer durch das Adresssignal ADD bezeichneten Zeilenadresse RA in dem Speicherfeld 2 eine Zeile aus. Der Spaltendecoder 25 wählt entsprechend einem durch das Adresssignal ADD bezeichneten Spaltenadresse CA in dem Speicherfeld 2 eine Spalte aus.

**[0092]** Der Wortleitungstreiber 30 aktiviert auf der Grundlage des Zeilenauswahlergebnisses des Zeilendecoders 20 eine Lesewortleitung RWL (im Datenlesebetrieb) bzw. eine Schreibwortleitung WWL (im Datenschreibbetrieb). Die Zeilenadresse RA und die Spaltenadresse CA bezeichnen eine MTJ-Speicherzelle, aus der gelesen bzw. in die geschrieben werden soll (im folgenden gelegentlich als "ausgewählte Speicherzelle" bezeichnet).

**[0093]** Die Schreibwortleitungen WWL werden in ei-

nem Bereich 6, der dem Wortleitungstreiber 30 gegenüberliegt, wobei das Speicherfeld 2 dazwischenliegt, mit einer Massespannung GND verbunden. "Lese-/Schreibsteuerschaltung 50, 60" bezieht sich jeweils kollektiv auf eine Gruppe von Schaltungen, die in einem zu dem Speicherfeld 2 benachbarten Bereich bereitgestellt ist, um einer Bitleitung BL der ausgewählten Speicherzellenspalte (im folgenden gelegentlich als "ausgewählte Spalte" bezeichnet) bei den Lese- und Schreibvorgängen einen Datenschreibstrom bzw. einen Datenlesestrom zuzuführen.

**[0094]** Mit Bezug auf [Fig. 2](#) weist das Speicherfeld 2 eine Mehrzahl von MTJ-Speicherzellen MC auf, die in n Zeilen und m Spalten angeordnet sind (wobei n und m natürliche Zahlen sind). Für jede MTJ-Speicherzelle MC sind eine Lesewortleitung RWL, eine Schreibwortleitung WWL, eine Bitleitung BL und eine Referenzspannungsleitung SL bereitgestellt. Die Lesewortleitungen RWL und die Schreibwortleitungen WWL erstrecken sich entsprechend den Speicherzellenzeilen in die Zeilenrichtung. Die Bitleitungen BL und die Referenzspannungsleitungen SL erstrecken sich entsprechend den Speicherzellenspalten in die Spaltenrichtung.

**[0095]** Dementsprechend sind in dem gesamten Speicherfeld 2 Lesewortleitungen RWL1 bis RWLn, Schreibwortleitungen WWL1 bis WWLn, Bitleitungen BL1 bis BLm und Referenzspannungsleitungen SL1 bis SLm bereitgestellt. Im folgenden werden die Lesewortleitungen, Schreibwortleitungen, Bitleitungen und Referenzspannungsleitungen gelegentlich allgemein als RWL, WWL, BL und SL bezeichnet und gelegentlich spezifisch als RWL1, WWL1, BL1, SL1 und Ähnliches. Im Datenschreibbetrieb verbindet der Wortleitungstreiber 30 ein Ende einer Schreibwortleitung WWL der ausgewählten Speicherzellenzeile (im folgenden gelegentlich als "ausgewählte Zeile" bezeichnet) mit einer Versorgungsspannung Vcc. Wie oben beschrieben ist das andere Ende jeder Schreibwortleitung WWL in dem Bereich 6 mit der Massespannung GND verbunden. Dadurch kann der Schreibwortleitung WWL der ausgewählten Zeile in der Richtung von dem Wortleitungstreiber 30 zu dem Bereich 6 hin ein Datenschreibstrom Ip in Zeilenrichtung zugeführt werden. [Fig. 3](#) ist ein Signalverlaufsdiagramm, das den Datenschreibbetrieb in eine MTJ-Speicherzelle und den Datenlesebetrieb aus ihr veranschaulicht.

**[0096]** Zunächst wird der Datenschreibbetrieb beschrieben. Der Wortleitungstreiber 30 verbindet entsprechend dem Zeilenauswahlergebnis des Zeilendecoders 20 eine Schreibwortleitung WWL der ausgewählten Zeile mit der Versorgungsspannung Vcc, um sie auf HIGH-Pegel (im folgenden als "H-Pegel" bezeichnet) zu aktivieren. Die Schreibwortleitungen WWL der nicht ausgewählten Zeilen werden dagegen in inaktivem Zustand gehalten, d.h. auf

"LOW-Pegel" (im folgenden als "L-Pegel" bezeichnet), und ihre Spannung wird daher auf der Masse- spannung GND gehalten.

**[0097]** Somit fließt durch die Schreibwortleitung WWL der ausgewählten Zeile ein Datenschreibstrom  $I_p$  in Zeilenrichtung. Demzufolge wird an jedes magnetoresistive Tunnelement TMR in den MTJ-Speicherzellen der ausgewählten Zeile ein Magnetfeld in der schwer zu magnetisierenden Richtung HA der freien magnetischen Schicht VL angelegt. Durch die Schreibwortleitungen WWL der nicht ausgewählten Zeile fließt kein Strom.

**[0098]** Im Datenschreibbetrieb ist keine Lesewortleitung RWL aktiviert. Anders ausgedrückt werden die Lesewortleitungen RWL in inaktivem Zustand (L-Pegel) gehalten, und die Zugriffstransistoren ATR werden nicht eingeschaltet. Dementsprechend agieren die Referenzspannungsleitungen SL nicht, und ihre Spannung wird auf Massespannung GND gehalten.

**[0099]** Die Lese/Schreibsteuerschaltungen 50 und 60 steuern die Bitleitungsspannungen auf beiden Seiten des Speicherfelds 2 so, dass auf der Bitleitung BL der ausgewählten Spalte ein Datenschreibstrom  $\pm I_w$  mit einer dem Speicherdatenpegel entsprechenden Richtung erzeugt wird.

**[0100]** Zum Schreiben z.B. des Datenwerts "1" legt die Lese/Schreibsteuerschaltung 60 die Bitleitungsspannung auf den Zustand hoher Spannung (H-Pegel: Versorgungsspannung Vcc), und die Lese-/Schreibsteuerschaltung 50 legt die Bitleitungsspannung auf den Zustand niedriger Spannung (L-Pegel: Massespannung GND). Demzufolge fließt durch die Bitleitung BL der ausgewählten Spalte ein Datenschreibstrom  $+I_w$  in der Richtung von der Lese/Schreibsteuerschaltung 60 zu der Lese/Schreibsteuerschaltung 50.

**[0101]** Zum Schreiben des Datenwerts "0" steuern die Lese/Schreibsteuerschaltungen 50 und 60 die Bitleitungsspannungen in entgegengesetzter Weise. Demzufolge fließt durch die Bitleitung BL der ausgewählten Spalte ein Datenschreibstrom  $-I_w$  in der Richtung von der Lese/Schreibsteuerschaltung 50 zu der Lese/Schreibsteuerschaltung 60.

**[0102]** Der durch die Bitleitung BL in Spaltenrichtung fließende Datenschreibstrom  $\pm I_w$  erzeugt ein Datenschreibmagnetfeld. Dieses Datenschreibmagnetfeld wird an das magnetoresistive Tunnelement TMR in der leicht zu magnetisierenden Richtung der freien magnetischen Schicht VL angelegt.

**[0103]** Durch Einstellen der jeweiligen Richtungen der Datenschreibströme  $I_p$  und  $\pm I_w$  kann die freie magnetische Schicht VL in der ausgewählten Spei-

cherzelle in der leicht zu magnetisierenden Achse in der dem Speicherdatenpegel entsprechenden Richtung magnetisiert werden. Es sei angemerkt, dass hier die Richtung des Datenschreibstroms  $\pm I_w$  zum Erzeugen eines Magnetfelds in der leicht zu magnetisierenden Richtung entsprechend dem Datenschreibdatenpegel gesteuert wird und dass die Richtung des Datenschreibstroms  $I_p$  zum Erzeugen eines Magnetfelds in der schwer zu magnetisierenden Richtung unabhängig von dem Schreibdatenpegel fest ist. Das vereinfacht den Aufbau zum Zuführen eines Datenschreibstroms zu der Schreibwortleitung WWL.

**[0104]** Im folgenden wird der Datenlesebetrieb beschrieben.

**[0105]** Im Datenlesebetrieb aktiviert der Wortleitungstreiber 30 entsprechend dem Zeilenauswahlergebnis des Zeilendecoders 20 eine Lesewortleitung RWL der ausgewählten Zeile auf H-Pegel. Die Lesewortleitungen RWL der nicht ausgewählten Zeilen werden in inaktivem Zustand (L-Pegel) gehalten. Im Datenlesebetrieb wird keine Schreibwortleitung WWL aktiviert. Anders ausgedrückt wird jede Schreibwortleitung WWL in inaktivem Zustand (L-Pegel: Massespannung GND) gehalten.

**[0106]** Vor einem Datenlesevorgang werden die Bitleitungen BL z.B. auf Massespannung GND vorgeladen. Wenn der Datenlesevorgang begonnen wird, wird eine Lesewortleitung RWL der ausgewählten Zeile auf H-Pegel aktiviert, und der entsprechende Zugriffstransistor ATR wird eingeschaltet. In den diesen Zugriffstransistoren ATR entsprechenden MTJ-Speicherzellen werden jeweils die magnetoresistiven Tunnelemente TMR elektrisch zwischen einer Referenzspannung (Massespannung GND) und einer entsprechenden Bitleitung BL geschaltet.

**[0107]** Wenn zum Beispiel eine Bitleitung der ausgewählten Spalte auf die Versorgungsspannung Vcc hochgezogen wird, wird nur dem magnetoresistiven Tunnelement TMR der ausgewählten Speicherzelle ein Lesestrom  $I_s$  zugeführt. Demzufolge unterliegt die Bitleitung BL der ausgewählten Spalte entsprechend dem elektrischen Widerstandswert des magnetoresistiven Tunnelements TMR in der ausgewählten Speicherzelle, d.h. entsprechend dem Speicherdatenpegel der ausgewählten Speicherzelle, einer Spannungsänderung.

**[0108]** Es wird nun angenommen, dass  $\Delta V_0$  und  $\Delta V_1$  jeweils eine Spannungsänderung auf der Bitleitung BL der ausgewählten Spalte bezeichnen, wenn die ausgewählte Speicherzelle den Datenwert "0" bzw. "1" speichert. Der Speicherdatenwert der ausgewählten Speicherzelle wird gelesen, indem die Differenz zwischen der Spannung auf der Bitleitung BL der ausgewählten Speicherzelle und einer Referenz-

spannung Vref erfasst und verstärkt wird. Die Referenzspannung Vref hat einen Wert zwischen  $\Delta V_0$  und  $\Delta V_1$ .

**[0109]** Der Spannungspegel der Referenzspannungsleitungen SL wird sowohl im Lese- als auch im Schreibbetrieb auf Massespannung GND gelegt. Dementsprechend braucht nur die Referenzspannungsleitung SL mit einem Knoten verbunden zu werden, um die Massespannung GND z.B. einem Bereich in den Lese/Schreibsteuerschaltungen **50** oder **60** zuzuführen. Die Referenzspannungsleitung SL kann sich entweder in die Zeilenrichtung oder in die Spaltenrichtung erstrecken.

**[0110]** Es sei angemerkt, dass sich die vorliegende Erfindung wie aus der folgenden Beschreibung ersichtlich auf die Anordnung von Versorgungsleitungen zum Zuführen einer Betriebsspannung zu der peripheren Schaltung des Speicherfelds **2** bezieht. Auch wenn [Fig. 2](#) einen einfachen Speicherfeldaufbau zeigt, kann die vorliegende Erfindung ungeachtet der Anordnung der MTJ-Speicherzellen und Signalleitungen (wie z.B. der Bitleitungen BL) in dem Speicherfeld **2** verwendet werden. Die vorliegende Erfindung kann zum Beispiel auf ein Speicherfeld angewendet werden, das eine offene Bitleitungsstruktur oder eine gefaltete Bitleitungsstruktur aufweist.

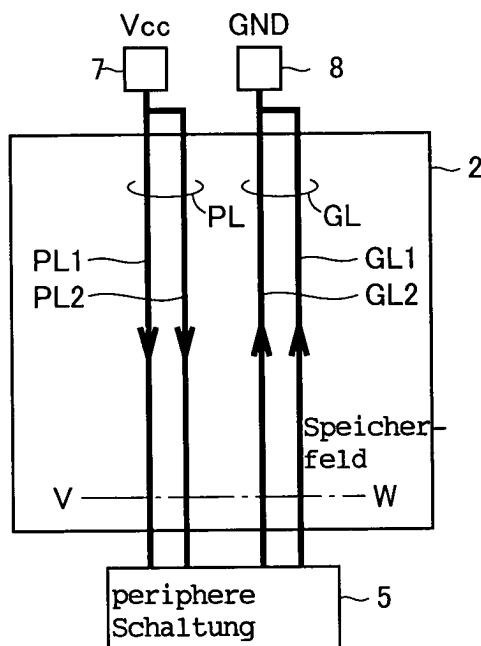

**[0111]** [Fig. 4](#) ist ein Blockdiagramm, das die Anordnung der Versorgungsleitungen für die periphere Schaltung nach einer ersten Ausführungsform veranschaulicht. In [Fig. 4](#) entspricht die periphere Schaltung **5** jeder der in [Fig. 1](#) dargestellten peripheren Schaltungen **5a**, **5b** und **5c**. Wie in [Fig. 4](#) dargestellt, werden die Betriebsspannungen der peripheren Schaltung **5**, d.h. die Versorgungsspannung Vcc und die Massespannung GND über eine Versorgungsspannungsleitung PL und eine Masseleitung GL zugeführt. Im folgenden werden die Versorgungsspannungsleitung PL und die Masseleitung GL gelegentlich allgemein als "Versorgungsleitungen" bezeichnet.

**[0112]** Die Versorgungsspannungsleitung PL ist mit einem Versorgungsknoten **7** verbunden, um die Versorgungsspannung Vcc von außen zu empfangen, und führt der peripheren Schaltung **5** die Versorgungsspannung Vcc zu. In ähnlicher Weise ist die Masseleitung GL mit einem Masseknoten **8** verbunden, um die Massespannung GND von außen zu empfangen, und führt der peripheren Schaltung **5** die Massespannung GND zu. Diese Versorgungsleitungen sind so angeordnet, dass die Magnetfelder, die jeweils durch den in der Versorgungsspannungsleitung PL und in der Masseleitung GL fließenden Strom erzeugt werden, einander in dem Speicherfeld **2** gegenseitig aufheben.

**[0113]** Bei dem in [Fig. 4](#) dargestellten Beispiel er-

strecken sich die Versorgungsspannungsleitung PL und die Masseleitung GL in dem Bereich nahe der peripheren Schaltung **5** in dieselbe Richtung. Darüber hinaus sind der Versorgungsknoten **7** und der Masseknoten **8** so bereitgestellt, dass die Ströme durch die Versorgungsspannungsleitung PL und die Masseleitung GL in entgegengesetzte Richtungen fließen.

**[0114]** [Fig. 5](#) und [Fig. 6](#) sind Querschnitte entlang der in [Fig. 4](#) dargestellten Linie X-Y. [Fig. 5](#) und [Fig. 6](#) zeigen ein erstes und ein zweites Anordnungsbeispiel für die Versorgungsleitungen nach der ersten Ausführungsform.

**[0115]** Wie in [Fig. 5](#) dargestellt, sind die Versorgungsspannungsleitung PL und die Masseleitung GL in dem ersten Anordnungsbeispiel der ersten Ausführungsform in einem Bereich nahe dem Speicherfeld **2** bereitgestellt. Die Versorgungsspannungsleitung PL und die Masseleitung GL sind beide in einer Metallverdrahtungslage ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnellemente TMR angeordnet ist. In [Fig. 5](#) sind die Versorgungsspannungsleitung PL und die Masseleitung GL in der Lage angeordnet, die oberhalb des magnetoresistiven Tunnellements TMR angeordnet ist. Diese Versorgungsleitungen können jedoch alternativ auch in einer Lage bereitgestellt sein, die unterhalb des magnetoresistiven Tunnellements TMR angeordnet ist.

**[0116]** Mit diesem Aufbau heben sich das durch den in der Versorgungsspannungsleitung PL fließenden Strom erzeugte Magnetfeld (in [Fig. 5](#) durch eine durchgezogene Linie dargestellt) und das durch den in der Masseleitung GL fließenden Strom erzeugte Magnetfeld (in [Fig. 5](#) durch eine gestrichelte Linie dargestellt) in dem Speicherfeld **2**, d.h. in den magnetoresistiven Tunnellementen TMR, gegenseitig auf.

**[0117]** Auf diesen Versorgungsleitungen wird besonders beim Einschalten oder während des Schaltungsbetriebs eine (Schalt-)Stromspitze erzeugt. Je doch auch die magnetischen Störungen, die durch die Stromspitze auf die Versorgungsleitungen erzeugt werden, heben sich in dem Speicherfeld **2** gegenseitig auf. Daher kann die MRAM-Vorrichtung stabil betrieben werden, wobei ein fehlerhaftes Schreiben in die MTJ-Speicherzellen verhindert wird.

**[0118]** Darüber hinaus können Metallverdrahtungen, die in derselben Metallverdrahtungslage ausgebildet sind, als Versorgungsspannungsleitung PL und Masseleitung GL verwendet werden. Das verringert die Anzahl der für die MRAM-Vorrichtung erforderlichen Metallverdrahtungslagen und trägt dadurch zu einer Vereinfachung des Herstellungsvorgangs bei.

**[0119]** Wie in [Fig. 6](#) dargestellt, sind bei dem zwei-

ten Anordnungsbeispiel der ersten Ausführungsform die Versorgungsspannungsleitung PL und die Masseleitung GL in verschiedenen Verdrahtungslagen ausgebildet, die entweder oberhalb oder unterhalb des magnetoresistiven Tunnellements TMR angeordnet sind. Die Versorgungsspannungsleitung PL und die Masseleitung GL überlappen ineinander in vertikaler Richtung.

**[0120]** Dieser Aufbau verringert weiterhin die Differenz zwischen dem Abstand von der Versorgungsspannungsleitung PL zu dem Speicherfeld 2 und dem Abstand von der Masseleitung GL zu dem Speicherfeld 2. Demzufolge heben sich die magnetischen Störungen von den Versorgungsleitungen in dem Speicherfeld 2 in größerem Maße gegenseitig auf. Dementsprechend kann im Vergleich zu der in [Fig. 5](#) dargestellten Anordnung ein Betriebsspielraum effizienter sichergestellt und ein fehlerhafter Betrieb effizienter verhindert werden.

**[0121]** Bei einer ersten Abwandlung der ersten Ausführungsform ist das Speicherfeld in eine Mehrzahl von Speicherblöcken aufgeteilt, und die peripheren Schaltungen sind entsprechend den Speicherblöcken bereitgestellt. Für diesen Aufbau wird die Anordnung der Versorgungsleitungen beschrieben.

**[0122]** [Fig. 7](#) und [Fig. 8](#) sind Blockdiagramme, die jeweils ein erstes bzw. zweites Anordnungsbeispiel für die Versorgungsleitungen der peripheren Schaltungen nach der ersten Abwandlung der ersten Ausführungsform zeigen.

**[0123]** Wie in [Fig. 7](#) dargestellt, ist das in [Fig. 1](#) dargestellte Speicherfeld 2 z.B. in zwei Speicherblöcke MBa und MBb aufgeteilt. In dem ersten Anordnungsbeispiel ist die von den Speicherblöcken MBa und MBb gemeinsam genutzte periphere Schaltung 5 an der Grenze zwischen den Speicherblöcken MBa und MBb bereitgestellt. Wie bei der ersten Ausführungsform werden der peripheren Schaltung 5 über die Versorgungsspannungsleitung PL und die Masseleitung GL die Versorgungsspannung Vcc und die Massespennung GND zugeführt. An beiden Enden der Versorgungsspannungsleitung PL sind Versorgungsknoten 7a und 7b bereitgestellt, und an beiden Seiten der Masseleitung GL sind Masseknoten 8a und 8b bereitgestellt. Die besondere Anordnung der Versorgungsspannungsleitung PL und der Masseleitung GL ist dieselbe wie in [Fig. 5](#) und [Fig. 6](#) dargestellt.

**[0124]** Mit dem obigen Aufbau fließt über die jeweiligen Strompfade auf der Versorgungsspannungsleitung PL und der Masseleitung GL ein Strom zum Zuführen der Versorgungsspannung Vcc und der Massespennung GND zu jedem Teil der peripheren Schaltung 5. Die von den durch die Strompfade fließenden Strömen erzeugten Magnetfelder heben sich gegenseitig in dem Speicherblock auf. Dementspre-

chend können dieselben Wirkungen wie bei der ersten Ausführungsform auch dann erzielt werden, wenn die periphere Schaltung für ein in eine Mehrzahl von Speicherblöcken aufgeteiltes Speicherfeld 2 bereitgestellt wird.

**[0125]** Wie in [Fig. 8](#) dargestellt ist in dem zweiten Ausführungsbeispiel nach der ersten Abwandlung der ersten Ausführungsform die periphere Schaltung für jeden Speicherblock bereitgestellt. In dem dargestellten Beispiel sind jeweils periphere Schaltungen 5 und 5# entsprechend den Speicherblöcken MBa und MBb bereitgestellt.

**[0126]** Der peripheren Schaltung 5 werden über eine Versorgungsspannungsleitung PLA und eine Masseleitung GLa die Versorgungsspannung Vcc und die Massespennung GND zugeführt. In ähnlicher Weise werden der peripheren Schaltung 5# durch eine Versorgungsspannungsleitung PLb und eine Masseleitung GLb die Versorgungsspannung Vcc und die Massespennung GND zugeführt.

**[0127]** Die Versorgungsspannungsleitung PLA, PLb und die Masseleitung GLa und GLb erstrecken sich in dieselbe Richtung. Versorgungsknoten 7a und 7b zum Zuführen der Versorgungsspannung Vcc zu den jeweiligen Versorgungsspannungsleitungen PLA und PLb liegen einander in der Längsrichtung der Versorgungsleitungen gegenüber, wobei die Speicherblöcke (das Speicherfeld) dazwischenliegen. In ähnlicher Weise liegen sich Masseknoten 8a und 8b zum Zuführen der Massespennung GND zu den jeweiligen Masseleitungen GLa und GLb in der Längsrichtung der Versorgungsleitungen gegenüber, wobei die Speicherblöcke (das Speicherfeld) dazwischenliegt.

**[0128]** Der Versorgungsknoten und der Masseknoten, die derselben peripheren Schaltung entsprechen, liegen einander gegenüber, wobei die Speicherblöcke (das Speicherfeld) dazwischen liegen. Demzufolge fließt in der Versorgungsspannungsleitung PLA und der Masseleitung GLa, die der peripheren Schaltung 5 entsprechen, ein Strom in dieselbe Richtung. In ähnlicher Weise fließt in der Versorgungsspannungsleitung PLb und der Masseleitung GLb, die der Schaltung 5# entsprechen, ein Strom in dieselbe Richtung. Darüber hinaus fließt in den Versorgungsspannungsleitung PLA und PLb ein Strom in entgegengesetzte Richtungen, und in den Masseleitungen GLa und GLb fließt ein Strom in entgegengesetzte Richtungen.

**[0129]** Ein Paar von Versorgungsspannungsleitungen PLA und PLb bzw. ein Paar von Masseleitungen GLa und GLb können jeweils in nur einer Metallverdrahtungslage oder in verschiedenen Lagen ausgebildet sein, die entweder oberhalb oder unterhalb des magnetoresistiven Tunnellements TMR angeordnet sind, wie in dem in [Fig. 5](#) und [Fig. 6](#) dargestellten Fall

ein Paar aus einer Versorgungsspannungsleitung PL und einer Masseleitung GL.

**[0130]** Mit diesem Aufbau können dieselben Wirkungen wie bei der ersten Ausführungsform erzielt werden, auch wenn das Speicherfeld in eine Mehrzahl von Blöcken aufgeteilt ist und die periphere Schaltung für jeden Speicherblock bereitgestellt ist.

**[0131]** Bei der ersten Ausführungsform und ihrer ersten Abwandlung sind die Versorgungsleitung für die periphere Schaltung in dem Bereich um das Speicherfeld herum (d.h. in der Nachbarschaft des Speicherfelds) bereitgestellt. Zur verbesserten Integration der MRAM-Vorrichtung können die Versorgungsleitungen oberhalb oder unterhalb des Speicherfelds bereitgestellt sein, so dass sie sich über das Speicherfeld erstrecken.

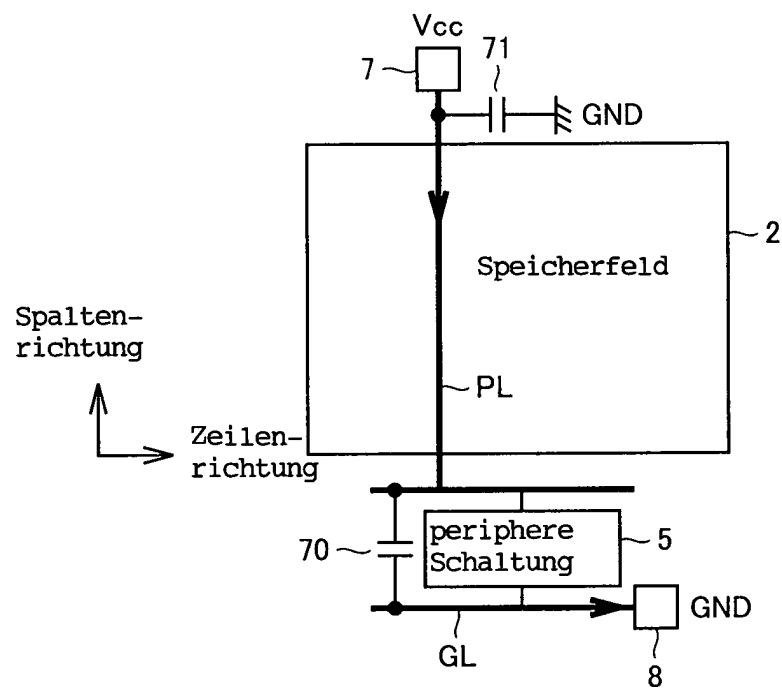

**[0132]** [Fig. 9](#) ist ein Blockdiagramm, das ein erstes Anordnungsbeispiel für die Versorgungsleitungen für die periphere Schaltung nach der zweiten Abwandlung der ersten Ausführungsform zeigt.

**[0133]** Wie in [Fig. 9](#) dargestellt werden in dem ersten Anordnungsbeispiel nach der zweiten Abwandlung der ersten Ausführungsform die Versorgungsspannungsleitung PL und die Masseleitung GL zum Zuführen der Versorgungsspannung Vcc und der Massespansnung GND zu der peripheren Schaltung 5 oberhalb und/oder unterhalb des Speicherfelds 2 bereitgestellt, so dass sie sich über das Speicherfeld 2 erstrecken.

**[0134]** Der Versorgungsknoten 7 und der Masseknoten 8 liegen der peripheren Schaltung 5 in der Längsrichtung der Versorgungsleitungen gegenüber, wobei das Speicherfeld 2 dazwischen liegt. Dementsprechend fließt in der Versorgungsspannungsleitung PL und der Masseleitung GL ein Strom in die entgegengesetzten Richtungen.

**[0135]** [Fig. 10a](#) bis [Fig. 10c](#) sind Querschnitte entlang der in [Fig. 9](#) dargestellten Linie P-Q. [Fig. 10a](#) bis [Fig. 10c](#) zeigen insbesondere das erste Anordnungsbeispiel für die Versorgungsleitungen nach der zweiten Abwandlung der ersten Ausführungsform.

**[0136]** In dem in [Fig. 10A](#) dargestellten Beispiel sind die Versorgungsspannungsleitung PL und die Masseleitung GL wie in dem in

**[0137]** [Fig. 5](#) dargestellten Fall in einer Metallverdrahtungslage ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnelemente TMR angeordnet ist. In [Fig. 10A](#) sind die Versorgungsspannungsleitung PL und die Masseleitung GL in einer Lage ausgebildet, die oberhalb der magnetoresistiven Tunnelemente TMR angeordnet ist. Diese Versorgungsleitungen können jedoch auch in ei-

ner Lage ausgebildet sein, die unterhalb der magnetoresistiven Tunnelemente TMR angeordnet ist. Die Ausbildung dieser Versorgungsleitungen in derselben Metallverdrahtungslage verringert die Anzahl der für die MRAM-Vorrichtung erforderlichen Metallverdrahtungslagen.

**[0138]** Mit diesem Aufbau können ein verringrigerter Betriebsspielraum und ein fehlerhaftes Schreiben, die durch magnetische Störungen von den Versorgungsleitungen bewirkt werden, auch dann verhindert werden, wenn die Versorgungsleitungen oberhalb oder unterhalb des Speicherfelds 2 bereitgestellt sind, so dass sie sich über das Speicherfeld 2 erstrecken.

**[0139]** In dem in [Fig. 10B](#) dargestellten Beispiel sind die Versorgungsspannungsleitung PL und die Masseleitung GL in verschiedenen Metallverdrahtungslagen ausgebildet, die entweder oberhalb oder unterhalb des magnetoresistiven Tunnelementes TMR angeordnet sind, und überlappen einander in vertikaler Richtung wie in dem in [Fig. 6](#) dargestellten Fall.

**[0140]** Auch dieser Aufbau verhindert wie der in [Fig. 10A](#) dargestellte Fall die nachteiligen Wirkungen der magnetischen Störungen von den Versorgungsleitungen. Es sei angemerkt, dass auch in dem in [Fig. 10B](#) dargestellten Beispiel die Versorgungsspannungsleitung PL und die Masseleitung GL in Lagen ausgebildet sein können, die unterhalb des magnetoresistiven Tunnelementes TMR angeordnet sind.

**[0141]** Wie in [Fig. 10C](#) dargestellt können die Versorgungsspannungsleitung PL und die Masseleitung GL in den Lagen bereitgestellt sein, die jeweils oberhalb und unterhalb des magnetoresistiven Tunnelementes TMR angeordnet sind. Da jedoch in der Versorgungsspannungsleitung PL und der Masseleitung GL ein Strom in die entgegengesetzten Richtungen fließt, Wechselwirken die durch diese Versorgungsleitungen erzeugten magnetischen Störungen in dem Bereich, in dem die magnetoresistiven Tunnelemente TMR bereitgestellt sind (d.h. in dem Speicherfeld), in einer konstruktiven Weise miteinander. Wenn in der Versorgungsspannungsleitung PL und der Masseleitung GL ein Strom in die entgegengesetzten Richtungen fließt, müssen diese Versorgungsleitungen dementsprechend in einer Lage oder in Lagen bereitgestellt sein, die entweder oberhalb oder unterhalb des magnetoresistiven Tunnelementes TMR angeordnet sind.

**[0142]** [Fig. 11](#) ist ein Blockdiagramm, das ein zweites Anordnungsbeispiel für die Versorgungsleitungen der peripheren Schaltung nach der zweiten Abwandlung der ersten Ausführungsform zeigt.

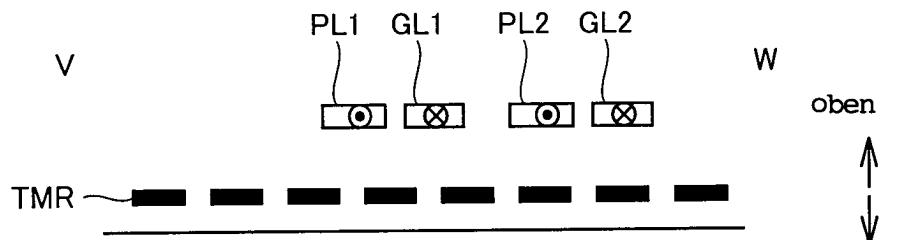

[0143] Mit Bezug auf [Fig. 9](#) und [Fig. 11](#) sind in dem zweiten Anordnungsbeispiel nach der zweiten Abwandlung der ersten Ausführungsform eine Mehrzahl von Versorgungsspannungsleitungen PL und eine Mehrzahl von Masseleitungen GL zum Zuführen der Versorgungsspannung Vcc und der Massespannung GND zu der peripheren Schaltung **5** bereitgestellt. In [Fig. 11](#) sind als Beispiel zwei Versorgungsspannungsleitungen PL1 und PL2 und zwei Masseleitungen GL1 und GL2 bereitgestellt. In den Versorgungsspannungsleitungen PL1 und PL2 fließt ein Strom in dieselbe Richtung. In ähnliche Weise fließt in den Masseleitungen GL1 und GL2 ein Strom in dieselbe Richtung. Dieser Aufbau verringert die Stromdichte jeder Verdrahtung, und dadurch verringert er die Möglichkeit der durch Elektromigration oder Ähnliches bewirkten Unterbrechung von Verdrahtungen.

[0144] [Fig. 12A](#) bis [Fig. 12C](#) sind Querschnitte entlang der in [Fig. 11](#) dargestellten Linie V-W. [Fig. 12A](#) bis [Fig. 12C](#) zeigen insbesondere das zweite Anordnungsbeispiel für die Versorgungsleitungen nach der zweiten Abwandlung der ersten Ausführungsform.

[0145] In dem in [Fig. 12A](#) dargestellten Beispiel sind die Versorgungsspannungsleitungen PL1 und PL2 und die Masseleitungen GL1 und GL2 in einer Metallverdrahtungslage ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnellemente TMR ausgebildet ist, wie in dem in [Fig. 10A](#) dargestellten Fall. In dem dargestellten Beispiel sind die Versorgungsleitungen in einer Lage ausgebildet, die oberhalb der magnetoresistiven Tunnellemente TMR ausgebildet ist. Die Versorgungsleitungen können jedoch auch in einer Lage ausgebildet sein, die unterhalb der magnetoresistiven Tunnellemente TMR angeordnet ist. Die Ausbildung der Versorgungsleitung in derselben Metallverdrahtungslage verringert die Anzahl der für die MRAM-Vorrichtung erforderlichen Metallverdrahtungslagen.

[0146] In dem in [Fig. 12B](#) dargestellten Beispiel sind die Versorgungsspannungsleitung PL1 und PL2 und die Masseleitungen GL1 und GL2 in verschiedenen Metallverdrahtungslagen ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnellemente TMR ausgebildet sind, und überlappen einander wie in dem in [Fig. 10B](#) dargestellten Fall in vertikaler Richtung. In dem dargestellten Beispiel sind die Versorgungsleitungen in den Lagen ausgebildet, die oberhalb der magnetoresistiven Tunnellemente TMR angeordnet sind. Die Versorgungsleitungen können jedoch auch in Metallverdrahtungslagen ausgebildet sein, die unterhalb der magnetoresistiven Tunnellemente TMR ausgebildet sind.

[0147] In dem in [Fig. 12C](#) dargestellten Beispiel sind die Versorgungsleitungen in Lagen ausgebildet, die oberhalb und unterhalb der magnetoresistiven

Tunnellemente TMR angeordnet sind. So sind zum Beispiel die Versorgungsleitung PL1 und die Masseleitung GL1 in derselben Metallverdrahtungslage ausgebildet, die oberhalb der magnetoresistiven Tunnellemente TMR angeordnet ist, und die Versorgungsspannungsleitung PL2 und die Masseleitung GL2 sind in derselben Metallverdrahtungslage ausgebildet, die unterhalb der magnetoresistiven Tunnellemente TMR angeordnet ist.

[0148] In diesem Beispiel überlappen sich Verdrahtungen mit derselben Stromrichtung gegenseitig, wobei die magnetoresistiven Tunnellemente TMR dazwischenliegen. Anders ausgedrückt: Die Verdrahtungen sind entsprechend der Stromrichtung paarweise angeordnet. Vorzugsweise sind die Verdrahtungen jedes Paars in Hinblick auf die magnetoresistiven Tunnellemente TMR vertikal symmetrisch angeordnet. So sind zum Beispiel die Versorgungsspannungsleitungen PL1 und PL2, die dieselbe Stromrichtung haben, in Hinblick auf die magnetoresistiven Tunnellemente TMR vertikal symmetrisch angeordnet. In ähnlicher Weise sind die Masseleitungen GL1 und GL2, die dieselbe Stromrichtung haben, im Hinblick auf die magnetoresistiven Tunnellemente TMR vertikal symmetrisch angeordnet.

[0149] Mit diesem Aufbau heben die von den Versorgungsleitungen erzeugten magnetischen Störungen einander in den magnetoresistiven Tunnellementen TMR gegenseitig auf. Demzufolge kann die Anordnung von Versorgungsleitungen, die in der Lage ist, die nachteiligen Wirkungen der von den Versorgungsleitungen erzeugten magnetischen Störungen zu unterdrücken, verwirklicht werden, indem beide Metallverdrahtungslagen, die oberhalb und unterhalb der magnetoresistiven Tunnellemente TMR angeordnet sind, verwendet werden.

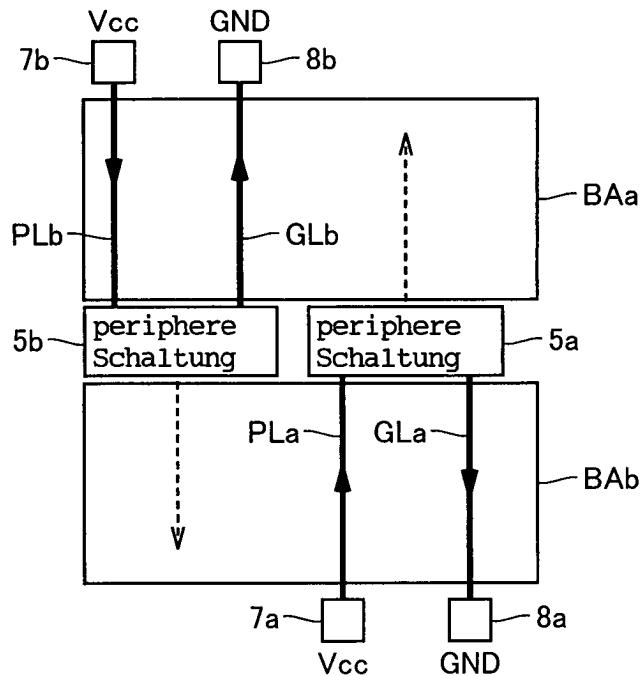

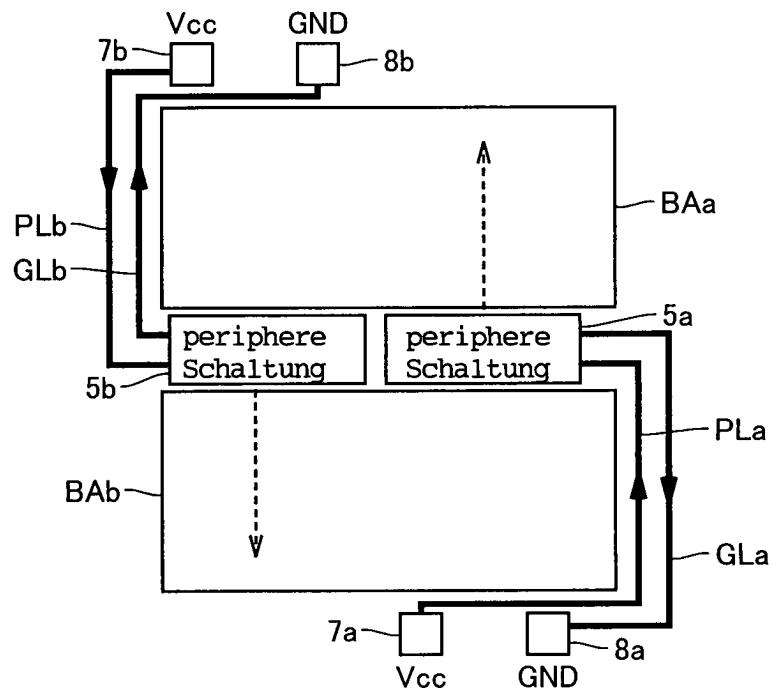

[0150] In der dritten Abwandlung der ersten Ausführungsform sind die peripheren Schaltungen auf beiden Seiten des Speicherfelds bereitgestellt. Im folgenden wird die Anordnung der Versorgungsleitungen in diesem Aufbau beschrieben.

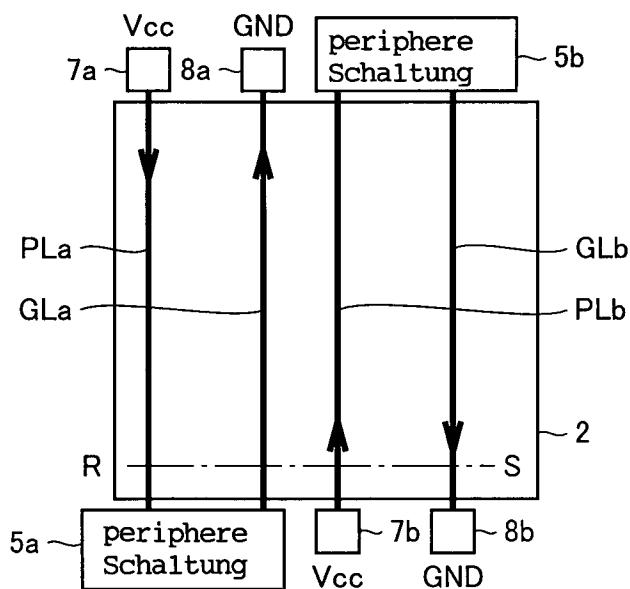

[0151] [Fig. 13](#) ist ein Blockdiagramm, das die Anordnung der Versorgungsleitungen nach der dritten Abwandlung der ersten Ausführungsform veranschaulicht. Wie in [Fig. 13](#) dargestellt, führen in der dritten Abwandlung der ersten Ausführungsform die Versorgungsleitungen den peripheren Schaltungen **5a** und **5b**, die einander gegenüberliegen, wobei das Speicherfeld **2** dazwischenliegt, die Versorgungsspannung Vcc und die Massespannung GND zu.

[0152] Genauer gesagt: die Versorgungsspannungsleitung PLa und die Masseleitung GLa führen der peripheren Schaltung **5a** die Versorgungsspannung Vcc und die Massespannung GND zu. Die Versorgungsspannungsleitungen PLb und die Masselei-

tung GLb führen der peripheren Schaltung **5b** die Versorgungsspannung Vcc und die Massespannung GND zu. Wie in dem in [Fig. 9](#) dargestellten Fall fließt in der Versorgungsspannungsleitung und in der Masseleitung ein Strom in entgegengesetzten Richtungen zum Zuführen einer Betriebsspannung zu derselben peripheren Schaltung.

**[0153]** Der Versorgungsknoten **7a** und der Masseknoten **8a**, die der peripheren Schaltung **5a** entsprechen, liegen der peripheren Schaltung **5a** gegenüber, wobei das Speicherfeld **2** dazwischenliegt. Die Versorgungsspannungsleitung PLa erstreckt sich zwischen dem Versorgungsknoten **7a** und der peripheren Schaltung **5a**, und die Masseleitung GLa erstreckt sich zwischen dem Masseknoten **8a** und der peripheren Schaltung **5a**.

**[0154]** Der Versorgungsknoten **7b** und der Masseknoten **8b**, die der peripheren Schaltung **5b** entsprechen, liegen in ähnlicher Weise der peripheren Schaltung **5b** gegenüber, wobei das Speicherfeld **2** dazwischenliegt. Die Versorgungsspannungsleitung PLb erstreckt sich zwischen dem Versorgungsknoten **7b** und der peripheren Schaltung **5b**, und die Masseleitung GLb erstreckt sich zwischen dem Masseknoten **8b** und der peripheren Schaltung **5b**.

**[0155]** Dementsprechend fließt in den Versorgungsspannungsleitungen PLa und PLb ein Strom in die entgegengesetzten Richtungen, und in den Masseleitungen GLa und GLb fließt ein Strom in die entgegengesetzten Richtungen.

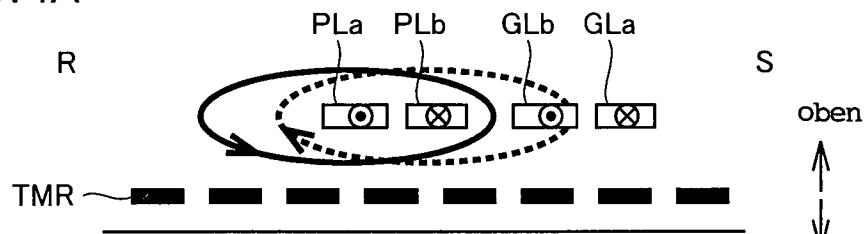

**[0156]** [Fig. 14A](#) bis [Fig. 14C](#) sind Querschnitte entlang der in [Fig. 13](#) dargestellten Linie R-S. [Fig. 14A](#) bis [Fig. 14C](#) zeigen insbesondere die Anordnung der Versorgungsleitungen nach der dritten Abwandlung der ersten Ausführungsform.

**[0157]** Mit Bezug auf [Fig. 14A](#) sind in einem ersten Anordnungsbeispiel die Versorgungsspannungsleitungen PLa und PLb und die Masseleitungen GLa und GLb in einer Metallverdrahtungslage ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnelemente TMR angeordnet sind. Die Versorgungsspannungsleitungen PLa und PLb mit entgegengesetzten Stromrichtungen sind nahe beieinander angeordnet. In ähnlicher Weise sind die Masseleitungen GLa und GLb nahe beieinander angeordnet. Dieser Aufbau ermöglicht die Unterdrückung der nachteiligen Wirkungen der magnetischen Störungen von den Versorgungsleitungen auf das Speicherfeld in dem Bereich, in dem die magnetoresistiven Tunnelemente TMR bereitgestellt sind. In dem in [Fig. 14A](#) dargestellten Beispiel sind die Versorgungsleitungen in der Lage ausgebildet, die oberhalb der magnetoresistiven Tunnelemente TMR angeordnet ist. Diese Versorgungsleitungen können jedoch auch alternativ in einer Lage ausgebil-

det sein, die unterhalb der magnetoresistiven Tunnellemente TMR angeordnet ist. Darüber hinaus verringert das Ausbilden der Versorgungsleitungen in derselben Metallverdrahtungslage die Anzahl der für die MRAM-Vorrichtung erforderlichen Metallverdrahtungslagen.

**[0158]** Wie in [Fig. 14B](#) dargestellt sind in einem zweiten Anordnungsbeispiel die Versorgungsspannungsleitungen PLa und PLb nahe beieinander in verschiedenen Metallverdrahtungslagen ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnelemente angeordnet sind, und überlappen einander in der vertikalen Richtung. In ähnlicher Weise sind die Masseleitungen GLa und GLb nahe beieinander in verschiedene Metallverdrahtungslagen ausgebildet, die entweder oberhalb oder unterhalb der magnetoresistiven Tunnelemente angeordnet sind, und überlappen einander in der vertikalen Richtung.

**[0159]** In diesem Fall fließt in den Versorgungsleitungen, die in derselben Metallverdrahtungslage ausgebildet sind, ein Strom in die entgegengesetzten Richtungen. Anders ausgedrückt sind die Versorgungsspannungsleitung PLa und die Masseleitung GLa in derselben Metallverdrahtungslage ausgebildet, und die Versorgungsspannungsleitung PLb und die Masseleitung GLb sind in derselben Metallverdrahtungslage ausgebildet.

**[0160]** Wie in dem in [Fig. 14A](#) dargestellten Fall ermöglicht dieser Aufbau die Unterdrückung der nachteiligen Wirkungen der magnetischen Störungen von den Versorgungsleitungen auf den Bereich in dem die magnetoresistiven Tunnelemente TMR bereitgestellt sind (d.h. das Speicherfeld).

**[0161]** In dem in [Fig. 14B](#) dargestellten Beispiel sind die Versorgungsleitungen in den Metallverdrahtungslagen ausgebildet, die oberhalb der magnetoresistiven Tunnelemente ausgebildet sind.

**[0162]** Diese Versorgungsleitungen können jedoch auch alternativ in den Metallverdrahtungslagen ausgebildet sind, die unterhalb der magnetoresistiven Tunnelemente TMR angeordnet sind.