## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

|                                                                                                                                                                                                    |  |                                                                                                                                           |                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| (51) International Patent Classification 6 :<br><b>G09G 3/28, 3/10</b>                                                                                                                             |  | A1                                                                                                                                        | (11) International Publication Number: <b>WO 00/17846</b><br>(43) International Publication Date: 30 March 2000 (30.03.00) |

| (21) International Application Number: PCT/US99/19714<br>(22) International Filing Date: 30 August 1999 (30.08.99)                                                                                 |  | (81) Designated States: CN, JP, KP, KR, MG, RU, European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE). |                                                                                                                            |

| (30) Priority Data:<br>09/159,211 23 September 1998 (23.09.98) US<br>09/310,446 12 May 1999 (12.05.99) US                                                                                          |  | Published<br><i>With international search report.</i>                                                                                     |                                                                                                                            |

| (71) Applicant (for AT BE CH CN CY DE DK ES FI FR GB GR IE IT JP KP LU MC NL PT RU SE only): MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD. [JP/JP]; 1006, Oaza Kadoma, Kadoma-shi, Osaka 571-8501 (JP). |  |                                                                                                                                           |                                                                                                                            |

| (71) Applicant (for MG only): GREELEY, Paul, D. [US/US]; Ohlandt, Greeley, Ruggiero & Perle, 9th floor, One Landmark Square, Stamford, CT 06901-2682 (US).                                         |  |                                                                                                                                           |                                                                                                                            |

| (72) Inventor: WEBER, Larry, F.; 1 Emmy Lane, New Paltz, NY 12561 (US).                                                                                                                            |  |                                                                                                                                           |                                                                                                                            |

| (74) Agent: KOFFSKY, David, N.; Ohlandt, Greeley, Ruggiero & Perle, L.L.P., 9th floor, One Landmark Square, Stamford, CT 06901-2682 (US).                                                          |  |                                                                                                                                           |                                                                                                                            |

## (54) Title: POSITIVE COLUMN AC PLASMA DISPLAY

## (57) Abstract

An AC PDP (50) has a plurality of addressable subpixel sites, each subpixel site including an address electrode (52) positioned on one substrate (51) and first and second sustain electrodes (60, 62, 64) positioned on an opposed substrate (58). An intersection between the address electrode and the first sustain electrode defines a first discharge site and an intersection between the address electrode and the second electrode defines a second discharge site. A scan driver (70) is active during an address phase, and applies a negative going signal to the first sustain electrode. An address driver (53) applies an address signal to the address electrode which creates a discharge at the first discharge site and causes a discharge thereat which induces a wall voltage at the second discharge site in accordance with a determined subpixel value. A sustain driver (68) applies a sustain signal to both the first sustain electrode and the second sustain electrode and creates a "ping pong" action of the wall charge states at the discharge sites and enables the use of positive column light emission in the PDP.

**FOR THE PURPOSES OF INFORMATION ONLY**

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

|    |                          |    |                                       |    |                                           |    |                          |

|----|--------------------------|----|---------------------------------------|----|-------------------------------------------|----|--------------------------|

| AL | Albania                  | ES | Spain                                 | LS | Lesotho                                   | SI | Slovenia                 |

| AM | Armenia                  | FI | Finland                               | LT | Lithuania                                 | SK | Slovakia                 |

| AT | Austria                  | FR | France                                | LU | Luxembourg                                | SN | Senegal                  |

| AU | Australia                | GA | Gabon                                 | LV | Latvia                                    | SZ | Swaziland                |

| AZ | Azerbaijan               | GB | United Kingdom                        | MC | Monaco                                    | TD | Chad                     |

| BA | Bosnia and Herzegovina   | GE | Georgia                               | MD | Republic of Moldova                       | TG | Togo                     |

| BB | Barbados                 | GH | Ghana                                 | MG | Madagascar                                | TJ | Tajikistan               |

| BE | Belgium                  | GN | Guinea                                | MK | The former Yugoslav Republic of Macedonia | TM | Turkmenistan             |

| BF | Burkina Faso             | GR | Greece                                | ML | Mali                                      | TR | Turkey                   |

| BG | Bulgaria                 | HU | Hungary                               | MN | Mongolia                                  | TT | Trinidad and Tobago      |

| BJ | Benin                    | IE | Ireland                               | MR | Mauritania                                | UA | Ukraine                  |

| BR | Brazil                   | IL | Israel                                | MW | Malawi                                    | UG | Uganda                   |

| BY | Belarus                  | IS | Iceland                               | MX | Mexico                                    | US | United States of America |

| CA | Canada                   | IT | Italy                                 | NE | Niger                                     | UZ | Uzbekistan               |

| CF | Central African Republic | JP | Japan                                 | NL | Netherlands                               | VN | Viet Nam                 |

| CG | Congo                    | KE | Kenya                                 | NO | Norway                                    | YU | Yugoslavia               |

| CH | Switzerland              | KG | Kyrgyzstan                            | NZ | New Zealand                               | ZW | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP | Democratic People's Republic of Korea | PL | Poland                                    |    |                          |

| CM | Cameroon                 | KR | Republic of Korea                     | PT | Portugal                                  |    |                          |

| CN | China                    | KZ | Kazakhstan                            | RO | Romania                                   |    |                          |

| CU | Cuba                     | LC | Saint Lucia                           | RU | Russian Federation                        |    |                          |

| CZ | Czech Republic           | LI | Liechtenstein                         | SD | Sudan                                     |    |                          |

| DE | Germany                  | LK | Sri Lanka                             | SE | Sweden                                    |    |                          |

| DK | Denmark                  | LR | Liberia                               | SG | Singapore                                 |    |                          |

**Positive Column AC Plasma Display****FIELD OF THE INVENTION**

5        This invention relates to AC plasma display panels and, more particularly, to a an AC plasma display panel that emits most of its light from the positive column region of a gas discharge and, as a result, exhibits substantially improved levels of image brightness and 10        luminous efficiency.

**BACKGROUND OF THE INVENTION**

Prior art AC plasma display panels (PDPs) generate the majority of their emitted light from the negative 15        glow region of a gas discharge. As is known to those skilled in the art, gas discharges exhibit two distinct light emitting regions, i.e. the negative glow wherein a plasma exists with an excess of positively charged ions and the positive column wherein the plasma evidences a 20        balance of positively charged ions and electrons.

PDP subpixel sites operate using the same fundamental principle as a fluorescent lamp. More particularly, a PDP subpixel employs ultraviolet light generated by a gas discharge to excite visible light 25        emitting phosphors. A fluorescent lamp uses the positive column region of a gas discharge to generate most of its light since the positive column has a much higher luminous efficiency than the negative glow.

The positive column has not been previously 30        successfully applied to AC PDPs because the limited physical space of the small subpixel sites do not easily allow sufficient room for the usually long dimensions of a positive column.

**The Positive Column and the Negative Glow**

In qualitative terms, the power in a gas discharge is divided between the two major regions: the positive column and the negative glow. The positive column is 5 characterized by an equal density of electrons and ions that are of a very high density that shields out most of an applied electric field. In the positive column the high density of highly conductive electrons and ions quickly move to cancel any high field region.

10 The negative glow is characterized by a very high level of positive ions and a very low level of negative electrons. The high density of positive charge means that the electric field in the negative glow is very high. The very high electric field allows a major part 15 of the potential applied across the gas to be dropped across the negative glow. Since the positive column and the negative glow are electrically "connected" in series, all of the current through the gas discharge passes through both the positive column and the negative 20 glow. To determine the instantaneous power dissipated in a given discharge region, it is necessary to simply multiply the discharge current by the voltage drop across the region.

The positive column and the negative glow have 25 considerably different luminous efficiencies. In general, the positive column is very efficient and the negative glow is inefficient. A fundamental reason for this difference is that most of the current flow in the positive column is due to electrons and most of the 30 current flow in the negative glow is due to ions.

Energy absorbed by electrons can be used to efficiently excite atoms that ultimately emit light. Alternatively energy absorbed by ions eventually gets transferred to the gas atoms as kinetic energy and simply heats up the

gas.

As stated above, the positive column has approximately equal numbers of electrons and ions.

Since the electrons have roughly 100 times the mobility of the ions, they will conduct 100 times more of the current than the ions in the positive column. Because most of the current flow in the positive column is in the electrons, virtually all of the power dissipated in the positive column goes into the kinetic energy of the electrons. This kinetic energy can be transferred to the excitation of atoms with efficiencies greater than 80% if the electric field is of the correct low value. Virtually all of the excited atoms generate ultraviolet photons which can further excite the phosphors to emit the desired visible light.

The negative glow has a high number of ions and a much smaller number of electrons. Even though the electrons have two orders of magnitude greater mobility than the ions, the ions are of such a large density that much of the power dissipated in the negative glow goes to the kinetic energy of the ions. However, the electric field in the negative glow is very high and therefore the electrons gain much higher kinetic energies than in the lower field of the positive column. The higher electron kinetic energies mean that the electrons can both excite and ionize the atoms. Electron energy used to ionize the atoms creates ions that flow to the cathode and are ultimately neutralized at the cathode surface.

While electron impact ionization of atoms is the source of ions and electrons that are needed to make the gas discharge conductive, it does not create any ultraviolet photons. Therefore the high electric fields in the negative glow allow a large amount of impact

ionization which results in a much lower conversion efficiency of electron kinetic energy to ultraviolet photons. This UV conversion efficiency may be typically only 30% compared to 80% in the positive column.

5 It is known that the positive column exhibits an 80% total efficiency and that the negative glow exhibits an efficiency of 15%. This difference in efficiencies - indicates why it is much more desirable to dissipate energy in the positive column than in the negative glow

10 and is the fundamental reason that fluorescent lamps are designed to use the positive column and why they achieve a high luminous efficiency of 80 lumens per watt. To achieve this result, the fluorescent lamp design maximizes the power dissipation in the highly efficient

15 positive column and minimizes it in the low efficiency negative glow.

One way that most fluorescent lamps reduce dissipation in the negative glow is to use a heated cathode that emits large numbers of electrons that serve 20 to drive the gas discharge. This source of electrons reduces the voltage drop across the negative glow by an order of magnitude which, for equal currents, reduces the power dissipation in the negative glow by an order of magnitude. Such a reduction allows for more

25 dissipation in the much more efficient positive column. The use of this same idea for PDPs would require a heated cathode for each of the hundreds of thousands of subpixels in the display. Because such an arrangement is impractical, it is difficult to reduce the power

30 dissipation in the negative glow of a plasma display.

A second strategy for increasing the efficiency of the fluorescent lamp is to increase the length of the positive column. This is the reason that the common fluorescent lamp is a long tube. The positive column

can be modeled as a resistor. Therefore the longer the positive column, the greater its resistance and the greater its power dissipation. The properties of the positive column allow it to be easily extended in length 5 as long as there is sufficient voltage to establish the desired current across its resistance. This means that for a constant current, as the positive column is made - longer, the voltage across the positive column needs to increase proportionally. Further, the longer the 10 positive column, the more favorable is the ratio between the power dissipated in the positive column and that dissipated in the negative glow.

While the principle of making a gas discharge more efficient by using a long positive column is well known, 15 it has not been successfully applied to PDPs. One reason is that it has long been thought that the long nature of the positive column is not practical for the very small subpixels of a plasma display and therefore, observers have stated that most of the light from a PDP 20 comes from the negative glow.

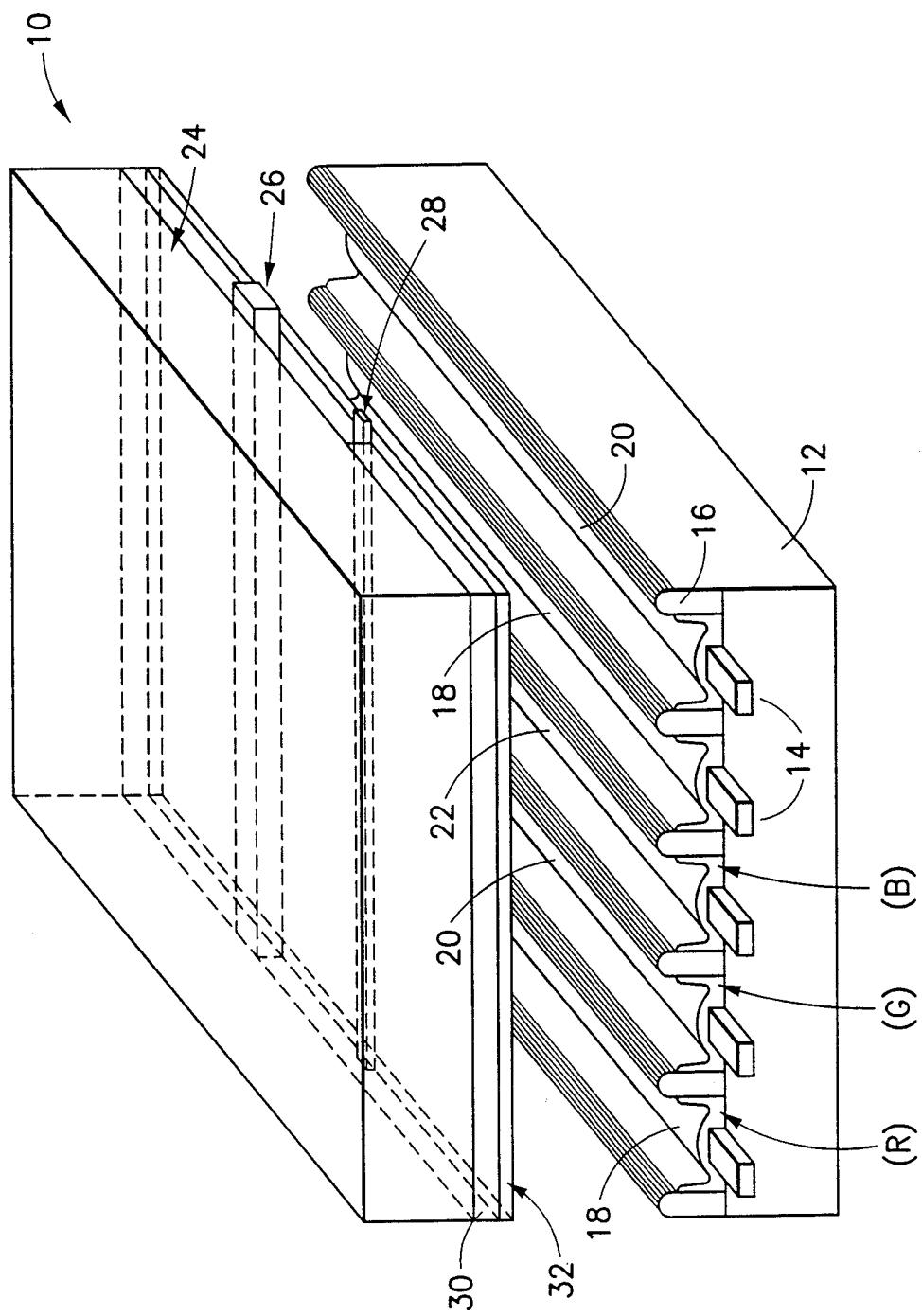

Fig. 1 shows a prior art color AC PDP from U.S. Patent 5,745,086. This structure utilizes ultraviolet light which is generated by a gas discharge to selectively excite red, green and blue phosphors to emit 25 the desired full color visible light. Figs. 2a-2c show typical cross sectional views of the subpixels in the AC PDP of Fig. 1. Such an AC PDP operates with AC voltages and provide write voltages which exceed the firing voltage of the ionizable gas at a given discharge site, 30 as defined by selected column and row electrodes. The discharge is continuously "sustained" by applying an alternating sustain signal (which, by itself, is insufficient to initiate a discharge). The technique relies upon wall charges generated on the dielectric

layers of the substrates which, in conjunction with the sustain signal, operate to maintain continuing discharges.

In order for an AC plasma panel to exhibit reliable 5 operation, its wall charge states must be repeatable and standardized. More specifically, the wall charge states must exhibit repeatable values irrespective of a previous data storage state, so that succeeding address and sustain signals reliably cooperate to assure 10 repeatable pixel site operation.

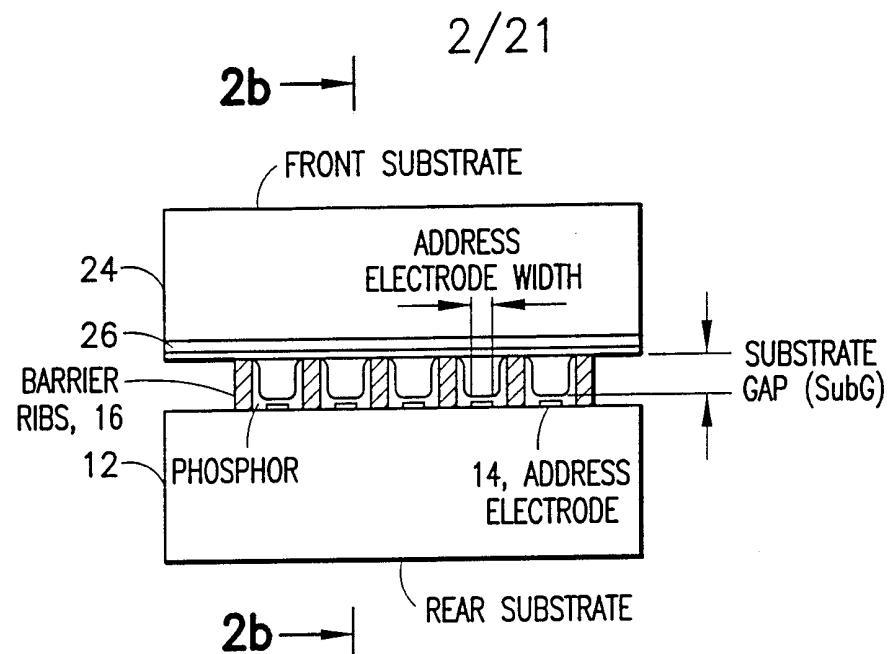

In Figs. 1 and 2a-2c, PDP 10 includes a back substrate 12 upon which plural column address electrodes 14 are supported. Column address electrodes 14 are separated by barrier ribs 16 and are covered by red, 15 green and blue phosphors 18, 20 and 22, respectively. A front transparent substrate 24 includes a pair of sustain electrodes 26 and 28 for each row of pixel sites. A dielectric layer 30 is emplaced on front substrate 24 and a magnesium oxide or similar high gamma 20 material overcoat layer 32 covers the entire lower surface thereof, including all of sustain electrodes 26 and 28.

The structure of Fig. 1 is sometimes called a single substrate AC PDP since both sustain electrodes 26 and 28, for each row, are on a single substrate of the 25 panel. An inert gas mixture is positioned between substrates 12 and 24 and is excited to a discharge state by a sustain signal applied by sustain electrodes 26 and 28. The discharging inert gas produces ultra-violet 30 light that excites the red, green and blue phosphor layers 18, 20 and 22, respectively to emit visible light. If the driving voltages applied to column address electrodes 14 and sustain electrodes 26, 28 are appropriately controlled, a full color image is visible

through front substrate 24.

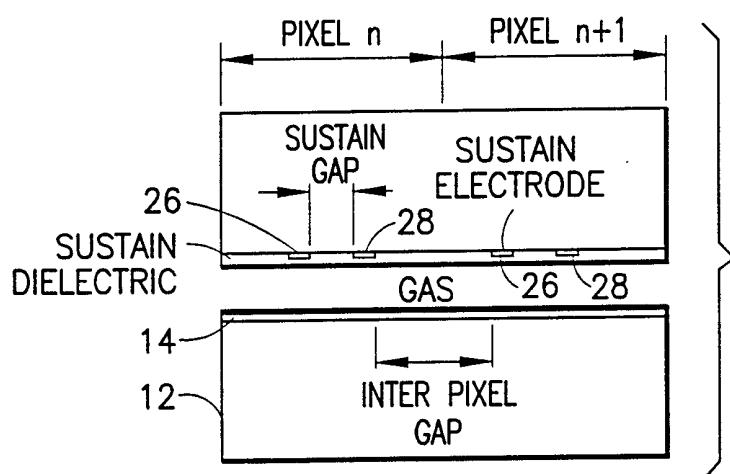

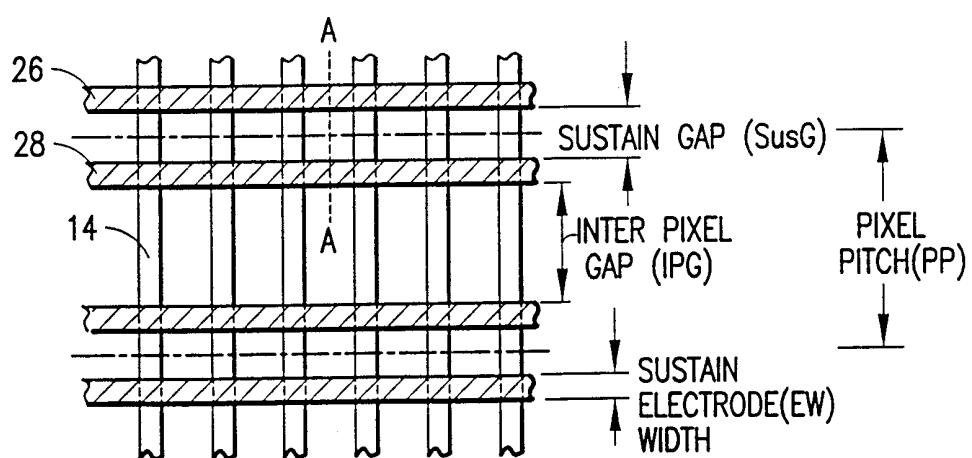

The table shown in Fig. 2d provides typical dimensions of prior art PDPs (in micrometers) for various designs. Designs F, N, M and P are designs used 5 in practical displays by various manufacturers. Note that for these designs, the gap distance between the front substrate sustain electrodes, called the sustain - gap (SusG) is usually approximately equal to the gap distance between the front substrate and the rear substrate, referred to as the substrate gap (SubG). 10 This is illustrated by the ratio SusG/SubG which ranges between .84 and 1.23 for the four prior art designs.

While many different dimensions have been successfully used, the approximate equality between 15 these two gaps has been maintained. Note also that the sustain gap is always less than the distance between the sustain electrode of one subpixel and the sustain electrode of a neighboring subpixel which is referred to as the inter pixel gap (IPG). This is illustrated by 20 the ratio SusG/IPG which ranges between .29 and .37 for the four prior art designs.

If the IPG is not considerably larger than the SusG, there will be strong interaction between subpixels that will cause operational failures. More 25 specifically, if the IPG is smaller than the SusG, then when the sustain signal is applied, the electric field across the IPG will be larger than the electric field across the SusG. This will allow a discharge to occur along the IPG which would modify the charge on the 30 sustain dielectric layers and substantially modify the operation of the discharge along the sustain gap.

It is therefore an object of this invention to provide a full color PDP which exhibits improved image brightness and luminous efficiency when compared to

prior art PDPs.

It is a further object of this invention to provide a full color PDP wherein subpixel sites utilize positive column discharges to achieve improved luminous 5 efficiencies and high levels of light emission.

#### SUMMARY OF THE INVENTION

An AC PDP has a plurality of addressable subpixel sites, each subpixel site including an address electrode positioned on one substrate and first and second sustain electrodes positioned on an opposed substrate. An 10 intersection between the address electrode and the first sustain electrode defines a first discharge site and an intersection between the address electrode and the 15 second electrode defines a second discharge site. A scan driver is active during an address phase, and applies a negative going signal to the first sustain electrode. An address driver applies an address signal to the address 20 electrode which creates a discharge at the first discharge site. As a result, a positive column moves along the address electrode to the second discharge site and causes a discharge thereat which induces a wall 25 voltage at the second discharge site in accordance with a determined subpixel value. A sustain driver applies a sustain signal to both the first sustain electrode and the second sustain electrode and creates a "ping pong" action of the wall charge states at the discharge sites and enables the use of positive column light emission in 30 the PDP.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Fig. 1 shows a prior art color AC PDP.

Fig. 2a shows a first sectional view of the AC PDP

of Fig. 1.

Fig. 2b shows a second sectional view of the AC PDP of Fig. 1.

5

Fig. 2c shows a schematic plan view of the AC PDP of Fig. 1.

10 Fig. 2d is a Table which provides measurements of both prior art PDPs and a PDP incorporating the invention.

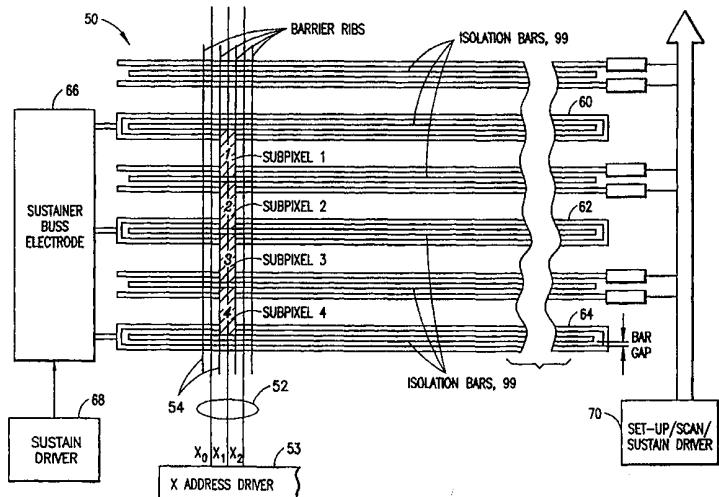

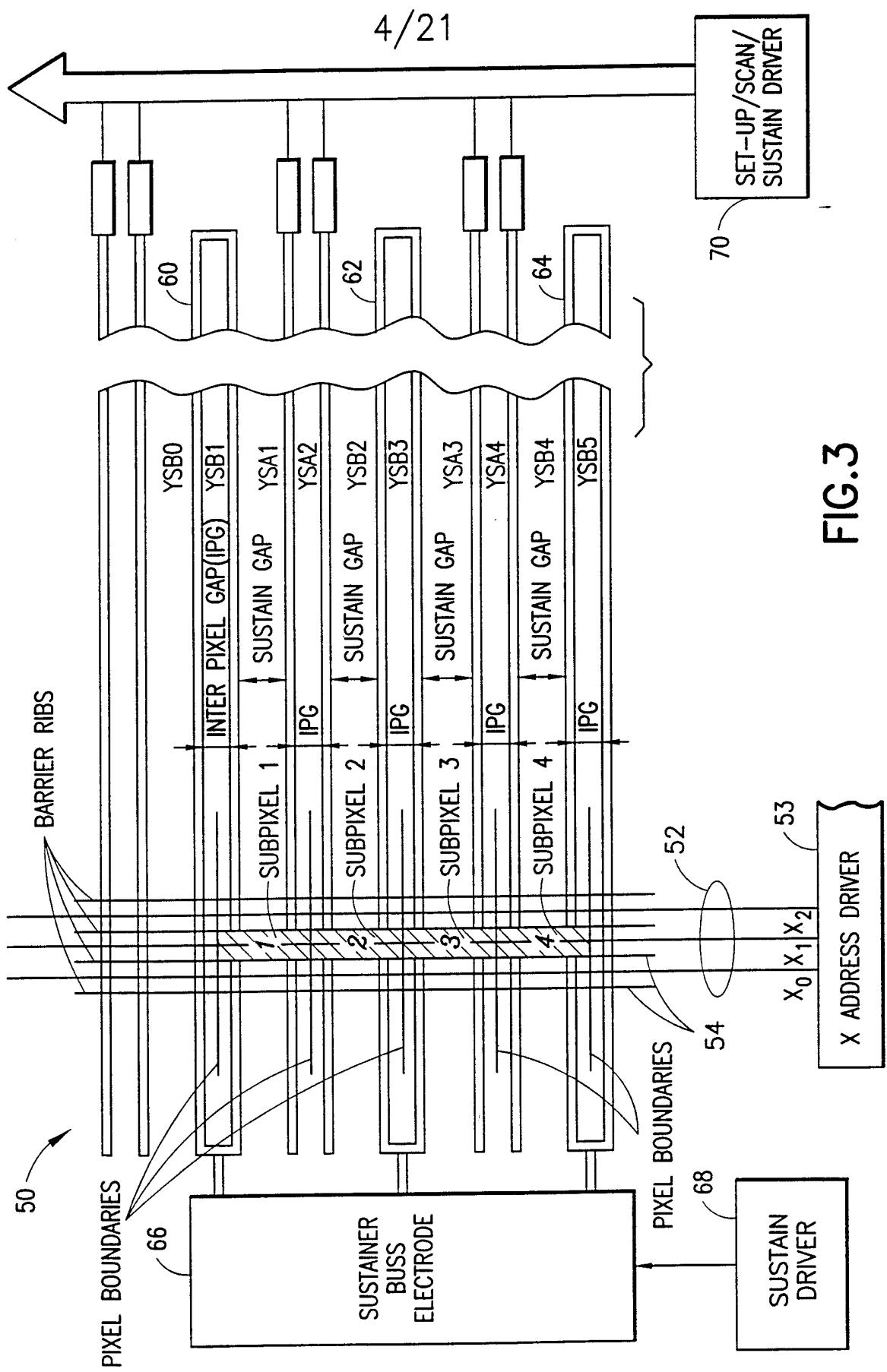

15 Fig. 3 is a schematic which illustrates the electrode arrangements of a PDP incorporating the invention.

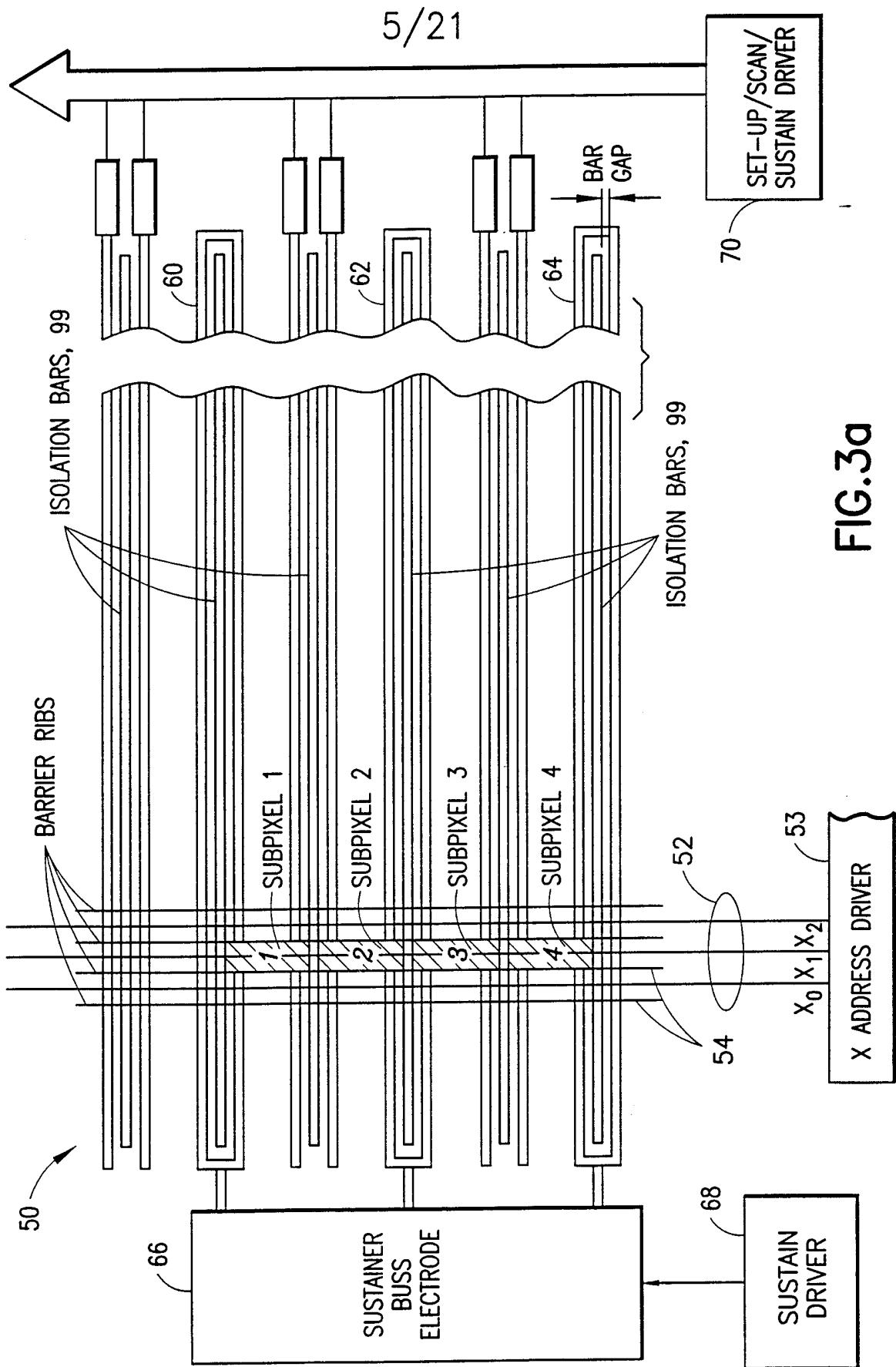

Fig. 3a illustrates an electrode arrangement of Fig. 3, which further incorporates electrode isolation bars.

20

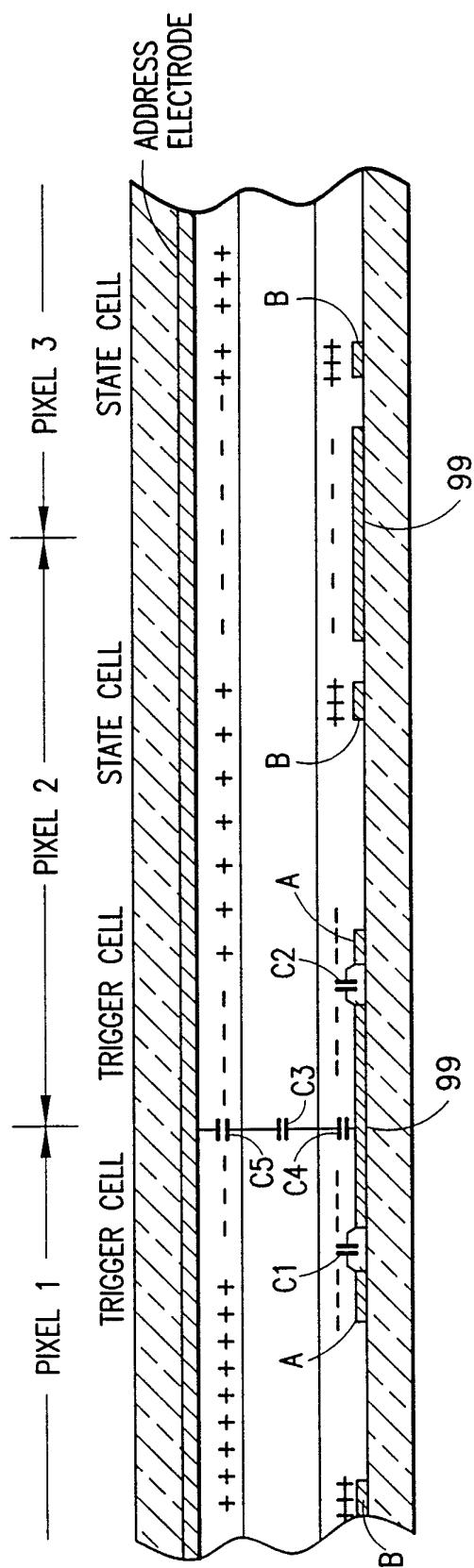

Fig. 3b is a sectional view of a part of the electrode arrangement of Fig. 3a, helpful in enabling an understanding of the operation of the electrode isolation bars.

25

Fig. 4 is a sectional view of a subpixel in the PDP of Fig. 3.

30 Figs. 5a-5f illustrate the operation of the subpixel of Fig. 4.

Fig. 6a is a plot of sustain voltage versus sustain gap illustrating the relationship between minimum sustain voltages required to establish a discharge for

conventional design PDPs having relatively small sustain gaps and for PDPs constructed in accordance with the invention and exhibiting relatively large sustain gaps.

5

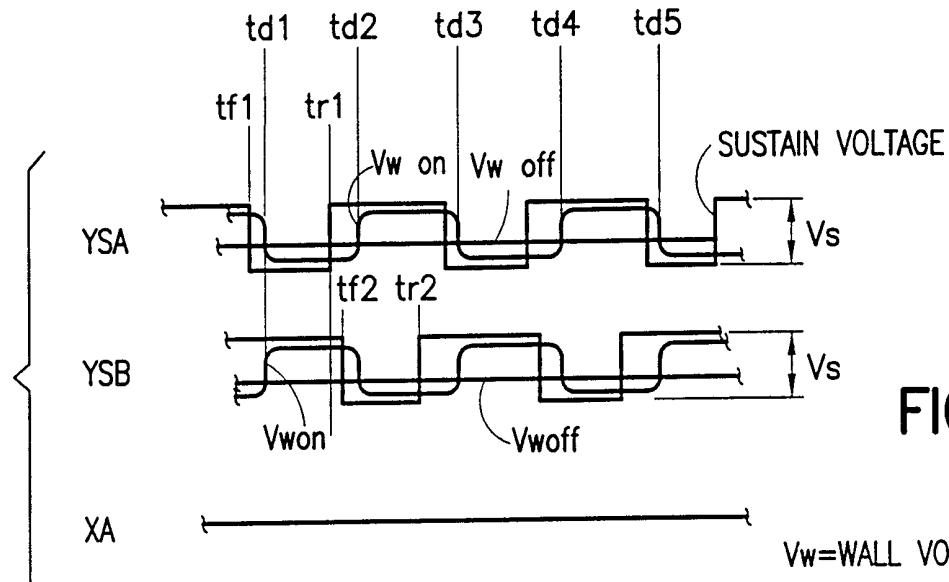

Fig. 6b illustrates a set of sustain waveforms used with the invention.

10 Fig. 7 illustrates a set of sustain waveforms that will create an errant erase operation.

Fig. 8 illustrates a set of prior art sustain waveforms that will not operate with the invention.

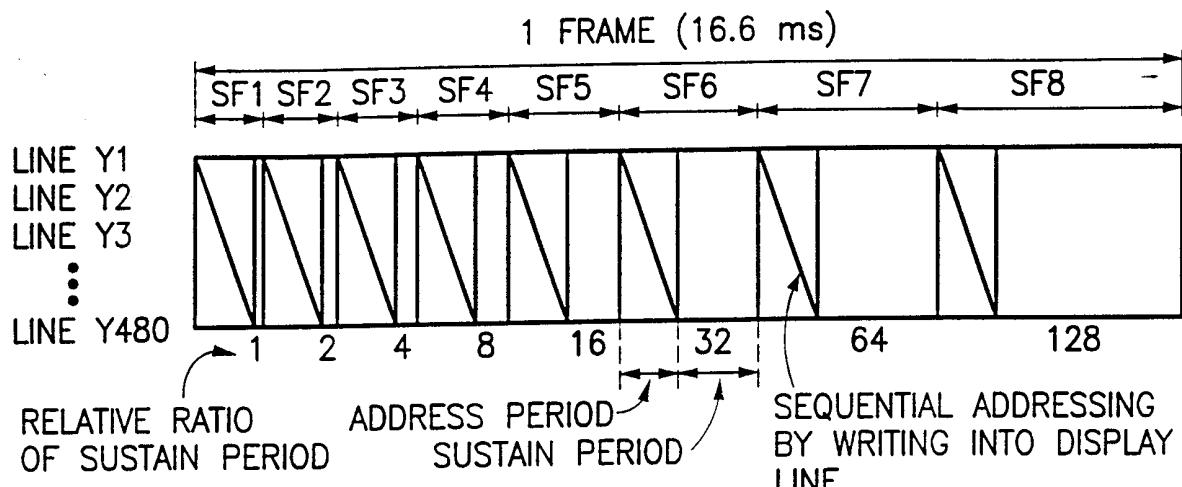

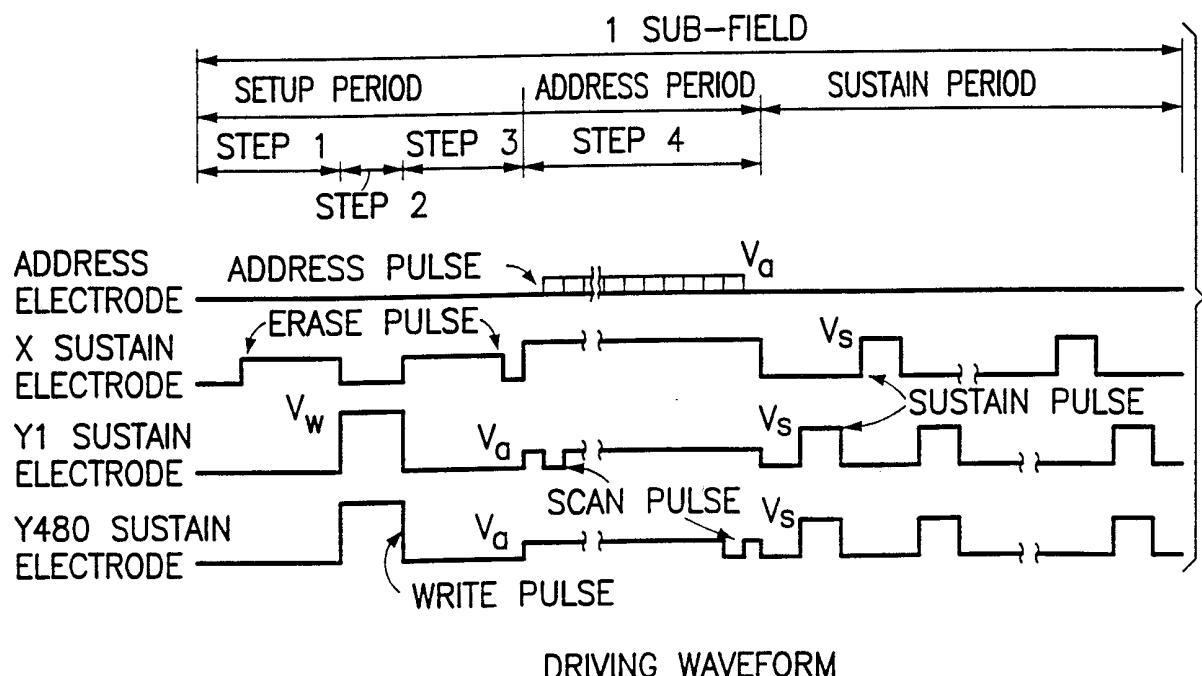

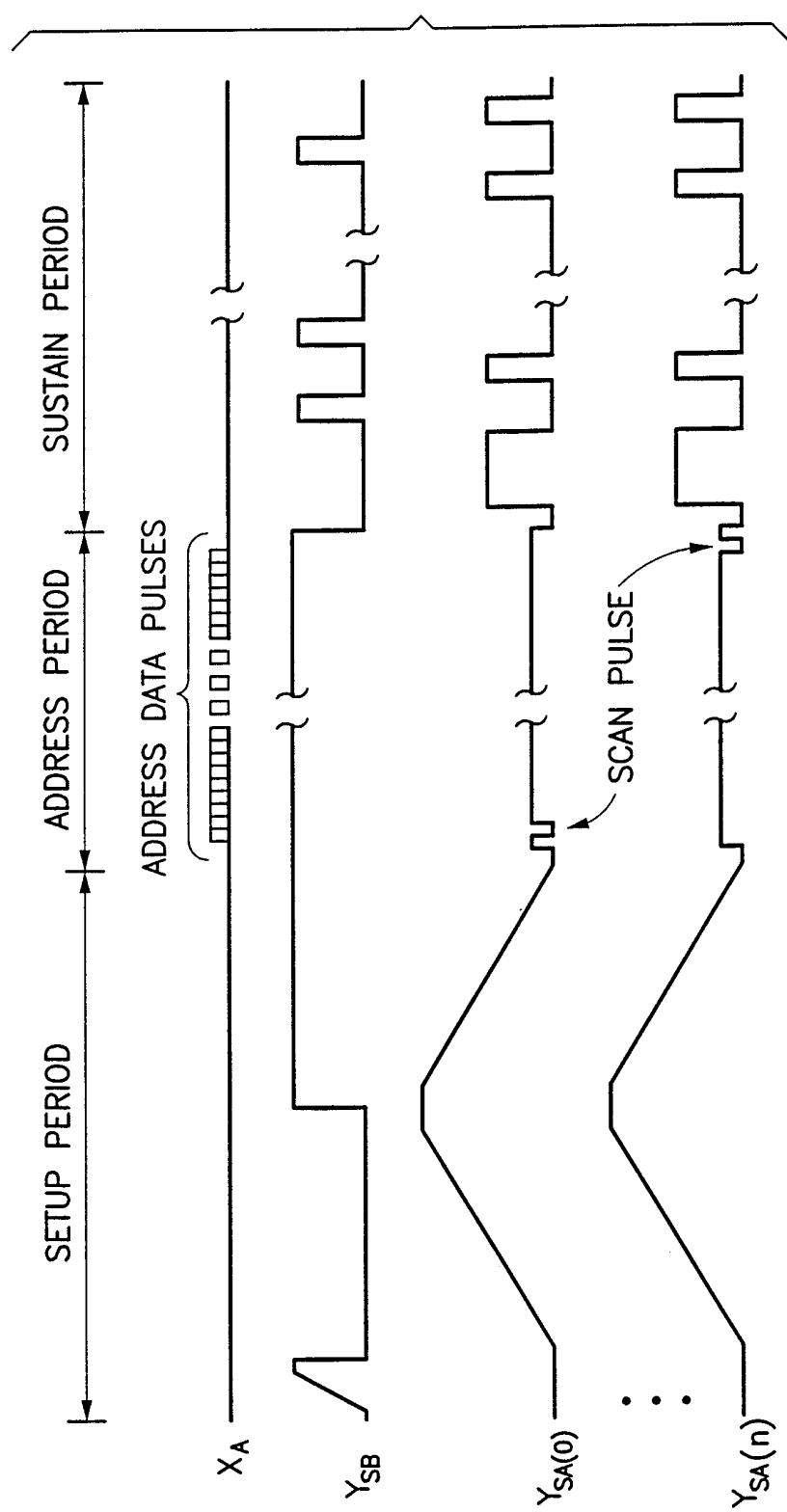

15 Figs 9a and 9b show prior art addressing and sustain waveforms.

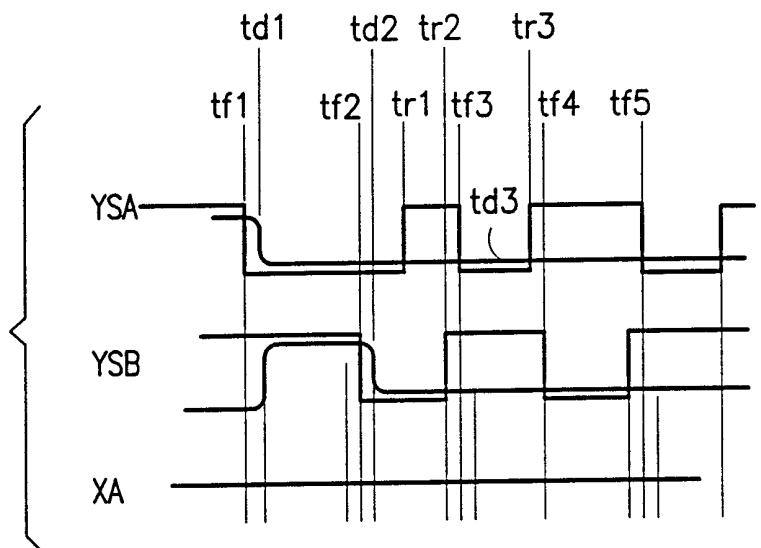

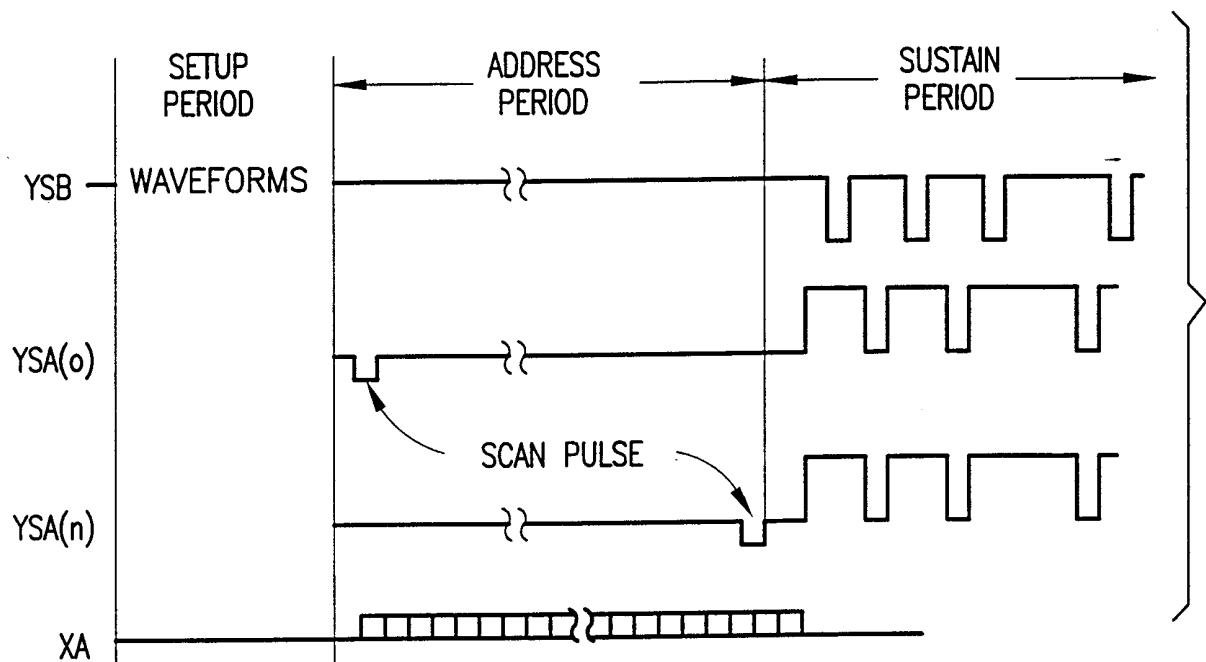

20 Fig. 10 shows a set of waveforms that have been found to be successful for addressing the subpixels using the principles of the invention.

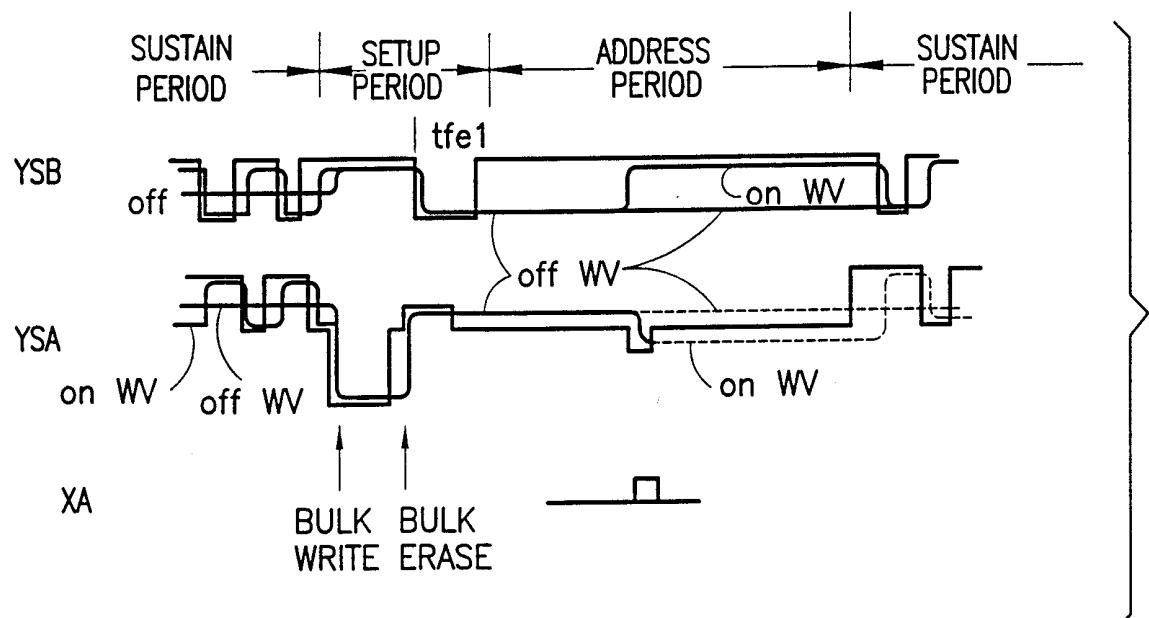

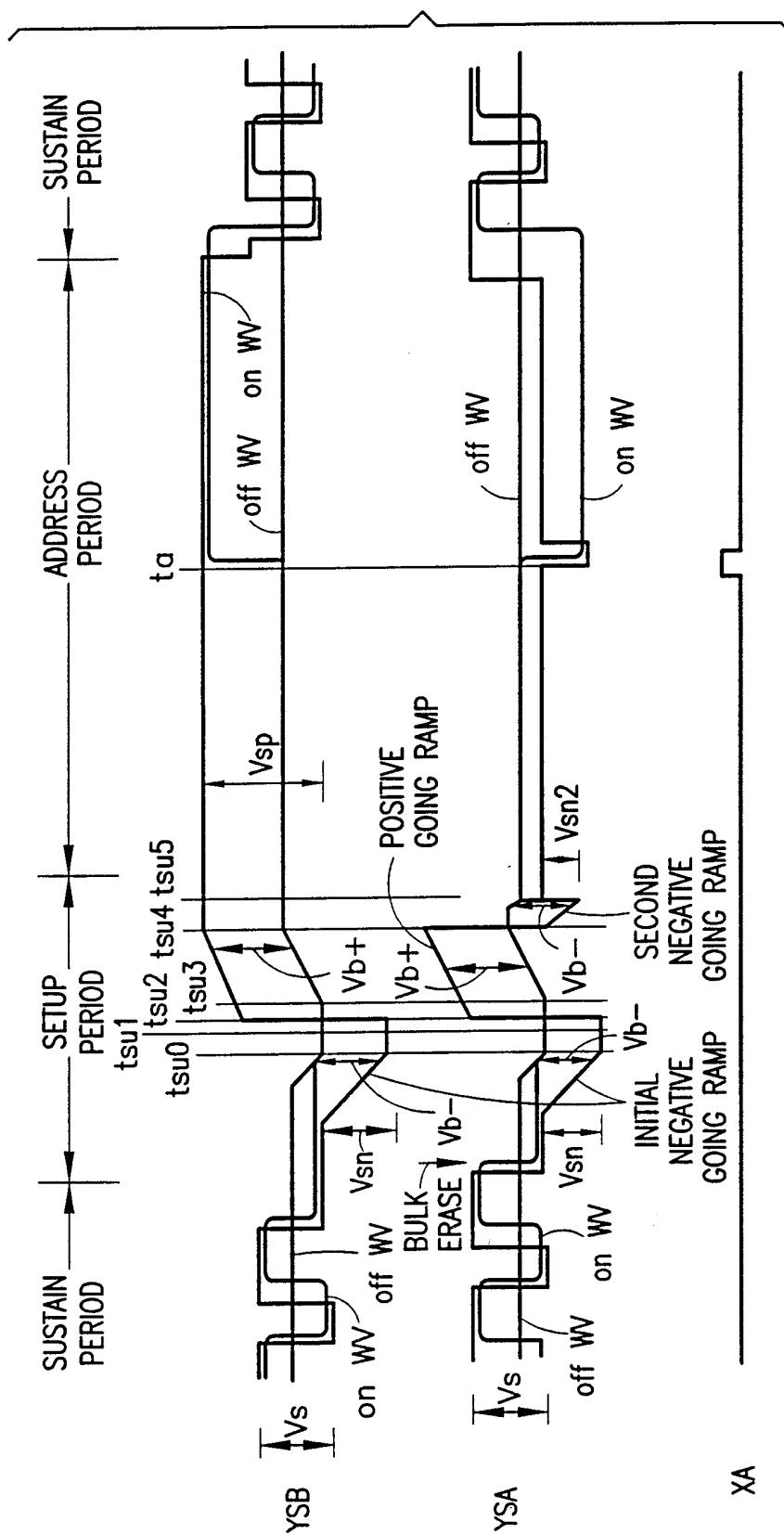

Fig. 11 shows details of pulse setup waveforms used with the invention.

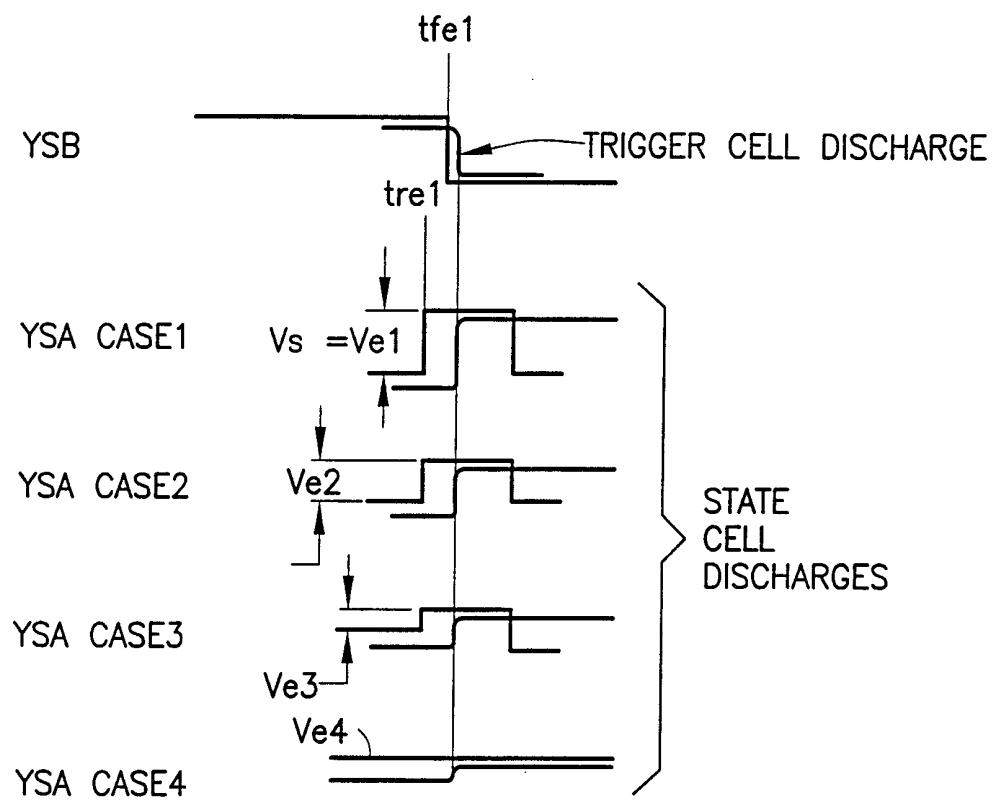

25 Fig. 12 shows a single erase pulse of possible amplitudes Ve1, Ve2, Ve3 or Ve4 that may be applied to the YSA sustain electrodes.

30 Fig. 13 illustrates prior art ramp setup waveforms.

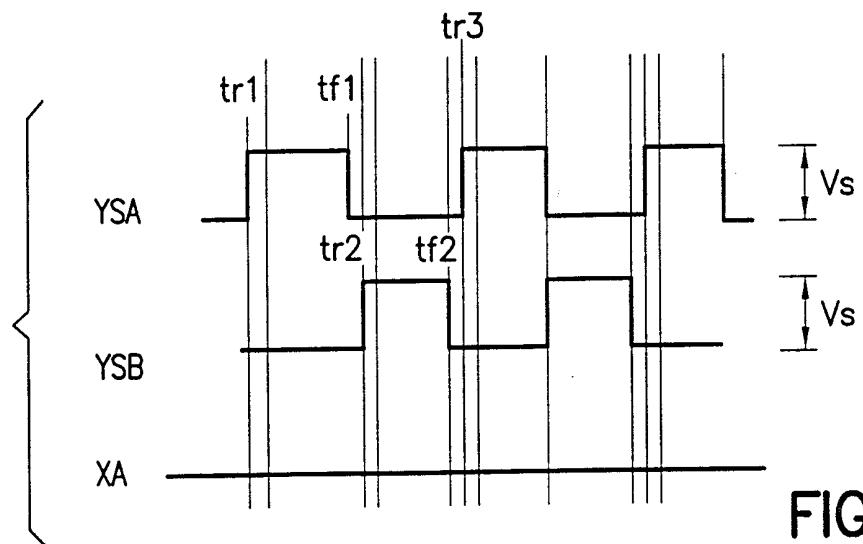

Fig. 14 illustrates a set of waveforms for operating the invention.

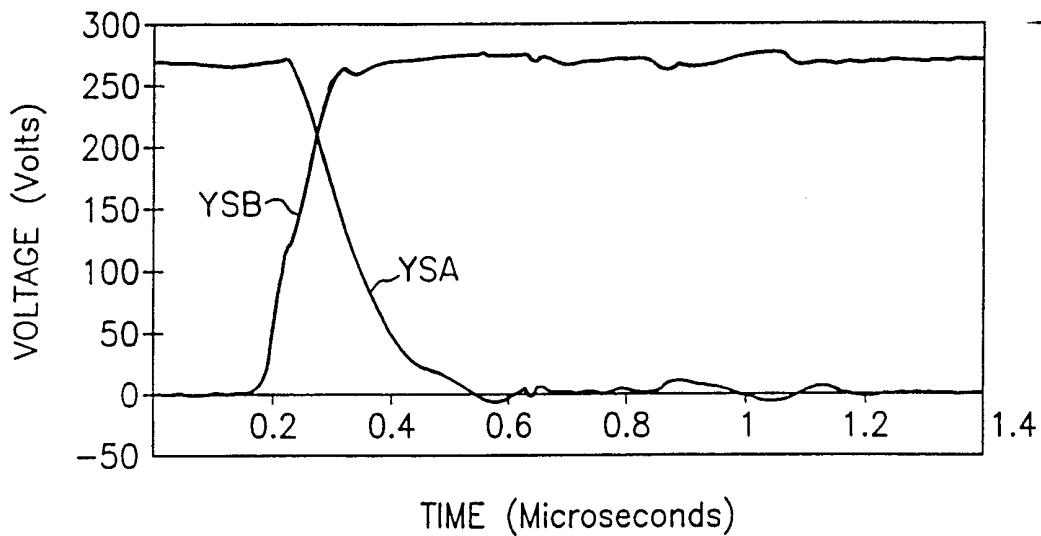

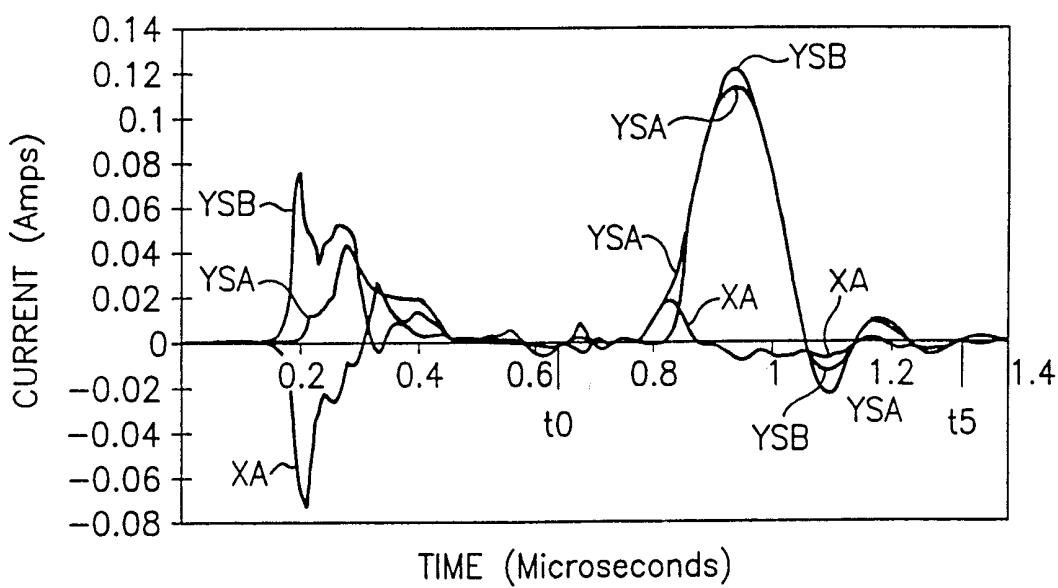

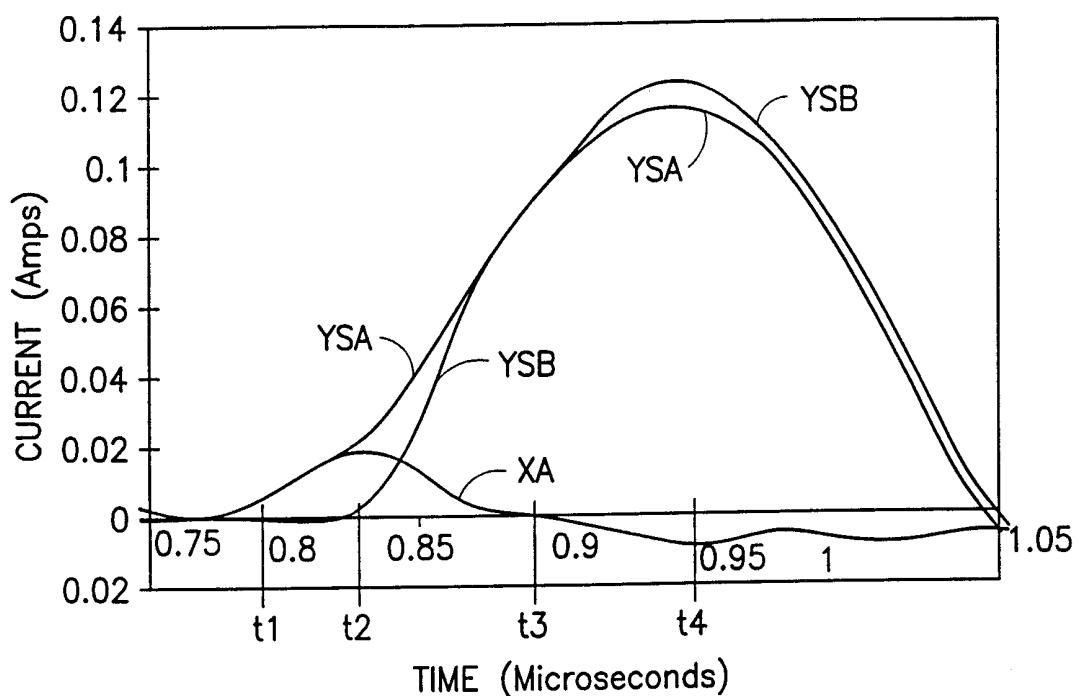

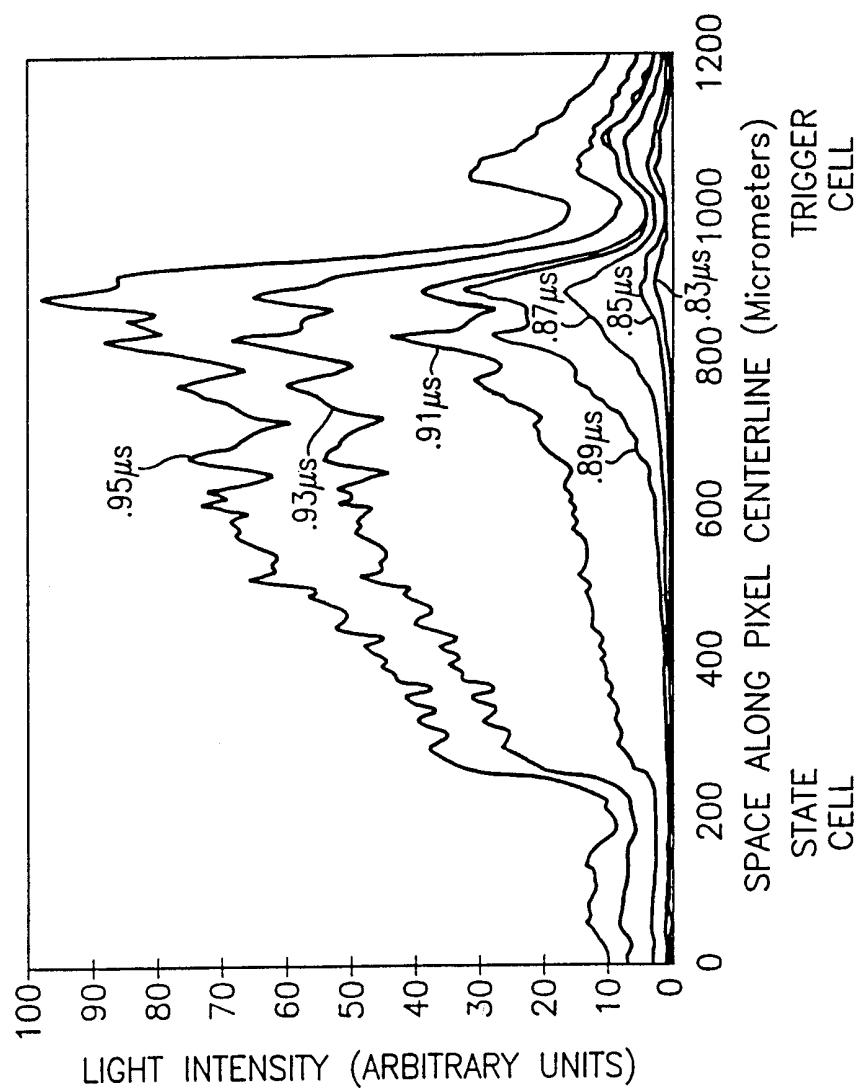

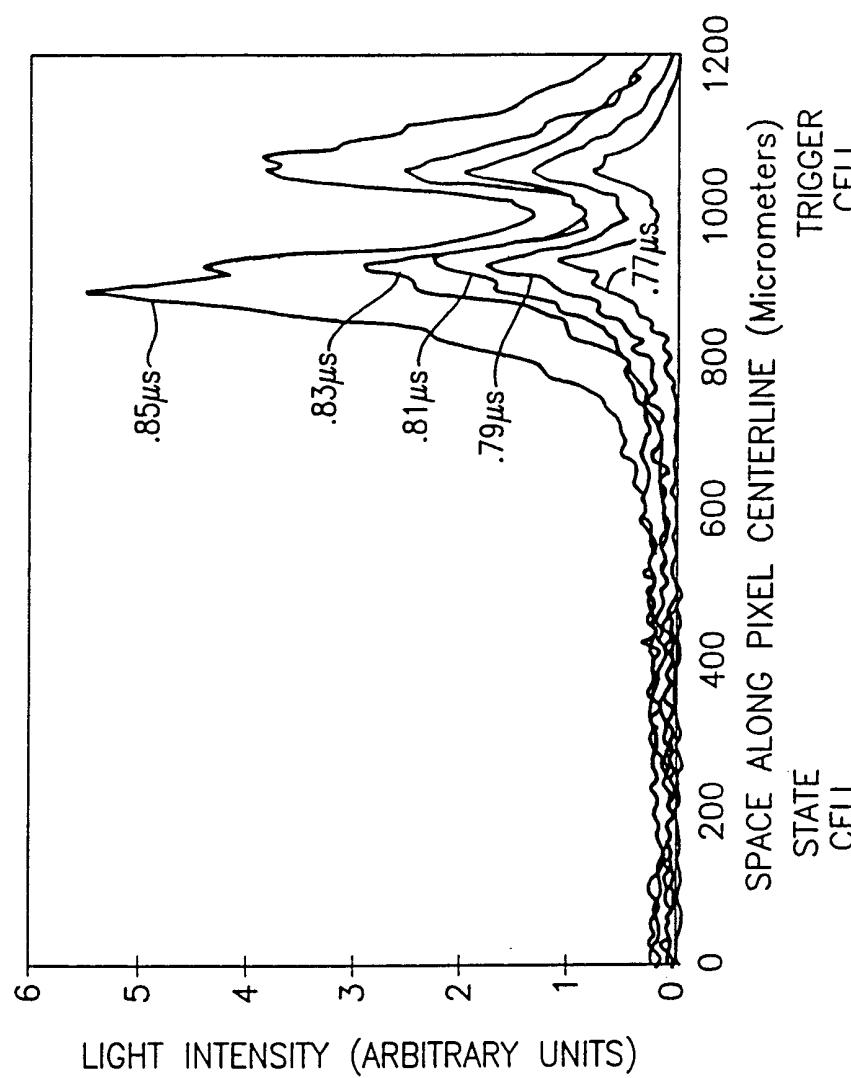

Figs. 15a-15c show actual measured sustain voltages

and currents for the address electrode, the trigger cell sustain electrode and the state cell sustain electrode in a PDP incorporating the invention hereof.

5 Figs. 16a and 16b show measured gas discharge light observed from a subpixel as a function of space and time during the discharge shown in Fig. 15.

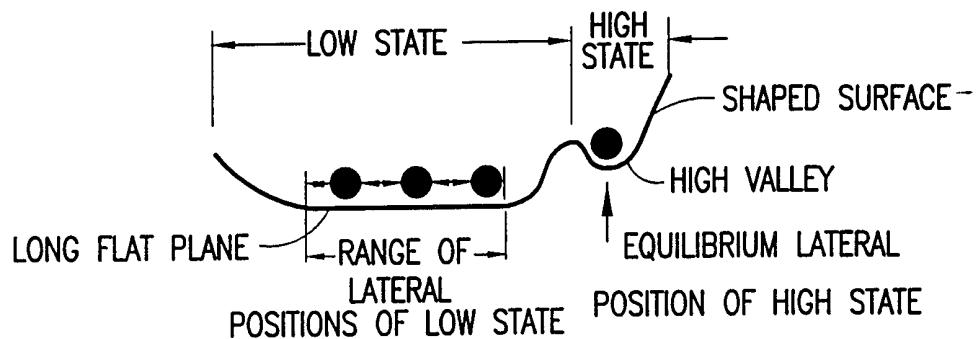

10 Fig. 17 shows an analogy of the stability of a typical plasma display subpixel.

Fig. 18 shows the same sustain waveforms that were shown in Fig. 6b and the allowed values of wall voltages for both ON and OFF states.

15 Fig. 19 shows an allowed choice of the OFF state wall voltage for the trigger cell and the state cell that is within the bounds described in Fig. 18.

20 DETAILED DESCRIPTION OF THE INVENTION

Initially, a high level description of the invention will be presented, followed by a detailed discussion of the theory of operation and a consideration of a number of design considerations that 25 are important to creating a high brightness PDP employing the invention hereof.

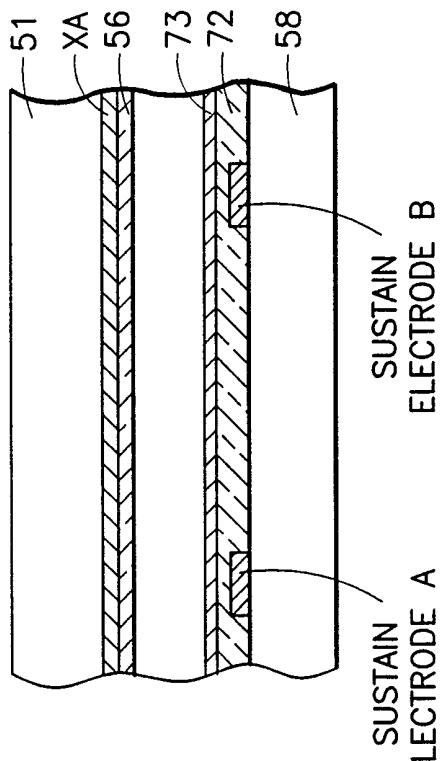

In Fig. 3, a schematic electrode layout is shown of a PDP 50 incorporating the invention. Fig 4 is a sectional view across subpixel 1 in Fig. 3. On an upper substrate 51, a plurality of single trace address electrodes 52 (X0 - Xn-1) are positioned and are driven, selectively, by an X address driver 53 during an address phase of operation. Address electrodes X0 - Xn-1 are separated by barrier ribs 54. Each address electrode is

covered by a dielectric/phosphor coating 56. On lower substrate 58 are positioned a plurality of sustain loops 60, 62, 64, etc., each of which comprises a pair of parallel trace electrodes, e.g., YSB0 and YSB1. All of 5 sustain loops 60, 62, 64, etc., are driven in common from sustain bus electrode 66, which is, in turn, connected to a sustain driver 68.

Interleaved between the sustain loops are pairs of 10 single trace scan electrodes, e.g., YSA1, YSA2, etc.. which are individually driven by a scan/sustain driver 70. Scan/sustain driver 70, during a sustain phase, applies sustain signals to each of scan electrodes YSA1, YSA2, . . . , which act as sustain electrodes during the 15 sustain phase. Scan/sustain driver 70, during an address phase, sequentially applies scan voltages to the scan electrodes in a raster scan manner. Each of the scan electrodes and sustain loop electrodes is covered by a dielectric coating 72 (Fig. 4) and, for example, an MgO overcoat 73. A dischargeable gas is maintained between 20 upper substrate 51 and lower substrate 58.

When appropriate sustain signals are applied to PDP 50, subpixel illumination selectively occurs between 25 adjoining scan and sustain electrodes (along intersecting address electrodes) by virtue of positive column discharges. The discharges at an ON subpixel "ping pong" between one discharge cell which exists at the intersection of a sustain electrode and an address electrode, and a second discharge cell which exists at a scan electrode and the address electrode.

30 A fundamental principle of operation of PDP 50 that makes the light from the positive column dominant over the negative glow light, is that the distance between each scan electrode and adjoining sustain electrode (sustain gap) is made as long as possible in order to

make the positive column as long as possible. This has the effect of increasing the power dissipated in the positive column relative to the power dissipated in the negative glow and thereby increases the relative light 5 emitted by the positive column. The techniques used to operate the invention enable the sustain gap to be much greater than the substrate gap SubG. In addition the techniques allow the SusG to be larger than the inter 10 pixel gap (IPG) without an exchange of the roles of these two gaps.

An electrode dimension design, while not necessarily optimum, has been found to operate according to the invention with a highly luminous positive column along the sustain gap in a practical AC PDP having a gas 15 mixture of 10% xenon and 90% neon with a gas pressure of 450 Torr and an MgO cathode material 73. The design has a pixel pitch of 1320 um which is appropriate for a 4:3 aspect ratio VGA color PDP having 640 by 480 pixels and a 42 inch diagonal. In this design the sustain 20 electrode width is 100 um, the sustain gap is 700 um and the inter pixel gap is 420 um. The substrate gap is 110 um.

It is always true that the sum of the sustain gap, the inter pixel gap and twice the sustain electrode 25 width is equal to the pixel pitch in the dimension perpendicular to the sustain electrodes. The dimensions of the aforesaid embodiment of PDP 50 are shown in Table 1 (Fig. 2d) under design INV. Clearly the design violates the conventional prior art design rules since 30 the sustain gap is 6.36 times larger than the substrate gap and in addition the sustain gap is 1.67 times greater than the inter pixel gap. Comparison of the Table 1 ratios SusG/SubG and SusG/IPG shows that the INV design is considerably different than the prior art

designs. Under prior art operating conditions, the INV design would not operate properly.

What follows below is a description of how to configure PDP 50 so that it can utilize subpixel dimensions similar to the INV design and still maintain acceptable plasma display sustaining and addressing operations and, in addition, generate most of the light - from the positive column.

First to be described will be how to operate with such a large ratio of 6.36 of the sustain gap to the substrate gap. This initial description will temporarily ignore the issue of interaction between neighboring subpixels, however this issue will be covered in further detail below.

The invention allows two independent sustain discharges to occur along the substrate gap, the first sustain discharge being between the first sustain electrode (i.e., the scan electrode) and the address electrode, and the second sustain discharge being between the second sustain electrode and the address electrode. It is to be noted here that the scan electrodes perform a scan function during the address phase and perform a sustain function during a sustain phase. During the address phase, the scan driver applies sequential scan voltages to the scan electrodes, whereas during the sustain phase, a sustain signal is applied, in common, to all of the scan electrodes, which accordingly operate as sustain electrodes.

The 700 um sustain gap is so large relative to the 110 um substrate gap that it is difficult to strike a discharge between the two sustain electrodes at a reasonably low voltage. However the substrate gap is only 110 um and therefore it is easy to strike a discharge at a reasonably low voltage between an address

electrode and a sustain electrode. The problem is that the sustain gap is so great that it initially appears difficult to set up a discharge along the sustain gap even though there are discharges between the sustain 5 electrodes and the address electrode along the substrate gap.

The sustain operation results in each subpixel being divided into two seemingly independent cells, one cell defined by the intersection of a first sustain 10 electrode and the address electrode and the second cell defined by the intersection of the second sustain electrode and the address electrode. It is a fundamental teaching of this invention of a technique that allows strong conductivity between these two 15 seemingly independent plasma display cells.

To discuss this sustain technique further, it is desirable to re-name the two cells discussed above. Hereafter, the cell that initiates the discharge will be named the trigger cell and the cell to which (i) the 20 positive column extends and (ii) stores the pixel state, will be named the state cell. Hereafter the term scan electrode will only be used during an address phase of operation of the invention.

The fundamental principle is to operate the trigger 25 cell in such a manner that when an appropriate discharge is initiated therein, a highly ionized positive column will emanate out therefrom and will move along the sustain gap (and the spanning address electrode) until it intersects with the state cell. This highly ionized 30 positive column then forms a conductive channel between the trigger cell and the state cell which acts to discharge the wall charges on both the trigger cell and the state cell.

When the highly conductive channel forms and

discharges the wall voltages on the dielectrics at the

trigger and state cells, a highly luminous positive

column discharge is formed that has greater luminance

5 than the negative glow. The details of how this is

accomplished will be discussed below.

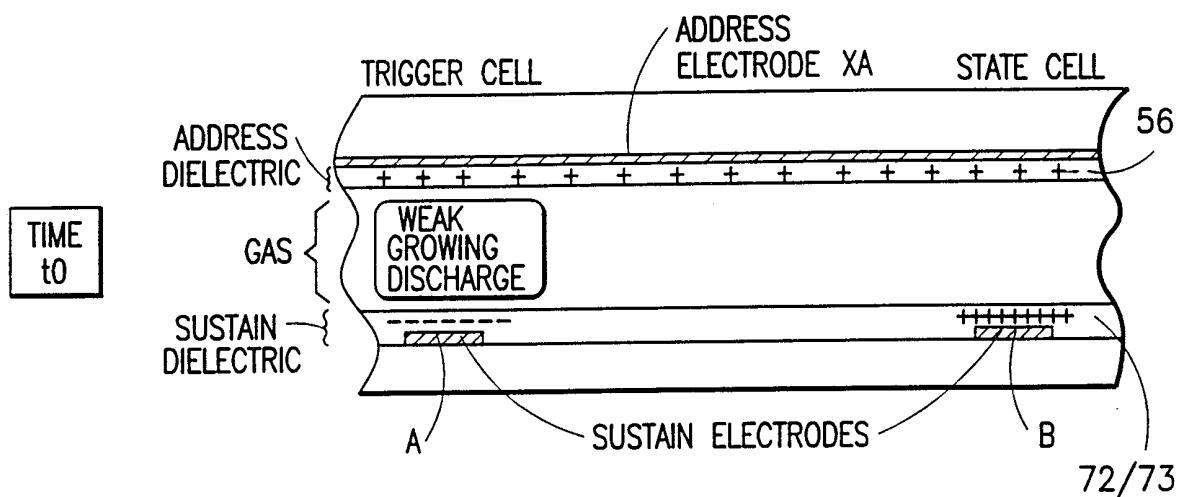

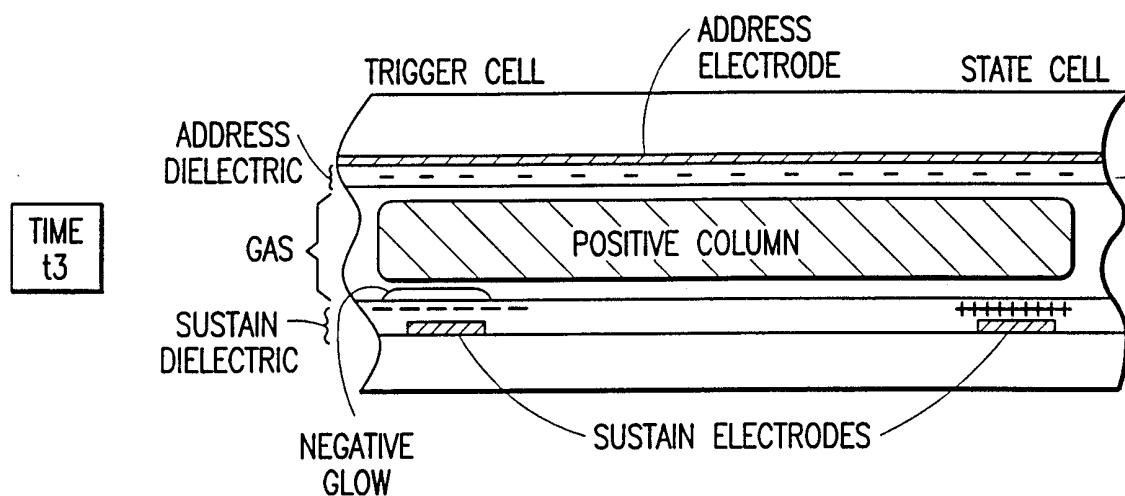

Figs. 5a-5f are a time sequence illustrating the

above described operation. To examine the trigger cell

discharge, assume a negative going pulse is applied to

10 the trigger cell sustain electrode A so that it

initiates a trigger cell discharge across the substrate

gap, while the sustain electrode A acts as the cathode

with respect to address electrode XA. Further assume

that the initial voltage across the trigger cell

15 substrate gap is at least 250 volts. Under such

conditions, a highly conductive positive column can

occur that emanates from the trigger cell to the state

cell.

At time  $t_0$  (Fig. 5a), the voltage across the

20 substrate gap is high and the discharge is growing in

intensity, but has not yet reached a level of intensity

that results in any significant field distortion and it

has not significantly altered the initial wall charge

distribution on any of the dielectric surfaces. At time

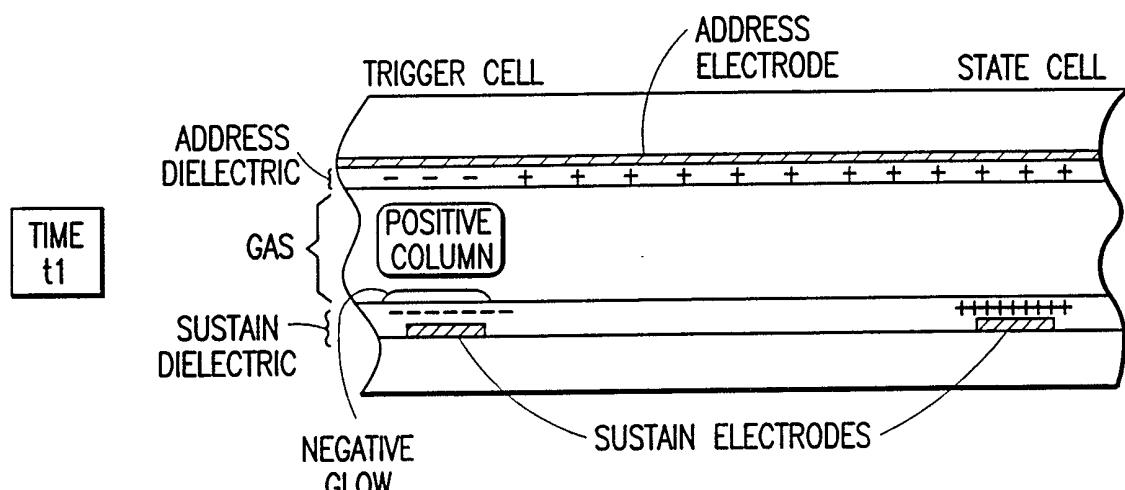

25  $t_1$  (Fig. 5b), the discharge has reached a level of

intensity that field distortion has created a highly

conductive plasma region near the trigger cell address

electrode XA (acting as the anode). This plasma region

is the positive column. Near the trigger cell sustain

30 electrode (acting as the cathode) is the negative glow

region that has a high electric field and a very high

ion density but a relatively low electron density. This

highly conductive discharge and field distortion

discharges the dielectric capacitors over both sustain

electrode A and address electrode XA of the trigger cell.

In most color plasma displays the dielectric covering the address electrode comprises a phosphor 5 layer that is usually a powder with a low density. Such a low density powder usually has a low relative dielectric constant, causing the capacitance of the dielectric layer covering the address electrode to be considerably less than the capacitance of the dielectric 10 layer covering the sustain electrode. Because of these differences in capacitances, when a discharge current flows through the two capacitors, the voltage across the address electrode dielectric 56 will change much more quickly than that across sustain dielectric 15 (including MgO layer 73).

As the current from the trigger cell discharge flows onto address dielectric 56, the dielectric surface becomes more and more negative. This is shown as negative charges on the trigger cell address dielectric 20 56 at time t1 (Fig. 5b). Note that the trigger cell address electrode dielectric 56 charge distribution changes considerably between times t0 and t1, whereas the charge distribution for the trigger cell sustain dielectric 72 has not changed at all between these 25 times. This signifies that, even though the same amount of charge has flowed through these two dielectrics, the voltage of address electrode dielectric 56 has changed much more because it has a much lower capacitance than the sustain electrode dielectric 72.

30 At some point during the trigger cell discharge the voltage on the address electrode dielectric 56 becomes so negative that the regions of dielectric 56 along address electrode XA further away from the center of the trigger cell will have a more positive potential than

the regions in the center of the trigger cell. Electrons from the highly conductive plasma very quickly move to these regions of more positive potential and effectively couple the energy stored in the capacitance of the 5 extended dielectric 56 into the discharge.

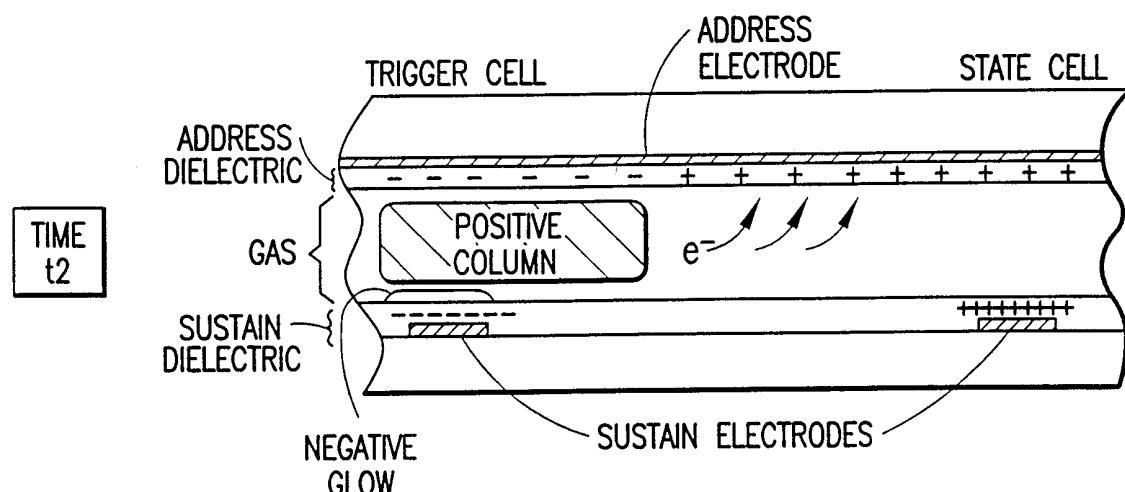

Fig. 5c (time t2) shows how the positive column has extended itself away from the center of the trigger cell - and is discharging this extended region further. Note that as the positive column extends from the center of 10 the trigger cell, the regions of address electrode dielectric 56 in contact with the positive column become negatively charged whereas those regions not yet contacted by the positive column remain positively charged.

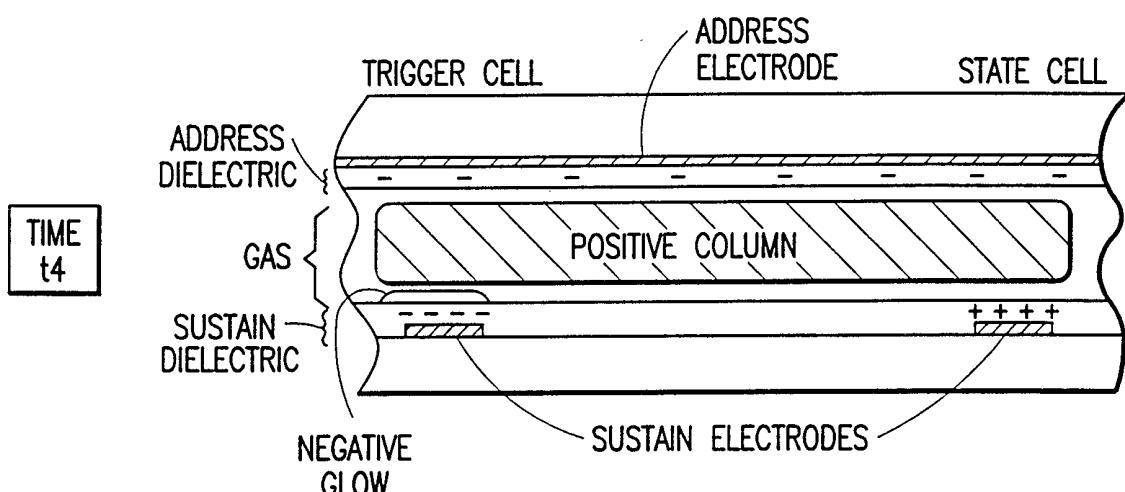

15 At time t3 (Fig. 5d), the positive column from the trigger cell discharge has reached the state cell and the electrons from the positive column flow to the positive potential of dielectric 72 covering the state cell sustain electrode B. Dielectric 72 has a 20 dielectric constant considerably higher than the dielectric constant of address electrode dielectric 56, allowing considerably more charge to flow into the state cell sustain dielectric 72 before its potential changes significantly.

25 With the highly conductive positive column bridging the sustain gap at time t3, the current between sustain electrodes A and B begins to rise to very high levels and most of the energy stored in the sustain electrode dielectric capacitance of both the state cell and the 30 trigger cell is deposited into the electron energy of the positive column. The positive column forms a highly luminous filament that bridges the sustain gap. This filament grows in intensity until it reaches a peak at time t4 (Fig. 5e).

At this point the charge deposited by the discharge on dielectric 72 covering sustain electrode B has risen to a sufficiently large level that the voltage across the positive column is reduced to a low level and to a 5 point where the light generation rate peaks and then begins to decrease. Compare the trigger cell and state cell dielectric wall charge distributions for times t3 and t4 (Fig. 5e) and note that the state cell sustain dielectric 72 has less positive charge at time t4 and 10 also note that the trigger cell sustain dielectric 72 has less negative charge at time t4. Also note that address electrode dielectric 56 has less negative charge at time t4 compared to t3.

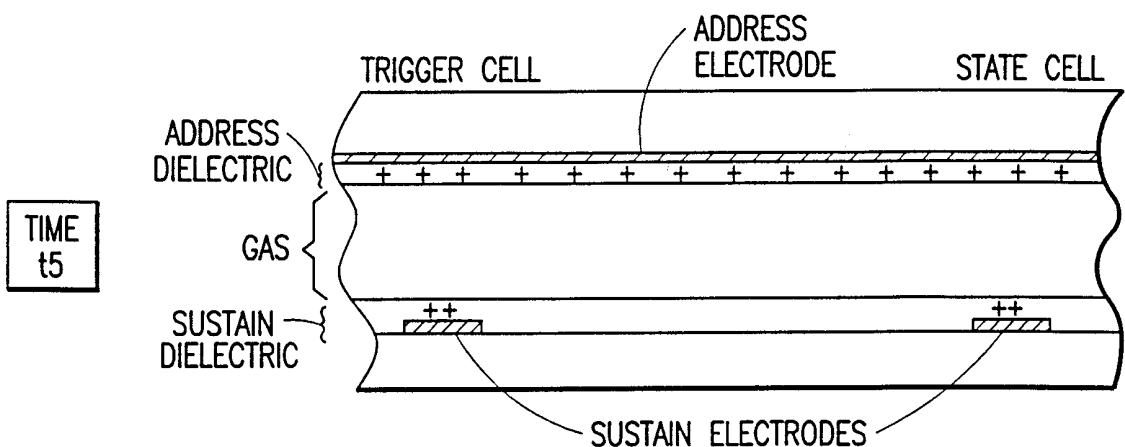

After the peak at time t4, the discharge continues 15 to decay in intensity until at time t5 (Fig. 5f), the discharge current no longer flows. At this point the space charges created in the gas volume have flowed to all of the dielectric surfaces. If the initial voltage across the gas volume is high enough so that a 20 sufficiently strong discharge occurs, then there is sufficient available space charge to substantially reduce the voltage across the gas to zero volts for nearly all regions of the subpixel. This means that nearly all dielectric surfaces at time t5 will be at one 25 potential.

That fact is important for analysis of the 30 subsequent discharges. The single potential of all dielectric surfaces at time t5 is signified in Fig. 5f by the equal density of positive charges on all dielectric surfaces.

#### **Isolation Bars**

Fig. 3a shows a second embodiment of the electrode layout of Fig. 3 wherein conductive isolation bars 99

have been placed within each inter pixel gap IPG. Since the electrode topology of Fig. 3 has a larger sustain gap than inter pixel gap, it is desirable to provide an isolation means which restricts the 5 spreading of positive column discharges across inter pixel gaps. Such a means is provided by conductive isolation bars 99.

Figs. 5a-5f show how the positive column moves along the sustain gap between the trigger cell and the 10 state cell. In this figure the positive column moves from left to right. It is important to consider why the positive column moves to the right in this case and why it does not move to the left. If it were to move to the left then it could move across the inter-pixel 15 gap which could cause an undesirable interaction with a neighboring pixel which could errantly change the state of the neighboring pixel. Another important consideration is why does the positive column stop once it has reached the state cell or in other words, why 20 does the positive column not continue its spread past the state cell across the inter pixel gap and on to the large positive charge of the neighboring state cell. An additional problem with the positive column 25 extending across either the left or the right inter pixel gap is the large amount of undesirable light generated between the pixels.

Fig. 3b shows a cross section of three pixels of the plasma panel with the electrodes of figure 3a. Figure 3b also shows the initial charge distribution on 30 the dielectric layers at the time  $t_0$  which is the same time as shown in figure 5a. In pixel 2 of figure 3b the positive column moves from the trigger cell to the state cell in the exact way shown in figure 5. This movement occurs because the electrons from the leading

edge of the positive column are attracted to the positive charge along the dielectric covering the address electrode as shown in Fig. 5c. Since the address electrode dielectric to the right of the Fig.

5 3b, pixel 2 trigger cell is positive, the pixel 2 positive column will move to the right. Note that the address electrode dielectric to the left of the pixel 2 - trigger cell is negative. This will repel the positive column electrons and therefore inhibit the growth of

10 the positive column to the left of the pixel 2 trigger cell.

Once the pixel 2 positive column reaches the state cell, it does not continue to move to the right to the positive charge of the pixel 3 state cell because of

15 the negative charge on the dielectric covering the address electrode in the inter pixel gap between the pixel 2 state cell and the pixel 3 state cell.

It is therefore the presence of the negative charge along the dielectric in the inter pixel gap that

20 inhibits the positive column from moving across the inter pixel gap and causing errant neighboring addressing and discharge light. It is important to take measures to insure that this negative charge exists.

25 Dielectric surfaces that are near gas discharges have a well known characteristic that the dielectric regions farther from the main discharge activity charge up more negatively than those regions in close contact with the discharge. This phenomenon is fundamentally

30 caused by the different velocities of the electrons and the ions in the gas. Because of the relative masses of these charged particles the electrons have approximately 100 times the velocity of the ions in a gas discharge. This means that electrons will fly out

of the discharge 100 times faster than the ions. When the initial electrons fly out they will charge the dielectric surface negatively and set up a negative potential that will repel the electrons. This negative potential will attract the positive ions.

5 As the sustain discharges continue, this negative potential continues to grow until an equilibrium potential is reached. The equilibrium potential is determined by the condition that an equal number of 10 ions and electrons flow to the surface. This equilibrium potential will repel the high velocity electrons and attract the low velocity positive ions so that the ion currents and the electron currents are equal. This equal ion and electron current condition 15 will result in a zero sum of these opposite polarity currents. If the sum of the currents is zero, then there is no net charge flowing to the dielectric surface and the potential will stop changing. This stable potential is defined as the equilibrium 20 potential.

The condition for establishing the negative charge in the inter pixel gap is that there be no significant discharge activity in the inter pixel gap. The sustain discharges will then establish the negative charges in 25 the inter pixel gaps as shown in figure 3b by the mechanism discussed in the previous paragraph.

The purpose of the isolation bar 99 is to insure that there is no significant discharge activity in the inter pixel gap so that the negative charge can 30 accumulate there. It is convenient to make the isolation bar with the same material and process as the front plate sustain electrodes. In this way the isolation bar is simply defined by a simple front plate electrode mask change. Figure 3a shows that the

isolation bars 99 are not directly electrically connected to any other electrodes, but are left floating. This means that the potential on the shorting bars will be determined by the capacitive coupling between the isolation bars and the other electrodes in the plasma panel. Figure 3b shows the coupling capacitors, C1 through C5, for the isolation bar between pixels 1 and 2. If a pulse is applied to the electrodes A in figure 3b, a fixed percentage of that pulse will also appear on isolation bar 99. The value of this fixed percentage is determined by the pixel geometry's and materials dielectric properties.

The exact value of this percentage is determined by the capacitive divider comprised of the parallel combination of C1 and C2 with the series combination of C3, C4 and C5 shown in figure 3b. The magnitudes of capacitors C1 and C2 will be relatively large because they are formed in the glass layers of the front substrate glass and the dielectric glass which have high relative dielectric constants. The magnitude of the series combination of C3, C4 and C5 will be relatively low since series combinations of capacitors are always smaller than the smallest capacitor which in this case is C3. Since C3 is across the gas which has the lowest possible relative dielectric constant of 1, C3 will have a relatively low value compared to C1 and C2 which have the much higher glass relative dielectric constants which typically range from 7 to 15. This means that the fixed percentage of the pulse amplitude applied to the A sustain electrode that appears on isolation bar 99 is considerably greater than 50% but less than 100%. The exact value of this fixed percentage depends on the exact pixel geometry and materials relative dielectric constants.

While the above analysis was made for sustain pulses applied to the A sustain electrodes, the exact same results also occur if the sustain pulse is applied to the B sustain electrodes of figure 3b. This is 5 because of the symmetry of the A and B sustain electrodes shown in figure 3b.

The value of this fixed percentage is important - for the proper operation of the isolation bar. As stated above it is necessary for there to be no 10 significant discharge activity in the inter pixel gap.

Since the isolation bar is very similar to the sustain electrodes, if the voltage pulses on the isolation bars are too high then an undesirable sustain discharge could occur to the isolation bar. It is therefore 15 necessary to design the plasma display materials, electrode geometry's and sustain pulse amplitudes in such a way that when the sustain pulses are applied to the normal sustain electrodes that the fixed percentage discussed above is sufficiently low so that the pulsed 20 potential that results on the isolation bar is below the voltage at which the sustain discharges can occur on the isolation bar. This minimum sustain voltage measured on the isolation bar is designated Vsminib.

As long as the pulsed voltage on the isolation bar 25 is below Vsminib, there will be no significant discharge activity along the isolation bar and therefore there will be no significant discharge activity in the inter pixel gaps. This will allow the negative charge to build up in the inter-pixel gap 30 which will repel the movement of the positive column across the inter pixel gap. This will eliminate the undesirable errant discharges to neighboring pixels or undesirable inter-pixel light.

When the isolation bar pulsed potential remains below Vsminib, the isolation bar has the desired effect of acting like a shield for the electric fields from the sustain electrodes that extend into the inter pixel gap. It acts like this shield primarily because of the negative charge on the dielectric layers shown in the inter pixel gap of figure 3b that accumulates due to lack of discharge activity.

U. S. patent 3,666,981 to Lay documents the usage of electrostatic isolation bars to prevent discharges from spreading out to neighboring cells on dual substrate monochrome PDPs. In the Lay electrode topology, the isolation bars are placed between every sustain electrode on both the front and the back substrates. In the invention presented here, the isolation bars are placed on only one substrate and only between every other sustain electrode. More specifically, this invention requires that the isolation bars be placed between only the sustain electrodes that are at the same potential during the sustain operation. This is shown in figures 3a and 3b.

Note in figure 3b that one isolation bar is between the two A sustain electrodes and another isolation bar is between the two B sustain electrodes. At any given time in the sustain period, both A sustain electrodes are at the same potential and both B sustain electrodes are at the same sustain potential. The potential on the A electrodes is frequently different than the potential on the B electrodes.

This invention would not work properly if the isolation bars were placed between sustain electrodes that are at a different potential during the sustain period. For instance if isolation bars were placed between the A and B electrodes of Fig. 3b there would

be very significant problems. First of all the region between the sustain electrodes A and B is across the sustain gap which is where the main discharge of the panel occurs. Isolation bars in the region of the 5 sustain gap will of course have the undesirable property of blocking the most significant light emission of the panel. In addition the placement of the isolation bars in the sustain gap would interfere with the electric field in the sustain gap and would 10 also possibly interfere with the movement of the positive column from the trigger cell to the state cell.

In addition the pulsed potential that appears on an isolation bar placed between the A and B electrodes 15 will be much different compared to the pulsed potential of isolation bars placed between two sustain electrodes that are always at the same potential during the sustain period. Since the A and B sustain electrodes are frequently at different potentials during the 20 sustain waveform the isolation bar between the A and B electrodes would float to a lower potential when a sustain pulse is applied to either sustain electrode than the potential of an isolation bar placed between pulsed equipotential sustain electrodes. The reason 25 for this is a differing capacitive divider ratio for the two different cases. For the case of the isolation bar between the A and B electrodes, the isolation bar will be pulsed to less than 50% of the amplitude of the pulse applied to either sustain electrode. For the 30 geometry required by this invention where the isolation bar is between sustain electrodes of equal potential, the isolation bar will be pulsed to significantly greater than 50% of the pulse amplitude applied to the sustain electrodes.

Another problem with placing the isolation bars between the A and B sustain electrodes is the significant increase in capacitance between the A and B sustain electrodes. When the isolation bars are placed 5 between the sustain electrodes of equal potential according to the principles of this invention, there is a minimal increase in the capacitance between the A and B sustain electrodes. This significantly reduced capacitance will significantly reduce the power 10 dissipated in the circuits that must drive the panel capacitance.

Using the electrode topology shown in Fig. 3a, a PDP has been successfully operated where the inter pixel gap was set to be approximately equal to the 15 sustain gap, isolation bars 99 were centered in the inter pixel gaps and the width of each isolation bar 99 was approximately 50% to 80% of the inter pixel gap.

#### Sustain Waveform Considerations

20 Applying a sufficiently large negative going sustain pulse to the trigger cell sustain electrode allows a strong discharge to occur between the trigger cell sustain electrode and the state cell sustain electrode, even though these electrodes have a sustain 25 gap of 700 um and a substrate gap of only 110 um. The extension of the positive column along the address electrode serves as an effective means of coupling the seemingly distant trigger cell and state cell.

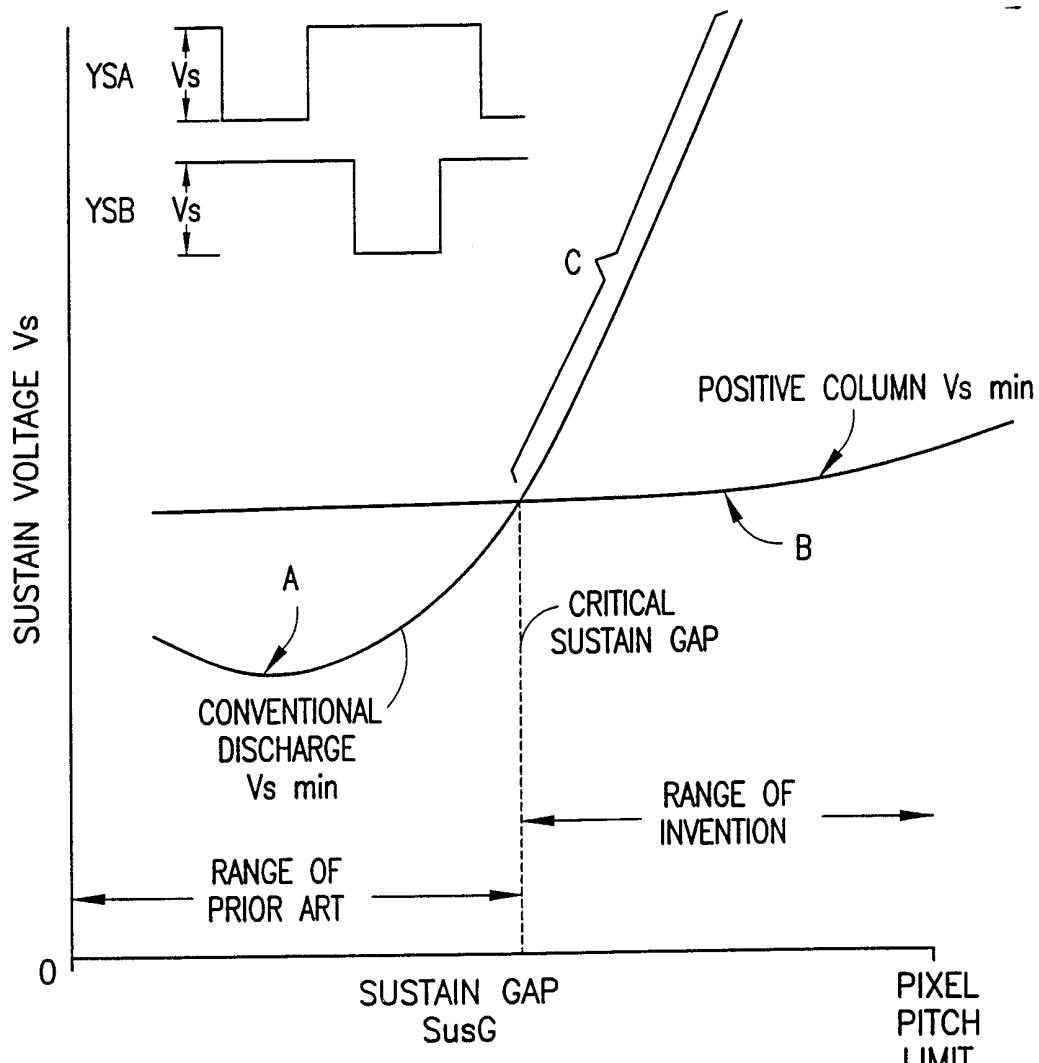

Referring to Fig. 6a, it will be understood that, 30 due to the large sustain gap used by the invention, the invention departs from a common relationship of voltages used in the prior art. Curve A is similar to the classic U shaped gas discharge Paschen curve and defines how the minimum sustain voltage required by the

prior art to just sustain a cell discharge between the two sustain electrodes (i.e.,  $V_{smin}$ ) behaves as the sustain gap is varied.

For operation on the right side of the U, as the 5 sustain gap increases, the  $V_{smin}$  voltage increases because the electric field decreases due to the larger sustain gap distance which causes fewer ionizations per - volt. For operation on the left side of the U, as the 10 sustain gap is reduced, the  $V_{smin}$  voltage increases because there are fewer electron collisions with gas atoms which causes fewer ionizations per volt.

In prior art AC PDPs, due to their small sustain 15 gaps,  $V_{smin}$  was relatively low and sustain voltages were employed that substantially exceeded  $V_{smin}$ . By contrast, due to the large sustain gap of the invention, operation on the far right side of curve A applies and so  $V_{smin}$  is substantially larger. This allows a practical sustain operation with another 20 discharge mode that is illustrated by curve B. Curve B is defined as the minimum sustain voltage required to achieve a sufficiently strong discharge at a trigger cell, initially having an ON state wall voltage, which creates a positive column that travels to an adjacent state cell so as to successfully establish the state 25 cell wall voltage to the ON state.

Note that curve B is much more weakly dependent on the sustain gap than is curve A. This is primarily because the initiation voltage of the curve B trigger cell discharge should be independent of the sustain gap 30 since the trigger cell discharge initially occurs across the substrate gap and not the sustain gap, as does the curve A discharge. The curve B voltage increases only slightly with sustain gap because the trigger cell discharge must increase in strength

slightly for the positive column to extend to the state cell for the longer sustain gaps.

The distinctly different shapes of curves A and B allow sustain operation according to the invention for 5 sustain gaps larger than the intersection point of the two curves (i.e., the critical sustain gap). Use of the larger gaps allows operation below the Vsmin of curve A (i.e., portion C of curve A), yet at a sustain voltage above curve B so that the invention discharge mode will successfully sustain the sub-pixels.

For sustain gaps larger than the intersection point, the prior art discharge between the two sustain electrodes, as defined by portion C of curve A, will not occur because the curve B discharge of the 15 invention will occur at a lower sustain voltage and therefore will discharge to change the wall voltage before the higher voltage prior art discharge has time to form.

Electrode waveforms will hereafter be described 20 that allow a stable sequence of plasma display subpixel discharges and allow a subpixel to be in either the ON state or the OFF state. These waveforms and conditions are necessary in order to achieve inherent memory in the AC PDP display subpixels.

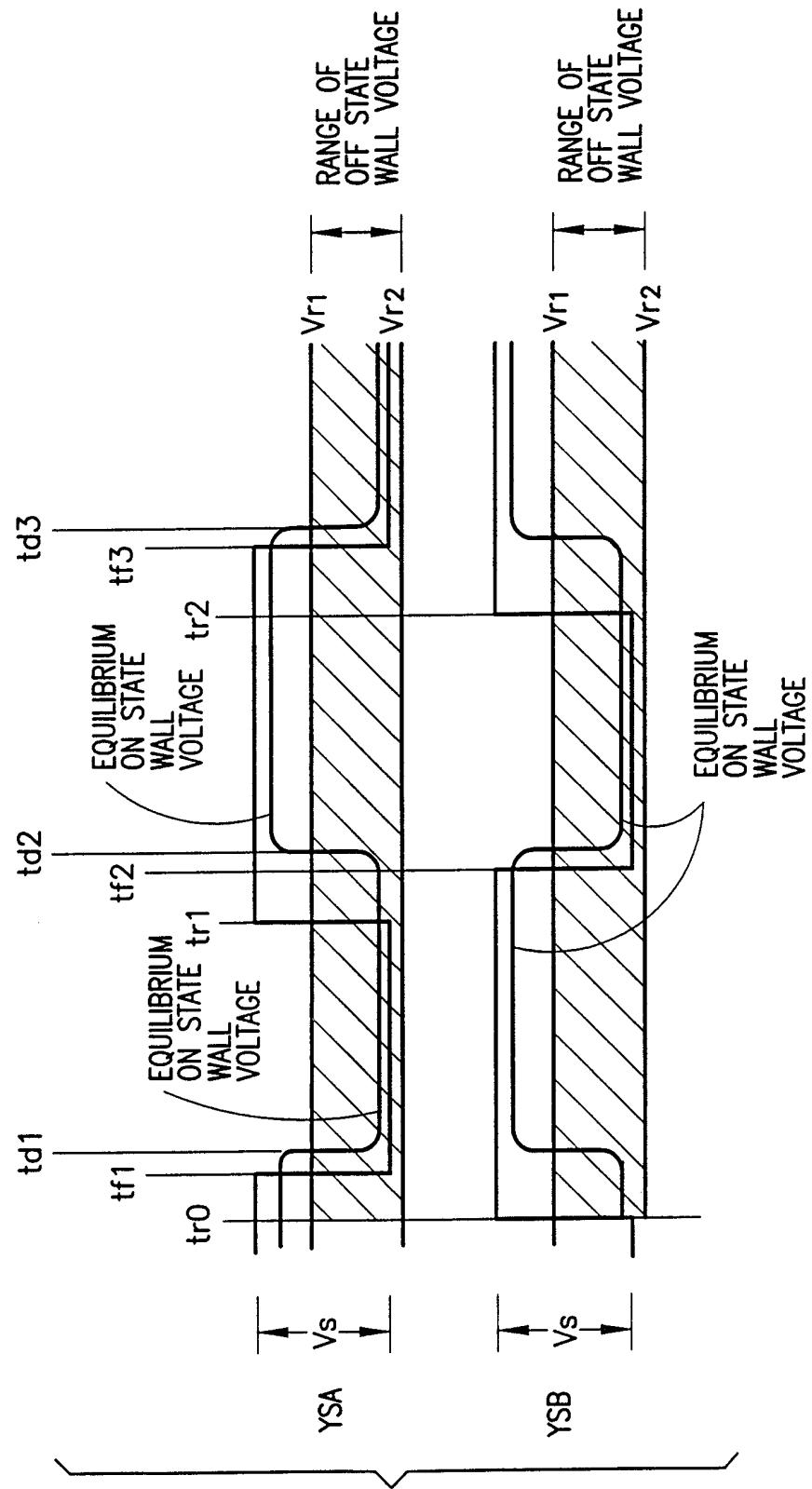

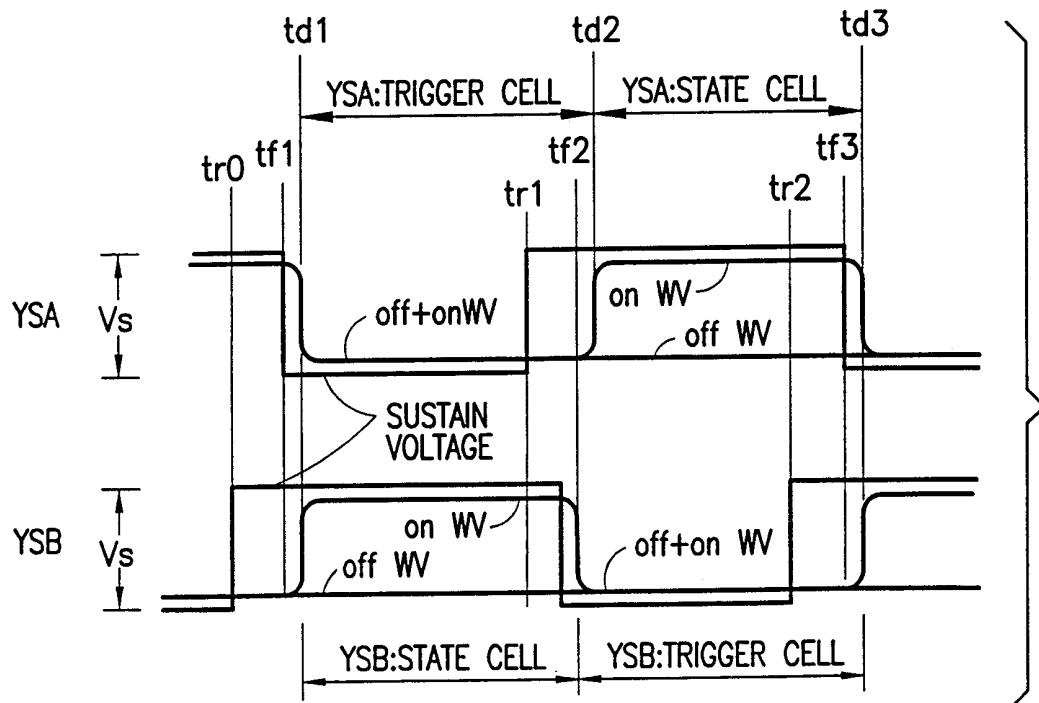

25 Fig. 6b shows one set of sustain waveforms that has been found to work well and that allow the subpixels to be in either the on state or the off state. Also shown in Fig. 6b are the wall voltage levels for both the on state and the off state. The 30 wall voltage drawn for a given sustain electrode occurs due to charge on the dielectric covering the given sustain electrode and the charge on the address electrode dielectric that intersects the given sustain electrode. All wall voltages are drawn with a polarity

such that the voltage across the substrate gap can be determined by subtracting the wall voltage from the sustain voltage. The two sustain electrodes in a subpixel are designated to be either YSA (the scan electrode during the address phase) or YSB and the address electrode is designated XA. Fig. 6b shows five sustain discharges which are labeled td1 through td5. - Sustain pulses with amplitudes Vs are sequentially applied as shown in Fig. 6b.

Referring to the cell structures of Fig. 3, Fig. 5 and the waveforms of Fig. 6b, at tf1 the YSA sustain electrode falls and creates a discharge at td1 between the YSA sustain electrode and the address electrode XA. At time td1, all of the YSA sustain electrodes intersect trigger cells and initiate a trigger discharge with the address electrode similar to that shown in Fig. 5. Each trigger discharge initiated in a trigger cell generates a positive column that moves from the trigger cell along the address electrode to the state cell.

At time td1 all of the YSB sustain electrodes intersect state cells. Note, that at time td1 the wall voltage of the YSB electrodes rises even though there is no sustain pulse applied to the YSB sustain electrode. This is the action of the positive column extending from the trigger cell to the state cell that intersects with the YSB sustain electrode. The positive column discharge causes a change of the wall voltage of both the state cell and the trigger cell.

At time td2 there is another discharge that is initiated by the fall of sustain electrode YSB at time tf2. At this time all of the trigger cells intersect sustain electrode YSB and the resulting trigger discharge causes the positive column to extend to the

state cell that intersects the electrode YSA. Note that the wall voltage on the state cell at electrode YSA rises at time  $td_2$  even though there is no sustain pulse at YSA during this time. This is the action of 5 the positive column from the trigger cell causing a discharge with the state cell.

It is important to realize that a given physical - cell has a designation of state cell or trigger cell that is different at times  $td_1$  and  $td_2$ . Note that at 10 time  $td_1$  the trigger cells are positioned between the address electrode and sustain electrode YSA, whereas at time  $td_2$  the trigger cells are positioned between the address electrode and sustain electrode YSB. Similarly at time  $td_1$ , the state cells are positioned at sustain 15 electrode YSB whereas, at time  $td_2$  the state cells are positioned at sustain electrode YSA. This alternation of the roles of the cells between state and trigger status occurs every half cycle of the sustain waveform.

This alteration is a necessary condition for the 20 successful sustaining of these subpixels.

The discharges at times  $td_3$ ,  $td_4$  and  $td_5$  operate in a way very similar to those described above for times  $td_1$  and  $td_2$ .

The showing in Fig. 5f of wall charge distribution 25 at time  $t_5$  shows that at the end of the discharge, all of the dielectric surfaces are at the same potential due to the large number of charged particles generated during the discharge. After each discharge, the wall voltage adjusts to a level very close to the sustain 30 voltage level. This of course means that the voltage across the substrate gap is near zero.

The important point is that after the ON state discharge, the voltages across the substrate gap at both the trigger cell and the state cell are nearly

zero. Further, after an ON state discharge, all dielectric surfaces are at the same potential as shown in Fig. 5f.

Understanding the ON state wall charge distribution of the dielectric surfaces after the discharge is important because it forms the initial condition for the next discharge. Since the voltage across the substrate gap after the discharge is nearly zero, it is a good approximation to assume that any subsequent increase or decrease in applied sustain voltage will cause the amplitude of the sustain voltage change to be applied across the trigger cell or state cell substrate gap.

There are further aspects to be considered regarding the waveforms of Fig. 6b. Note that these waveforms are designed so that the trigger cell discharges are always initiated by a negative-going sustain voltage transition. This is important because it means that the cathode of the trigger cell discharge is always the dielectric surface that covers the sustain electrode and not the dielectric surface that covers the address electrode. These two surfaces usually have considerably different properties when used as cathodes.

For instance, in experimental subpixels that were measured, the initial discharge breakdown voltage,  $V_{b-}$ , when the trigger cell sustain voltage was the cathode, was measured to be approximately 200 volts, but the same cell breakdown voltage,  $V_{b+}$ , was measured to be approximately 300 volts when the address electrode was the cathode. This is because the sustain dielectric is usually coated with a high secondary emission material such as MgO and the address dielectric is coated with or is made entirely of some suitable phosphor material.

The high secondary emission material such as MgO has a high gamma coefficient which means that it emits a high number of secondary electrons when it is bombarded with positive ions from a gas discharge. This gives the 5 discharge a relatively low voltage characteristic which is desirable to reduce circuit costs and power dissipation in the negative glow region of the discharge.

The phosphor material that covers the address 10 electrode is designed to efficiently convert ultraviolet light to visible light. The phosphor generally does not have a high secondary emission material, such as MgO, because such materials usually absorb the ultraviolet light generated by the gas 15 discharge which would give the display poor luminous efficiency. It is important that the cathode of the trigger cell sustain discharge be the dielectric surface that covers the sustain electrodes and not the dielectric that covers the address electrodes. This is 20 achieved by initiating the trigger cell discharge with the negative-going edge of the sustain pulses, as shown for all of the discharges in Fig. 6b.

#### **Address Waveforms**

25 Figs 9a and 9b show prior art addressing and sustain waveforms from U.S. Patent 5,746,086. In order to achieve gray scale in AC plasma displays that have inherent memory, the prior art breaks a frame time into multiple subfields, as shown in Fig. 9a. Fig. 9b shows 30 that each subfield is broken into various periods. For the purpose of this discussion the Fig. 9b prior art steps 1, 2 and 3 will be called the setup period and the prior art step 4 will be called the address period. The last period will be called the sustain period.

While this invention, in a preferred embodiment, employs such an addressing/sustain operation, the waveforms and their points of application differ markedly.

5        The setup period has the purpose of placing all of the subpixels in the panel in a well established wall voltage state that is appropriate for the proper operation of the address period. The setup period also serves to prime the subpixels in the OFF state so that

10      the address period discharge will be well primed and will therefore occur properly. The address period has the purpose of changing the state of a subpixel if there are coincident address pulses on both the YSA electrode and the XA electrode that define the

15      subpixel. The sustain period has the purpose of generating light from the subpixels that are in the ON state and not generating light from subpixels that are in the OFF state.

Fig. 10 shows a set of waveforms that have been

20      found to be successful for addressing the subpixels using the principles of the invention. These waveforms are designed to prime and then set all of the subpixels in the PDP to the OFF state during the setup period and to turn the selected subpixels to the ON state during

25      the address period. A similar set of waveforms, not shown here, could be designed utilizing the principles taught in this invention that sets all of the subpixels in the panel to the ON state during the setup period and then turns the selected subpixels to the OFF state

30      during the address period.

Details of the sustain period operation have been covered extensively above and are the same as presented in Fig. 6b. It is next appropriate to discuss the setup period. There are two types of waveforms that

are used during the setup period and they are called the pulse setup waveforms and the ramp setup waveforms.

The pulse setup waveforms will be presented first.

## 5 Pulse Type Setup Waveforms

Fig. 11 shows details of the pulse setup waveforms. These waveforms are divided into a bulk write and a bulk erase. The bulk write has the function of placing both the OFF cells and the ON cells 10 into the ON state. After the bulk write pulse, all of the subpixels in the panel have one ON state set of wall voltages. All trigger cells in the panel have one well defined wall voltage and all state cells in the panel have another well defined wall voltage.

15 During the bulk erase waveform, all of the subpixels are placed in the OFF state so that there will be no discharge during the sustain period that follows the setup period, unless a selective write occurs during the address period. The bulk write is 20 accomplished by placing such a large negative pulse on the YSA sustain electrodes that all of the trigger cells discharge regardless of whether the subpixel is initially either in the ON state or the OFF state. This large negative bulk write pulse causes the 25 positive column to spread from each trigger cell to an adjoining state cell so that the voltage across the substrate gap of the state cell is reduced to zero and all of the state cells in the PDP are placed into the ON state.

30 The bulk erase pulse is designed to place the bulk erase state cell at exactly the desired wall voltage level needed for proper selective addressing. Fig. 12 shows how this operates. At time  $t_{rel}$ , a single erase pulse, of possible amplitudes  $Ve1$ ,  $Ve2$ ,  $Ve3$  or  $Ve4$ , is

applied to the YSA sustain electrodes. Note that Fig. 12 shows four different waveform rows, each having a different possible value of  $V_e$ .

At time  $t_{f1}$ , the YSB sustain voltage falls and 5 causes a trigger discharge in the trigger cells. This happens in all of the trigger cells in the PDP since it is assumed that a bulk write placed all of the subpixels in the ON state just prior to time  $t_{r1}$ . The positive column from all of the trigger cell discharges 10 spread to all of the state cells and reduces the voltage across all of the state cell substrate gaps to zero. Because of this, each state cell wall voltage moves to a value nearly equal to the applied erase pulse amplitude of  $V_{e1}$ ,  $V_{e2}$ ,  $V_{e3}$  or  $V_{e4}$ , as shown for 15 each of the four cases in Fig. 12.

This novel property of the invention allows the wall voltage of a state cell to be conveniently set to any desired level in accord with the potential applied thereto, and is used in the addressing operation.

20 Note that  $V_{e1}$  is the same pulse amplitude as a high level of the YSA sustain pulse which is at  $V_s$  volts. Setting the state cell wall voltage to  $V_{e1}$  sets all of the state cells to the ON state. Note also that  $V_{e4}$  is the same as the low level of the YSA sustain 25 pulse. Setting the erase pulse to  $V_{e4}$  sets all of the state cells to the OFF state. The  $V_{e4}$  case of Fig. 12 initiates a trigger cell discharge when the state cell sustain voltage is at the low level which causes the trigger cell positive column to reduce the voltage 30 across the state cell substrate gap to zero, thereby placing the state cell in the OFF state.

For proper selective addressing during the address period, it is likely that a wall voltage such as that shown for the  $V_{e3}$  case of Fig. 12 is desired. This is

intended to place the OFF state wall voltage somewhere in the allowed OFF state range. It is not important to discuss the exact wall voltage level at this point since  $V_e$  can be easily adjusted to any desired level 5 that optimizes the selective addressing.

Note that prior art electrode dimensions do not allow a convenient exact establishment of the wall voltages as shown in Fig. 12. In the prior art, the 10 erase pulse can cause a discharge that will change the wall voltage but the final value of wall voltage depends on the initial wall voltage value across the sustain gap and the intensity of the erase discharge. These two values are not known to any strong degree of 15 certainty so that the prior art wall voltage after the discharge is also somewhat unknown.

However with the Fig. 12 technique, the final wall voltage is very closely equal to the value of  $V_e$  which is easily controlled. Note that it is the value of  $V_e$  that is applied to the state cell which, in Fig. 12, 20 is at the YSA sustain electrode at time  $t_{fel}$ , and determines the final value of the wall voltage after the bulk erase operation. The exact value of the initial voltage across the trigger cell substrate gap does not determine the value of the final wall voltage 25 of the state cell as long as the trigger cell substrate gap has enough initial voltage to initiate a proper trigger cell discharge that will extend its positive column to the state cell. The prior art erase discharge does not have this same independence.

30

#### **Ramp Type Setup Waveforms**

Prior art ramp setup waveforms are shown in Fig. 13 (as taught in US patent number 5,745,086). In these waveforms, a slowly rising or falling ramp is used to

cause a weak discharge in a gas that has a positive resistance characteristic. This allows the wall voltage to slowly follow the ramp and maintains the voltage across the gas very close to the breakdown voltage of the gas. The rising ramp of Fig. 13 serves the purpose of the bulk write which places both the ON and the OFF subpixels in a single well established wall voltage state.

The falling ramp of Fig. 13 serves the purpose of the bulk erase which places all of the subpixels in an off state with a well established wall voltage level. The advantage of the ramp setup waveforms of Fig. 13 over the pulse setup waveforms of Figs. 11 and 12 is the significantly lower amount of light that the ramp setup waveforms generate compared to the pulse waveforms which allows the ramp waveforms to have a display with a significantly enhanced contrast, as described in the '086 patent. The advantage of the pulse setup waveforms of Figs. 11 and 12 over the ramp waveforms of Fig. 13 is the reduced amount of time that the pulse setup waveforms take, compared to the ramp waveforms.

The prior art ramp waveform shown in Fig. 13 utilizes a positive resistance discharge between the YSA and the YSB sustain electrodes. During the rising ramp, the YSB sustain dielectric is the cathode, and during the falling ramp the YSA sustain dielectric is the cathode. These prior art waveforms will not work with the invention presented here. The positive resistance discharge utilized in the ramp waveforms requires that there be negligible electric field distortion in the discharge gap. If there is significant field distortion, then the familiar negative resistance characteristic discharge occurs and

the ramp waveform causes an unstable sequence of discharges. Since the existence of a positive column represents a state of a very high level of field distortion, there can be no positive column discharge 5 during the ramp, as a positive resistance discharge is required. Therefore, it is not possible to utilize the positive resistance ramp discharge with the fundamental - discharge technique of this new invention, i.e., to initiate a discharge in a trigger cell that causes its 10 positive column to extend to the state cell which changes the wall voltage of the state cell, and still achieve a positive resistance discharge on a ramp.

Since the positive resistance discharge of the ramp will not create any highly conductive positive 15 column between the trigger cell and the state cell, it is reasonable to assume that the trigger cell and state cell discharges will be independent during the ramp.

It is necessary for the setup period waveforms to establish the wall voltages of both the trigger cell 20 and the state cell to the OFF state range or else the subpixel can errantly turn ON during the sustain period, even without a selective address pulse during the address period. Because of the independence of the discharges during the ramp, it is sometimes desirable 25 to apply the ramp waveforms to both the YSA and the YSB electrodes, as shown in the invention waveforms shown in Fig. 14.

The first operation of the Fig. 14 setup period is the bulk erase which places all of the ON subpixels to 30 the OFF state. This is accomplished with the same technique shown in Fig. 12 (case 4) whereby the positive column from the YSA trigger cell goes to the state cell while the YSB voltage is low. This places the wall voltages of both the trigger cells and the

state cells to the level of the low sustain voltage. This bulk erase only causes a discharge in subpixels that were in the ON state during the sustain period. The subpixels that are OFF during the sustain period 5 will have some unknown wall voltage.

For consistent addressing operation during the address period, it is desirable for the setup waveforms - to place all cells at a fixed, well established OFF state wall voltage. The ramp waveforms of Fig. 14 10 accomplish this.

Note that the ramp waveforms shown in Fig. 14 are considerably different than those shown in Fig. 13. One major difference is that the initial ramp of Fig. 13 is positive-going and the initial ramp of Fig. 14 is 15 negative-going. It is important for the initial ramp of this invention to be negative-going in order to achieve stable operation. This insures that the initial falling ramp discharge has the sustain electrode dielectric as the cathode and is necessary so 20 that the high secondary emission surface (such as MgO) can create a stable discharge.

In order to understand why the MgO cathode has a more stable ramp discharge than the phosphor layer, it is necessary to discuss some details of the ramp 25 discharge. In many respects the positive resistance discharge that occurs due to the ramp is similar to a constant current DC discharge. The constant current that passes through this positive resistance discharge is proportional to the ramp rate in volts per 30 microsecond of the applied ramp. The discharge in the positive resistance mode adjusts itself so that the voltage across the substrate gap is exactly at the breakdown voltage of the discharge.

Recall that for the MgO cathode of the measured devices, this is approximately 200 volts and that for the measured phosphor cathodes, approximately 300 volts. If the substrate gap voltage is above the 5 breakdown voltage, the discharge current will increase until enough charge builds up on the dielectric layers to reduce the voltage across the substrate gap back down to the breakdown voltage. If the substrate gap voltage is below the breakdown voltage, the discharge 10 current decreases to a point where it does not discharge the capacitance of the dielectric layers at such a high rate and the changing ramp voltage placed on the external electrode causes the magnitude of the voltage across the substrate gap to increase until it 15 reaches the breakdown voltage. Once the breakdown voltage is reached, the discharge attains a constant stable level with time, where the rate of increase of the ramp voltage is exactly balanced by the rate of increase of voltage across the dielectric layers.