## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-253544 (P2004-253544A)

平成16年9月9日(2004.9.9) (43) 公開日

(51) Int.C1.7

FI

テーマコード (参考)

HO1L 21/60

HO1L 21/60 HO1L 21/92 5FO44

604J

HO1L 21/92 602G

> 審査請求 有 請求項の数 9 OL (全 16 頁)

(21) 出願番号 (22) 出願日

特願2003-41253 (P2003-41253)

平成15年2月19日 (2003.2.19)

(71) 出願人 000005821

311S

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100076174

弁理士 宮井 暎夫

(74) 代理人 100105979

弁理士 伊藤 誠

(72) 発明者 石川 和弘

大阪府門真市大字門真1006番地

松下電器産業株式会社内

(72) 発明者 三村 忠昭

大阪府門真市大字門真1006番地

松下電器産業株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57)【要約】

【課題】エリアパッド構造に適用可能で、且つ高密度実 装を可能にする小型化で多ピン化が図れ、ショート不良 や信頼性試験でのリーク不良を防止する。

【解決手段】半導体素子1上にマトリックス状に形成さ れた複数の電極にバンプ3を形成し、半導体素子1を支 持する半導体キャリア基板4の配線電極6とバンプ3と が、半田あるいは導電性接着剤5を介して接続し、かつ 半導体素子1と半導体キャリア基板4との間を封止樹脂 7で充填している半導体装置であって、バンプ3を1段 または2段以上に積み上げて形成した。これにより、半 導体キャリア基板4の凹凸形状の反りうねりに応じて、 半導体素子 1 上の複数の電極上に形成したバンプの高さ (段数)を可変させることができるバンプ積層構造を実 現でき、マトリックス配列にある全てのエリア端子の電 気的な接続性とその信頼性を確保できる実装構造を有す るものである。

【選択図】 図 1

- 半導体素子

- 電極パッド バンプ

- ハック 半導体キャリア基板 半田或いは導電性接着剤

- 配線電板部

- 液状封止樹脂

#### 【特許請求の範囲】

### 【請求項1】

半導体素子上にマトリックス状に形成された複数の電極にバンプを形成し、前記半導体素子を支持する半導体キャリア基板の配線電極と前記バンプとが、半田あるいは導電性接着剤を介して接続し、かつ前記半導体素子と前記半導体キャリア基板との間を封止樹脂で充填している半導体装置であって、前記バンプを1段または2段以上に積み上げて形成したことを特徴とする半導体装置。

#### 【請求項2】

半導体素子上にマトリックス状に形成された複数の電極にバンプを形成し、前記半導体素子を支持する半導体キャリア基板の配線電極と前記バンプとが電気的に接続され、かつ前記半導体素子と前記半導体キャリア基板との間にシール状封止樹脂が形成されている半導体装置であって、前記バンプを1段または2段以上に積み上げて形成したことを特徴とする半導体装置。

## 【請求項3】

半導体キャリア基板の反りうねりの形状に応じて、半導体素子と前記半導体キャリア基板との間隔が広くなる位置ほど、積み上げるバンプの段数を多くした請求項1または2記載の半導体装置。

#### 【請求項4】

半導体素子の電極にバンプが1段または2段以上に、バンプの段数が均一に形成されている請求項1または2記載の半導体装置。

#### 【請求項5】

半導体素子の電極のうち少なくとも二つ以上に共通化された電極グループと、この電極グループとリンクする冗長性を持たせた半導体キャリア基板の配線電極とが電気的に接続されている請求項1または2記載の半導体装置。

#### 【請求項6】

半導体素子上の電極に形成するバンプの段数は、均一化、あるいは前記半導体素子の中央部と外周部で異なる構成とした請求項5記載の半導体装置。

#### 【請求項7】

半導体素子上にマトリックス状に形成された複数の電極と半導体キャリア基板の配線電極とをバンプにより接続する半導体装置の製造方法であって、前記複数の電極にバンプを形成する工程と、前記バンプの中央部に凹み部を形成する工程と、2段目のバンプの先端部を前記凹み部に挿入し、2段目のバンプ形成を行う工程とを含む半導体装置の製造方法。

#### 【請求項8】

バンプの中央部に凹み部を形成する前に、前記バンプを平坦化するレベリング工程を行う 請求項7記載の半導体装置の製造方法。

#### 【請求項9】

3 段目以上のバンプ形成を 2 段目と同様に行う工程を含む請求項 7 または 8 記載の半導体 装置の製造方法。

## 【発明の詳細な説明】

#### [0001]

## 【発明の属する技術分野】

この発明は、マトリックス型に形成された複数の素子上電極パッドを有する半導体素子を用いたフリップチップ実装工法で実装した半導体装置に関するものであり、特に、移動体通信や光通信機器などのセット製品における高密度実装化や高速伝送化を図る分野に必要不可欠な、小型で且つ多ピン化への対応が可能である半導体装置およびその製造方法に関するものである。

#### [0002]

### 【従来の技術】

益々、光ディスクや移動体通信機器などのセット製品における高機能化、高速伝送化、高密度実装化に関する要求が高まっている。その中、従来の半導体装置では、高機能化に伴

20

10

30

30

40

50

20

30

40

50

う半導体素子の多ピン化により、半導体装置は益々、技術的に大型化してしまう状況にあり、セット製品への要望に回答できない大きな技術課題があった。そこで、従来の外側周辺だけの電極パッド(ペリフェラル構造)から、ペリフェラル構造内部のマトリックス型に形成された複数の電極パッドを形成したエリアパッド構造にすることにより、半導体装置の多ピン化で小型化を図ることが可能である。しかし、実際POE(Pad On Element)半導体素子を支持する半導体キャリア基板は、従来の外側周辺だけの電極パッドを有するペリフェラル構造に関しては、半導体キャリア基板の実装全面の反りうねりは、10μm以下であったが、エリアパッド構造により、約50~60μm程度と外側周辺だけの電極パッドより大きくなる。従って、ユーザ要望に回答できる製品化への実用化は技術的には、非常に困難であった。

[0003]

以下、図面を参照して従来の半導体装置の構造を説明する。図9と図10はそれぞれ従来のペリフェラル構造の半導体装置を示す断面図である。図9に示すように、表面の電極パッド1にAu等のバンプ3が形成された半導体素子1が、その主面側を下にして、支持体であるセラミックを絶縁基体とした多層回路基板よりなる半導体キャリア基板4に接続されている。半導体素子1上に形成されたバンプ3と半導体キャリア基板4上の複数の配線電極部6とが半田或いは導電性接着剤5により接合されている。そして、接合された半導体素子1と半導体キャリア基板4との隙間には、エポキシ系の液状封止樹脂7が充填被覆されている半導体装置である。

[0004]

次に、もうひとつの従来の半導体装置の例について図面を参照しながら、以下説明する。図9同様、図10に示すように、電極パッド2にAu等のバンプ3が形成された半導体素子1が、その主面側を下にして、支持体であるセラミックを絶縁基体とした多層回路基板よりなる半導体キャリア基板4に接続されている。半導体素子1上に形成されたバンプ3と半導体キャリア4上の複数の配線電極部6とが半田或いは導電性ペースト5を介さずダイレクトにボンディング接合され、シール状のエポキシ系封止樹脂7・1を介して、電気的に接続されているもう一つの従来の半導体装置である。

[00005]

なお、図9と図10に示す半導体キャリア基板4は、その裏面に外部端子8を有し、配線電極部6と外部端子8とは半導体キャリア基板4内に形成されたビア9により内部接続されているものである。

[0006]

以上これら従来の半導体装置は、半導体素子 1 の外側周辺 (ペリフェラル構造)に設けられた電極パッド 2 のみのフリップ接続の実装方法である。

[0007]

一方、ペリフェラル構造内部のマトリックス型に形成された複数の電極パッドを形成したエリアパッド構造にした場合の従来構造を図11(a)と図11(b)及び図12に示す。以下、図面を参照しながら説明する。図11(a)に示すように、半導体素子1上にマトリックス型に形成された複数の電極パッド2があり、それぞれの電極パッド2上にAu等のバンプ3が形成された半導体素子1が、その主面側を下にして、支持体であるセラミックを絶縁基体とした多層回路基板よりなる半導体キャリア基板4(凹形に反っている)に接続されている。半導体素子1上に形成されたバンプ3と半導体キャリア基板4上の複数の配線電極部6とが半田或いは導電性接着剤5により接合されている。しかし、マトリックス配列した外側部のみ接続されているが、反りうねりが大きい中央部は完全に接続れずにオープン不良になっている状況にある。この状態で半導体素子1と半導体キャリア基板4との隙間には、エポキシ系の液状封止樹脂7が充填被覆されている半導体装置である。

[0008]

また、図11(b)に示すように、半導体素子1上にマトリックス型に形成された複数の電極パッド2があり、それぞれの電極パッド2上にAu等のバンプ3が形成された半導体

20

30

40

50

素子 1 が、その主面側を下にして、支持体であるセラミックを絶縁基体とした多層回路基板よりなる半導体キャリア基板 4 (凸形に反っている)に接続されている。半導体素子 1 上に形成されたバンプ 3 と半導体キャリア基板 4 上の複数の配線電極部 6 とが半田或いは導電性接着剤 5 により接合されている。しかし、マトリックス配列した中央部のみ接続されているが、反りうねりが大きい外側部は完全に接続されずにオープン不良になっている状況にある。この状態で半導体素子 1 と半導体キャリア基板 4 との隙間には、エポキシ系の液状封止樹脂 7 が充填被覆されている半導体装置である。

[0009]

次に、図12に示すように、半導体素子1上にマトリックス型に形成された複数の電極パッド2があり、それぞれの電極パッド2上にAu等のバンプ3が形成された半導体素子1が、その主面側を下にして、支持体であるセラミックを絶縁基体とした多層回路子よりなる半導体キャリア基板4(凹形に反っている)に接続されている。半導体素子1の複数の配線である。半導体素のはは、形成されたバンプ3と半導体キャリア4上の複数の配線である。とが半田或系は上代フスト5を介さずダイレクトにボンディング接合され、シール状のエポキシ系したである。して、電気的に接続されているもうーつの従来の半導体装置である。した、沿路でありにおいるは、半導体キャリア基板の大きな反りうねりを緩和させるために、半導体カーフを反りうねりを緩和させるために、半導体カーフの構造においるが、製品のプラマへの致命的なダメージを与えるだけでなく、「でにマトリックス配列の中央部がオープンスの致命的なダメージを与えるだけでなく、すぐにマトリックス配列の中央部がオープンでの対策生し、信頼性試験への寿命も短く、すぐにマトリックス配列の中央部がオープとはが発生し、信頼性試験への寿命も短く、すぐにマトリックス配列の中央部がオープといるであり、では表情造ではデバイスを破壊に対象のないに伴い、さらに高い放熱性が必要であり、従来のエリアパッド構造では実現化は非常に困難であった。

[ 0 0 1 0 ]

【特許文献1】

特開平2-159047号公報(第3,4,6頁)

[ 0 0 1 1 ]

【発明が解決しようとする課題】

上記のように前記従来の半導体装置の構造では、半導体装置の更なる小型化・高機能化に 対 応 して ゆ く た め 、 半 導 体 素 子 の 電 極 パ ッ ド 数 を 増 加 さ せ た が 、 半 導 体 素 子 サ イ ズ が そ れ に 伴 い 大 き く な り 、 半 導 体 装 置 の 小 型 化 が 図 れ な く な る と い う 技 術 的 な 課 題 が あ っ た 。 ま た、半導体装置の大型化を阻止するために、従来の半導体素子の外側周辺だけの電極パッ ド ( ペ リ フ ェ ラ ル ) 構 造 か ら 、 ペ リ フ ェ ラ ル 構 造 内 部 の マ ト リ ッ ク ス 型 に 形 成 さ れ た 複 数 の電極パッドを形成したエリアパッド構造にしたが、エリア中央部を含めた半導体キャリ ア基板の反りうねり量は、従来のペリフェラル構造( 1 0 μ m 以下)よりも大きく、約 5 0~60μmであり、特に、反りうねり量が最大であるエリア中央部周辺でフリップ実装 後、オープン不良が多発している状況にあった。また、高温と高荷重を同時に印加させる も う 一 つ の 従 来 技 術 に お け る 半 導 体 装 置 に つ い て は 、 半 導 体 キ ャ リ ア 基 板 の 大 き な 反 り う ねりを緩和させるために、従来のペリフェラル構造の場合よりも更に、高い温度や荷重を 印加することにより、フリップ実装の位置ずれや、半導体素子への致命的なダメージを与 えるだけでなく、一旦、電気的に接続されるが、製品の応力負荷が発生し、信頼性試験へ の寿命も短く、すぐにマトリックス配列の中央部がオープンする不良が多発していた。そ のため、半導体素子を大きくさせずに、多ピン化が図れる半導体装置を可能にするために は、この反りうねりに対応できる新たな接続手段の確立が必要不可欠であった。

[ 0 0 1 2 ]

したがって、この発明の目的は、前記従来の半導体装置の課題を解決するもので、POE構造を有するエリアパッド構造に適用可能(低コスト化)で、且つ高密度実装を可能にする小型化で多ピン化が図れことはもちろん、マトリックス形状に有る複数の隣接端子とのショート不良を防止することができ、また製品に大きな負荷を加える信頼性試験において発生するオープン不良やリーク不良をも防止或いは無くすることができる半導体装置およ

30

40

50

びその製造方法を提供することである。

#### [0013]

【課題を解決するための手段】

上記課題を解決するためにこの発明の請求項1記載の半導体装置は、半導体素子上にマトリックス状に形成された複数の電極にバンプを形成し、前記半導体素子を支持する半導体キャリア基板の配線電極と前記バンプとが、半田あるいは導電性接着剤を介して接続し、かつ前記半導体素子と前記半導体キャリア基板との間を封止樹脂で充填している半導体装置であって、前記バンプを1段または2段以上に積み上げて形成した。

[0014]

このように、半田あるいは導電性接着剤を介して半導体素子を半導体キャリア基板に接続する構成において、バンプを1段または2段以上に積み上げて形成したので、半導体キャリア基板の凹凸形状の反りうねりに応じて、半導体素子上の複数の電極上に形成したバンプの高さ(段数)を可変させることができるバンプ積層構造を実現できる。例えば半導体キャリア基板の反りうねりが凹形の場合、半導体素子上のマトリックス配列のエリア中央部にバンプを2段以上に積み上げ、半導体キャリア基板の反りうねりの小さい最外周部は従来通りの1段バンプで対応可能である。このように、マトリックス配列にある全てのエリア端子の電気的な接続性とその信頼性を確保できる実装構造を有するものである。

[ 0 0 1 5 ]

請求項2記載の半導体装置は、半導体素子上にマトリックス状に形成された複数の電極にバンプを形成し、前記半導体素子を支持する半導体キャリア基板の配線電極と前記バンプとが電気的に接続され、かつ前記半導体素子と前記半導体キャリア基板との間にシール状封止樹脂が形成されている半導体装置であって、前記バンプを1段または2段以上に積み上げて形成した。

[0016]

このように、半田あるいは導電性接着剤を介さず半導体素子を半導体キャリア基板に接続する構成において、バンプを1段または2段以上に積み上げて形成したので、半導体キャリア基板の凹凸形状の反りうねりに応じて、半導体素子上の複数の電極上に形成したバンプの高さ(段数)を可変させることができるバンプ積層構造を実現できる。例えば半導体キャリア基板の反りうねりが凹形の場合、半導体素子上のマトリックス配列のエリア中央部にバンプを2段以上に積み上げ、半導体キャリア基板の反りうねりの小さい最外周部は従来通りの1段バンプで対応可能である。このように、マトリックス配列にある全てのエリア端子の電気的な接続性とその信頼性を確保できる実装構造を有するものである。

[0017]

請求項3記載の半導体装置は、請求項1または2記載の半導体装置において、半導体キャリア基板の反りうねりの形状に応じて、半導体素子と前記半導体キャリア基板との間隔が広くなる位置ほど、積み上げるバンプの段数を多くした。このように、半導体キャリア基板の反りうねりの形状に応じて、半導体素子と半導体キャリア基板との間隔が広くなる位置ほど、積み上げるバンプの段数を多くしたので、半導体素子の中央部の電極に2段以上のバンプを、また外側周辺に1段のバンプを形成するように、半導体キャリア基板の反りうねりの形状に応じて、積み上げるバンプの段数を可変させることで、格子配列された全ての端子の接続性を確保できる。

[0018]

請求項4記載の半導体装置は、請求項1または2記載の半導体装置において、半導体素子の電極にバンプが1段または2段以上に、バンプの段数が均一に形成されている。このように、半導体素子の電極にバンプが1段または2段以上に、バンプの段数が均一に形成されているので、半導体キャリア基板の表面層の凹凸が小さい場合にバンプ高さを均一にして接続することができる。

[0019]

請求項5記載の半導体装置は、請求項1または2記載の半導体装置において、半導体素子の電極のうち少なくとも二つ以上に共通化された電極グループと、この電極グループとリ

30

40

50

ンクする冗長性を持たせた半導体キャリア基板の配線電極とが電気的に接続されている。 このように、半導体素子の電極のうち少なくとも二つ以上に共通化された電極グループと 、この電極グループとリンクする冗長性を持たせた半導体キャリア基板の配線電極とが電 気的に接続されているので、凹凸が大きい半導体キャリア基板に対しても、電気的接続性 を十分確保でき、電気的な接続性の更なる向上を図ることができる。

(6)

[0020]

請求項6記載の半導体装置は、請求項5記載の半導体装置において、半導体素子上の電極に形成するバンプの段数は、均一化、あるいは前記半導体素子の中央部と外周部で異なる構成とした。このように、半導体素子上の電極に形成するバンプの段数は、均一化、あるいは半導体素子の中央部と外周部で異なる構成としたので、半導体キャリア基板の凹凸形状に応じて、半導体素子の中央部のみや外周部のみにバンプを積層するランダム化した構成だけでなく、全面部への均一化したバンプの積層をも可能となる。

[ 0 0 2 1 ]

請求項7記載の半導体装置の製造方法は、半導体素子上にマトリックス状に形成された複数の電極と半導体キャリア基板の配線電極とをバンプにより接続する半導体装置の製造方法であって、前記複数の電極にバンプを形成する工程と、前記バンプの中央部に凹み部を形成する工程と、2段目のバンプ形成を行う工程とを含む。

[0022]

このように、複数の電極にバンプを形成する工程と、バンプの中央部に凹み部を形成する工程と、2段目のバンプの先端部を凹み部に挿入し、2段目のバンプ形成を行う工程とを含むので、バンプ高さを確保し、マトリックス状に配置された隣接するエリア端子とのショート不良を防止することができる。また、製品に大きな負荷を加える信頼性試験において発生するオープン不良やリーク不良をも防止することができる。そのため、高密度実装を可能にする小型で多ピン化が図れる高機能な半導体装置を実現できる。

[0023]

請求項8記載の半導体装置の製造方法は、請求項7記載の半導体装置の製造方法において、バンプの中央部に凹み部を形成する前に、バンプを平坦化するレベリング工程を行う。このように、バンプの中央部に凹み部を形成する前に、バンプを平坦化するレベリング工程を行うので、凹み部を精度良く形成することができる。

[0024]

請求項9記載の半導体装置の製造方法は、請求項7または8記載の半導体装置の製造方法において、3段目以上のバンプ形成を2段目と同様に行う工程を含む。このように、3段目以上のバンプ形成を2段目と同様に行う工程を含むので、3段目以上のバンプ形成に関して、バンプ積み上げ製造工程に準じて形成することができ、バンプの積層ずれを防止することができる。

[0025]

【発明の実施の形態】

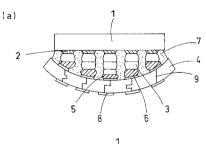

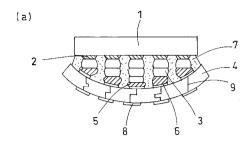

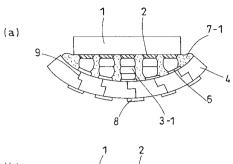

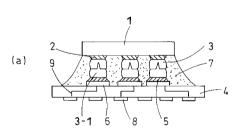

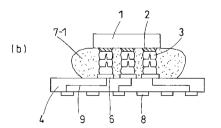

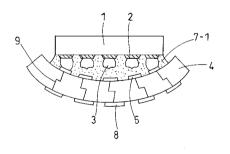

この発明の第1の実施の形態を図1に基づいて説明する。図1(a)はこの発明の第1の実施形態における半導体装置を示す断面図、(b)は第1の実施形態の変形例を示す断面図である。

[0026]

図1に示すように、半導体素子1上に形成された複数のA1等の電極パッド2は、半導体素子1の周辺にペリフェラル状に配列された部分のみではなく、半導体素子内部にも複数の電極パッド2がエリア状にマトリックス配列された格子配列になっている。また、半導体素子1を支持する半導体キャリア基板4の凹凸形状の反りうねりに応じて、半導体素子1上の複数の電極パッド2上に形成したバンプ3の高さ(段数)を1段または2段以上に可変させることができるバンプ積層構造を有している。

[ 0 0 2 7 ]

半導体キャリア基板4が凹形の場合を図1(a)に示す。図1(a)に示すように、半導

20

30

40

50

体素子1上にマトリックス型にエリア配列された複数の電極パッド2に、 A u 等のバンプ3を形成する。この場合、半導体キャリア基板4の表層面は凹形であるため、半導体素子1 と半導体キャリア基板4 との間隔が広くなる半導体素子1 のエリア中央部を中心にバンプ高さを高くするため、2 段から3 段にバンプ3を積層している。一方、エリアパッドの最外周部においては、反りうねりが小さいため、従来通りの1 段バンプを形成している。

[0028]

次に、エリア配列にある電極パッド 2 に形成したバンプ 3 を下にして、半田或いは導電性接着剤 5 を介して半導体キャリア基板 4 の上層面にあるエリア状にマトリックス配列された複数の配線電極部 6 と接着されており、半導体素子 1 と半導体キャリア 4 基板間にはエポキシ系の封止樹脂 7 で充填被覆されている構造である。

[0029]

また、半導体キャリア基板 4 が凸形の場合を図 1 (b)に示す。図 1 (b)に示すように、半導体キャリア基板 4 の表層面は凸形であるため、半導体素子 1 と半導体キャリア基板 4 との間隔が広くなる半導体素子 1 のエリアパッドの最外周部を中心にバンプ 3 の高さを高くする必要があるため、 2 段から 3 段にバンプ 3 を積層している接続構造を有している。一方、エリア中央部は逆に、反りうねりが小さいため、従来通りの 1 段バンプを形成している構造である。

[0030]

なお、図1(a)、(b)に示す半導体キャリア基板4は、その裏面に外部端子8を有し、配線電極部6と外部端子8とは半導体キャリア基板4内に形成されたビア9により内部接続されている。

[ 0 0 3 1 ]

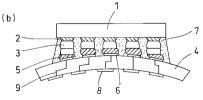

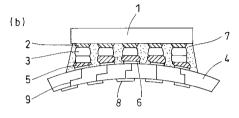

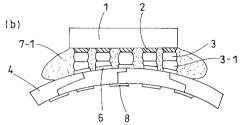

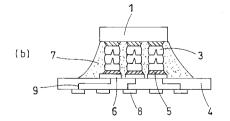

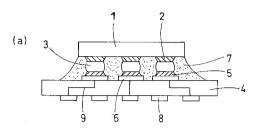

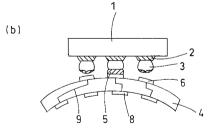

この発明の第2の実施の形態を図2に基づいて説明する。図2(a)はこの発明の第2の実施形態における半導体装置を示す断面図、(b)は第2の実施形態の変形例を示す断面図である。

[0032]

図 2 に示すように、半導体素子 1 上に形成された複数の A 1 等の電極パッド 2 は、半導体素子 1 の周辺にペリフェラル状に配列された部分のみではなく、半導体素子内部にも複数の電極パッド 2 がエリア状にマトリックス配列された格子配列になっている。また、半導体素子 1 を支持する半導体キャリア基板 4 の凹凸形状の反りうねりに応じて、半導体素子 1 上の複数の電極パッド 2 上に形成したバンプ 3 の高さ(段数)を 1 段または 2 段以上に可変させることができるバンプ積層構造を有している。

[0033]

半導体キャリア基板 4 が凹形の場合を図 2 ( a )に示す。図 2 ( a )に示すように、半導体素子 1 上にマトリックス型にエリア配列された複数の電極パッド 2 に、 A u 等のバンプ 3 を形成する。この場合、半導体キャリア基板 4 の表層面は凹形であるため、半導体素子 1 と半導体キャリア基板 4 との間隔が広くなる半導体素子 1 のエリア中央部を中心にバンプ高さを高くするため、 2 段から 3 段にバンプ 3 を積層している。一方、エリアパッドの最外周部においては、反りうねりが小さいため、従来通りの 1 段バンプを形成している。この半導体装置においては、半導体キャリア基板 4 の上層面にあるエリア状にマトリックス配列された複数の配線電極部 6 とバンプ 3 とが、半導体キャリア基板 4 に貼付けられたシール状のエポキシ系の封止樹脂 7 ー 1 を押し広げて、ダイレクトに接続された構造である。

[0034]

また、半導体キャリア基板 4 が凸形の場合を図 2 ( b )に示す。図 2 ( b )に示すように、半導体キャリア基板 4 の表層面は凸形であるため、半導体素子 1 と半導体キャリア基板 4 との間隔が広くなる半導体素子 1 のエリアパッドの最外周部を中心にバンプ 3 の高さを高くする必要があり、 2 段から 3 段にバンプ 3 を積層している接続構造を有している。一方、エリア中央部は逆に、反りうねりが小さいため、従来通りの 1 段バンプを形成している構造である。

30

40

50

[0035]

なお、図2(a)、(b)に示す半導体キャリア基板4は、その裏面に外部端子8を有し、配線電極部6と外部端子8とは半導体キャリア基板4内に形成されたビア9により内部接続されている。

[0036]

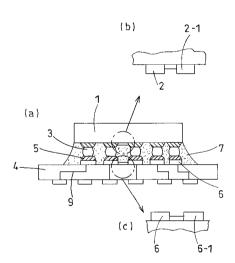

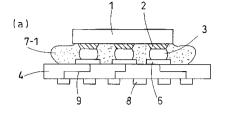

この発明の第3の実施の形態を図3および図4に基づいて説明する。図3はこの発明の第3の実施形態における半導体装置を示す断面図、図4は第3の実施形態の変形例を示す断面図である。

[0037]

図3(a)に示すように、半導体素子1上にマトリックス状に形成された複数の電極2にバンプ3を形成し、半導体素子1を支持する半導体キャリア基板4の配線電極6とバンプ3とが、半田あるいは導電性接着剤5を介して接続し、かつ半導体素子1と半導体キャリア基板4との間を封止樹脂7で充填している構成において、半導体素子1上のエリア状にあるマトリックス型の電極パッド2のうち、少なくとも二つ以上に共通化された電極パッド2と、半導体キャリア基板4の配線電極部6とが、冗長性を持った構造を有している。

[0038]

この場合、半導体素子1上にある電極パッド2のうち、二つ以上の電極パッドとして、冗長性を持たせた電極パッドグループ2・1と、半導体キャリア基板4上にあるマトリックス型の配線電極部6のうち、前記半導体素子1の冗長性を持たせた電極パッドグループ2・1(図3(b))とリンクする冗長性を持たせた配線電極部グループ6-1(図3(c))とを有している。この状態において、電極パッド2に形成したバンプ3と半導体キャリア基板4上の配線電極部6(6・1含む)が、半田或いは導電性接着剤5を介して電気的に接続されている。また、半導体素子1と半導体キャリア基板4との間にはエポキシ系の封止樹脂7が充填被覆されている構造である。

[0039]

また、図4に示すように、半導体素子1上にマトリックス状に形成された複数の電極2にバンプ3を形成し、半導体素子1を支持する半導体キャリア基板4の配線電極6とバンプ3とが電気的に接続され、かつ半導体素子1と半導体キャリア基板4との間にシール状封止樹脂7-1が形成されている構成において、半導体素子1上のエリア状にあるマトリックス型の電極パッド2のうち、少なくとも二つ以上に共通化された電極パッド2と、半導体キャリア基板4の配線電極部6とが、冗長性を持った構造を有している。図4において、Aの拡大図は図3(b)、Bの拡大図は図3(c)と同様である。

[0040]

この場合、半導体素子1上にある電極パッド2のうち、二つ以上の電極パッドとして、例えば三つの電極パッドグループ2・1と、半導体キャリア基板4上にあるマトリックス型の配線電極部6のうち、前記半導体素子1の三つの電極パッドグループ2・1とリンクする3つの配線電極部グループ6・1とを有している。この状態において、電極パッド2に形成したバンプ3と半導体キャリア基板4上の配線電極部6(6・1含む)が、シール状のエポキシ系の封止樹脂7・1を押し広げて、ダイレクトに接続された構造である。

[0041]

なお、図3および図4において、半導体素子1上の電極パッド2に形成するバンプ3の段数は均一化しているが、第1,2の実施形態と同様に半導体素子1の中央部と外周部で異なる構成としてもよい。

[0042]

また、図3,4に示す半導体キャリア基板4は、その裏面に外部端子8を有し、配線電極部6と外部端子8とは半導体キャリア基板4内に形成されたビア9により内部接続されている。

[0043]

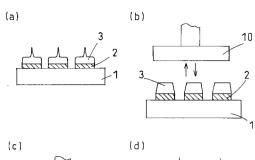

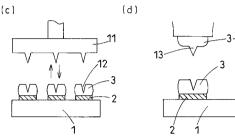

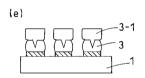

次に、第1~3の実施形態において、バンプ高さを確保するためのバンプ積層に関する製造方法を図5および図6に基づいて説明する。図5(a)~(d)はこの発明の実施形態

のバンプ積層接続技術に関する製造方法を示す断面図である。

#### [0044]

図 5 (a)に示すように、半導体素子1上のマトリックス型に形成された複数の電極パッド2上に、バンプ3を形成し、図 5 (b)に示すように形成したバンプ3をレベリングカール10で平坦化する。次に、図 5 (c)に示すように、平坦化したレベリング済みバンプ3の中央部に、V字形などの凸形ツール11を用いて、V字形などの凹み部12を形成する工程を有している。また、図 5 (d)、(e)に示すように、2段目のバンプ3 - 1の頭頂部(先端部)13を前記平坦化されたバンプ3の中央部に形成した凹み部12を狙って挿入し、2段目のバンプ形成を行い、レベリングツール10で2段目のバンプ3 - 1を平坦化させる。その後、3段目のバンプ形成に関しても前記に示した図 5 (a)~(e)のように形成することができ、バンプの積層ばらつきをかなり小さくすることが可能である。これにより、エリア状にマトリックス配列されたバンプの積層ずれを完全に防止することができ、隣接するエリア状のバンプ間でのショート不良を完全に防止できる高い信頼性を確保したバンプを積層することができる。

#### [0045]

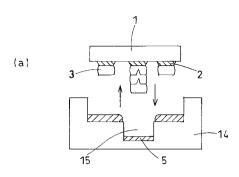

また、図 6 ( a )、( b )はエリア状にマトリックス型に配列した積層バンプの先端部に、半田或いは導電性接着剤 5 を転写塗布する場合の転写製造方法を示す断面図である。

#### [0046]

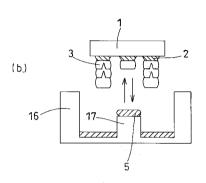

図6(a)に示すように、半導体キャリア基板 4 が凹形の場合においては、バンプ形成した半導体素子 1 のバンプ積層形状は凸状であり、凹形の転写台 1 4 の凹み部分 1 5 にある半田或いは導電性接着剤 5 を転写塗布する方法で転写塗布工程を実施する。また、図6(b)に示すように、半導体キャリア基板 4 が凸形の場合においては、バンプ形成した半導体素子 1 のバンプ積層形状は凹状であり、凸形の転写台 1 6 の凸部 1 7 に塗布された半田或いは導電性接着剤 5 を転写させることもできるものである。

#### [0047]

本実施形態の積層ばらつきを抑えることができる製造方法においてバンプを積み上げる積層バンプ技術や、半導体素子1と半導体キャリア基板4とが冗長性を持たせた構造を有していることにより、隣接する電極パッド2間でのショート不良の防止や信頼性試験でのリーク不良の防止ができるだけでなく、製品の組立歩留(%)を急激に向上させることができるものである。なお、レベリング工程を行わずにバンプ3の中央部に凹み部12を形成してもよい。

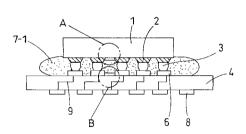

## [0048]

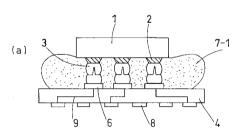

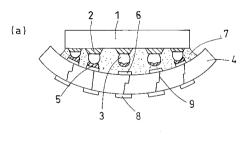

前記に示した図 5 ( a )~( e )に示したバンプ積層製造方法を用いて、バンプの高さを 2 段、または 3 段以上に、エリア状に全面バンプ高さを均一に形成した構造を有すること もできる。その実施の形態を図 7 および図 8 に示している。

#### [0049]

図 7 および図 8 はそれぞれこの発明の第 4 , 5 の実施の形態の半導体装置を示す断面図である。図 7 ( a )、図 8 ( a )にはバンプ高さを 2 段にエリア状に均一にして接続させた場合を示す。また図 7 ( b )、図 8 ( b )にはバンプ高さを 3 段にエリア状に均一にして接続させた場合を示す。

## [ 0 0 5 0 ]

まず、第4の実施形態では、図7(a)、(b)に示すように、半導体素子1上にマトリックス型にエリア配列された複数の電極パッド2に、Au等のバンプ3を形成する。この場合、半導体キャリア基板4の表層面は凹凸が小さいため、半導体素子1のエリア中央部とエリアパッドの最外周部においては、2段(図7(a))または、3段(図7(b))を均一にバンプをエリア全面に積層している。そして、エリア配列にある電極パッド2に形成したバンプ3を下にして、半田或いは導電性接着剤5を介して半導体キャリア基板4の上層面にあるエリア状にマトリックス配列された複数の配線電極部6と接着されており、半導体素子1と半導体キャリア基板4間にはエポキシ系の封止樹脂7で充填被覆されている構造である。

40

30

20

50

20

30

40

50

[0051]

次に、第5の実施形態では、図8(a)、(b)に示すように、半導体素子1上にマトリックス型にエリア配列された複数の電極パッド2に、Au等のバンプ3を形成する。この場合も、半導体キャリア基板4の表層面は凹凸が小さいため、半導体素子1のエリア中央部とエリアパッドの最外周部においては、2段(図8(a))、3段(図8(b))にバンプをエリア全面に積層している。次に、エリア配列にある電極パッド2に形成したバンプ3と半導体キャリア基板4の上層面にあるエリア状にマトリックス配列された複数の配線電極部6とが、シール状のエポキシ系の封止樹脂7-1を押し広げて、ダイレクトに接続された構造である。

[0052]

なお、図 7 ( a ) と図 7 ( b ) 及び図 8 ( a ) と図 8 ( b ) に示す半導体キャリア基板 4 は、その裏面に外部端子 8 を有している。

[0053]

以上説明した本実施形態における半導体装置は、半導体素子1上にあるエリア状の複数の電極パッド2を形成したPOE(Pad On Element)構造を有した半導体素子1(特にエリアパッド構造を有する)と、それを支持する半導体キャリア基板4(反りうねりが大きい)とが、積層したバンプ3等を介してフリップチップ接続している構造を有していることから、半導体キャリア基板4の反りうねりが大きい場合に対しても、必要以上な荷重や応力を負荷させることなく、確実に接続特性を確保することができる。

[0054]

また、多ピンで小型化が図れる半導体製品の組立歩留(%)を従来の約10%から、約98.5%程度に、急激に向上させることもできる。更に、半導体素子1とそれを支持する半導体キャリア基板 4 とはそれぞれ、冗長性を持たせた構造を有していることから、凹凸が大きい半導体キャリア基板に対しても、電気的接続性を十分確保できるものである。また、本発明の実施形態の半導体装置に使用している、バンプ積層技術においては、平坦化したバンプ面上に、V字形などの凹み部12を形成することにより、バンプ3を積み上げる際の積層ばらつきを十分に抑えることができる製造方法であり、マトリックス状に隣接する積層バンプ間での接触(ショート)不良や信頼性試験でのリーク不良の防止もできるものである。

[ 0 0 5 5 ]

また、マトリックス状に配列されたエリアパッド配列構造を有していることから、高密度実装を可能にする小型化で且つ多ピン化が図れる高機能な半導体装置の実現はもちろん、発熱体である半導体素子からの熱をマトリックス状のエリアバンプの端子部からそれぞれ放熱することにより、従来のペリフェラル構造に比べて熱抵抗は17mm (チップ10mm角)のパッケージにおいては、実装基板上においては、約30 / Wであったが、マトリックス型のエリアパッド構造にすることにより、熱抵抗は約24 / W程度に大きく減少させることもができる。すなわち、熱抵抗値は、従来比で約20%と大きく減少させることができるものであり、高放熱性を有するセット製品への商品展開の拡大化も実施することができるものである。

[0056]

【発明の効果】

この発明の請求項1記載の半導体装置によれば、半田あるいは導電性接着剤を介して半導体素子を半導体キャリア基板に接続する構成において、バンプを1段または2段以上に積み上げて形成したので、半導体キャリア基板の凹凸形状の反りうねりに応じて、半導体素子上の複数の電極上に形成したバンプの高さ(段数)を可変させることができるバンプ積層構造を実現できる。例えば半導体キャリア基板の反りうねりが凹形の場合、半導体素子上のマトリックス配列のエリア中央部にバンプを2段以上に積み上げ、半導体キャリア基板の反りうねりの小さい最外周部は従来通りの1段バンプで対応可能である。このように、マトリックス配列にある全てのエリア端子の電気的な接続性とその信頼性を確保できる実装構造を有するものである。その結果、半導体キャリア基板の反りうねりが大きい場合

30

40

50

に対しても、必要以上の荷重や応力を負荷させることなく、確実に接続特性を確保することができる。具体的には、多ピンで小型化が図れる半導体製品の組立歩留りを従来の約1 0%から、約98.5%程度に、急激に向上させることができる。

## [ 0 0 5 7 ]

この発明の請求項 2 記載の半導体装置によれば、半田あるいは導電性接着剤を介さず半導体素子を半導体キャリア基板に接続する構成において、バンプを 1 段または 2 段以上に積み上げて形成したので、半導体キャリア基板の凹凸形状の反りうねりに応じて、半導体子上の複数の電極上に形成したバンプの高さ(段数)を可変させることができるバンプ積層構造を実現できる。例えば半導体キャリア基板の反りうねりが凹形の場合、半導体キャリアオを 2 段以上に積み上げ、半導体キャリアよの反りうねりの小さい最外周部は従来通りの 1 段バンプで対応可能である。このように対しても、以上の荷重や応力を負荷させることなく、確実に接続特性を確保でるに対しても、必要以上の荷重や応力を負荷させることなく、確実に接続特性を確保することができる。具体的には、多ピンで小型化が図れる半導体製品の組立歩留りを従来の約 1 0 %から、約 9 8 . 5 %程度に、急激に向上させることができる。

#### [0058]

請求項3では、半導体キャリア基板の反りうねりの形状に応じて、半導体素子と半導体キャリア基板との間隔が広くなる位置ほど、積み上げるバンプの段数を多くしたので、半導体素子の中央部の電極に2段以上のバンプを、また外側周辺に1段のバンプを形成するように、半導体キャリア基板の反りうねりの形状に応じて、積み上げるバンプの段数を可変させることで、格子配列された全ての端子の接続性を確保できる。

#### [0059]

請求項4では、半導体素子の電極にバンプが1段または2段以上に、バンプの段数が均一に形成されているので、半導体キャリア基板の表面層の凹凸が小さい場合にバンプ高さを均一にして接続することができる。

### [0060]

請求項5では、半導体素子の電極のうち少なくとも二つ以上に共通化された電極グループと、この電極グループとリンクする冗長性を持たせた半導体キャリア基板の配線電極とが電気的に接続されているので、凹凸が大きい半導体キャリア基板に対しても、電気的接続性を十分確保でき、電気的な接続性の更なる向上を図ることができる。

#### [0061]

請求項6では、半導体素子上の電極に形成するバンプの段数は、均一化、あるいは半導体素子の中央部と外周部で異なる構成としたので、半導体キャリア基板の凹凸形状に応じて、半導体素子の中央部のみや外周部のみにバンプを積層するランダム化した構成だけでなく、全面部への均一化したバンプの積層をも可能となる。

#### [0062]

この発明の請求項7記載の半導体装置の製造方法によれば、複数の電極にバンプを形成する工程と、バンプの中央部に凹み部を形成する工程と、2段目のバンプの先端部を凹み部に挿入し、2段目のバンプ形成を行う工程とを含むので、バンプ高さを確保し、マトリックス状に配置された隣接するエリア端子とのショート不良を防止することができる。また、製品に大きな負荷を加える信頼性試験において発生するオープン不良やリーク不良をも防止することができる。そのため、高密度実装を可能にする小型で多ピン化が図れる高機能な半導体装置を実現できる。

#### [0063]

請求項8では、バンプの中央部に凹み部を形成する前に、バンプを平坦化するレベリング 工程を行うので、凹み部を精度良く形成することができる。

#### [0064]

請求項9では、3段目以上のバンプ形成を2段目と同様に行う工程を含むので、3段目以上のバンプ形成に関して、バンプ積み上げ製造工程に準じて形成することができ、バンプ

の積層ずれを防止することができる。

【図面の簡単な説明】

- 【図1】(a)はこの発明の第1の実施形態における半導体装置を示す断面図、(b)は 第1の実施形態の変形例を示す断面図である。

- 【図2】(a)はこの発明の第2の実施形態における半導体装置を示す断面図、(b)は 第2の実施形態の変形例を示す断面図である。

- 【図3】この発明の第3の実施形態における半導体装置を示す断面図である。

- 【図4】第3の実施形態の変形例を示す断面図である。

- 【図5】(a)~(d)はこの発明の実施形態のバンプ積層接続技術に関する製造方法を示す断面図である。

- 【図 6 】(a)、(b)は半田或いは導電性接着剤を転写塗布する場合の転写製造方法を示す断面図である。

- 【図7】この発明の第4の実施の形態の半導体装置を示す断面図である。

- 【図8】この発明の第5の実施の形態の半導体装置を示す断面図である。

- 【図9】(a)は従来の半導体装置を示す断面図、(b)は半導体素子の平面図である。

- 【図10】(a)は従来の半導体装置を示す断面図、(b)は半導体素子の平面図である

- 【図11】(a)、(b)は従来のエリアパッド構造の半導体装置を示す断面図である。

- 【図12】従来のエリアパッド構造の半導体装置を示す断面図である。

【符号の説明】

- 1 半導体素子

- 2 電極パッド

- 2 1 冗長性を有した電極パッドグループ

- 3 Au等のバンプ

- 3 1 二段目のバンプ

- 4 半導体キャリア基板

- 5 半田或いは導電性接着剤

- 6 半導体キャリア基板上に有る配線電極部

- 6 1 冗長性を有した配線電極グループ

- 7 エポキシ系の液状封止樹脂

- 7 1 シール状の封止樹脂

- 8 外部端子

- 9 ビア

- 10 レベリングツール

- 11 V字形などの凸形ツール

- 12 V字形などの凹み部

- 1 3 バンプ頭頂部

- 1 4 半田或いは導電性接着剤が塗布された凹形転写台

- 15 凹形転写台の凹み部分

- 1 6 半田或いは導電性接着剤が塗布された凸形転写台

- 17 凸形転写台の凸の部分

10

20

30

40

## 【図1】

- 半導体素子 電極パッド パンプ 半導体キャリア基板 半田或いは導電性接着剤 配線電極部 液状封止樹脂

## 【図2】

## 【図3】

## 【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

(b) 2

# 【図11】

【図12】

## フロントページの続き

(72)発明者 植田 賢治

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 竹村 康司

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 永井 紀行

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5F044 KK01 LL07 LL11 QQ02 QQ04 RR18