(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5529854号

(P5529854)

(45) 発行日 平成26年6月25日(2014.6.25)

(24) 登録日 平成26年4月25日(2014.4.25)

|                        |            |      |

|------------------------|------------|------|

| (51) Int.Cl.           | F 1        |      |

| HO1L 21/8234 (2006.01) | HO1L 27/08 | 102A |

| HO1L 27/088 (2006.01)  | HO1L 29/78 | 301V |

| HO1L 29/78 (2006.01)   | HO1L 29/80 | C    |

| HO1L 21/336 (2006.01)  | HO1L 29/80 | E    |

| HO1L 27/098 (2006.01)  | HO1L 27/08 | 102C |

請求項の数 19 (全 13 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-509604 (P2011-509604)  |

| (86) (22) 出願日 | 平成21年5月11日 (2009.5.11)        |

| (65) 公表番号     | 特表2011-522402 (P2011-522402A) |

| (43) 公表日      | 平成23年7月28日 (2011.7.28)        |

| (86) 國際出願番号   | PCT/US2009/043518             |

| (87) 國際公開番号   | W02009/140224                 |

| (87) 國際公開日    | 平成21年11月19日 (2009.11.19)      |

| 審査請求日         | 平成24年5月9日 (2012.5.9)          |

| (31) 優先権主張番号  | 12/119,367                    |

| (32) 優先日      | 平成20年5月12日 (2008.5.12)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                             |

|-----------|-----------------------------------------------------------------------------|

| (73) 特許権者 | 506173145<br>ビシェイーシシリコニクス<br>アメリカ合衆国 95054 カリフォルニア州 サンタクララ、ローレルウッド ロード 2201 |

| (74) 代理人  | 100105924<br>弁理士 森下 賢樹                                                      |

| (72) 発明者  | リ、ジアン<br>アメリカ合衆国 94306 カリフォルニア州 パロアルト、ロスブルズ アベニュー 822                       |

| (72) 発明者  | オウヤン、キング<br>アメリカ合衆国 95054 カリフォルニア州 アサートン、エンシナ アベニュー 66                      |

最終頁に続く

(54) 【発明の名称】パワー電界効果トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

J F E T コンポーネントと、

J F E T コンポーネントに近接して配置された第1のゲート領域を有する第1の蓄積型 MOSFET と、

J F E T コンポーネントに近接して配置された第2のゲート領域を有する第2の蓄積型 MOSFET と、

を含み、

J F E T コンポーネントは、

縦型コンタクトトレンチ内に設けられ、当該装置のソースと接続されるソースコンタクトと、

前記縦型コンタクトトレンチの底部に設けられ、当該装置のバルクシリコン領域とは異なる導電型を有するドープ領域と、

を有し、

第1の蓄積型 MOSFET および第2の蓄積型 MOSFET のドレイン領域は、前記縦型コンタクトトレンチに接して設けられ、

第1の蓄積型 MOSFET のソース領域は、第1のゲート領域に対して、第1の蓄積型 MOSFET のドレイン領域の反対側に設けられ、

第2の蓄積型 MOSFET のソース領域は、第2のゲート領域に対して、第2の蓄積型 MOSFET のドレイン領域の反対側に設けられ、

10

20

J F E Tコンポーネント、第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tが当該装置のバルクシリコン領域であって、J F E Tコンポーネントと第1のゲート領域との間に位置するJ F E Tコンポーネントの表面および第1ゲート領域の表面から離れた領域と、J F E Tコンポーネントと第2のゲート領域との間に位置するJ F E Tコンポーネントの表面および第2のゲート領域の表面から離れた領域と、を流れる電流を生じさせるように構成されるハイブリッドパワー電界効果トランジスタ装置。

**【請求項2】**

前記縦型コンタクトトレンチの側壁に形成され、J F E Tコンポーネントの側方に配置された第1のショットキー領域をさらに含み、

前記ドープ領域は、前記ドレイン領域と接しない深さに設けられる請求項1に記載の装置。 10

**【請求項3】**

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tは、ゲートトレンチ側壁の薄膜酸化物およびゲートトレンチ底部に近い厚膜ゲート酸化物領域を含み、ゲート-ドレイン容量を低減する請求項1に記載の装置。

**【請求項4】**

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tは、自己整合による位置決めを容易にする高密度設計レイアウトにしたがって配置される請求項1に記載の装置。

**【請求項5】**

ゲート酸化物による電子散乱を低減するように、前記バルクシリコン領域を通る誘導電流フローが構成される請求項1に記載の装置。 20

**【請求項6】**

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E TがNチャネルM O S F E Tである請求項1に記載の装置。

**【請求項7】**

第2の蓄積型M O S F E Tが当該装置のソースと接続する絶縁ゲートをさらに有する請求項1に記載の装置。

**【請求項8】**

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tがトレンチ型縦型装置として形成されている請求項1に記載の装置。 30

**【請求項9】**

J F E Tコンポーネントと、

J F E Tコンポーネントに近接して配置された第1のゲート領域を有する第1の蓄積型M O S F E Tと、

J F E Tコンポーネントに近接して第1の蓄積型M O S F E Tと反対側に配置された第2のゲート領域を有する第2の蓄積型M O S F E Tと、

を含み、

J F E Tコンポーネントは、

縦型コンタクトトレンチ内に設けられ、当該装置のソースと接続されるソースコンタクトと、

前記縦型コンタクトトレンチの底部に設けられ、当該装置のバルクシリコン領域とは異なる導電型を有するドープ領域と、

を有し、

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tのドレイン領域は、前記縦型コンタクトトレンチに接して設けられ、

第1の蓄積型M O S F E Tのソース領域は、第1のゲート領域に対して、第1の蓄積型M O S F E Tのドレイン領域の反対側に設けられ、

第2の蓄積型M O S F E Tのソース領域は、第2のゲート領域に対して、第2の蓄積型M O S F E Tのドレイン領域の反対側に設けられ、

J F E Tコンポーネント、第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E T

10

20

30

40

50

が当該装置のバルクシリコン領域であって、J F E Tコンポーネントと第1のゲート領域との間に位置するJ F E Tコンポーネントの表面および第1のゲート領域の表面から離れた領域と、J F E Tコンポーネントと第2のゲート領域との間に位置するJ F E Tコンポーネントの表面および第2のゲート領域の表面から離れた領域と、を流れる電流を生じさせるように構成され、

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tはトレンチ型縦型構造として形成されているパワーM O S F E T装置。

【請求項10】

J F E Tコンポーネントの側方に配置された第1のショットキー領域と、

J F E Tコンポーネントの側方であって、第1のショットキー領域とは反対側に配置された第2のショットキー領域とを、

さらに含む請求項9に記載の装置。 10

【請求項11】

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tは、底部厚膜ゲート酸化物領域を含み、ゲート・ドレイン容量を低減する請求項9に記載の装置。

【請求項12】

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tは、自己整合による位置決めを容易にする高密度設計レイアウトにしたがって配置されている請求項9に記載の装置。

。

【請求項13】 20

ゲート酸化物による電子散乱を低減するように、前記バルクシリコン領域を通る誘導電流フローが構成されている請求項9に記載の装置。

【請求項14】

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E TがNチャネル型M O S F E Tである請求項9に記載の装置。

【請求項15】

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E TがPチャネル型M O S F E Tである請求項9に記載の装置。

【請求項16】 30

J F E Tコンポーネントと、

J F E Tコンポーネントに近接して配置された第1のゲート領域を有する第1の蓄積型M O S F E Tと、

J F E Tコンポーネントに近接して第1の蓄積型M O S F E Tと反対側に配置された第2のゲート領域を有する第2の蓄積型M O S F E Tと、

J F E Tコンポーネントの側方に配置された第1のショットキー領域と、

J F E Tコンポーネントの側方であって、第1のショットキー領域と反対側に配置された第2のショットキー領域と、

を含み、

J F E Tコンポーネントは、

縦型コンタクトトレンチ内に設けられ、当該装置のソースと接続されるソースコンタクトと、 40

前記縦型コンタクトトレンチの底部に設けられ、当該装置のバルクシリコン領域とは異なる導電型を有するドープ領域と、

を有し、

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tのドレイン領域は、前記縦型コンタクトトレンチに接して設けられ、

第1の蓄積型M O S F E Tのソース領域は、第1のゲート領域を中心に、第1の蓄積型M O S F E Tのドレイン領域の反対側に設けられ、

第2の蓄積型M O S F E Tのソース領域は、第2のゲート領域を中心に、第2の蓄積型M O S F E Tのドレイン領域の反対側に設けられ、

J F E Tコンポーネント、第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tが当該装置のバルクシリコン領域であって、J F E Tコンポーネントと第1のゲート領域との間に位置するJ F E Tコンポーネントの表面および第1のゲート領域の表面から離れた領域と、J F E Tコンポーネントと第2のゲート領域との間に位置するJ F E Tコンポーネントの表面および第2のゲート領域の表面から離れた領域と、を流れる電流を生じさせるように構成される、パワーF E T装置。

**【請求項17】**

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tは、底部厚膜ゲート酸化物領域を含み、ゲート - ドレイン容量を低減する請求項16に記載の装置。

**【請求項18】**

第1の蓄積型M O S F E Tおよび第2の蓄積型M O S F E Tは、自己整合による位置決めを容易にする高密度設計レイアウトにしたがって配置されている請求項16に記載の装置。

**【請求項19】**

ゲート酸化物による電子散乱を低減するように、前記バルクシリコン領域を通る誘導電流フローが構成される請求項16に記載の装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

概して、本発明細書により、高電流パワー電界効果トランジスタが示される。

20

**【0002】**

本明細書は異なる種類の半導体装置を垂直集積することによって作製されるトレンチ型高電流パワー半導体の構造に関する。低順電圧および高電流におけるオン抵抗特性により、D C - D C変換用途における同期整流トランジスタとして使用されるノーマリーオフ型の装置が得られる。

**【背景技術】**

**【0003】**

パワーM O S F E T(金属酸化物半導体電界効果トランジスタ)は、アナログ回路アプリケーションおよびデジタル回路アプリケーションの両方において、省エネルギー・スイッチとして実施される最も有用な電界効果トランジスタの一つを含む。

30

**【0004】**

一般に、トレンチ型パワーM O S F E Tは、平面構造に対比される縦型構造を用いて構築される。縦型構造により、トランジスタは、高阻止電圧および高電流を維持することができる。同様に、縦型構造により、コンポーネント領域およびアクティブな装置密度は、概して、電流に比例し、装置の「オン」特性として維持され、シリコンドリフトコンポーネントの厚さは装置の「オフ」特性としての降伏電圧に比例する。トレンチ型パワーM O S F E T装置の最も明白な利点の一つは、逆リーク電流が少なく、かつオン抵抗(Rdson)がより低いことである。

**【0005】**

D C - D C変換におけるキーとなる用途の一つとして、還流モードにおいてp - nボディダイオードを有する同期整流トランジスタとして使用されるとき、パワーM O S F E T装置は他の利点を有する。従来のパワーM O S F E Tにおけるp - nボディダイオードの使用は逆電圧阻止の役割を果たす。しかし、還流モードにおけるp - nボディダイオードからの逆回復は、逆に、D C - D C変換における全スイッチング効率に寄与する。

40

**【0006】**

一般に、逆回復効果に対する下記の2つの周知の解決法がある。1) パワーM O S F E Tと共にパッケージ化される外部のショットキー装置を用いる。2) M O S F E Tに集中ショットキーダイオードを集積し、モノリシックアプローチとして寄生ボディダイオードを回避する。歴史的に、これら2つの方法に加えて、電子またはプロトン放射を用いることなどのキャリア - 寿命 - コントロール技術が採用される。これらの技術は、ボディダイ

50

オードの逆回復電荷  $Q_{rr}$  を低減するのに有用であると判明している。

#### 【0007】

しかし、これら全ての解決法には欠点がある。たとえば、外部のショットキーによる手法は、高インダクタンスを招き、さらに全体のスイッチング効率の向上の低下を招きうる。一方、一体的に集積されたショットキーの手法は、シリコン領域の何パーセントかがショットキーの集積に割り当てられ、集積されたショットキーの小面積によって、電流能力および順電圧の低減効果が制限されるため、オン抵抗低減のためのシリコンの有効面積の利用に影響する。放射による手法は、放射によって生じるダメージのため、閾値電圧、リーケ電流および降伏電圧に大きな変化を生じさせる。プロセスおよび製品の複雑さの観点から、これら全ての解決法は、装置の製造においてさらなるマスク層を加えるなどの、余分なプロセス段階を加える必要があるため、経済的に妥当でない。10

#### 【0008】

2003年にChengら(Xu Cheng, Johnny K. Sin, Baowei Kang, Chuguang Feng, Yu Wu and Xingming Liu, IEEE Transactions on electron devices, Vol. 50, No.5, (2003). P14 22)は、高電圧 VDMOSFETにおいてセル分配されたショットキーコンタクトを用いて逆回復が速いボディダイオードを得るのに新規な装置構造を発表した。実験結果は、逆回復チャージの 50 % 減少、およびボディダイオードのソフトネスファクター (softness factor) の増加を示した。両方の構造は、各アクティブセルに「本来備わっている」ショットキーダイオードの作製用に設計される。言い換えると、ショットキーダイオードおよびアクティブなMOSFETは、同じ間隔を有する。プロセスコントロール上の問題のため、各アクティブセルにショットキーダイオードを加えることにより、低電圧活用のパワー装置に対するオン抵抗を低減するために重要となる間隔の短縮余地の可能性が制限される。この手法により、 $R_{ds(on)}$  低減のための間隔の短縮に敏感ではない、高電圧 DMOS 装置(たとえば、> 500V)の様々な利点が提供される(オン抵抗コンポーネントの多くが高電圧利用のためのドリフト領域であるため)。しかし、低電圧利用において、間隔の短縮は、アクティブセルにショットキー装置を追加することにより制限されるべきではない。低電圧装置利用のためオン抵抗に影響を与えることなく、パワー装置にショットキーダイオードをいかに集積するかが課題である。20

#### 【0009】

Baligaら(Tsengyou Syan, Prasd Venkatraman and B. J.Baliga, IEEE Trans. On Electron Devices, Vol. 41 No.5 (1994), P800)は、かつて、1990年代の半ばに、非常にオン抵抗が低い縦型チャネルパワー装置として、蓄積型電界効果トランジスタ(ACCUFET)を提案した。その後、いくつかの同様な装置の構造が発表された。しかし、高逆リーケ電流は、最も問題となる欠点である。ゲートが接地されるとき、「ノーマリーオフ」特性を得ることが非常に難しい。 $n$  チャネル装置用に  $n$  型のゲートが使用されるとき、装置をオフにして条件を満たす逆電圧阻止を得るために負のゲートバイアスが必要とされる。可能な改良方法の一つは、ディープサブミクロンのリソグラフィを用いて間隔を低減することである。しかし、ACCUFETがパワースイッチング装置として使用されるとき、従来のパワー MOSFET とは異なる主要な装置特性を無視すべきではない。空乏幅を狭くする少数のキャリアの蓄積により、逆および順阻止が限定された期間にのみ維持されるという双方向のスイッチング特性が示される。この効果により、阻止能力の有効性が制限される。Yoshinori Konishi (米国特許第5,844,273)により提案された、変形ACCUFET構造として、 $p$ - $n$  ダイオードは、非ボディチャネル領域に形成されうる。この  $p$  型から  $N+$  ソースの間の方向の直接的な接続により、逆リーケを低減しうるが、低オン抵抗および低順電圧の利点は得られていない。3040

#### 【発明の開示】

#### 【0010】

以下に示される実施の形態は、好ましくは、ゲート酸化物散乱によって引き起こされるチャネル移動度の問題を回避し、定格高電流で低順電圧 ( $V_f$ ) を示し、より高速なスイッチングのためのチャネル長の短縮を示す高密度パワー電界効果トランジスタを実現する50

。本実施の形態は、同期整流トランジスタのように、D C - D C 変換に応用されうる。

#### 【0011】

実施の形態において、装置はパワー電界効果トランジスタ装置として実施される。装置は縦型トレンチコンタクト、ジャンクションF E T ( J F E T ) コンポーネント、J F E T コンポーネントに近接して配置された第1の蓄積M O S F E T 、および第1の蓄積型M O S F E T とは反対側においてJ F E T コンポーネントに近接して配置された第2の蓄積型M O S F E T に形成された、ショットキーダイオードを含む。J F E T コンポーネント、縦型ショットキーおよび第1の蓄積M O S F E T は、「オン」モードでの電流バスおよび「オフ」モードでの電圧阻止の両方を提供するように構成される。装置のバルクシリコン領域を流れる誘導電流は、ゲート酸化物の拡散を低減せるように構成される。また、トレンチ構造の底部付近に形成された第2の蓄積型M O S F E T は、ゲート電極がnチャネル装置に対してプラスバイアス下のとき、電流バスに電子を蓄積させる。これは当該装置のオン抵抗の低減に役立つ。10

#### 【0012】

実施の形態では、トレンチ端の近くに形成された第2の蓄積M O S F E T はソースに接続された絶縁ゲートを有する非蓄積型M O S F E T で代用される。この構造は、逆電圧阻止特性を変えることなく、ゲート - ドレイン容量を低減するように設計される。両方の実施の形態において、当該装置の短いチャネル長は、コンタクトトレンチ深さ、コンタクト注入およびゲートトレンチ深さに関連して統一して行われるアニールを規定することで形成される。20

#### 【0013】

概して、本明細書は、非常に短いチャネルを有し、寄生n p nなしでバルクシリコンから電流を流すハイブリッドパワー電界効果トランジスタ(F E T)装置を開示する。装置は、J F E T コンポーネント、J F E T コンポーネントに近接して配置された第1の蓄積型M O S F E T 、およびトレンチ端の底部のJ F E T コンポーネントに近接して配置された第2の蓄積型M O S F E T またはソースと接続する絶縁ゲートを有するM O S F E T を含む。

#### 【図面の簡単な説明】

#### 【0014】

本明細書に組み込まれ、本明細書の一部をなす添付図面は、本発明の実施の形態を例示し、記述とともに本発明の本質を説明するために役立つ。30

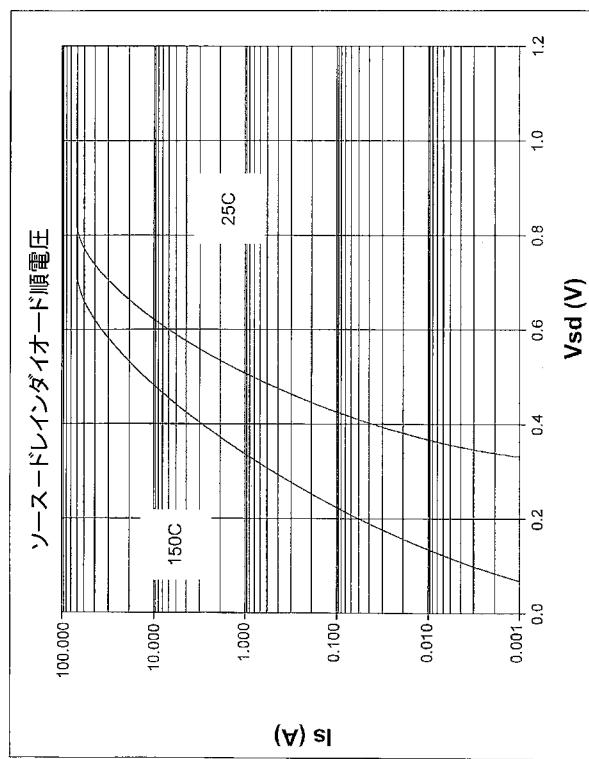

【図1】図1は、本発明の実施の形態に係る装置の、2つの異なるジャンクション温度における異なる定格電流下の順電圧降下(V<sub>f</sub>)を示す。

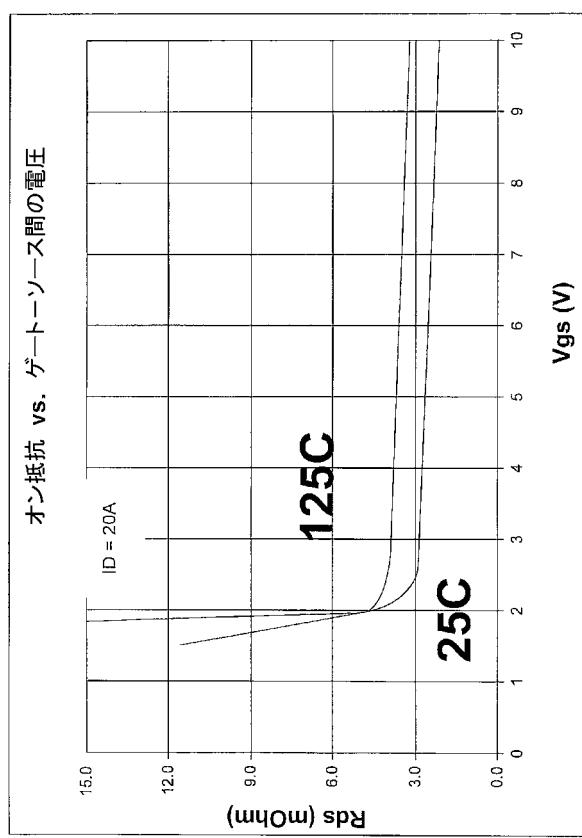

【図2】図2は、本発明の実施の形態に係る、2つの異なるジャンクション温度で測定された本装置のオン抵抗(R<sub>dson</sub>)を示す。

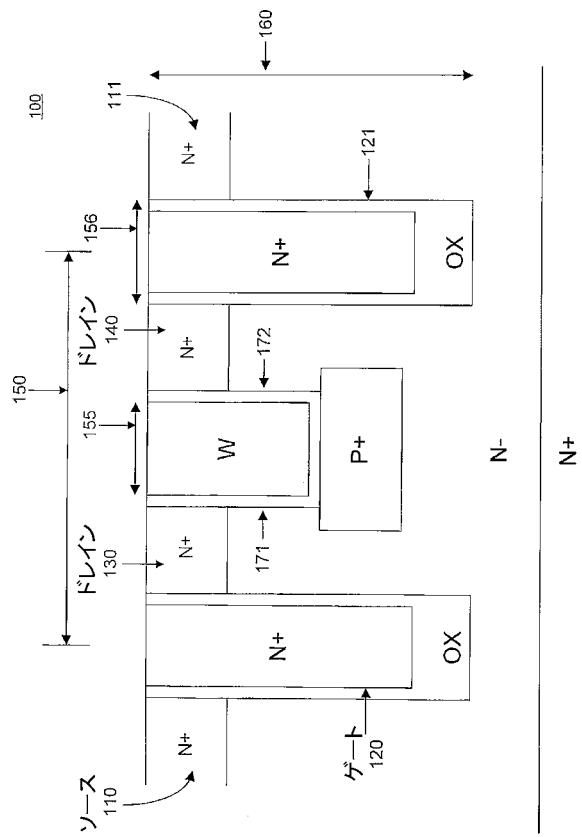

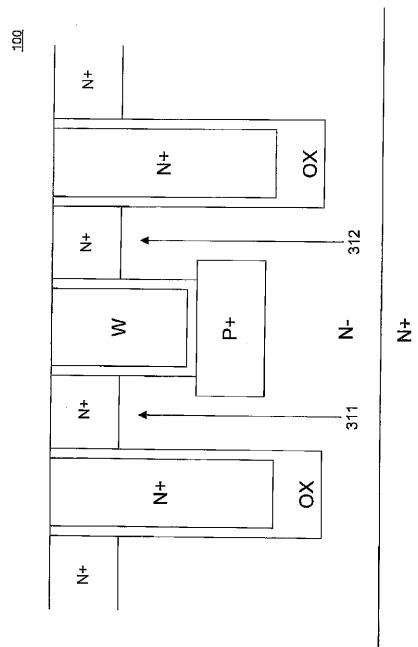

【図3】図3は、本発明の実施の形態に係るNチャネルパワー電界効果トランジスタ(F E T)の概略断面図を示す。

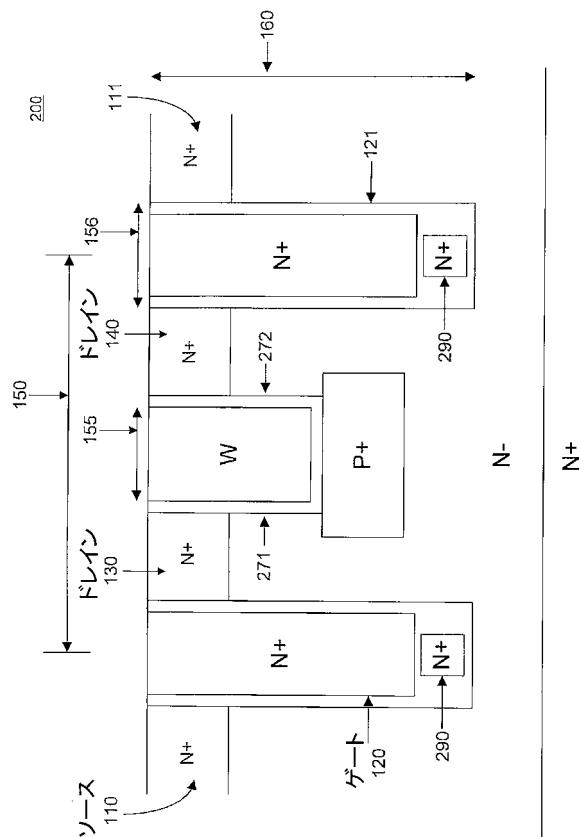

【図4】図4は、本発明の第2の実施の形態に係るNチャネルパワー電界効果トランジスタ(F E T)の概略断面図を示す。

【図5】図5は、本発明の実施の形態に係る装置によって実現される電流フローを示すダイヤグラムである。40

#### 【発明を実施するための形態】

#### 【0015】

本発明の好ましい実施の形態が詳細に記載され、その例が添付の図面に示される。発明は好ましい実施の形態とともに記載されるが、本発明をこれらの実施の形態に限定する意図がないことが理解されよう。むしろ、発明は、代用品、変更物および均等物によるとおりこれが意図され、添付の請求項によって規定される本発明の範囲に含まれることが意図される。さらに、後述する本発明の実施の形態の詳細な説明において、多くの特定の詳細は、本発明の理解を十分にするために示される。しかし、本発明の当業者によって、本発明はこれらの特定の詳細なしで実施されうることが認識される。他の例では、本発明の実施の50

形態の態様を不必要に不明確にしないように、周知の方法、処理、コンポーネントおよび回路は詳細に記述されていない。

#### 【0016】

本発明の実施の形態は、ゲート酸化物層でのキャリアインターフェースによる電子散乱を低減する高密度パワー電界効果トランジスタ（FET）である。本発明の実施の形態は、装置の高電流フローが主にチャネル表面に沿った部分（たとえば、ゲート酸化物層と直に接する）とは反対側の装置のバルクシリコンを通るパワーFETを実現する。これにより、ゲート酸化物の分子構造が電子散乱を引き起こすことが避けられる。この結果、シリコン装置のゲート酸化物散乱効果によるチャネル移動度が相対的に低減する。本発明の実施の形態およびその利点はさらに以下に記述される。

10

#### 【0017】

パワーMOSFETコンポーネントの主要部分の配置は、一般に、フォトリソグラフィにより正確に規定される。フォトリソグラフィプロセスは、コンポーネントの領域を規定し、他の層の上に別の層を形成してコンポーネントを構築することに用いられる。複雑な装置はしばしば多くの異なるビルドアップ層を有し、各層はコンポーネントや異なるインターロケクトを有し、その下の層の上に積層されている。装置コンポーネントが下に横たわるシリコンウエハの表面上に構築されるため、これらの複雑な装置によってもたらされるトポグラフィは、しばしば、多くの「丘」および「谷」を有する、見慣れた陸地の「山領域」に似ている。RC遅延を小さくするための、さらに複雑なインターロケクトによる縦型の集積化を達成することが一般的な傾向である。

20

#### 【0018】

図1は、本発明の実施の形態に係る装置の、2つの異なるジャンクション温度における異なる定格電流下での順電圧降下（V<sub>f</sub>）を示す。図2は、本発明の実施の形態に係る、2つの異なるジャンクション温度で測定された当該装置のオン抵抗（R<sub>dson</sub>）を示す。

#### 【0019】

本発明の実施の形態による装置の利点は、従来のパワーMOSFETのような「ボディ」を形成することなくボディダイオードが形成される事実であることに注意するべきである。当該実施の形態では、ボディダイオードは3つのキーとなるコンポーネント（（1）JFET、（2）縦型ショットキーおよび（3）注入によってトレニチコンタクトの下に形成されるp-n接合）を有する。ゲートトレニチ高さまたは深さに関連する、このようなコンタクト構造の配置は、N+ソースとP+コンタクトとが接続されないことを確保し、縦型ショットキー装置がN+縦型配列におけるN+ソースとP+コンタクトとの間に形成されうるように設計される。ゲートが接地されると、還流ダイオードのように、電流は「ソース」から「ボディ」にボディダイオードから流れうる。言い換えると、トータル順電圧降下（V<sub>f</sub>）は、各ジャンクションの配置に依存する配分を有するこれら3つのコンポーネントによってもたらされる。ボディダイオードの本質的な構成により、この装置は、DC-DC変換で用いられる還流モードにおいて同期されたFET機能を提供することができる。このボディダイオードの構成を設計および最適化することにより、シリコン有効面積の利用におけるR<sub>dson</sub>のトレードオフなしで、低順電圧降下ダイオードが高電流で得られる。図1は、2つの異なるジャンクション温度150、25での異なる定格電流下でのこの順電圧降下（V<sub>f</sub>）を示す。図2は、2つの異なるジャンクション温度125、25で測定された、当該装置のオン抵抗（R<sub>dson</sub>）を示す。

30

#### 【0020】

パワー装置の観点から、RC遅延より性能指数（FOM）を検討することが主にバックエンドよりもむしろフロントエンドからの垂直集積の異なるタイプを達成する動機となる。逆漏出が低減されるとき、装置のオン抵抗に影響を与えることなく、異なる装置を垂直に集積することは課題である。本発明では、新しい構造により、トレニチ構造において、ショットキーダイオード、ジャンクション電界効果トランジスタ（JFET）および蓄積モードのMOSFETの垂直集積が提供される。従来のトレニチ型パワーMOSFETと

40

50

比較すると、チャネルにボディがない。ACCUE (原型構造および変更構造) と比較すると、JFET装置と連結した縦型ショットキー装置を形成すること自体が独創的である。また、p-nダイオードを有するJFETの形成は、トレンチ底部付近のゲート酸化物における逆方向降伏を回避しつつ、ゲートトレンチ底部に近づくように策定される。

#### 【0021】

電流フローが主に装置の表面に留まる傾向があることによる電子散乱効果を受ける従来技術のパワーMOSFETとは違い、当該垂直集積構造の電流フローは、シリコンからのバルク伝導によって生じる。このような本装置の利点により、ゲート酸化物の分子構造がシリコンのチャネル移動度を低減する電子散乱を引き起こすことを避けることができる。ACCUEとは違い、ボディがないにもかからず、本装置は、ビルドインボディダイオードを有する。電流駆動される従来のパワージャンクションFET (JFET) と比較すると、本装置は依然として、比較的低駆動電圧でオンとなりうる電圧駆動装置である。

。

#### 【0022】

従来のパワーMOSFET、JFETおよびACCUEに対する本パワー装置の3つの利点は、1) N-チャンネル装置において寄生n-p-nがなく、「ボディ」が形成されていないため、装置の堅牢さ(ruggness)を改善するのに役立ちうこと、2) 高定格電流において「本質的に備わる」低順電圧(Vf)機能がアクティブセルにおいて特定のオン抵抗に影響することなく得られること、3) 本装置のチャネル長がトレンチ深さおよびトレンチ型パワーMOSFETのようなボディプロファイルによって規定されず、チャネル長が縦型ショットキーおよびJFET配置によって規定されるNチャネル装置としては、0.1μm～0.4μmの範囲でより短いこと、である。ドーピング極性が逆であれば、等価なp-チャンネル装置が形成されうる。

20

#### 【0023】

図3は、本発明の実施の形態によるNチャネルパワーFET100の概略断面図である。図3に示すように、ハイブリッドパワーFET100の断面図に、ソース110、111、ドレイン130、140およびゲート120、121が示されている。装置100は、トレンチ型縦型装置構造である。図3に示すように、ソースおよびドレイン領域は、N+にドープされている。装置のバルクシリコンはN-であり、基板自体はN+である。ゲート120、121は、図示されたような酸化物層を有するNシリコンである。領域155によって示された装置の中心部分に、ソースコンタクトがある。当該コンポーネントは、図示されたP+ゲートの上部に配置されたタンゲステンコンタクトを有する。また、このソースコンタクトにより、2つのショットキー領域171、172が実現される。ゲート酸化物の底部は、ゲート酸化物層の側壁より厚いことに注意されたい。この特性により、ゲート-ドレイン間の容量を低くすることができる。寸法150により、装置の間隔が2.0μmから0.5μmの範囲に規定される。チャネル長は、P+注入および続くアニールによって規定される。チャネル幅は、寸法150、155およびP+注入の横断プロファイルによって規定される。

30

#### 【0024】

ある実施の形態において、2つのゲート120と121との間の間隔150は、1μm未満である。コンタクト領域155の幅は、典型的には、0.25μm未満である。ゲート領域156の幅は、典型的には、0.25μm未満である。ゲート領域の表面から底部までの装置100の深さ160は、典型的には、1μm未満である。このように、装置100は、超高密度装置として実現されうる。たとえば、装置100は、1インチ平方当たり約1Gセル以上の密度を得るように使用されうる。さらに、装置100の構造は、製造プロセス中の自己整合トレンチコンタクトに適する。

40

#### 【0025】

装置100により、3つの主なコンポーネントを有する「ハイブリッド」型パワーMOSFET装置が実現される。ここで使用されるハイブリッドという用語は、装置100に、独自の機能を提供する3つの異なる種類のコンポーネントが組み込まれることを意味す

50

る。第1の種類は、ゲート120、121を有する2つの蓄積型MOSFETである。第2の種類は、装置の中心部分のJFET(たとえば、領域155の下)である。第3の種類はドレイン130、140に近接する2つのショットキー領域171、172である。

#### 【0026】

図4は、異なるゲート配置を有する第2の実施の形態を示す。図4は、本発明の実施の形態による、NチャネルハイブリッドパワーFET200の概略断面図を示す。装置200のゲートの底部が装置100の底部とは異なることに注意されたい。第2のゲートとしての底部ゲート290は、ソースと接続するように絶縁されている。他の側面では、装置200は、実質的に装置100と同様である。図4に示すように、ソードおよびドレイン領域はN+型にドープされている。装置のバルクシリコンはN-であり、基板自身はN+である。ゲートは、図示されたような酸化物層を有するNシリコンである。図示されたようなP+ゲートの上部に配置されたタングステンコンタクトが装置200の中心に存在する。また、このソースコンタクトコンポーネントは、2つのショットキー領域271、272を実現する。

#### 【0027】

図5は、本発明の実施の形態による装置100によって実現される電流フローを示す図である。図5に示すように、電流は装置100のバルクシリコンを流れる。電流フローは、電流フロー線311、312で示される。電流フローは、主に、ゲート酸化物の表面に沿う部分と対比されるバルクを通る。これにより、従来技術に比べて多くの利点が得られる。装置100の構成はn-p-n寄生損失を持たないため、より広く安全な動作領域が得られる。上述したように、電流フローは装置100のバルクを通ることで、チャネル移動度の低下が少なくなり、装置100の全抵抗が低減される。

#### 【0028】

さらに、装置100は相対的に低い閾値電圧を有する。たとえば、実施の形態では、閾値電圧は、1.0V~1.1Vの範囲である。低閾値電圧により、2つのバッテリーセル未満で装置をオンとすることができます。ゲート酸化物の近くに反転がないため、装置100は、従来の装置に比べて「でこぼこ(raggedness)」が改善される。また、装置100は、定格高電流での順電圧を低くし、余分に集積されたショットキーまたは外部ショットキーダイオードなしでこの特性を得ることができる。

#### 【0029】

前述した本発明の特定の実施の形態の記述は、説明の目的で示されている。これらは、包括的であること、または発明を開示されたままの形態に限定することを意図しておらず、明らかに、上述した教示に照らして多くの変更および変形が可能である。実施の形態は、本発明の本質および実際の応用を最も良く説明するために選ばれ、記述されており、これにより、当業者は、本発明および予期された特定の使用に適するような様々な変更とともに様々な実施の形態を利用することができる。本発明の範囲は添付の請求項およびその均等物によって規定されることが意図される。

#### 【0030】

##### (コンセプト) 短いまとめ

この明細書は少なくとも以下の広いコンセプトを開示する。

コンセプト1：JFETコンポーネントと、JFETコンポーネントに近接して配置された第1の蓄積型MOSFETと、トレンチ底部端においてJFETコンポーネントに近接して配置された第2の蓄積型MOSFETと、を含み、JFETコンポーネント、第1の蓄積型MOSFETおよび第2の蓄積型MOSFETが当該装置のバルクシリコン領域を流れる電流を生じさせるように構成されているハイブリッドパワー電界効果トランジスタ装置。

コンセプト2：.チャネル装置中のn+ソースとp+コンタクトを連結することなく、縦型コンタクトトレンチの側壁に形成され、JFETコンポーネントの側方に配置された第1のショットキー領域をさらに含むコンセプト1に記載の装置。

コンセプト3：.第1の蓄積型MOSFETおよび第2の蓄積型MOSFETは、トレン

10

20

30

40

50

チ側壁の薄膜酸化物およびトレンチ底部に近い厚膜ゲート酸化物領域を含み、ゲート - ドレイン容量を低減するコンセプト 1 に記載の装置。

コンセプト 4 : 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が自己位置決めを容易にするように、高電流設計レイアウトにより配置されるコンセプト 1 に記載の装置。

コンセプト 5 : 装置のバルクシリコン領域を通る誘導電流フローがゲート酸化物の拡散を低減するように構成されるコンセプト 1 に記載の装置。

コンセプト 6 : 第 1 の蓄積型 MOSFET および前記第 2 の蓄積型 MOSFET が N チャネル MOSFET であるコンセプト 1 に記載の装置。

コンセプト 7 : 第 1 の蓄積型 MOSFET および第 2 の MOSFET が前記ソースと接続する絶縁ゲートを有するコンセプト 1 に記載の装置。 10

コンセプト 8 : JFET コンポーネント、第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET がトレンチ型縦型装置として形成されているコンセプト 1 に記載の装置。

コンセプト 9 : . JFET コンポーネントと、JFET コンポーネントに近接して配置された第 1 の蓄積型 MOSFET と、第 1 の蓄積型 MOSFET の反対側の JFET コンポーネントに近接して配置された第 2 の蓄積型 MOSFET と、を含み、JFET コンポーネント、第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が装置のバルクシリコン領域を通る電流フローを引き起こすように構成され、JFET コンポーネント、第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET はトレンチ型縦型構造として形成されているパワー MOSFET 装置。 20

コンセプト 10 : JFET コンポーネントの側方に配置された第 1 のショットキー領域と、第 1 のショットキー領域とは反対側の JFET コンポーネントの側方に配置された第 2 のショットキー領域とを、さらに含むコンセプト 9 に記載の装置。

コンセプト 11 : . 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が厚膜でより下方の酸化物ゲート領域を含み、ゲート - ドレイン容量を低減するコンセプト 9 に記載の装置。

コンセプト 12 : 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が自己位置決めを容易にする高電流設計レイアウトに従って配置されているコンセプト 9 に記載の装置。

コンセプト 13 : 装置のバルクシリコン領域を通る誘導電流フローがゲート酸化物の拡散を低減するように構成されているコンセプト 9 に記載の装置。 30

コンセプト 14 : 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が N チャネル型 MOSFET であるコンセプト 9 に記載の装置。

コンセプト 15 : 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が P チャネル型 MOSFET であるコンセプト 9 に記載の装置。

コンセプト 16 : JFET コンポーネントと、JFET コンポーネントに近接して配置された第 1 の蓄積型 MOSFET と、第 1 の蓄積型 MOSFET とは反対側の FET コンポーネントに近接して配置された第 2 の蓄積型 MOSFET と、JFET コンポーネントの側方に配置された第 1 のショットキー領域と、第 1 のショットキー領域とは反対側の JFET コンポーネントの側方に配置された第 2 のショットキー領域と、を含み、JFET コンポーネント、第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が装置のバルクシリコン領域を通る電流を引き起こすように構成されているパワー FET 装置。 40

コンセプト 17 : 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が厚膜でより下方の酸化物ゲート領域を含み、ゲート - ドレイン容量を低減するコンセプト 16 に記載の装置。

コンセプト 18 : . 第 1 の蓄積型 MOSFET および第 2 の蓄積型 MOSFET が自己位置決めを容易にするように高電流設計レイアウトに従って配置されているコンセプト 16 に記載の装置。

コンセプト 19 : 装置のバルクシリコン領域を通る誘導電流フローがゲート酸化物の拡散を低減するように構成されるコンセプト 16 に記載の装置。 50

【図1】

【図2】

【図3】

【図4】

【図5】

FIG. 5

---

フロントページの続き

| (51)Int.Cl.              | F I               |

|--------------------------|-------------------|

| H 01 L 29/808 (2006.01)  | H 01 L 27/06 101U |

| H 01 L 21/337 (2006.01)  | H 01 L 27/06 102A |

| H 01 L 27/095 (2006.01)  | H 01 L 29/78 301G |

| H 01 L 27/06 (2006.01)   |                   |

| H 01 L 21/8248 (2006.01) |                   |

| H 01 L 21/8222 (2006.01) |                   |

審査官 岩本 勉

(56)参考文献 特開2003-069042(JP,A)

特開2002-110984(JP,A)

特開2004-247496(JP,A)

特表平09-508492(JP,A)

特表2008-536316(JP,A)

特表2007-503108(JP,A)

国際公開第2006/108011(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336、21/8234-21/8238、

21/8249、

27/06-27/08、27/088-27/095、

29/76、29/772-29/78、

29/80-29/812