(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7635342号**

**(P7635342)**

(45)発行日 令和7年2月25日(2025.2.25)

(24)登録日 令和7年2月14日(2025.2.14)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| H 1 0 D | 30/67 (2025.01) | F I | H 1 0 D | 30/67 | 1 0 3 B |

| H 0 5 B | 33/14 (2006.01) |     | H 0 5 B | 33/14 | Z       |

| H 1 0 D | 1/68 (2025.01)  |     | H 1 0 D | 1/68  |         |

| H 1 0 D | 84/80 (2025.01) |     | H 1 0 D | 30/67 | 1 0 2 N |

| H 1 0 D | 84/83 (2025.01) |     | H 1 0 D | 30/67 | 1 0 2 T |

請求項の数 5 (全46頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2023-195731(P2023-195731) |

| (22)出願日           | 令和5年11月17日(2023.11.17)      |

| (62)分割の表示         | 特願2022-8373(P2022-8373)の分割  |

| 原出願日              | 平成26年10月30日(2014.10.30)     |

| (65)公開番号          | 特開2024-23327(P2024-23327A)  |

| (43)公開日           | 令和6年2月21日(2024.2.21)        |

| 審査請求日             | 令和5年12月5日(2023.12.5)        |

| (31)優先権主張番号       | 特願2013-226963(P2013-226963) |

| (32)優先日           | 平成25年10月31日(2013.10.31)     |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72)発明者  | 三宅 博之<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| (72)発明者  | 及川 欣聰<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| (72)発明者  | 鈴木 幸恵<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| 審査官      | 西村 治郎                                          |

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

トランジスタのゲート電極としての機能を有する第1の導電膜と、前記第1の導電膜の上方に位置する領域を有する第1の酸化シリコン膜と、前記第1の酸化シリコン膜の上面に接する領域を有し、かつ、前記トランジスタのチャネル形成領域を有する第1の酸化物半導体膜と、前記第1の酸化シリコン膜の上面に接する領域を有する第2の酸化物半導体膜と、前記第1の酸化物半導体膜の上方に位置する領域を有し、かつ、前記第1の酸化物半導体膜と電気的に接続された第2の導電膜及び第3の導電膜と、前記第1の酸化物半導体膜の上面に接する領域を有し、かつ、前記第2の酸化物半導体膜の上面に接する領域を有する第2の酸化シリコン膜と、前記第2の酸化シリコン膜を介して前記第1の酸化物半導体膜の上方に位置する領域を有し、かつ、前記トランジスタの第2のゲート電極としての機能を有する第4の導電膜と、前記第2の酸化シリコン膜の上方に位置する領域を有する絶縁膜と、前記絶縁膜の上方に位置する領域を有し、かつ、前記第3の導電膜と電気的に接続された画素電極と、を有し、前記絶縁膜は、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニア膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜及び酸化ネオジム膜のいずれか一であり、

前記絶縁膜のうち、前記第2の酸化シリコン膜の上面に接する領域は、前記第1の酸化物半導体膜と重なりを有し、

前記第2の酸化物半導体膜は、上面が前記絶縁膜に接している領域であって、かつ、前記絶縁膜を介して前記画素電極と重なる領域に、第1の領域を有し、

前記第2の酸化物半導体膜は、上面が前記第2の酸化シリコン膜に接している第2の領域を有し、

前記第2の酸化物半導体膜は、前記画素電極と接する領域を有さず、

断面視において、前記第1の領域は前記第2の領域よりも、前記画素電極との間隔が小さい、

半導体装置。

10

### 【請求項2】

トランジスタのゲート電極としての機能を有する第1の導電膜と、

前記第1の導電膜の上方に位置する領域を有する第1の酸化シリコン膜と、

前記第1の酸化シリコン膜の上面に接する領域を有し、かつ、前記トランジスタのチャネル形成領域を有する第1の酸化物半導体膜と、

前記第1の酸化シリコン膜の上面に接する領域を有する第2の酸化物半導体膜と、

前記第1の酸化物半導体膜の上方に位置する領域を有し、かつ、前記第1の酸化物半導体膜と電気的に接続された第2の導電膜及び第3の導電膜と、

前記第1の酸化物半導体膜の上面に接する領域を有し、かつ、前記第2の酸化物半導体膜の上面に接する領域を有する第2の酸化シリコン膜と、

前記第2の酸化シリコン膜を介して前記第1の酸化物半導体膜の上方に位置する領域を有し、かつ、前記トランジスタの第2のゲート電極としての機能を有する第4の導電膜と、

前記第2の酸化シリコン膜の上方に位置する領域を有する絶縁膜と、

前記絶縁膜の上方に位置する領域を有し、かつ、前記第3の導電膜と電気的に接続された画素電極と、を有し、

前記絶縁膜は、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ラントン膜、酸化セリウム膜及び酸化ネオジム膜のいずれか一であり、

前記絶縁膜のうち、前記第2の酸化シリコン膜の上面に接する領域は、前記第1の酸化物半導体膜と重なりを有し、

前記第2の酸化物半導体膜は、上面が前記絶縁膜に接している領域であって、かつ、前記絶縁膜を介して前記画素電極と重なる領域に、第1の領域を有し、

前記第2の酸化物半導体膜は、上面が前記第2の酸化シリコン膜に接している第2の領域を有し、

前記第2の酸化物半導体膜は、前記画素電極と接する領域を有さず、

断面視において、前記第1の領域は前記第2の領域よりも、前記画素電極との間隔が小さく、

前記第1の領域は、容量素子の第1の電極としての機能を有し、

前記画素電極は、前記容量素子の第2の電極としての機能を有する、

半導体装置。

40

### 【請求項3】

トランジスタのゲート電極としての機能を有する第1の導電膜と、

前記第1の導電膜の上方に位置する領域を有する第1の酸化シリコン膜と、

前記第1の酸化シリコン膜の上面に接する領域を有し、かつ、前記トランジスタのチャネル形成領域を有する第1の酸化物半導体膜と、

前記第1の酸化シリコン膜の上面に接する領域を有する第2の酸化物半導体膜と、

前記第1の酸化物半導体膜の上方に位置する領域を有し、かつ、前記第1の酸化物半導体膜と電気的に接続された第2の導電膜及び第3の導電膜と、

前記第1の酸化物半導体膜の上面に接する領域を有し、かつ、前記第2の酸化物半導体

50

膜の上面に接する領域を有する第2の酸化シリコン膜と、

前記第2の酸化シリコン膜の上方に位置する領域を有する絶縁膜と、

前記絶縁膜の上方に位置する領域を有し、かつ、前記第3の導電膜と電気的に接続された画素電極と、を有し、

前記絶縁膜は、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜及び酸化ネオジム膜のいずれか一であり、

前記絶縁膜のうち、前記第2の酸化シリコン膜の上面に接する領域は、前記第1の酸化物半導体膜と重なりを有し、

前記第2の酸化物半導体膜は、上面が前記絶縁膜に接している領域であって、かつ、前記絶縁膜を介して前記画素電極と重なる領域に、第1の領域を有し、

前記第2の酸化物半導体膜は、上面が前記第2の酸化シリコン膜に接している第2の領域を有し、

前記第2の酸化物半導体膜は、前記画素電極と接する領域を有さず、

断面視において、前記第1の領域は前記第2の領域よりも、前記画素電極との間隔が小さい、

半導体装置。

#### 【請求項4】

トランジスタのゲート電極としての機能を有する第1の導電膜と、

前記第1の導電膜の上方に位置する領域を有する第1の酸化シリコン膜と、

前記第1の酸化シリコン膜の上面に接する領域を有し、かつ、前記トランジスタのチャネル形成領域を有する第1の酸化物半導体膜と、

前記第1の酸化シリコン膜の上面に接する領域を有する第2の酸化物半導体膜と、

前記第1の酸化物半導体膜の上方に位置する領域を有し、かつ、前記第1の酸化物半導体膜と電気的に接続された第2の導電膜及び第3の導電膜と、

前記第1の酸化物半導体膜の上面に接する領域を有し、かつ、前記第2の酸化物半導体膜の上面に接する領域を有する第2の酸化シリコン膜と、

前記第2の酸化シリコン膜の上方に位置する領域を有する絶縁膜と、

前記絶縁膜の上方に位置する領域を有し、かつ、前記第3の導電膜と電気的に接続された画素電極と、を有し、

前記絶縁膜は、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜及び酸化ネオジム膜のいずれか一であり、

前記絶縁膜のうち、前記第2の酸化シリコン膜の上面に接する領域は、前記第1の酸化物半導体膜と重なりを有し、

前記第2の酸化物半導体膜は、上面が前記絶縁膜に接している領域であって、かつ、前記絶縁膜を介して前記画素電極と重なる領域に、第1の領域を有し、

前記第2の酸化物半導体膜は、上面が前記第2の酸化シリコン膜に接している第2の領域を有し、

前記第2の酸化物半導体膜は、前記画素電極と接する領域を有さず、

断面視において、前記第1の領域は前記第2の領域よりも、前記画素電極との間隔が小さく、

前記第1の領域は、容量素子の第1の電極としての機能を有し、

前記画素電極は、前記容量素子の第2の電極としての機能を有する、

半導体装置。

#### 【請求項5】

請求項1乃至請求項4のいずれか一において、

前記第1の酸化物半導体膜及び前記第2の酸化物半導体膜は、In、Ga及びZnを主

成分として含む半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、物、方法、又は製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、又は組成物（コンポジション・オブ・マター）に関する。本発明の一態様は、半導体装置、表示装置、電子機器、それらの作製方法、又はそれらの駆動方法に関する。とくに、本発明の一態様は、例えば、トランジスタ及び容量素子を有する半導体装置に関する。

【背景技術】

【0002】

液晶表示装置や発光表示装置に代表されるフラットパネルディスプレイの多くに用いられているトランジスタは、ガラス基板上に形成されたアモルファスシリコン、単結晶シリコン又は多結晶シリコンなどのシリコン半導体によって構成されている。また、該シリコン半導体を用いたトランジスタは、集積回路（IC）などにも利用されている。

【0003】

近年、シリコン半導体に代わって、半導体特性を示す金属酸化物をトランジスタに用いる技術が注目されている。なお、本明細書中では、半導体特性を示す金属酸化物を酸化物半導体とよぶこととする。例えば、酸化物半導体として、酸化亜鉛、またはIn-Ga-Zn系酸化物を用いたトランジスタを作製し、該トランジスタを表示装置の画素のスイッチング素子などに用いる技術が開示されている（特許文献1及び特許文献2参照）。

【0004】

また、開口率を高めるために、トランジスタの酸化物半導体膜と同じ表面上に設けられた酸化物半導体膜と、トランジスタに接続する画素電極とが所定の距離を離れて設けられた容量素子を有する表示装置が開示されている（特許文献3参照）。

【先行技術文献】

【特許文献】

【0005】

【文献】特開2007-123861号公報

【文献】特開2007-96055号公報

【文献】米国特許第8102476号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

容量素子は一对の電極の間に誘電体膜が設けられており、一对の電極のうち、少なくとも一方の電極は、トランジスタを構成するゲート電極、ソース又はドレインなど遮光性を有する導電膜で形成されていることが多い。

【0007】

また、容量素子の容量値を大きくするためには、容量素子の占有面積を大きくする、具体的には一对の電極が重畳している面積を大きくするという手段がある。しかしながら、表示装置において、一对の電極が重畳している面積を大きくするために遮光性を有する導電膜の面積を大きくすると、画素の開口率が低減し、画像の表示品位が低下する。

【0008】

そこで、上記課題に鑑みて、本発明の一態様は、開口率が高く、且つ容量値を増大させることが可能な容量素子を有する半導体装置を提供することを課題の一つとする。また、製造コストが低い半導体装置を提供することを課題の一つとする。または、新規な半導体装置などを提供することを課題の一つとする。

【0009】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課

10

20

30

40

50

題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】**

**【0010】**

本発明の一態様は、第1の酸化物半導体膜と、第2の酸化物半導体膜とを含むトランジスタと、一対の電極間に絶縁膜を含む容量素子と、を有する半導体装置であって、トランジスタは、第1の酸化物半導体膜と、第1の酸化物半導体膜に接して設けられたゲート絶縁膜と、ゲート絶縁膜に接して設けられ、第1の酸化物半導体膜と重畳する位置に設けられた第2の酸化物半導体膜と、第1の酸化物半導体膜に接続されたソース電極及びドレイン電極と、を有し、容量素子の一対の電極の一方が、第2の酸化物半導体膜と同一表面上に設けられることを特徴とする半導体装置である。10

**【0011】**

また、本発明の他の一態様は、第1の酸化物半導体膜と、第2の酸化物半導体膜とを含むトランジスタと、一対の電極間に絶縁膜を含む容量素子と、を有する半導体装置であって、トランジスタは、第2の酸化物半導体膜を含むゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と重畳する位置の第1の酸化物半導体膜と、第1の酸化物半導体膜上のソース電極及びドレイン電極と、を有し、容量素子の一対の電極の一方が、第2の酸化物半導体膜と同一表面上に設けられることを特徴とする半導体装置である。

**【0012】**

また、本発明の他の一態様は、第1の酸化物半導体膜と、第2の酸化物半導体膜とを含むトランジスタと、一対の電極間に絶縁膜を含む容量素子と、を有する半導体装置であって、トランジスタは、第1の酸化物半導体膜と、第1の酸化物半導体膜上のソース電極及びドレイン電極と、第1の酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の第1の酸化物半導体膜と重畳する位置の第2の酸化物半導体膜を含むゲート電極と、を有し、容量素子の一対の電極の一方が、第2の酸化物半導体膜と同一表面上に設けられることを特徴とする半導体装置である。20

**【0013】**

また、上記各構成において、容量素子の一対の電極の他方が、第1の酸化物半導体膜と同一表面上に設けられると好ましい。また、容量素子は、可視光において透光性を有すると好ましい。30

**【0014】**

また、上記各構成において、第1の酸化物半導体膜及び第2の酸化物半導体膜は、 $In - M - Zn$ 酸化物（MはAl、Ti、Ga、Y、Zr、La、Ce、Nd、SnまたはHfを表す）であると好ましい。

**【0015】**

また、上記各構成の半導体装置を用いる、表示装置及び電子機器も本発明の一態様に含まれる。

**【発明の効果】**

**【0016】**

本発明の一態様により、開口率が高く、且つ容量値を増大させることができ容量素子を有する半導体装置を提供することができる。また、製造コストが低い半導体装置を提供することができる。または、新規な半導体装置などを提供することができる。40

**【0017】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

**【図面の簡単な説明】**

**【0018】**

10

20

30

40

50

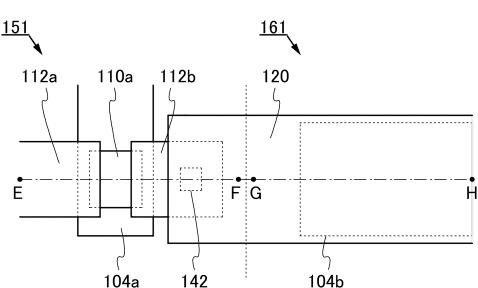

【図 1】半導体装置の一態様を示す上面図及び断面図。

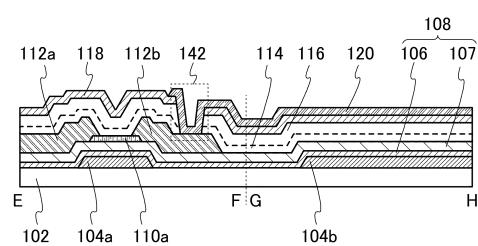

【図 2】半導体装置の作製方法の一態様を示す断面図。

【図 3】半導体装置の作製方法の一態様を示す断面図。

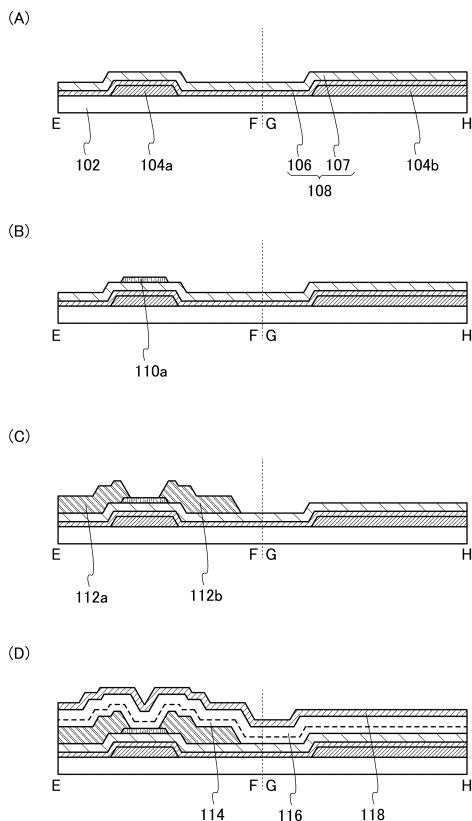

【図 4】半導体装置の一態様を示す上面図及び断面図。

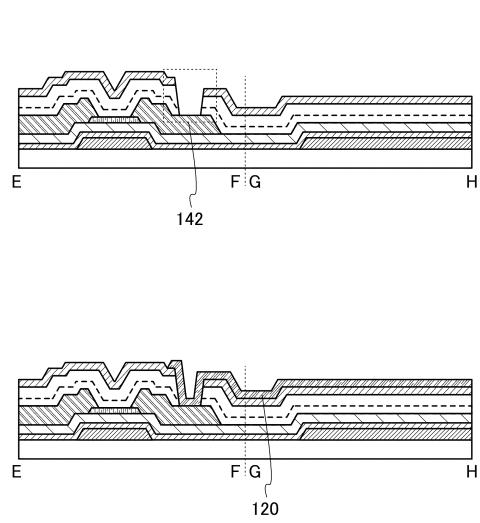

【図 5】半導体装置の作製方法の一態様を示す断面図。

【図 6】半導体装置の作製方法の一態様を示す断面図。

【図 7】半導体装置の一態様を示す上面図及び断面図。

【図 8】半導体装置の一態様を示す上面図及び断面図。

【図 9】半導体装置の作製方法の一態様を示す断面図。

【図 10】半導体装置の作製方法の一態様を示す断面図。

【図 11】半導体装置の一形態を示す断面図及びバンド図。

10

【図 12】表示装置を説明するブロック図及び回路図。

【図 13】表示モジュールを説明する図。

【図 14】電子機器を説明する図。

【図 15】半導体装置の一態様を示す断面図。

【図 16】半導体装置の一態様を示す断面図。

【図 17】半導体装置の一態様を示す上面図及び断面図。

【図 18】半導体装置の一態様を示す上面図及び断面図。

【図 19】半導体装置の一態様を示す断面図。

【図 20】半導体装置の一態様を示す断面図。

【図 21】半導体装置の一態様を示す断面図。

【図 22】半導体装置の一態様を示す断面図。

20

**【発明を実施するための形態】**

**【0019】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。但し、本発明の一態様は以下の説明に限定されず、本発明の主旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明の一態様は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態において、同一部分または同様の機能を有する部分には、同一の符号または同一のハッチパターンを異なる図面間で共通して用い、その繰り返しの説明は省略する。

30

**【0020】**

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

**【0021】**

また、本明細書等において用いる第1、第2等の序数詞は、構成要素の混合を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

40

**【0022】**

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

**【0023】**

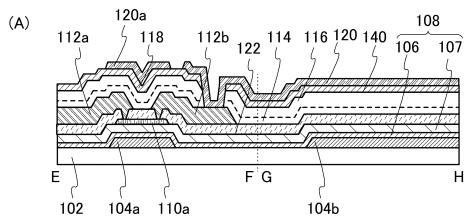

(実施の形態1)

本実施の形態では、本発明の一態様の半導体装置について、図1乃至図3を用いて説明する。

**【0024】**

<半導体装置の構成例>

50

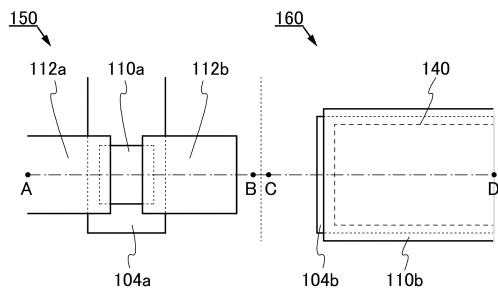

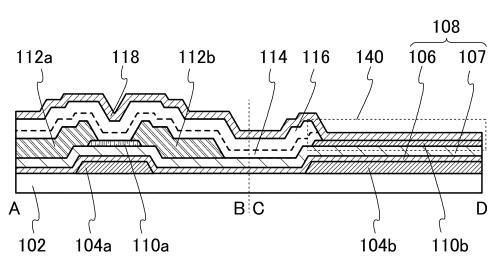

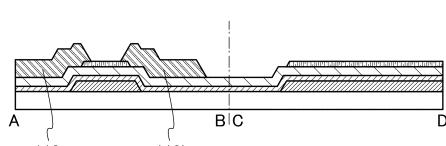

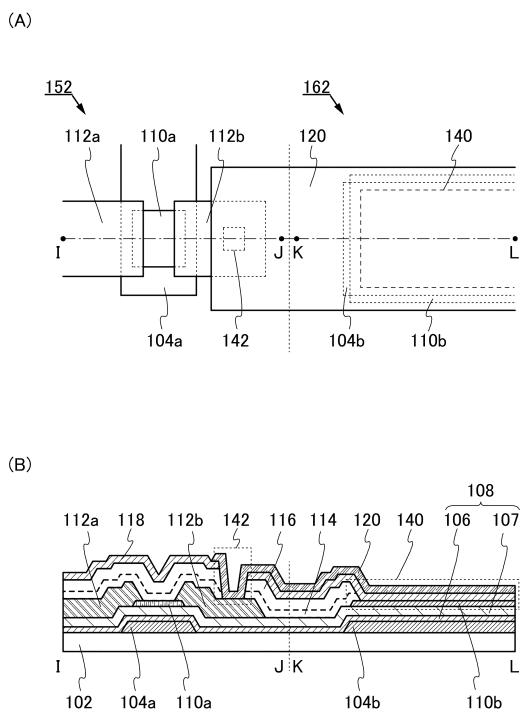

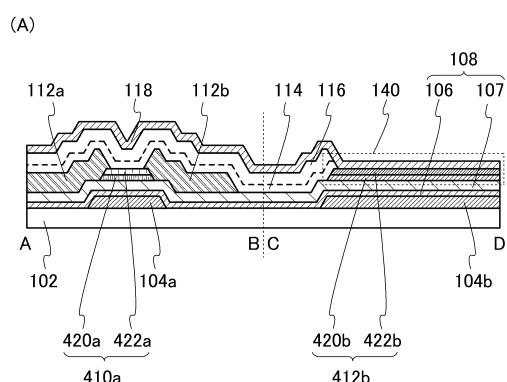

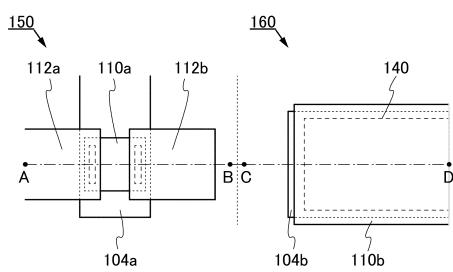

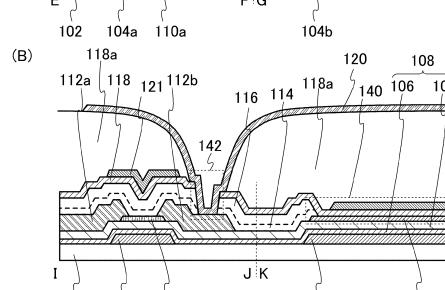

図1( A )は、本発明の一態様の半導体装置の上面図であり、図1( B )は、図1( A )の一点鎖線A - B間、及び一点鎖線C - D間における切断面の断面図に相当する。なお、図1( A )において、煩雑になることを避けるため、半導体装置の構成要素の一部(ゲート絶縁膜等)を省略して図示している。

#### 【0025】

図1( A )、( B )に示す半導体装置は、第1の酸化物半導体膜110aと、第2の酸化物半導体膜104aとを含むトランジスタ150と、一対の電極間に絶縁膜を含む容量素子160と、を有する。なお、容量素子160において、一対の電極の一方が第2の酸化物半導体膜104aと同一平面上の第2の酸化物半導体膜104bであり、一対の電極の他方が第1の酸化物半導体膜110aと同一平面上の第1の酸化物半導体膜110bである。

10

#### 【0026】

トランジスタ150は、基板102上の第2の酸化物半導体膜104aを含むゲート電極と、第2の酸化物半導体膜104aを含むゲート電極上のゲート絶縁膜として機能する絶縁膜108と、絶縁膜108上の第2の酸化物半導体膜104aを含むゲート電極と重畠する位置の第1の酸化物半導体膜110aと、第1の酸化物半導体膜110a上のソース電極112a及びドレイン電極112bとを有する。別言すると、トランジスタ150は、第1の酸化物半導体膜110aと、第1の酸化物半導体膜110aに接して設けられたゲート絶縁膜として機能する絶縁膜108と、絶縁膜108に接して設けられ、第1の酸化物半導体膜110aと重畠する位置に設けられた第2の酸化物半導体膜104aと、第1の酸化物半導体膜110aに接続されたソース電極112a及びドレイン電極112bとを有する。なお、図1( A )、( B )に示すトランジスタ150は、所謂ボトムゲート構造である。

20

#### 【0027】

なお、第1の酸化物半導体膜110aは、トランジスタ150のチャネル領域として機能する。また、第2の酸化物半導体膜104aは、トランジスタ150のゲート電極として機能する。よって、第1の酸化物半導体膜110aよりも第2の酸化物半導体膜104aの抵抗率が低い。また、第1の酸化物半導体膜110aと第2の酸化物半導体膜104aは、同一の金属元素を有すると好ましい。第1の酸化物半導体膜110aと第2の酸化物半導体膜104aを同一の金属元素を有する構成とすることで、製造装置(例えば、成膜装置、加工装置等)を共通に用いることが可能となるため、製造コストを抑制することができる。

30

#### 【0028】

したがって、トランジスタ150は、第1の酸化物半導体膜110aと、第1の酸化物半導体膜110aに接する絶縁膜108と、絶縁膜108と接し、第1の酸化物半導体膜110aと重畠する位置の第2の酸化物半導体膜104aと、を有し、第1の酸化物半導体膜110aと第2の酸化物半導体膜104aは、同一の金属元素を有し、第1の酸化物半導体膜110aよりも第2の酸化物半導体膜104aの抵抗率が低い。

#### 【0029】

また、第2の酸化物半導体膜104a、104bに、別途金属膜等で形成される配線等を接続してもよい。例えば、図1に示す半導体装置を表示装置の画素部のトランジスタ及び容量素子に用いる場合、引き回し配線、またはゲート配線等を金属膜で形成し、該金属膜に第2の酸化物半導体膜104a、104bを接続させる構成を用いてもよい。引き回し配線、またはゲート配線等を金属膜で形成することによって、配線抵抗を下げる事が可能となるため、信号遅延等を抑制することができる。

40

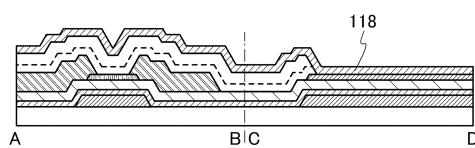

#### 【0030】

また、トランジスタ150上、より詳しくは、第1の酸化物半導体膜110a、ソース電極112a及びドレイン電極112b上に絶縁膜114、116、118が形成されている。絶縁膜114、116、118は、トランジスタ150の保護絶縁膜としての機能を有する。

50

**【 0 0 3 1 】**

容量素子 160 は、基板 102 上の一対の電極の一方の電極としての機能を有する第 2 の酸化物半導体膜 104b と、第 2 の酸化物半導体膜 104b 上の誘電体膜として機能する絶縁膜 108 と、絶縁膜 108 を介して第 2 の酸化物半導体膜 104b と重畳する位置の一対の電極の他方の電極としての機能を有する第 1 の酸化物半導体膜 110b と、を有する。また、容量素子 160 上、より詳しくは、第 1 の酸化物半導体膜 110b 上に保護絶縁膜としての機能を有する絶縁膜 118 が形成されている。

**【 0 0 3 2 】**

なお、上述のように絶縁膜 108 は、トランジスタ 150 においては、ゲート絶縁膜として機能し、容量素子 160 においては、誘電体膜として機能する。また、本実施の形態においては、絶縁膜 108 は、絶縁膜 106 と、絶縁膜 107 との積層構造である。ただし、本発明の一態様はこれに限定されず、絶縁膜 108 が単層構造、または 3 層以上の積層構造でもよい。

10

**【 0 0 3 3 】**

また、容量素子 160 は、透光性を有する。すなわち、容量素子 160 が有する、第 1 の酸化物半導体膜 110b、第 2 の酸化物半導体膜 104b、及び絶縁膜 108 は、それぞれ透光性を有する材料により構成される。このように、容量素子 160 が透光性を有することで、画素内のトランジスタが形成される箇所以外の領域に大きく（大面積に）形成することができるため、開口率を高めつつ容量値を増大させた半導体装置を得ることができる。この結果、表示品位の優れた半導体装置を得ることができる。また、容量素子 160 としては、トランジスタ 150 の作製工程を利用することで作製できる。したがって、製造コストが低い半導体装置を得ることができる。

20

**【 0 0 3 4 】**

なお、トランジスタ 150 及び容量素子 160 に用いる絶縁膜 106、並びにトランジスタ 150 及び容量素子 160 上に設けられる絶縁膜 118 としては、少なくとも水素を含む絶縁膜を用いる。また、トランジスタ 150 及び容量素子 160 に用いる絶縁膜 107、並びにトランジスタ 150 及び容量素子 160 上に設けられる絶縁膜 114、116 としては、少なくとも酸素を含む絶縁膜を用いる。このように、トランジスタ 150 及び容量素子 160 に用いる絶縁膜、並びにトランジスタ 150 及び容量素子 160 上に用いる絶縁膜を、上述の構成の絶縁膜とすることによって、トランジスタ 150 及び容量素子 160 が有する第 1 の酸化物半導体膜及び第 2 の酸化物半導体膜の抵抗率を制御することができる。

30

**【 0 0 3 5 】**

具体的には、トランジスタ 150 において、第 1 の酸化物半導体膜 110a は、チャネル領域として用いるため、第 1 の酸化物半導体膜 110b、第 2 の酸化物半導体膜 104a、104b と比較し抵抗率が高い。一方で、第 1 の酸化物半導体膜 110b、及び第 2 の酸化物半導体膜 104a、104b は電極としての機能を有するため、第 1 の酸化物半導体膜 110a と比較し抵抗率が低い。

30

**【 0 0 3 6 】**

ここで、第 1 の酸化物半導体膜 110a、110b、及び第 2 の酸化物半導体膜 104a、104b の抵抗率の制御方法について、以下説明を行う。

40

**【 0 0 3 7 】**

## &lt; 酸化物半導体の抵抗率の制御方法 &gt;

第 1 の酸化物半導体膜 110a、110b、及び第 2 の酸化物半導体膜 104a、104b に用いることのできる酸化物半導体膜は、膜中の酸素欠損及び / 又は膜中の水素、水等の不純物濃度によって、抵抗率を制御することができる半導体材料である。そのため、第 1 の酸化物半導体膜 110a、110b、及び第 2 の酸化物半導体膜 104a、104b へ酸素欠損及び / 又は不純物濃度が増加する処理、または酸素欠損及び / 又は不純物濃度が低減する処理を選択することによって、同一工程で形成されたそれぞれの酸化物半導体膜の抵抗率を制御することができる。

50

## 【0038】

具体的には、トランジスタ150のゲート電極として機能する第2の酸化物半導体膜104a、容量素子160の電極として機能する第2の酸化物半導体膜104b、及び容量素子160の電極として機能する第1の酸化物半導体膜110bに用いる酸化物半導体膜にプラズマ処理を行い、該酸化物半導体の膜中の酸素欠損を増加させる、および／または酸化物半導体の膜中の水素、水等の不純物を増加させることによって、キャリア密度が高く、抵抗率が低い酸化物半導体膜とすることができる。また、酸化物半導体膜に水素を含む絶縁膜を接して形成し、該水素を含む絶縁膜から酸化物半導体膜に水素を拡散させることによって、キャリア密度が高く、抵抗率が低い酸化物半導体膜とすることができます。

## 【0039】

一方、トランジスタ150のチャネル領域として機能する第1の酸化物半導体膜110aは、絶縁膜107、114、116を設けることによって、水素を含む絶縁膜106、118と接しない構成とする。絶縁膜107、114、116の少なくとも一つに酸素を含む絶縁膜、別言すると、酸素を放出することが可能な絶縁膜を適用することで、第1の酸化物半導体膜110aに酸素を供給することができる。酸素が供給された第1の酸化物半導体膜110aは、膜中または界面の酸素欠損が補填され抵抗率が高い酸化物半導体膜となる。なお、酸素を放出することが可能な絶縁膜としては、例えば、酸化シリコン膜、または酸化窒化シリコン膜を用いることができる。

## 【0040】

また、抵抗率が低い酸化物半導体膜を得るために、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて、水素、ボロン、リン、または窒素を酸化物半導体膜に注入してもよい。

## 【0041】

また、抵抗率が低い酸化物半導体膜を得るために、該酸化物半導体膜にプラズマ処理を行ってもよい。例えば、該プラズマ処理としては、代表的には、希ガス(He、Ne、Ar、Kr、Xe)、水素、及び窒素の中から選ばれた一種を含むガスを用いたプラズマ処理が挙げられる。より具体的には、Ar雰囲気下でのプラズマ処理、Arと水素の混合ガス雰囲気下でのプラズマ処理、アンモニア雰囲気下でのプラズマ処理、Arとアンモニアの混合ガス雰囲気下でのプラズマ処理、または窒素雰囲気下でのプラズマ処理などが挙げられる。

## 【0042】

上記プラズマ処理によって、酸化物半導体膜は、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損は、キャリアを発生する要因になり得る場合がある。また、酸化物半導体膜の近傍、より具体的には、酸化物半導体膜の下側または上側に接する絶縁膜から、水素が供給されると、上記酸素欠損と水素が結合すると、キャリアである電子を生成する場合がある。

## 【0043】

一方、酸素欠損が補填され、水素濃度が低減された酸化物半導体膜は、高純度真性化、又は実質的に高純度真性化された酸化物半導体膜といえる。ここで、実質的に真性とは、酸化物半導体膜のキャリア密度が、 $1 \times 10^{17}$ 個/cm<sup>3</sup>未満であること、好ましくは $1 \times 10^{13}$ 個/cm<sup>3</sup>未満であること、さらに好ましくは $1 \times 10^{-9}$ 個/cm<sup>3</sup>以上 $1 \times 10^{11}$ 個/cm<sup>3</sup>未満であることを指す。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができます。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度を低減することができる。

## 【0044】

また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6$ μmでチャネル長Lが $10$ μmの素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が $1$ Vから $10$ Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$ A以下

10

20

30

40

50

という特性を得ることができる。したがって、上述した高純度真性または実質的に高純度真性である酸化物半導体膜を用いる第1の酸化物半導体膜110aをチャネル領域に用いるトランジスタ150は、電気特性の変動が小さく、信頼性の高いトランジスタとなる。

#### 【0045】

絶縁膜106として、例えば、水素を含む絶縁膜、別言すると水素を放出することが可能な絶縁膜、代表的には窒化シリコン膜を用いることで、第2の酸化物半導体膜104a、104bに水素を供給することができる。また、絶縁膜118としては、例えば、絶縁膜106と同様に水素を含む絶縁膜を用いることで、第1の酸化物半導体膜110bに水素を供給することができる。水素を放出することが可能な絶縁膜としては、膜中の含有水素濃度が $1 \times 10^{22}$ atoms/cm<sup>3</sup>以上であると好ましい。このような絶縁膜を第2の酸化物半導体膜104a、104b及び第1の酸化物半導体膜110bに接して形成することで、第2の酸化物半導体膜104a、104b及び第1の酸化物半導体膜110bに効果的に水素を含有させることができる。このように、第2の酸化物半導体膜104a、104b及び第1の酸化物半導体膜110bに接する絶縁膜の構成を変えることによって、酸化物半導体膜の抵抗率を制御することができる。10

#### 【0046】

酸化物半導体膜に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。したがって、水素が含まれている絶縁膜と接して設けられた第2の酸化物半導体膜104a、104b及び第1の酸化物半導体膜110bは、第1の酸化物半導体膜110aよりもキャリア密度の高い酸化物半導体膜となる。20

#### 【0047】

トランジスタ150のチャネル領域が形成される第1の酸化物半導体膜110aは、水素ができる限り低減されていることが好ましい。具体的には、第1の酸化物半導体膜110aにおいて、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られる水素濃度を、 $2 \times 10^{20}$ atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$ atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下とする。30

#### 【0048】

一方、トランジスタ150のゲート電極及び容量素子160の電極として機能する第2の酸化物半導体膜104a、104bと、容量素子160の電極として機能する酸化物半導体膜110bは、第1の酸化物半導体膜110aよりも水素濃度及び/又は酸素欠損量が多く、抵抗率が低い酸化物半導体膜である。

#### 【0049】

また、第1の酸化物半導体膜110a、110bと、第2の酸化物半導体膜104a、104bは、同一の金属元素を有する。第1の酸化物半導体膜110a、110bと、第2の酸化物半導体膜104a、104bを同一の金属元素を有する構成とすることで、製造コストを低減できるため好ましい。ただし、第1の酸化物半導体膜110a、110bと、第2の酸化物半導体膜104a、104bは、同一の金属元素を有していても、組成が異なる場合がある。例えば、トランジスタ及び容量素子の作製工程中に、膜中の金属元素が脱離し、異なる金属組成となる場合がある。40

#### 【0050】

このように、本発明の一態様の半導体装置においては、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同時に形成する、別言すると、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同一表面上に形成することで、製造コストを低減することが可能となる。また、50

トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜は、酸化物半導体膜を含む構成である。該酸化物半導体膜に適切な処理を行うことで、抵抗率が低く、且つ透光性を有する導電膜とすることができる。該導電膜を用いることで、トランジスタおよび／または容量素子に透光性を付与することができる。

#### 【0051】

ここで、図1(A)、(B)に示す半導体装置のその他の構成要素の詳細について、以下説明を行う。

#### 【0052】

##### <基板>

基板102の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板102として用いてもよい。また、シリコンや炭化シリコンを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板102として用いてもよい。なお、基板102として、ガラス基板を用いる場合、第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)、第9世代(2400mm×2800mm)、第10世代(2950mm×3400mm)等の大面積基板を用いることで、大型の表示装置を作製することができる。また、基板102として、可撓性基板を用い、可撓性基板上に直接、トランジスタ150、容量素子160等を形成してもよい。

10

#### 【0053】

これらその他にも、基板102として、様々な基板を用いて、トランジスタを形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板の一例としては、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はSOI基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

30

#### 【0054】

なお、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、石材基板、木材基板、布基板(天然纖維(絹、綿、麻)、合成纖維(ナイロン、ポリウレタン、ポリエステル)若しくは再生纖維(アセテート、キュプラ、レーヨン、再生ポリエステル)などを含む)、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

40

#### 【0055】

##### <第1の酸化物半導体膜及び第2の酸化物半導体膜>

第1の酸化物半導体膜110a、110b、及び第2の酸化物半導体膜104a、104bは、少なくともインジウム(In)、亜鉛(Zn)及びM(Al、Ti、Ga、Y、

50

Zr、La、Ce、SnまたはHf等の金属)を含むIn-M-Zn酸化物で表記される膜を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

#### 【0056】

スタビライザーとしては、上記Mで記載の金属を含め、例えば、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)等がある。10

#### 【0057】

第1の酸化物半導体膜110a、110b、及び第2の酸化物半導体膜104a、104bを構成する酸化物半導体として、例えば、In-Ga-Zn系酸化物、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。20

#### 【0058】

なお、ここで、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### 【0059】

また、第1の酸化物半導体膜110a、110bと、第2の酸化物半導体膜104a、104bは、上記酸化物のうち、同一の金属元素を有する。第1の酸化物半導体膜110a、110bと、第2の酸化物半導体膜104a、104bを同一の金属元素として、製造コストを低減させることができる。例えば、同一の金属組成の金属酸化物ターゲットを用いることで製造コストを低減させることができる。また同一の金属組成の金属酸化物ターゲットを用いることによって、酸化物半導体膜を加工する際のエッチングガスまたはエッティング液を共通して用いることができる。30

#### 【0060】

##### <絶縁膜>

トランジスタ150のゲート絶縁膜、及び容量素子160の誘電体膜として機能する絶縁膜106、107としては、プラズマCVD法、スパッタリング法等により、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜および酸化ネオジム膜を一種以上含む絶縁層を、それぞれ用いることができる。なお、絶縁膜106、107の積層構造とせずに、上述の材料から選択された単層の絶縁層を用いてもよい。40

#### 【0061】

なお、トランジスタ150のチャネル領域として機能する第1の酸化物半導体膜110aと接する絶縁膜107は、酸化物絶縁膜であることが好ましく、化学量論的組成よりも過剰に酸素を含有する領域(酸素過剰領域)を有することがより好ましい。別言すると、絶縁膜107は、酸素を放出することが可能な絶縁膜である。なお、絶縁膜107に酸素

10

20

30

40

50

過剰領域を設けるには、例えば、酸素雰囲気下にて絶縁膜 107 を形成すればよい。または、成膜後の絶縁膜 107 に酸素を導入して、酸素過剰領域を形成してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

#### 【0062】

また、絶縁膜 106、107 として、酸化ハフニウムを用いる場合、以下の効果を奏する。酸化ハフニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、等価酸化膜厚に対して物理的な膜厚を大きくできるため、等価酸化膜厚を 10 nm 以下または 5 nm 以下とした場合でも、トンネル電流によるリーク電流を小さくすることができます。すなわち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系や立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

10

#### 【0063】

なお、本実施の形態では、絶縁膜 106 として窒化シリコン膜を形成し、絶縁膜 107 として酸化シリコン膜を形成する。窒化シリコン膜は、酸化シリコン膜と比較して比誘電率が高く、酸化シリコン膜と同等の静電容量を得るのに必要な膜厚が大きいため、トランジスタ 150 のゲート絶縁膜及び容量素子 160 の誘電体膜として機能する絶縁膜 108 として、窒化シリコン膜を含むことで絶縁膜を物理的に厚膜化することができる。よって、トランジスタ 150 及び容量素子 160 の絶縁耐圧の低下を抑制、さらには絶縁耐圧を向上させて、トランジスタ 150 及び容量素子 160 の静電破壊を抑制することができる。

20

#### 【0064】

##### <ソース電極及びドレイン電極>

ソース電極 112a、及びドレイン電極 112b に用いることのできる材料としては、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニア、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いることができる。例えば、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、モリブデン膜上に銅膜を積層した二層構造、モリブデンとタングステンを含む合金膜上に銅膜を積層した二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。また、ソース電極 112a、及びドレイン電極 112b を三層構造とする場合、一層目及び三層目には、チタン、窒化チタン、モリブデン、タングステン、モリブデンとタングステンを含む合金、モリブデンとジルコニアを含む合金、又は窒化モリブデンでなる膜を形成し、2 層目には、銅、アルミニウム、金又は銀、或いは銅とマンガンの合金等の低抵抗材料でなる膜を形成することができる。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。また、ソース電極 112a、及びドレイン電極 112b に用いることのできる材料は、例えば、スパッタリング法を用いて形成することができる。

30

#### 【0065】

##### <保護絶縁膜>

トランジスタ 150 の保護絶縁膜として機能する絶縁膜 114、116、118 及び容量素子 160 の保護絶縁膜として機能する絶縁膜 118 としては、プラズマ CVD 法、スパッタリング法等により、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジ

40

50

ルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜および酸化ネオジム膜を一種以上含む絶縁層を、それぞれ用いることができる。

#### 【0066】

なお、容量素子160において、絶縁膜118は、容量素子160の電極として機能する第1の酸化物半導体膜110bの抵抗率を低下させる機能も有する。

#### 【0067】

また、トランジスタ150のチャネル領域として機能する第1の酸化物半導体膜110aと接する絶縁膜114は、酸化物絶縁膜であることが好ましく、酸素を放出することが可能な絶縁膜を用いる。酸素を放出することが可能な絶縁膜を別言すると、化学量論的組成よりも過剰に酸素を含有する領域（酸素過剰領域）を有する絶縁膜である。なお、絶縁膜114に酸素過剰領域を設けるには、例えば、酸素雰囲気下にて絶縁膜114を形成すればよい。または、成膜後の絶縁膜114に酸素を導入して、酸素過剰領域を形成してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

10

#### 【0068】

絶縁膜114として、酸素を放出することが可能な絶縁膜を用いることで、トランジスタ150のチャネル領域として機能する第1の酸化物半導体膜110aに酸素を移動させ、第1の酸化物半導体膜110aの酸素欠損量を低減することが可能となる。例えば、膜の表面温度が100以上700以下、好ましくは100以上500以下の加熱処理で行われる、昇温脱離ガス分析（以下、TDS分析とする。）によって測定される酸素分子の放出量が、 $1.0 \times 10^{18}$ 分子/cm<sup>3</sup>以上ある絶縁膜を用いることで、第1の酸化物半導体膜110aに含まれる酸素欠損量を低減することができる。

20

#### 【0069】

また、絶縁膜114の厚さは、5nm以上150nm以下、好ましくは5nm以上50nm以下、好ましくは10nm以上30nm以下とすることができる。絶縁膜116の厚さは、30nm以上500nm以下、好ましくは150nm以上400nm以下とすることができる。

#### 【0070】

また、絶縁膜114、116は、同種の材料の絶縁膜を用いることができるため、絶縁膜114と絶縁膜116の界面が明確に確認できない場合がある。したがって、本実施の形態においては、絶縁膜114と絶縁膜116の界面は、破線で図示している。なお、本実施の形態においては、絶縁膜114と絶縁膜116の2層構造について説明したが、これに限定されず、例えば、絶縁膜114の単層構造、絶縁膜116の単層構造、または3層以上の積層構造としてもよい。

30

#### 【0071】

なお、ソース電極112a及びドレイン電極112bと、第1の酸化物半導体膜110aとの間に、絶縁膜122を設けてもよい。その場合の例を、図17(A)、(B)に示す。ソース電極112a及びドレイン電極112bと、第1の酸化物半導体膜110aとは、絶縁膜122に設けられたコンタクトホールを介して接続されている。絶縁膜122は、絶縁膜108で述べた内容と同様な材質や膜質を採用することができる。

40

#### 【0072】

<表示装置の作製方法>

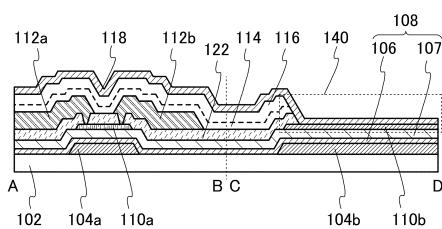

次に、図1(A)、(B)に示す半導体装置の作製方法の一例について、図2及び図3を用いて説明する。

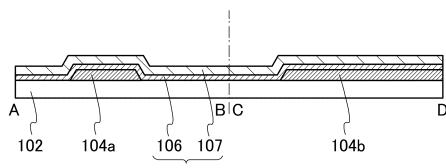

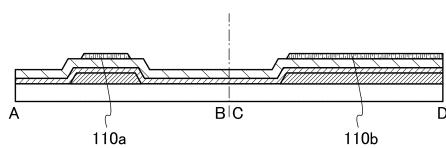

#### 【0073】

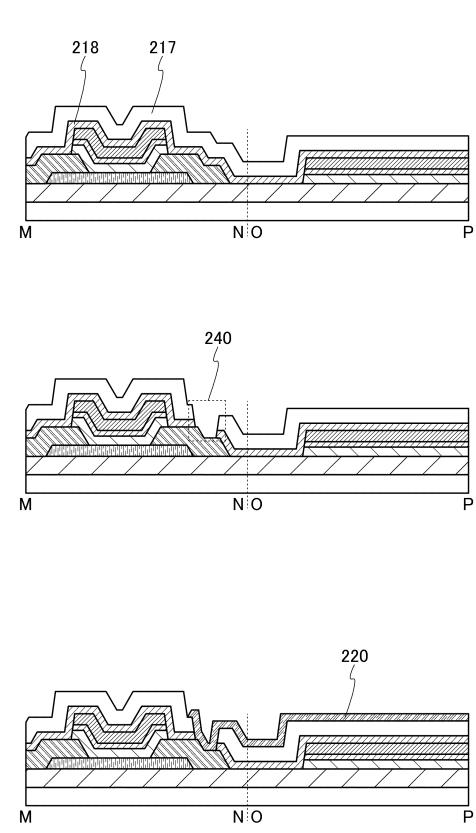

まず、基板102上に第2の酸化物半導体膜104aを含むゲート電極と、一対の電極の一方の電極として機能する第2の酸化物半導体膜104bを形成する。その後、基板102、及び第2の酸化物半導体膜104a、104b上に絶縁膜106、107を含む絶縁膜108を形成する（図2(A)参照）。

50

**【 0 0 7 4 】**

なお、基板 102、第2の酸化物半導体膜 104a、104b、及び絶縁膜 106、107としては、上述の列挙した材料の中から選択することで形成できる。なお、本実施の形態においては、基板 102 としてはガラス基板を用い、第2の酸化物半導体膜 104a、104b としては、In - Ga - Zn 酸化物膜 (In : Ga : Zn = 1 : 1 : 1 の金属酸化物ターゲットを使用。) を用い、絶縁膜 106 としては、水素を放出することが可能な窒化シリコン膜を用い、絶縁膜 107 としては、酸素を放出することが可能な酸化窒化シリコン膜を用いる。

**【 0 0 7 5 】**

第2の酸化物半導体膜 104a、104b に水素を放出することが可能な窒化シリコン膜を接して設けることにより、第2の酸化物半導体膜 104a、104b の抵抗率を下げることが可能となる。

10

**【 0 0 7 6 】**

また、第2の酸化物半導体膜 104a、104b は、基板 102 上に酸化物半導体膜を成膜後、該酸化物半導体膜の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで形成される。

**【 0 0 7 7 】**

次に、絶縁膜 108 上の第2の酸化物半導体膜 104a を含むゲート電極と重畠する位置に第1の酸化物半導体膜 110a と、絶縁膜 108 上の第2の酸化物半導体膜 104b と重畠する位置に第1の酸化物半導体膜 110b と、をそれぞれ形成する (図 2 (B) 参照)。

20

**【 0 0 7 8 】**

第1の酸化物半導体膜 110a、110b としては、上述の列挙した材料の中から選択することで形成できる。なお、本実施の形態においては、第1の酸化物半導体膜 110a、110b としては、In - Ga - Zn 酸化物膜 (In : Ga : Zn = 1 : 1 : 1 の金属酸化物ターゲットを使用。) を用いる。

**【 0 0 7 9 】**

また、第1の酸化物半導体膜 110a、110b は、絶縁膜 108 上に酸化物半導体膜を成膜後、該酸化物半導体膜の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで形成される。

30

**【 0 0 8 0 】**

また、第1の酸化物半導体膜 110a と、第1の酸化物半導体膜 110b は、同一の酸化物半導体膜より加工して形成されるため、少なくとも同一の金属元素を有する。また、第1の酸化物半導体膜 110a、110b のエッティング加工の際に、オーバーエッティングによって絶縁膜 107 の一部 (第1の酸化物半導体膜 110a、110b から露出した領域) がエッティングされ膜厚が減少することがある。

**【 0 0 8 1 】**

第1の酸化物半導体膜 110a、110b を形成後、熱処理を行うと好ましい。該熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下、より好ましくは 350 以上 450 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧雰囲気で行えばよい。また、熱処理の雰囲気は、不活性ガス雰囲気で熱処理を行った後に、第1の酸化物半導体膜 110a、110b から脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。ここで熱処理によって、絶縁膜 106、107、及び第1の酸化物半導体膜 110a、110b の少なくとも 1 つから水素や水などの不純物を除去することができる。なお、該熱処理は、第1の酸化物半導体膜 110a、110b を島状に加工する前に行ってもよい。

40

**【 0 0 8 2 】**

なお、第1の酸化物半導体膜 110a をチャネル領域とするトランジスタ 150 に安定した電気特性を付与するためには、第1の酸化物半導体膜 110a 中の不純物を低減し、第1の酸化物半導体膜 110a を真性または実質的に真性にすることが有効である。

50

**【0083】**

次に、絶縁膜108、及び第1の酸化物半導体膜110a、110b上に導電膜を成膜し、該導電膜の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで、絶縁膜108及び第1の酸化物半導体膜110a上にソース電極112a、及びドレイン電極112bを形成する(図2(C)参照)。

**【0084】**

ソース電極112a、及びドレイン電極112bとしては、上述の列挙した材料の中から選択することで形成できる。なお、本実施の形態においては、ソース電極112a、及びドレイン電極112bとしては、チタン膜と、アルミニウム膜と、チタン膜との3層の積層構造を用いる。

10

**【0085】**

次に、絶縁膜108、第1の酸化物半導体膜110a、110b、ソース電極112a、及びドレイン電極112b上に絶縁膜114、116を形成する(図2(D)参照)。

**【0086】**

絶縁膜114、116としては、上述の列挙した材料の中から選択することで形成できる。なお、本実施の形態においては、絶縁膜114、116としては、酸素を放出することが可能な酸化窒化シリコン膜を用いる。

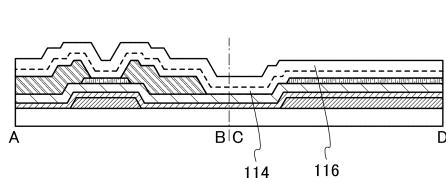

**【0087】**

次に、絶縁膜114、116の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで開口140を形成する(図3(A)参照)。

20

**【0088】**

開口140としては、第1の酸化物半導体膜110bが露出するように形成する。開口140の形成方法としては、例えば、ドライエッティング法を用いることができる。ただし、開口140の形成方法としては、これに限定されず、ウェットエッティング法、またはドライエッティング法とウェットエッティング法を組み合わせた形成方法としてもよい。なお、開口140を形成するためのエッティング工程によって、第1の酸化物半導体膜110bの膜厚が減少する場合がある。

**【0089】**

この後、熱処理を行うことが好ましい。該熱処理によって、絶縁膜114、または絶縁膜116に含まれる酸素の一部を第1の酸化物半導体膜110aに移動させ、第1の酸化物半導体膜110a中の酸素欠損を補填することができる。この結果、第1の酸化物半導体膜110aに含まれる酸素欠損量を低減することができる。一方、絶縁膜114と接しない第1の酸化物半導体膜110bの酸素欠損量は低減されないため、第1の酸化物半導体膜110bは、第1の酸化物半導体膜110aより多くの酸素欠損を含有することとなる。熱処理の条件としては、第1の酸化物半導体膜110a、110bを形成後の熱処理と同様とすることができます。

30

**【0090】**

次に、開口140を覆うように、絶縁膜116、及び第1の酸化物半導体膜110b上に絶縁膜118を形成する(図3(B)参照)。

**【0091】**

絶縁膜118としては、上述の列挙した材料の中から選択することで形成できる。なお、本実施の形態においては、絶縁膜118としては、水素を放出することが可能な窒化シリコン膜を用いる。絶縁膜118に含まれる水素が第1の酸化物半導体膜110bに拡散すると、第1の酸化物半導体膜110bの抵抗率が低下する。なお、第1の酸化物半導体膜110bの抵抗率の低下に伴い、図3(A)と図3(B)に示す第1の酸化物半導体膜110bのハッチングを変えて図示している。

40

**【0092】**

第1の酸化物半導体膜110bの抵抗率は、少なくとも第1の酸化物半導体膜110aよりも低く、好ましくは、 $1 \times 10^{-3}$  cm以上 $1 \times 10^{-4}$  cm未満、さらに好ましくは、 $1 \times 10^{-3}$  cm以上 $1 \times 10^{-1}$  cm未満であるとよい。なお、絶縁膜11

50

8は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、トランジスタ150に含まれる第1の酸化物半導体膜110aへ拡散するのを防ぐ効果も奏する。

#### 【0093】

また、本実施の形態の絶縁膜118として用いる窒化シリコン膜としては、ブロック性を高めるために、高温で成膜されることが好ましく、例えば100以上基板の歪み点以下、より好ましくは300以上400以下の温度で加熱して成膜することが好ましい。

#### 【0094】

また、第1の酸化物半導体膜110bの形成に伴い、容量素子160が作製される。容量素子160は、一対の電極間に誘電体層が挟持された構造であり、一対の電極の一方が第2の酸化物半導体膜104bであり、一対の電極の他方が第1の酸化物半導体膜110bである。また、絶縁膜108が容量素子160の誘電体層として機能する。

#### 【0095】

以上の工程によって、トランジスタ150と、容量素子160とを同一基板上に形成することができる。

#### 【0096】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0097】

##### (実施の形態2)

本実施の形態では、本発明の一態様の半導体装置について、実施の形態1に示す半導体装置の変形例について、図4乃至図6を用いて説明する。なお、実施の形態1の図1乃至図3で示した符号と同様の箇所または同様の機能を有する箇所については同様の符号を用い、その繰り返しの説明は省略する。

#### 【0098】

##### <半導体装置の構成例(変形例1)>

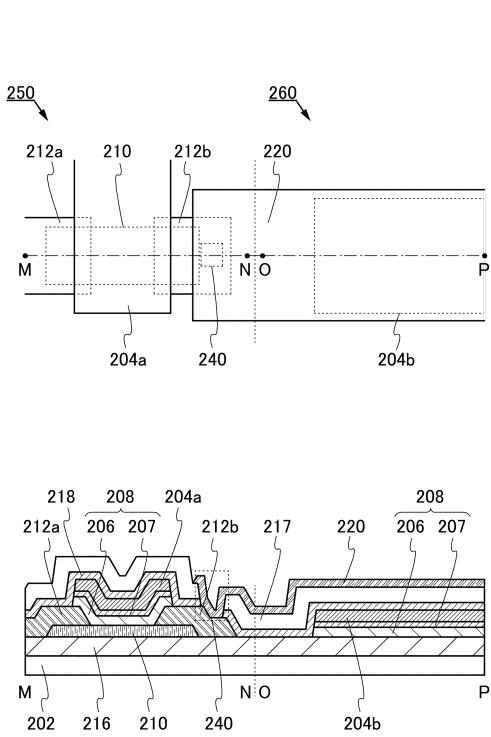

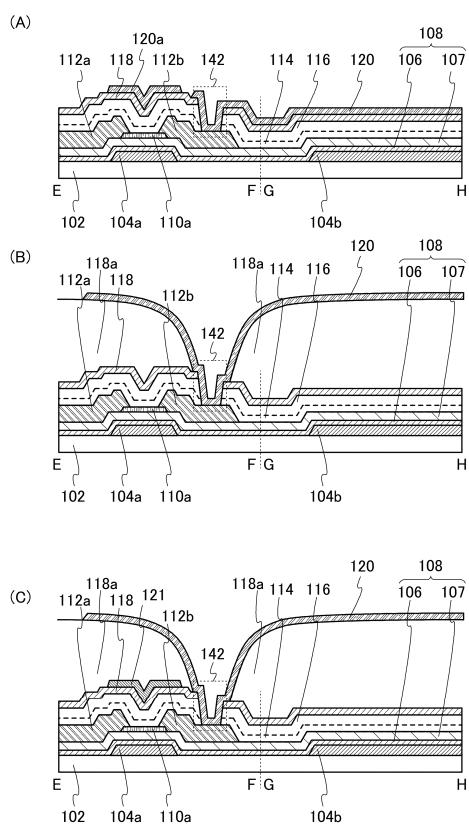

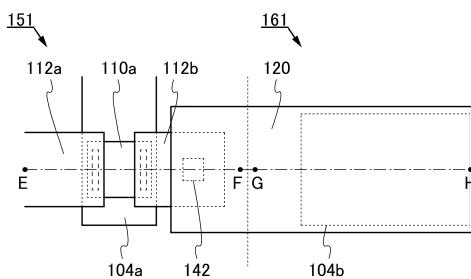

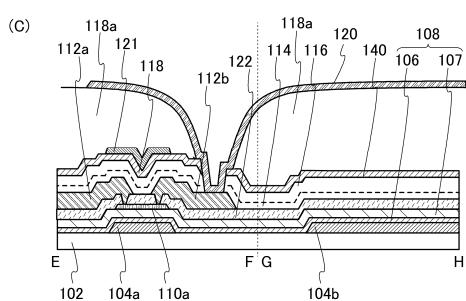

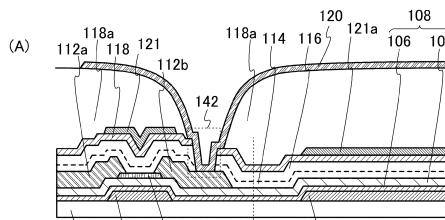

図4(A)は、本発明の一態様の半導体装置の上面図であり、図4(B)は、図4(A)の一点鎖線E-F間、及び一点鎖線G-Hにおける切断面の断面図に相当する。なお、図4(A)において、煩雑になることを避けるため、半導体装置の構成要素の一部(ゲート絶縁膜等)を省略して図示している。

#### 【0099】

図4(A)、(B)に示す半導体装置は、第1の酸化物半導体膜110aと、第2の酸化物半導体膜104aとを含むトランジスタ151と、一対の電極間に絶縁膜を含む容量素子161と、を有する。なお、容量素子161において、一対の電極の一方が第2の酸化物半導体膜104aと同一平面上の第1の酸化物半導体膜104bであり、一対の電極の他方が導電膜120である。

#### 【0100】

トランジスタ151は、基板102上の第2の酸化物半導体膜104aを含むゲート電極と、第2の酸化物半導体膜104aを含むゲート電極上のゲート絶縁膜として機能する絶縁膜108と、絶縁膜108上の第2の酸化物半導体膜104aを含むゲート電極と重畠する位置の第1の酸化物半導体膜110aと、第1の酸化物半導体膜110a上のソース電極112a及びドレイン電極112bとを有する。なお、図4(A)、(B)に示すトランジスタ151は、所謂ボトムゲート構造である。

#### 【0101】

また、トランジスタ151上、より詳しくは、第1の酸化物半導体膜110a、ソース電極112a及びドレイン電極112b上に絶縁膜114、116、118が形成されている。絶縁膜114、116、118は、トランジスタ151の保護絶縁膜としての機能を有する。また、絶縁膜114、116、118には、ドレイン電極112bに達する開口142が形成されており、開口142を覆うように絶縁膜118上に導電膜120が形成されている。導電膜120は、例えば、画素電極としての機能を有する。

10

20

30

40

50

**【0102】**

容量素子 161 は、基板 102 上の一対の電極の一方の電極としての機能を有する第 2 の酸化物半導体膜 104b と、第 2 の酸化物半導体膜 104b 上の誘電体膜として機能する絶縁膜 108、114、116、118 と、絶縁膜 108、114、116、118 を介して第 2 の酸化物半導体膜 104b と重畠する位置の一対の電極の他方の電極としての機能を有する導電膜 120 と、を有する。すなわち、導電膜 120 は、画素電極としての機能と容量素子の電極としての機能を有する。

**【0103】**

なお、上述のように絶縁膜 108 は、トランジスタ 151 においては、ゲート絶縁膜として機能し、容量素子 161 においては、誘電体膜の一部として機能する。また、絶縁膜 114、116、118 は、トランジスタ 151 においては、保護絶縁膜として機能し、容量素子 161 においては、誘電体膜の一部として機能する。なお、図 4 (A)、(B) においては、誘電体膜の一部として絶縁膜 114、116、118 を設ける構成について例示したが、これに限定されない。例えば、トランジスタ 151 の作製工程において、開口 142 を形成時に容量素子 161 の絶縁膜 114、116、118 を除去してもよい。

10

**【0104】**

また、容量素子 161 は、透光性を有する。すなわち、容量素子 161 が有する、第 2 の酸化物半導体膜 104b、絶縁膜 108、114、116、118、及び導電膜 120 は、それぞれ透光性を有する材料により構成される。このように、容量素子 161 が透光性を有することで、画素内のトランジスタが形成される箇所以外の領域に大きく（大面積に）形成することができるため、開口率を高めつつ容量値を増大させた半導体装置を得ることができる。この結果、表示品位の優れた半導体装置を得ることができる。また、容量素子 161 としては、トランジスタ 151 の作製工程を利用することで作製できる。したがって、製造コストが低い半導体装置を得ることができる。

20

**【0105】**

なお、絶縁膜 106、118 としては、少なくとも水素を含む絶縁膜を用いる。また、絶縁膜 107、114、116 としては、少なくとも酸素を含む絶縁膜を用いる。このように、トランジスタ 151 及び容量素子 161 に用いる絶縁膜またはトランジスタ 151 及び容量素子 161 に接する絶縁膜を、上述の構成の絶縁膜とすることによって、トランジスタ 151 及び容量素子 161 が有する第 1 の酸化物半導体膜及び第 2 の酸化物半導体膜の抵抗率を制御することができる。

30

**【0106】**

なお、第 1 の酸化物半導体膜 110a、及び第 2 の酸化物半導体膜 104a、104b の抵抗率については、実施の形態 1 の記載を参照することで、制御することができる。

**【0107】**

実施の形態 1 の図 1 (A)、(B) に記載の半導体装置と、図 4 (A)、(B) に示す半導体装置の主な違いとしては、容量素子 161 の他方の電極を導電膜 120 とした点である。このように、容量素子 161 の一対の電極の他方は、画素電極として機能する導電膜 120 としてもよい。

40

**【0108】**

このように、本発明の一態様の半導体装置においては、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同時に形成する、別言すると、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同一表面上に形成することで、製造コストを低減することができる。また、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜は、酸化物半導体膜を含む構成である。該酸化物半導体膜に適切な処理を行うことで、導電率が高く、且つ透光性を有する導電膜とすることができます。該導電膜を用いることで、トランジスタおよび / または容量素子に透光性を付与することができる。

**【0109】**

50

なお、ソース電極 112a 及びドレイン電極 112b と、第1の酸化物半導体膜 110aとの間に、絶縁膜 122 を設けてよい。その場合の例を、図 18 (A)、(B) に示す。

#### 【0110】

なお、導電膜 120 と同時に成膜し、同時にエッチングして、同時に形成した導電膜 120a をトランジスタのチャネル領域と重なるように設けてよい。その場合の例を、図 15 (A)、図 19 (A) に示す。導電膜 120a は、一例としては、導電膜 120 と同時に成膜し、同時にエッチングして、同時に形成するため、同じ材料を有している。そのため、プロセス工程の増加を抑制することができる。ただし、本発明の実施形態の一態様は、これに限定されない。導電膜 120a は、導電膜 120 とは異なる工程で形成してもよい。導電膜 120a は、トランジスタのチャネル領域と重なる領域を有している。したがって、導電膜 120a は、トランジスタの第2のゲート電極としての機能を有している。そのため、導電膜 120a は、第2の酸化物半導体膜 104a と接続されていてもよい。または、導電膜 120a は、第2の酸化物半導体膜 104a と接続されずに、第2の酸化物半導体膜 104a とは異なる信号や異なる電位が供給されていてもよい。

10

#### 【0111】

ここで、図 4 (A)、(B) に示す半導体装置のその他の構成要素の詳細について、以下説明を行う。

#### 【0112】

##### <導電膜>

20

導電膜 120 は、画素電極としての機能を有する。導電膜 120 としては、例えば、可視光において、透光性を有する材料を用いればよい。具体的には、インジウム (In)、亜鉛 (Zn)、錫 (Sn) の中から選ばれた一種を含む材料を用いるとよい。また、導電膜 120 としては、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物 (ITO)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。また、導電膜 120 としては、例えば、スパッタリング法を用いて形成することができる。

#### 【0113】

30

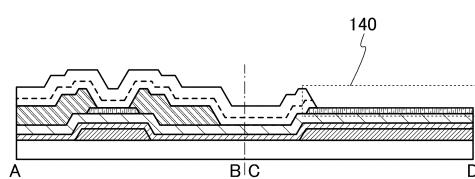

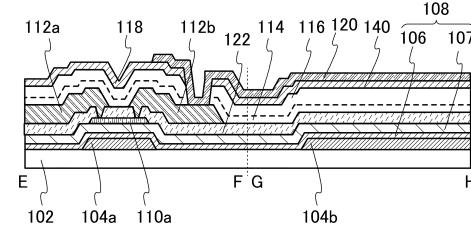

##### <表示装置の作製方法 (変形例 1)>

次に、図 4 (A)、(B) に示す半導体装置の作製方法の一例について、図 5 及び図 6 を用いて説明する。

#### 【0114】

まず、基板 102 上に第2の酸化物半導体膜 104a を含むゲート電極と、一対の電極の一方の電極として機能する第2の酸化物半導体膜 104b を形成する。その後、第2の酸化物半導体膜 104a、104b 上に絶縁膜 106、107 を含む絶縁膜 108 を形成する (図 5 (A) 参照)。

#### 【0115】

次に、絶縁膜 108 上の第2の酸化物半導体膜 104a を含むゲート電極と重畠する位置に第1の酸化物半導体膜 110a を形成する (図 5 (B) 参照)。

40

#### 【0116】

第1の酸化物半導体膜 110a は、絶縁膜 108 上に酸化物半導体膜を成膜し、該酸化物半導体膜の所望の領域が残るようにパターニングし、その後不要な領域をエッチングすることで形成される。

#### 【0117】

また、第1の酸化物半導体膜 110a のエッチング加工の際に、オーバーエッチングによって絶縁膜 107 の一部 (第1の酸化物半導体膜 110a から露出した領域) がエッチングされ膜厚が減少することがある。

#### 【0118】

50

第1の酸化物半導体膜110aを形成後、熱処理を行うと好ましい。該熱処理は、実施の形態1の第1の酸化物半導体膜110a形成後の熱処理を参酌することで行うことができる。

#### 【0119】

次に、絶縁膜108、及び第1の酸化物半導体膜110a上に導電膜を成膜し、該導電膜の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで第1の酸化物半導体膜110a上にソース電極112a、及びドレイン電極112bを形成する(図5(C)参照)。

#### 【0120】

次に、絶縁膜108、第1の酸化物半導体膜110a、ソース電極112a、及びドレイン電極112b上に絶縁膜114、116、118を形成する(図5(D)参照)。

10

#### 【0121】

次に、絶縁膜114、116、118の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで開口142を形成する(図6(A)参照)。

#### 【0122】

開口142としては、ドレイン電極112bが露出するように形成する。開口142の形成方法としては、例えば、ドライエッティング法を用いることができる。ただし、開口142の形成方法としては、これに限定されず、ウェットエッティング法、またはドライエッティング法とウェットエッティング法を組み合わせた形成方法としてもよい。

20

#### 【0123】

次に、開口142を覆うように絶縁膜118上に導電膜を成膜し、該導電膜の所望の領域が残るようにパターニング及びエッティングを行い、導電膜120を形成する(図6(B)参照)。

#### 【0124】

以上の工程によって、トランジスタ151と、容量素子161とを同一基板上に形成することができる。

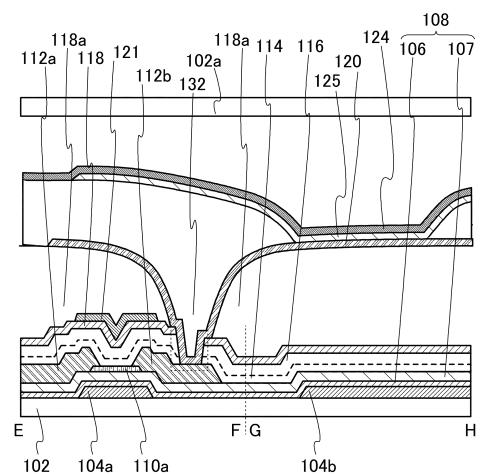

#### 【0125】

なお、絶縁膜118の上に、絶縁膜118aを配置してもよい。その場合の例を図15(B)、(C)、及び図19(B)、(C)に示す。絶縁膜118aとしては、例えば、有機樹脂材料を用いて形成することができる。絶縁膜118aに適用できる材料としては、例えば、アクリル系樹脂、ポリイミド系樹脂、ポリアミド系樹脂などが挙げられる。

30

#### 【0126】

なお、図15(C)、図19(C)に示すように、導電膜121を設けてもよい。導電膜121は、トランジスタのチャネル領域と重なるように設けてもよい。導電膜121は、導電膜120で述べた内容と同様な材料を用いて形成してもよい。導電膜121は、トランジスタのチャネル領域と重なる領域を有している。したがって、導電膜121は、トランジスタの第2のゲート電極としての機能を有している。そのため、導電膜121は、第2の酸化物半導体膜104aと接続されていてもよい。または、導電膜121は、第2の酸化物半導体膜104aと接続されずに、第2の酸化物半導体膜104aとは異なる信号や異なる電位が供給されていてもよい。

40

#### 【0127】

なお、導電膜121と同時に成膜し、同時にエッティングして、同時に形成した導電膜121aを容量素子の電極と重なるように設けて、容量素子を構成してもよい。その場合の例を図20(A)、(B)、(C)に示す。この結果、容量素子の容量値を大きくすることができます。

#### 【0128】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などを適宜組み合わせて用いることができる。

#### 【0129】

(実施の形態3)

50

本実施の形態では、本発明の一態様の半導体装置について、実施の形態1に示す半導体装置の変形例について、図7を用いて説明する。なお、実施の形態1の図1乃至図3で示した符号と同様の箇所または同様の機能を有する箇所については同様の符号を用い、その繰り返しの説明は省略する。

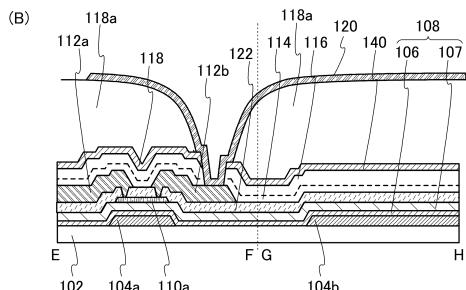

### 【0130】

<半導体装置の構成例(変形例2)>

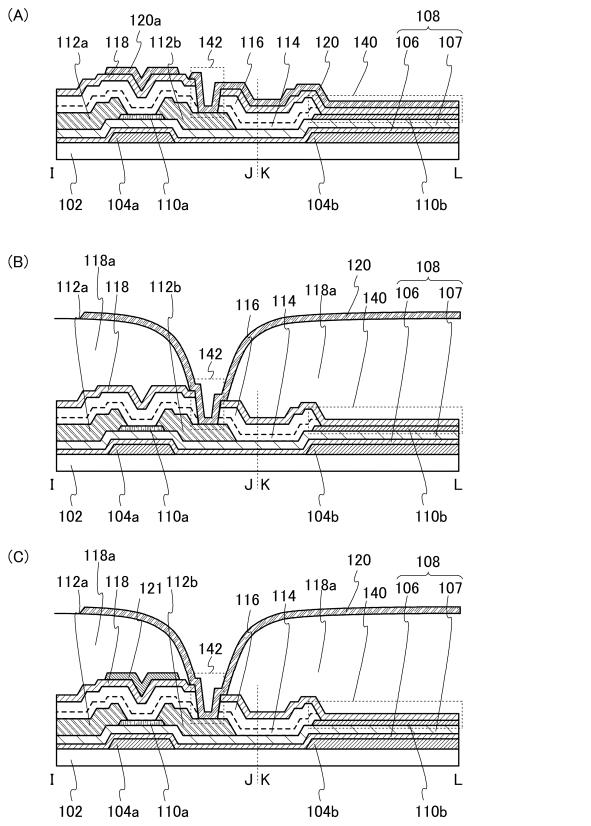

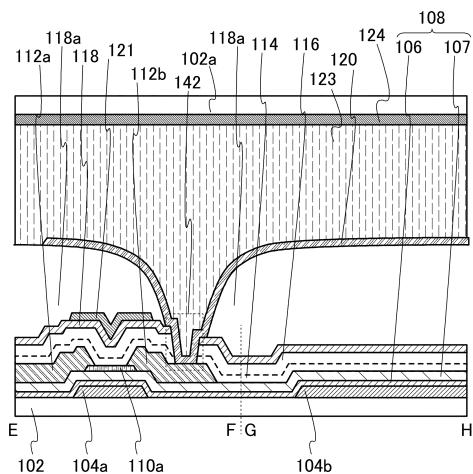

図7(A)は、本発明の一態様の半導体装置の上面図であり、図7(B)は、図7(A)の一点鎖線I-J間、及び一点鎖線K-Lにおける切断面の断面図に相当する。なお、図7(A)において、煩雑になることを避けるため、半導体装置の構成要素の一部(ゲート絶縁膜等)を省略して図示している。

10

### 【0131】

図7(A)、(B)に示す半導体装置は、第1の酸化物半導体膜110aと、第2の酸化物半導体膜104aとを含むトランジスタ152と、一対の電極間に絶縁膜を含む容量素子162と、を有する。

### 【0132】

トランジスタ152は、基板102上の第2の酸化物半導体膜104aを含むゲート電極と、第2の酸化物半導体膜104aを含むゲート電極上のゲート絶縁膜として機能する絶縁膜108と、絶縁膜108上の第2の酸化物半導体膜104aを含むゲート電極と重畠する位置の第1の酸化物半導体膜110aと、第1の酸化物半導体膜110a上のソース電極112a及びドレイン電極112bとを有する。なお、図7(A)、(B)に示すトランジスタ152は、所謂ボトムゲート構造である。

20

### 【0133】

また、トランジスタ152上、より詳しくは、第1の酸化物半導体膜110a、ソース電極112a及びドレイン電極112b上に絶縁膜114、116、118が形成されている。絶縁膜114、116、118は、トランジスタ152の保護絶縁膜としての機能を有する。また、絶縁膜114、116、118には、ドレイン電極112bに達する開口142が形成されており、開口142を覆うように絶縁膜118上に導電膜120が形成されている。導電膜120は、例えば、画素電極としての機能を有する。

### 【0134】

また、容量素子162において、一対の電極の一方が第2の酸化物半導体膜104bであり、一対の電極の他方が導電膜120である。また、容量素子162は、一対の電極間に、さらに電極を有する。該電極は、第1の酸化物半導体膜110aと同一平面上に形成された第1の酸化物半導体膜110bである。

30

### 【0135】

このように、一対の電極間にさらに電極を設ける構成とすることで、容量素子の面積を増加させずに、容量を大きくすることができる。容量素子162としては、例えば、以下の構造とみることができる。容量素子162は、第2の酸化物半導体膜104bと第1の酸化物半導体膜110aに挟持される絶縁膜108を誘電体膜とする第1の容量素子と、第1の酸化物半導体膜110aと導電膜120に挟持される絶縁膜118を誘電体膜とする第2の容量素子が積層して設けられる構造である。

40

### 【0136】

なお、上述のように絶縁膜108は、トランジスタ152において、ゲート絶縁膜として機能し、容量素子162において、誘電体膜の一部として機能する。また、絶縁膜114、116、118は、トランジスタ152において、保護絶縁膜として機能する。また、絶縁膜118は、容量素子162において、誘電体膜の一部として機能する。

### 【0137】

また、容量素子162は、透光性を有する。すなわち、容量素子162が有する、第1の酸化物半導体膜110b、第2の酸化物半導体膜104b、絶縁膜108、118、及び導電膜120は、それぞれ透光性を有する材料により構成される。このように、容量素子162が透光性を有することで、画素内のトランジスタが形成される箇所以外の領域に

50

大きく(大面積に)形成することができるため、開口率を高めつつ容量値を増大させた半導体装置を得ることができる。この結果、表示品位の優れた半導体装置を得ることができる。また、容量素子162としては、トランジスタ152の作製工程を利用することで作製できる。したがって、製造コストが低い半導体装置を得ることができる。

#### 【0138】

なお、絶縁膜106、118としては、少なくとも水素を含む絶縁膜を用いる。また、絶縁膜107、114、116としては、少なくとも酸素を含む絶縁膜を用いる。このように、トランジスタ152及び容量素子162に用いる絶縁膜またはトランジスタ152及び容量素子162に接する絶縁膜を、上述の構成の絶縁膜とすることによって、トランジスタ152及び容量素子162が有する第1の酸化物半導体膜及び第2の酸化物半導体膜の抵抗率を制御することができる。10

#### 【0139】

なお、第1の酸化物半導体膜110a、110b及び第2の酸化物半導体膜104a、104bの抵抗率については、実施の形態1の記載を参照することで、制御することができる。

#### 【0140】

実施の形態1の図1(A)、(B)に記載の半導体装置と、図7(A)、(B)に示す半導体装置の主な違いとしては、容量素子162の電極構造である。

#### 【0141】

本発明の一態様の半導体装置においては、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同時に形成する、別言すると、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同一表面上に形成することで、製造コストを低減することが可能となる。また、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜は、酸化物半導体膜を含む構成である。該酸化物半導体膜に適切な処理を行うことで、導電率が高く、且つ透光性を有する導電膜とすることができます。該導電膜を用いることで、トランジスタおよび/または容量素子に透光性を付与することができる。20

#### 【0142】

なお、図7(A)、(B)に示す半導体装置の作製方法としては、図1(A)、(B)に示す半導体装置、及び図4(A)、(B)に示す半導体装置の作製方法を組み合わせることで、形成することができる。30

#### 【0143】

なお、図15(A)と同様に、導電膜120aをトランジスタのチャネル領域と重なるように設けてもよい。その場合の例を図16(A)、及び図19(A)に示す。

#### 【0144】

また、図15(B)、(C)と同様に、絶縁膜118の上に、絶縁膜118aを配置してもよい。その場合の例を図16(B)、(C)、及び図19(B)、(C)に示す。

#### 【0145】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。40

#### 【0146】

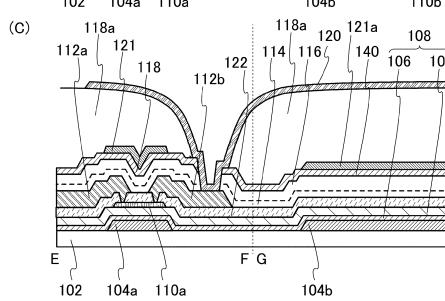

##### (実施の形態4)

本実施の形態では、本発明の一態様の半導体装置について、実施の形態1に示す半導体装置の変形例について、図8乃至図10を用いて説明する。なお、実施の形態1の図1乃至図3で示した符号と同様の箇所または同様の機能を有する箇所については同様の符号を用い、その繰り返しの説明は省略する。

#### 【0147】

##### <半導体装置の構成例(変形例3)>

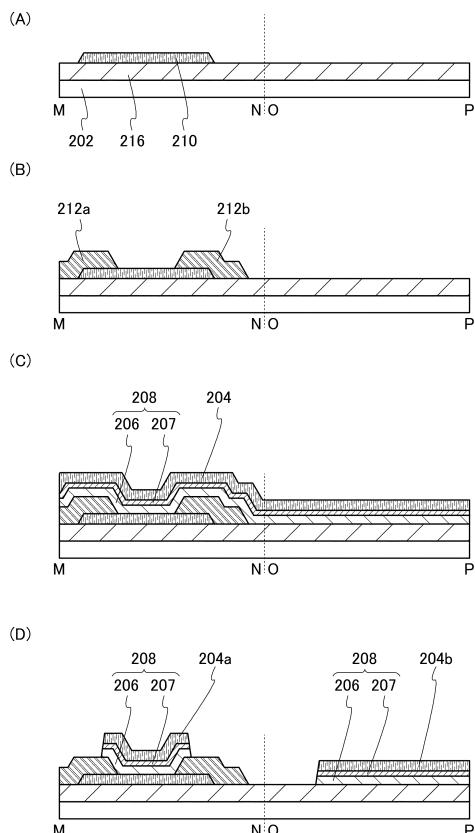

図8(A)は、本発明の一態様の半導体装置の上面図であり、図8(B)は、図8(A)の一点鎖線M-N間、及び一点鎖線O-P間における切断面の断面図に相当する。なお50

、図8(A)において、煩雑になることを避けるため、半導体装置の構成要素の一部(ゲート絶縁膜等)を省略して図示している。

#### 【0148】

図8(A)、(B)に示す半導体装置は、第1の酸化物半導体膜210と、第2の酸化物半導体膜204aとを含むトランジスタ250と、一対の電極間に絶縁膜を含む容量素子260と、を有する。なお、容量素子260において、一対の電極の一方が第2の酸化物半導体膜204aと同一平面上の第2の酸化物半導体膜204bであり、一対の電極の他方が導電膜220である。

#### 【0149】

トランジスタ250は、基板202上の絶縁膜216と、絶縁膜216上の第1の酸化物半導体膜210と、第1の酸化物半導体膜210上のソース電極212a及びドレイン電極212bと、第1の酸化物半導体膜210上のゲート絶縁膜として機能する絶縁膜208と、絶縁膜208上の第1の酸化物半導体膜210と重畠する位置の第2の酸化物半導体膜204aを含むゲート電極と、を有する。なお、図8(A)、(B)に示すトランジスタ250は、所謂トップゲート構造である。

10

#### 【0150】

また、トランジスタ250上、より詳しくは、第2の酸化物半導体膜204aを含むゲート電極、ソース電極212a、及びドレイン電極212b上に絶縁膜218、217が形成されている。絶縁膜218、217は、トランジスタ250の保護絶縁膜としての機能を有する。また、絶縁膜218、217にはドレイン電極212bに達する開口240が形成されており、開口240を覆うように絶縁膜217上に導電膜220が形成されている。導電膜220は、例えば、画素電極としての機能を有する。

20

#### 【0151】

容量素子260は、基板202上の絶縁膜216と、絶縁膜216上の絶縁膜208と、絶縁膜208上の一対の電極の一方としての機能を有する第2の酸化物半導体膜204bと、第2の酸化物半導体膜204b上の誘電体膜として機能する絶縁膜218、217と、絶縁膜218、217を介して第2の酸化物半導体膜204bと重畠する位置の一対の電極の他方としての機能を有する導電膜220と、を有する。すなわち、導電膜220は、画素電極としての機能と容量素子の電極としての機能を有する。

#### 【0152】

30

なお、上述のように絶縁膜208は、トランジスタ250においては、ゲート絶縁膜として機能し、容量素子260においては、誘電体膜の一部として機能する。また、絶縁膜218、217は、トランジスタ250においては、保護絶縁膜として機能し、容量素子260においては、誘電体膜の一部として機能する。なお、図8(A)、(B)においては、誘電体膜の一部として絶縁膜218、217を設ける構成について例示したが、これに限定されない。例えば、トランジスタ250の作製工程において、容量素子260の絶縁膜218、217の一部を除去してもよい。

#### 【0153】

また、容量素子260は、透光性を有する。すなわち、容量素子260が有する、絶縁膜216、206、207、218、217は、それぞれ透光性を有する材料により構成される。このように、容量素子260が透光性を有することで、画素内のトランジスタが形成される箇所以外の領域に大きく(大面積に)形成することができるため、開口率を高めつつ容量値を増大させた半導体装置を得ることができる。この結果、表示品位の優れた半導体装置を得ることができる。また、容量素子260としては、トランジスタ250の作製工程を利用することで作製できる。したがって、製造コストが低い半導体装置を得ることができる。

40

#### 【0154】

なお、絶縁膜207、218としては、少なくとも水素を含む絶縁膜を用いる。また、絶縁膜216、206、217としては、少なくとも酸素を含む絶縁膜を用いる。このように、トランジスタ250及び容量素子260に用いる絶縁膜またはトランジスタ250

50

及び容量素子 260 に接する絶縁膜を、上述の構成の絶縁膜とすることによって、トランジスタ 250 及び容量素子 260 が有する第 1 の酸化物半導体膜及び第 2 の酸化物半導体膜の抵抗率を制御することができる。

#### 【0155】

具体的には、トランジスタ 250 において、第 1 の酸化物半導体膜 210 は、チャネル形成領域として用いるため、第 2 の酸化物半導体膜 204a、204b と比較し抵抗率が高い。一方で、第 2 の酸化物半導体膜 204a、204b は電極としての機能を有するため、抵抗率が低い。

#### 【0156】

ここで、第 1 の酸化物半導体膜 210、及び第 2 の酸化物半導体膜 204a、204b の抵抗率の制御方法について、以下説明を行う。

10

#### 【0157】

##### <酸化物半導体の抵抗率の制御方法 2>

第 1 の酸化物半導体膜 210、及び第 2 の酸化物半導体膜 204a、204b に用いることのできる酸化物半導体は、膜中の酸素欠損及び／又は膜中の水素、水等の不純物濃度によって、抵抗率を制御することができる半導体材料である。そのため、第 1 の酸化物半導体膜 210、及び第 2 の酸化物半導体膜 204a、204b へ酸素欠損及び／又は不純物濃度が増加する処理、または酸素欠損及び／又は不純物濃度が低減する処理を選択することによって、それぞれの酸化物半導体の有する抵抗率を制御することができる。

#### 【0158】

具体的には、トランジスタ 250 のゲート電極として機能する第 2 の酸化物半導体膜 204a、容量素子 260 の電極として機能する第 2 の酸化物半導体膜 204b に用いる酸化物半導体膜にプラズマ処理を行い、該酸化物半導体の膜中の酸素欠損を増加させる、および／または酸化物半導体の膜中の水素、水等の不純物を増加させることによって、キャリア密度が高く、低抵抗な酸化物半導体とすることができます。また、酸化物半導体に水素を含む絶縁膜を接して形成し、該水素を含む絶縁膜から酸化物半導体に水素を拡散させることによって、キャリア密度が高く、抵抗率が低い酸化物半導体とすることができます。

20

#### 【0159】

一方、トランジスタ 250 のチャネル形成領域として機能する第 1 の酸化物半導体膜 210 は、絶縁膜 216、206 を設けることによって、水素を含む絶縁膜 218 と接しない構成とする。また、絶縁膜 216、206 の少なくとも一方は、酸素を放出することができる可能な絶縁膜とすることで、第 1 の酸化物半導体膜 210 に酸素を供給することができる。酸素が供給された第 1 の酸化物半導体膜 210 は、膜中または界面の酸素欠損が補填され高抵抗な酸化物半導体となる。なお、酸素を放出することができる可能な絶縁膜としては、例えば、酸化シリコン膜、または酸化窒化シリコン膜を用いることができる。

30

#### 【0160】

このように、本発明の一態様の半導体装置においては、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同時に形成する、別言すると、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜を同一表面上に形成することで、製造コストを低減することができる。また、トランジスタのゲート電極として機能する導電膜と、容量素子の電極として機能する導電膜は、酸化物半導体膜を含む構成である。該酸化物半導体膜に適切な処理を行うことで、導電率が高く、且つ透光性を有する導電膜とすることができます。該導電膜を用いることで、トランジスタおよび／または容量素子に透光性を付与することができる。

40

#### 【0161】

ここで、図 8 (A)、(B) に示す半導体装置のその他の構成要素の詳細について、以下説明を行う。

#### 【0162】

##### <絶縁膜>

絶縁膜 216 としては、実施の形態 1 の絶縁膜 116 に列挙した材料を援用することで

50

形成することができる。また、絶縁膜 206、207としては、それぞれ実施の形態1の絶縁膜106、107に列挙した材料を援用することで形成することができる。

**【0163】**

<第1の酸化物半導体膜及び第2の酸化物半導体膜>

第1の酸化物半導体膜210としては、実施の形態1の第1の酸化物半導体膜110aに列挙した材料を援用することで形成することができる。また、第2の酸化物半導体膜204a、204bとしては、実施の形態1の第2の酸化物半導体膜104a、104bに列挙した材料を援用することで形成することができる。

**【0164】**

<ソース電極及びドレイン電極>

ソース電極212a及びドレイン電極212bとしては、実施の形態1のソース電極112a及びドレイン電極112bに列挙した材料を援用することで形成することができる。

10

**【0165】**

<導電膜>

導電膜220としては、実施の形態2の導電膜120に列挙した材料を援用することで形成することができる。

**【0166】**

<表示装置の作製方法(変形例2)>

次に、図8(A)、(B)に示す半導体装置の作製方法の一例について、図9及び図10を用いて説明する。

20

**【0167】**

まず、基板202上に絶縁膜216を形成し、絶縁膜216上に酸化物半導体膜を成膜する。その後、該酸化物半導体膜の所望の領域が残るようにパターニングし、その後不要な領域をエッチングすることで第1の酸化物半導体膜210を形成する(図9(A)参照)。

**【0168】**

次に、絶縁膜216、及び第1の酸化物半導体膜210上に導電膜を成膜し、該導電膜の所望の領域が残るようにパターニングし、その後不要な領域をエッチングすることでソース電極212a、及びドレイン電極212bを形成する(図9(B)参照)。

30

**【0169】**

次に、絶縁膜216、第1の酸化物半導体膜210、ソース電極212a、及びドレイン電極212b上に絶縁膜206、207を含む絶縁膜208と、第2の酸化物半導体膜204を成膜する(図9(C)参照)。

**【0170】**

次に、第2の酸化物半導体膜204上にレジストマスクを形成し、第2の酸化物半導体膜204の所望の領域が残るようにパターニングし、その後不要な領域をエッチングすることで、第2の酸化物半導体膜204a、204bを形成する。この時、第2の酸化物半導体膜204a、204b下方の絶縁膜206、207も同時にエッチングし、島状に分離された絶縁膜206、207とする(図9(D)参照)。

40

**【0171】**

次に、絶縁膜216、ソース電極212a、ドレイン電極212b、及び第2の酸化物半導体膜204a、204b上に絶縁膜218、217を形成する(図10(A)参照)。

。

**【0172】**

次に、絶縁膜217上にレジストマスクを形成し、絶縁膜218、217の所望の領域が残るようにパターニングし、その後不要な領域をエッチングすることで、開口240を形成する。なお、開口240としては、ドレイン電極212bに達するように形成する(図10(B)参照)。

**【0173】**

50

次に、開口 240 を覆うように絶縁膜 217 上に導電膜を成膜し、該導電膜上にレジストマスクを形成し、導電膜の所望の領域が残るようにパターニングし、その後不要な領域をエッティングすることで導電膜 220 を形成する（図 10（C）参照）。

#### 【0174】

以上の工程によって、トランジスタ 250 と、容量素子 260 とを同一基板上に形成することができる。

#### 【0175】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0176】

##### （実施の形態 5）

本実施の形態では、本発明の一態様の半導体装置について、実施の形態 1 に示す半導体装置の変形例について、図 11 を用いて説明する。

#### 【0177】

##### <半導体装置の構成例（変形例 4）>

図 11（A）に示す半導体装置は、実施の形態 1 に示すトランジスタ 150 及び容量素子 160 の第 1 の酸化物半導体膜 110a、110b を、酸化物積層膜 410a、410b とする構成である。したがって、その他の構成は、トランジスタ 150 及び容量素子 160 と同じであり、その詳細な説明は省略する。

#### 【0178】

酸化物積層膜 410a、410b の詳細について、以下説明する。

#### 【0179】

酸化物積層膜 410a、410b は、酸化物半導体膜 420a、420b と、酸化物膜 422a、422b と、を有する。なお、以下の説明においては、酸化物半導体膜 420a、420b を酸化物半導体膜 420、酸化物膜 422a、422b を酸化物膜 422 とそれぞれ表記して説明する。

#### 【0180】

酸化物半導体膜 420 と酸化物膜 422 としては、少なくとも 1 つの同じ構成元素を有する金属酸化物を用いることが好ましい。または、酸化物半導体膜 420 と酸化物膜 422 の構成元素を同一とし、両者の組成を異ならせてよい。

#### 【0181】

酸化物半導体膜 420 が In - M - Zn 酸化物（M は Al、Ti、Ga、Y、Zr、La、Ce、Nd、Sn または Hf を表す）の場合、In - M - Zn 酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In : M、Zn : M を満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In : M : Zn = 1 : 1 : 1、In : M : Zn = 5 : 5 : 6 (1 : 1 : 1.2)、In : M : Zn = 3 : 1 : 2 等が好ましい。なお、成膜される酸化物半導体膜 420 の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス 20 % の変動を含む。

#### 【0182】

なお、酸化物半導体膜 420 が In - M - Zn 酸化物であるとき、In および M の和を 100 atomic %としたとき、In と M の原子数比率は、好ましくは In が 25 atomic %以上、M が 75 atomic %未満、さらに好ましくは In が 34 atomic %以上、M が 66 atomic %未満とする。

#### 【0183】

酸化物半導体膜 420 は、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタのオフ電流を低減することができる。

#### 【0184】

酸化物半導体膜 420 の厚さは、3 nm 以上 200 nm 以下、好ましくは 3 nm 以上 1

10

20

30

40

50

0.0 nm以下、さらに好ましくは3 nm以上5.0 nm以下とする。

#### 【0185】

酸化物膜422は、代表的には、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物（MはAl、Ti、Ga、Y、Zr、La、Ce、Nd、SnまたはHfを表す）であり、且つ酸化物半導体膜420よりも伝導帯の下端のエネルギーが真空準位に近く、代表的には、酸化物膜422の伝導帯の下端のエネルギーと、酸化物半導体膜420の伝導帯の下端のエネルギーとの差が、0.05 eV以上、0.07 eV以上、0.1 eV以上、または0.15 eV以上、且つ2 eV以下、1 eV以下、0.5 eV以下、または0.4 eV以下である。即ち、酸化物膜422の電子親和力と、酸化物半導体膜420の電子親和力との差が、0.05 eV以上、0.07 eV以上、0.1 eV以上、または0.15 eV以上、且つ2 eV以下、1 eV以下、0.5 eV以下、または0.4 eV以下である。10

#### 【0186】

酸化物膜422が、上記の元素MをInより高い原子数比で有することで、以下の効果を有する場合がある。（1）酸化物膜422のエネルギーギャップを大きくする。（2）酸化物膜422の電子親和力を小さくする。（3）外部からの不純物を遮蔽する。（4）酸化物半導体膜420と比較して、絶縁性が高くなる。また、元素Mは酸素との結合力が強い金属元素であるため、MをInより高い原子数比で有することで、酸素欠損が生じにくくなる。

#### 【0187】

酸化物膜422がIn-M-Zn酸化物であるとき、InおよびMの和を100 atomic%としたとき、InとMの原子数比率は、好ましくは、Inが50 atomic%未満、Mが50 atomic%以上、さらに好ましくは、Inが25 atomic%未満、Mが75 atomic%以上とする。20

#### 【0188】

また、酸化物半導体膜420、及び酸化物膜422がIn-M-Zn酸化物（MはAl、Ti、Ga、Y、Zr、La、Ce、Nd、SnまたはHfを表す）の場合、酸化物半導体膜420と比較して、酸化物膜422に含まれるMの原子数比が大きく、代表的には、酸化物半導体膜420に含まれる上記原子と比較して、1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比である。30

#### 【0189】

また、酸化物膜422をIn:M:Zn = x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、酸化物半導体膜420をIn:M:Zn = x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]とすると、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも大きく、好ましくは、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも1.5倍以上である。さらに好ましくは、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも2倍以上大きく、より好ましくは、y<sub>1</sub>/x<sub>1</sub>がy<sub>2</sub>/x<sub>2</sub>よりも3倍以上大きい。このとき、酸化物半導体膜420において、y<sub>2</sub>がx<sub>2</sub>以上であると、酸化物半導体を用いたトランジスタに安定した電気特性を付与できるため好ましい。ただし、y<sub>2</sub>がx<sub>2</sub>の3倍以上になると、酸化物半導体を用いたトランジスタの電界効果移動度が低下してしまうため、y<sub>2</sub>はx<sub>2</sub>の3倍未満であると好ましい。40

#### 【0190】

酸化物半導体膜420及び酸化物膜422がIn-M-Zn酸化物の場合、In-M-Zn酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、M > In、Zn - Mを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:Ga:Zn = 1:3:2、In:Ga:Zn = 1:3:3、In:Ga:Zn = 1:3:4、In:Ga:Zn = 1:3:5、In:Ga:Zn = 1:3:6、In:Ga:Zn = 1:3:7、In:Ga:Zn = 1:3:8、In:Ga:Zn = 1:3:9、In:Ga:Zn = 1:3:10、In:Ga:Zn = 1:6:4、In:Ga:Zn = 1:6:5、In:Ga:Zn = 1:6:6、In:Ga:Zn = 1:6:7、In:Ga:Zn = 1:6:8、In:Ga:Zn = 1:6:9、In

: Ga : Zn = 1 : 6 : 10 が好ましい。なお、上記スパッタリングターゲットを用いて成膜された酸化物半導体膜 420 及び酸化物膜 422 に含まれる金属元素の原子数比はそれぞれ、誤差として上記スパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス 20 % の変動を含む。

#### 【0191】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体膜 420 のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

10

#### 【0192】

酸化物膜 422 は、後に形成する絶縁膜 114 または絶縁膜 116 を形成する際の、酸化物半導体膜 420 へのダメージ緩和膜としても機能する。酸化物膜 422 の厚さは、3 nm 以上 100 nm 以下、好ましくは 3 nm 以上 50 nm とする。

#### 【0193】

酸化物半導体膜 420 において、第 14 族元素の一つであるシリコンや炭素が含まれると、酸化物半導体膜 420 において酸素欠損が増加し、n 型化してしまう。このため、酸化物半導体膜 420 におけるシリコンや炭素の濃度、または酸化物膜 422 と、酸化物半導体膜 420 との界面近傍のシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18} \text{ atoms/cm}^3$  以下、好ましくは  $2 \times 10^{17} \text{ atoms/cm}^3$  以下とする。

20

#### 【0194】

また、酸化物半導体膜 420 において、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18} \text{ atoms/cm}^3$  以下、好ましくは  $2 \times 10^{16} \text{ atoms/cm}^3$  以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜 420 のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

#### 【0195】

また、酸化物半導体膜 420 に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n 型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。従って、酸化物半導体膜 420 において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18} \text{ atoms/cm}^3$  以下にすることが好ましい。

30

#### 【0196】

なお、酸化物半導体膜 420 及び酸化物膜 422 は、各層を単に積層するのではなく連続接合（ここでは特に伝導帯の下端のエネルギーが各膜の間で連続的に変化する構造）が形成されるように作製する。すなわち、各膜の界面において、酸化物半導体にとってトラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないような積層構造とする。仮に、積層された酸化物半導体膜 420 及び酸化物膜 422 の間に不純物が混在していると、エネルギーバンドの連続性が失われ、界面でキャリアがトラップされ、あるいは再結合して、消滅してしまう。

40

#### 【0197】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体膜にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7} \text{ Pa} \sim 1 \times 10^{-4} \text{ Pa}$  程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバ

50

一内に気体、特に炭素または水素を含む気体が逆流しないようにしておくことが好ましい。

**【0198】**

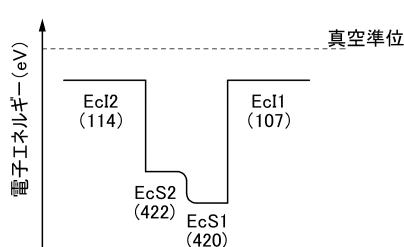

ここで、酸化物積層膜のバンド構造について、図11(B)を用いて説明する。

**【0199】**

図11(B)は、酸化物積層膜と該酸化物積層膜に接する絶縁膜のバンド構造の一部を模式的に示している。ここでは、絶縁膜107及び絶縁膜114として酸化シリコン膜を設けた場合について説明する。なお、図11(B)に表すEcI1は絶縁膜107として用いる酸化シリコン膜の伝導帯下端のエネルギーを示し、EcS1は酸化物半導体膜420の伝導帯下端のエネルギーを示し、EcS2は酸化物膜422の伝導帯下端のエネルギーを示し、EcI2は絶縁膜114として用いる酸化シリコン膜の伝導帯下端のエネルギーを示す。

10

**【0200】**

図11(B)に示すように、酸化物半導体膜420及び酸化物膜422において、伝導帯下端のエネルギーは障壁が無くなだらかに変化する。換言すると、連続的に変化するともいうことができる。これは、酸化物半導体膜420と酸化物膜422が共通の元素を含み、酸化物半導体膜420及び酸化物膜422の間で、酸素が相互に移動することで混合層が形成されるためであるといふことができる。

**【0201】**

図11(B)より、酸化物半導体膜420がウェル(井戸)となり、チャネル領域が酸化物半導体膜420に形成されることがわかる。なお、酸化物半導体膜420及び酸化物膜422は、伝導帯下端のエネルギーが連続的に変化しているため、酸化物半導体膜420と酸化物膜422が連続接合している、ともいえる。

20

**【0202】**

なお、図11(B)に示すように、酸化物膜422と、絶縁膜114との界面近傍には、絶縁膜114の構成元素であるシリコンまたは炭素等の不純物や欠陥に起因したトラップ準位が形成され得るもの、酸化物膜422が設けられることにより、酸化物半導体膜420と該トラップ準位とを遠ざけることができる。ただし、EcS1とEcS2とのエネルギー差が小さい場合、酸化物半導体膜420の電子が該エネルギー差を越えてトラップ準位に達することがある。トラップ準位に電子が捕獲されることで、絶縁膜界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。したがって、EcS1とEcS2とのエネルギー差を、0.1eV以上、好ましくは0.15eV以上とすると、トランジスタのしきい値電圧の変動が低減され、安定した電気特性となるため好適である。

30

**【0203】**

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0204】**

(実施の形態6)

本実施の形態では、本発明の一態様の半導体装置のトランジスタ及び容量素子に適用可能な酸化物半導体膜の一例について説明する。

40

**【0205】**

<酸化物半導体膜の結晶性>

以下では、酸化物半導体膜の構造について説明する。

**【0206】**

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、CAAC-O<sub>S</sub>(C Axis Aligned Crystalline Oxide Semiconductor)膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

**【0207】**

50

まずは、C A A C - O S 膜について説明する。

【0208】

C A A C - O S 膜は、c 軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

【0209】

C A A C - O S 膜を透過型電子顕微鏡 (T E M : T r a n s m i s s i o n E l e c t r o n Microscope) によって観察すると、明確な結晶部同士の境界、即ち結晶粒界 (グレインバウンダリーともいう。) を確認することができない。そのため、C A A C - O S 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

【0210】

C A A C - O S 膜を、試料面と概略平行な方向から T E M によって観察 (断面 T E M 観察) すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C A A C - O S 膜の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映した形状であり、C A A C - O S 膜の被形成面または上面と平行に配列する。

【0211】

一方、C A A C - O S 膜を、試料面と概略垂直な方向から T E M によって観察 (平面 T E M 観察) すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

【0212】

断面 T E M 観察および平面 T E M 観察より、C A A C - O S 膜の結晶部は配向性を有していることがわかる。

【0213】

なお、本明細書において、「平行」とは、二つの直線が - 10° 以上 10° 以下の角度で配置されている状態をいう。従って、- 5° 以上 5° 以下の場合も含まれる。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。従って、85° 以上 95° 以下の場合も含まれる。

【0214】

また、C A A C - O S 膜に含まれるほとんどの結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさである。従って、C A A C - O S 膜に含まれる結晶部は、一辺が 10 nm 未満、5 nm 未満または 3 nm 未満の立方体内に収まる大きさの場合も含まれる。ただし、C A A C - O S 膜に含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、平面 T E M 像において、2500 nm<sup>2</sup> 以上、5 μm<sup>2</sup> 以上または 1000 μm<sup>2</sup> 以上となる結晶領域が観察される場合がある。

【0215】

C A A C - O S 膜に対し、X 線回折 (X R D : X - R a y D i f f r a c t i o n ) 装置を用いて構造解析を行うと、例えば I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S 膜の o u t - o f - p l a n e 法による解析では、回折角 (2θ) が 31° 近傍にピークが現れる場合がある。このピークは、I n G a Z n O<sub>4</sub> の結晶の (009) 面に帰属されることから、C A A C - O S 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

【0216】

一方、C A A C - O S 膜に対し、c 軸に概略垂直な方向から X 線を入射させる i n - p l a n e 法による解析では、2θ が 56° 近傍にピークが現れる場合がある。このピークは、I n G a Z n O<sub>4</sub> の結晶の (110) 面に帰属される。I n G a Z n O<sub>4</sub> の単結晶酸化物半導体膜であれば、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、(110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、C A A C - O S 膜の場合は、2θ を 56° 近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

【0217】

10

20

30

40

50

以上のことから、C A A C - O S 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 T E M 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。

#### 【 0 2 1 8 】

なお、結晶部は、C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、C A A C - O S 膜の形状をエッチングなどによって変化させた場合、結晶の c 軸が C A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

10

#### 【 0 2 1 9 】

また、C A A C - O S 膜中において、c 軸配向した結晶部の分布が均一でなくてもよい。例えば、C A A C - O S 膜の結晶部が、C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも c 軸配向した結晶部の割合が高くなることがある。また、C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域が変質し、部分的に c 軸配向した結晶部の割合の異なる領域が形成されることもある。

#### 【 0 2 2 0 】

なお、I n G a Z n O<sub>4</sub> の結晶を有するC A A C - O S 膜のo u t - o f - p l a n e 法による解析では、2<sup>θ</sup> が 31° 近傍のピークの他に、2<sup>θ</sup> が 36° 近傍にもピークが現れる場合がある。2<sup>θ</sup> が 36° 近傍のピークは、C A A C - O S 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。C A A C - O S 膜は、2<sup>θ</sup> が 31° 近傍にピークを示し、2<sup>θ</sup> が 36° 近傍にピークを示さないことが好ましい。

20

#### 【 0 2 2 1 】

C A A C - O S 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

30

#### 【 0 2 2 2 】

また、C A A C - O S 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【 0 2 2 3 】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないと、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

40

#### 【 0 2 2 4 】

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特

50

性の変動が小さい。

**【0225】**

次に、微結晶酸化物半導体膜について説明する。

**【0226】**

微結晶酸化物半導体膜は、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体膜に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下、または1 nm以上3 nm以下の微結晶であるナノ結晶(nc:nanocrystalline)を有する酸化物半導体膜を、nc-OS(nanocrystalline Oxide Semiconductor)膜と呼ぶ。また、nc-OS膜は、例えば、TEMによる観察像では、結晶粒界を明確に確認できない場合がある。10

**【0227】**

nc-OS膜は、微小な領域(例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域)において原子配列に周期性を有する。また、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない場合がある。例えば、nc-OS膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、nc-OS膜に対し、結晶部よりも大きいプローブ径(例えば50 nm以上)の電子線を用いる電子線回折(制限視野電子線回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OS膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径(例えば1 nm以上30 nm以下)の電子線を用いる電子線回折(ナノビーム電子線回折ともいう。)を行うと、スポットが観測される。また、nc-OS膜に対しナノビーム電子線回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、nc-OS膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。20

**【0228】**

nc-OS膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、nc-OS膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc-OS膜は、CAC-OS膜と比べて欠陥準位密度が高くなる。30

**【0229】**

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAC-OS膜のうち、二種以上を有する積層膜であってもよい。

**【0230】**

本発明の一態様の半導体装置のトランジスタ及び容量素子に含まれる酸化物半導体膜は、上述のいずれの結晶状態の酸化物半導体膜を適用してもよい。また、積層構造の酸化物半導体膜を含む場合、各酸化物半導体膜の結晶状態が異なっていてもよい。但し、トランジスタのチャネル領域として機能する酸化物半導体膜には、CAC-OS膜を適用することが好ましい。また、容量素子の電極として機能する酸化物半導体膜は、トランジスタに含まれる酸化物半導体膜よりも不純物濃度が高いため、結晶性が低減する場合がある。40

**【0231】**

以上、本実施の形態で示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

**【0232】**

(実施の形態7)

本実施の形態では、本発明の一態様の半導体装置を用いる表示装置について、図12を用いて説明を行う。なお、実施の形態1に示す機能と同様の箇所については、同様の符号を付し、その詳細な説明は省略する。50

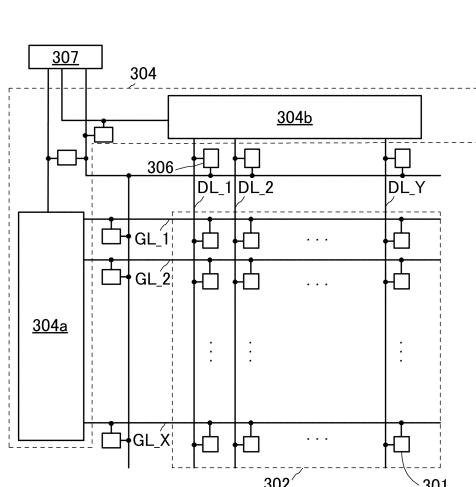

**【 0 2 3 3 】**

図12(A)に示す表示装置は、表示素子の画素を有する領域(以下、画素部302という)と、画素部302の外側に配置され、画素を駆動するための回路を有する回路部(以下、駆動回路部304という)と、素子の保護機能を有する回路(以下、保護回路306という)と、端子部307と、を有する。なお、保護回路306は、設けない構成としてもよい。

**【 0 2 3 4 】**

駆動回路部304の一部、または全部は、画素部302と同一基板上に形成されていることが望ましい。これにより、部品数や端子数を減らすことが出来る。駆動回路部304の一部、または全部が、画素部302と同一基板上に形成されていない場合には、駆動回路部304の一部、または全部は、COG(Chip On Glass)やTAB(Tape Automated Bonding)によって、実装することができる。10

**【 0 2 3 5 】**

画素部302は、X行(Xは2以上の自然数)Y列(Yは2以上の自然数)に配置された複数の表示素子を駆動するための回路(以下、画素回路301という)を有し、駆動回路部304は、画素を選択する信号(走査信号)を出力する回路(以下、ゲートドライバ304aという)、画素の表示素子を駆動するための信号(データ信号)を供給するための回路(以下、ソースドライバ304b)などの駆動回路を有する。

**【 0 2 3 6 】**

ゲートドライバ304aは、シフトレジスタ等を有する。ゲートドライバ304aは、端子部307を介して、シフトレジスタを駆動するための信号が入力され、信号を出力する。例えば、ゲートドライバ304aは、スタートパルス信号、クロック信号等が入力され、パルス信号を出力する。ゲートドライバ304aは、走査信号が与えられる配線(以下、走査線 $GL\_1$ 乃至 $GL\_X$ という)の電位を制御する機能を有する。なお、ゲートドライバ304aを複数設け、複数のゲートドライバ304aにより、走査線 $GL\_1$ 乃至 $GL\_X$ を分割して制御してもよい。または、ゲートドライバ304aは、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ゲートドライバ304aは、別の信号を供給することも可能である。20

**【 0 2 3 7 】**

ソースドライバ304bは、シフトレジスタ等を有する。ソースドライバ304bは、端子部307を介して、シフトレジスタを駆動するための信号の他、データ信号の元となる信号(画像信号)が入力される。ソースドライバ304bは、画像信号を元に画素回路301に書き込むデータ信号を生成する機能を有する。また、ソースドライバ304bは、スタートパルス、クロック信号等が入力されて得られるパルス信号に従って、データ信号の出力を制御する機能を有する。また、ソースドライバ304bは、データ信号が与えられる配線(以下、データ線 $DL\_1$ 乃至 $DL\_Y$ という)の電位を制御する機能を有する。または、ソースドライバ304bは、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ソースドライバ304bは、別の信号を供給することも可能である。30

**【 0 2 3 8 】**

ソースドライバ304bは、例えば複数のアナログスイッチなどを用いて構成される。ソースドライバ304bは、複数のアナログスイッチを順次オン状態にすることにより、画像信号を時分割した信号をデータ信号として出力できる。また、シフトレジスタなどを用いてソースドライバ304bを構成してもよい。40

**【 0 2 3 9 】**

複数の画素回路301のそれぞれは、走査信号が与えられる複数の走査線 $GL$ の一つを介してパルス信号が入力され、データ信号が与えられる複数のデータ線 $DL$ の一つを介してデータ信号が入力される。また、複数の画素回路301のそれぞれは、ゲートドライバ304aによりデータ信号のデータの書き込み及び保持が制御される。例えば、m行n列目の画素回路301は、走査線 $GL\_m$ (mはX以下の自然数)を介してゲートドライバ

304aからパルス信号が入力され、走査線 $GL\_m$ の電位に応じてデータ線 $DL\_n$ ( $n$ はY以下の自然数)を介してソースドライバ304bからデータ信号が入力される。

#### 【0240】

図12(A)に示す保護回路306は、例えば、ゲートドライバ304aと画素回路301の間の配線である走査線 $GL$ に接続される。または、保護回路306は、ソースドライバ304bと画素回路301の間の配線であるデータ線 $DL$ に接続される。または、保護回路306は、ゲートドライバ304aと端子部307との間の配線に接続することができる。または、保護回路306は、ソースドライバ304bと端子部307との間の配線に接続することができる。なお、端子部307は、外部の回路から表示装置に電源及び制御信号、及び画像信号を入力するための端子が設けられた部分をいう。

10

#### 【0241】

保護回路306は、自身が接続する配線に一定の範囲外の電位が与えられたときに、該配線と別の配線とを導通状態にする回路である。

#### 【0242】

図12(A)に示すように、画素部302と駆動回路部304にそれぞれ保護回路306を設けることにより、ESD(Electro Static Discharge: 静電気放電)などにより発生する過電流に対する表示装置の耐性を高めることができる。ただし、保護回路306の構成はこれに限定されず、例えば、ゲートドライバ304aに保護回路306を接続した構成、またはソースドライバ304bに保護回路306を接続した構成とすることもできる。あるいは、端子部307に保護回路306を接続した構成とすることもできる。

20

#### 【0243】

また、図12(A)においては、ゲートドライバ304aとソースドライバ304bによって駆動回路部304を形成している例を示しているが、この構成に限定されない。例えば、ゲートドライバ304aのみを形成し、別途用意されたソースドライバ回路が形成された基板(例えば、単結晶半導体膜、多結晶半導体膜で形成された駆動回路基板)を実装する構成としても良い。

#### 【0244】

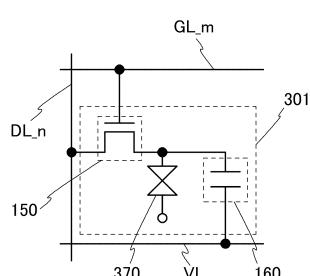

また、図12(A)に示す複数の画素回路301は、例えば、図12(B)に示す構成とすることができる。

30

#### 【0245】

図12(B)に示す画素回路301は、液晶素子370と、トランジスタ150と、容量素子160と、を有する。なお、トランジスタ150、及び容量素子160は、実施の形態1に示す図1の構成の半導体装置を用いることができる。

#### 【0246】

液晶素子370の一対の電極の一方の電位は、画素回路301の仕様に応じて適宜設定される。液晶素子370は、書き込まれるデータにより配向状態が設定される。なお、複数の画素回路301のそれぞれが有する液晶素子370の一対の電極の一方に共通の電位(コモン電位)を与えてよい。また、各行の画素回路301の液晶素子370の一対の電極の一方に異なる電位を与えてよい。

40

#### 【0247】

例えば、液晶素子370を備える表示装置の駆動方法としては、TNモード、STNモード、VAモード、ASM(Axially Symmetric Aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、MVAモード、PVA(Patterned Vertical Alignment)モード、IPSモード、FFSモード、又はTBA(Transverse Bend Alignment)モードなどを用いてよい。

また、表示装置の駆動方法としては、上述した駆動方法の他、ECB(Electric

50

ally Controlled Birefringence) モード、PDL C (Polymer Dispersed Liquid Crystal) モード、PNL C (Polymer Network Liquid Crystal) モード、ゲストホストモードなどがある。ただし、これに限定されず、液晶素子及びその駆動方式として様々なものを用いることができる。

#### 【0248】

また、ブルー相 (Blue Phase) を示す液晶とカイラル剤とを含む液晶組成物により液晶素子を構成してもよい。ブルー相を示す液晶は、応答速度が 1 msec 以下と短い。また、ブルー相を示す液晶は、光学的等方性であるため、配向処理が不要であり、且つ視野角依存性が小さい。

10

#### 【0249】

m 行 n 列目の画素回路 301において、トランジスタ 150 のソース電極またはドレン電極の一方は、データ線 DL\_n に電気的に接続され、他方は液晶素子 370 の一対の電極の他方に電気的に接続される。また、トランジスタ 150 のゲート電極は、走査線 GL\_m に電気的に接続される。トランジスタ 150 は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

#### 【0250】

容量素子 160 の一対の電極の一方は、電位が供給される配線（以下、電位供給線 VL）に電気的に接続され、他方は、液晶素子 370 の一対の電極の他方に電気的に接続される。なお、電位供給線 VL の電位の値は、画素回路 301 の仕様に応じて適宜設定される。容量素子 160 は、書き込まれたデータを保持する保持容量としての機能を有する。

20

#### 【0251】

例えば、図 12 (A) の画素回路 301 を有する表示装置では、ゲートドライバ 304 a により各行の画素回路 301 を順次選択し、トランジスタ 150 をオン状態にしてデータ信号のデータを書き込む。

#### 【0252】

データが書き込まれた画素回路 301 は、トランジスタ 150 がオフ状態になることで保持状態になる。これを行毎に順次行うことにより、画像を表示できる。

#### 【0253】

なお、表示素子として、液晶素子 370 を用いた場合の例を示したが、本発明の実施形態の一態様は、これに限定されない。

30

#### 【0254】

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置の一例としては、EL (エレクトロルミネッセンス) 素子 (有機物及び無機物を含む EL 素子、有機 EL 素子、無機 EL 素子)、LED (白色 LED、赤色 LED、緑色 LED、青色 LED など)、トランジスタ (電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ (GLV)、プラズマディスプレイ (PDP)、MEMS (マイクロ・エレクトロ・メカニカル・システム)、デジタルマイクロミラーデバイス (DMD)、DMS (デジタル・マイクロ・シャッター)、IMOD (インターフェアレンス・モジュレーション) 素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有するものがある。EL 素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニングディスプレイ (FED) 又はSED 方式平面型ディスプレイ (SED: Surface-conduction Electron-emitter Display) などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ (透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ) などが

40

50

ある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。

**【0255】**

表示素子として液晶素子を用いた場合の例を図21に示す。基板102aには、共通電極124が設けられている。そして、共通電極124と導電膜120との間には、液晶層123が設けられている。

**【0256】**

または、表示素子として発光素子を用いた場合の例を図22に示す。導電膜120の上に絶縁膜132、発光層125、共通電極124が設けられている。

**【0257】**

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

**【0258】**

(実施の形態8)

本実施の形態では、本発明の一態様の半導体装置を用いる表示モジュール及び電子機器について、図13及び図14を用いて説明を行う。

**【0259】**

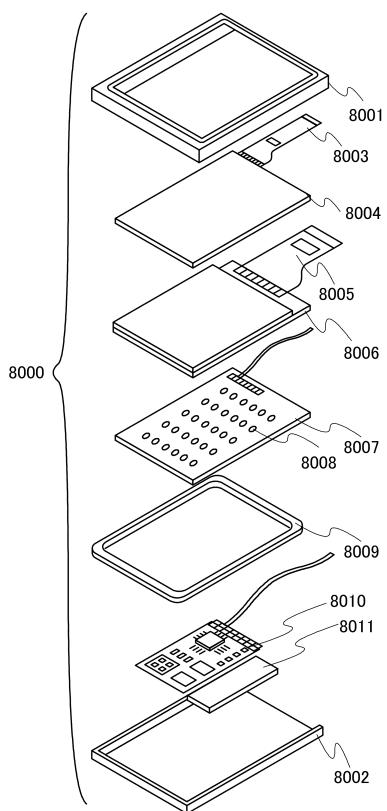

図13に示す表示モジュール8000は、上部カバー8001と下部カバー8002との間に、FPC8003に接続されたタッチパネル8004、FPC8005に接続された表示パネル8006、バックライトユニット8007、フレーム8009、プリント基板8010、バッテリー8011を有する。

**【0260】**

本発明の一態様の半導体装置は、例えば、表示パネル8006に用いることができる。

**【0261】**

上部カバー8001及び下部カバー8002は、タッチパネル8004及び表示パネル8006のサイズに合わせて、形状や寸法を適宜変更することができる。

**【0262】**

タッチパネル8004は、抵抗膜方式または静電容量方式のタッチパネルを表示パネル8006に重畠して用いることができる。また、表示パネル8006の対向基板(封止基板)に、タッチパネル機能を持たせるようにすることも可能である。また、表示パネル8006の各画素内に光センサを設け、光学式のタッチパネルとすることも可能である。

**【0263】**

バックライトユニット8007は、光源8008を有する。光源8008は、バックライトユニット8007の端部に設け、光拡散板を用いる構成としてもよい。

**【0264】**

フレーム8009は、表示パネル8006の保護機能の他、プリント基板8010の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム8009は、放熱板としての機能を有していてもよい。

**【0265】**

プリント基板8010は、電源回路、ビデオ信号及びクロック信号を出力するための信号処理回路を有する。電源回路に電力を供給する電源としては、外部の商用電源であっても良いし、別途設けたバッテリー8011による電源であってもよい。バッテリー8011は、商用電源を用いる場合には、省略可能である。

**【0266】**

また、表示モジュール8000は、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。

**【0267】**

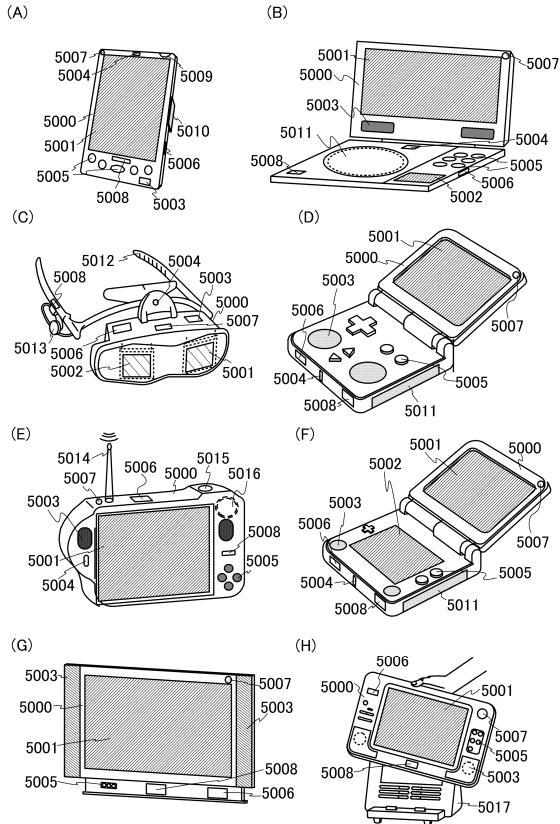

図14(A)乃至図14(H)は、電子機器を示す図である。これらの電子機器は、筐体5000、表示部5001、スピーカ5003、LEDランプ5004、操作キー5005(電源スイッチ、又は操作スイッチを含む)、接続端子5006、センサ5007(

10

20

30

40

50

力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、において又は赤外線を測定する機能を含むもの)、マイクロフォン 5008、等を有することができる。

#### 【0268】

図14(A)はモバイルコンピュータであり、上述したものその他に、スイッチ 5009、赤外線ポート 5010、等を有することができる。図14(B)は記録媒体を備えた携帯型の画像再生装置(たとえば、DVD再生装置)であり、上述したものその他に、第2表示部 5002、記録媒体読込部 5011、等を有することができる。図14(C)はゴーグル型ディスプレイであり、上述したものその他に、第2表示部 5002、支持部 5012、イヤホン 5013、等を有することができる。図14(D)は携帯型遊技機であり、上述したものその他に、記録媒体読込部 5011、等を有することができる。図14(E)はテレビ受像機能付きデジタルカメラであり、上述したものその他に、アンテナ 5014、シャッターボタン 5015、受像部 5016、等を有することができる。図14(F)は携帯型遊技機であり、上述したものその他に、第2表示部 5002、記録媒体読込部 5011、等を有することができる。図14(G)はテレビ受像器であり、上述したものその他に、チューナ、画像処理部、等を有することができる。図14(H)は持ち運び型テレビ受像器であり、上述したものその他に、信号の送受信が可能な充電器 5017、等を有することができる。

#### 【0269】

図14(A)乃至図14(H)に示す電子機器は、様々な機能を有することができる。例えば、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能、タッチパネル機能、カレンダー、日付又は時刻などを表示する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、無線通信機能、無線通信機能を用いて様々なコンピュータネットワークに接続する機能、無線通信機能を用いて様々なデータの送信又は受信を行う機能、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能、等を有することができる。さらに、複数の表示部を有する電子機器においては、一つの表示部を主として画像情報を表示し、別の一つの表示部を主として文字情報を表示する機能、または、複数の表示部に視差を考慮した画像を表示することで立体的な画像を表示する機能、等を有することができる。さらに、受像部を有する電子機器においては、静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する機能、撮影した画像を記録媒体(外部又はカメラに内蔵)に保存する機能、撮影した画像を表示部に表示する機能、等を有することができる。なお、図14(A)乃至図14(H)に示す電子機器が有することのできる機能はこれらに限定されず、様々な機能を有することができる。

#### 【0270】

本実施の形態において述べた電子機器は、何らかの情報を表示するための表示部を有することを特徴とする。

#### 【0271】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【符号の説明】

#### 【0272】

102 基板

102a 基板

104a 酸化物半導体膜

104b 酸化物半導体膜

106 絶縁膜

107 絶縁膜

108 絶縁膜

10

20

30

40

50

|         |         |    |

|---------|---------|----|

| 1 1 0 a | 酸化物半導体膜 |    |

| 1 1 0 b | 酸化物半導体膜 |    |

| 1 1 2 a | ソース電極   |    |

| 1 1 2 b | ドレイン電極  |    |

| 1 1 4   | 絶縁膜     |    |

| 1 1 6   | 絶縁膜     |    |

| 1 1 8   | 絶縁膜     |    |

| 1 1 8 a | 絶縁膜     |    |

| 1 2 0   | 導電膜     | 10 |

| 1 2 0 a | 導電膜     |    |

| 1 2 1   | 導電膜     |    |

| 1 2 1 a | 導電膜     |    |

| 1 2 2   | 絶縁膜     |    |

| 1 3 2   | 絶縁膜     |    |

| 1 4 0   | 開口      |    |

| 1 4 2   | 開口      |    |

| 1 5 0   | トランジスタ  |    |

| 1 5 1   | トランジスタ  |    |

| 1 5 2   | トランジスタ  |    |

| 1 6 0   | 容量素子    | 20 |

| 1 6 1   | 容量素子    |    |

| 1 6 2   | 容量素子    |    |

| 2 0 2   | 基板      |    |

| 2 0 4   | 酸化物半導体膜 |    |

| 2 0 4 a | 酸化物半導体膜 |    |

| 2 0 4 b | 酸化物半導体膜 |    |

| 2 0 6   | 絶縁膜     |    |

| 2 0 7   | 絶縁膜     |    |

| 2 0 8   | 絶縁膜     |    |

| 2 1 0   | 酸化物半導体膜 | 30 |

| 2 1 2 a | ソース電極   |    |

| 2 1 2 b | ドレイン電極  |    |

| 2 1 6   | 絶縁膜     |    |

| 2 1 7   | 絶縁膜     |    |

| 2 1 8   | 絶縁膜     |    |

| 2 2 0   | 導電膜     |    |

| 2 4 0   | 開口      |    |

| 2 5 0   | トランジスタ  |    |

| 2 6 0   | 容量素子    |    |

| 3 0 1   | 画素回路    | 40 |

| 3 0 2   | 画素部     |    |

| 3 0 4   | 駆動回路部   |    |

| 3 0 4 a | ゲートドライバ |    |

| 3 0 4 b | ソースドライバ |    |

| 3 0 6   | 保護回路    |    |

| 3 0 7   | 端子部     |    |

| 3 7 0   | 液晶素子    |    |

| 4 1 0 a | 酸化物積層膜  |    |

| 4 1 0 b | 酸化物積層膜  |    |

| 4 2 0   | 酸化物半導体膜 | 50 |

|         |            |    |

|---------|------------|----|

| 4 2 0 a | 酸化物半導体膜    |    |

| 4 2 0 b | 酸化物半導体膜    |    |

| 4 2 2   | 酸化物膜       |    |

| 4 2 2 a | 酸化物膜       |    |

| 4 2 2 b | 酸化物膜       |    |

| 5 0 0 0 | 筐体         |    |

| 5 0 0 1 | 表示部        |    |

| 5 0 0 2 | 表示部        |    |

| 5 0 0 3 | スピーカ       |    |

| 5 0 0 4 | L E D ランプ  | 10 |

| 5 0 0 5 | 操作キー       |    |

| 5 0 0 6 | 接続端子       |    |

| 5 0 0 7 | センサ        |    |

| 5 0 0 8 | マイクロフォン    |    |

| 5 0 0 9 | スイッチ       |    |

| 5 0 1 0 | 赤外線ポート     |    |

| 5 0 1 1 | 記録媒体読込部    |    |

| 5 0 1 2 | 支持部        |    |

| 5 0 1 3 | イヤホン       |    |

| 5 0 1 4 | アンテナ       | 20 |

| 5 0 1 5 | シャッター ボタン  |    |

| 5 0 1 6 | 受像部        |    |

| 5 0 1 7 | 充電器        |    |

| 8 0 0 0 | 表示モジュール    |    |

| 8 0 0 1 | 上部カバー      |    |

| 8 0 0 2 | 下部カバー      |    |

| 8 0 0 3 | F P C      |    |

| 8 0 0 4 | タッチパネル     |    |

| 8 0 0 5 | F P C      |    |

| 8 0 0 6 | 表示パネル      | 30 |

| 8 0 0 7 | バックライトユニット |    |

| 8 0 0 8 | 光源         |    |

| 8 0 0 9 | フレーム       |    |

| 8 0 1 0 | プリント基板     |    |

| 8 0 1 1 | バッテリー      |    |

## 【図面】

## 【図1】

(A)

(B)

## 【図2】

(A)

(B)

(C)

(D)

10

20

30

40

## 【図3】

(A)

(B)

## 【図4】

(A)

(B)

50

【図5】

【図6】

10

20

【図7】

【図8】

30

40

50

【図9】

【図10】

10

20

30

40

【図11】

(B)

【図12】

(B)

50

【図13】

【図14】

【図15】

【図16】

【図17】

(A)

(B)

【図18】

(A)

(B)

10

20

【図19】

【図20】

30

40

50

【図21】

【図22】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|                            | F I                         |

|----------------------------|-----------------------------|

| H 1 0 D    86/40 (2025.01) | H 1 0 D    84/80    1 0 1 A |

| H 1 0 K    59/121(2023.01) | H 1 0 D    84/83    1 0 1 E |

| H 1 0 K    59/123(2023.01) | H 1 0 D    86/40    1 0 1 Z |

| H 1 0 K    59/80 (2023.01) | H 1 0 K    59/121    2 1 6  |

| G 0 2 F    1/1368(2006.01) | H 1 0 K    59/123           |

|                            | H 1 0 K    59/80            |

|                            | G 0 2 F    1/1368           |

## (56)参考文献

国際公開第2012/086513 (WO , A 1 )

特開2011-129895 (JP , A )

特開2011-076079 (JP , A )

国際公開第2011/070981 (WO , A 1 )

特開2012-083738 (JP , A )

## (58)調査した分野 (Int.Cl. , DB名)

H 1 0 D    1 / 6 8

H 1 0 D    3 0 / 6 7

H 1 0 D    8 4 / 8 0

H 1 0 D    8 6 / 4 0

H 0 5 B    3 3 / 0 0

H 0 5 B    4 4 / 0 0

H 0 5 B    4 5 / 6 0

H 1 0 K    5 9 / 8 0

H 1 0 K    5 0 / 0 0 - 9 9 / 0 0

G 0 2 F    1 / 1 3 6 8