(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-260235

(P2005-260235A)

(43) 公開日 平成17年9月22日(2005.9.22)

(51) Int.C1.<sup>7</sup>

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792

F 1

H01L 29/78 371

H01L 27/10 434

テーマコード(参考)

5FO83

5F1O1

審査請求 未請求 請求項の数 20 O L (全 19 頁)

(21) 出願番号 特願2005-65101 (P2005-65101)

(22) 出願日 平成17年3月9日 (2005.3.9)

(31) 優先権主張番号 10/797296

(32) 優先日 平成16年3月9日 (2004.3.9)

(33) 優先権主張国 米国(US)

(71) 出願人 500147506

シリコンストーリッジ テクノロジー

インコーポレイテッド

SILICON STORAGE TECHNOLOGY, INC.

アメリカ合衆国 94086 カリフォルニア州 サニーヴェイル ソノラ コート

1171

(74) 代理人 100082005

弁理士 熊倉 賢男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100074228

弁理士 今城 俊夫

最終頁に続く

(54) 【発明の名称】トレンチ内に独立制御可能な制御ゲートを有する埋込ビット線型不揮発性浮遊ゲートメモリセル、そのアレイ、及び製造方法

## (57) 【要約】

【課題】高密度を実現できる埋込ビット線型読み取り/プログラム不揮発性メモリセル及びアレイを提供する。

【解決手段】セル及びアレイは、離間した複数のトレンチを有し、各トレンチの間には平面が設けられている半導体基板内に形成される。各々のトレンチは側壁及び底壁を有する。各々のメモリセルは、電荷を蓄えるための浮遊ゲートを有する。セルは、離間したソース/ドレイン領域を有し、この領域の間にはチャネルが形成され、チャネルは2つの部分を有する。ソース/ドレイン領域の一方側はトレンチの底壁にある。浮遊ゲートは、トレンチ内でチャネルの第1の部分を覆いトレンチの側壁から離間している。ゲート電極は、基板の平面内にある第2の部分においてチャネルの導電性を制御する。ソース/ドレイン領域の他方側は基板の平面内にある。また、独立制御可能な制御ゲートはトレンチ内にあり、浮遊ゲートから絶縁され、浮遊ゲートと容量結合する。

【選択図】 図2R

**【特許請求の範囲】****【請求項 1】**

側壁及び底壁をもつトレンチを有する実質的に平坦な表面を備える第1の導電型の実質的に単結晶の半導体材料と、

前記半導体材料の前記平面に沿った、前記第1の導電型とは異なる第2の導電型の第1の領域と、

前記半導体材料の前記トレンチの前記底壁に沿った、前記第2の導電型の第2の領域と、

、

前記第1の領域に隣接する前記表面に沿う第1の部分と、前記第2の領域に隣接する前記側壁に沿う第2の部分とを有し、電荷を伝導するために前記第1の領域と前記第2の領域とを接続するチャネル領域と、

前記チャネル領域上の誘電体と、

前記トレンチ内にあり、前記誘電体上にあり、前記チャネル領域の前記第2の部分から離間した浮遊ゲートと、

前記誘電体上にあり、前記チャネル領域の前記第1の部分から離間した第1のゲート電極と、

前記トレンチ内にあり、前記浮遊ゲートと容量結合される第2のゲート電極と、

を備えることを特徴とする不揮発性メモリセル。

**【請求項 2】**

前記実質的に単結晶の半導体材料が、単結晶シリコンであることを特徴とする請求項1

に記載のセル。 20

**【請求項 3】**

前記浮遊ゲートが、前記第1のゲート電極と実質的に隣接した先端部を有することを特徴とする請求項1に記載のセル。

**【請求項 4】**

前記先端部と前記第1のゲート電極との間に、前記浮遊ゲートから前記第1のゲート電極への電子のファウラーノルドハイムトンネル現象を可能にする第2の誘電体を更に備えることを特徴とする請求項3に記載のセル。

**【請求項 5】**

前記浮遊ゲートと前記トレンチの前記底壁との間に、前記浮遊ゲートから前記第2の領域へのファウラーノルドハイムトンネル現象を可能にする第2の誘電体を更に備えることを特徴とする請求項1に記載のセル。 30

**【請求項 6】**

各々が側壁及び底壁をもつ複数のトレンチを有する実質的に平坦な表面を備える第1の導電型の実質的に単結晶の半導体材料と、

前記半導体基板材料内に複数のロウ及びカラムに配列された複数の不揮発性メモリセルと、

を備える複数のロウ及びカラムに配列された不揮発性メモリセルのアレイであって、各々のセルが、

前記半導体材料の前記表面に沿った、前記第1の導電型とは異なる第2の導電型の第1の領域と、

前記半導体材料の前記トレンチの底壁に沿った、前記第2の導電型の第2の領域と、

前記第1の領域に隣接する前記表面に沿う第1の部分と、前記第2の領域に隣接する前記側壁に沿う第2の部分とを有し、電荷を伝導するために前記第1の領域と前記第2の領域とを接続するチャネル領域と、

前記チャネル領域上の誘電体と、

前記誘電体上にあり、前記チャネル領域の前記第2の部分から離間した浮遊ゲートと、

前記誘電体上にあり、前記チャネル領域の前記第1の部分から離間した第1のゲート電極と、

前記トレンチ内にあり、前記浮遊ゲートと容量結合される第2のゲート電極と、 40

10

30

40

50

を備え、

同じ口ウの前記セルが、前記第1のゲート電極を共用し、

同じカラムの前記セルが、前記第1の領域、前記第2の領域、及び前記第2のゲート電極を共用し、

隣接するカラムの前記セルが、一方側で前記第1の領域を共用し、他方側で前記第2のゲート電極及び前記第2の領域を共用する

ことを特徴とする不揮発性メモリセルのアレイ。

【請求項7】

前記実質的に単結晶の半導体材料が、単結晶シリコンであることを特徴とする請求項6に記載のアレイ。10

【請求項8】

各々のセルにおいて前記浮遊ゲートが、第1のゲート電極と実質的に隣接した先端部を有することを特徴とする請求項6に記載のアレイ。

【請求項9】

各々のセルが、前記先端部と前記第1のゲート電極との間に、前記浮遊ゲートから前記第1のゲート電極への電子のファウラーノルドハイムトンネル現象を可能にする第2の誘電体を更に備えることを特徴とする請求項8に記載のアレイ。

【請求項10】

各々のセルが、前記浮遊ゲートと前記トレンチの前記底壁との間に、前記浮遊ゲートから前記第2の領域への電子のファウラーノルドハイムトンネル現象を可能にする第2の誘電体を更に備えることを特徴とする請求項6に記載のアレイ。20

【請求項11】

分離領域が、セルの隣接する口ウを分離することを特徴とする請求項6に記載のアレイ。。

【請求項12】

第1の導電型の実質的に単結晶の半導体基板材料内に複数の口ウ及びカラムに配列された複数の不揮発性メモリセルを有するアレイを製造する方法であって、

実質的に平坦な表面を有する前記半導体基板上に、前記カラム方向へ延び、互いに実質的に平行で離間しており、各々の一対の間には活性領域が形成される分離領域を形成する段階と、30

前記活性領域の各々に複数のメモリセルを形成する段階と、

を含み、前記メモリセルの各々を形成する段階が、

側壁及び底壁を有するトレンチを前記半導体基板の表面内に形成する段階と、

前記側壁に沿って前記側壁から絶縁されている浮遊ゲートを前記トレンチ内に形成する段階と、

前記第1の導電型とは異なる第2の導電型の第1の領域を、前記トレンチの前記底壁に沿って前記基板内に形成する段階と、

前記第1の領域から絶縁され前記浮遊ゲートと容量結合される第1のゲート電極を前記トレンチ内に形成する段階と、

表面に沿い前記トレンチから離間した第2の導電型の第2の領域を前記基板内に形成する段階と、40

前記第2の領域と前記トレンチとの間に表面から離間した第2のゲート電極を形成する段階と、

を含むことを特徴とする不揮発性メモリセルのアレイを製造する方法。

【請求項13】

前記第1のゲート電極を形成する前記段階が、前記第2のゲート電極を複数のカラムを横切って前記口ウ方向に連続的に形成する段階を含むことを特徴とする請求項12に記載の方法。

【請求項14】

前記第2のゲート電極を形成する前記段階が、前記第2のゲート電極を複数の口ウを横

50

切って前記カラム方向に連続的に形成する段階を含むことを特徴とする請求項 1 2 に記載の方法。

【請求項 1 5】

前記第 1 の領域及び前記第 2 の領域を形成する前記段階が、前記第 1 の領域及び第 2 の領域を複数のカラムを横切って前記口ウ方向に連続的に形成する段階を含むことを特徴とする請求項 1 4 に記載の方法。

【請求項 1 6】

前記同じ口ウ内の前記セルが前記第 2 のゲート電極を共用し、同じカラム内の前記セルが前記第 1 の領域、前記第 2 の領域、及び前記第 1 のゲート電極を共用し、隣接するカラム内の前記セルが、一方側で前記第 2 の領域を共用し、他方側で前記第 1 のゲート電極及び前記第 1 の領域を共用することを特徴とする請求項 1 5 に記載の方法。

【請求項 1 7】

実質的に平坦な表面を有する第 1 の導電型の実質的に単結晶の半導体基板材料内に不揮発性メモリセルを製造する方法であって、

側壁及び底壁を有するトレンチを前記半導体基板の表面内に形成する段階と、

側壁に沿って側壁から絶縁されている浮遊ゲートを前記トレンチ内に形成する段階と、

前記第 1 の導電型とは異なる第 2 の導電型の第 1 の領域を、前記トレンチの前記底壁に沿って前記基板内に形成する段階と、

前記第 1 の領域から絶縁され前記浮遊ゲートと容量結合される第 1 のゲート電極を前記トレンチ内に形成する段階と、

表面に沿い前記トレンチから離間した第 2 の導電型の第 2 の領域を前記基板内に形成する段階と、

前記第 2 の領域と前記トレンチとの間に表面から離間した第 2 のゲート電極を形成する段階と、

を含むことを特徴とする不揮発性メモリセルを製造する方法。

【請求項 1 8】

前記第 2 の浮遊ゲートから前記第 2 のゲート電極への電子のファウラーノルドハイムトンネル現象を可能にする厚さをもつ絶縁材を、前記第 2 のゲート電極と前記浮遊ゲートとの間に形成する段階を更に含むことを特徴とする請求項 1 7 に記載の方法。

【請求項 1 9】

前記浮遊ゲートから前記第 2 の領域への電子のファウラーノルドハイムトンネル現象を可能にする絶縁材を、前記浮遊ゲートと前記トレンチの前記底壁との間に形成する段階を更に含むことを特徴とする請求項 1 7 に記載の方法。

【請求項 2 0】

前記浮遊ゲートを形成する前記段階が、前記基板の表面上に前記浮遊ゲートを形成する段階を含むことを特徴とする請求項 1 8 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本出願は、2003年4月7日出願の係属中の特許出願番号 10/409,407 の部分継続出願であり、その開示内容は引用によって本明細書に組み込まれている。

【0 0 0 2】

本発明は、電荷を蓄えるためにトレンチ内の浮遊ゲートを使用する埋込ビット線型読取り／プログラム不揮発性メモリセルに関する。詳細には、本発明は、やはりトレンチ内で浮遊ゲートに容量結合された独立制御可能な制御ゲートを有する不揮発性メモリセル、そのようなセルのアレイ、及び製造方法に関する。

【背景技術】

【0 0 0 3】

半導体基板の平面上に形成された記憶用の浮遊ゲートを使用する読取り／プログラム不揮発性メモリセルは、本技術分野ではよく知られている。例えば、米国特許第 5,029

10

20

30

40

50

, 130号及び第6, 426, 896号を参照されたい。一般に、この形式のメモリセルは、半導体基板の水平面上に形成され、ホット電子注入による浮遊ゲートのプログラム及びポリ間のファウラーノルドハイムトンネル現象による浮遊ゲートからの電子の消去を含む。浮遊ゲートは電荷を蓄えるか又は蓄えない。浮遊ゲートに蓄えられた電荷は、トランジスタのプレーナチャネル内の電荷の伝導を制御する。半導体処理の集積度が高くなるとこのような記憶デバイスの密度を高めることが望まれる。

【0004】

【特許文献1】米国特許第5, 029, 130号

【特許文献2】米国特許第6, 426, 896号

10

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、高密度の記憶デバイスに対する要求が高まるにつれて、半導体基板のこのようなセルの密度を高めることが必要になる。

【課題を解決するための手段】

【0006】

本発明において、不揮発性メモリセルは、トレンチを備えた実質的に平坦な表面を有する、第1の導電型の実質的に単結晶の半導体材料内に形成される。トレンチは、側壁及び底壁を有する。第1の導電型とは異なる第2の導電型の第1の領域は、平面に沿って半導体材料内に存在する。第2の導電型の第2の領域は、トレンチの底壁に沿って半導体材料内に存在する。チャネル領域は、第1の部分及び第2の部分を有し、電荷の伝導のために第1の領域と第2の領域とを接続する。第1の部分は、第1の領域に隣接する表面に沿い、第2の部分は、第2の領域に隣接する側壁に沿う。チャネル領域上には誘電体がある。浮遊ゲートはトレンチの誘電体を覆い、チャネル領域の第2の部分から離間している。第1のゲート電極は誘電体を覆い、チャネル領域の第1の部分から離間している。第2のゲート電極はトレンチ内にあり、浮遊ゲートと容量結合している。

本発明はまた、上記不揮発性メモリセルのアレイ、及び該不揮発性メモリセル並びに該アレイの製造方法に関する。

【発明を実施するための最良の形態】

【0007】

図1Aから1F、及び図2Aから2Rは本発明の方法を示し、本発明のメモリセルアレイを形成する処理工程を示している。本方法は、好ましくはP型であり本技術分野ではよく知られている半導体基板10から始まる。以下に説明する各層の厚さは、設計ルール及び処理技術の世代に依存するであろう。本明細書では、0.10ミクロン処理を説明する。しかしながら、当業者であれば、本発明はいずれかの特定の世代の処理技術に限定されないこと、又は以下に説明するいずれかの処理パラメータのどの特定の値にも限定されないことを理解できるであろう。

【0008】

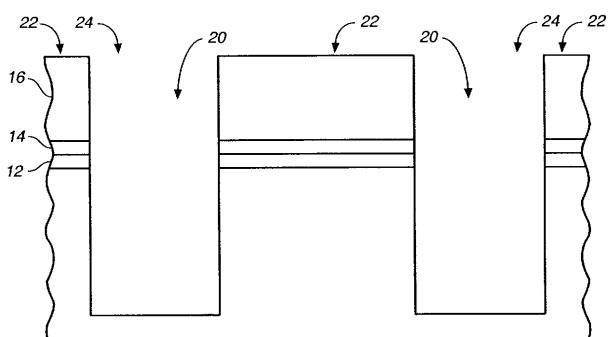

分離領域の形成

図1Aから1Fは、基板上に分離領域を形成するための公知のSTI法を示す。図1Aを参照すると、半導体基板10（又は半導体井戸）の平面図が示されており、好ましくはP型であり本技術分野では公知である。第1の材料層12及び第2の材料層14は、基板上に形成される（例えば、成長法又は蒸着法）。例えば、第1の層12は、二酸化ケイ素（以下「酸化物」と呼ぶ）とすることができます、酸化又は酸化物蒸着（例えば、化学蒸着法又はCVD）といった任意の公知の方法で、基板10上に約60から150オングストロームの厚さで形成される。第2の層14は、窒化ケイ素（以下「窒化物」と呼ぶ）とすることができます、CVD法で酸化物層12上に約1000から2000オングストロームの厚さで形成されることが好ましい。図1Bは、結果として得られた構造体の断面図を示す。

【0009】

第1の層12及び第2の層14の形成後に、窒化物層14上には適切なフォトレジスト

20

30

40

50

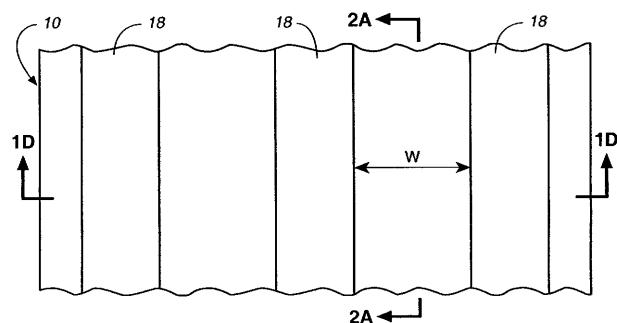

材 1 6 が塗布され、次に、マスキング工程が行われ、図 1 C に示すように Y 方向又は縦方向に延びる特定領域（帯 1 8）からフォトレジスト材が選択的に除去される。フォトレジスト材 1 6 が除去された場所では、標準的なエッチング処理（つまり、異方性窒化物及び酸化物エッチング処理）を使用して、帯 1 8 内の露出した窒化物層 1 4 及び酸化物層 1 2 がエッチング除去され、構造体内にトレンチ 2 0 が形成される。隣接する帯 1 8 の間の距離 W は、使用される処理工程の最小リソグラフィック形状サイズと同程度に小さくすることができる。次に、図 1 D に示すように、シリコンエッチング処理は、トレンチ 2 0 をシリコン基板 1 0 内に約 500 から 4000 オングストロームの深さまで下方へ延ばすために使用される。フォトレジスト材 1 6 が除去されていない場所では、窒化物層 1 4 及び酸化物層 1 2 は残っている。図 1 D に示す結果として得られた構造体は、分離領域 2 4 と交互になつた活性領域 2 2 を有する。

10

#### 【 0 0 1 0 】

構造体は更に処理されて残留フォトレジスト材 1 6 が除去される。次に、図 1 E に示すように、二酸化ケイ素等の分離材料は、厚い酸化物層を蒸着した後に第 1 のトレンチ 2 0 内の酸化物ブロック 2 6 以外の酸化物層を除去するための化学機械研磨 C M P 法（窒化物層 1 4 をエッチングストッパーとして用いて）によって第 1 のトレンチ 2 0 内に形成される。次に、図 1 F に示すように、残留窒化物層 1 4 及び酸化物層 1 2 は、分離領域 2 4 に沿って延びる S T I 酸化物ブロック 2 6 を残して、窒化物 / 酸化物エッチング法により除去される。

20

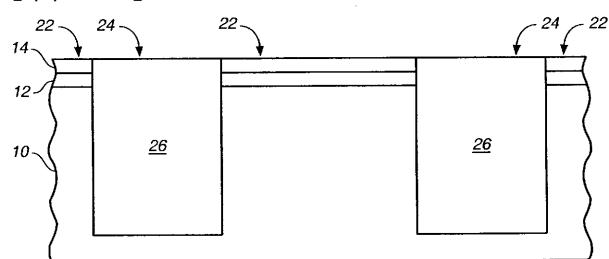

#### 【 0 0 1 1 】

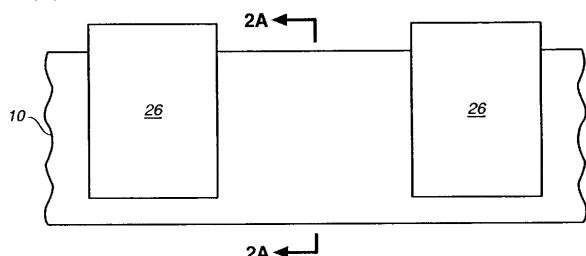

前述の S T I 分離法は分離領域 2 4 を形成する好ましい方法である。しかしながら、公知の L O C O S 分離法（例えば、L O C O S、ポリバッファ L O C O S 等）を使用することもでき、この場合、トレンチ 2 0 は基板内に延びず、分離材料は帯領域 1 8 内の基板表面上に形成することができる。図 1 A から 1 F は基板のメモリセルアレイ領域を示しており、メモリセルのカラムは、分離領域 2 4 によって分離された活性領域 2 2 に形成されることになる。基板 1 0 は、少なくとも 1 つの周縁領域を含み、ここにはメモリセルアレイ領域内に形成されたメモリセルを作動させための制御回路が形成されることに留意されたい。また、分離ブロック 2 6 は、前述の同じ S T I 又は L O C O S 処理中に周縁領域内に形成されることが好ましい。

30

#### 【 0 0 1 2 】

##### メモリセル形成

図 1 F に示す構造体は更に以下のように処理される。図 2 A から 2 Q は、構造体の活性領域 2 2 を図 1 F の構造体に直交する方向（図 1 C 及び 1 F に示す線 2 A - 2 A に沿う）から見た断面図を示す。

30

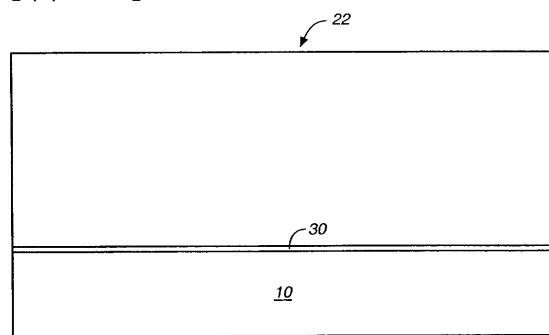

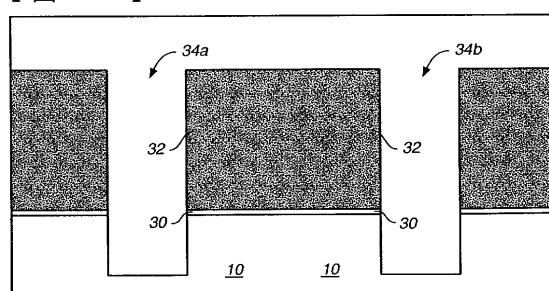

#### 【 0 0 1 3 】

図 2 A に示すように、まず絶縁層 3 0（好ましくは酸化物）が基板 1 0 上に形成される。記憶デバイスのセルアレイ部分の周縁領域に対する良好な独立制御のために、この時点では基板 1 0 の活性領域 2 2 部分をドープすることができる。このドープ処理は、V t 注入又はセルウエル注入と呼ばれる場合が多く、本技術分野ではよく知られている。この注入時に、周縁領域は、構造体全体にわたって蒸着され基板のメモリセルアレイ領域だけから除去されるフォトレジスト層によって保護される。

40

#### 【 0 0 1 4 】

次に、窒化物等の硬質マスク材の厚い層 3 2（例えば、厚さ ~ 3500）は、酸化物層 3 0 上に形成される。複数の平行な第 2 のトレンチ 3 4 は、フォトレジスト（マスキング）材料を窒化物層 3 2 上に塗布し、次に、選択されている平行帯領域からフォトレジスト材を除去するためのマスキング処理を行うことによって窒化物層 3 2 内に形成される。異方性窒化物エッチング処理は、帯領域内の窒化物層 3 2 の露出部分を除去して、酸化物層 3 0 まで下方に延びこれを露出させる第 2 のトレンチ 3 4 を形成するために使用される。フォトレジスト材を除去した後、異方性酸化物エッチング処理は、酸化物層 3 0 の露出部分を除去して、第 2 のトレンチ 3 4 を基板 1 0 まで下方へ延ばすために使用される。次

50

に、シリコン異方性エッチング処理は、第2のトレンチ34を各々の活性領域22の基板10内まで下方へ延ばすために使用される（例えば、約0.15um技術であれば約0.15umの深さといった、約1の形状サイズに相当する深さまで下方へ）。もしくは、フォトレジスト材は、トレンチ34が基板10内に形成された後に除去することもできる。図2Bは結果として得られる活性領域22を示す。

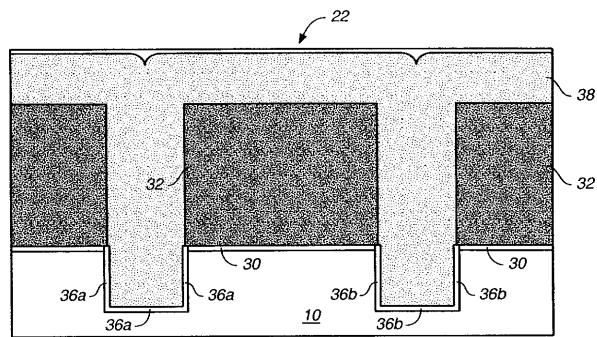

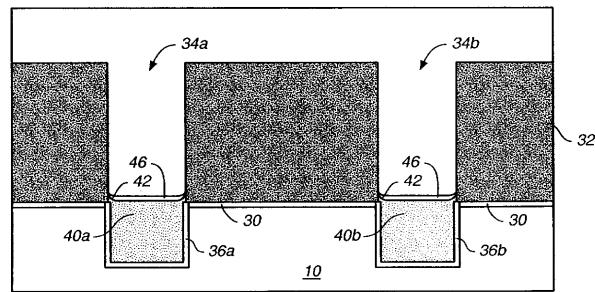

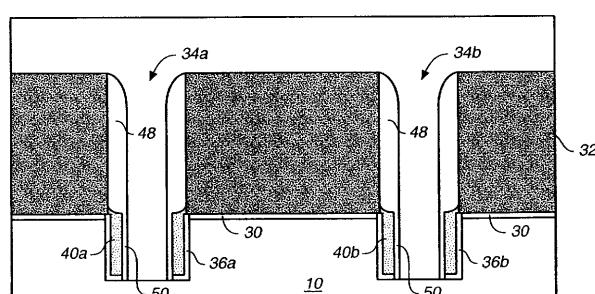

#### 【0015】

次に、絶縁材層36（例えば、厚さ～70から120）は、第2のトレンチ34の底壁及び下方側壁を形成する第2のトレンチ34の露出されたシリコンに沿って形成される（好ましくは熱酸化処理にて）。次に、第2のトレンチ34を充填するポリシリコン（以下、「ポリ」と呼ぶ）の厚い層38が構造体上に形成される。ポリ層38は、イオン注入によって、又はインサイチュ（in-situ）処理によってドープすることができる（例えば、n+）。図2Cは、結果として得られた活性領域22を示す。

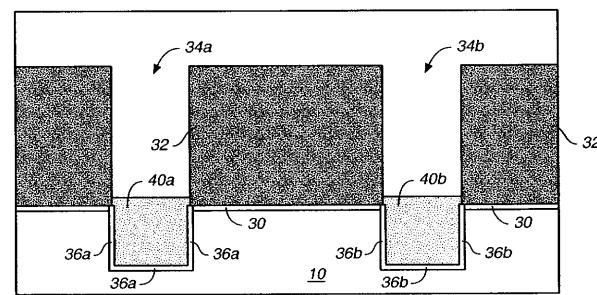

#### 【0016】

ポリエッチング処理（例えば、窒化物層32をエッチングストップとして使用するCMP処理）は、第2のトレンチ34内に残留するポリシリコン38のブロック40以外のポリ層38を除去するために使用される。次に、制御されたポリエッチング処理は、ポリブロック40の高さを低くするために使用され、図2Dに示すように、ポリブロック40の上端は、基板表面よりも上に位置するが分離領域24のSTIブロック26の上端よりも下に位置することになる。

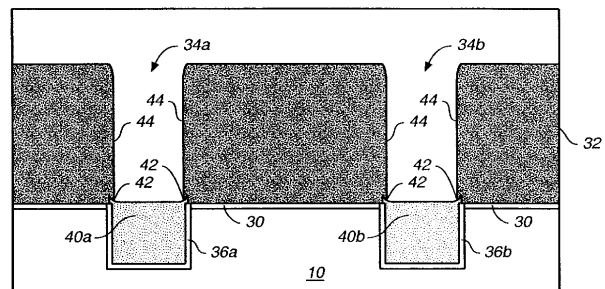

#### 【0017】

次に、別のポリエッチングが行われ、ポリブロック40の上端（第2のトレンチの側壁に隣接した）に傾斜部42が形成される。次に、窒化物スペーサ44は、ポリブロック40の傾斜部42より上方で第2のトレンチの側壁に沿って形成される。スペーサを形成することは本技術分野ではよく知られており、構造体の外形の全体を覆う特定の材料の蒸着、及びこれに続く異方性エッチングを含み、これにより構造体の水平面からこの材料は除去されるが、構造体の垂直方向の表面上には殆どそのままこの材料が残るようになる。スペーサ44は、酸化物や窒化物等の任意の誘電体で形成することができる。本発明において、絶縁スペーサ44は、構造体の全体にわたって窒化物層を蒸着し、次に、スペーサ44以外の蒸着窒化物層を除去するための公知の反応性イオンエッチング（RIE）等の異方性窒化物エッチング処理を施すことによって形成される。図2Eは、結果として得られた活性領域22を示す。スペーサ44がポリブロック40の傾斜部42で形成される先端部の鋭度を高めるために使用される場合には、窒化物スペーサ44の形成は随意的であることに留意されたい。つまり、図2から2Rは、随意的な窒化物スペーサ44をもたない残りの処理工程を示している。

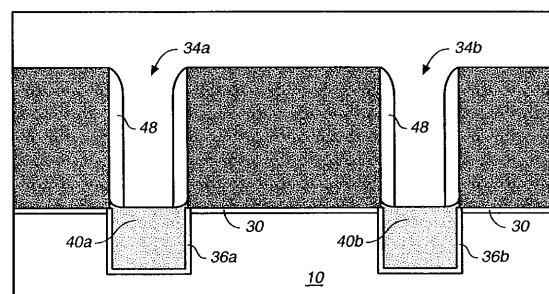

#### 【0018】

次に、熱酸化処理が行われ、図2Fに示すように、ポリブロック40の露出上面が酸化する（上面に酸化物層46を形成する）。次に、構造体上に酸化物を蒸着し（例えば、厚さ約350）、これに続いて異方性酸化物エッチング処理を行うことにより、第2のトレンチ34の側壁に沿って酸化物スペーサ48（図2Gに示す）が形成される。また、酸化物エッチング処理は、第2のトレンチ34の各々の酸化物層46の中央部を除去する。図2Gは、結果として得られた活性領域22を示す。

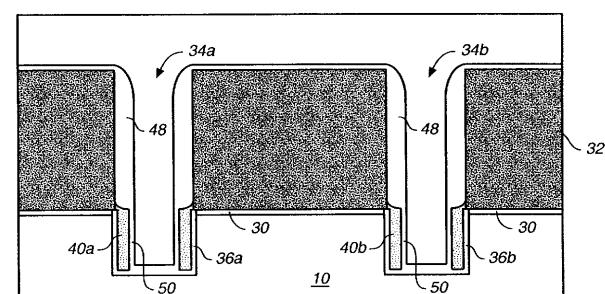

#### 【0019】

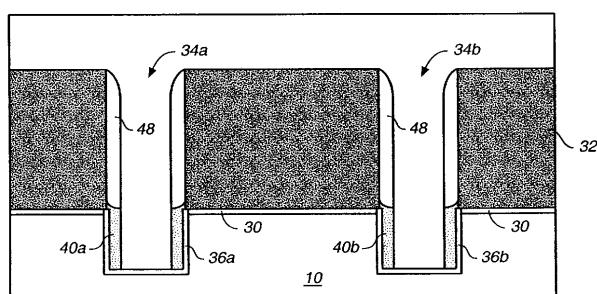

次に、酸化物スペーサ48によって保護されていないポリブロック40の中央部を除去する異方性ポリエッチング処理が行われ、図2Hに示すように、第2のトレンチ34の各々に、対向する一対のポリブロック40が残る。次に、絶縁蒸着及び異方性エッチングバック処理を使用して、第2のトレンチ34の内側のポリブロック40aの露出した側面に沿って絶縁層50が形成される（図2Iに示す）。絶縁材は、任意の絶縁材とすることができます（例えば、酸化物/窒化物/酸化物（ONO）又は他の高誘電体）。絶縁材は、酸化物蒸着/エッチング処理がやはり酸化物スペーサ48を厚くし、第2のトレンチ34の各々の底部にある酸化物層36の露出部分を除去して、図2Jに示すように基板10を露

10

20

30

40

50

出させる結果となるように、酸化物であることが好ましい。更に、この処理は、トレンチ34の各々の底部の酸化物層36が除去される際に、トレンチ34内の活性領域22の隣接するカラムの間のSTI酸化物も除去する。

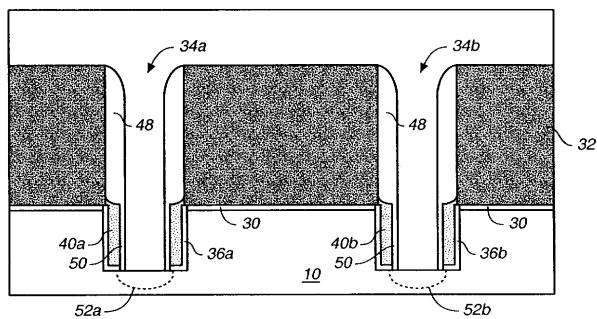

【0020】

次に、適切なイオン注入（及び可能な焼鈍）は構造体の表面を横切って行われ、第2のトレンチ34の底部の露出した基板部分に第1の（ソース）領域52が形成される。ソース領域52は、第2のトレンチ34に対して自己整列し、活性領域22のカラムに対して実質的に直交する連続的な列を形成し、基板の第1の導電型（例えばP型）とは異なる第2の導電型（例えばN型）を有する。イオンは、窒化物層32に対して何ら影響を及ぼさない。図2Kは、結果として得られた活性領域22を示す。

10

【0021】

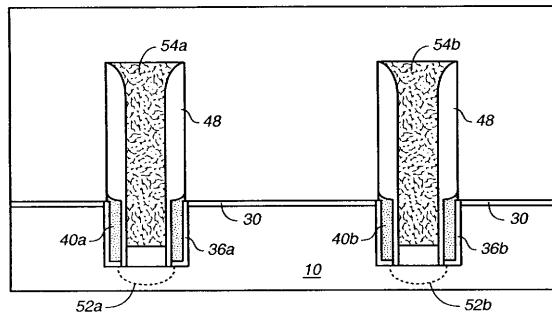

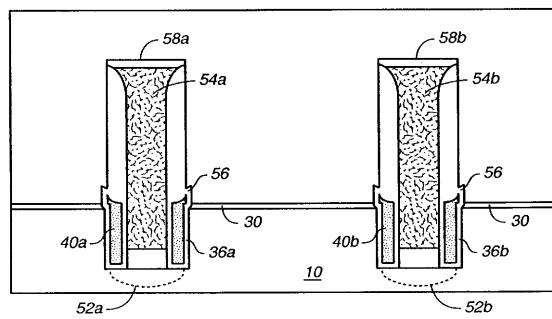

続いて酸化蒸着工程が行われ、各々のトレンチ34の底部を酸化物層35で充填する。この酸化物層35は、少なくとも約100オングストロームであり、蒸着形成されることになる制御ゲート54とポリブロック40との間に容量結合が生じ得るように、形成されることになる浮遊ゲートポリブロック40の高さよりは薄い。次に、ポリ蒸着工程、及びこれに続くポリCMPエッチング（エッチングストップとして窒化物層32を用いて）が行われ、図2Lに示すように、第2のトレンチ34がポリブロック40で充填される。従って、ポリ54は、連続的な列の各々のトレンチ34を充填する。次に、窒化物エッチング処理が施されて、窒化物層32が除去されてポリブロック40の上縁部が露出する。次に、トンネル酸化物層56は、熱酸化処理、酸化物蒸着処理、又は両処理によってポリブロック40の露出した上縁部に形成される。また、この酸化物形成工程は、ポリブロック40の露出した上端面に酸化物層58を形成すると同時に、基板10の酸化物層30の厚みを増大させであろう。この段階で、活性領域22をマスキングすることによって、周縁領域に随意的なイオン注入を行うことができる。図2M及び2Nは、結果として得られた活性領域22を示す。

20

【0022】

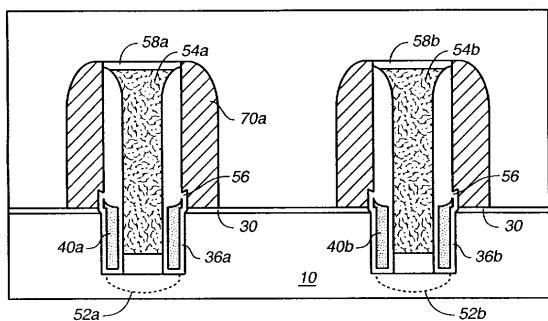

次に、窒化物スペーサ70は、図2Nに示す構造体に隣接して形成される。このことは、表面全体にシリコン窒化物70を蒸着し、次に、窒化物を異方性エッチングしてスペーサ70を形成することで実現できる。図2Oは、結果として得られた構造体を示す。

30

【0023】

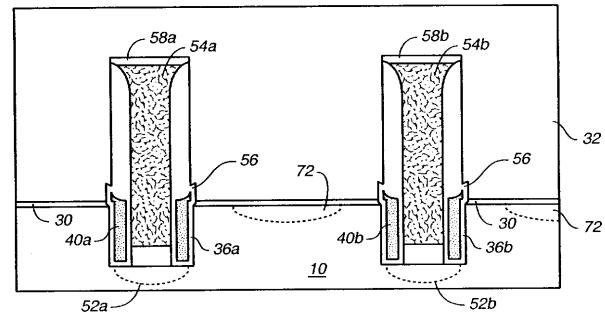

構造体全体にわたる注入が行われる。具体的には、各窒化物スペーサ70の間の領域にはドレイン領域72が形成される。注入エネルギーは、分離酸化物より下方に広がるのに十分な大きさである。つまり、ドレイン領域72はロウ方向に連続的である。図2Pは、結果として得られた構造体を示す。

【0024】

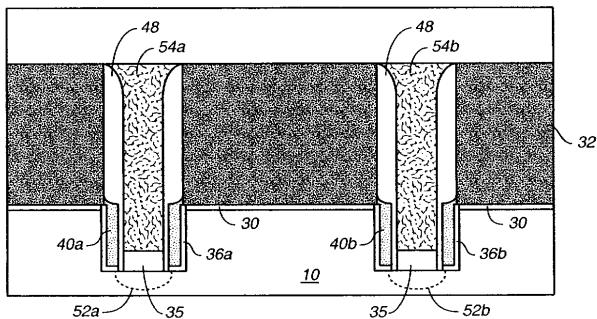

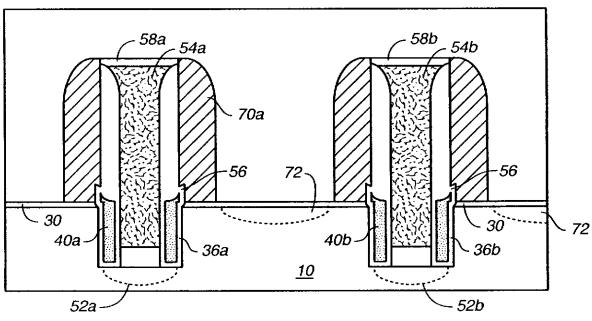

窒化物スペーサ70が除去され、図2Qは、結果として得られた構造体を示す。

【0025】

最後に、ポリ蒸着工程によって構造体上にポリ層62（例えば厚さ約500）を形成する。続いて、フォトレジスト蒸着及びマスキング工程が行なわれて活性領域22に相互に離間した複数の帯状ポリ層62が形成される。図2Rは、結果として得られた活性領域22を示す。各々のポリ層62は、メモリアレイのワード線として機能する。

40

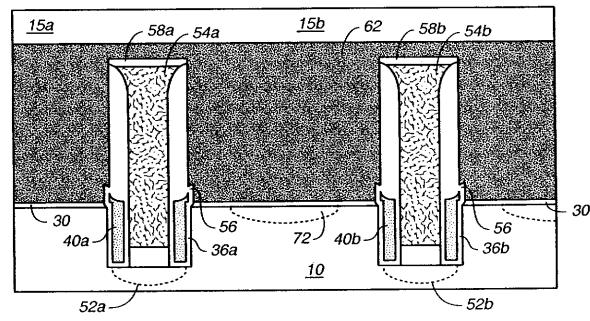

【0026】

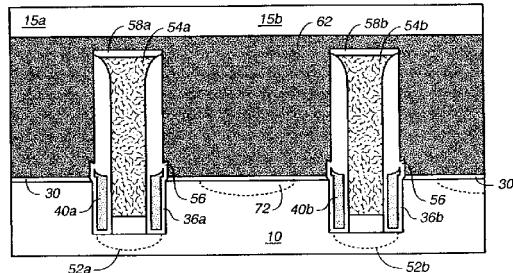

図2Rに示すように、本発明の処理は、各々のメモリセル15がソース領域52とドレイン領域72との間にあるメモリセルのアレイを形成する（当業者であればソース及びドレインという用語は作動中に入れ替わり得ることを理解できるであろう）。非平面のチャネル領域はソース領域52とドレイン領域72とを接続し、チャネル領域は第1の部分及び第2の部分の2つの部分を有している。チャネル領域の第1の部分は、一方のトレンチ34の一方の側壁に沿うと共に第1のソース領域52aに隣接している。チャネル領域の第2の部分は、基板10の平面に沿うと共にトレンチ34とドレイン領域72との間にある。誘電体層はチャネル領域を覆っている。チャネルの第1の部分を覆う誘電体は層36

50

a である。チャネルの第 2 の部分を覆う誘電体は層 3 0 である。浮遊ゲート 4 0 a は層 3 6 a を覆い、第 1 のソース領域 5 2 a に隣接するチャネル領域の第 1 の部分を覆っている。ポリ層 6 2 によって形成されるゲート電極 6 2 は、誘電体層 3 0 上にあり、チャネル領域の第 2 の部分を覆っている。制御ゲート 5 4 はソース領域 5 2 から絶縁され、浮遊ゲート 4 0 a と容量結合する。各々の浮遊ゲート 4 0 は、ゲート電極 6 2 及び基板 1 0 の表面に対して実質的に直交する。最後に、ソース領域 5 2 a 等のソース領域、及びそれに関連する制御ゲート 5 4 a 等の制御ゲートは、同一活性領域 2 2 内の一方側に隣接するメモリセル 1 5 と共に用され、ドレイン領域 7 2 は、他方側に隣接するメモリセル 1 5 と共に用される。

## 【0027】

10

全ての浮遊ゲート 4 0 は、トレンチ 3 4 内に配置され、各々の浮遊ゲート 4 0 は、チャネル領域の一部と向かい合うと共に絶縁されている。更に、各々の浮遊ゲート 4 0 は、上方部分を含み、この上方部分は、基板表面の上方まで延び、ゲート電極 6 2 の 1 つに向かい合うと共に絶縁されている端部で終端しており、酸化物層 5 6 を経由するファウラーノルドハイムトンネル現象のための経路をもたらすようになっている。各々の制御ゲート 5 4 は、浮遊ゲート 4 4 に沿って延びる共に浮遊ゲート 4 4 から絶縁されており（酸化物層 5 0 によって）、浮遊ゲート 4 4 との間に強化された電圧結合をもたらすようになっている。

## 【0028】

20

アレイを形成する複数のメモリセル 1 5 に関連して相互接続は以下の通りである。同じカラム、即ち同じ活性領域 2 2 のメモリセル 1 5 において、各々のメモリセル 1 5 用のゲート電極を形成するワード線 6 2 は、Y 方向に各々のメモリセル 1 5 まで延びる。同じ口ウ、即ち活性領域 2 2 及び S T I 2 6 を横切るメモリセル 1 5 では、ソース線 5 2 及びこれに関連する制御ゲート 5 4 は、X 方向にこれらの各々のメモリセル 1 5 まで連続的に延びる。更に、ドレイン線 7 2 は、X 方向に各々のメモリセル 1 5 まで連続的に延びる。最後に、以上の説明から分かるように、隣接する口ウのメモリセル 1 5 は、一方側で同じソース領域 5 2 及びこれに関連する同じ制御ゲート 5 4 を共用し、他方側で同じドレイン領域 7 2 を共用する。メモリセル 1 5 の各々は、4 つの独立制御可能な端子であるワード線 6 2 、制御ゲート 5 4 、ドレイン領域 7 2 、及びソース領域 5 2 を有する。

## 【0029】

30

当業者であれば理解できるように、線 5 2 a 、 5 2 b 、 5 2 c 等は埋込拡散線であり、これらの線に対する接続は、メモリセルアレイの外側で行う必要がある。1 つの方法は、制御ゲート 5 4 と同様のポリブロック 5 4 を使用することであるが、このポリブロック 5 4 は、アレイの外側で埋込拡散線 5 2 a 、 5 2 b 、 5 2 c 等と電気的に接触する。更に、アレイの外側で埋込拡散線 5 2 a 、 5 2 b 、 5 2 c 等と接触するポリブロック 5 4 は、アレイ内の独立制御ゲート 5 4 と電気的に接触してはいけない。更に、線 7 2 a 、 7 2 b 、 7 2 c は同様に埋込拡散線であり、これらの線に対しても接続を行う必要がある。つまり、メモリセル 1 5 のアレイは仮想接地アレイである。

## 【0030】

40

メモリセルの動作

以下に図 2 R に示すメモリセル 1 5 の動作について説明する。

## 【0031】

消去

メモリセル 1 5 を消去するには 2 つの方法がある。第 1 の方法では、メモリセル 1 5 は、ドレイン領域 7 2 に 0 V 、ソース領域 5 2 に 0 V を印加することで消去できる。ソース領域 5 及びドレイン領域 7 2 に同一の電圧が印加されるので、チャネル領域内には電荷が全く伝導されないことになる。制御ゲート 5 4 には - 8 から - 1 5 V 程度の負電圧が印加される。最後に、ワード線 6 2 には + 2 から + 4 V 程度の正電圧が印加される。制御ゲート 5 4 は、浮遊ゲート 4 0 に対して高度に容量結合されるので、浮遊ゲート 4 0 には高い負電圧が生じることになる。これにより浮遊ゲート 4 0 とワード線 6 2 との間に大きな電

50

圧差が生じる。浮遊ゲート 4 0 に蓄えられた全ての電子は、制御ゲート 5 4 で跳ね返され、ワード線 6 2 に印加された正電圧によって引き寄せられ、ファウラー・ノルドハイムトンネル現象のメカニズムにより浮遊ゲート 4 0 から除去され、トンネル酸化物 5 6 を通ってワード線 6 2 に通り抜ける。消去に関するこのポリ間トンネル現象のメカニズムは、その開示内容の全てが引用によって本明細書に組み込まれている米国特許第 5,029,130 号に説明されている。

#### 【 0 0 3 2 】

メモリセル 1 5 を消去する第 2 の方法は、ドレイン領域 7 2 に対して 0 V、ソース領域 5 2 に対して + 2 から + 5 V 程度の低い正電圧を印加することである。制御ゲート 5 4 には - 8 から - 15 V 程度の負電圧が印加される。最後に、ワード線 6 2 には、0 から - 2 V 程度のゼロ又は低い負電圧が印加される。ワード線 6 2 に対して正電圧が印加されないので、チャネル領域はオン状態にはならない。更に、制御ゲート 5 4 は、浮遊ゲート 4 0 に対し高度に容量結合されているので、浮遊ゲート 4 0 には低い負電圧が生じることになる。これにより浮遊ゲート 4 0 とソース領域 5 2 との間に大きな電圧差が生じる。浮遊ゲート 4 0 に蓄えられた全ての電子は、制御ゲート 5 4 で跳ね返され、ソース領域 5 2 に印加された正電圧によって引き寄せられ、ファウラー・ノルドハイムトンネル現象のメカニズムにより浮遊ゲート 4 0 から除去され酸化物 3 5 を通ってソース領域 5 2 に通り抜ける。

#### 【 0 0 3 3 】

#### プログラミング

メモリセル 1 5 のプログラミングは以下のように行うことができる。ソース領域 5 2 は + 3 から + 5 V の正電圧に保持される。制御ゲート 5 4 は + 8 から + 10 V の正電圧に保持される。ワード線 6 2 は、1 から 3 V の正電圧に保持される。ドレイン領域 7 2 は接地電位に保持される。制御ゲート 5 4 は、浮遊ゲート 4 0 に対して高度に容量結合されているので、制御ゲート 5 4 の + 8 から + 10 V の正電圧は、浮遊ゲート 4 0 にチャネル領域の第 1 の部分をオン状態にさせるのに十分な高い正電位を生じさせる。ワード線 6 2 上の 1 から 3 V の正電圧は、チャネル領域の第 2 の部分をオン状態にさせるのに十分である。つまり、電子は、チャネル領域内をドレイン領域 7 2 からソース領域 5 2 まで流れることになる。しかしながら、電子は、チャネル領域が平面からトレンチ 3 4 へ実質的に 90° 方向を変えるチャネル領域内の接合部において、浮遊ゲート 4 0 の高い正電圧に起因した急激な電圧の増大を経験することになる。これにより電子は浮遊ゲート 4 0 にホットチャネル注入されることになる。プログラミングに関するこのホットチャネル電子注入メカニズムは、その開示内容の全てが引用によって本明細書に組み込まれている米国特許第 5,029,130 号に説明されている。

#### 【 0 0 3 4 】

#### 読み取り

メモリセル 1 5 の読み取りは、以下のように行うことができる。ソース領域 5 2 は、接地電位にて保持される。制御ゲート 5 4 は、正電圧 V dd にて保持される。ワード線 6 2 は、通常はチャネル領域の第 2 の部分をオン状態にするのに十分な正電圧 V dd にて保持される。ドレイン領域 7 2 は、+ 1.0 V といった低い正電圧に保持される。制御ゲート 5 4 上の正電圧 V dd は、浮遊ゲート 4 0 がプログラムされない場合にはチャネル領域の第 1 の部分をオン状態にするのに十分である。この場合、電子は、チャネル領域内をソース領域 5 2 からドレイン領域 7 2 まで流れることになる。しかしながら、浮遊ゲート 4 0 がプログラムされる場合、制御ゲート 5 4 上の正電圧 V dd は、チャネル領域の第 1 の部分をオン状態にするには十分でない。この場合、チャネルは非導電性のままである。つまり、ドレイン領域 7 2 で検出される電流の大きさ又は電流の有無は、浮遊ゲート 4 0 のプログラミング状態を決定する。

#### 【 0 0 3 5 】

#### メモリセルアレイの動作

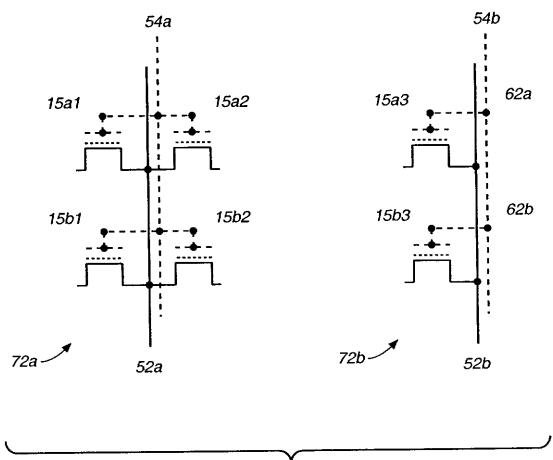

次に、メモリセル 1 5 のアレイの動作について説明する。図 3 には、メモリセルのアレイが概略的に示されている。図 3 に示すように、メモリセル 1 5 のアレイは、複数のカラ

10

20

30

40

50

ム、即ち 15a (1-3) 及び 15b (1-3)、複数の口ウ、即ち 15 (a-b) 1、15 (a-b)、及び 15 (a-b) 3 に配列された複数のメモリセルを含む。メモリセル 15 に接続されたワード線 62 は、同じカラムの他のメモリセル 15 にも接続される。ソース領域 52 及び制御ゲート 54 は、同じ口ウのセル 15 に接続され、両側のメモリセル 15 によって共用される。ドレイン領域 72 は、同じ口ウのセルに接続され、両側のメモリセル 15 によって共用される。1つの口ウ内のメモリセル 15 は、一方側のメモリセル 15 と接する共通ドレイン領域 72 を有し、他方側のメモリセルと接する共通ソース領域 52 及び制御ゲート 54 を有する。

【0036】

消去

10

消去動作には前述したように 2 つの可能な動作モードがある。第 1 のモードでは個々のメモリセル 15 を消去できる。各種の線に印加される電圧は以下の通りである。選択されているメモリセル 15 に関するドレイン領域 72 には接地電位が印加される。同様に、選択されていないメモリセル 15 に関するドレイン領域 72 には接地電位が印加される。選択されているメモリセル 15 に関するソース領域 52 には接地電位が印加される。同様に、選択されていないメモリセル 15 に関するソース領域 52 には接地電位が印加される。選択されているメモリセル 15 に関するワード線 62 には約 +2 から +4 V の正電圧が印加される。選択されていないメモリセル 15 に関するワード線 62 には接地電位が印加される。最後に、選択されているメモリセル 15 に関する制御ゲート 54 には -8 から -1 5 V 程度の高い負電圧が印加される。選択されていないメモリセル 15 に関する制御ゲート 54 には接地電位が印加される。

20

【0037】

前述したように、選択されているメモリセル 15 に関しては、浮遊ゲート 40 に対する制御ゲート 54 の大きな静電容量は浮遊ゲート 40 に高い負電圧をもたらす。隣接ワード線 62 上の正電圧により、電子はワード線 62 に引き寄せられることになり、ファウラーノルドハイムトンネル現象のメカニズムにより、電子は浮遊ゲート 40 から除去される。同じカラム内の選択されていないメモリセル 15 に関しては、+2 から +4 V の低い正電圧がワード線 62 に印加されるが、選択されていないメモリセル 15 の制御ゲート 54 は接地電位に保持されるので、同じカラム内の選択されていないメモリセル 15 の浮遊ゲート 40 上の電子は、ワード線 62 に引き寄せられないことになる。同じ口ウの選択されていないメモリセル 15 に関しては、制御ゲート 54 には高い負電圧が印加されるが、対応するワード線 62 は接地電位に保持される。つまり、選択されていないメモリセル 15 の浮遊ゲート 40 から電子を引き寄せる正電圧は全く存在しない。このモードにおいて、消去はビット選択可能である。

30

【0038】

消去の第 2 のモードにおいては、印加される各種電圧は以下の通りである。選択されているメモリセル 15 に関するドレイン領域 72 は接地電位が供給される。同様に、選択されていないメモリセル 15 に関するドレイン領域 72 には接地電位が供給される。選択されているメモリセル 15 に関するソース領域 52 には +2 から +4 V の低い正電圧が供給される。選択されていないメモリセル 15 に関するソース領域 52 には接地電位が供給される。選択されているメモリセル 15 に関するワード線 62 には接地電位から約 0 から -2 V の低い負電圧が供給される。選択されていないメモリセル 15 に関するワード線 62 には接地電位から約 0 から -2 V の低い負電圧が供給される。最後に、選択されているメモリセル 15 に関する制御ゲート 54 には、-8 から -1 5 V 程度の高い負電圧が供給される。選択されていないメモリセル 15 に関する制御ゲート 54 には接地電位が供給される。

40

【0039】

この動作モードにおいて、同じ口ウ内の全てのメモリセル 15 は同時に消去される。つまり、このモードにおいて、消去は口ウ選択可能である。選択されている口ウのメモリセル 15 に関しては、浮遊ゲート 40 に対する制御ゲート 54 の大きな静電容量は、浮遊ゲ

50

ート 4 0 に高い負電圧をもたらす。隣接ソース領域 5 2 上の正電圧により、電子はソース領域 5 2 に引き寄せられることになり、ファウラーノルドハイムトンネル現象のメカニズムにより、電子は浮遊ゲート 4 0 から除去される。選択されていないロウのメモリセル 1 5 に関しては、制御ゲート 5 4 は接地電位に保持される。最後に、全てのワード線 6 2 に供給される接地電位から負電圧により、全てのメモリセル 1 5 のチャネル領域は確実にオン状態にならない。

#### 【 0 0 4 0 】

##### プログラム

メモリセル 1 5 の浮遊ゲート 4 0 がプログラムされると想定する。この場合、前述の議論に基づいて、各種の線に印加される電圧は以下の通りである。線 7 2 b は接地電位であるが他の全てのドレイン領域 7 2 a は  $V_{dd}$  である。線 5 2 a は +3 から +5 V であるが他の全てのソース線 5 2 b は接地電位である。線 6 2 b は +1 から +3 V であるが全てのワード線 6 2 a は接地電位から -2 V である。線 6 2 b は +1 から +3 V であるが他の全てのワード線 6 2 a は接地電位から -2 V である。線 5 4 a は +8 から +10 V であるが他の全ての線 5 4 b は接地電位である。選択されていないメモリセル 1 5 上の「外乱」は以下の通りである。

#### 【 0 0 4 1 】

未選択カラムのメモリセル 1 5 に関しては、ワード線 6 2 a に対して 0 から -2 V を印加することは、チャネル領域の第 2 の部分（ワード線 6 2 a が制御する部分）がオン状態にないので、それらのメモリセル 1 5 a ( 1 - n ) 及び 1 5 c ( 1 - n ) に関する全てのチャネル領域がオン状態にならないことを意味する。つまり、外乱は全く存在しない。同じ選択カラムにあるが、選択メモリセル 1 5 と共にソース領域 5 2 及び制御ゲート 5 4 をもつ側の未選択ロウのメモリセル 1 5 b 1 に関しては、線 7 2 a に対して  $V_{dd}$  を印加することは、そのメモリセル 1 5 b 1 に殆ど又は全く電流が流れないことを意味する。最後に、同じ選択カラムにあるが選択メモリセル 1 5 と共にドレイン領域 7 2 をもつ側の未選択ロウのメモリセル 1 5 b 3 に関しては、線 5 4 b 及び 5 2 b に対して接地電位を印加することは、そのメモリセル 1 5 b 3 に殆ど又は全く電流が流れないことを意味する。

#### 【 0 0 4 2 】

##### 読み取り

メモリセル 1 5 の浮遊ゲート 4 0 を読み取る場合を想定する。前述の議論に基づいて、各種の線に印加される電圧は以下の通りである。ドレイン領域線 7 2 b は約 +1 V の正電圧に保持されるが、未選択ドレイン線 7 2 a は接地電位に保持される。制御ゲート線 5 4 a は正電圧  $V_{dd}$  に保持されるが、未選択制御ゲート 5 4 b は地電位に保持される。選択ワード線 6 2 b は正電圧  $V_{dd}$  に保持されるが、未選択ワード線 6 2 a は接地電位に保持される。最後に、選択ソース線 5 2 a は地電位に保持されるが、選択ドレイン線 7 2 b に直接隣接する未選択ソース線 5 2 b は 1 V に保持され、未選択ドレイン線 7 2 a に直接隣接する未選択ソース線 5 2 は接地電位に保持される。つまり、選択されているメモリセル 1 5 の一方側の全てのメモリセル 1 5 は、ソース 5 2 及びドレイン 7 2 への印加電圧と同じ電圧を有し、同様に、他方側の全てのメモリセルはソース 5 2 及びドレイン 7 2 への印加電圧と同じ電圧を有することになる。選択されていないメモリセル 1 5 上の「外乱」は以下の通りである。

#### 【 0 0 4 3 】

未選択カラムのメモリセル 1 5 に関しては、ワード線 6 2 a に対して 0 V を印加することは、それらのメモリセル 1 5 に関するチャネル領域が全てオン状態にならないことを意味する。つまり、外乱は全く存在しない。同じ選択ロウにあるが未選択ロウにあるメモリセル 1 5 b 1 及び 1 5 b 3 に関しては、それらのメモリセルのソース 5 2 及びドレイン 7 2 に対して同じ電圧を印加することは、チャネル領域がオン状態にならないことを意味する。つまり、メモリセル 1 5 b 2 に対する外乱は殆ど又は全く生じない。

#### 【 0 0 4 4 】

以上の説明から、新規な高密度不揮発性メモリセル、アレイ、及び製造方法を理解でき

10

20

30

40

50

るはずである。単一ビットがメモリセルの各々の浮遊ゲートに記憶されるようになった好適な実施形態を説明したが、複数のビットを単一のメモリセルの浮遊ゲートに記憶させて記憶密度を高めることも本発明の精神の範疇にあることを理解されたい。

【図面の簡単な説明】

【0045】

【図1A】分離領域を形成するために本発明方法の第1のステップで使用される半導体基板の平面図である。

【図1B】図1Aの線1B-1Bに沿って見た構造体の断面図であり、本発明の最初の処理ステップを示す。

【図1C】構造体の平面図であり、図1Bの構造体を処理する次のステップを示し、本ステップで分離領域が形成される。 10

【図1D】図1Cの線1D-1Dに沿って見た構造体の断面図であり、構造体内に形成された分離トレンチを示す。

【図1E】図1Dの構造体の断面図であり、分離トレンチ内の分離ブロック材の形成を示す。

【図1F】図1Eの構造体の断面図であり、分離領域の最終的な構造を示す。

【図2A】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。 20

【図2B】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2C】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。 20

【図2D】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2E】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。 30

【図2F】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2G】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2H】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。 40

【図2I】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2J】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2K】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2L】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮 50

遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2M】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2N】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2O】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2P】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2Q】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図2R】図1Fの線2A-2Aに沿って見た半導体構造体の断面図であり、本発明の浮遊ゲートメモリセルの不揮発性記憶アレイの形成における半導体構造体の処理ステップを示す。

【図3】本発明のメモリセルアレイの概略的な回路図である。

【符号の説明】

【0046】

- 10 半導体基板

- 15a メモリセル

- 15b メモリセル

- 30 酸化物層（誘電体層）

- 36a 誘電体層

- 36b 誘電体層

- 40a 浮遊ゲート

- 40b 浮遊ゲート

- 52a ソース領域

- 52b ソース領域

- 54a 制御ゲート

- 54b 制御ゲート

- 56 トンネル酸化物層

- 58a 酸化物層

- 58b 酸化物層

- 62 ゲート電極

- 72 ドレイン領域

10

20

30

40

【図 1 A】

【図 1 C】

【図 1 B】

【図 1 D】

【図 1 E】

【図 2 A】

【図 1 F】

【図 2 B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2I】

【図2H】

【図2J】

【図2K】

【図2M】

【図2L】

【図2N】

【図2O】

【図2Q】

【図2P】

【図2R】

【図3】

## フロントページの続き

(74)代理人 100086771

弁理士 西島 孝喜

(72)発明者 ダナ リー

アメリカ合衆国 カリフォルニア州 95051 サンタ クララ エリオット ストリート 2

652

(72)発明者 ボニー チェン

アメリカ合衆国 カリフォルニア州 95014 クーパーティノ カーメン ロード 1005

9

(72)発明者 ソーラブ キアニアン

アメリカ合衆国 カリフォルニア州 94022 ロス アルトス ミランダ ロード 1432

0

F ターム(参考) 5F083 EP03 EP22 EP33 EP34 EP55 EP56 EP62 EP67 ER13 ER16

ER23 ER30 JA04 KA01 KA07 KA13 NA01 PR40

5F101 BA12 BA14 BA29 BD03 BD16 BD22 BD33 BD35 BE02 BE05

BE07