(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5376704号

(P5376704)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年10月4日(2013.10.4)

|                          |                      |

|--------------------------|----------------------|

| (51) Int.Cl.             | F 1                  |

| G 11 C 16/06 (2006.01)   | G 11 C 17/00 6 3 4 B |

| G 06 K 19/07 (2006.01)   | G 06 K 19/00 H       |

| G 11 C 11/4094 (2006.01) | G 06 K 19/00 J       |

|                          | G 06 K 19/00 N       |

|                          | G 11 C 11/34 3 5 3 F |

請求項の数 3 (全 14 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2004-360153 (P2004-360153)  |

| (22) 出願日     | 平成16年12月13日 (2004.12.13)      |

| (65) 公開番号    | 特開2005-196949 (P2005-196949A) |

| (43) 公開日     | 平成17年7月21日 (2005.7.21)        |

| 審査請求日        | 平成19年10月17日 (2007.10.17)      |

| 審判番号         | 不服2012-3574 (P2012-3574/J1)   |

| 審判請求日        | 平成24年2月24日 (2012.2.24)        |

| (31) 優先権主張番号 | 特願2003-415184 (P2003-415184)  |

| (32) 優先日     | 平成15年12月12日 (2003.12.12)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 塙野入 豊<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 熱海 知昭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 加藤 清<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のメモリセルと、

プリチャージ電位線、プリチャージ信号線及び複数のスイッチを有するプリチャージ回路と、

遅延回路と、

複数のビット線と電気的に接続されたカラムデコーダと、

複数のワード線と電気的に接続されたロウデコーダと、

前記ロウデコーダと電気的に接続された書き込み制御信号を伝達する書き込み制御信号線と、

前記ロウデコーダと電気的に接続された読み出し制御信号を伝達する読み出し制御信号線と、を有し、

前記複数のメモリセルは、それぞれ前記複数のビット線の一と前記複数のワード線の一が絶縁体を介して交差する領域に記憶素子を有し、

前記遅延回路の入力ノードは、前記書き込み制御信号線及び前記読み出し制御信号線と電気的に接続され、クロック信号線には接続されず、

前記遅延回路の出力ノードは、前記プリチャージ信号線に電気的に接続され、

前記ロウデコーダは、前記クロック信号線には接続されず、

前記遅延回路はインバータ及び論理回路を有し、

前記遅延回路のインバータ及び論理回路のそれぞれの数は、前記複数のワード線の一に

電気的に接続された前記ロウデコーダの一の回路を構成するインバータ及び論理回路のそれぞれの数と同じであり、

前記遅延回路による遅延時間は、前記ロウデコーダの遅延時間と等しく、

前記プリチャージ信号線は、前記複数のスイッチの入力ノードと電気的に接続され、

前記複数のスイッチは、それぞれ前記複数のビット線の一と前記プリチャージ電位線の導通を制御し、

前記書き込み制御信号及び前記読み出し制御信号がHレベルの時に前記遅延回路を通してプリチャージ信号が出力され、前記複数のスイッチがオンし、前記複数のビット線にプリチャージ電位が供給され、

前記書き込み制御信号がHレベルで、前記読み出し制御信号がLレベルの時に書き込み動作を行い、

前記書き込み制御信号がLレベルで、前記読み出し制御信号がHレベルの時に読み出し動作を行うことを特徴とする半導体装置。

#### 【請求項2】

請求項1において、

複数の画素を有する表示手段を有することを特徴とする半導体装置。

#### 【請求項3】

請求項1または請求項2に記載の前記半導体装置は、DRAM、SRAM、FeRAM、マスクROM、PROM、EPROM、EEPROM又はフラッシュメモリであることを特徴とする半導体装置。

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体素子を有する半導体装置に関する。また、本発明は無線通信によりデータの交信が可能な半導体装置（以下、「IDタグ」ともいう。）に関する。

##### 【背景技術】

##### 【0002】

近年、半導体素子を有する半導体装置は、コンピュータや携帯端末等の電子機器だけでなく、ICカード等の様々な分野に応用され、大容量化が進められている。半導体装置は、ビット線とワード線が絶縁体を介して交差する領域に記憶素子を含むメモリセルを複数有するメモリセルアレイと、前記ワード線が非選択の状態において、前記ビット線の電位を任意の電位に設定するプリチャージ回路とを有する。

30

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0003】

半導体装置の大容量化に伴って、長くなった配線の抵抗や大型化したデコーダの複雑さにより、アドレスの選択が遅延してしまうことがあった。そうすると、ビット線のプリチャージ動作を行う際に、ワード線が選択の状態である場合が生じ、その結果、誤作動がおきて、メモリセルが有するデータが書き換えられたり、破壊されたりすることがあった。つまり、データの読み出しと書き込みを正確に行うことが出来なかった。

40

##### 【0004】

上記の実情を鑑み、本発明は、アドレスの選択が遅延しても、誤作動を防止し、データの読み出しと書き込みを正確に行うことが可能な半導体装置、IDタグの提供を課題とする。

##### 【課題を解決するための手段】

##### 【0005】

上述した従来技術の課題を解決するために、本発明は以下の構成を有する半導体装置、IDタグを提供する。

##### 【0006】

本発明の半導体装置は、データ保持手段、プリチャージ手段及び遅延手段の3つの要素を

50

含むことを特徴とする。データ保持手段は複数のメモリセルを有する。プリチャージ手段はプリチャージ電位線、プリチャージ信号線及び複数のスイッチを有する。遅延手段は複数のトランジスタを有する。また、上記の3つの要素に加えて、カラムデコーダとロウデコーダを有するアドレス選択手段、複数の画素を有する表示手段の一方又は両方を有することを特徴とする。

【0007】

データ保持手段が有する複数のメモリセルの各々は、ビット線とワード線が絶縁体を介して交差する領域に記憶素子を含むことを特徴とする。記憶素子は、トランジスタ、容量素子及び抵抗素子から選択された1つ又は複数である。

【0008】

プリチャージ手段が有するプリチャージ電位線はプリチャージ電位を伝達する配線であり、プリチャージ信号線はプリチャージ信号を伝達する配線である。また、複数のスイッチの各々は、プリチャージ電位線とビット線の間に設けられることを特徴とする。複数のスイッチの各々は、スイッチング機能を有する素子であり、多くの場合において、トランジスタ又はアナログスイッチである。また、複数のスイッチの入力ノードは、前記プリチャージ信号線に接続する。なお、複数のスイッチの各々がトランジスタの場合、複数のスイッチの入力ノードとは、トランジスタのゲート電極に相当する。また、複数のスイッチの各々がアナログスイッチの場合、複数のスイッチの入力ノードとは、アナログスイッチを構成するN型トランジスタのゲート電極とP型トランジスタのゲート電極に相当する。

【0009】

遅延手段の入力ノードは、CK線及びWEB線に接続することを特徴とする。又は、遅延手段の入力ノードは、CK線、WEB線及びCEB線に接続することを特徴とする。又は、遅延手段の入力ノードは、REB線及びWEB線に接続することを特徴とする。又は、遅延手段の入力ノードは、REB線、WEB線及びCEB線に接続することを特徴とする。また、遅延手段の出力ノードは、プリチャージ信号線に接続することを特徴とする。なお、遅延手段は複数のトランジスタを有し、前記複数のトランジスタは、複数の論理回路を構成する。従って、遅延手段の入力ノードとは、複数の論理回路のうち、一端に配置された論理回路の入力ノードに相当する。

【0010】

本発明のIDタグは、データ保持手段、プリチャージ手段及び遅延手段の3つの要素を含む記憶手段と、制御手段、電源発生手段及び送受信手段を有することを特徴とする。また、本発明のIDタグは、データ保持手段、プリチャージ手段、遅延手段及びアドレス選択手段の4つの要素を含む記憶手段と、制御手段、電源発生手段及び送受信手段を有することを特徴とする。

【発明の効果】

【0011】

データ保持手段、プリチャージ手段及び遅延手段を有する本発明は、誤作動を防止し、データの読み出しと書き込みを正確に行なうことが可能な半導体装置を提供することができる。また、データ保持手段、プリチャージ手段及び遅延手段に加えて、表示手段を有する本発明は、高機能化と高付加価値化を実現した半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0012】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

(実施の形態1)

【0013】

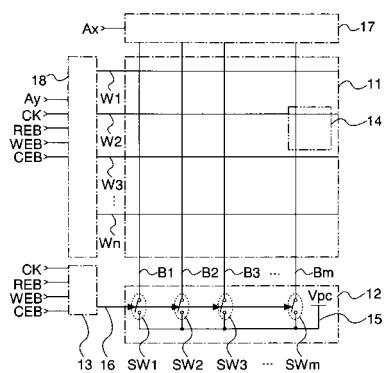

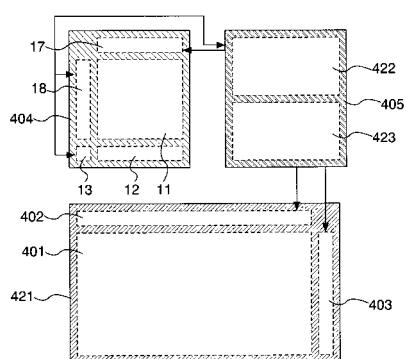

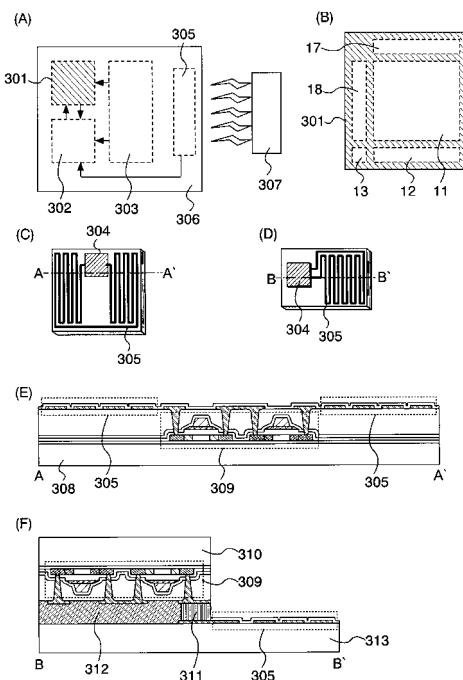

本発明の半導体装置は、データ保持手段11(以下メモリセルアレイ11と表記)、プリ

10

20

30

40

50

チャージ手段12及び遅延手段13の3つの基幹の要素を含むことを特徴とする(図1参照)。本発明の半導体装置は、データを記憶する機能を有する記憶手段に相当するものであり、当該記憶手段は、データ保持手段11、プリチャージ手段12及び遅延手段13の3つの基幹の要素を含む。

【0014】

メモリセルアレイ11は、マトリクス状に配置されたメモリセル14を複数有する(図1参照)。また、メモリセルアレイ11は、列方向に1列目からn列目までのビット線B1～Bn(nは自然数)と、行方向に1行目からm行目までのワード線W1～Wm(mは自然数)を有する。メモリセル14はビット線Bx(1×n)とワード線Wy(1×m)が絶縁体を介して交差する領域に記憶素子を含む。

10

【0015】

記憶素子は、トランジスタ、容量素子及び抵抗素子から選択された1つ又は複数である。本発明の半導体装置がDRAM(Dynamic Random Access Memory)の場合、記憶素子として、1つのトランジスタと1つの容量素子を用いる。また、SRAM(Static Random Access Memory)の場合、記憶素子として、6つのトランジスタ、5つのトランジスタ、4つのトランジスタと2つの抵抗素子、又は4つのトランジスタと1つの抵抗素子を用いる。なお、記憶素子として6つのトランジスタ、又は4つのトランジスタと2つの抵抗素子を用いる場合には、各列に2本のビット線(1本はビット線、もう1本はビットバー線)を配置する。なお本発明は、DRAM、SRAMに制約されず、記憶素子の構成に従って、FeRAM(Ferroelectric Random Access Memory)、マスクROM(Read Only Memory)、PROM(Programmable Read Only Memory)、EPROM(Electrically Programmable Read Only Memory)、EEPROM(Electrically Erasable Read Only Memory)、フラッシュメモリ等に成りうる。

20

【0016】

プリチャージ手段12(プリチャージ回路ともいう)は、プリチャージ電位線15、プリチャージ信号線16及び複数のスイッチSW1～SWm(mは自然数)を有する(図1参照)。複数のスイッチSWx(1×m)は、プリチャージ電位線15とビット線Bxの間に設けられる。また、複数のスイッチSWxは、スイッチング機能を有する素子であり、例えば、トランジスタ又はアナログスイッチである。さらに、複数のスイッチSWxの入力ノードはプリチャージ信号線16に接続する。つまり、スイッチSWxは、プリチャージ信号線16から伝達されるプリチャージ信号により導通又は非導通が制御される。

30

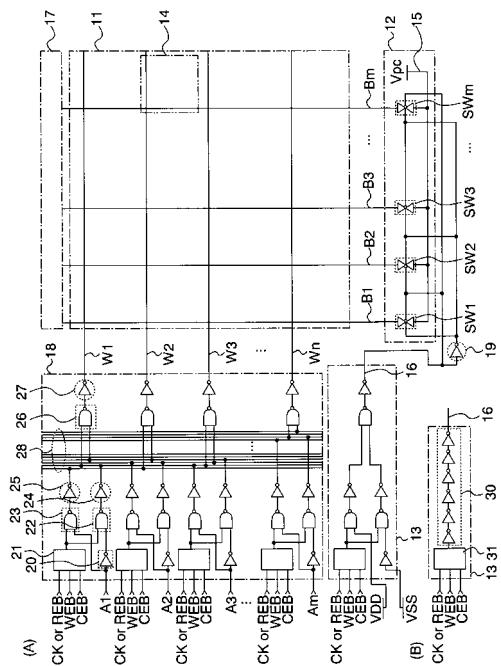

【0017】

本実施の形態では、スイッチSWxとして、アナログスイッチを用いる形態を示す(図2(A)参照)。アナログスイッチの入力ノードとは、アナログスイッチを構成するN型トランジスタのゲート電極とP型トランジスタのゲート電極に相当する。つまり、両トランジスタのゲート電極はプリチャージ信号線16に電気的に接続する。より詳しくは、アナログスイッチを構成するP型トランジスタのゲート電極はプリチャージ信号線16に直接接続し、N型トランジスタのゲート電極は、インバータ19の出力ノードに接続する。インバータ19の入力ノードはプリチャージ信号線16に接続する。

40

【0018】

遅延手段13(遅延回路ともいう)は、複数のトランジスタを有する(図1、2参照)。具体的には、遅延手段13は、複数のトランジスタから構成される複数の論理回路を有し、前記複数のトランジスタは少なくとも1つのインバータを構成する。さらに具体的には、遅延手段13は、AND、NAND、OR、NOR、EOR、ENOR、TriBUF(トライステートバッファ)及びTriINV(トライステートインバータ)等から選択された複数の論理回路と複数のインバータ、又は直列に接続された複数のインバータを有する。

そこで、図2(A)には遅延手段13が論理回路とインバータを有する場合を示し、図2

50

(B) には遅延手段 13 がインバータのみを有する場合を示す。

前者の図 2 (A) に示す形態では、遅延手段 13 の入力ノードとは論理回路 21 の入力ノードに相当し、前記遅延手段 13 の出力ノードとはインバータ 27 の出力ノードに相当する。なお、図 2 (A) に示すデコーダは、インバータ 20、論理回路 21 ~ 23、インバータ 24、25、論理回路 26、インバータ 27 及び配線 28 を有する。但し、デコーダの構成は上記の記載に制約されず、様々な構成が適用される。

また、後者の図 2 (B) に示す形態では、遅延手段 13 は、インバータ群 30 及び論理回路 31 を有する。遅延手段 13 の入力ノードとは論理回路 31 の入力ノードに相当し、前記遅延手段 13 の出力ノードとはインバータ群 30 の出力ノードに相当する。

#### 【0019】

10

遅延手段 13 の入力ノードは、CK 線及びWEB 線に接続するか、又は、CK 線、WEB 線及びCEB 線に接続するか、又は、REB 線及びWEB 線に接続するか、又は、又は REB 線、WEB 線及びCEB 線に接続し、出力ノードはプリチャージ信号線 16 に接続する。入力ノードの接続は、プリチャージ動作を行うタイミングと CK との関係と、CEB 信号の必要の有無に依存する。より詳しくは、CK と同期でプリチャージ動作を行う場合、遅延手段 13 の入力ノードは CK 線及びWEB 線に接続するか、又は、CK 線、WEB 線及びCEB 線に接続する。一方、CK と非同期でプリチャージ動作を行う場合、遅延手段 13 の入力ノードは REB 線及びWEB 線に接続するか、又は、REB 線、WEB 線及びCEB 線に接続する。

CEB 信号は、1 つのチップしか設けられていない場合や、複数のチップが設けられているにもかかわらず、読み出しや書き込みの動作を常時行う場合には不必要である。

20

なお、CK 線は CK (clock) 信号を伝達する配線であり、WEB (write enable) 線は WEB 信号を伝達する配線であり、REB (read enable) 線は REB 信号を伝達する配線であり、CEB (chip enable) 線は CEB 信号を伝達する配線である。また、WEB 信号は書き込み制御信号であり、REB 信号は読み出し制御信号であり、CEB 信号はチップ選択信号である。

#### 【0020】

遅延手段 13 を有する本発明は、プリチャージ手段 12 が有するスイッチ SWx の導通又は非導通を制御するプリチャージ信号の出力を遅延させることができる。そのため、ワード線 Wy の選択から非選択への切り替わりが遅延しても、プリチャージ信号の出力も遅延するため、前記ワード線 Wy が選択された状態で、プリチャージ動作を行うことがない。従って、上記構成を有する本発明の半導体装置は、誤作動を防止し、データの読み出しと書き込みを正確に行うことができる。

30

#### 【0021】

本発明は、データ保持手段 11、プリチャージ手段 12 及び遅延手段 13 の 3 つの基幹の要素に加えて、アドレス選択手段を含むことを特徴とする(図 1、2 参照)。

アドレス選択手段は、カラムデコーダ 17 とロウデコーダ 18 を有し、複数のメモリセル 14 から 1 つのメモリセルを選択する役目を担う。カラムデコーダ 17 はビット線 B1 ~ Bm に接続し、ロウデコーダ 18 はワード線 W1 ~ Wn に接続する。また、カラムデコーダ 17 は列アドレス選択線に接続し、ロウデコーダ 18 は行アドレス選択線に接続する。なお列アドレス選択線は、列アドレス選択信号 (Ax, 1 x m) を伝達する配線であり、行アドレス選択線は、行アドレス選択信号 (Ay, 1 y n) を伝達する配線である。さらに、ロウデコーダ 18 は、CK 線、REB 線、WEB 線及びCEB 線から選択された複数の配線に接続する。ロウデコーダ 18 に接続する配線は、遅延手段 13 の入力ノードの接続と同様に、プリチャージ動作を行うタイミングと CK との関係と、CEB 信号の必要の有無に依存する。

40

本実施の形態では、行アドレス選択線 Ay はインバータ 20 の入力ノードに接続する。CK 線、REB 線、WEB 線及びCEB 線から選択された複数の配線は、論理回路 21 の入力ノードに接続する。インバータ 27 の出力ノードはワード線 Wy に接続する。

#### 【0022】

50

本発明は、上記に挙げたデータ保持手段11、プリチャージ手段12及び遅延手段13の3つの基幹の要素以外に、複数の画素を有する表示手段(図1、2には示さない)を有していてもよい。表示手段を有することにより、高機能化と高付加価値化が実現した半導体装置を提供することができる。

【0023】

また、図示しないが、本発明は、2値のデータを判定する際に用いるセンスアンプや、読み出しと書き込みのどちらの動作を行うかを制御する読み出し/書き込み回路、データを外部に出力する出力回路等の必要な回路を適宜有していてもよい。

【0024】

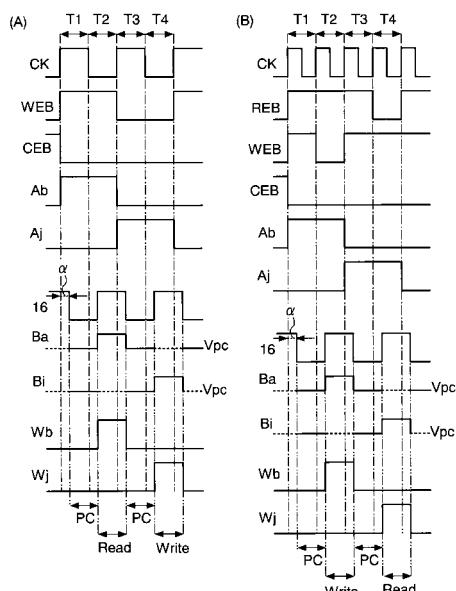

上記構成を有する半導体装置の動作について、図3(A)(B)のタイミングチャートを用いて説明する。 10

まず、CKと同期でプリチャージ動作を行う場合について、図3(A)を用いて説明する。ここでは、CKがHレベル、WEBがHレベル、又はCKがHレベル、WEBがLレベルのときにプリチャージ動作を行い、CKがLレベル、WEBがHレベルのときに読み出し動作を行い、CKがLレベル、WEBがLレベルのときに書き込み動作を行う形態について説明する。

なお、図3(A)(B)のタイミングチャート中の配線の電位を示す波形における点線は、浮遊状態(不定状態、又はフローティング状態ともいう)を示す。また、CEBは動作の制御には依存せず、何らかの動作を行う際には、常時Hレベル又はLレベルであり、ここでは、CEBは常時Lレベルとする。 20

【0025】

期間T1において、CKはHレベル、WEBはHレベル、CEBはLレベルであり、b行目(1 b n、bは自然数)のアドレスを選択するアドレス選択信号AbはHレベルである。期間T1が開始してから遅延期間が経過すると、遅延手段13からLレベルのプリチャージ信号がプリチャージ信号線16に伝達され、前記プリチャージ信号線16はLレベルの信号と同電位となる。そうすると、プリチャージ信号線16を介して、Hレベル又はLレベルの信号が入力された全てのアナログスイッチSW1～SWmは導通状態となり、全てのビット線B1～Bmがプリチャージ電位Vpcにプリチャージされる。

【0026】

期間T2において、CKはLレベル、WEBはHレベル、CEBはLレベル、AbはHレベルである。期間T2が開始してから遅延期間が経過すると、カラムデコーダ17がa列目(1 a m、aは自然数)のビット線Baを選択する。同時に、b行目のワード線WbにHレベルの信号が伝達されて、前記ワード線Wbは選択状態になる。そうすると、(a, b)の座標に配置されたメモリセル14から、ビット線BaのHレベルのデータの読み出しが行われる。 30

【0027】

期間T3において、CKはHレベル、WEBはLレベル、CEBはLレベル、j行目(1 j n、jは自然数)のアドレスを選択するアドレス選択信号AjはHレベルである。期間T3が開始してから遅延期間が経過すると、Lレベルのプリチャージ信号がプリチャージ信号線16に伝達され、全てのアナログスイッチSW1～SWmは全て導通状態となり、全てのビット線B1～Bmがプリチャージ電位Vpcにプリチャージされる。 40

【0028】

期間T4において、CKはLレベル、WEBはLレベル、CEBはLレベル、AjはHレベルである。期間T4が開始してから遅延期間が経過すると、カラムデコーダ17がi列目(1 i m、iは自然数)のビット線Biを選択状態にし、Hレベルの信号が伝達される。同時に、j行目のワード線WjにHレベルの信号が伝達されて、前記ワード線Wjは選択状態となる。そうすると、(i, j)の座標に配置されたメモリセル14に、Hレベルのデータが書き込まれる。

【0029】

続いて、CKと非同期でプリチャージ動作を行う形態について、図3(B)を用いて説明 50

する。この場合、R E B が H レベル、W E B が H レベルのときにプリチャージ動作を行い、R E B が H レベル、W E B が L レベルのときに書き込み動作を行い、R E B が L レベル、W E B が H レベルのときに読み出し動作を行う。また、C E B は常時 L レベルとする。

#### 【 0 0 3 0 】

期間 T 1 において、R E B は H レベル、W E B は H レベル、A b は H レベルである。期間 T 1 が開始してから遅延期間 が経過すると、L レベルのプリチャージ信号がプリチャージ信号線 1 6 に伝達され、全てのアナログスイッチ S W 1 ~ S W m は導通状態となり、全てのビット線 B 1 ~ B m がプリチャージ電位 V p c にプリチャージされる。

#### 【 0 0 3 1 】

期間 T 2 において、R E B は H レベル、W E B は L レベル、A b は H レベルである。期間 T 2 が開始してから、遅延期間 が経過すると、ビット線 B a とワード線 W b が選択状態になる。そうすると、( a 、 b ) の座標に配置されたメモリセル 1 4 に対して、ビット線 B a の H レベルのデータの書き込みが行われる。

10

#### 【 0 0 3 2 】

期間 T 3 において、R E B は H レベル、W E B は H レベル、A j は H レベルである。期間 T 3 が開始してから遅延期間 が経過すると、L レベルのプリチャージ信号がプリチャージ信号線 1 6 に伝達され、全てのアナログスイッチ S W 1 ~ S W m は導通状態となり、全てのビット線 B 1 ~ B m がプリチャージ電位 V p c にプリチャージされる。

#### 【 0 0 3 3 】

期間 T 4 において、R E B は L レベル、W E B は H レベル、A j は H レベルである。期間 T 4 が開始してから遅延期間 が経過すると、ビット線 B i とワード線 W j が選択状態になる。そうすると、( i 、 j ) の座標に配置されたメモリセル 1 4 から、ビット線 B i の H レベルのデータの読み出しが行われる。

20

#### 【 0 0 3 4 】

このように、プリチャージ期間 T 1 、 T 3 、書き込み期間及び読み出し期間 T 2 、 T 4 の各々において、上記のように動作することで、プリチャージ動作、書き込み動作及び読み出し動作のそれぞれの動作を行う。

#### 【 0 0 3 5 】

上記構成を有する本発明は、スイッチ S W x の導通又は非導通を制御するプリチャージ信号の出力を遅延させることができる。そのため、ワード線 W y の選択から非選択への切り替わりが遅延しても、プリチャージ信号の出力も遅延するため、前記ワード線 W y が選択された状態で、プリチャージ動作を行うことがない。従って、上記構成を有する本発明は、誤作動を防止し、データの読み出しと書き込みを正確に行うことができる。

30

( 実施の形態 2 )

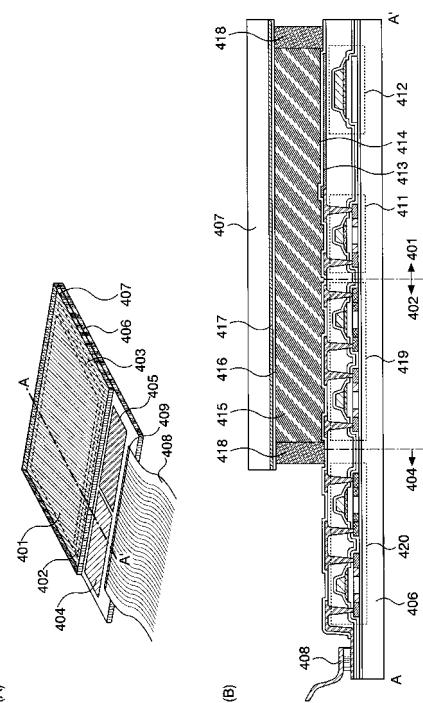

#### 【 0 0 3 6 】

本発明の半導体装置の一形態であるパネルについて図面を用いて説明する。パネルは、基板 4 0 6 上に、複数の画素を有する画素部 4 0 1 と、複数のトランジスタを含む駆動回路 4 0 2 、 4 0 3 を有する(図 4 ( A ) 参照)。駆動回路 4 0 2 、 4 0 3 は、基板 4 0 6 に一体形成せずに、外付けにしたり、COG ( C h i p O n G l a s s ) 方式等により基板 4 0 6 上に実装したりしてもよい。従って、表示手段とは、画素部 4 0 1 のみ、又は画素部 4 0 1 と駆動回路 4 0 2 、 4 0 3 に相当する。また、パネルは、基板 4 0 6 上に、VRAM ( 画面表示専用メモリ ) 、 RAM 又は ROM に相当する記憶手段 4 0 4 と、CPU ( C e n t r a l P r o c e s s i n g U n i t 、中央処理ユニット ) 4 0 5 を有する。さらに、パネルは、基板 4 0 6 上に、駆動回路 4 0 2 、 4 0 3 、記憶手段 4 0 4 及び CPU 4 0 5 を制御する信号を供給する入力端子 4 0 9 を有する。入力端子 4 0 9 には、接続ファイルム 4 0 8 を介して、ビデオ信号等の信号や電位が供給される。また、パネルは、画素部 4 0 1 と駆動回路 4 0 2 、 4 0 3 を囲むシール材(図 4 ( A ) には示さない)を有し、基板 4 0 6 と基板 4 0 7 は、前記シール材により貼り付けられている。なお、図示するパネルでは、対向基板 4 0 7 は、画素部 4 0 1 と駆動回路 4 0 2 、 4 0 3 上のみに設けているが、全面に設けてもよい。但し、CPU 4 0 5 は、発熱する恐れがあるため、前記 CPU 40

40

50

U 4 0 5 に接するように、放熱板を設けるとよい。

【 0 0 3 7 】

図 4 ( B ) はパネルの A - A ' における断面図を示し、画素部 4 0 1 は TFT 4 1 1 と容量素子 4 1 2 を有し、駆動回路 4 0 2 は TFT からなる素子群 4 1 9 を有し、記憶手段 4 0 4 は TFT からなる素子群 4 2 0 を有する。基板 4 0 6 と基板 4 0 7 の間には、画素電極 4 1 3 、配向膜 4 1 4 、液晶層 4 1 5 、配向膜 4 1 6 、対向電極 4 1 7 を有する。基板 4 0 6 と対向基板 4 0 7 には偏光板が貼り付けられている。

【 0 0 3 8 】

基板 4 0 6 上の回路を構成する素子は、非晶質半導体に比べて移動度等の特性が良好な多結晶半導体（ポリシリコン）により形成されることが好ましく、そうすると、モノリシック化が実現される。このように、画素部と駆動回路以外に、記憶手段や CPU 等の機能回路の一体形成を実現したパネルはシステムオンパネルと呼ばれ、システムの多機能化を図ることができる。上記構成を有するパネルは、接続する外部 IC の個数が減少するため、小型・軽量・薄型が実現され、最近普及が急速に進んだ携帯端末に適用すると大変有効である。なお、本形態では、表示素子として液晶素子を用いたパネルを示したが、本発明はこれに制約されない。表示素子として、発光素子等の他の表示素子を用いたパネルに適用してもよい。

10

【 0 0 3 9 】

上記のパネルにおいて、実施の形態 1 において説明した半導体装置の構成は、記憶手段 4 0 4 の構成に適用される。つまり、記憶手段 4 0 4 は、データ保持手段 1 1 、プリチャージ手段 1 2 及び遅延手段 1 3 を有することを特徴とする。また、カラムデコーダ 1 7 とロウデコーダ 1 8 を有するアドレス選択手段も有することを特徴とする（図 5 参照）。上記特徴により、本発明のパネルは、誤作動を防止し、データの読み出しと書き込みを正確に行うことができるという効果を奏する。

20

【 0 0 4 0 】

次に、画素部 4 0 1 及び駆動回路 4 0 2 、 4 0 3 を含む表示手段 4 2 1 、記憶手段 4 0 4 、 CPU 4 0 5 の相互関係とその一連の動作について以下に簡単に説明する。

CPU 4 0 5 は、制御部 4 2 2 と演算部 4 2 3 とを含む。

30

記憶手段 4 0 4 からデータの読み出し又は書き込みを行う場合、まず、 CPU 4 0 5 が具備する制御部 4 2 2 が含むプログラムカウンタから、データが格納されたメモリセル又はデータを格納するメモリセルのアドレスの情報は、記憶手段 4 0 4 が含むアドレス選択手段であるロウデコーダ 1 8 と遅延手段 1 3 に供給される。

指定されたアドレスから読み出された情報は、カラムデコーダ 1 7 から、制御部 4 2 2 が含む命令レジスタに供給される。また、指定されたアドレスに書き込む情報は演算部 4 2 3 が含むレジスタから供給される。

表示手段 4 2 1 が含む画素部 4 0 1 における画像の表示は、 CPU 4 0 5 から駆動回路 4 0 2 、 4 0 3 に供給される信号に従って行われる。なお、映像信号が記憶手段 4 0 4 に記憶されている場合、記憶手段 4 0 4 から CPU 4 0 5 を介して信号線側の駆動回路 4 0 2 に供給される。

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

40

（実施の形態 3 ）

【 0 0 4 1 】

本発明の ID タグ（RFID タグ、 IC タグ、電子タグ、 IC チップ、無線チップ、無線プロセッサ、無線メモリともいう）の構成について説明する。本発明の ID タグ 3 0 6 は、記憶手段 3 0 1 、制御手段 3 0 2 及び電源発生手段 3 0 3 を含む IC チップ 3 0 4 と、アンテナ 3 0 5 （送受信手段ともいう）とを有する（図 6 ( A ) 参照）。

【 0 0 4 2 】

上記のパネルにおいて、実施の形態 1 において上述した半導体装置の構成は、記憶手段 3 0 1 の構成に適用される。つまり、記憶手段 3 0 1 は、データ保持手段 1 1 、プリチャージ手段 1 2 及び遅延手段 1 3 を有することを特徴とする。また、カラムデコーダ 1 7 とロ

50

ウデコーダ18を有するアドレス選択手段も有することを特徴とする(図6(B)参照)。上記特徴により、本発明のIDタグは、誤作動を防止し、データの読み出しと書き込みを正確に行うことができるという効果を奏する。なお、記憶手段301は、データ保持手段が含む記憶素子の構成に従って、RAM、ROM等になりうるが、IDタグに用いる記憶手段301としては、ROMを用いるとよい。

#### 【0043】

制御手段302はロジック回路から構成される。制御手段302(制御回路ともいう)は、CPU(中央処理回路)等に相当する。電源発生手段303は、非接触型の場合、コイル状に巻かれたアンテナ305の電磁誘導作用、相互誘導作用又は静電気による誘導作用が採用される。従って、この場合には、電源発生手段303(電源発生回路ともいう)は、アンテナ305と動作する。アンテナ305は、その巻き数を制御することにより、受信する周波数の高さを選ぶことができる。

10

#### 【0044】

アンテナ305をICチップ304と同一の基板上に形成する方法(図6(C)(E)参照)、又はアンテナ305を含む基板313上に、ICチップ304を実装する方法(図6(D)(F)参照)のどちらかの方法を採用する。前者の方法を採用する場合、基板308上にTFT群309とアンテナ305を設ける(図6(E)参照)。一方、後者の方法を採用する場合、アンテナ305を含む基板313上に、導電層311と絶縁層312を介して、TFT群309を含む基板310を実装する(図6(F)参照)。なお、図6(E)(F)に示すTFT群309は、記憶手段301、制御手段302及び電源発生手段303のいずれかの手段の構成要素である。

20

#### 【0045】

次に、IDタグ306を用いた通信手順について、以下に簡単に説明する(図6(A)参照)。まず、IDタグ306が含むアンテナ305がリーダライタ307からの電波を受信する。そうすると、電源発生手段303において、共振作用により起電力が発生する。そして、IDタグ306が含む記憶手段301と制御手段302が起動して、制御手段302により、記憶手段301内のデータが信号化される。次に、IDタグ306が含むアンテナ305から信号を発信する。そうすると、IDタグ306は、リーダライタ307が含むアンテナにより送信された信号を受信する。受信した信号は、リーダライタ307が含むコントローラ(図6(A)には示さない)を介して、データ処理装置(図6(A)には示さない)に送信され、ソフトウェアを用いてデータ処理が行われる。上記通信手順は、コイル型のアンテナを用い、IDタグのコイルとリーダライタのコイル間に誘導されて発生する磁束を利用した電磁誘導方式を用いた場合である。しかしながら、本発明は上記方式に制約されず、マイクロ波帯の電波を使った電波方式を用いてもよい。

30

#### 【0046】

IDタグ306は、非接触で通信を行う点、複数読み取りが可能である点、データの書き込みが可能である点、様々な形状に加工可能である点、選択する周波数によっては、指向性が広く、認識範囲が広い点等の利点を有する。IDタグ306は、非接触による無線通信で、人や物の個々の情報を識別可能なICタグ、ラベル加工を施して目標物への貼り付けを可能としたラベル、イベントやアミューズメント向けのリストバンド等に適用することができる。また、IDタグ306を樹脂材料により成型加工してもよいし、無線通信を阻害する金属に直接固定してもよい。さらに、IDタグ306は、入退室管理システムや精算システムといった、システムの運用に活用することができる。

40

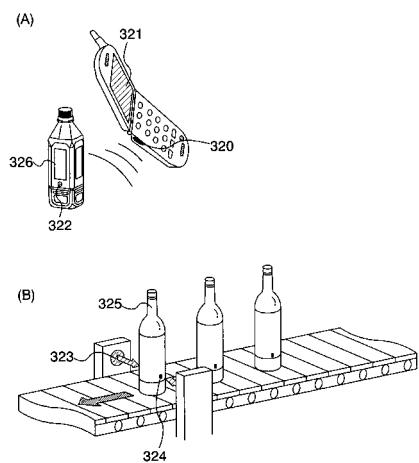

#### 【0047】

次に、IDタグ306を実際に使用する際の一形態について説明する。表示部321を含む携帯端末の側面には、リーダライタ320が設けられ、品物326の側面にはIDタグ322が設けられる(図7(A)参照)。IDタグ322にリーダライタ320をかざすと、表示部321に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品325をベルトコンベアにより搬送する際に、リーダライタ323と、前記商品325に設けられたIDタグ3

50

24を用いて、前記商品325の検品を行うことができる(図7(B)参照)。このように、システムにIDタグを活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。

【実施例1】

【0048】

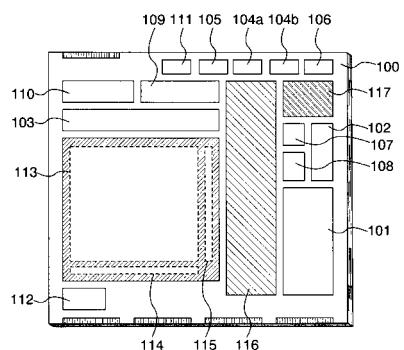

本発明の実施例について、図8を用いて説明する。本発明の半導体装置は、大別して、データ記憶ブロック、表示ブロック、画像処理ブロック、制御ブロックの4つのブロックを有し、全てのブロックは、基板100上に設けられる。

データ記憶ブロックは、プログラムROM(PROM)101、作業領域用RAM(WRAM)102、音声データ用プログラムROM(AudioROM)103、ラインバッファRAM104a、104b、インレンジRAM(INRAM)105、カラーパレットRAM(CRAM)106、メモリコントローラ107、デコーダ/レジスタ108、音声データ用プログラムROMコントローラ109、音声データ用DA変換回路/演算増幅器110、メモリ用参照電源発生回路(Vref電源)111及び階調電源112を有する。

表示ブロックは、画素部113と駆動回路114、115を有する。画像処理ブロックは、画像処理回路116を有する。制御ブロックは、CPU117を有する。

【0049】

上記のように、表示ブロックだけではなく、データ記憶ブロック、画像処理ブロック及び制御ブロックを有する半導体装置は、接続するICの個数を減らし、小型・薄型・軽量を実現する。また、表示ブロック、画像処理ブロック及び制御ブロックが互いに隣接している半導体装置は、データの流れに沿った配置となっており、正確な動作を実現する。本発明は、記憶ブロックを構成する各メモリの構成に適用される。本実施例は、上記の実施の形態と自由に組み合わせることができる。

【実施例2】

【0050】

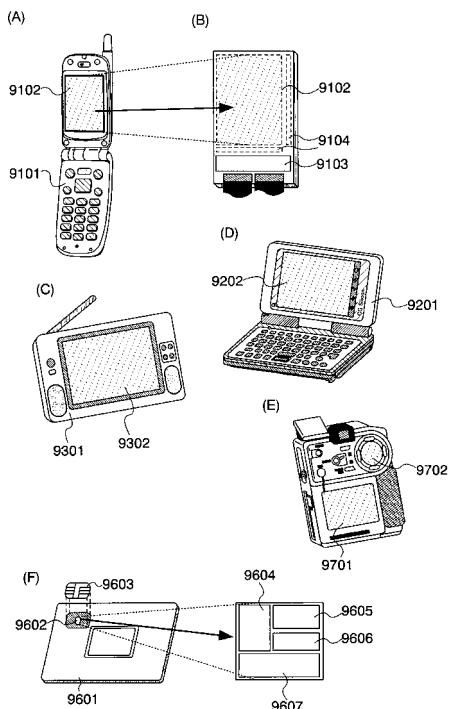

本発明が適用される電子機器の一例として、テレビ装置、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(携帯電話機)、PDA等の携帯情報端末、携帯型ゲーム機、モニター、パーソナルコンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。以下にはその具体例について説明する。

【0051】

図9(A)は携帯端末であり、本体9101、表示部9102等を含む。図9(C)は携帯型テレビ受像機であり、本体9301、表示部9302等を含む。図9(D)は、携帯情報端末であり、本体9201、表示部9202等を含む。図9(E)は、デジタルビデオカメラであり、表示部9701、9702等を含む。

【0052】

表示部を含むパネルは、図9(B)に示すように駆動回路9104、CPUや記憶手段等の機能回路9103を具備する。本発明は、機能回路9103が有する記憶手段の構成に適用される。駆動回路9104だけでなく、機能回路9103が一体形成されたパネルを有する電子機器は、接続する外部ICの個数を減らすことができるため、小型・薄型・軽量が実現する。また、表示部を構成する表示素子として、自発光型の発光素子を用いると、バックライトなどが必要ないため、液晶素子を用いる場合に比べて、薄型・小型・軽量が実現される。

【0053】

また、図9(F)は接触型ICカードであり、本体9601、ICチップ9602、モジュール端子9603を含む。ICチップ9602は、RAM9604、ROM9605、CPU9606及びRAM9607等を含む。本発明は、ICチップ9602が有するRAM9604、9607とROM9605の記憶手段の構成に適用される。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0054】

- 【図1】本発明の実施の形態1を説明する図。

【図2】本発明の実施の形態1を説明する図。

【図3】本発明の実施の形態1を説明する図。

【図4】本発明の実施の形態2を説明する図。

【図5】本発明の実施の形態2を説明する図。

【図6】本発明の実施の形態3を説明する図。

【図7】本発明の実施の形態3を説明する図。

【図8】本発明の実施例1を説明する図。

【図9】本発明の実施例2を説明する図。

10

## 【符号の説明】

## 【0055】

- 1 1 データ保持手段(メモリセルアレイ)、1 2 プリチャージ手段

1 3 遅延手段、1 4 メモリセル

1 5 プリチャージ電位線、1 6 プリチャージ信号線

1 7 カラムデコーダ、1 8 ロウデコーダ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

---

フロントページの続き

合議体

審判長 藤原 敬士

審判官 西脇 博志

審判官 近藤 幸浩

(56)参考文献 特開平5 - 274886 (JP, A)

特開2003 - 208790 (JP, A)

特開平8 - 180682 (JP, A)

特開2001 - 148194 (JP, A)

特開2003 - 173683 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/06

G06K 19/07

G11C 11/409