(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6378552号

(P6378552)

(45) 発行日 平成30年8月22日(2018.8.22)

(24) 登録日 平成30年8月3日(2018.8.3)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652H |

| HO1L 29/12  | (2006.01) | HO1L 29/78 | 652T |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 301B |

| HO1L 29/739 | (2006.01) | HO1L 29/78 | 301H |

| HO1L 21/28  | (2006.01) | HO1L 29/78 | 301Q |

請求項の数 13 外国語出願 (全 22 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2014-129764 (P2014-129764) |

| (22) 出願日     | 平成26年6月25日 (2014.6.25)       |

| (65) 公開番号    | 特開2015-15464 (P2015-15464A)  |

| (43) 公開日     | 平成27年1月22日 (2015.1.22)       |

| 審査請求日        | 平成29年6月19日 (2017.6.19)       |

| (31) 優先権主張番号 | 13/934,053                   |

| (32) 優先日     | 平成25年7月2日 (2013.7.2)         |

| (33) 優先権主張国  | 米国 (US)                      |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 390041542<br>ゼネラル・エレクトリック・カンパニー<br>アメリカ合衆国、ニューヨーク州 123<br>45、スケネクタディ、リバーロード、1<br>番 |

| (74) 代理人  | 100137545<br>弁理士 荒川 聰志                                                             |

| (74) 代理人  | 100105588<br>弁理士 小倉 博                                                              |

| (74) 代理人  | 100129779<br>弁理士 黒川 俊久                                                             |

| (74) 代理人  | 100113974<br>弁理士 田中 拓人                                                             |

最終頁に続く

(54) 【発明の名称】チャネル周縁の広い金属酸化物半導体(MOS)素子及び製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体素子であって、(0001)配向SiC基板上に配置された炭化ケイ素(SiC)ドリフト層を備え、前記SiCドリフト層が、前記半導体素子のチャネル長に対して平行に配向された複数の反復トレンチ形状を含む非平面の表面を含み、前記チャネルが、前記SiCドリフト層の特定の結晶面に配置され、

前記複数の反復トレンチ形状の間の各領域は、前記SiCドリフト層の他の部分のドーパント濃度よりも高いドーパント濃度を有し、

前記反復トレンチ形状の間の領域の前記ドーパント濃度は、ほぼ、前記SiCドリフト層の臨界電界の2倍を前記反復形状の周期幅で除した値以下である、

半導体素子。

10

## 【請求項2】

前記SiCドリフト層の前記非平面の表面の少なくとも一部に一致して配置された非平面ウェル領域を、さらに備えた、請求項1に記載の素子。

## 【請求項3】

前記反復トレンチ形状の深さは、前記SiCドリフト層の厚さの約10%以下である、

請求項2に記載の素子。

## 【請求項4】

少なくとも、前記SiCドリフト層の一部及び前記ウェル領域の一部に一致して配置された非平面誘電層と、

20

前記非平面誘電層の少なくとも一部に一致して配置された非平面ゲートと、をさらに備えた、請求項 2 または 3 に記載の素子。

【請求項 5】

前記反復トレンチ形状は、三角形のピーク、バレーおよび傾斜側壁を含む三角形状のトレンチを有する三角形の形状を含む、請求項 1 から 4 のいずれかに記載の素子。

【請求項 6】

a を前記の反復する三角形の形状の辺の長さとし、b を前記の反復する三角形の形状の底辺の長さ又は前記の反復する三角形の形状のピッチとした場合、前記の反復する三角形の形状により、約  $2a / b$  に等しく前記チャネルの幅が広がる、請求項 5 に記載の素子。

【請求項 7】

前記結晶面は、前記 SiC ドリフト層の

【数 1】

$\{0\bar{3}3\bar{8}\}$

面である、請求項 5 または 6 に記載の素子。

【請求項 8】

前記反復トレンチ形状は、矩形ピーク形状を含む、請求項 1 から 4 のいずれかに記載の素子。

【請求項 9】

a を前記の反復する矩形形状の高さとし、b を前記の反復する矩形形状のピッチとした場合、前記の反復する矩形形状により、約  $(2a + b) / b$  に等しく前記チャネルの幅が広がる、請求項 8 に記載の素子。

【請求項 10】

前記結晶面は、前記 SiC ドリフト層の

【数 2】

$\{11\bar{2}0\}$

面である、請求項 8 または 9 に記載の素子。

【請求項 11】

前記結晶面は、前記 SiC ドリフト層の

【数 3】

$\{1\bar{1}00\}$

面である、請求項 8 または 9 記載の素子。

【請求項 12】

前記半導体素子は、三角形状、矩形状又はハニカムセル状設計を有するセル状半導体素子である、請求項 1 から 11 のいずれかに記載の素子。

【請求項 13】

前記半導体素子は、ハニカムセル状設計を有するセル状半導体素子であり、前記チャネルは、前記 SiC ドリフト層の

【数 4】

$\{11\bar{2}0\}$

面に沿って配列された、請求項 12 に記載の素子。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書で開示する主題は、炭化ケイ素 (SiC) 電力素子 (例えば、MOSFET、IGBT 等) 等の金属酸化物半導体 (MOS) 素子に関する。

【背景技術】

10

20

30

40

50

## 【0002】

本節は、本開示の様々な側面に関することがある技術の様々な側面について、読者に紹介することを意図しており、本開示は、以下に説明及び／又は特許請求される。ここでの検討が、本開示の様々な側面をよりよく理解しやすくなるように、背景技術を読者に提供するのに役立つものと信じる。したがって、各記述は、このような観点で読まれるべきであり、従来技術を認めるものとして読まれるべきではないことが、理解されるべきである。

## 【0003】

パワーエレクトロニクスシステムは、電力のある形態から負荷による消費形態へと変換するために、現代の電気システム全体を通じて広く用いられている。パワーエレクトロニクスシステムの多くは、この電力変換法にて、サイリスタ、ダイオード、並びに様々な種類のトランジスタ（例えば、金属酸化物半導体電界効果トランジスタ（MOSFET）、接合ゲート電界効果トランジスタ（JFET）、絶縁ゲートバイポーラトランジスタ（IGBT）、及び他の適切なトランジスタ）等、様々な半導体素子及び要素を利用している。

10

## 【0004】

特に、高電圧及び／又は高電流の用途では、炭化ケイ素（SiC）、窒化アルミニウム（AlN）、窒化ガリウム（GaN）等の広バンドギャップ半導体を利用した素子は、対応するシリコン（Si）素子よりも高温で動作し、ON抵抗が低く、チップサイズが小さいという点で、多くの利点を提供することができる。このように、広バンドギャップ半導体素子は、例えば、配電システム（例えば、配電網において）、発電システム（例えば、太陽及び風力変換機）並びに消費財（例えば、電気自動車、機器、電源等）等の電気変換の用途に、複数の利点を提供している。しかしながら、SiC及びSi材料システム間の差異により、例えば、Si素子では良好に作用する材料処理及び構造の特徴（例えば、素子設計及び／又は製造方法）が、対応するSiC半導体素子には不適当であったり、その逆であったりすることがある。したがって、広バンドギャップ半導体材料には、それらの利点の他に、素子の設計及び製造を通じて問題も生じている。

20

## 【先行技術文献】

## 【特許文献】

## 【0005】

30

## 【特許文献1】米国特許第8211770号明細書

## 【発明の概要】

## 【0006】

当初から特許請求されている主題の範囲と同等の特定の実施形態の概要を以下に述べる。これらの実施形態は、特許請求された発明の範囲を限定することを意図しているわけではなく、むしろ、これらの実施形態は、本発明の形態のとりうる形態の簡単な概要を提供することのみを意図している。実際に、本開示は、以下に述べる実施形態と同様であるか又は異なった様々な形態を包含しうる。

## 【0007】

一実施形態では、半導体素子は、（0001）配向SiC基板上に配置された炭化ケイ素（SiC）ドリフト層を備える。SiCドリフト層は、半導体素子のチャンネル領域に対して平行に配向された複数の反復形状を含む非平面の表面を含む。さらに、チャネル領域は、SiCドリフト層の特定の結晶面に配置されている。

40

## 【0008】

他の実施形態では、半導体素子の製造方法は、炭化ケイ素（SiC）ドリフト層の上面に、SiCドリフト層の

## 【0009】

## 【数1】

{0338}

50

【0010】

面、

【0011】

【数2】

{11 $\bar{2}$ 0}

【0012】

面又は

【0013】

【数3】

{11 $\bar{0}$ 0}

【0014】

面に沿って配向した側壁を有する複数の反復形状を含む非平面の表面を形成するステップを含む。本方法は、SiCドリフト層の非平面の表面の少なくとも一部から、非平面ウェル領域を形成するステップと、非平面ウェル領域の少なくとも一部から、非平面n+又はp+領域を形成するステップとを含む。

【0015】

他の実施形態では、半導体素子は、(0001)配向SiC基板上に配置された炭化ケイ素(SiC)ドリフト層を備える。SiCドリフト層は、SiCドリフト層の結晶面内に、半導体素子のチャネル領域を配置するように構成された側壁を有する、複数の反復する三角形状又は矩形形状がある非平面の表面を有する。結晶面はSiCドリフト層の

【0016】

【数4】

{0 $\bar{3}$ 3 $\bar{8}$ }

【0017】

面、

【0018】

【数5】

{11 $\bar{2}$ 0}

【0019】

面又は

【0020】

【数6】

{11 $\bar{0}$ 0}

【0021】

である。さらに、反復する三角形状又は矩形形状は、SiCドリフト層の他の部分のドーパント濃度よりも高いドーパント濃度を有する。

【0022】

図面全体を通じて同様の符号が同様の部分を表す添付の図面を参照して以下の詳細な説明を読むことで、本発明のこれら及び他の特徴、態様、及び利点がより良く理解されるであろう。

【図面の簡単な説明】

【0023】

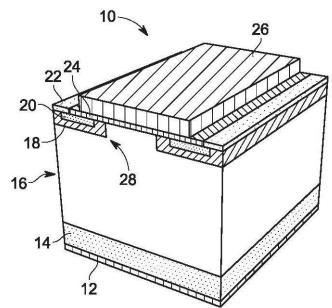

【図1】模式的な平面MOSFET素子の概略図である。

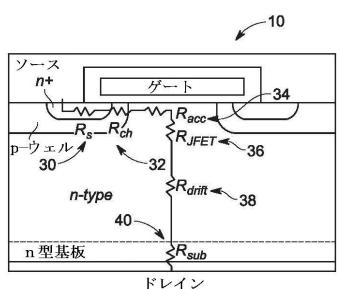

【図2】模式的なMOSFET素子における様々な領域の抵抗を示す概略図である。

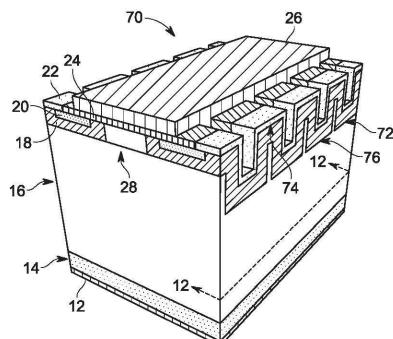

【図3】本手法の一実施形態による、三角波素子断面形状を有する垂直非平面MOSFE

10

20

30

40

50

T素子の模式図である。

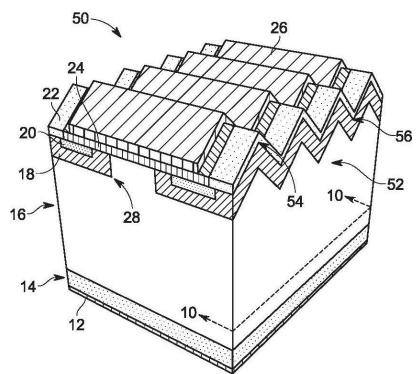

【図4】本手法の一実施形態による、三角波素子断面形状を有する非平面ラテラルMOSFET素子の模式図である。

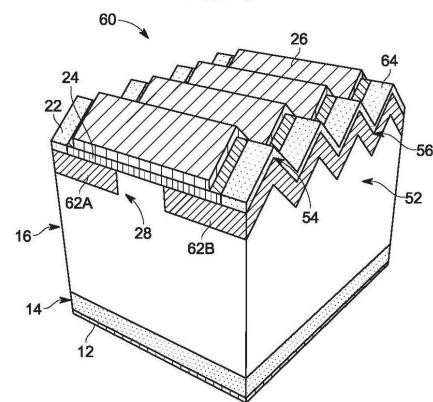

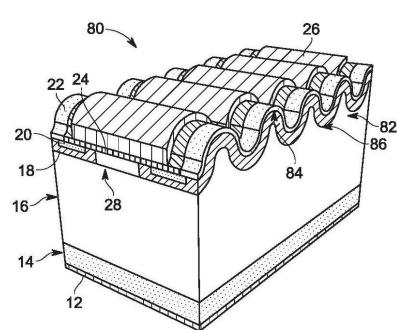

【図5】本手法の一実施形態による、矩形波素子断面形状を有する非平面MOSFET素子の模式図である。

【図6】本手法の一実施形態による、正弦波素子断面形状を有する非平面MOSFET素子の模式図である。

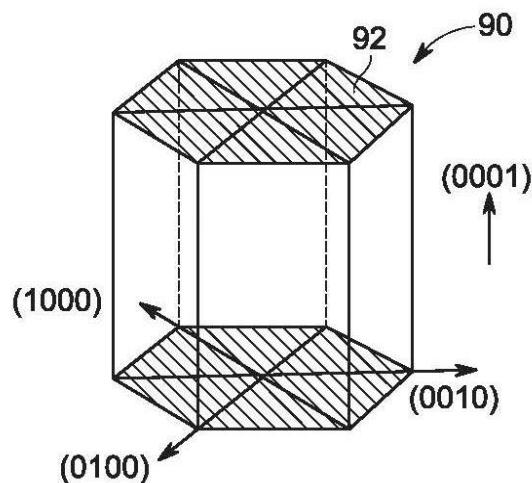

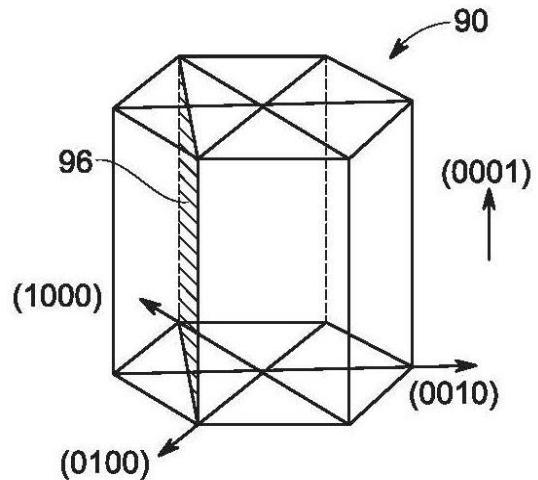

【図7A】4H-SiC又は6-H-SiC六方晶SiC結晶の(0001)結晶面を示す図である。

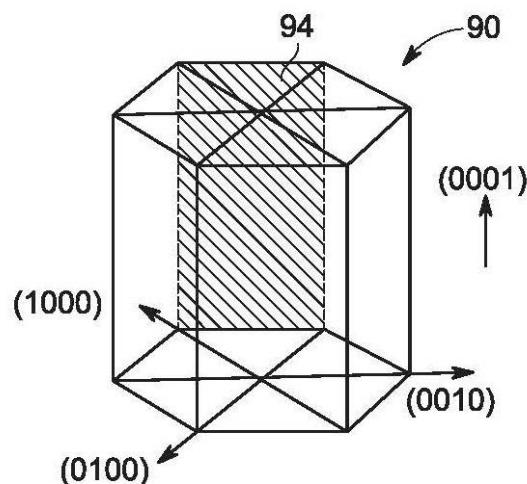

【図7B】4H-SiC又は6-H-SiC六方晶SiC結晶の垂直

【0024】

【数7】

(1100)

【0025】

結晶面を示す図である。

【図7C】4H-SiC又は6-H-SiC六方晶SiC結晶の垂直

【0026】

【数8】

(1120)

【0027】

結晶面を示す図である。

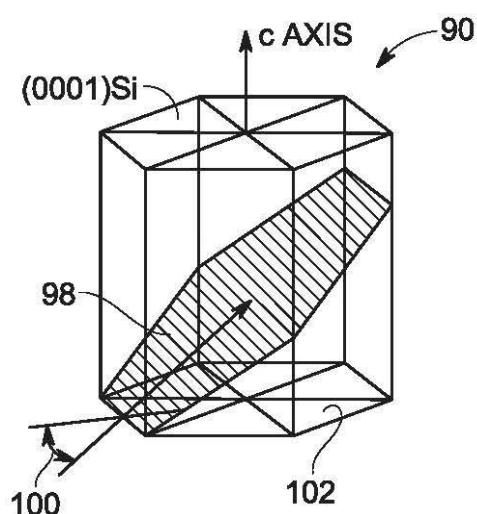

【図7D】4H-SiC又は6-H-SiC六方晶SiC結晶の

【0028】

【数9】

(0338)

【0029】

結晶面を示す図である。

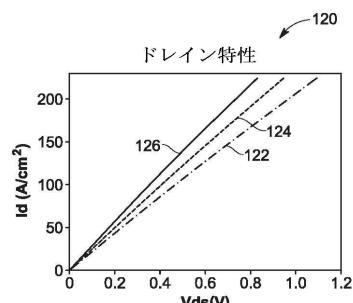

【図8】平面SiC MOSFET素子、非平面SiC MOSFET素子の一実施形態、及び特定の結晶面に沿って配置されたチャネルを有する非平面SiC MOSFET素子の一実施形態のドレイン特性を示すグラフである。

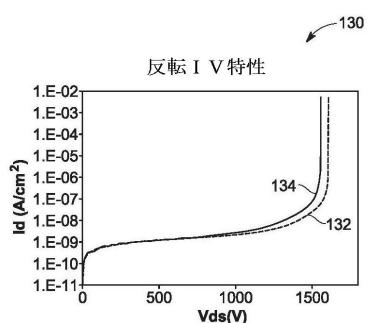

【図9】平面MOSFET素子及び非平面MOSFET素子の一実施形態の逆電流-電圧(I-V)特性を示すグラフである。

【図10】本手法の一実施形態による、図3のMOSFET素子の断面図である。

【図11】トレンチ形状(例えば、p/n-ウェル下のドリフト層でのドーピングに比べて)間で、トレンチ形状がより深く、ドリフト領域でのドーピングがより強い、図3のMOSFET素子の一実施形態の断面図である。

【図12】本手法の一実施形態による、図5のMOSFET素子の断面図である。

【図13】トレンチ形状(例えば、p/n-ウェル下のドリフト層でのドーピングに比べて)間で、トレンチ形状がより深く、ドリフト領域でのドーピングがより強い、図5のMOSFET素子の一実施形態の断面図である。

【図14】本手法の一実施形態による、ハニカムセル状SiC素子設計を示す図である。

【発明を実施するための形態】

【0030】

ある実施形態又は具体的な複数の実施形態について、以下に説明する。これらの実施形態を簡潔に説明することに伴い、現実の実装例のあらゆる特徴を本明細書に記述しているわけではない。あらゆる技術又は設計プロジェクト同様、現実の実装例等の開発形態において、システム関連及びビジネス関連の制約への対応等、設計者の具体的目標を達成する

10

20

30

40

50

ために、多数の実装独自の決定がなされる必要があり、この制約は実装毎に様々であることが理解されるべきである。さらに、このような開発の取り組みは、複雑であって時間を要することがあるが、本開示の利点を享受する当業者が設計、作製及び製造を日常的に引き受けるわけではないことが、理解されるべきである。

#### 【0031】

本開示の様々な実施形態の要素について述べる場合、要素が単一であっても、1つ又は複数の要素を意味することを意図している。「備える」、「含む」及び「有する」は、非排他的であり、列挙された要素以外にも他の要素がありうることを意味している。さらに、本開示の「1つの実施形態」又は「一実施形態」と言及するとき、既述の特徴も組み込んだ追加の実施形態の存在を排除することを意図しているわけではないことが、理解されるべきである。

10

#### 【0032】

現代のパワーエレクトロニクスの本質的な構成要素の1つは、電界効果トランジスタ(MOSFET)素子である。例えば、図1に、平面n-チャネル電界効果トランジスタの活性セルを示す。すなわち、このトランジスタは、二重拡散金属酸化物半導体電界効果トランジスタ(DMOSFET)であり、以後、MOSFET素子10とする。MOSFET素子10の特定の要素及び以下に述べる他の素子を明確に示すために、特定の公知の設計要素(例えば、上面金属化、不活性化、端部終端等)を省略していることを理解されたい。図1に示すMOSFET素子10は、n型基板層14の下方、素子の底面に配置されたドレイン接点12を含む。基板層14上には、n型ドリフト層16が配置されている。MOSFET素子10の表面近傍には、p-ウェル18(例えば、ウェル領域18)及びn+領域20が、ソース接点22下に配置されている。さらに、誘電層24が、ゲート26をn+領域20及びp-ウェル18から絶縁している。動作中、適切なゲート電圧(例えば、MOSFET素子10閾値電圧以上)により、反転層がチャネル領域28内に形成されうる。チャネル領域28により、ソース接点22及びドレイン接点12間に電流が流れうる。チャネル領域28は、一般に、MOSFET素子では、p-ウェル領域18とゲート誘電体24との間に界面により規定可能であることが、理解されるべきである。したがって、チャネル領域28の幅又は周縁は、以下にさらに説明するように、MOSFET素子の表面領域に比例しうる。

20

#### 【0033】

30

図2に示すように、MOSFET素子10の様々な領域の各々は、関連抵抗を有することがあり、MOSFET素子10の全抵抗(例えば、オン抵抗 $R_{ds(on)}$ )は、これら各抵抗の合計として表現可能である。例えば、図2に示すように、MOSFET素子10のオン抵抗 $R_{ds(on)}$ は、抵抗 $R_s$ 30(例えば、n+領域20の抵抗及びソース接点22の抵抗)、抵抗 $R_{ch}$ 32(例えば、ウェル領域18の反転チャネル抵抗)、抵抗 $R_{ac}$ 34(例えば、ゲート酸化物24と、ウェル領域18間に配置されたドリフト層16の一部との間の蓄積層の抵抗)、抵抗 $R_{JFET}$ 36(例えば、ウェル領域18間のネック領域の抵抗)、抵抗 $R_{drift}$ 38(例えば、ドリフト層16の抵抗)、及び抵抗 $R_{sub}$ 40(例えば、基板層14の抵抗)の合計として近似できる。

#### 【0034】

40

MOSFET伝導損失を低減するため、MOSFETの1つ又は複数の要素の抵抗(例えば、 $R_{ds(on)}$ )を最小化することが望ましい。MOSFETのチャネル抵抗がMOSFETの全抵抗の主要部分であり、及び/又は、MOSFETのチャネル移動度が低いと、MOSFET素子(例えば、図1のMOSFET10)のオン抵抗(例えば、 $R_{ds(on)}$ )が重要になり、素子性能に影響しうる。このように、素子のオン抵抗が低くなるように、MOSFET素子を設計することが望ましい。さらに、ある種のMOSFET素子(例えば、SiC MOSFET素子)は、一般に、同様のシリコンMOSFET素子よりも反転層キャリア移動度が低い(例えば、チャネル抵抗 $R_{ch}$ 32が高い)ことを理解されたい。したがって、MOSFETのチャネル要素の抵抗を最小化する(例えば、減少させる、制限する、又は下げる)ことにより、オン抵抗がより小さいMOSFET素子(

50

例えば、SiC MOSFET素子)を設計することが、特に望ましい。さらに、上述のように、SiC基板により、Si基板には実装が難しいか又は不適切な素子製造技術を、実現することができるようになる。

#### 【0035】

このように、ここでは、MOSゲート及び/又はMOS制御半導体素子(例えば、MOSFET、絶縁ゲートバイポーラトランジスタ(IGBT)、絶縁ベースMOS制御サイリスタ(IBMCT)、ベース抵抗MOS制御サイリスタ(BRT)等)のオン抵抗を低減する、多くの素子構造及び方法を開示している。以下に詳述するように、本実施形態により、表面領域が広くチャネル幅が広い(例えば、チャネル周縁が広い)非平面半導体素子の製造が可能になり、これにより、より低い抵抗の素子を製造することが可能となる。10 例えば、以下に述べるように、ここに開示した実施形態は、例えば、正弦波、三角波、矩形波、のこぎり波に類似の素子断面形状を提供する反復トレンチ形状を含む、半導体素子(例えば、SiC素子)の例を含む。開示した素子の実施形態により、素子毎(及びチップ毎)の有効表面領域が増大する。この素子により、チャネル抵抗が減少することに加えて、1つ又は複数の接点抵抗が減少し、半導体素子の接点領域を広げることにより、熱放散を向上させうる。さらに、以下に詳述するように、本手法は、チャネル抵抗をさらに低減し、及び/又は素子の全オン抵抗(例えば、 $R_{ds(on)}$ )を低減するために、矩形又はハニカム構造等のセル素子の設計(例えば、SiCセル素子設計)にも適用可能である。なお、以下に示す素子の実施形態は、SiC素子として提案されているが、これらは、例として提示されているに過ぎない。他の実施形態において、半導体素子は、本手法の効果を失うことなく、シリコン(Si)、ゲルマニウム(Ge)、窒化アルミニウム(AlN)、窒化ガリウム(GaN)、ガリウムヒ素(GaAs)、ダイヤモンド(C)、又は他の半導体材料で製造することができる。20

#### 【0036】

上記内容を考慮しつつ、図3は、非平面SiC n-チャネルDMOSFET素子50(以下、MOSFET素子50)の一実施形態の概略図である。図1のMOSFET素子10同様、図3のMOSFET素子50は、n型基板層14下方の素子の底面に配置されたドレイン接点12を含む。基板層14上方に、n型ドリフト層16(例えば、エピタキシャルSiC層)が配置されている。MOSFET素子50の表面近傍には、ウェル領域18(例えば、p-ウェル18)及びn+領域20が、ソース接点22の下方に配置されている。さらに、誘電層24が、ゲート26をn+領域20及びp-ウェル18から絶縁している。図示のMOSFET素子50及び後述の他のMOSFET素子は、特定のドーピング(例えば、p-ウェル18及びn+領域20)を有するものとして説明かつ記述されているものの、当業者により理解されるように、他の実施形態では、MOSFET素子の様々な層が、逆方式でドーピングされてもよい(例えば、n-ウェル及びp+領域を利用)。30

#### 【0037】

図1のMOSFET素子10では、平面上に素子が作製されているのに対し、図3に示すMOSFET素子50の表面形状52は、反復ピーク形状54及びトレンチ形状56が反復した三角波状に形成されている。したがって、ドリフト層16の表面、p-ウェル18、n+領域20、ソース接点22、ゲート誘電体24及びゲート26の各々は、この三角波形状を呈する(例えば、ピーク形状54及びトレンチ56形状の繰り返し)。さらに、MOSFET50のチャネル領域28(例えば、反復ピーク及びトレンチ形状54及び56と平行に配向)も同様に三角波形状を呈し、ピーク形状54及びトレンチ56形状により、チャネル領域28のチャネル幅が広がる(例えば、チャネル周縁が広がる)ことになる。上述の如く、このようにMOSFET素子50におけるチャネル領域28の幅が広がることにより、MOSFET素子50の1つ又は複数の個々の抵抗(例えば、チャネル抵抗及び/又はソースとn+領域18との間の接点抵抗)が低減しうるため、MOSFET素子50のオン抵抗(例えば、 $R_{ds(on)}$ )を低減することができる。40

#### 【0038】

10

20

30

40

50

同様に、図4は、非平面SiCラテラルMOSFET素子60(以下、LMOSFET素子60)の他の実施形態の概略図である。図3のMOSFET素子50同様、図4のn-チャネルLMOSFET素子60は、p型ドリフト層16を上に配したn又はp型基板層14を含む。LMOSFET素子60の表面近傍には、ソース接点22の下方に第1のn-ウェル62Aが配置されており、ドレイン接点64の下方に第2のn-ウェル62Bが配置されている。さらに、誘電層24が、ゲート26をn-ウェル62A及び62Bから絶縁している。図示したLMOSFET素子60の動作中、素子閾値電圧を超えるゲート電圧が印加されると、チャネル領域66(例えば、ドリフト層16とゲート酸化物24との間の界面に)に導電チャネル(例えば、反転層)が形成され、ソース接点22とドレイン接点64との間に横方向の電荷キャリアを流すことができる。

10

## 【0039】

図3のMOSFET素子50と同様、図4に示すLMOSFET素子60の表面形状52は、ピーク形状54及びトレンチ形状56が反復した三角波状を呈する。したがって、ドリフト層16の表面、n-ウェル62A及び62B、ソース接点22、ゲート誘電体24、ゲート26、並びにドレイン接点64の各々は、このような三角波形状(例えば、ピーク54とトレンチ56形状の繰り返し)を呈しうる。さらに、LMOSFET60のチャネル領域66(例えば、反復ピーク形状54及びトレンチ形状56と平行に配向)は、同様にこのような三角波形状を呈しうるので、チャネル領域66は、ピーク54及びトレンチ56形状により、チャネル幅(例えば、チャネル周縁が広がる)が広がる結果となる。上述のように、LMOSFET60のチャネル領域66の幅が広がると、LMOSFET素子60の1つ又は複数の個々の抵抗(例えば、チャネル抵抗及び/又はソース/ドレインとn+領域18との間の接点抵抗)が低減しうるので、LMOSFET素子60の全オノン抵抗が低減することになる。

20

## 【0040】

図5及び図6は、非平面形状のMOSFET素子の実施形態の概略図である。特に、図5に、矩形ピーク形状74及び矩形トレンチ形状76を繰り返す矩形波状の素子断面形状72のSiC DMOSFET素子70(以下、MOSFET素子70)を示す。図6に、曲線的なピーク形状84及び曲線的なトレンチ形状86を繰り返す正弦波状の素子断面形状82のSiC DMOSFET素子80(以下、MOSFET素子80)を示す。ここに開示する素子断面形状(例えば、素子断面形状52、72及び82)は、単に非平面断面の例として提示されているものであり、限定を意味しないことが理解されるであろう。図5及び図6にそれぞれ示すMOSFET素子70及び80には、図1のMOSFET素子10について上述したように、対応する多くの素子形状(例えば、ドレイン接点12、n型基板14、n型ドリフト層16、p-ウェル18、n+領域20、ソース接点22、誘電層24及びゲート26)があることを理解されたい。

30

## 【0041】

図5に示すMOSFET素子70の矩形波表面形状72により、同様の矩形波形状(例えば、ピーク形状74とトレンチ形状72の繰り返し)が、ドリフト層16の表面、p-ウェル18、n+領域20、ソース接点22、ゲート誘電体24及びゲート26にも与えられている。同様に、図6に示すMOSFET素子80の正弦波表面形状82により、正弦波形状(例えば、反復ピーク形状84とトレンチ形状86の繰り返し)が、ドリフト層16の表面、p-ウェル18、n+領域20、ソース接点22、ゲート誘電体24及びゲート26にも与えられている。さらに、MOSFET素子70及び80のチャネル領域28(例えば、反復ピーク形状74及び84並びに反復するトレンチ形状76及び86にそれぞれ平行に配向される)では、反復ピーク形状(例えば、矩形ピーク形状74又は曲線的なピーク形状84)及びトレンチ形状(例えば、矩形トレンチ形状76又は曲線的なトレンチ形状86)により、平面素子と比べて、チャネル幅を広く(例えば、チャネル周縁を広く)することができる。上述の如く、MOSFET素子70及び80においてこのようにチャネル領域28が広がると、MOSFET素子70及び80の1つ又は複数の個々の抵抗(例えば、チャネル抵抗及び/又はソースとn+領域18との間の接点抵抗)を低

40

50

減することができるので、それぞれの素子のオン抵抗を低減することができる。

【0042】

上述のように、図3乃至図6によると、ここに開示する様々な非平面MOSFET素子の各々では、素子毎の有効表面領域が広がり、チャネル幅が広がる。このことにより、例えば、オン抵抗のより低い素子を製造することが可能となる。さらに、SiC素子は、SiC素子の特定の形状が、SiC結晶の特定の結晶面に沿って配向又は配列されるよう、SiC結晶から作製されうることを理解されたい。このことを考慮しつつ、図7に、六方晶SiC結晶90（例えば、4H-SiC又は6H-SiC）の結晶面の例を示す。特に、図7Aに、4H-SiC又は6H-SiC結晶の（0001）面92（{0001}面族を示す）を示し、これは、他の結晶面を定義する基礎とすることができる。図7B及び7Cに、垂直

【0043】

【数10】

(1 $\bar{1}$ 00)

【0044】

面94（

【0045】

【数11】

{1 $\bar{1}$ 00}

【0046】

面族を示す）及び垂直

【0047】

【数12】

(11 $\bar{2}$ 0)

【0048】

面96（

【0049】

【数13】

{11 $\bar{2}$ 0}

【0050】

面族を示す）の4H-SiC又は6H-SiC結晶90をそれぞれ示す。さらに、図7Dに、4H-SiCの（

【0051】

【数14】

(0 $\bar{3}$ 3 $\bar{8}$ )

【0052】

）面98（

【0053】

【数15】

{0 $\bar{3}$ 3 $\bar{8}$ }

【0054】

面族を示す）又は

【0055】

10

20

30

40

【数16】

$(000\bar{1})$

【0056】

面102を基準として角度100（例えば、約55°又は54.74°）に配向した6H-SiC結晶90を示す。{a b c d}なる表記が、結晶格子の対称性により(a b c d)面と等価な全ての面の集合を示すことが、当業者に理解されるように、一般的に理解されるであろう。

【0057】

さらに、様々な面（例えば、面92、94、96及び98）により、ある結晶面に沿って配向又は配列された素子要素の様々な電気的特性が得られることを理解されたい。例えば、ある実施形態では、SiC MOSFET素子のチャネル（例えば、チャネル領域28）を、特定の面に沿って配置することにより、チャネルの有効反転チャネル移動度を高めることができる。具体例として、図7Cの

【0058】

【数17】

$(11\bar{2}0)$

【0059】

面96に配置されたチャネルにより、ボルト秒当たり約43平方センチメートル( $\text{cm}^2/\text{V s}$ )の有効チャネル移動度が可能になり、図7Bの

【0060】

【数18】

$(1\bar{1}00)$

【0061】

面94に配置されたチャネルにより、約32  $\text{cm}^2/\text{V s}$ の有効チャネル移動度が可能になります。

【0062】

【数19】

$(0\bar{3}3\bar{8})$

【0063】

面98に配置されたチャネルにより、約35  $\text{cm}^2/\text{V s}$ の有効チャネル移動度が可能になる。このように、ある実施形態では、トレンチ形状（例えば、図3乃至図6のトレンチ形状56、76及び86の壁）は、特定の面（例えば、図7に示す面92、94、96及び98）に沿って（例えば、対応するチャネル領域28に沿って）配向されて、ここに開示されるMOSFET素子（例えば、図3乃至図6のMOSFET素子50、60、70及び80）の有効反転チャネル移動度をさらに向上（そして、これによりオン抵抗を低減）させることができる。

【0064】

従来の半導体作製技術（例えば、フォトリソグラフィ、イオン注入、アニーリング、化学気相蒸着(CVD)、誘電体蒸着、ゲート金属蒸着、オーム接点形成等）が、非平面SiC MOSFET素子（例えば、図3乃至図6のMOSFET素子50、60、70及び80）の作製に利用されうることが理解されるべきである。例えば、ある実施形態では、非平面SiC表面（例えば、図3及び図4に示す三角波断面52を有する、図5に示す矩形波断面72を有する、又は、図6に示す正弦波断面82を有する）が、リソグラフィマスクによるウェット又はドライエッチングで形成されうる。このように、例えば、エッチング化学/条件、マスク材料（例えば、傾斜エッチング法又はテーパー断面エッチング法に用いる傾斜レジストマスク）、及び/又はグレースケールリソグラフィ技術により、

10

20

30

40

50

トレンチの形状が制御されうる。特定の素子形状（例えば、トレンチ形状及び／又はチャネル領域等）を、SiC結晶の特定の面（例えば、図7に示す面92、94、96及び98）に沿って配列又は配向することに加えて、以下に詳述するある実施形態では、特定の素子寸法及びドーパント濃度により、反転チャネル移動度が向上したMOSFET素子（例えば、図3乃至図6MOSFET素子50、60、70及び80）が可能になることを理解されたい。

【0065】

図8及び図9に、数値シミュレーションで得た、様々な形状寸法又は配向で製造されたMOSFET素子の特徴例を示す。シミュレーションのパラメータは、SiC基板、ドリフト層ドーピング $8 \times 10^{16} \text{ cm}^{-3}$ 、トレンチの深さ $1 \mu\text{m}$ 、トレンチピッチ $2 \mu\text{m}$ 、チャネル長 $0.7 \mu\text{m}$ 、反転チャネル移動度 $15 \text{ cm}^2/\text{Vs}$ である。図8は、比較用の様々なMOSFET素子のドレイン特性（例えば、約20Vのゲート電圧でのドレイン電流（ $I_d$ ）対ソース-ドレイン電圧（ $V_{ds}$ ））のグラフ120である。グラフ120に示すように、直線122に示す平面MOSFET素子（例えば、図1のMOSFET素子10）は、直線124よりも傾きが小さい。この直線124は、非平面MOSFET素子（例えば、図3のMOSFET素子50）を示している。例えば、図3の非平面MOSFET素子50は、表面領域が、図1のMOSFET素子10より約1.4倍広い。なお、MOSFET素子10は、非平面MOSFET素子の全オン抵抗 $R_{ds}(\text{on})$ を約14%低減している。

【0066】

さらに、図8のグラフ120の直線126は、非平面MOSFET素子（例えば、図3のMOSFET素子50）のドレイン特性を示す。ここで、図7Dに示すように、トレンチは、基板14（<0001>配向4H-/6H-SiCウェハを示す）の上面に配置されたSiCドリフト層16の

【0067】

【数20】

(0 $\bar{3}$ 3 $\bar{8}$ )

【0068】

面98上にチャネル領域がくるように、配向されている。このように、直線26は、非平面MOSFET構造を単独で用いるよりも、オン抵抗 $R_{ds}(\text{on})$ がさらに14%低減していることを示している。したがって、グラフ120に示すドレイン特性が導電チャネル移動度（例えば、反転チャネル移動度）及びオン抵抗を一般的に示すため、図8のグラフ120は、特定のMOSFET素子の実施形態で得られる一般的傾向を示している。すなわち、ある実施形態では、非平面MOSFET素子（例えば、図3乃至図6のMOSFET素子50、60、70及び80）は、平面MOSFET素子（例えば、図1のMOSFET素子10）よりも、オン抵抗を低減し、及び／又はチャネル移動度を向上させることができ、導電チャネルが特定の面（例えば、図7に示す面92、94、96及び98）に沿って配列又は配向された非平面MOSFET素子（例えば、図3乃至図6のMOSFET素子50、60、70及び80）により、オン抵抗をさらに低減し、及び／又はチャネル移動度をさらに向上させうる。

【0069】

さらに、図9は、比較のための様々なMOSFET素子の逆電流-電圧（ $I_V$ ）特性（例えば、ドレイン電流（ $I_d$ ）対ソース-ドレイン電圧（ $V_{ds}$ ））のグラフ130である。グラフ130に示すように、平面MOSFET素子（例えば、図1のMOSFET素子10）を表す曲線132は、非平面MOSFET素子（例えば、図3のMOSFET素子50）を表す曲線134よりも、ある電圧（例えば、約1500Vよりも高い $V_{ds}$ で）で電流が少ないと示している。したがって、グラフ130に示す反転 $I_V$ 特性は、平面MOSFET素子（例えば、図1のMOSFET素子10）と比べて、非平面MOSFET素子（例えば、図3のMOSFET素子50）についての阻止能力が、一般に僅かな減

10

20

30

40

50

少を示す(例えば、約3%)。ある状況では、非平面MOSFET素子(例えば、図3のMOSFET素子50)で観測された阻止能力の低下により、このような非平面素子を特定の用途に用いることができなくなることが、理解されるであろう。しかしながら、図5及び図6のそれぞれのMOSFET素子70及び80等のある実施形態は、図3に示す角の尖ったピーク形状54及びトレンチ形状56がないp-ウェル18を有し、平面MOSFET素子(例えば、図1のMOSFET素子10)と比べて、阻止能力が得られることも理解されるであろう。

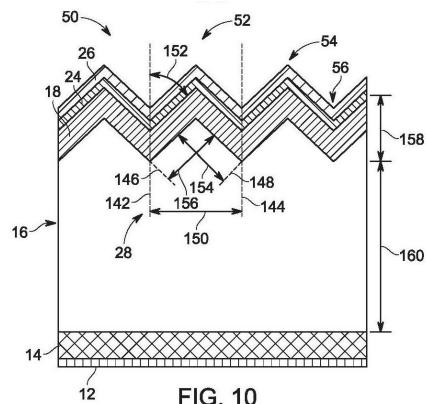

#### 【0070】

このことを考慮しつつ、図10に、図3に示すMOSFET素子50の実施形態の直線10-10線に沿った断面図を示す。このように、図10に示すMOSFET素子50には、上述の特徴(例えば、ドレイン接点12、基板14、ドリフト層16、p-ウェル18、n+領域(図示せず)、誘電層24及びゲート26)がある。さらに、図10に、三角波素子断面形状52を示す。この断面形状は、ピーク54及びトレンチ56を含む。素子断面形状52の様々な寸法についての説明を容易にするため、図10には、垂直の破線142及び144がある。これらの破線は、一般に、MOSFET素子50の底面又はドレイン接点12に対して垂直である。さらに説明をわかりやすくするために、図10には、点線146及び148がある。これらの破線は、p-ウェル18とドリフト層16との間の界面の一部からともに延びている。

#### 【0071】

図10に示す破線142及び144は、距離150を規定している。この距離を、三角波素子断面形状52の波長又はピッチと称することがある。すなわち、この距離150に亘って、MOSFET素子50の特定の要素(例えば、ドリフト層16、p-ウェル領域18、n+領域(図示せず)、ゲート誘電体24及びゲート26)が、トレンチ形状56(例えば、極小)からピーク形状54(例えば、極大)を経て他のトレンチ形状56に戻る完全なサイクルで遷移しうる。さらに、図10に、三角波素子断面形状52の角度152を示す。この三角波素子断面形状52は、p-ウェル18と垂直破線142との間に延びて図示されている。また、図10は、2つの距離154及び156を示している。これらの距離は、それぞれ、点線146及び148から他の点へ、ドリフト層16とp-ウェル18との間の界面に沿って延びてあり、三角波素子断面形状52の振幅を一般的に示している。ある実施形態では、図10に示すように距離154及び156が同じであってもよいが、他の実施形態では、距離154及び156が異なることもある。三角波素子断面形状52の特定の形状は、少なくとも部分的に、距離150、角度152、距離154、及び/又は距離156に依存することが、理解されるであろう。また、図1に示す平面MOSFET素子10と比べて、図10に示すMOSFET素子50では、一般に、導電チャネルの周縁の広がり(例えば、チャネル領域28の広がった幅)は、ほぼ、距離154(又は156)の2倍を距離150(例えば、三角波素子断面形状52の波長又はピッチ)で除した値と同等になっている。

#### 【0072】

さらに、ある実施形態では、図10に示すMOSFET素子50は、ある寸法をとりうる。例えば、ある実施形態では、距離150(例えば、三角波素子断面形状52の波長又はピッチ)は、ほぼ、トレンチ形状の深さ158の合計の2倍以上でありうる。トレンチ形状56の深さ158は、一般に、中間のピーク形状54の高さ158に対応するので、トレンチの深さ及びピークの高さは、ここでは互換的に用いられるであることを理解されたい。さらに、ある実施形態では、トレンチ形状56(例えば、トレンチ形状56の壁)は、SiC基板の

#### 【0073】

#### 【数21】

<11 $\overline{2}$ 0>

#### 【0074】

10

20

30

40

50

方向に沿って配向され、トレンチ壁（例えば、

【0075】

【数22】

(0001̄)

【0076】

面について）の角度152は、約56°（例えば、55.74°）で、チャネル領域28がSiC基板上の六方晶SiCドリフト層16の

【0077】

【数23】

10

{0338̄}

【0078】

面（例えば、図7に示す

【0079】

【数24】

(0338̄)

【0080】

面98）にきて、非平面素子構造単独のときよりも、さらに導電チャネル移動度が高く（例えば、オン抵抗が低く）なっていてもよい。<a b c d>なる表記が、結晶格子の対称性により[a b c d]方向と等価な全ての方向の集合を示すことが、当業者には理解されるであろう。

20

【0081】

ある実施形態では、トレンチ形状の深さ158は、オン抵抗（例えば、 $R_{ds(on)}$ ）と阻止能力（例えば、阻止電圧（BV））との最善の折衷案が得られるように選択される。すなわち、トレンチの深さ158が充分に大きければ、トレンチ形状56は、ドリフト層16の厚さ160の実質的な部分を使い果たすことになる。このドリフト層16は、MOSFET素子50の阻止能力を阻害しうる。一方、ドリフト層16の厚さ160が充分に大きく、MOSFET素子50の阻止能力を阻害することなくより深いトレンチ形状56に対応していれば、MOSFET素子50のオン抵抗 $R_{ds(on)}$ は、ドリフト層16が厚いと抵抗が大きくなるため、大きくなりうる。このように、ある実施形態では、トレンチ形状56の深さ158は、ドリフト層16の厚さ160の約10%以下でありうる。このドリフト層16は、適切な阻止能力を維持しつつ、適切にオン抵抗（例えば、 $R_{ds(on)}$ ）を低くすることができる。なお、余談であるが、垂直MOSFET50は、上述及び後述のように、特定の寸法及び/又はドーパント濃度で実現可能であるが、図4のL MOSFET60は、より広範な様々な寸法（例えば、任意の適切なトレンチの深さ158）及び/又はドーパント濃度で実現可能である。

30

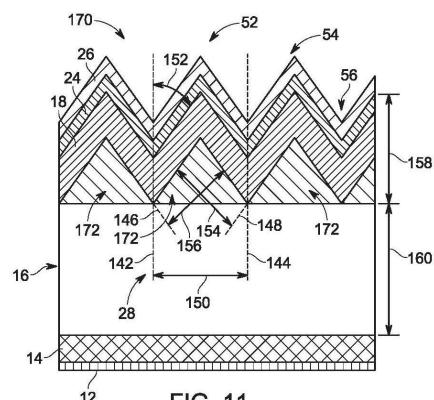

【0082】

図11に示すように、他の手法が、トレンチ形状56をさらに深く（例えば、トレンチ形状56の深さ158をさらに大きく）するために利用可能である。例えば、図11に、MOSFET素子170を示す。この素子は、トレンチ形状56がさらに深い（例えば、トレンチ形状56のドリフト層16の厚さ160に対する深さ158の比がさらに大きい）図10に示すMOSFET素子50の一実施形態である。さらに、MOSFET素子170は、オン抵抗 $R_{ds(on)}$ と阻止能力とで妥協することなく、このようにより深いトレンチ形状56を達成している。図示した実施形態では、トレンチ形成に先立って、MOSFET素子170の各ピーク形状54（例えば、各トレンチ形状56間）内に、ドーピング領域172を作製（例えば、ドーパント注入又はエピタキシャル成長を利用）することにより、より深いトレンチ形状56が実現する。非平面形状（例えば、MOSFET素子170の三角波素子断面形状52）により得られる電解遮蔽により、MOSFET素子

40

50

170を遮蔽する性能に悪影響を与えることなく、領域172内のドーピングを（例えば、ドリフト層16内のドーパント濃度を基準として）高めることができることが、理解されるであろう。

#### 【0083】

例えば、ある実施形態では、領域172内のドーパント濃度（例えば、単位立方センチメートルの逆数（ $1 / \text{cm}^3$ ）で）は、臨界電界 $Q_{cr}$ に基づいて決まることがある。この臨界電界 $Q_{cr}$ は、式： $Q_{cr} = E_c * \epsilon$ により計算可能である。ここで、 $E_c$ は、半導体が破壊せずに耐えられる最大電界であり、 $\epsilon$ は、半導体材料の絶対誘電率（例えば、SiCについて $2 \times 10^{13} \text{ cm}^{-2}$ ）。したがって、ある実施形態では、図11に示すように、ドーパント濃度は、ほぼ、臨界電界（例えば、 $2 Q_{cr}$ ）の2倍を距離155（例えば、ピーク形状54の幅、ピーク形状54の側壁に沿ったウェル領域間の距離）で除した値以下である。ある実施形態では、距離155は、トレンチの深さ158とともに変化しうる、ウェル領域間のドーピング濃度Nは、これに伴い、 $N < 2 Q_c / ( \text{距離} 155 )$ なる関係に基づいて変化しうる。したがって、ある実施形態では、作製に際して特定のMOSFET素子寸法（例えば、距離150、154、156、158、160及び角度152）及びドーピング（例えば、ドリフト層16及びドーピング領域172内）を利用することにより、深いトレンチ形状56が得られ、この形状により、素子の阻止能力を犠牲にすることなく、素子抵抗を低減（例えば、チャネル抵抗を低減）可能であることを理解されたい。

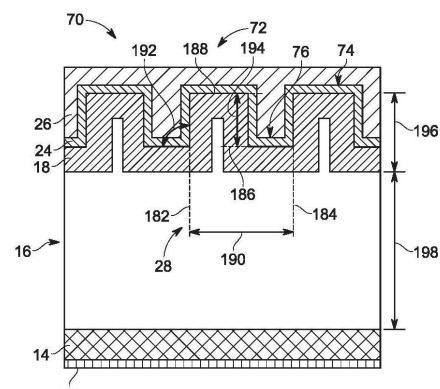

#### 【0084】

図12は、図5に示すMOSFET素子70の実施形態の直線12-12線に沿った断面図である。このように、図12に示すMOSFET素子70は、上述の形状（例えば、ドレイン接点12、基板14、ドリフト層16、p-ウェル18、n+領域（図示せず）、誘電層24及びゲート26）を含む。さらに、図12に、矩形波素子断面形状72を示す。この断面形状は、矩形ピーク74及び矩形トレンチ76を含む。素子断面形状72の様々な寸法についての説明をわかりやすくするため、図12は、垂直の破線182及び184を含む。これらの破線は、一般に、MOSFET素子70の底面又はドレイン接点12に対して垂直である。さらに説明をわかりやすくするために、図12は、垂直点線186及び188（例えば、MOSFET70の底面又はドレイン接点12に平行）を含む。各点線は、p-ウェル18と誘電層24との間の水平の界面からともに延びている。

#### 【0085】

図12に示す破線182及び184は、距離190を規定している。この距離を、矩形波素子断面形状72のピッチ又は波長と称することがある。すなわち、この距離190に亘って、MOSFET素子70の特定の要素（例えば、ドリフト層16、p-ウェル領域18、n+領域（図示せず）、ゲート誘電体24及びゲート26）が、ピーク形状74（例えば、極大）からトレンチ形状76（例えば、極小）を経て他のピーク形状74に戻る完全なサイクルで遷移しうる。さらに、図12に、矩形波素子断面形状72の角度192を示す。この矩形波素子断面形状72は、p-ウェル18と垂直破線142との間に延びて図示されており、約90°であってもよい。ある実施形態では、角度192が90°より大きく、台形のトレンチ設計が得られることが理解されるであろう。また、図12に、距離194を示している。この距離は、点線186及び188間を延び、矩形波素子断面形状72のトレンチの深さを一般的に示している。トレンチ形状76の深さ194は、一般に、中間のピーク形状74の高さ194に対応するので、トレンチの深さ及びピークの高さは、ここでは互換的に用いられることが理解されるであろう。矩形波素子断面形状72の特定の形状は、少なくとも部分的に距離190、角度192及び/又は距離194に依存することが理解されるであろう。また、図1に示す平面MOSFET素子10と比べて、図12に示すMOSFET素子70では、一般に、導電チャネルの周縁が広く（例えば、チャネル領域28の幅が大きく）、約 $(2a + b) / b$ （ここでaは、距離194、bは距離190）となっていることが理解されるであろう。

#### 【0086】

さらに、ある実施形態では、図12に示すMOSFET素子70は、ある寸法になって

10

20

30

40

50

いてもよい。例えば、ある実施形態では、距離 190（例えば、矩形波素子断面形状 72 の波長又はピッチ）は、ほぼ、深さ 196 の p - ウェル 18 と空乏領域の和の 2 倍以上となりうる。さらに、ある実施形態では、トレンチ形状 76 が、SiC 結晶の

【0087】

【数 25】

<11 $\bar{2}0$ >

【0088】

又は

【0089】

【数 26】

10

<11 $\bar{0}0$ >

【0090】

方向に沿って配向され、それにより、素子のチャネル領域 28 が、六方晶 SiC 基板の

【0091】

【数 27】

(11 $\bar{2}0$ )

【0092】

20

面 96 又は

【0093】

【数 28】

(11 $\bar{0}0$ )

【0094】

面 94（図 7 に示すように）に配置されて、反転チャネル移動度が高くなるとともに全オ

ン抵抗が低くなつてもよい。

【0095】

ある実施形態では、トレンチの深さ 194 は、オン抵抗  $R_{ds} (on)$  と阻止能力との最善の折衷案が得られるように選択されうる。すなわち、トレンチの深さ 194 が充分に大きければ、トレンチ形状 76 は、ドリフト層 16 の厚さ 198 の実質的な部分を使い果たすことになる。これにより、MOSFET 素子 70 の阻止能力（例えば、BV）が阻害されることになる。一方、ドリフト層 16 の厚さ 198 が充分に大きく、MOSFET 素子 70 の阻止能力を阻害することなくより深い p - ウェル 18 に対応していれば、MOSFET 素子 70 のオン抵抗  $R_{ds} (on)$  は、ドリフト層 16 が厚くなると抵抗が大きくなるため、大きくなりうる。このように、ある実施形態では、p - ウェル 18 の深さ 196 が、ドリフト層 16 の厚さ 198 の約 10% 以下でありうる。このドリフト層 16 は、適切な阻止能力を維持しつつ、適切にオン抵抗を低くすることができる。

30

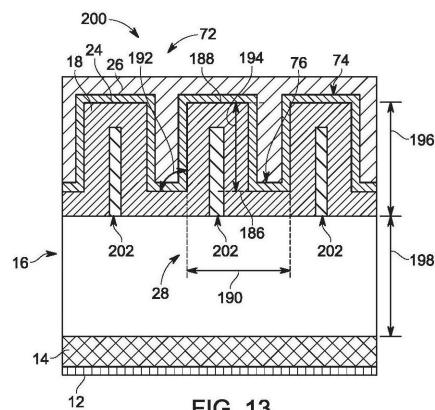

【0096】

40

図 13 に示す如く、矩形トレンチ形状 76 をさらに深く（例えば、p - ウェル 18 の深さ 196 をさらに大きく）するために、他の手法が用いられうる。例えば、図 13 に、MOSFET 素子 200 を示す。この素子は、図 12 に示す MOSFET 素子 70 の一実施形態において矩形トレンチ形状 76 がさらに深く（例えば、ドリフト層 16 の厚さ 198 に対する p - ウェルの深さ 196 の比がさらに大きくなる）なつたものである。さらに、MOSFET 素子 200 では、オン抵抗と阻止能力とで妥協することなく、トレンチ形状 76 がさらに深くなっている。すなわち、ここで説明した実施形態では、MOSFET 素子 200 の各矩形ピーク形状 74（例えば、各矩形トレンチ形状 76 間）内に（例えば、トレンチ形状 76 に先立つ）ドーピング領域 202 を形成することにより、さらに深いトレンチ形状 76（例えば、ドリフト層 16 内へとさらに深く延びた p - ウェル 18）が実現

50

している。非平面形状（例えば、MOSFET素子200の矩形波素子断面形状72）により得られる電解遮蔽により、MOSFET素子200の性能に悪影響を与えることなく、領域202内のドーピングを（例えば、ドリフト層16内のドーパント濃度を基準として）高めることができることが、理解されるであろう。例えば、ある実施形態では、領域202内のドーパント濃度（例えば、単位立方センチメートルの逆数（ $1 / \text{cm}^{-3}$ ）で）は、臨界電界 $Q_{cr}$ に基づいて決まることがある。この臨界電界 $Q_{cr}$ は、式： $Q_{cr} = E_c * 10$ により計算可能である。ここで、 $E_c$ は、半導体が破壊せずに耐えられる最大電界であり、 $E$ は、半導体材料の絶対誘電率（例えば、SiCについて $1 \times 10^{13} \text{ cm}^{-2}$ ）である。したがって、ある実施形態では、図12に示すように、ドーパント濃度は、ほぼ、臨界電界（例えば、 $2 Q_{cr}$ ）の2倍を距離187（例えば、ピーク形状74の幅、ピーク形状74の側壁上のウェル領域間の距離）で除した値以下であります。ある実施形態では、作製に際して特定のMOSFET素子寸法（例えば、距離190、194、196、198及び角度192）及びドーピング（例えば、ドリフト層16及びドーピング領域202内）を利用することにより、より深いトレンチ形状76が得られ、この形状により、素子の阻止能力を犠牲にすることなく、素子抵抗を低減（例えば、チャネル移動度を向上、オン抵抗を低減）可能であることを理解されたい。

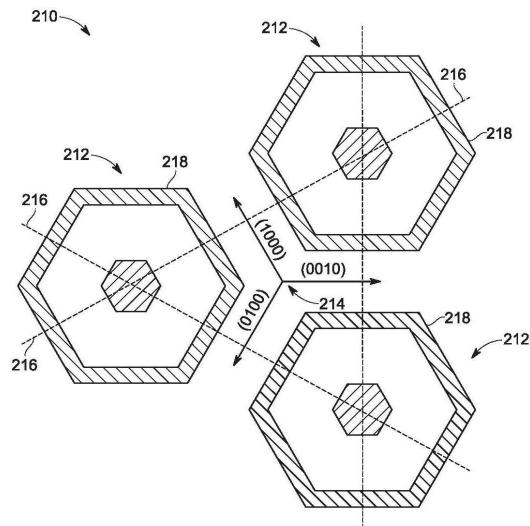

## 【0097】

上述の本手法は、セル状構造（例えば、三角形状、矩形状、ハニカム状等）にも適用可能であることが、理解されるべきである。例えば、図14に、六方セル状設計210の平面図を示す。この設計にて、MOSFET作用面積212の一例が、図示したSiC基板のSiC結晶軸214に沿ってとられている。図示したMOSFET素子212の作製の際、SiC結晶構造の六角状配向（図7について上述）により、様々な方向（例えば、軸214を基準とする）にそれぞれ配向されるとともに、同時に、特定の結晶面（例えば、

## 【0098】

## 【数29】

(0338)

## 【0099】

面、

## 【0100】

## 【数30】

(1120)

## 【0101】

面又は

## 【0102】

## 【数31】

(1100)

## 【0103】

面）に沿ったトレンチ側壁のあるチャネル周縁に対して垂直な同一のトレンチ形状（直線216で示す）が同時作成できるようになる。図示した図14の六方セル状設計210は軸対称であるため、各トレンチ形状216は、同一のチャネル移動度を提供することが、理解されるであろう。例えば、ある実施形態では、トレンチ形状216は、図3乃至図6及び図10乃至図13で上述したトレンチ形状56、76及び86と構造が同様のトレンチ形状でありうる。具体例として、ある実施形態では、各トレンチ形状216は、矩形トレンチ形状（例えば、図12及び図13に示すトレンチ形状76と同様）であってもよく、さらに、六方晶SiC基板の

## 【0104】

10

20

30

40

【数32】

(1120)

【0105】

面96（例えば、図7に示すように）に沿って配向又は配列されていてもよい。詳細に上述したように、これらのトレンチ形状216では、各MOSFET素子212の表面領域及びチャネル幅が増大しうるものであるため、反転チャネル移動度が高くなるとともにオン抵抗が低くなる。

【0106】

本手法の技術的效果として、半導体素子（例えば、MOSFET、IGBT、及び他の適切な半導体素子）内の素子抵抗が減少する。本実施形態として、素子毎の表面領域が広く、チャネル幅が広い（例えば、チャネル周縁が広い）非平面半導体素子（例えば、SiC素子）がある。これにより、低抵抗のSiC素子を製造することができる。開示した素子の実施形態では、チャネル抵抗を低減することに加えて、SiC素子構造内の界面での接点領域を広げることにより、チップ毎の有効表面領域が広くなつて1つ又は複数の接点抵抗が低減している。さらに、本手法は、ハニカム構造等のセル状SiC素子設計にも適用して、チャネル伝導を向上させ、及び／又はオン抵抗を減少させることができる。

10

【0107】

ここで記述では、本発明を開示するため、及び当業者が本発明を実施できるように、複数の例を用いており、最善の形態も含まれている。発明の実施には、任意の素子又はシステムを作製及び使用すること、並びに、任意の組み込まれた方法を実施することが含まれる。本発明の特許可能な範囲は、特許請求の範囲に規定され、当業者が想到する他の例を含む。このような他の例は、特許請求の範囲の逐語的な文言から異なることのない構造的要素を含むか、又は、特許請求の範囲の逐語的文言とは実質的でない部分が異なる均等な構造的要素を含む場合、特許請求の範囲に含まれることが意図されている。

20

【符号の説明】

【0108】

- |     |                        |    |

|-----|------------------------|----|

| 10  | MOSFET素子               |    |

| 12  | ドレイン接点                 |    |

| 14  | n型基板層                  | 30 |

| 16  | n型ドリフト層                |    |

| 18  | p-ウェル                  |    |

| 20  | n+領域                   |    |

| 22  | ソース接点                  |    |

| 24  | 誘電層                    |    |

| 26  | ゲート                    |    |

| 28  | チャネル領域                 |    |

| 50  | 非平面SiC n-チャネルDMOSFET素子 |    |

| 50  | MOSFET素子               |    |

| 52  | 表面形状                   | 40 |

| 54  | 反復ピーク形状                |    |

| 56  | トレンチ形状                 |    |

| 60  | 非平面SiCラテラルMOSFET素子     |    |

| 60  | LMOSFET素子              |    |

| 62A | n-ウェル                  |    |

| 62B | n-ウェル                  |    |

| 64  | ドレイン接点                 |    |

| 66  | チャネル領域                 |    |

| 70  | SiCDMOSFET素子           |    |

| 70  | MOSFET素子               | 50 |

|       |                        |    |

|-------|------------------------|----|

| 7 2   | 矩形波表面形状                |    |

| 7 2   | 素子断面形状                 |    |

| 7 4   | 矩形ピーク形状                |    |

| 7 6   | 矩形トレンチ形状               |    |

| 8 0   | S i C D M O S F E T 素子 |    |

| 8 0   | M O S F E T 素子         |    |

| 8 2   | 正弦波表面形状 8 2            |    |

| 8 2   | 素子断面形状                 |    |

| 8 4   | ピーク形状                  |    |

| 8 6   | トレンチ形状                 | 10 |

| 9 0   | 六方晶 S i C 結晶           |    |

| 9 2   | 面                      |    |

| 9 4   | 面                      |    |

| 9 6   | 面                      |    |

| 9 8   | 面                      |    |

| 1 0 2 | 面                      |    |

| 1 2 0 | グラフ                    |    |

| 1 3 0 | グラフ                    |    |

| 1 5 0 | 距離                     |    |

| 1 5 2 | 角度                     | 20 |

| 1 5 4 | 距離                     |    |

| 1 5 6 | 距離                     |    |

| 1 5 8 | 深さ                     |    |

| 1 6 0 | 厚さ                     |    |

| 1 7 0 | M O S F E T 素子         |    |

| 1 7 2 | 領域                     |    |

| 1 8 7 | 距離                     |    |

| 1 9 0 | 距離                     |    |

| 1 9 2 | 角度                     |    |

| 1 9 4 | 深さ                     | 30 |

| 1 9 6 | 深さ                     |    |

| 1 9 8 | 厚さ                     |    |

| 2 0 0 | M O S F E T 素子         |    |

| 2 0 2 | ドーピング領域                |    |

| 2 1 0 | 六方セル状設計                |    |

| 2 1 2 | M O S F E T 素子         |    |

| 2 1 4 | S i C 結晶軸              |    |

| 2 1 6 | トレンチ形状                 |    |

| 2 1 6 | 直線                     |    |

【図1】

FIG. 1

(従来技術)

【図3】

FIG. 3

【図2】

FIG. 2

【図4】

FIG. 4

【図5】

FIG. 5

【図7A】

FIG. 7A

【図6】

FIG. 6

【図 7 B】

FIG. 7B

【図 7 C】

FIG. 7C

【図 7 D】

FIG. 7D

【図 8】

FIG. 8

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

【図 13】

FIG. 13

【図 14】

FIG. 14

## フロントページの続き

## (51)Int.Cl.

H 01 L 29/41 (2006.01)

## F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 E |

| H 01 L | 29/78 | 6 5 2 K |

| H 01 L | 29/78 | 6 5 3 A |

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 29/78 | 6 5 2 M |

| H 01 L | 29/78 | 6 5 8 G |

| H 01 L | 29/78 | 6 5 5 A |

| H 01 L | 21/28 | 3 0 1 B |

| H 01 L | 29/44 | S       |

## (72)発明者 アレキサンダー・ヴィクトロヴィッチ・ボロトニコフ

アメリカ合衆国、ニューヨーク州、ニスカユナ、ビルディング・ケイ1 - 3エイ59、ワン・リサ

ーチ・サークル、ゼネラル・エレクトリック・カンパニイ・グローバル・リサーチ

## (72)発明者 ピーター・アルマーン・ロジー

アメリカ合衆国、ニューヨーク州、ニスカユナ、ビルディング・ケイ1 - 3エイ59、ワン・リサ

ーチ・サークル、ゼネラル・エレクトリック・カンパニイ・グローバル・リサーチ

審査官 杉山 芳弘

## (56)参考文献 特開2013-077761 (JP, A)

特開2010-258385 (JP, A)

特開2012-038771 (JP, A)

特開平05-075121 (JP, A)

特開2004-079577 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336

H 01 L 29 / 78

H 01 L 29 / 12