(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4797185号

(P4797185)

(45) 発行日 平成23年10月19日(2011.10.19)

(24) 登録日 平成23年8月12日(2011.8.12)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/331  | (2006.01) | HO1L 29/72 | Z    |

| HO1L 29/73   | (2006.01) | HO1L 27/06 | 101U |

| HO1L 27/06   | (2006.01) | HO1L 29/78 | 653B |

| HO1L 21/8248 | (2006.01) | HO1L 29/78 | 656B |

| HO1L 21/8222 | (2006.01) |            |      |

請求項の数 30 (全 17 頁) 最終頁に続く

(21) 出願番号

特願2002-270858 (P2002-270858)

(22) 出願日

平成14年9月18日 (2002.9.18)

(65) 公開番号

特開2003-179067 (P2003-179067A)

(43) 公開日

平成15年6月27日 (2003.6.27)

審査請求日

平成17年9月16日 (2005.9.16)

(31) 優先権主張番号

09/956382

(32) 優先日

平成13年9月18日 (2001.9.18)

(33) 優先権主張国

米国(US)

(73) 特許権者 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 11110

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100104352

弁理士 朝日 伸光

(74) 代理人 100106183

弁理士 吉澤 弘司

最終頁に続く

(54) 【発明の名称】縦型リプレイスメント・ゲート・トランジスタと両立性のあるバイポーラ接合トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

縦型バイポーラ接合トランジスタの加工方法であって、半導体基板に、第1導電型をドープした埋め込みコレクタ領域(206)を形成するステップと、

前記半導体基板の埋め込みコレクタ領域の上に、順に、第1絶縁層(210)、犠牲層(215)、そして第2絶縁層(220)を形成するステップと、

前記第1絶縁層(210)、犠牲層(215)及び第2絶縁層(220)を通じて、前記埋め込みコレクタ領域が露出するように、ウインドウ(227)を形成するステップと、

前記ウインドウに、前記埋め込みコレクタ領域と接触し、前記第1導電型をドープしたコレクタ領域(234)と、第2導電型をドープしたベース領域(235)とを含む、ドープト半導体プラグ(231)を形成するステップと、

前記ドープト半導体プラグのベース領域の上に重なり、前記第1導電型をドープした、エミッタ領域(241)を形成するステップと、

エッチングプロセスにより、前記犠牲層を除去して、前記ドープト半導体プラグの一部を露出させるステップと、

前記ドープト半導体プラグの露出部にゲート誘電体(250)を形成するステップ、

前記犠牲層の除去によって生じた空間に、前記ゲート誘電体の周囲に、半導体材料または導電体材料を充填し、制御端子(266)を形成するステップと

を含む方法。

【請求項 2】

前記第1導電型がP型かつ第2導電型がN型である、または、該第1導電型がN型かつ第2導電型がP型である、請求項1に記載の方法。

【請求項 3】

前記犠牲層を除去する際のエッチングプロセスが、等方性ウエット・エッチングまたは等方性ドライ・エッチングである、請求項1に記載の方法。

【請求項 4】

前記第1絶縁層、犠牲層、第2絶縁層を順に形成するステップは、前記第1絶縁層(210)の上、前記犠牲層の上、または該第1絶縁層(210)と犠牲層両方の上、エッチ・ストップ層(211, 216)を形成するステップをさらに含み、該エッチ・ストップ層が、前記エッチングプロセスにより犠牲層を除去してドープト半導体プラグの一部を露出させるステップの際に、該第1絶縁層(210)、前記第2絶縁層(220)、または該第1絶縁層(210)と第2絶縁層(220)両方へのエッチャントの接触を防止する、請求項1に記載の方法。10

【請求項 5】

前記第1絶縁層(210)および前記第2絶縁層(220)の材料が、ドープト二酸化シリコンである請求項1に記載の方法。

【請求項 6】

前記第1絶縁層(210)および前記第2絶縁層(220)の材料が、ドープト二酸化シリコンであり、20

前記半導体基板を加熱して前記第1絶縁層(210)および前記第2絶縁層(220)からドーパントを拡散させて、ドープト半導体プラグの隣接領域をさらにドープするステップをさらに含み、前記第1絶縁層(210)および前記第2絶縁層(220)のドープト二酸化シリコンの導電型が、ドープト半導体プラグに含まれるコレクタ領域の導電型と反対である、請求項1に記載の方法。

【請求項 7】

前記ドープト半導体プラグが、in situドーピングおよび注入から選択されるプロセスによってドープされる、請求項1に記載の方法。

【請求項 8】

前記ドープト半導体プラグが、シリコン、シリコン・ゲルマニウム、およびシリコン・ゲルマニウム炭素からなる群から選択される結晶性半導体材料から形成される、請求項1に記載の方法。30

【請求項 9】

前記半導体基板が、シリコン基板である請求項1に記載の方法。

【請求項 10】

前記ゲート誘電体を形成するステップは、酸素含有雰囲気で700から1000の範囲の温度にて前記半導体基板を加熱すること、化学気相成長法、原子層堆積法、およびジェット蒸着法から選択されるプロセスによって実行される、請求項1に記載の方法。

【請求項 11】

前記ゲート誘電体の材料が、二酸化シリコン、窒化シリコン、酸窒化シリコンおよび金属酸化物からなる群から選択される、請求項1に記載の方法。40

【請求項 12】

前記ゲート誘電体の厚みが、1nmから20nmである、請求項1に記載の方法。

【請求項 13】

前記埋め込みコレクタ領域が、前記コレクタ領域より高いドーピング濃度を有する、請求項1に記載の方法。

【請求項 14】

前記制御端子への電圧の印加により、前記ドープト半導体プラグのコレクタ領域およびベース領域内にデブリーション領域を形成する請求項1に記載の方法。50

## 【請求項 15】

集積回路構造の加工方法であって、

半導体基板の主表面のMOSFETを形成する領域に、第1導電型をドープした第1ドープ領域(205)を形成するステップであって、前記第1ドープ領域がソース領域である、ステップ、

前記半導体基板の主表面の縦型バイポーラ接合トランジスタを形成する領域に、第2導電型をドープした埋め込みコレクタ領域(206)を形成するステップと、

前記第1ドープ領域及び埋め込みコレクタ領域上に、順に、第1絶縁層(210)、犠牲層(215)、そして第2絶縁層(220)を形成するステップと、

前記第1絶縁層(210)、犠牲層(215)、第2絶縁層(220)を通じて、前記MOSFETを形成する領域に、前記第1ドープ領域を露出するように第1ウインドウ(225)を形成し、前記縦型バイポーラ接合トランジスタを形成する領域に、前記埋め込みコレクタ領域を露出するように第2ウインドウ(227)を形成するステップと、

前記第1ウインドウに、第2の導電型でドープされた第1ドープト半導体プラグ(230)を形成し、前記第2ウインドウに、前記第2導電型をドープしたコレクタ領域(234)、および前記第1導電型をドープしたベース領域(235)を含み、該コレクタ領域が前記埋め込みコレクタ領域と接触している、第2ドープト半導体プラグ(231)を形成するステップと、

前記第1ドープト半導体プラグ上に第2ドープト領域(242)を、及び第2ドープト半導体プラグ上にエミッタ領域(241)を形成するステップであって、該第2ドープト領域がドレイン領域である、ステップ、

前記半導体基板を加熱することにより、前記第1絶縁層(210)及び第2絶縁層(220)からの固体拡散によって、該第1及び第2絶縁層(210, 220)のドーパントが前記第1ドープト半導体プラグに移動することにより、該第1ドープト半導体プラグと該第1絶縁層(210)の隣接する領域に第1ドープト領域の拡張部(270)を、該第1ドープト半導体プラグと該第2絶縁層(220)の隣接する領域に第2ドープト領域の拡張部(272)を形成するステップと、

エッチングプロセスにより、前記犠牲層を除去し、それにより第1ドープト半導体プラグおよび第2ドープト半導体プラグの一部を露出するステップと、

前記第1ドープト半導体プラグの露出部及び第2ドープト半導体プラグの露出部上に、ゲート誘電体(250)を形成するステップと、

前記犠牲層の除去によって生じた空間に、前記ゲート誘電体の周囲に、半導体材料または導電体材料を充填することにより、前記MOSFETが形成される領域にゲート(265)を形成し、前記縦型バイポーラ接合トランジスタを形成する領域に制御端子(266)を形成するステップを含む方法。

## 【請求項 16】

前記第1導電型がP型かつ第2導電型がN型である、または、該第1導電型がN型かつ第2導電型がP型である、請求項15の方法。

## 【請求項 17】

前記第1ドープト領域をソース領域に代えてドレイン領域とし、前記第2ドープト領域をドレイン領域に代えてソース領域とする、請求項15の方法。

## 【請求項 18】

前記犠牲層を除去する際のエッチングプロセスが、等方性ウエット・エッチングまたは等方性ドライ・エッチングである、請求項15に記載の方法。

## 【請求項 19】

前記第1絶縁層、犠牲層、第2絶縁層を順に形成するステップは、前記第1絶縁層(210)の上、前記犠牲層の上、または該第1絶縁層(210)と該犠牲層両方の上に、エッチ・ストップ層(211, 216)を形成するステップをさらに含み、該エッチ・ストップ層が、前記エッチングプロセスにより犠牲層を除去し第1ドープト半導体プラグおよび第2ドープト半導体プラグの一部を露出するステップの際に、該第1絶縁層(210)

10

20

30

40

50

、前記第2絶縁層(220)、または該第1絶縁層(210)と第2絶縁層(220)両方へのエッチャントの接触を防止する、請求項15に記載の方法。

【請求項20】

前記第1絶縁層(210)および第2絶縁層(220)の材料が、ドープト二酸化シリコンである、請求項15に記載の方法。

【請求項21】

前記第1絶縁層(210)および第2絶縁層(220)のドープト二酸化シリコンの導電型が、第1ドープト半導体プラグの導電型と反対である、請求項20に記載の方法。

【請求項22】

前記第1ドープト半導体プラグおよび第2ドープト半導体プラグが、in situまたは注入によってドープされる、請求項15に記載の方法。

【請求項23】

前記第1ドープト半導体プラグおよび第2ドープト半導体プラグが、シリコン、シリコン・ゲルマニウム、およびシリコン・ゲルマニウム炭素からなる群から選択される結晶性半導体材料から形成される、請求項15に記載の方法。

【請求項24】

前記ゲート誘電体を形成するステップは、酸素含有雰囲気で700から1000の範囲の温度に前記半導体基板を加熱すること、化学気相成長法、原子層堆積法、およびジエット蒸着法から選択されるプロセスによって実行される、請求項15に記載の方法。

【請求項25】

前記ゲート誘電体の材料が、二酸化シリコン、窒化シリコン、酸窒化シリコンおよび金属酸化物からなる群から選択される、請求項15に記載の方法。

【請求項26】

前記ゲート誘電体の厚みが、1nmから20nmである、請求項15に記載の方法。

【請求項27】

前記制御端子に電圧を印加して、前記第2ドープト半導体プラグ内の電流を制御する、請求項15に記載の方法。

【請求項28】

前記第2ドープト領域およびエミッタ領域を形成するステップの次に、該第2ドープト領域およびエミッタ領域上に、窒化シリコン層(239)を形成するステップをさらに含む、請求項15に記載の方法。

【請求項29】

前記第1ドープト半導体プラグ(230)と第2ドープト半導体プラグ(231)を形成するステップの後に、前記第1ドープト半導体プラグの頭部(232)および第2ドープト半導体プラグの頭部(233)を、平坦化するステップをさらに含む、請求項15に記載の方法。

【請求項30】

前記半導体基板が、シリコン基板である、請求項15に記載の方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、異なる導電型の接合を組み込んだ半導体デバイス、およびこうしたデバイスを作る方法を対象とする。より具体的には、本発明は、バイポーラ接合トランジスタ・デバイス、およびこうしたデバイスを組み込んだ集積回路の加工方法に関する。

【0002】

【従来の技術】

半導体デバイス性能の向上およびデバイス密度(単位面積当たりのデバイス数)を高くすることは、従来から半導体産業の重要な目的となっている。デバイス密度は、個々のデバイスをより小さくすること、およびデバイスをより密に詰め込むことによって高くする。しかし、デバイスの寸法(フィーチャ・サイズまたはデザイン・ルールとも呼ばれる)が

10

20

30

40

50

小さくなると、デバイスを形成する方法およびその構成要素を適合させなければならない。例えば、生産ライン・フィーチャ・サイズは、現在0.25ミクロンから0.12ミクロンの範囲にあり、微細化の傾向は変えようがない。しかし、デバイスの寸法が縮小すると、何らかの製作上の制限が、特にリソグラフィ工程で発生する。実際、現在のリソグラフィ工程は、今日のデバイス・ユーザーが要求する必要最小限のサイズで、正確にデバイスを製作することができない点に近づいている。

#### 【0003】

現在、大部分の金属酸化物半導体電界効果トランジスタ(MOSFETs)は、横型配置で形成され、電流は基板の正面またはボーダー表面と平行に流れる。これらMOSFETデバイスのサイズが縮小し、デバイス密度が高くなるに従って、加工プロセスの難しさも上昇する。特に、リソグラフィ・パターンへの画像描写に用いられる放射線の波長がデバイス寸法に近づいているので、チャネルを作るためのリソグラフィ工程は問題である。したがって、横型MOSFETについては、ゲート長は、リソグラフィ技術で精密に制御することができない点に近づいている。

10

#### 【0004】

実装密度の最近の進歩により、いろいろな形の縦型MOSFETが得られている。特に、縦型デバイスは、Takato, H. 等の「Impact of Surrounding Gates Transistor (SGT) for Ultra-High-Density LSI's」、IEEE Transactions on Electron Devices、38(3)巻、573~577頁(1991年)に記述され、ブレーナMOSFETデバイスの代替として提案されている。最近では、縦型リプレイスメント・ゲート・トランジスタとして特徴づけられるMOSFETが記述されている。Hergenrother等「The Vertical-Replacement Gate (VRG) MOSFET: A 50-nm Vertical MOSFET with Lithography-Independent Gate Length」Technical Digest of the International Electron Devices Meeting、75頁、1999年を参照されたい。

20

#### 【0005】

一般に、集積回路は、MOSFET、JFETおよびバイポーラ接合トランジスタを含めた複数の能動素子、および抵抗器、コンデンサなどの受動構成部品を有する。共有の米国特許第6,027,975号、第6,197,641号は、縦型リプレイスメント・ゲート(VRG)MOSFETを加工するためのある種の技術を教示しており、参照により本明細書に組み込む。したがって、集積回路の製作コストを低減するために、MOSFETの加工に用いられるのと同様の両立性のある処理ステップを用いて、バイポーラ接合トランジスタ(BJTs)を製作することが有利である。

30

#### 【0006】

【発明が解決しようとする課題】

縦型MOSFETの加工と両立性のあるプロセスを用いてBJTを加工するための、アーキテクチャおよび加工プロセスが提供される。

#### 【0007】

40

#### 【課題を解決するための手段】

本発明の一実施形態によれば、半導体デバイスは、半導体材料の第1層を有し、その中に第1ドープト領域を形成する。複数の半導体および絶縁層が第1ドープト領域の上に重なり、複数の層にウインドウまたはトレーナーが形成される。第1ドープト領域とは異なる導電型の第2ドープト領域が、ウインドウ内で、第1ドープト領域の上に重なっている。やはりウインドウ内で、第2ドープト領域とは異なる導電型の第3ドープト領域が、第2領域の上に重なっている。第1領域は、BJTのコレクタ領域であり、第2領域はベースである。第3領域はエミッタである。

#### 【0008】

関連の製作方法では、集積回路構造を、デバイス形成に適当な半導体層を形成すること、

50

および第1面に沿って第1表面を設けることによって加工する。その上に複数の層を形成し、複数の層内にウインドウを形成する。B J T デバイスでは、第1デバイス領域を半導体層に形成し、このデバイス領域がコレクタである。ベース層をコレクタ層の上に形成し、エミッタ領域をベースの上に形成する。ベースおよびエミッタ領域はいずれもウインドウ内に形成される。

【 0 0 0 9 】

本発明によれば、B J T および縦型M O S F E T は、両立性のある加工プロセスを用いて、最小限の加工ステップを追加して、同じ半導体基板に加工することができる。すなわち、どちらのデバイスも複数の共用の絶縁層および半導体層から形成され、各デバイスの活性領域のいくつかはウインドウ内の複数の層に形成される。

10

【 0 0 1 0 】

好みしい実施形態の説明と以下の図面を用いて検討すれば、本発明をより容易に理解することができ、本発明のさらなる利益および効果がさらに容易に分かるであろう。

【 0 0 1 1 】

一般的習慣により、各種記載の特徴は縮尺ではなく、本発明に関連する特定の特徴を強調するように描かれている。参照符号は、図面および試験すべてについて同じ要素を意味する。

【 0 0 1 2 】

【発明の実施の形態】

トランジスタおよび集積回路の加工に関して、用語「主表面」は、例えばプレーナ・プロセスで、複数のトランジスタが、その中およびその周りで加工される半導体層の表面を指す。本明細書で用いる用語「縦型」は、主表面に対して実質的に直交していることを意味する。一般に、主表面は、バイポーラ・トランジスタ・デバイスが加工される単結晶シリコン層の<100>面に沿っている。M O S F E T については、用語「縦型トランジスタ」は、個々の半導体構成部品が主表面に対して垂直に配列しているトランジスタを意味し、従って電流はドレインからソースへ垂直に流れる。例として、縦型M O S F E T については、ソース、チャネルおよびドレイン領域は、主表面に対して比較的垂直なアラインメントで形成される。B J T に関しては、用語「縦型トランジスタ」は、コレクタ、ベースおよびエミッタ領域が、主表面に対して比較的垂直なアラインメントで形成されることを意味する。コレクタは、トランジスタ動作中に、電流の伝導および電荷のコレクションを含む、バイポーラ・トランジスタ・デバイスのコレクタ機能を行う半導体層の一部を意味する。そのような領域が無くてもトランジスタの電気特性が変わらない場合には、同じ導電型の隣接領域はコレクタに含まれない。

20

【 0 0 1 3 】

本発明は、縦型リプレイスメント・ゲート金属酸化物半導体電界効果トランジスタ (M O S F E T s ) の加工と類似しており両立性があるプロセスを用いて、バイポーラ接合トランジスタ (B J T s ) を加工するプロセスを対象とする。ここに記述する一つまたは複数の実施形態によれば、B J T およびV R G トランジスタは、コストおよび加工の複雑さを最小化する方法で、例えばV R G 形成に対して追加のマスク・ステップの数を最小にするように、単一のシリコン基板上に形成される。本発明は、これらの目的を実現するB J T デバイスおよび加工プロセスを開示する。

30

【 0 0 1 4 】

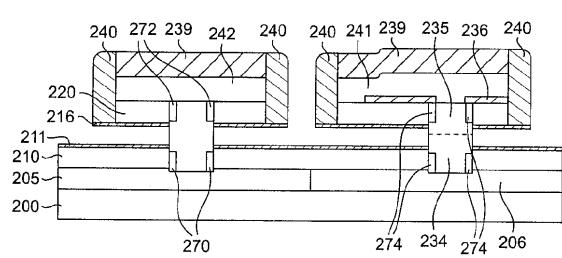

図1A から 1Q は、本発明による代表的なデバイスを形成するための加工の様々な段階にある、集積回路構造200の断面図を示す。この説明から、バイポーラ接合トランジスタを単独で、またはV R G トランジスタの加工とともに、いかにして加工できるかが明白になるであろう。

40

【 0 0 1 5 】

V R G M O S F E T およびB J T 両方を形成するための加工プロセスを、図1A から 1Q に図示する。単一の加工プロセスで両方のデバイス型を加工することの両立性を実証するために、V R G M O S F E T およびB J T 両方の形成を図示する。しかし、本発明は、縦

50

型MOSFETおよびBJTが並列配列で、または同じプロセス・フロー中に加工される実施形態に限定されるものではない。

【0016】

本明細書に記載の様々な半導体フィーチャおよび領域は、シリコン半導体処理に基づくことが好ましいが、本発明の他の実施形態は、単独または組み合わせた、化合物半導体またはヘテロ接合半導体を含む異なる半導体材料に基づいてもよい。

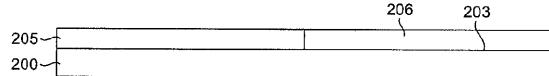

【0017】

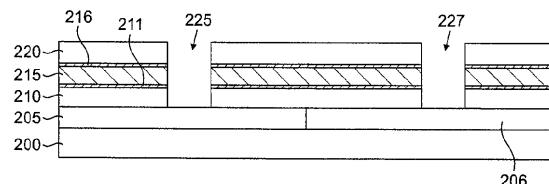

図1Aを参照すると、濃厚にドープしたソース領域205を、シリコン基板200、好ましくは<100>結晶配向を有する基板に、露出した主表面203に沿って形成する。この縦型MOSFETの実施形態では、後述するように、デバイスのソース領域はシリコン基板に形成され、ドレイン領域はその後形成される縦型チャネルの上に形成される。別法として、ドレイン領域を基板に形成し、ソース領域を縦型チャネルの上に形成することもできる。前の実施形態が、本明細書の説明の主題である。しかし、本明細書の説明から、ドレイン領域がシリコン基板に形成され、ソース領域がその後形成される縦型チャネルの上に形成されるデバイスを容易に形成できることは明らかであろう。

【0018】

MOSFETデバイスに、濃厚にドープしたソース領域205を形成した後、ソース領域205をマスクし、シリコン基板200に埋め込みコレクタ領域206を形成する。ソース領域205にn型をドープした場合は、埋め込みコレクタ領域206にはp型をドープし、PNPBJTの一領域を形成する。ソース領域205にp型をドープする実施形態では、埋め込みコレクタ領域206にはn型がドープされ、NPNBJTを形成する。本発明の他の実施形態では、埋め込み絶縁体充填トレンチまたはLOCOS領域（すなわち、シリコンの局所酸化）など、何らかの形の分離を同じドーパント型領域の間に介在させる場合は、ソース領域205にp型（またはn型）をドープすることができ、埋め込みコレクタにもp型（またはn型）をドープすることができる。

【0019】

濃厚にドープしたソース領域205および埋め込みコレクタ領域206の深さ、その中のドーパント濃度およびドーパントの型（例えば、n型またはp型）は、すべて設計選択事項である。ドーパントがリン（P）、ヒ素（As）、アンチモン（Sb）、またはホウ素（B）である代表的なソース領域205は、約 $1 \times 10^{19}$ 原子/cm<sup>3</sup>から約 $5 \times 10^{20}$ 原子/cm<sup>3</sup>の範囲のドーパント濃度を有する。基板200におけるソース領域205の深さは、約200nm未満であることが好ましい。埋め込みコレクタ領域206の代表的濃度も、約 $1 \times 10^{19}$ 原子/cm<sup>3</sup>から約 $5 \times 10^{20}$ 原子/cm<sup>3</sup>の範囲である。埋め込みコレクタ領域206の深さは、一般にソース領域の深さと同じである。下記から明らかなように、埋め込みコレクタ領域206は、後で形成され図1Fで参照符合234によって識別される隣接コレクタ領域（すなわち、「コレクタ」動作の大部分が行われる活性コレクタ領域）より高いドーピング濃度を有する。したがって、コレクタ領域234との電気的接触は、より高いドーピング濃度の結果より低い抵抗を有する、より高くドープされた埋め込みコレクタ206を経由して行われる。

【0020】

図1Bでは、ソース領域205および埋め込みコレクタ206の上に複数の材料層が形成される。一実施形態では、材料210、211、215、216および220の5層が、基板200のソース領域205および埋め込みコレクタ206の上に形成される。絶縁層210は、ソース領域205および埋め込みコレクタ206を、上に重なる層から電気的に分離する。したがって、絶縁層210は、この絶縁の目的に合致する材料から構成され、絶縁の目的に整合する厚みを有する。適当な材料の例には、ドープト酸化シリコンが含まれる。ドープト絶縁層の使用は、絶縁層210もドーパント・ソースとしての役割を果たして、後で説明するように、引き続き形成されるMOSFETデバイスのソース／ドレイン拡張部に、固相拡散プロセスによってドープするような実施形態で有利である。二酸化シリコン・ドーピング・ソースの一例は、PSG（リンガラス、すなわちリンドープト

10

20

30

40

50

酸化シリコン) または BSG (ボロン・ガラス、すなわちボロン・ドープト酸化シリコン) である。当分野の技術者なら、基板上に PSG または BSG の層を形成する適當な手段、例えば、プラズマ増速化学気相成長法 (PECVD) を知っている。絶縁層 210 の適當な厚みは、約 25 nm から約 250 nm の範囲である。絶縁層 210 は、 $1 \times 10^{-2}$  / cm<sup>3</sup> のオーダーの高いドーパント濃度を有する。

#### 【0021】

絶縁層 210 の上に、エッチ・ストップ層 211 を形成する。エッチ・ストップは、当分野の技術者に知られているように、エッチングが下にある層または上に重なる層に進行するのを防止することを意図している。したがって、エッチ・ストップは、選択されたエッチング液に対して、隣接層より著しく大きな耐エッチング性を有する。具体的にこの場合は、選択されたエッチング液に対して、エッチ・ストップ層 211 のエッチング速度は、後述する犠牲層である上に重なる層のエッチング速度よりずっと遅い。本発明によれば、二酸化シリコン (例えば、テトラエチレンオルソシリケート (TEOS) から形成された二酸化シリコン) の犠牲層の除去のために、下にある層に対するエッチング液の作用を制限する適當なエッチ・ストップ材料が選択される。窒化シリコン (Si<sub>3</sub>N<sub>4</sub>) はこうした適當なエッチ・ストップ材料である。

#### 【0022】

エッチ・ストップ層 211 の厚みは、エッチング工程で取り除かれる材料の深さに対して、選択されたエッチング液に対するエッチ・ストップ材料の抵抗性がどの程度であるかで決まる。エッチング液が下にある層に作用するのを防ぐことに加えて、エッチ・ストップ層 211 は、固相拡散工程中にソース / ドレイン拡張部を作るのに用いられたドーパントの、下方への拡散に対するオフセット・スペーサおよび拡散バリヤの役割も果たし、これによりゲートに対するソース / ドレイン拡張部の間隔および長さを画定する。エッチ・ストップ層 211 は、約 5 nm から約 50 nm の範囲の厚みを有する。

#### 【0023】

エッチ・ストップ層 211 の上に、(例えば、TEOS プロセスによって) 犠牲層 215 を形成する。後続の処理ステップ中に、犠牲層 215 を除去し、犠牲層 215 が空けたスペースに MOSFET ゲートを形成する。したがって、犠牲層 215 の絶縁材料は、エッチング液が、エッチ・ストップ層 211 と比べて、犠牲層 215 を除去するために著しく高い選択性を有するように選ばれる。犠牲層 215 の厚みは、最終 MOSFET デバイスのチャネル長に対応するように選ばれる。二酸化シリコンは、犠牲層 215 の適當な半導体材料の一例である。

TEOS プロセスでは、一般に、酸素雰囲気中、650 から 750 での化学気相成長 (CVD) によって、気化した液体 TEOS (テトラエチルオルソシリケート前駆体 (Si(OCH<sub>3</sub>)<sub>4</sub>) が分解してシリコン酸化膜 (TEOS 堆積酸化物と呼ばれる) の形成が起こる。こうした TEOS 堆積は、良好な均一性およびステップ・カバレッジを実現することが知られている。一般に、この堆積膜は、二酸化シリコンと呼ばれることが多いが、シリコンの非化学量論的酸化物であることが分かっている。オゾン (O<sub>3</sub>) を、例えば反応酸素の 10 パーセントまで混ぜると、より低温での堆積が促進される。オゾンを含む代表的な反応は、400 および 300 トルで、オゾン 6 パーセントを含む酸素を 1 分当たり 4 標準リットル (slm) 、He を 1.5 slm、および TEOS を 1 分当たり 300 標準立方センチメートル (sccm) として行われる。

#### 【0024】

エッチ・ストップ層 216 は、犠牲層 215 の上にも形成される。エッチ・ストップ層 216 は、層 211 の機能と同様な役割を果たし、例えば窒化シリコンで形成することができる。

#### 【0025】

エッチ・ストップ層 216 の上に、絶縁層 220 を形成する。絶縁層 220 は、絶縁層 210 と同じエッチング速度 (共通のエッチング液に対して) を有することが有利であるので、これらの層を同じ材料、例えば PSG または BSG から形成することが好ましく、し

10

20

30

40

50

たがって、これもまたMOSFETソース／ドレイン拡張部へのドーパント・ソースとしての役割を果たすことができる。

【0026】

層210、211、215、216および220のすべては、通常の化学気相成長法(CVD)プロセス、または他のよく知られた堆積技術を用いて堆積することができる。上記の層の順序については、他の実施形態が、大きな変更、例えば堆積層の減少を含んでもよいことにも留意しなければならない。いずれにせよ、得られる構造を用いてMOSFETデバイス用の一つの縦型チャネル領域と、BJTデバイス用の他の領域が形成される。

【0027】

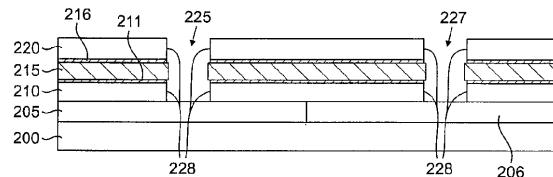

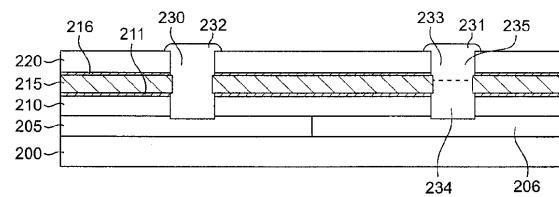

図1Cを参照すると、開口、ウインドウ、またはトレンチ225および227が、絶縁層220、エッチ・トップ層216、犠牲層215、エッチ・トップ層211、および絶縁層210を通して、MOSFETのソース領域205およびBJTの埋め込みコレクタ領域206まで異方にエッチングされている。ウインドウの水平寸法、すなわち図1Dの断面の水平寸法は、最終デバイスの所望の性能特性、加工されるデバイスのサイズ的制約、およびウインドウ225および227の形成に用いられるリソグラフィ工程の限界によって決まる。ウインドウ225および227の長さ、すなわち頁内部への距離も、主として設計選択事項である。ウインドウ225および227は、同寸法である必要は無い。所与のウインドウ水平寸法に対して、ウインドウ内に後で形成されるコンダクタの電流容量は、ウインドウ長さの増大と共に増加する。

【0028】

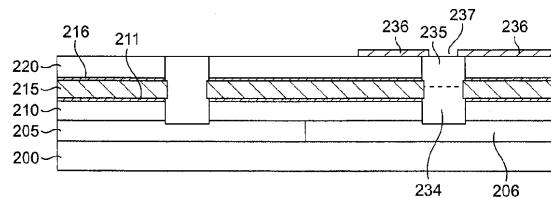

次いで、ウインドウ225および227は、化学洗浄工程(例えば、RCAまたはピランハ・クリーン)にかけて、ウインドウ225および227の底のシリコンを洗浄する。この洗浄ステップの結果、ウインドウ225および227との境界を形成している絶縁層210および220の小部分が除去される。得られたくぼみ228を図1Dに示す。こうして、犠牲層215およびエッチ・トップ層211および216は、絶縁層210および220の端部を越えて延在する。

【0029】

図1Eを参照すると、デバイス品質の結晶性半導体材料(例えばシリコン)230および231を、それぞれウインドウ225および227内に形成する。使用可能な結晶性半導体材料の他の例には、シリコングルマニウムおよびシリコングルマニウム炭素がある。結晶性半導体材料をウインドウ内に形成する技術は、当分野の技術者にはよく知られている。例えば、結晶性半導体材料は、エピタキシャルに(すなわち、それぞれソース領域205および埋め込みコレクタ領域206から成長させて)または堆積させて、ウインドウ225および227内に形成することができる。他の実施形態では、基板200全体上にアモルファス・シリコンを堆積させ、ウインドウ225および227、ならびに各ウインドウ上端の頭部232および233を除いてすべてを除去する。次いでアモルファス・シリコンは、例えばレーザーでアニールしてこれを再結晶化する。

【0030】

ウインドウ225内の結晶性半導体材料またはプラグ230には、ドープしてMOSFETチャネルを形成し、かつ反対にドープしたソースおよびドレイン拡張部を形成しなければならない。但し、一般に後者はプロセスの後方で形成される。チャネル領域を形成するために結晶性半導体材料230をドーピングする各種の周知技術は適当である。エピタキシャル成長または堆積による形成中のIn-situドーピング、または形成後の結晶性半導体材料230中へのドーパントの注入は、チャネル領域を形成する適当な方法である。In-situ、すなわち化学気相成長法で材料の層が形成されるときのドーパント導入は、よく知られており本明細書では詳細に説明しない。一般に、ドーパントは、堆積工程の適当な点で雰囲気中に導入されて所望の濃度を形成する。これらの技術はいずれも、BJTの結晶性半導体材料231の、二つの反対にドープされた領域の形成にも適用することができる。

【0031】

10

20

30

40

50

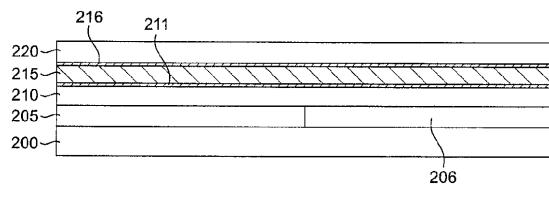

結晶性半導体材料 230 および 231 は、ドープされていない状態で成長または堆積し、次いで注入によってドーピングすることもできる。BJT 用の結晶性半導体材料 231 は、2 つのドーパント型を含む。すなわち、頭部領域 235 はベースを形成し、したがって下にあるコレクタ領域 234 とは反対のドーパント型を有するので、2 つの注入ステップが必要になる。第 1 ステップでは、両領域 234 および 235 には、イオン注入によって第 1 ドーパント型をドープする。次いで、適当なエネルギーでイオンを注入することによって反対にドーピングして、領域 234 のドーパントを第 1 ドーパント型から第 2 ドーパント型へ変えてベース領域 235 を形成し、一方、下にあるベース領域 234 は、第 1 ドーパント型でドーピングされたままである。代表的な最終ドーパント濃度は、エミッタについて 1 × 10<sup>19</sup> から 5 × 10<sup>20</sup> / cm<sup>3</sup>、ベースについては 1 × 10<sup>17</sup> / cm<sup>3</sup> およびコレクタについては 1 × 10<sup>16</sup> / cm<sup>3</sup> である。MOSFET 用チャネルの底部にソース / ドレイン拡張部を形成するためには、基板 200 から結晶性半導体材料 230 の底部へドーパントを拡散することができる。イオン注入も、結晶性半導体材料 230 の頭部にソース / ドレイン拡張部領域を作るための適当な手段である。また下記に詳述するように、隣接する絶縁層からソース / ドレイン拡張部の領域にドーパントを拡散するために固相拡散を用いることもできる。

#### 【0032】

さらに他の実施形態では、ウインドウ 227 の 2 つの BJT 領域 234 および 235 に異なる半導体材料を用いることが所望される。このときは、次に他の材料をその中に堆積させることができるように、成長エピタキシャル層が完全にウインドウ 227 を充填しないようにする。当分野の技術者なら分かるように、この実施形態に従ってウインドウ 227 に異なる材料を形成させるには、他のウインドウで何らかの加工ステップが行われている間は、ウインドウ 225 と 227 を交互にマスキングする必要である。

#### 【0033】

結晶性半導体材料 230 および 231 にドープし、ドーパントがその中に所望どおりに分布した後は（ある実施形態では、ソースおよびドレイン拡張部は、プロセスのこの点ではまだ形成されていない）、基板には、ドーパントの分布に著しく影響を与える条件を施すべきではない。このステップの後、1100 を超える温度に基板をさらさないことが、必ずしもではないが、好ましい。実際、プロセスのこの点の後、1000 を超える温度に基板をさらさないことが有利である。ある実施形態では、基板は、900 を超える温度に長時間（例えば、数分を超えて）さらさない。しかし、基板に、約 1000 の温度で、ドーパントの分布に悪影響を与える瞬時熱アニールを施すことができる。別法として、所望のドーパント分布を生じさせるように、この後の高温処理を計画することもできる。

#### 【0034】

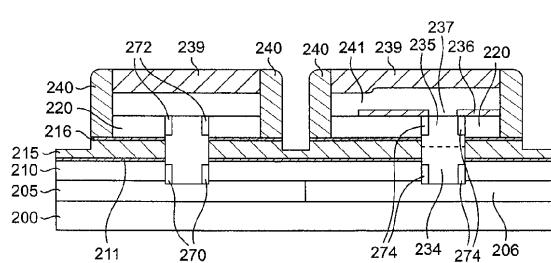

結晶性半導体材料 230 および 231 の頭部 232 および 233 は、例えば化学的 / 機械的研磨によって除去される。この工程の結果、図 1F に示したように、結晶性半導体材料 230 および 231 の上面と絶縁層 220 とが平坦化される。同様に図 1F に示したように、ベース領域 235 に隣接する絶縁層の領域上に、窒化シリコン層 236 を形成する。窒化層 236 は、今後形成されるエミッタを、絶縁層 220 の BSG 材料からの p 型固相拡散から分離することが好ましい。ベース領域 235 にアクセスするために、窒化シリコン層 236 にウインドウ 237 をエッチングする。これらのプロセス・ステップの間、MOSFET デバイスはマスクされる。

#### 【0035】

絶縁層 220 および窒化シリコン層 236 を含めた構造全体の上に、共形層 238 を形成する。層 238 は、MOSFET の自己整合頭部コンタクト（この実施形態ではドレイン・コンタクト）を提供する。層 238 の適当な材料の 1 例は、ドープト多結晶シリコンであり、この場合ドーパントの型は、MOSFET チャネル・ドーパントと反対である。層 238 のドーパントの濃度は、約 1 × 10<sup>20</sup> 原子 / cm<sup>3</sup> より高い。

#### 【0036】

10

20

30

40

50

図1Gにさらに示したように、層238の上に共形層239を堆積する。層239用に選ぶ材料は、犠牲層215のエッティング速度より著しく遅いエッティング速度を有するように選ぶ。好ましくは、239用に選ぶ材料は、エッチ・ストップ層211および216の材料と同じである。適当な材料の一例は窒化シリコンである。層239は、既知の技術を用いて層238の上に形成される。

#### 【0037】

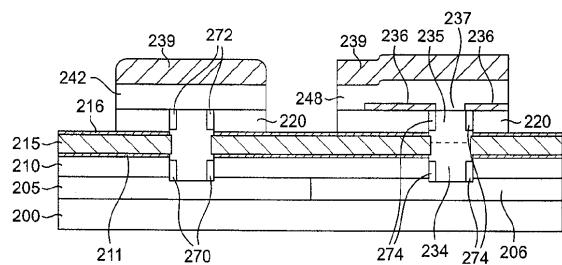

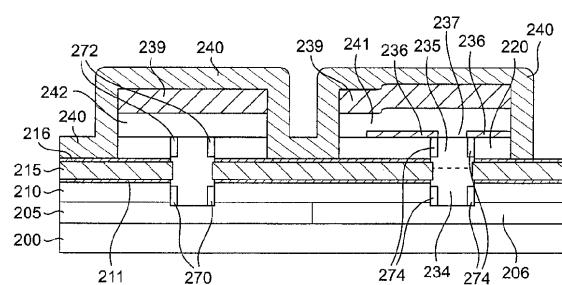

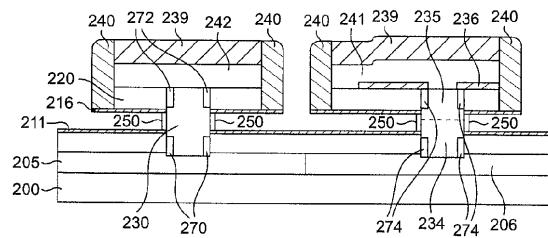

通常のリソグラフィ技術を用いて、層238、層239および絶縁層220をパターン化し、残る部分が結晶性半導体材料230またはベース235の上に重なる部分または隣接部だけとなるように、(1つまたは複数のドライ・エッチ・ステップを用いて)エッティングする。図1Hを参照されたい。ここで、BJTのエミッタは参考符合241で呼ばれ、MOSFETのドレインは参考符合242で呼ばれる。

10

#### 【0038】

一実施形態では、プロセスのこの点で、上記のようにPSGまたはBSG材料から形成されている絶縁層210および220からの固相拡散によってソース/ドレイン拡張部を形成する。ドーパントは、絶縁層210および220からの固相拡散によって、結晶性半導体材料230および231内に移動させられて、MOSFETのソース拡張部270およびドレイン拡張部272、およびBJTの領域拡張部274を形成する。固相拡散では、酸化物(例えば、二酸化シリコン)はドーパント・ソースとしての役割を果たす。高温で、ドーパントは、結晶性半導体材料230および231のドープされた酸化物から隣接のドープされてない(またはわずかにドープされた)領域に移動させられる。ドープされる領域が、結晶性半導体材料230および231と、ドーパント・ソースとしての役割を果たす絶縁層210および220の間の界面によって画定されているので、この技術は有利である。この技術は、自己整合ソース/ドレイン拡張部(すなわち、ソース・ドレイン拡張部がゲートと整合している)の形成を可能にする。固相拡散技術の例は、Ono, M等「Sub-50nm Gate Length N-MOSFETs with 10nm Phosphorus Source and Drain Junctions」、IEDM 93、119~122頁(1993年)、およびSaito, M等「An SPDD D-MOSFET Structure Suitable for 0.1 and Sub 0.1 Micron Channel Length and Its Electrical Characteristics」、IEDM 92、897~900頁(1992年)に記載されており、これらを参考により本明細書に組み込む。

20

#### 【0039】

絶縁層210および220からドープされる結晶性半導体材料230部分のドーパントの濃度は、一般に、少なくとも約 $1 \times 10^{19} / \text{cm}^3$ であり、約 $5 \times 10^{19} / \text{cm}^3$ のドーパント濃度が有利であると考えられる。この固相拡散技術を用いて、非常に浅いソースおよびドレイン拡張部270/272を得ることができる。ソース拡張部270およびドレイン拡張部272は、結晶性半導体材料230内部へ、好ましくは結晶性半導体材料230の幅の半分未満まで浸透していることが示されている。このようにドーパントの浸透を制限することにより、結晶性半導体材料230の反対側からチャネル領域で重なる可能性が回避される。さらに、ソース拡張部270およびドレイン拡張部272がゲート誘電体250の下へ延在する距離は、ゲート長の4分の1未満に制限されることが好ましい。この距離は、オフセット・スペーサとしての役割を果たすエッチ・ストップ層211および216の厚みによって制御することができる。当分野の技術者なら周知のように、ソース拡張部270およびドレイン拡張部272のドーパントは、結晶性半導体材料230のチャネル260のドーパントとは反対の型である。

30

#### 【0040】

図1Iに示したように、次いで共形層240を堆積する。所与のエッチ化学反応に対して、層240の材料は、犠牲層215のエッティング速度より著しく遅いエッティング速度であるように選ぶ。層240の適当な材料の一例は窒化シリコンである。層240の厚みは、

40

50

ドレイン 242、エミッタ 241、層 239 および絶縁層 220 の残る部分が、その後のエッティング液との接触から保護されるように選ばれる。

【0041】

次いで、ドライ・プラズマ・エッティングなどの異方性エッティングを用いて層 240 をエッティングする。これによりエッチ・ストップ層 216 の一部分が除去される。したがって、図 1J に示したように、異方性エッティング後に残る層 240 の部分は、絶縁層 220、ドレイン 242、エミッタ 241、および層 239 の横に隣接する側壁のみである。このエッティング工程の結果、エッチ・ストップ層 211 の一部が除去され、ここで犠牲層 215 が露出する。

【0042】

次いで、デバイスに、ウエット・エッティング（例えば、水性フッ化水素酸）または等方性ドライ・エッティング（例えば、無水フッ化水素酸）を施す。これにより、犠牲層 215 の露出残存部分が除去される。結果を図 1K に示す。ここでは、絶縁層 210 は、エッチ・ストップ層 211 にまだ覆われている。絶縁層 220 およびドレイン 242 は、エッチ・ストップ層 216、ならびに層 239 および 240 の残存部分によって包まれている。したがって、絶縁層 210 および 220、ならびにドレイン 242 の残存部分は、その後のエッティング手段との接触から分離されている。犠牲層 215 の除去によって露出した結晶性半導体材料 230 の領域は、MOSFET デバイスの物理的チャネル長を画定する。さらに、BJT 領域内のエミッタ 241 および絶縁層 220 は、層 239 および 240、ならびにエッチ・ストップ層 216 によって保護されている。

10

【0043】

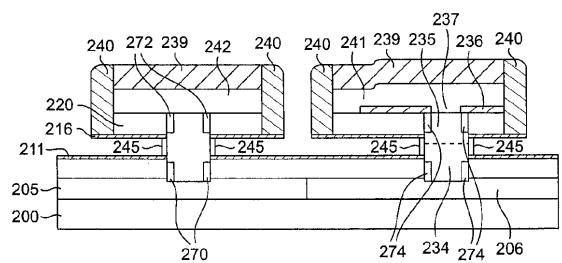

図 1L を参照すると、熱二酸化シリコンの犠牲層 245 を、結晶性半導体材料 230 および 231（後者がコレクタ領域 234 およびベース領域 235 を含む）の露出表面上に、約 10 nm 未満のオーダーの厚みまで成長させる。犠牲二酸化シリコン 245 を、通常の等方性エッティング（例えば、水性フッ化水素酸）を用いて除去する（図 1M 参照）。犠牲二酸化シリコン 245 の形成および除去の結果、結晶性半導体材料 230 および 231 各々の表面は、より滑らかになり側壁欠陥のいくつかは除去される。エッチ・ストップ層 211 および 216 は、この手段が絶縁層 210 および 220、ならびにドレイン 242 に接触することを防ぐ。このステップは必要ないが、結晶性半導体材料 230 および 231 に過度の欠陥がある場合には、これを含めることが望ましいであろう。

20

【0044】

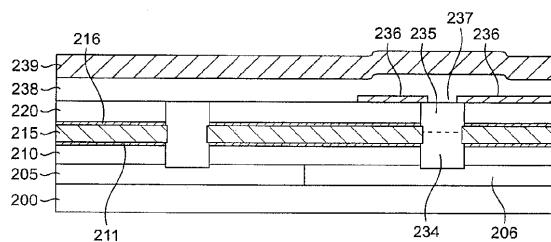

次いで、ゲート誘電体またはゲート酸化膜の層 250 を、結晶性半導体材料 230 および 231 の露出部分に形成する。図 1N を参照されたい。適当な誘電体材料には、例えば、熱成長二酸化シリコン、酸窒化シリコン、窒化シリコンまたは金属酸化物が含まれる。ゲート誘電体 250 の厚みは、約 1 nm から約 20 nm である。適当な厚みの一例は 6 mm である。一実施形態では、酸素含有雰囲気で約 700 から約 1000 の範囲の温度に基板を加熱することによって、二酸化シリコン層を形成する。ゲート誘電体 250 を形成する他の手段には、化学気相成長法、ジェット蒸着法、原子層堆積法があり、これらすべてが適当であると思われる。所望の厚みのゲート誘電体 250 を形成する条件は、当分野の技術者にはよく知られている。

30

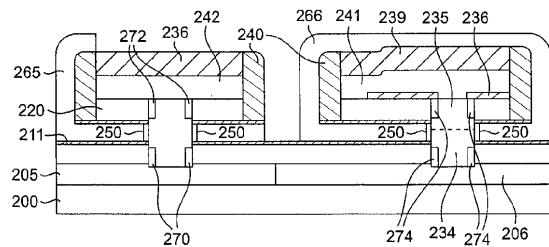

【0045】

図 1O を参照すると、ゲートは、十分共形で適当なゲート材料からなる層 255（例えば、ドーパントを *in situ* で導入し、次いで再結晶化して多結晶シリコンを形成したドープト・アモルファス・シリコンの層）を堆積することによってゲート誘電体 250 の周辺に形成される。好ましくは、このステップは、結晶性半導体材料 230 および 231 のドーパントのドーパント・プロファイルに著しい影響を与えない条件で行われる。適当なゲート電極材料の他の例には、ドープト多結晶シリコン、ドープト・シリコン・ゲルマニウム、およびドープト・シリコン・ゲルマニウム炭素がある。適当に低い抵抗率を有し、ゲート誘電体 250 の材料および他の半導体処理ステップと適合する金属および金属含有化合物も、適当なゲート材料であると考えられる。こうした金属の例には、チタン、窒化

40

50

チタン、タングステン、タングステン・シリサイド、タンタル、窒化タンタル、およびモリブデンが含まれる。ゲート材料が、半導体プラグ材料230のバンド・ギャップほぼ中央近くの仕事関数を有すると有利である。ゲートを形成する適当な手段には、化学気相成長法、電気めつき法、およびこれらの組合せが含まれる。

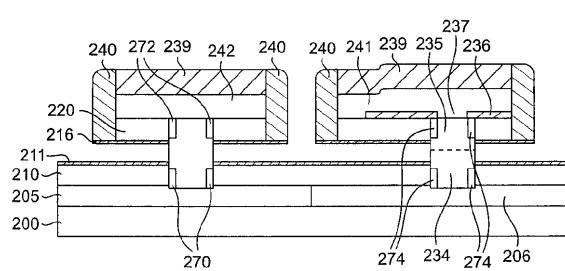

【0046】

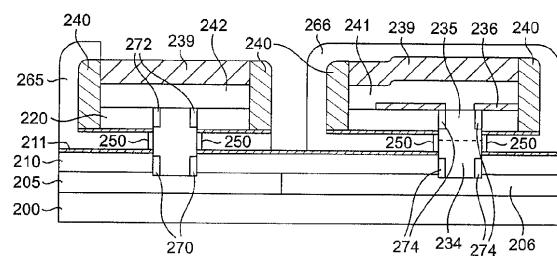

図1Pを参照すると、層255をパターン化して、MOSFETデバイスのゲート265およびBJTデバイスの制御端子266を形成する。ゲート265の配置は、主として設計選択事項である。ゲート265は、MOSFETのチャネル260を形成する結晶性半導体材料230およびゲート酸化膜250を囲んでいる。BJTの領域では、制御端子266を所望によりパターン化し、フローティングさせておく（すなわち、他の導電層と接続しない）か、この頁面外の第3次元での配線によって、ベース領域235と接続することができる。

10

【0047】

図1Qは、完成した構造を示す。MOSFETドレイン242へのアクセスは、絶縁層239にウインドウをエッチングすることによって実現される。BJTエミッタ241には、層255および絶縁層239にウインドウをエッチングすることによってアクセスする。MOSFETソース領域205およびBJT埋め込みコレクタ領域206の両方には、図1Q断面の面外の第3次元でアクセスする。BJTベース領域235へも、第3次元でアクセスする。

20

【0048】

さらに他の実施形態では、ドープされていない二酸化シリコンの薄層（例えば、厚み約25nm）を、ソース領域205の上に形成する。図1Eを参照すると、この層（示さず）は、絶縁層210（ドーパント・ソース）から下へソース領域205を通過し、次いで、結晶性半導体材料230が形成されると、上の結晶性半導体材料230へと拡散する、望ましくない固相拡散へのバリヤとして働く。

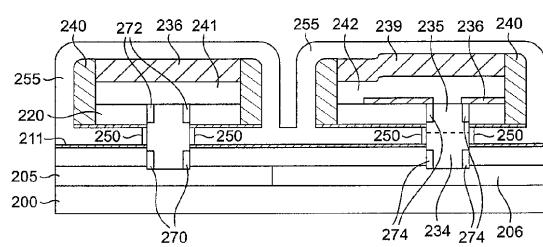

【0049】

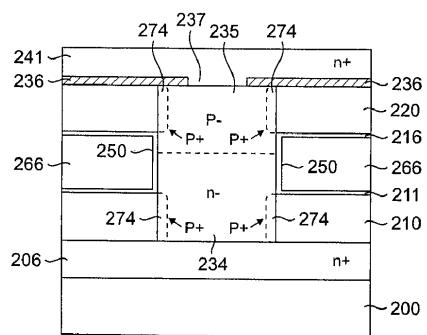

本発明の教示により、上述の加工プロセス・フローに従って組み立てられたNPN BJTの断面図を図2に示す。図2に示した層および領域は、それぞれ図1Aから1Qの同じ番号の層および領域に対応する。この例では、エミッタ241にはn+をドープし、ベース235にはpをドープし、コレクタ領域234にはnをドープし、埋め込みコレクタ206にはn+をドープしている。こうして、通常のNPN BJTトランジスタが形成されている。NMOS VRGデバイスの加工により、PNP BJTトランジスタの形成が可能になる。したがって、PMOSおよびNMOS VRGデバイスの両方を有するCMOS集積回路では、本発明の教示に従って、プロセス・フローに追加のステップをほとんど必要とせずに、NPNおよびPNPトランジスタの両方を形成することができる。MOSFETのソースおよびドレイン拡張部270および272の形成と同時に、BJTに拡張部274が形成される。拡張部274は、BJTの動作には必要ないが、有害作用はない。MOSFETの酸化膜と同時に形成される酸化膜250は、コレクタ234とベース235がゲート255を経由して短絡するのを防止する。

30

【0050】

有利には、一実施形態では、BJTの制御端子266は、分離した導電領域を形成する。この領域には、電圧を印加することができ、したがって酸化膜250と共に働くと、電界効果作用、すなわち電界効果領域内の可動電荷キャリアのデプレーション、反転、またはアキュムレーションによってバイポーラ接合トランジスタのある種の性能特性を制御または修正することができる。例えば、層制御端子266への適当な電圧の印加により、コレクタ領域234およびベース領域235内にデプレーション領域を形成することができる。こうして、印加電圧は、コレクタ234およびベース235を通る電流を制御する。印加電圧は、BJTの耐圧または利得（すなわち、BJTの出力動力に対する入力動力の割合）の制御にも用いることができる。MOSFETのゲートのように、制御端子は、高い入力インピーダンスを示す。

40

50

## 【0051】

上記の実施形態は、本発明を用いたプロセスの具体例を例示するために提供される。当分野の技術者なら、本発明を実施するために有用な、多くのプロセス・シーケンス、材料、および手段があることを理解するであろう。本発明は、頭記の特許請求の範囲と整合性がある点以外は、例示した例に限定されるものではない。

## 【図面の簡単な説明】

【図1A】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1B】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1C】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1D】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。 10

【図1E】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1F】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1G】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1H】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1I】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1J】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1K】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1L】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1M】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1N】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。 20

【図1O】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1P】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図1Q】順次加工ステップ中の、本発明の一実施形態による回路構造の断面図である。

【図2】本発明の一実施形態によるバイポーラ接合トランジスタ構造の断面図である。

【図1A】

【図1D】

【図1B】

【図1E】

【図1C】

【図1F】

【図1H】

【図1G】

【図1I】

【図1J】

【図1L】

【図1K】

【図1M】

## 【図1N】

【図1P】

【図10】

【 図 1 Q 】

【 図 2 】

## フロントページの続き

(51)Int.Cl. F I

H 01 L 29/78 (2006.01)

H 01 L 27/04 (2006.01)

(74)代理人 100106703

弁理士 産形 和央

(74)代理人 100096943

弁理士 白井 伸一

(74)代理人 100091889

弁理士 藤野 育男

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100102808

弁理士 高梨 憲通

(74)代理人 100107401

弁理士 高橋 誠一郎

(74)代理人 100085176

弁理士 加藤 伸晃

(72)発明者 サミア チャードリイ

アメリカ合衆国 32836 フロリダ, オーランド, オークサイド - コート 10039

(72)発明者 ポール アーサー レイマン

アメリカ合衆国 32835 フロリダ, オーランド, キャノン レーク サークル 7893

(72)発明者 ジョン ルッセル マックマッケン

アメリカ合衆国 32835 フロリダ, オーランド, ヴァインランド オークス ブルヴァード 8124

(72)発明者 ロス トムソン

アメリカ合衆国 34711 フロリダ, クレアモント, サマーウッド ドライブ 556

(72)発明者 ジャック キングシェンゲ ザオ

アメリカ合衆国 18069 ペンシルヴァニア, オレフィールド, オーヴァールック ロード 6662

審査官 大嶋 洋一

(56)参考文献 特開2000-091578 (JP, A)

特開平07-161726 (JP, A)

特開平01-238166 (JP, A)

特開昭61-269377 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/331

H01L 21/8222

H01L 21/8248

H01L 27/04

H01L 27/06

H01L 29/73

H01L 29/78