(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5972016号

(P5972016)

(45) 発行日 平成28年8月17日(2016.8.17)

(24) 登録日 平成28年7月22日(2016.7.22)

(51) Int.Cl.

H04N 5/268 (2006.01)

H04N 5/225 (2006.01)

F 1

H04N 5/268

H04N 5/2255/268

5/225

Z

請求項の数 4 (全 9 頁)

(21) 出願番号 特願2012-89696 (P2012-89696)

(22) 出願日 平成24年4月10日 (2012.4.10)

(65) 公開番号 特開2013-219624 (P2013-219624A)

(43) 公開日 平成25年10月24日 (2013.10.24)

審査請求日 平成27年4月10日 (2015.4.10)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 西田 徳朗

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 西谷 憲人

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

毎秒 60 フレームの動画信号を出力する撮像手段と、

前記撮像手段から出力された前記動画信号を記憶するメモリと、

前記撮像手段から出力された前記動画信号の偶数フレームを第1の動画信号に割り当て、前記メモリから前記偶数フレームを読み出すことにより毎秒 30 フレームの前記第1の動画信号を生成するとともに、奇数フレームを第2の動画信号に割り当て、前記メモリから前記奇数フレームを読み出すことにより毎秒 30 フレームの前記第2の動画信号を生成し、前記第1の動画信号と前記第2の動画信号とを出力する手段であって、所定の出力フォーマットに従って前記第1の動画信号を出力する第1の出力部と、前記所定の出力フォーマットに従って前記第2の動画信号を出力する第2の出力部とを含む出力手段と、

前記第1の出力部による前記第1の動画信号の出力と並列に、前記第2の出力部により前記第2の動画信号を出力する場合に、前記偶数フレームと前記奇数フレームとが共通の同期信号により同じタイミングで読み出されるように前記メモリからの前記偶数フレームと前記奇数フレームの読み出しタイミングを制御することにより、前記第1の動画信号に含まれるフレームと前記第2の動画信号に含まれるフレームとが、同じタイミングで出力されるように、前記第1の動画信号の出力タイミングと前記第2の動画信号の出力タイミングとを制御する制御手段とを備え、

前記制御手段は、前記撮像手段から出力された毎秒 60 フレームの動画信号における偶数フレームと奇数フレームを各フレームに対応した異なるアドレスに記憶するように前記

10

20

メモリを制御するとともに、前記撮像手段から出力された毎秒 60 フレームの動画信号における一つの偶数フレームが前記メモリに記憶された後、次の奇数フレームの前記メモリへの記憶が完了する前に、前記メモリからの前記一つの偶数フレームと前記次の奇数フレームの読み出しが開始されるように、前記メモリからの前記偶数フレームと前記奇数フレームの読み出しを制御することを特徴とする撮像装置。

【請求項 2】

前記撮像手段が前記毎秒 60 フレームの動画信号を出力する第 1 のモードと、前記撮像手段が毎秒 30 フレームの動画信号を生成する第 2 のモードの一方を設定する設定手段を備え。 10

前記制御手段は、前記第 1 のモードにおいては、前記第 1 の出力部による前記第 1 の動画信号の出力と並列に、前記第 2 の出力部により前記第 2 の動画信号が出力されるように、前記出力手段を制御し、前記第 2 のモードにおいては、前記撮像手段から出力された毎秒 30 フレームの動画信号が前記第 1 の出力部と前記第 2 の出力部とから同時に出力されるように、前記出力手段を制御することを特徴とする請求項 1 に記載の撮像装置。

【請求項 3】

前記第 1 の出力部と前記第 2 の出力部はそれぞれ、SDI フォーマットに従って動画信号を出力することを特徴とする請求項 1 に記載の撮像装置。

【請求項 4】

前記撮像手段から出力された前記毎秒 60 フレームの動画信号に含まれる R 画素、G 画素、B 画素の比率は 4 : 4 : 4 であり、各画素のデータは 10 ビットのデジタルデータであることを特徴とする請求項 1 に記載の撮像装置。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は撮像装置に関し、特に撮影された動画信号を出力する際の制御に関する。

【背景技術】

【0002】

従来、動画を撮影する撮像装置においては、撮影された動画信号が装置外部に出力されるまでには、撮像素子の特性補正処理や動画信号のフォーマット変換処理など様々な処理回路を経由する。そのため、肉眼で見ている画像と、撮像装置から出力される画像との間では遅延が発生する。 30

【0003】

例えば、撮影された画像をリアルタイムで出力する系統と、画像信号を遅延させて出力する系統を有する装置も提案されている（例えば、特許文献 1 参照）。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開平 11 - 98396 号公報

【発明の概要】

【発明が解決しようとする課題】 40

【0005】

近年では、撮像装置で撮影可能な動画の画素数やフレームレートが大きくなっている。そのため、出力される動画信号のデータ量（データレート）も大きくなってしまい、SDI (Serial Digital Interface) のように非圧縮の動画を出力するフォーマットで規定されるデータレートを上回ってしまうことがある。

【0006】

そこで、元々 1 系統の動画信号を複数の系統を用いて出力することが考えられる。

【0007】

しかしながら、従来は、複数の系統を用いて動画を出力する際のフレーム遅延については考慮されていなかった。 50

**【0008】**

本発明はこの様な問題を鑑みてなされたものであり、動画信号を複数の系統により出力する際に、動画信号の遅延を適切に制御可能とすることを目的とする。

**【課題を解決するための手段】****【0009】**

撮像装置は、毎秒 60 フレームの動画信号を出力する撮像手段と、前記撮像手段から出力された前記動画信号を記憶するメモリと、前記撮像手段から出力された前記動画信号の偶数フレームを第 1 の動画信号に割り当て、前記メモリから前記偶数フレームを読み出すことにより毎秒 30 フレームの前記第 1 の動画信号を生成するとともに、奇数フレームを第 2 の動画信号に割り当て、前記メモリから前記奇数フレームを読み出すことにより毎秒 30 フレームの前記第 2 の動画信号を生成し、前記第 1 の動画信号と前記第 2 の動画信号とを出力する手段であって、所定の出力フォーマットに従って前記第 1 の動画信号を出力する第 1 の出力部と、前記所定の出力フォーマットに従って前記第 2 の動画信号を出力する第 2 の出力部とを含む出力手段と、前記第 1 の出力部による前記第 1 の動画信号の出力と並列に、前記第 2 の出力部により前記第 2 の動画信号を出力する場合に、前記偶数フレームと前記奇数フレームとが共通の同期信号により同じタイミングで読み出されるように前記メモリからの前記偶数フレームと前記奇数フレームの読み出しタイミングを制御することにより、前記第 1 の動画信号に含まれるフレームと前記第 2 の動画信号に含まれるフレームとが、同じタイミングで出力されるように、前記第 1 の動画信号の出力タイミングと前記第 2 の動画信号の出力タイミングとを制御する制御手段とを備え、前記制御手段は、前記撮像手段から出力された毎秒 60 フレームの動画信号における偶数フレームと奇数フレームを各フレームに対応した異なるアドレスに記憶するように前記メモリを制御するとともに、前記撮像手段から出力された毎秒 60 フレームの動画信号における一つの偶数フレームが前記メモリに記憶された後、次の奇数フレームの前記メモリへの記憶が完了する前に、前記メモリからの前記一つの偶数フレームと前記次の奇数フレームの読み出しが開始されるように、前記メモリからの前記偶数フレームと前記奇数フレームの読み出しを制御する。10

**【発明の効果】****【0010】**

動画信号を複数の系統により出力する際に、動画信号の遅延を適切に制御可能となる。30

**【図面の簡単な説明】****【0011】**

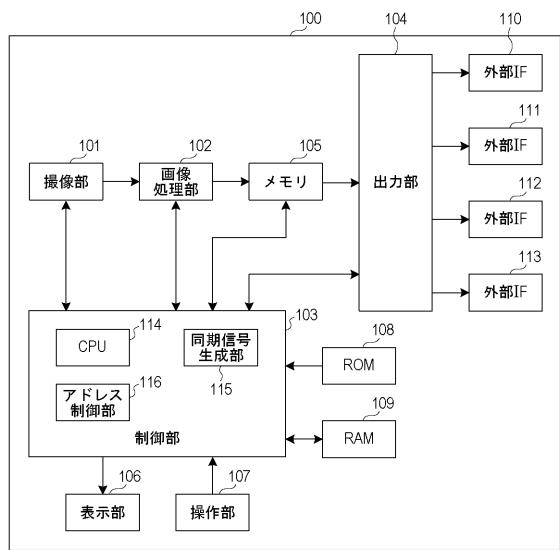

【図 1】本発明の実施形態における撮像装置のブロック図である。

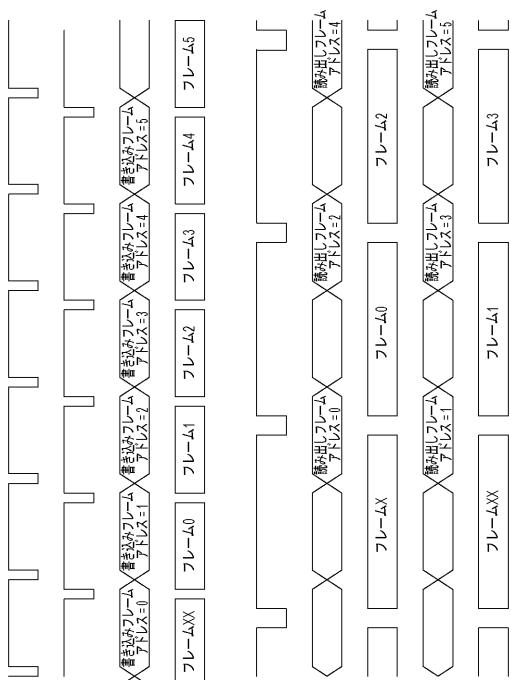

【図 2】本発明の実施形態における 60 f p s の動画信号を出力する場合のタイミングチャートである。

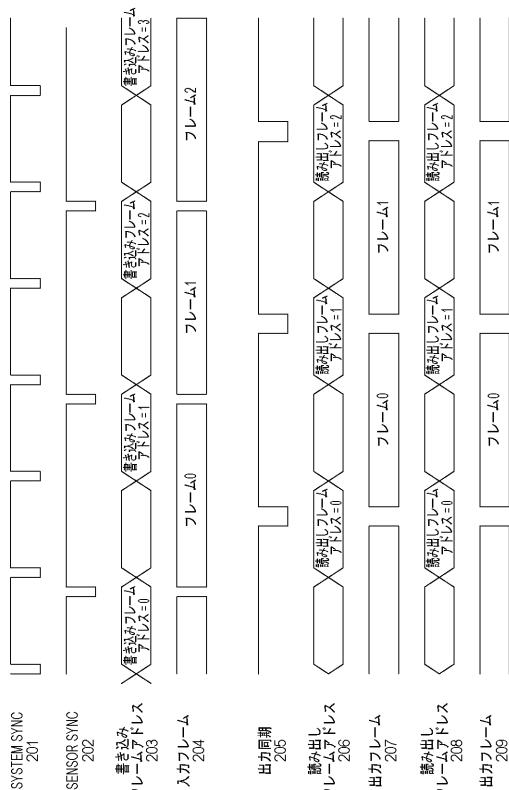

【図 3】本発明の実施形態における 30 f p s の動画信号を出力する場合のタイミングチャートである。

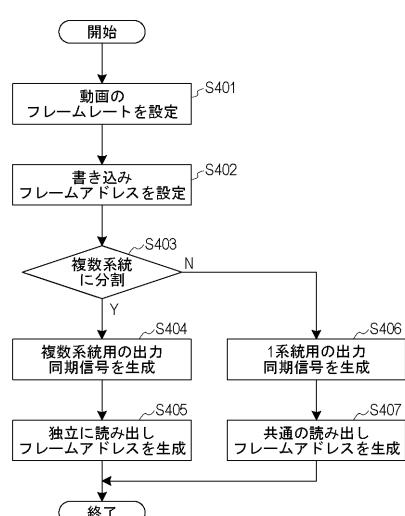

【図 4】本発明の実施形態における動画信号の出力処理を示すフローチャートである。

**【発明を実施するための形態】****【0012】**

本発明の実施形態について、図面を用いて詳細に説明する。図 1 は、本発明の実施形態にかかる撮像装置 100 の構成を示すブロック図である。

**【0013】**

図 1において、撮像部 101 はレンズ、撮像素子等を有し、被写体像を撮影して動画信号を取得する。撮像部 101 により取得される動画信号の画素数やフレームレート（単位時間あたりのフレーム数）は、制御部 103 により制御される。画像処理部 102 は、撮像部 101 により取得された動画信号に対し、様々な処理を施す。例えば、画像処理部 102 は、撮像素子の各画素のゲイン特性の補正、ホワイトバランスの補正、レンズと撮像素子の形状差により発生する周辺光量不足の補正などの処理を行う。画像処理部 102 は、各種の処理を施した動画信号をメモリ 105 に出力する。メモリ 105 は S D R A M と40

この S D R A M に対する信号の書き込み、読み出しを制御するメモリ制御部とを有する。メモリ 1 0 5 による動画信号の書き込み、読み出し処理は制御部 1 0 3 により制御される。

#### 【 0 0 1 4 】

制御部 1 0 3 は C P U 1 1 4 を有し、R O M 1 0 8 に記憶されたプログラム（ソフトウエア）に従って撮像装置 1 0 0 の各部を制御する。具体的には、制御部 1 0 3 は、撮像部 1 0 1 のレンズユニットに対して、ズーム制御やフォーカス制御を、撮像素子に対しては駆動同期信号の生成を行い、撮影フレームレートの設定などを行う。また、制御部 1 0 3 は、画像処理部 1 0 2 には各種補正制御や制御パラーメーターの送信や受信などを行う。10 また、制御部 1 0 3 は、メモリ 1 0 5 に対しては記録アドレスの設定や書き込み、読み出しの制御を行う。また、制御部 1 0 3 は、出力部 1 0 4 には外部 I F 1 1 0 ~ 1 1 3 から動画信号を出力するための同期信号の生成や出力の O N / O F F などを行う。また、制御部 1 0 3 は、表示部 1 0 6 に撮像部 1 0 1 からの動画や各種の情報を表示する。また、制御部 1 0 3 は、メモリ 1 0 5 による動画信号の書き込み、読み出しタイミングを制御するための各種の同期信号などを生成する同期信号生成部 1 1 5 を有する。また、制御部 1 0 3 は、メモリ 1 0 5 に対する動画信号の書き込み、読み出しのフレームアドレスを制御するためのアドレス制御部 1 1 6 を有する。

#### 【 0 0 1 5 】

出力部 1 0 4 は、メモリ 1 0 5 より読み出した動画信号を外部インターフェイス（I F ）1 1 0 - 1 1 3 より所定の伝送路を介して装置外部に出力する。外部 I / F 1 1 0 - 1 1 3 はそれぞれ、S D I に従って動画信号を出力する。S D I における伝送フォーマットは、S M P T E (S o c i e t y o f M o t i o n P i c t u r e a n d T e l e v i s i o n E n g i n e e r s) により伝送フォーマットが細かく規格化されている。例えば、サンプリング構造やピクセル深度、フレームレートなどが指定されている。20 3 G - S D I 規格の場合、出力可能な動画信号は、画角が水平 1 9 2 0 画素 × 垂直 1 0 8 0 画素、サンプリング構造 R G B 4 4 4 であれば、3 0 フレーム毎秒 ( f p s ) までと決められている。

#### 【 0 0 1 6 】

出力部 1 0 4 は、メモリ 1 0 5 より読み出した動画信号を伝送フォーマットに準拠する形態に変更した後、外部 I F 1 1 0 - 1 1 3 に出力する。また、外部 I F 1 1 0 - 1 1 3 の一つ、或いは、全てを使って動画信号を出力することが可能である。ユーザは操作部 1 0 7 を操作することにより、動画信号を出力するための外部 I F を選択することができる。30

#### 【 0 0 1 7 】

表示部 1 0 6 は液晶パネル等の表示装置を有し、撮像部 1 0 1 により得られた動画や各種の情報を表示する。操作部 1 0 7 はユーザが操作可能な各種のボタン、スイッチ等を有する。R O M 1 0 8 は C P U 1 1 4 の動作プログラムを記憶する。R A M 1 0 9 は制御部 1 0 3 によるワークメモリとして使用される。

#### 【 0 0 1 8 】

次に、撮像装置 1 0 0 により撮影した動画信号を外部に出力する際の処理について説明する。本実施形態では、撮像部 1 0 1 により撮影される動画信号の画素数を横 1 9 2 0 画素 × 縦 1 0 8 0 画素とする。また、撮像部 1 0 1 における撮像素子からの画像信号の読み出し方法はプログレッシブ方式、サンプリング構造を R G B 4 4 4 、各画素のデータを 1 0 b i t とする。また本実施形態では、撮影する動画のフレームレートを、6 0 f p s と 3 0 f p s の間でユーザが任意に設定できる。40

#### 【 0 0 1 9 】

図 2、図 3 は撮像装置 1 0 0 における動作タイミングチャートである。図 2 は 6 0 f p s の動画を撮影した場合の動作を示し、図 3 は 3 0 f p s の動画を撮影した場合を示している。50 3 G - S D I 規格では、水平 1 9 2 0 画素 × 垂直 1 0 8 0 画素、サンプリング構造 R G B 4 4 4 の 6 0 f p s の動画を出力することができない。そのため、本実施形態では

、 $60\text{ f p s}$ の動画を撮影した場合、この1系統の $60\text{ f p s}$ の動画信号から2系統の動画信号を生成して出力する。また、 $30\text{ f p s}$ の動画を撮影した場合、 $30\text{ f p s}$ の動画信号を1系統の動画信号として出力する。

#### 【0020】

図2、3において、SYSTEM SYNC201は撮像装置100の内部で基準となる同期信号である。本実施形態では、SYSTEM SYNC201の周波数は $60\text{ Hz}$ としている。このSYSTEM SYNC201に合わせて制御部103から各ブロックに命令が出力される。SENSOR SYNC202は撮像部101の撮像素子の駆動のための同期信号である。このSENSOR SYNC202に同期して撮像素子から電気的情報を読み出す。SYSTEM SYNC201とSENSOR SYNC202はある位相差をもって同期している。書き込みフレームアドレス203は制御部103からメモリ105に出力される書き込み用フレーム番号の情報である。画像処理部102から送信される各フレームの動画信号は、このフレーム番号に従いメモリ105の指定アドレスに書き込まれる。制御部103はSYSTEM SYNC201に同期してフレーム番号を出力し、メモリ105はSENSOR SYNC202に同期して書き込みフレームアドレスを取得する。メモリ105の容量によって記憶可能なフレーム数は決まっている。そのため、制御部103は、メモリ105に記憶される動画信号が容量オーバーとならないようにフレームアドレスの値を設定する。

#### 【0021】

20

入力フレーム204は、撮像部101から読み出されてメモリ105に書き込まれるフレームを示している。撮像部101はSENSOR SYNC202に同期して各フレームの動画信号を出力する。撮像部101から出力された各フレームの動画信号は、画像処理部102による処理に要する時間遅延されてメモリ105に出力される。なお、画像処理部102による遅延時間は所定の時間であり、フレーム周期に比べると非常に短い。

#### 【0022】

出力同期205は、動画信号を出力する際の同期信号である。撮影画角 $1920 \times 1080$ で、RGB444の10bitの動画信号を、3G-SDI規格に従って出力するために、1系統の動画信号のフレームレートは $30\text{ f p s}$ が上限である。そのため、出力同期205の周波数は $30\text{ Hz}$ である。SYSTEM SYNC201と出力同期205は、ある位相差を持って同期している。

#### 【0023】

読み出しフレームアドレス206、208はそれぞれ、制御部103からメモリ105に送信される読み出し用フレーム番号の情報である。制御部103はSYSTEM SYNC201に同期してフレーム番号を出力し、メモリ105は出力同期205に同期してフレームアドレスを取得する。このフレームアドレスにより、メモリ105から動画信号が読み出される。出力フレーム207、209は、メモリ105から読み出された動画信号を示している。各出力フレームは、出力同期205に同期している。尚、メモリ105の書き込みコマンドや読み出しコマンドも制御部103が出力する。

#### 【0024】

40

このように、撮像部により取得された動画信号は一旦、メモリ105に記憶されるため、出力するまでに遅延が発生していることがわかる。

#### 【0025】

まず、 $60\text{ f p s}$ の動画を撮影、出力する場合の処理について図2を用いて説明する。動画のフレームレートは $60\text{ f p s}$ であるので、SYSTEM SYNC201とSENSOR SYNC202は同じ周波数である。制御部103から書き込み用フレームアドレス203がSYSTEM SYNC201に同期してメモリ105に出力される。メモリ105は、SENSOR SYNC202に同期して各フレームの動画信号を記憶する。つまり、メモリ105には1秒間に60フレームの動画信号が書き込まれることになる。メモリ105の容量にも依存するが、メモリ105に書き込まれる動画信号が容量をオーバーしないように制御部103によって制御する。

**【0026】**

この様にメモリ105に書き込まれた60fpsの動画信号を読み出す際に、2系統の動画信号として読み出し、外部IF110-113の何れか二つを用いて出力する。1フレーム毎に第1の系統と第2の系統の動画信号に分割し、第1の系統には偶数フレームを、第2の系統には奇数フレームを割り当てる。即ち、取得された1系統の動画信号を、2系統の動画信号に対して1フレーム1おきに交互に割り当てる。

**【0027】**

そして、本実施形態では、各系統の動画信号のために、共通の出力同期信号205を生成する。一方、各系統の動画信号のために、独立に、読み出し用フレームアドレス206、208を生成して出力する。この構成にすることで、各系統の動画信号における各フレーム出力タイミングが、同じタイミングとなるように遅延時間を制御することが可能となる。10

**【0028】**

図2では、メモリ105にフレーム0の信号の書き込みに続いてフレーム1の書き込みが開始された後、フレーム1の書き込みが完了する前に、メモリ105からフレーム0とフレーム1の読み出しが開始されている。即ち、2系統の動画信号において同時に出力される偶数フレームと奇数フレームのうち、奇数フレームのメモリ105への書き込み開始後、この奇数フレームの書き込みが完了する前に、偶数フレームと奇数フレームを読み出す。なお、第1の系統に奇数フレームを割り当て、第2の系統に偶数フレームを割り当てる場合には、同時に出力される偶数フレームと奇数フレームのうち、偶数フレームの書き込みが完了する前に、偶数フレームと奇数フレームを読み出す。即ち、同時に出力される複数のフレームのうち、最後のフレームのメモリ105への書き込みが完了する前に、これら複数のフレームを読み出すように制御する。20

**【0029】**

この場合、出力同期205はSENSOR SYNC201よりも周波数が低いので、メモリ105から読み出されるフレーム番号が、書き込み中のフレーム番号を追い越すことはない。

**【0030】**

このように、60fpsの動画を撮影した場合、この1系統の動画を、それぞれのフレームレートが60fpsよりも低い30fpsとなるように複数の系統の動画に分けて出力する。その際、各系統の動画に含まれる各フレームの出力タイミング（位相）が同じになるように制御することにより、共通の出力同期信号により2系統の動画信号を出力することが可能となる。そのため、系統ごとに同期信号を生成する必要がなく、同期信号を生成するための回路規模を削減することができる。30

**【0031】**

次に、30fpsの動画を撮影、出力する場合の処理について、図3を用いて説明する。なお、図3では、外部IF110-113のうちの二つを使い、同じ30fpsの動画信号を同時に出力する場合を示しているが、もちろん、1系統の動画信号を出力する構成でもよい。

**【0032】**

動画信号のフレームレートは30fpsであるので、SENSOR SYNC202はSYSTEM SYNC202の半分の周波数の同期信号となっている。制御部103から書き込み用フレームアドレスがSYSTEM SYNC201に同期して出力されるが、図3の場合、SYSTEM SYNC201の二回に一回の割合で書き込みフレームアドレスが出力される。メモリ105は、SENSOR SYNC202に同期して各フレームの動画信号を記憶する。つまり、メモリ105には1秒間に30フレームの動画信号が書き込まれることになる。ここで、60fpsの動画信号を撮影する時と同様に、メモリ105に書き込まれる動画信号がメモリ105の容量をオーバーしないように制御部103によって制御する。40

**【0033】**

メモリ 105 より動画信号を読み出す場合、動画信号のフレームレートは 30 f p s であるので、外部 I F 110 - 113 の何れか一つにより 1 系統の動画信号として出力可能である。また、外部 I F 110 - 113 のうちの二つを使い、同じ 30 f p s の動画信号を同時に出力することもできる。また、制御部 103 は、第 1 の系統の読み出しフレームアドレス 206 と、第 2 の系統の読み出しフレームアドレス 208 に対し、同じ値を出力する。

#### 【 0034 】

図 3 では、メモリ 105 にフレーム 0 の信号の書き込みが開始された後、書き込みが完了する前に、メモリ 105 からフレーム 0 の信号の読み出しが開始され、第 1、第 2 の系統の動画信号として出力される。また、出力同期 205 は SENSOR SYNC 201 よりも周波数が低いので、メモリ 105 から読み出されるフレーム番号が、書き込み中のフレーム番号を追い越すことはない。

10

#### 【 0035 】

この様に、30 f p s の動画を撮影する場合にも、出力される動画信号を最短の遅延時間で出力することが可能である。

#### 【 0036 】

以上の動作を、図 4 のフローチャートを用いて説明する。図 4 は、撮影された動画を外部に出力する際の出力タイミングの制御を示すフローチャートである。図 4 の処理は制御部 103 により実行される。

#### 【 0037 】

ユーザが操作部 107 を操作して電源スイッチを投入すると、制御部 103 は、動画のフレームレートを所定のフレームレートに設定する。そして、この所定のフレームレートで撮影された動画が表示部 106 に表示される。この状態でユーザが操作部 107 を操作して、撮影する動画のフレームレートを変更する (S401)。動画のフレームレートが設定された場合、制御部 103 は、設定されたフレームレートに応じて書き込みフレームアドレスを設定する (S402)。次に、制御部 103 は、設定されたフレームレートに基づいて、撮影された動画信号を複数系統の動画信号に分割して出力するか否かを判別する (S403)。

#### 【 0038 】

前記のように、フレームレートが 60 f p s で、3G - SDI に従って動画を出力する場合、2 系統の動画信号に分割して出力する必要がある。その場合、制御部 103 は、各系統の動画信号を出力するための出力同期信号として、複数の系統の動画信号のための出力同期信号を生成する (S404)。この時、2 系統の動画信号において同時に出力される偶数フレームと奇数フレームのうち、メモリ 105 への奇数フレームの書き込みが完了する前に、偶数フレームと奇数フレームを読み出すように出力同期信号が生成される。また、制御部 103 は、各系統の動画信号を出力するために独立に読み出しフレームアドレスを生成する (S405)。

30

#### 【 0039 】

一方、撮影された動画信号を複数系統に分割せずに出力できる場合、制御部 103 は、一つの出力同期信号を生成する (S406)。例えば、図 3 に示す様に、同じ動画信号を複数の外部 I F から出力する場合であっても、制御部 103 は、各外部 I F から出力される動画信号のために、共通の出力同期信号を生成して出力する。また、制御部 103 は、一つの読み出しフレームアドレスを生成する。例えば、図 3 に示す様に、同じ動画信号を複数の外部 I F から出力する場合であっても、制御部 103 は、各外部 I F から出力される動画信号のために、共通の読み出しフレームアドレスを生成して出力する。

40

#### 【 0040 】

本実施形態では、60 f p s の動画信号を 2 系統の動画信号に分割して出力する構成であったが、これ以外のフレームレートの動画信号を 3 系統以上の動画信号に分割して出力する構成とすることも可能である。

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 特開2011-061327(JP,A)

特開2002-010129(JP,A)

特開平11-289493(JP,A)

特開2001-186484(JP,A)

特開2002-271786(JP,A)

特開2011-176635(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5 / 268

H04N 5 / 225

H04N 7 / 01