(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6259801号

(P6259801)

(45) 発行日 平成30年1月10日(2018.1.10)

(24) 登録日 平成29年12月15日(2017.12.15)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO3K 3/3562 (2006.01) | HO3K 3/3562 625 |

| HO3K 3/037 (2006.01)  | HO3K 3/037 Z    |

| GO6F 1/30 (2006.01)   | GO6F 1/30 M     |

請求項の数 2 (全 36 頁)

|              |                                                                    |

|--------------|--------------------------------------------------------------------|

| (21) 出願番号    | 特願2015-218479 (P2015-218479)                                       |

| (22) 出願日     | 平成27年11月6日 (2015.11.6)                                             |

| (62) 分割の表示   | 特願2011-263367 (P2011-263367)<br>の分割<br>原出願日 平成23年12月1日 (2011.12.1) |

| (65) 公開番号    | 特開2016-29851 (P2016-29851A)                                        |

| (43) 公開日     | 平成28年3月3日 (2016.3.3)                                               |

| 審査請求日        | 平成27年11月12日 (2015.11.12)                                           |

| (31) 優先権主張番号 | 特願2010-270534 (P2010-270534)                                       |

| (32) 優先日     | 平成22年12月3日 (2010.12.3)                                             |

| (33) 優先権主張国  | 日本国 (JP)                                                           |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 遠藤 正己<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 王丸 拓郎<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 緒方 寿彦                                          |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のフリップフロップと、

第2のフリップフロップと、を有し、

電源電位が供給されている第1の期間において、前記第2のフリップフロップがデータを保持し、

電源電位が停止されている第2の期間において、前記第1のフリップフロップがデータを保持し、

前記第1の期間から前記第2の期間への移行に際し、前記第2のフリップフロップから前記第1のフリップフロップへデータを移動し、

前記第2の期間から前記第1の期間への移行に際し、前記第1のフリップフロップから前記第2のフリップフロップへデータを移動する機能を有する半導体装置であって、

前記第1のフリップフロップは、記憶回路と、演算部と、を有し、

前記記憶回路は、酸化物半導体を有するトランジスタを有し、

前記記憶回路と、前記演算部とが積層されていることを特徴とする半導体装置。

## 【請求項 2】

請求項1において、

前記第1のフリップフロップの出力データを選択的に出力する選択回路を有し、

前記選択回路の出力データは、前記第2のフリップフロップに入力され、

前記第2のフリップフロップの出力データは、前記第1のフリップフロップに入力され

10

20

ることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体回路、半導体回路を複数有する回路、回路の駆動方法、及び回路を用いた半導体装置に関する。

【背景技術】

【0002】

近年、情報化社会はますます発達し、パーソナルコンピュータ、携帯電話等に対して、高速化、大容量化、小型化、軽量化等の要求が高まっている。このような時代の流れで、大規模集積回路（LSI：Large Scale Integration）や中央演算処理装置（CPU：Central Processing Unit）は、高集積化、動作速度の高速化、低消費電力化が求められている。10

【0003】

LSIやCPUなどの集積回路は、回路基板やプリント配線板に実装され様々な電子機器の部品の一つとして用いられている。

【0004】

回路を用いた電子機器は、動作時の消費電力だけでなく待機時の消費電力も重要視されている。特に携帯型の電子機器はバッテリーを電源としており、限られた電力量の中で使用可能時間が制限される。また、車載の電子機器は待機時の消費電力が大きいと、バッテリーの寿命の低下を招く恐れがある。また、電気自動車においては車載の電子機器のリーク電流に起因して一定の充電量あたりの走行距離が短縮してしまう。20

【0005】

回路の待機時の消費電力を低減するには、回路が有する半導体回路が演算を行っていない状態で電源を切るのが効果的である。例えば回路と同一のチップ上に電源遮断器を設け、電源遮断器により選択的に回路を休止状態に移行させて電力消費を抑える方法（特許文献1参照）などが知られている。

【0006】

ただし、回路に含まれる半導体回路が揮発性である場合、回路の電源を切ると、半導体回路内で処理途中のデータが消失してしまう。このような課題を解決する方法として、回路とは別に、電源を切っていてもデータの保持が可能な記憶回路部を設け、記憶回路部にデータを保持させてから電源を切る技術が開示されている（特許文献2、3参照）。特許文献2に示す回路は、回路の休止時に、不揮発性の記憶回路部にデータを保持させるため、休止時には回路に電力を供給する必要がなく、消費電力を低減できる。30

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許出願公開第2003/052730号明細書

【特許文献2】国際公開第2009/107408号

【特許文献3】米国特許出願公開第2004/105302号明細書

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記した方法で回路のデータを保持するためには、回路内にデータを保持するために備えている順序論理回路（例えばフリップフロップ（FF）等）に格納されているデータを不揮発性の記憶回路部に移し、当該回路にデータを保持させる。

【0009】

しかしながら、無数のFFを含む巨大な回路等の場合、無数のFFが保持する大量のデータを記憶回路部に書き込む必要がある。そのため、記憶回路部を回路とは別に設ける構成とした場合、大量のデータを限られた数の信号線を介して移動するため、回路から記憶回40

路部への書き込みに時間がかかり、速やかに休止状態に移行することができない。その結果、回路を頻繁に休止することができないため消費電力の低減効果が少なくなってしまう。

#### 【0010】

また、復帰動作時に記憶回路部から休止前のデータを読み出し、回路の各FFにそのデータを格納する動作も時間がかかり、休止状態から高速に復帰することは困難である。

#### 【0011】

本発明はこのような技術的背景のもとでなされたものである。したがって本発明は、速やかに休止状態への移行及び休止状態からの復帰ができる回路を提供することを課題の一とする。動作速度を低下させずに消費電力を低減させることができる回路を提供することを課題の一とする。または、該回路の駆動方法を提供することを課題の一とする。

10

#### 【課題を解決するための手段】

#### 【0012】

そこで、本発明者らは回路が備えるFF単位でデータの保存を行う。FFは1bitのデータを保持する順序論理回路である。そのため、FF毎にデータを保存することで、無数のFFを含む巨大な回路等の場合でも、複数のFFのそれぞれが1bit毎にデータを移せばよく、1bitのデータを移動する時間のみで無数のFFのデータを移すことができ、速やかに休止状態へ移行することができる。

#### 【0013】

具体的には、高速に動作するFF（本明細書においては揮発性FFという）毎に、揮発性FFの動作状態を記憶するためのFFであり、電力の供給が停止してもデータを保持できるFF（本明細書においては不揮発性FFという）を電気的に接続する構成とする。

20

#### 【0014】

動作時には高速に動作する揮発性FFを用い、待機時に際し、揮発性FFから不揮発性FFにデータを移動し、その後電力の供給を停止して休止状態へ移行する。揮発性FF毎に不揮発性FFが設けられているため、移動するデータが小さく、短時間でデータを移動できる。

#### 【0015】

また、復帰時も、それぞれのFFが1bitのデータを移動することによって揮発性FFのデータが復元できるので、速やかに演算を再開することができる。さらに、不揮発性FFからのデータの出力がクロック入力で制御され、不揮発性FFと揮発性FFが同期しているため、不揮発性FFから揮発性FFに確実にデータを移動することができる。

30

#### 【0016】

また、動作状態から、休止状態への移行及び休止状態から動作状態への復帰が速やかに行えるため、頻繁に休止状態へと移行することが可能となり、消費電力を低減できるという効果を奏する。

#### 【0017】

すなわち、本発明の一態様は、第1のフリップフロップと、不揮発性の記憶回路を有する第2のフリップフロップと、を有し、電力が供給されている動作状態において第1のフリップフロップがデータを保持し、電力の供給が停止している休止状態において、第2のフリップフロップがデータを保持し、動作状態から休止状態への移行に際して、第1のフリップフロップから第2のフリップフロップへデータを移し、休止状態から動作状態への復帰に際し、第2のフリップフロップから第1のフリップフロップへデータを移動する回路である。

40

#### 【0018】

また、本発明の一態様は、第1のフリップフロップと、不揮発性の記憶回路を備えた第2のフリップフロップと、を有し、第1のフリップフロップ及び第2のフリップフロップに対する電力の供給が停止される休止状態前に、第1のフリップフロップに保持されたデータを第2のフリップフロップに移動し、休止状態において、第2のフリップフロップによって該データが保持され、休止状態後に、第2のフリップフロップによって第1のフリッ

50

フロップの該データが復元される回路である。

【0019】

また、本発明の一態様は第2のフリップフロップの出力データが入力され、入力されたデータのいずれか一を選択的に出力する選択回路を有し、選択回路の出力データは、第1のフリップフロップに入力され、第1のフリップフロップの出力データは第2のフリップフロップに入力される回路である。

【0020】

上記本発明の一態様によれば、該回路は、第1のフリップフロップ毎に、休止状態においてもデータを保持する不揮発性の第2のフリップフロップが設けられているため、休止状態への移行時において、大量のデータを限られた数の信号線を介して移動するのではなく、第1のフリップフロップ毎に、不揮発性の第2のフリップフロップにデータを移動すればよく、短時間でデータの移動が完了し、速やかに休止状態へと移行することができる。

10

【0021】

休止状態へ速やかに移行できると、頻繁に休止状態への移行が可能となるため、消費電力を低減することができる。

【0022】

また、通常動作時には汎用の第1のフリップフロップを用いることができるため、使用できる材料等に制限が少なく、フリップフロップを高速で動作させることが可能な材料等も選択できるため、動作速度を低下させることなく消費電力を低減できる。

20

【0023】

また、本発明の一態様は、第2のフリップフロップは、半導体層に酸化物半導体を有するトランジスタ及び保持容量を備える記憶回路と、演算部と、を有し、記憶回路は、半導体層に酸化物半導体を有するトランジスタの第1の電極に前記第1のフリップフロップの出力データが入力され、半導体層に酸化物半導体を有するトランジスタの第2の電極は前記保持容量の第1の電極と電気的に接続され、保持容量の第2の電極は接地され、保持容量の第1の電極と半導体層に酸化物半導体を有するトランジスタの第2の電極はデータを保持するノードを構成し、演算部は論理回路を有し、論理回路がノードに電気的に接続するゲート電極を備えたトランジスタを有し、前記ノードによって保持されたデータに基づいて動作を行う回路である。

【0024】

30

上記本発明の一態様によれば、第2のフリップフロップはオフ電流が低減された酸化物半導体を用いたトランジスタと保持容量を用いて記憶回路を構成する。オフ電流が低減されたトランジスタを介して保持容量にデータを保持する構成を備えるため、電力の供給を停止してもデータの保持を行える不揮発性のフリップフロップを実現できる。不揮発性のフリップフロップを有することで、半導体回路を短時間で休止状態へ移行させることができるとなるため、頻繁に休止状態へ移行でき、消費電力を低減することができる。

【0025】

また、本発明の一態様は、半導体層に酸化物半導体を有するトランジスタと、第1のフリップフロップ、第2のフリップフロップの演算部、または第2のフリップフロップが有する保持容量と、が積層している回路である。したがって、第1のフリップフロップに加えて、記憶回路を有する第2のフリップフロップを設けても、回路面積を増大させることなく、高集積化が可能である。

40

【0026】

また、本発明の一態様は、該回路を用いた半導体装置である。

【0027】

また、本発明の一態様は、第1の期間において、第1のフリップフロップが第1のデータを格納し、第1の期間後の、第2の期間において、第1のフリップフロップが第1のデータを出力し、第2のフリップフロップに第1のデータを格納し、第2の期間後の、第3の期間において、回路への電力の供給を停止し、第3の期間後の、第4の期間において、回路への電力の供給を再開し、第2のフリップフロップに格納された第1のデータを出力し

50

、第4の期間後の、第5の期間において、第1のフリップフロップが第1のデータを格納し、第5の期間後の、第6の期間において、第1のフリップフロップが第2のデータを格納する、回路の駆動方法である。

#### 【0028】

また、本発明の一態様は、第2のフリップフロップの出力データが入力され、入力されたデータのいずれか一を選択的に出力する選択回路を有し、第1の期間において、選択回路から第1のデータを出力し、第1のフリップフロップが第1のデータを格納し、第1の期間後の、第2の期間において、第1のフリップフロップが第1のデータを出力し、第2のフリップフロップに第1のデータを格納し、第2の期間後の、第3の期間において、回路への電力の供給を停止し、第3の期間後の、第4の期間において、回路への電力の供給を再開し、第2のフリップフロップに格納された第1のデータを選択回路に出力し、第4の期間後の、第5の期間において、選択回路から第1のデータを第1のフリップフロップに出力し、第1のフリップフロップが第1のデータを格納し、第5の期間後の、第6の期間において、選択回路から第2のデータを出力する、回路の駆動方法である。

10

#### 【0029】

本明細書中において、論理回路とはAND回路やNOT回路等をはじめとする論理演算を行う回路のことである。論理演算回路とも呼ぶ。また、本明細書中では、論理回路をいくつか組み合わせた回路も総称して論理回路と呼ぶことがある。

#### 【0030】

本明細書中において、フリップフロップ(FF)とは制御信号に応じて、1bitの入力データの格納または出力を行う順序論理回路のことである。FFはいくつかの論理回路を組み合わせて構成することができる。

20

#### 【0031】

本明細書中において、半導体回路とは、複数の論理回路、順序論理回路、記憶回路等を組み合わせた回路のことである。

#### 【0032】

また、本明細書において、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順等の特定の順序を示すものではない。また、発明を特定するための事項として固有の名称を示すものではない。

30

#### 【0033】

また、一般的に電圧とは、ある二点間における電位の差(電位差ともいう)ことをいう。しかし、電圧及び電位の値は、回路図などにおいていずれもボルト(V)で表されることがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、ある一点の電位と基準となる電位(基準電位ともいう)との電位差を、該一点の電圧として用いる場合がある。

#### 【発明の効果】

#### 【0034】

本発明によれば、速やかに休止状態への移行及び休止状態からの復帰ができる回路を提供できる。動作速度を低下させずに消費電力を低減させることができる回路を提供できる。または、該回路の駆動方法を提供できる。

40

#### 【図面の簡単な説明】

#### 【0035】

【図1】本発明の一態様の半導体回路を示す図。

【図2】本発明の一態様の不揮発性FFの回路図。

【図3】本発明の一態様の揮発性FFの回路図。

【図4】本発明の一態様の半導体回路の動作を示すタイミングチャート。

【図5】本発明の一態様の半導体回路の断面図、上面図、及び回路図。

【図6】本発明の一態様の半導体回路の作製方法を示した図。

【図7】本発明の一態様の半導体回路の作製方法を示した図。

【図8】本発明の一態様の半導体回路の作製方法を示した図。

50

【図9】本発明の一態様の半導体回路の作製方法を示した図。

【図10】本発明の一態様の半導体装置を示した図。

【発明を実施するための形態】

【0036】

実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しうることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

【0037】

(実施の形態1)

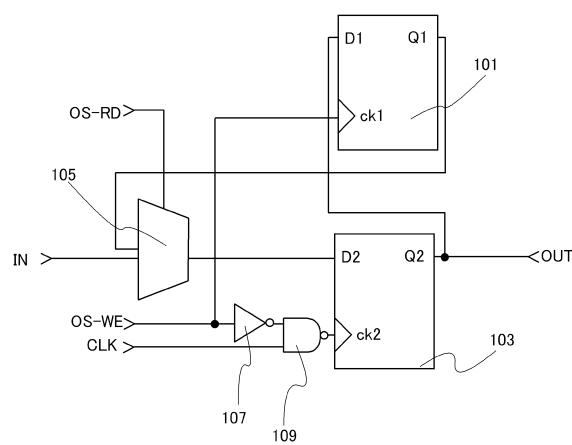

本実施の形態では、本発明の一態様の回路に用いる半導体回路について説明する。本発明の一態様の回路は、本実施の形態に示す半導体回路を複数有する。図1に本実施の形態の半導体回路を示す。

【0038】

図1に示す半導体回路は不揮発性FF101、揮発性FF103、選択回路105、インバータ回路107、NAND回路109を有する。半導体回路には、第1の制御信号(OS RD)、第2の制御信号(OS WE)、クロック信号(CLK)、外部入力データ(IN)、が入力され、外部出力データ(OUT)を半導体回路から出力する。

20

【0039】

不揮発性FF101は入力端子(D1)、出力端子(Q1)、及びクロック入力端子(c k1)を有している。不揮発性FF101の出力端子(Q1)は選択回路105の一方の入力端子と電気的に接続し、不揮発性FF101の入力端子(D1)は揮発性FF103の出力端子(Q2)と電気的に接続し、不揮発性FF101のクロック入力端子(c k1)には第2の制御信号(OS WE)が入力される。不揮発性FF101はクロック入力端子(c k1)にHレベルの信号が入力されたとき、入力端子(D1)に入力されているデータを格納し、クロック入力端子(c k1)にLレベルの信号が入力されたときに格納されたデータを出力端子(Q1)から出力する。不揮発性FF101は電力の供給を停止してもデータの保持を行うことができる記憶回路を有するFFである。

30

【0040】

なお、FFの入力端子とはFFに格納されるデータが入力される配線を指し、FFの出力端子とはFFからデータを出力する配線を指す。FFのクロック入力端子とは、FFの動作をデータの格納から出力、またはデータの出力から格納へと切り替える信号が入力される配線を指す。

【0041】

また、不揮発性FF101はリセット信号入力端子を有していても良い。リセット信号入力端子にリセット信号が入力されることで、クロックとは同期しない任意のタイミングで、FFの内部状態をリセットすることができる。

【0042】

不揮発性FF101に用いる回路は具体的に、図2に示すような回路で構成できる。なお、不揮発性FFの具体的な回路構成及び動作については実施の形態2で詳細を述べる。

40

【0043】

揮発性FF103は入力端子(D2)、出力端子(Q2)とクロック入力端子(c k2)を有している。揮発性FF103の出力端子(Q2)は不揮発性FF101の入力端子(D1)及び半導体回路の出力端子と電気的に接続している。揮発性FF103の入力端子(D2)は選択回路105の出力端子と電気的に接続している。揮発性FF103のクロック入力端子(c k2)にはNAND回路109の出力信号が入力される。揮発性FF103はクロック入力端子(c k2)にLレベルの信号が入力されたとき、入力端子(D2)に入力されているデータを格納し、クロック入力端子にHレベルの信号が入力されたと

50

きに格納されたデータを出力端子 (Q 2) から出力する。

【0044】

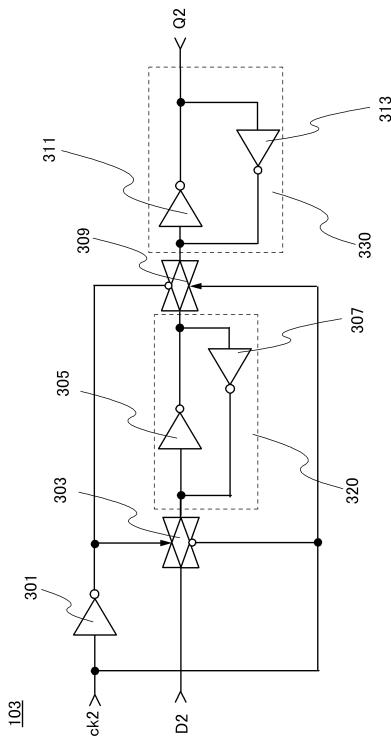

揮発性 FF103 は半導体回路の通常動作時に駆動する回路である。そのため、高速に駆動できるものが好ましい。揮発性 FF103 は例えば図 3 に示した回路で構成することができる。

【0045】

図 3 に示す揮発性 FF103 は第 5 のインバータ回路 301、第 1 のアナログスイッチ 303、第 2 のアナログスイッチ 309、第 1 のラッチ回路 320、及び第 2 のラッチ回路 330、を有する。

【0046】

第 1 のラッチ回路 320 は第 1 のインバータ回路 305 及び第 2 のインバータ回路 307 を有する。第 1 のラッチ回路 320 の入力端子は第 1 のアナログスイッチ 303 と電気的に接続しており、第 1 のラッチ回路 320 の出力端子は第 2 のアナログスイッチ 309 と電気的に接続している。

【0047】

第 1 のラッチ回路 320 に入力されたデータは、第 1 のインバータ回路 305 によって反転されてから、第 2 のアナログスイッチ 309 に出力される。同時に、第 1 のインバータ回路 305 によって反転されたデータは第 2 のインバータ回路 307 にも入力され、第 2 のインバータ回路 307 によって再び反転されてもとのデータと同値になる。第 2 のインバータ回路 307 によって反転されたデータは、再び第 1 のインバータ回路 305 に入力されて、同様の動作を繰り返す。このようにして、第 1 のラッチ回路 320 は入力したデータをフィードバックすることによって、電力が供給されている期間には、格納されたデータを保持する。なお、このように第 1 のアナログスイッチ 303 をオンとし、第 2 のアナログスイッチ 309 をオフとし、第 1 のラッチ回路 320 内にデータが保持されている状態を揮発性 FF にデータを格納した状態と呼ぶ。

【0048】

第 2 のラッチ回路 330 は第 3 のインバータ回路 311 及び第 4 のインバータ回路 313 を有する。第 2 のラッチ回路 330 の入力端子は第 2 のアナログスイッチ 309 と電気的に接続しており、第 2 のラッチ回路 330 の出力端子は出力端子 (Q 2) と電気的に接続している。第 2 のラッチ回路 330 は、第 1 のラッチ回路 320 と同様の構成及び動作によってデータを保持する。また、第 1 のアナログスイッチ 303 をオフとし、第 2 のアナログスイッチ 309 をオンとすると、第 1 のラッチ回路 320、第 2 のラッチ回路 330、揮発性 FF103 の出力端子が導通する。このように、揮発性 FF103 がデータを出力する状態を、揮発性 FF がデータを出力している状態と呼ぶ。

【0049】

揮発性 FF103 は、クロック入力端子 (ck2) から入力される信号に応じて、データの格納及び出力を行う。クロック入力端子 (ck2) に L レベルの信号が入力されたとき、第 1 のアナログスイッチ 303 の制御端子には第 5 のインバータ回路 301 によって反転された H レベルの信号が入力されてオンとなる。なお、アナログスイッチは第 1 の端子と第 2 の端子と、制御端子とを有し、制御端子に入力した信号が H レベルの信号のとき、第 1 の端子から第 2 の端子へ電流を流すオンの状態となり、制御端子に入力した信号が L レベルの信号のとき、第 1 の端子から第 2 の端子への電流の流れを遮断するオフの状態となる。第 2 のアナログスイッチ 309 には H レベルの信号が入力されてオフとなる。したがって、入力端子 (D 2) から入力されたデータが第 1 のラッチ回路 320 に保持される。

【0050】

続いて、クロック入力端子 (ck2) に H レベルの信号が入力されると、第 1 のアナログスイッチ 303 がオフ、第 2 のアナログスイッチ 309 がオンとなるため、第 1 のラッチ回路 320 によって保持されていたデータが第 2 のラッチ回路 330 に入力されて保持されるとともに、出力端子 (Q 2) へと出力される。

10

20

30

40

50

## 【0051】

揮発性FF103においてデータの保持を行うのは、揮発性の論理回路のみであるため、電力の供給が停止するとデータが失われる。なお、本発明に用いる揮発性FFは図3に示す回路に限らず、FFとして動作するものであれば他の構成の回路でもよい。

## 【0052】

なお、クロック信号は、一定の間隔でHレベル(Hレベルの信号、高電源電位レベル、ともいう)とLレベル(Lレベルの信号、低電源電位レベル、ともいう)を繰り返す信号である。フリップフロップにおいては、クロック入力端子から入力される信号であり、フリップフロップの動作をデータの格納から出力へと切り替える制御信号として機能する。

## 【0053】

また、揮発性FF103も、不揮発性FF101と同様に、リセット信号入力端子を有していてもよい。

## 【0054】

図1に示す選択回路105は2つの入力端子を有し、入力端子の一方は不揮発性FF101の出力データが入力され、入力端子の他方は外部入力データ(IN)が入力される。選択回路105は1つの出力端子を有し、出力端子は揮発性FF103の入力端子(D2)と電気的に接続している。選択回路105は揮発性FF103に入力するデータを選択する回路である。選択回路105は2つの入力端子に入力されたデータのどちらか一方を出力端子から出力する。選択回路105が入力された2つのデータのうち、どちらのデータを出力するかは、第1の制御信号(OS RD)によって制御されている。選択回路105は、第1の制御信号としてHレベルの信号が入力されると不揮発性FF101の出力データを出力し、Lレベルの信号が入力されると外部入力データ(IN)を出力する。

## 【0055】

インバータ回路107の入力端子には第2の制御信号(OS WE)が入力される。インバータ回路107の出力端子はNAND回路109の一方の入力端子と電気的に接続している。NAND回路109の他方の入力端子にはクロック信号(CLK)が入力される。NAND回路109の出力端子は揮発性FF103のクロック入力端子(CLK2)と電気的に接続している。そのため、揮発性FF103のクロック入力端子には第2の制御信号(OS WE)がLレベルのときには、クロック信号(CLK)と反転した信号が入力され、第2の制御信号(OS WE)がHレベルのときは、クロック信号(CLK)の値に関わらず、常にHレベルの信号が入力される。

## 【0056】

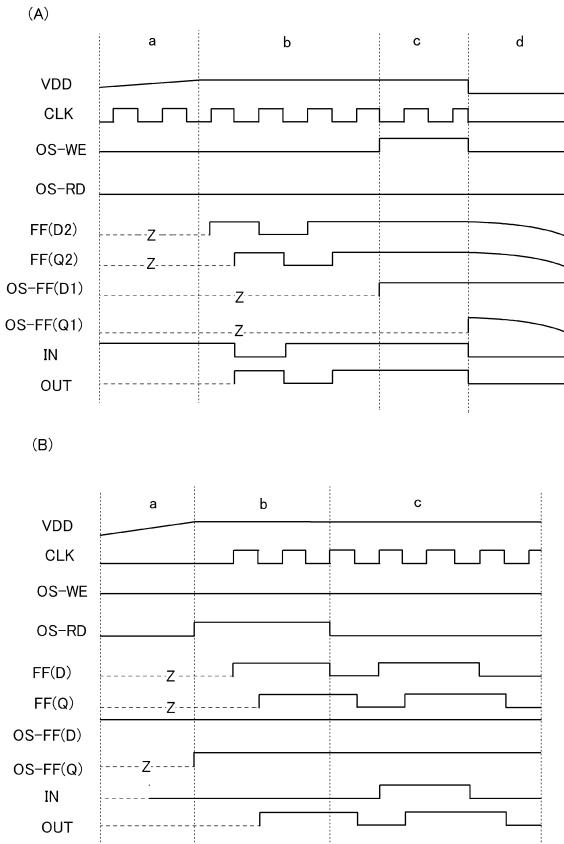

続いて、本実施の形態の半導体回路の動作方法について図4のタイミングチャートをもとに説明する。なお、ここでは説明の簡略化のために、Lレベル=0Vとするが、これに限らない。

## 【0057】

図4のタイミングチャートにおいて、VDDは半導体回路の電源を示している。半導体回路の電源を入れると、半導体回路内の論理回路へ電力が供給されるため、揮発性FF103はデータの格納及び出力の動作を行うことができるが、電源が切れて、論理回路への電力の供給が停止すると、データの格納及び出力の動作も停止し、それまで格納されていたデータが消失してしまう。ただし、本実施の形態で示す不揮発性FF101は電力の供給が停止し、論理回路が動作を停止してもデータを保持することができるFFである。

## 【0058】

図4のタイミングチャートにおいて、FF(D2)は揮発性FF103に格納されているデータを示し、FF(Q2)は揮発性FF103が出力するデータを示している。また、OS FF(D1)は不揮発性FF101に格納されているデータを示し、OS FF(Q1)は不揮発性FF101が出力するデータを示している。

## 【0059】

図4(A)のタイミングチャートは、電源を入れて半導体回路を起動させる期間a、揮発性FF103に通常動作を行わせる期間b、休止状態への移行に際し不揮発性FF101

10

20

30

40

50

に揮発性 FF103 のデータを移動して保存させる期間 c 、半導体回路の電源を切って休止状態となる期間 d を示している。

【 0 0 6 0 】

図 4 ( B ) のタイミングチャートは、半導体回路の休止状態からの復帰に際し、電源を入れて起動する期間 a 、不揮発性 FF に保存していたデータを揮発性 FF に移動して、揮発性 FF に休止状態以前のデータを復元させる期間 b 、揮発性 FF が再び通常動作を行う期間 c を示している。

【 0 0 6 1 】

本実施の形態の半導体回路は通常動作時には揮発性 FF103 に外部入力データ ( I N ) が入力され、揮発性 FF が外部入力データ ( I N ) を格納し、揮発性 FF103 に格納されたデータを外部出力データ ( O U T ) として出力する。

10

【 0 0 6 2 】

まず、半導体回路が起動するまでの初期動作について示す。図 4 ( A ) の期間 a に示すように、半導体回路の電源 V D D を入れる。

【 0 0 6 3 】

このとき、クロック信号 ( C L K ) も入力されているが、半導体回路が完全に起動するまではクロック信号 ( C L K ) が入力されても、揮発性 FF103 によるデータの格納及び出力の動作は起こらない。このとき揮発性 FF103 の内部状態については不定 ( Z ) である。揮発性 FF がリセット信号入力端子を有する場合、このタイミングでリセット信号を入力し、揮発性 FF の内部状態を規定してもよい。

20

【 0 0 6 4 】

半導体回路は電源 V D D が完全に立ち上ると動作が始まる。第 1 の期間 ( 図 4 ( A ) の期間 b ) において、揮発性 FF103 はクロック信号 ( C L K ) に応じて通常動作を行う。このとき、第 1 の制御信号 ( O S - R D ) は L レベルの信号を保っているため、選択回路 105 から揮発性 FF103 の入力端子 ( D 2 ) に外部入力データ ( I N ) が入力されている。このとき、クロック信号 ( C L K ) が H レベルとなると、揮発性 FF103 は外部入力データ ( I N ) を格納し、クロック信号 ( C L K ) が L レベルとなると、格納したデータを出力する。

【 0 0 6 5 】

このとき、出力されたデータは半導体回路の外部出力データ ( O U T ) として取り出されるとともに、不揮発性 FF101 の入力端子 ( D 1 ) へと出力される。しかし、第 2 の制御信号 ( O S - W E ) は L レベルを保っているため、不揮発性 FF の入力端子 ( D 1 ) に入力されたデータは不揮発性 FF101 に格納されず、不揮発性 FF101 の内部状態は不定のままである。

30

【 0 0 6 6 】

続く第 2 の期間 ( 図 4 ( A ) の期間 c ) は、半導体回路が休止状態へと移行するために、揮発性 FF103 から不揮発性 FF101 へとデータを移動する期間である。

【 0 0 6 7 】

第 2 の期間ではまず、第 2 の制御信号 ( O S - W E ) に H レベルの信号を入力する。第 2 の制御信号 ( O S - W E ) に H レベルの信号が入力されたことによって、不揮発性 FF101 のクロック入力端子 ( c k 1 ) 及び揮発性 FF103 のクロック入力端子 ( c k 2 ) に H レベルの信号が入力される。

40

【 0 0 6 8 】

揮発性 FF103 のクロック入力端子 ( c k 2 ) に H レベルの信号が入力されると、揮発性 FF103 は、格納されているデータを出力する。

【 0 0 6 9 】

不揮発性 FF101 のクロック入力端子 ( c k 1 ) に H レベルの信号が入力されると、不揮発性 FF101 は入力端子 ( D 1 ) に入力されているデータを格納する。このとき、不揮発性 FF101 の入力端子 ( D 1 ) に入力されているデータは、揮発性 FF103 が第 2 の制御信号 ( O S - W E ) に応じて出力したデータである。したがって、不揮発性 FF

50

101には揮発性FF103がクロック入力端子(ck1)にHレベルの信号が入力される直前に出力したデータが格納される。

【0070】

揮発性FF103から不揮発性FF101へのデータの移動は高速に行うことができる。これは、FFに保持されているデータが1bitのデータであり、非常に短い時間でデータの移動が完了するからである。

【0071】

続いて、第3の期間(図4(A)の期間d)で、半導体回路の電源を切る。ここで、半導体回路の電源を切るとは半導体回路内の論理回路に対する電力の供給及び半導体回路に入力していた全ての信号、データの供給を停止することである。

10

【0072】

このとき、第2の制御信号(OS-WE)がHレベルからLレベル(0V)に切り替わるため、不揮発性FF101は格納されているデータを出力する動作へと切り替わる。ただし、同時に半導体回路の電源が切られて不揮発性FF101内の論理回路への電力の供給も停止する。したがって、図4(A)の期間dに示すように、不揮発性FF101の動作が切り替わり、OS-FF(Q1)がHレベルとなり、その後、電力の供給が停止して、不揮発性FFからのデータの出力が停止する。なお、実際には、不揮発性FF101の動作の格納から出力への切り替え及び電力の供給の停止は短時間で行われるため、不揮発性FF101からデータの出力はない。しかし、図4(A)の期間dでは不揮発性FF101の動作が切り替わったことを明示するため、OS-FF(Q1)がHレベルになった後に、電力供給が停止するように示した。

20

【0073】

図4(A)の期間dでは、半導体回路に含まれる論理回路に対する電力の供給が停止されるため、論理回路が動作を停止する。したがって、揮発性FF103の内部に格納されているデータ(FF(D2))は消失する。しかし、不揮発性FF101は電力の供給が停止してもデータを保持することができるため、不揮発性FF101に格納されたデータ(OS-FF(D1))は保持され続ける。

30

【0074】

このとき不揮発性FF101によって保持されているデータは揮発性FF103が休止状態に移行する直前に出力したデータである。

【0075】

以上の過程で、半導体回路は休止状態への移行に際して、揮発性FFが出力したデータを不揮発性FFに移動し、電力の供給が停止されている期間も不揮発性FFにデータの保持を行わせるため、データを保持したまま休止状態へ移行することができる。また、FF単位でデータの移動を行ったため高速で休止状態へ移行することができる。

【0076】

続く第4の期間(図4(B)の期間a)で、半導体回路を休止状態から復帰させるため、再び半導体回路の電源を入れて動作を再開させる。このとき不揮発性FF101は揮発性FF103が休止状態に移行する直前に出力したデータを保持している。

40

【0077】

半導体回路が起動し、半導体回路内の論理回路が動作を開始すると、不揮発性FF101に格納されているデータは選択回路105へと出力される。

【0078】

続く第5の期間(図4(B)の期間b)において、選択回路105がデータを揮発性FF103に出力し、揮発性FF103がデータを格納する。第5の期間では、まず、第1の制御信号(OS-RD)にHレベルの信号を入力する。第1の制御信号(OS-RD)にHレベルの信号が入力されると、選択回路105は不揮発性FF101から入力されたデータを出力する。

【0079】

次に、クロック信号(CLK)を入力する。クロック信号(CLK)はNAND回路10

50

9の一方の入力端子に入力される。このとき、NAND回路109の他方の入力端子には第2の制御信号(OS-WE)がインバータ回路107によって反転された信号、すなわちHレベルの信号が入力されている。そのため、NAND回路109の出力端子からはクロック信号(CLK)が反転された信号が出力される。NAND回路から出力されたデータは揮発性FF103のクロック入力端子(ck2)に入力され、揮発性FF103はデータの格納及び出力を行う。

【0080】

クロック信号(CLK)がHレベルになったときに、揮発性FF103は入力端子(D2)に入力されているデータを格納する。このとき、揮発性FF103の入力端子(D2)に入力されているデータは、選択回路105を介して不揮発性FF101が出力したデータである。10

【0081】

不揮発性FF101が出力しているデータは休止状態への移行に際して、揮発性FF103から移動したデータである。つまり、ここで、揮発性FF103には休止状態へ移行する直前に保持していたデータが格納され、休止状態以前の状態へと復元されることになる。。

【0082】

続く第6の期間(図4(B)の期間c)では、選択回路105から外部入力データ(IN)を揮発性FF103に入力することで、半導体回路の通常動作を再開させる。

【0083】

第6の期間は、まず、第1の制御信号(OS-RD)にLレベルの信号を入力する。第1の制御信号(OS-RD)にLレベルの信号が入力されたことによって、選択回路105は外部入力データ(IN)を出力するようになる。20

【0084】

したがって、揮発性FF103の入力端子には外部入力データ(IN)が入力され、クロック入力端子(ck2)に入力される信号に応じて、外部出力データ(OUT)を出力する。

【0085】

上述したとおり、本実施の形態の半導体回路は通常動作時には高速で駆動できる揮発性FFを用いてデータの格納及び出力をを行い、休止状態へ移行する際、揮発性FFに格納されているデータを不揮発性FFに移動してから電源を切り、電力の供給を停止している間は不揮発性FFにデータを保持させる。また、休止状態からの復帰時には、不揮発性FFに保持されているデータを揮発性FFへ移動することで、揮発性FFを休止状態に移行する以前の状態へと復元させてから、通常動作を行わせる。30

【0086】

本発明の回路は、上述した半導体回路を複数備えた回路である。例えば、本実施の形態で示した半導体回路を複数並べてデータの保持を行うレジスタや、それらを基本要素として積層したメモリ等である。該複数の半導体回路のそれぞれに上述した動作をさせることで、休止状態へ移行する際、FF毎にデータの移動を行えばよく、短時間でデータの移動が完了し、速やかに休止状態へ移行できる。40

【0087】

よって、本実施の形態に示した半導体回路を用いることによって、速やかに休止状態への移行及び休止状態からの復帰ができる回路を提供できる。動作速度を低下させずに消費電力を低減させることができる回路を提供できる。また、該回路の駆動方法を提供できる。

【0088】

本実施の形態は他の実施の形態と組み合わせることができる。

【0089】

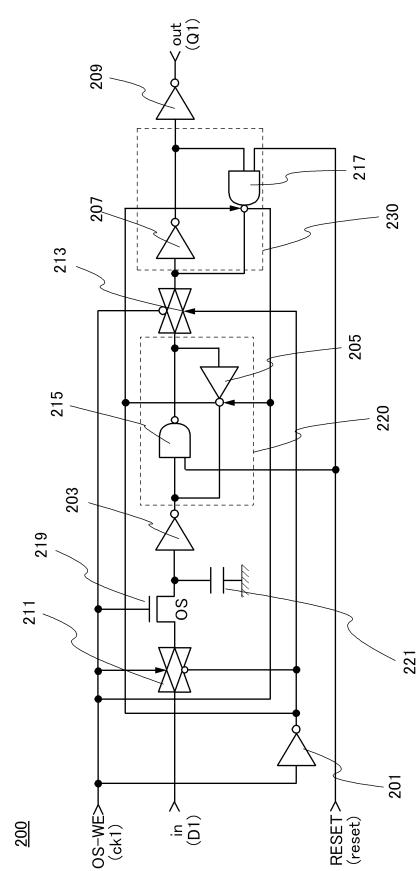

(実施の形態2)

本実施の形態では、実施の形態1に示した不揮発性FFの回路構成について示す。図2は不揮発性FFの回路構成の一例である。50

## 【0090】

不揮発性FFは記憶回路と、演算部を有する。図2に示す不揮発性FF200は記憶回路として半導体層に酸化物半導体を有するトランジスタ219及び保持容量221を有し、演算部に第1のインバータ回路203、第2のインバータ回路209、第1のアナログスイッチ211、第2のアナログスイッチ213、第1のラッチ回路220、及び第2のラッチ回路230を有する。

## 【0091】

トランジスタ219はゲート電極、第1の電極、第2の電極を備え、半導体層に酸化物半導体を有するトランジスタである。トランジスタ219のチャネル形成領域は、高純度化された酸化物半導体を含んでいるため、オフ電流が著しく低いという特性を有している。

10

## 【0092】

トランジスタ219のゲート電極は不揮発性FF200のクロック入力端子(c k 1)と電気的に接続しており、第2の制御信号(O S - W E)が入力される。トランジスタ219の第1の電極は第1のアナログスイッチ211と電気的に接続されて、トランジスタ219の第2の電極は保持容量221の第1の電極及び、第1のインバータ回路203の入力端子と電気的に接続している。

## 【0093】

保持容量221は第1の電極、第2の電極を有する。保持容量221の第1の電極はトランジスタ219の第2の電極及び第1のインバータ回路203の入力端子と電気的に接続している。保持容量221の第2の電極は接地されている。

20

## 【0094】

半導体層に酸化物半導体を有するトランジスタ219の第2の電極及び保持容量221の第1の電極は、電荷が保持されるノードを構成する。

## 【0095】

第1のインバータ回路203は上記ノードに電気的に接続するゲート電極を備えたトランジスタを有する。該トランジスタのゲート電極、半導体層に酸化物半導体を有するトランジスタ219の第2の電極及び保持容量221の第1の電極によってノードが形成されることで、電力の供給が停止しても保持容量221に電荷を保存することが可能である。第1のインバータ回路203の出力端子は第1のラッチ回路220の入力端子と電気的に接続する。

30

## 【0096】

なお、第1のインバータ回路203に含まれるトランジスタは、半導体層に酸化物半導体を用いる必要はない。不揮発性FF200において、トランジスタ219以外のトランジスタは、データの保持に関わらないため、シリコン等の高速に駆動できるトランジスタを用いる方が好ましい。

## 【0097】

第1のラッチ回路220は第3のインバータ回路205及びNAND回路215を有する。第1のラッチ回路220の入力端子は第1のインバータ回路203の出力端子と電気的に接続しており、第1のラッチ回路220の出力端子は第2のアナログスイッチ213と電気的に接続している。第3のインバータ回路205はクロック入力端子(c k 1)からの信号に応じて動作するクロックドインバータ回路である。そのため、第1のラッチ回路はクロック信号と同期して動作を行うので、より正確にデータの入力及び出力を行うことができる。なお、第3のインバータ回路205としては、クロック信号と同期する機能を有していない通常のインバータ回路を用いることも可能である。

40

## 【0098】

第2のラッチ回路230は第4のインバータ回路207及びNAND回路217を有する。第2のラッチ回路230の入力端子は第2のアナログスイッチ213と電気的に接続しており、第2のラッチ回路230の出力端子は第2のインバータ回路209の入力端子と電気的に接続している。NAND回路217はクロックドNAND回路である。

## 【0099】

50

また、本実施の形態の不揮発性FF200はリセット入力端子(reset)を有する。NAND回路215の一方の入力端子及びNAND回路217の一方の入力端子は不揮発性FF200のリセット入力端子(reset)と電気的に接続しており、第1のラッチ回路220及び第2のラッチ回路230にリセット信号(RESET)を入力している。リセット信号(RESET)としてLレベルの信号が入力されると、ラッチ回路内に保持していたデータを書き換えることができる。そのため、クロックのタイミングとは無関係に、任意のタイミングで不揮発性FF200のデータをリセットすることができる。

#### 【0100】

なお、リセット信号(RESET)には、リセットを行うとき以外はHレベルの信号を入力する。リセット信号としてHレベルの信号が入力されている間、NAND回路215及びNAND回路217はそれぞれ、他方の入力端子に入力されたデータを反転して出力する動作を行う。

10

#### 【0101】

第1のラッチ回路220に入力されたデータは、NAND回路215によって反転されながら、第2のアナログスイッチ213に出力される。同時に、NAND回路215によって反転されたデータは第3のインバータ回路205にも入力され、第3のインバータ回路205によって再び反転されてもとのデータと同値になる。第3のインバータ回路205に反転されたデータは再びNAND回路215に入力されて、同様の動作を繰り返す。このようにして、第1のラッチ回路220は入力したデータをフィードバックすることによってデータを保持する。第2のラッチ回路も同様にしてデータの保持を行う。

20

#### 【0102】

第2のインバータ回路209の入力端子は第2のラッチ回路230の出力端子と電気的に接続しており、第2のインバータ回路209の出力端子は出力端子(Q1)と電気的に接続しており、出力データ(out)を出力する。

#### 【0103】

第1のアナログスイッチ211及び第2のアナログスイッチ213はそれぞれ、第1の端子と第2の端子と、制御端子とを有する。第1のアナログスイッチ211及び第2のアナログスイッチ213は制御端子に入力した信号がHレベルの信号のとき、第1の端子から第2の端子へ電流を流すオンの状態となり、制御端子に入力した信号がLレベルの信号のとき、第1の端子から第2の端子への電流の流れを遮断するオフの状態となる。第1のアナログスイッチ211の第1の端子は入力端子(D1)と電気的に接続し、入力データ(in)が入力され、第2の端子は半導体層に酸化物半導体を有するトランジスタ219の第1の電極と電気的に接続している。第1のアナログスイッチ211の制御端子はクロック入力端子(CLK)と電気的に接続し、第2の制御信号(OS-WE)が入力される。第2のアナログスイッチ213の第1の端子は第1のラッチ回路220の出力端子と電気的に接続し、第2のアナログスイッチ213の第2の端子は第2のラッチ回路230の入力端子と電気的に接続している。第2のアナログスイッチ213の制御端子は第5のインバータ回路201と電気的に接続している。

30

#### 【0104】

第5のインバータ回路201は、クロック入力端子(ck1)と電気的に接続し、第2の制御信号(OS-WE)が入力される。第2の制御信号(OS-WE)は第5のインバータ回路201によって反転された後、第2のアナログスイッチ213及びNAND回路217に入力される。

40

#### 【0105】

第1のアナログスイッチ211及び第2のアナログスイッチ213は第2の制御信号(OS-WE)によってオンとオフの切り替えを行う。具体的には、第2の制御信号(OS-WE)がHレベルの信号の時、第1のアナログスイッチ211にはHレベルの信号が入力され、オンとなる。このとき、第2のアナログスイッチ213は、第5のインバータ回路201によって反転されたLレベルの信号が入力されオフとなる。第2の制御信号がLレベルの信号のときは反対に、第1のアナログスイッチ211がオフとなり、第2のアナロ

50

グスイッチ 213 がオンとなる。第1のアナログスイッチ 211 及び第2のアナログスイッチ 213 には常に異なる信号が入力されるため、一方がオンの時、他方は必ずオフとなり、両方が同時にオンになることはない。

#### 【0106】

次に、不揮発性 FF200 にデータを格納し(図4(A)の期間c)、電力の供給が停止してもデータを保持(図4(A)の期間d)し、再び電源が入り(図4(B)の期間a)、データを出力する(図4(B)の期間b)といった一連の動作について説明する。

#### 【0107】

まず、不揮発性 FF200 にデータを格納する方法について説明する。なお、本実施の形態では、入力データ(in)及び出力データ(out)については、実施の形態1で示したデータが入出力されるものとして、その詳細の説明は省略する。

10

#### 【0108】

不揮発性 FF200 にデータを格納する際、まず、第2の制御信号(OS WE)としてHレベルの信号を入力する(図4(A)の期間c)。第2の制御信号(OS WE)にHレベルの信号を入力すると、第2のアナログスイッチ213には、第5のインバータ回路201によって反転されたLレベルの信号が入力される。Lレベルの信号が入力されると、第2のアナログスイッチ213はオフとなり、第2のラッチ回路230へはデータが入力されない。一方、第1のアナログスイッチ211にはHレベルの信号が入力されてオンになる。

20

#### 【0109】

また、同時にトランジスタ219のゲート電極にもHレベルの信号が入力される。トランジスタ219は酸化物半導体を半導体層に用いたトランジスタであって、Nチャネル型のトランジスタである。したがって、このときトランジスタ219はオンとなり、第1のアナログスイッチ211を通過した入力データ(in)がトランジスタ219を介して、保持容量221及び第1のインバータ回路203に入力される。

#### 【0110】

保持容量221に入力データが入力されると、入力データ(in)が保持される。

#### 【0111】

第1のインバータ回路203にデータが入力されると、入力したデータを反転して、第1のラッチ回路220に出力する。

30

#### 【0112】

第1のラッチ回路220に入力されたデータは、NAND回路215によって反転されてから、第2のアナログスイッチ213に出力される。しかし、このとき、第2のアナログスイッチ213はオフであるため、第2のラッチ回路230へはデータが入力されない。

#### 【0113】

同時に、NAND回路215によって反転されたデータは第3のインバータ回路205にも入力され、第3のインバータ回路205によって再び反転され、元のデータと同値になる。第3のインバータ回路205に反転されたデータは再びNAND回路215に入力されて、同様の動作を繰り返す。このようにして、第1のラッチ回路220は入力したデータをフィードバックすることによってデータを保持する。

40

#### 【0114】

このように第1のアナログスイッチ211をオンとし、第2のアナログスイッチ213をオフとし、第1のラッチ回路内にデータが保持されている状態を不揮発性FFにデータを格納した状態と呼ぶ。

#### 【0115】

また、反対に第1のアナログスイッチ211をオフとし、第2のアナログスイッチ213をオンとして、第1のラッチ回路220、第2のラッチ回路230、第2のインバータ回路209及び不揮発性FF200の出力端子(Q1)が導通し、不揮発性FF200が信号を出力する状態を、不揮発性FFがデータを出力している状態と呼ぶ。

#### 【0116】

50

次に、第2の制御信号(O S W E)にLレベルの信号を入力する(図4(A)の期間d)。第2の制御信号にLレベルの信号が入力されると、第1のアナログスイッチ211及び、トランジスタ219はオフとなる。トランジスタ219がオフとなると、トランジスタの第2の電極と保持容量の第1の電極によって構成されたノード、及び第1のインバータ回路203の入力端子である、トランジスタのゲート電極が電気的に絶縁した浮遊状態となる。

【0117】

半導体層に酸化物半導体を用いたトランジスタ219のオフ電流は、シリコン半導体などで形成されるトランジスタの10万分の1以下であるため、トランジスタ219のリークによるノードに蓄積された電荷の消失は無視できるほど少ない。つまり、半導体層に酸化物半導体を用いたトランジスタ219により、保持容量221に蓄積された電荷は損なわれることが無く、電力の供給が無くても信号の保持が可能な不揮発性FFを実現することが可能である。

【0118】

例えばトランジスタ219の室温でのオフ電流が10zA(1zA(ゼプトアンペア))は $1 \times 10^{-21} A$ 以下であり、保持容量221の容量値が10fF程度である場合には、少なくとも $10^4$ 秒以上のデータの保持が可能である。なお、当該保持時間が、トランジスタ特性や容量値によって変動することはいうまでもない。

【0119】

こうして、浮遊状態のノードに電荷が保持されているため、半導体回路の電源を切っても不揮発性FF200はデータを保持することができる。よって、ここで半導体回路の電源を切る。

【0120】

このとき、第2のアナログスイッチ213の制御端子にはHレベルの信号が入力されており、オンとなって第1のラッチ回路220及び第2のラッチ回路230は導通する。しかし、論理回路への電力の供給が停止したため、第1のラッチ回路220が保持しているデータは第2のラッチ回路230へは入力されない。また、第1のラッチ回路220に保持されていたデータは、第1のラッチ回路220が有するNAND回路215及び第3のインバータ回路205のリーク電流によって損なわれるため、第1のラッチ回路220に保持されていたデータは消失してしまう。

【0121】

続いて、不揮発性FF200に格納されたデータを出力する動作について説明する。

【0122】

半導体回路に再び電源を入れ、不揮発性FF200内の論理回路への電力の供給を再開する(図4(B)の期間a)。

【0123】

論理回路に電力が供給されると、不揮発性FF200内の論理回路が動作を開始する。このとき、第2の制御信号(O S W E)はLレベルのままであるので、第1のアナログスイッチはオフであり、入力データは入力されない。

【0124】

したがって、保持容量221に保持されていたデータが第1のインバータ回路203に入力される。保持容量221は電源が切れている間も入力データ(in)を保持していたため、このとき第1のインバータ回路203に入力されるデータは、休止状態への移行前の入力データ(in)と同等のデータである。

【0125】

さらに、第1のインバータ回路203によって反転されたデータが第1のラッチ回路220に入力されて、第1のラッチ回路220のNAND回路215によって反転され、出力される。

【0126】

このとき、第2のアナログスイッチ213がオンであるため、第1のラッチ回路220か

10

20

30

40

50

ら第2のラッチ回路230へデータが出力される。データは第2のラッチ回路230によって反転された後、第2のインバータ回路209によって反転され、不揮発性FF200の出力端子から出力される。

【0127】

不揮発性FF200から出力される出力データ(out)は、不揮発性FFに入力した入力データが第1のインバータ回路203、第1のラッチ回路220、第2のラッチ回路230及び第2のインバータ回路209によって、計4回反転されたデータである。そのため、出力データ(out)は不揮発性FF200に入力した入力データ(in)と等しい値になる。

【0128】

以上が、不揮発性FFに入力データが格納され、電力の供給を停止しても、入力データを保持し、再び電源が入ったときに入力データと同値の出力データを出力する方法である。

【0129】

なお、本実施の形態では、不揮発性FFの記憶部として半導体層に酸化物半導体を有するトランジスタ及び保持容量を組み合わせた構成としたが、本発明の不揮発性FFが有する記憶回路はこれに限らず、E PROM(Electricaly Programmable Read Only Memory)、EEPROM(Electricaly Erasable and Programmable Read Only Memory)、フローティングゲート、強誘電体メモリ(FeRAM)、磁気メモリ(MRAM)、相変化メモリ(PrAM)、抵抗変化メモリ(ReRAM)、原子スイッチ(Atom Switch)等の不揮発性メモリとして機能するものであれば良い。

【0130】

電力の供給を停止してもデータを保持することができる不揮発性FFを揮発性FF毎に作製することによって、休止状態への移行時のデータの移動及び休止から復帰する際のデータの復元が短時間で完了し、頻繁に休止状態へと移行することが可能なため、消費電力の低減された半導体回路を提供できる。

【0131】

本実施の形態に示した不揮発性FFを実施の形態1に示した半導体回路に用いることによって、速やかに休止状態に移行できる回路を提供できる。または、短時間で休止状態から復帰させることによって、動作速度を低下させることなく、消費電力を低減させることができる半導体回路を提供できる。また、該回路の駆動方法を提供できる。

【0132】

本実施の形態は他の実施の形態と組み合わせることができる。

【0133】

(実施の形態3)

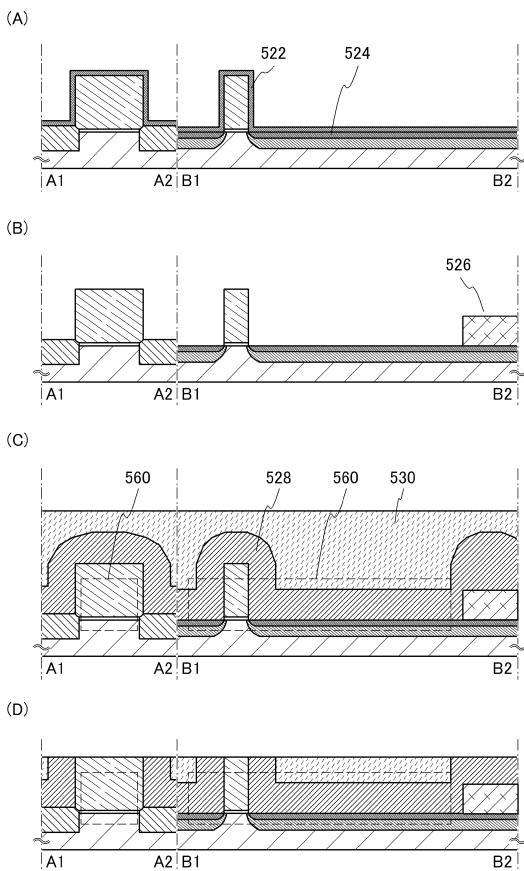

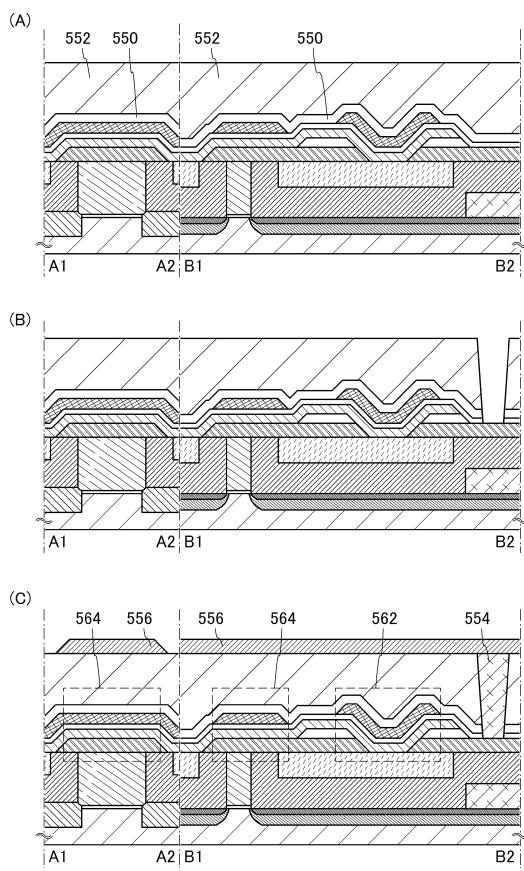

本実施の形態では、本発明の一態様に係る回路の構成及び作製方法について、図5乃至図9を用いて説明する。

【0134】

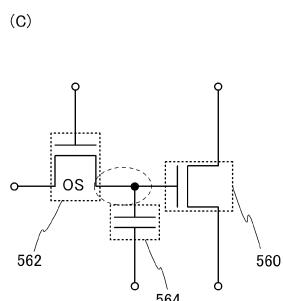

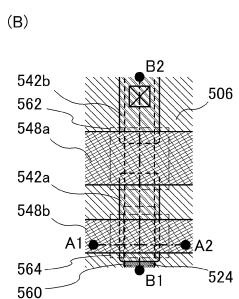

図5(C)は本実施の形態で示す半導体回路の回路構成である。本実施の形態の半導体回路は酸化物半導体を半導体層に用いたトランジスタ562と、酸化物半導体以外の材料を半導体層に用いたトランジスタ560と、保持容量564を有する。本実施の形態で示す半導体回路は実施の形態1及び実施の形態2で示した回路または半導体回路の一部を示したものである。例えば、トランジスタ562、保持容量564及びトランジスタ560はそれぞれ、図2に示す不揮発性FF200が有するトランジスタ219、保持容量221、第1のインバータ回路203が有するトランジスタに使用することができる。

【0135】

図5(C)に示した半導体回路において、半導体層に酸化物半導体を用いたトランジスタ562を、半導体層にシリコンを用いたトランジスタ560の上に積層した構成、及びその作製方法について述べる。トランジスタを積層することで回路の平面面積が縮小されて、高集積化が可能となる。

10

20

30

40

50

## 【0136】

<半導体装置の断面構成及び平面構成>

図5は、半導体回路の構成の一例である。図5(A)には半導体回路の断面を、図5(B)には半導体回路の上面をそれぞれ示す。ここで、図5(A)は、図5(B)のA1-A2及びB1-B2における断面に相当する。図5(A)及び図5(B)に示される半導体回路は、下部に第1の半導体材料を用いたトランジスタ560を有し、上部に第2の半導体材料を用いたトランジスタ562を有するものである。ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料に、高速動作が容易である酸化物半導体以外の材料を用い、揮発性FF及び不揮発性FFの演算部に備えるトランジスタを作製する。また、第2の半導体材料を長時間の電荷保持を可能とする酸化物半導体とすることで、不揮発性FFの記憶回路が有するトランジスタを作製することができる。10

## 【0137】

第1の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いるのが好ましい。他に、有機半導体材料などを用いてもよい。本実施の形態では、シリコンを用いる。

## 【0138】

なお、上記トランジスタは、いずれもNチャネル型トランジスタであるものとして説明するが、Pチャネル型トランジスタを用いることができるのではない。また、開示する発明の技術的な本質は、情報を保持するために酸化物半導体のようなオフ電流を十分に低減することが可能な半導体材料をトランジスタ562に用いる点にあるから、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。20

## 【0139】

図5におけるトランジスタ560は、半導体材料(例えば、シリコンなど)を含む基板500に設けられたチャネル形成領域516と、チャネル形成領域516を挟むように設けられた不純物領域520と、不純物領域520に接する金属化合物領域524と、チャネル形成領域516上に設けられたゲート絶縁層508と、ゲート絶縁層508上に設けられたゲート電極510と、を有する。なお、図において、明示的にはソース電極やドレイン電極を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極やドレイン電極と表現することがある。つまり、本明細書において、ソース電極との記載には、ソース領域が含まれる。また、ドレイン電極との記載には、ドレイン領域が含まれる。30

## 【0140】

トランジスタ560の金属化合物領域524の一部には、電極526が接続されている。ここで、電極526は、トランジスタ560のソース電極やドレイン電極として機能する。また、基板500上にはトランジスタ560を囲むように素子分離絶縁層506が設けられており、トランジスタ560上に絶縁層528及び絶縁層530が設けられている。なお、高集積化を実現するためには、図5(A)に示すようにトランジスタ560がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ560の特性を重視する場合には、ゲート電極510の側面にサイドウォール絶縁層を設け、そのサイドウォール絶縁層と重畳する領域に形成された不純物濃度が異なる領域を含めて不純物領域520を設けても良い。40

## 【0141】

図5におけるトランジスタ562は、絶縁層530上に設けられたソース電極またはドレイン電極542a及びソース電極またはドレイン電極542bと、ソース電極またはドレイン電極542a及びソース電極またはドレイン電極542bと電気的に接続されている酸化物半導体層544と、ソース電極またはドレイン電極542a、ソース電極またはド

10

20

30

40

50

レイン電極 542b、及び酸化物半導体層 544 を覆うゲート絶縁層 546 と、ゲート絶縁層 546 上に酸化物半導体層 544 と重疊するように設けられたゲート電極 548a と、ソース電極またはドレイン電極 542a と酸化物半導体層 544との間の、ゲート電極 548a の一部と重疊する領域に設けられた絶縁層 543a と、ソース電極またはドレイン電極 542b と酸化物半導体層 544との間の、ゲート電極 548a の一部と重疊する領域に設けられた絶縁層 543b と、を有する。なお、ソース電極またはドレイン電極と、ゲート電極との間の容量を低減するためには、絶縁層 543a 及び絶縁層 543b を設けることが望ましいが、絶縁層 543a 及び絶縁層 543b を設けない構成とすることも可能である。

## 【0142】

酸化物半導体層 544 の水素濃度は  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、望ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より望ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とすることが望ましい。なお、上述の酸化物半導体層 544 中の水素濃度は、二次イオン質量分析法 (S I M S : Secondary Ion Mass Spectroscopy) で測定されるものである。このように、水素濃度が十分に低減され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層 544 では、キャリア濃度を低減することが容易である。例えば、キャリア濃度が  $1 \times 10^{12}$  / cm<sup>3</sup> 未満、望ましくは、 $1 \times 10^{11}$  / cm<sup>3</sup> 未満、より望ましくは  $1 \times 10^{10}$  / cm<sup>3</sup> 未満となる。

## 【0143】

なお、酸化物半導体層中に含まれる、Li、Naなどのアルカリ金属、及びCaなどのアルカリ土類金属などの不純物は低減されていることが好ましい。具体的には、酸化物半導体層中に含まれるこれらの不純物濃度は、 $2 \times 10^{16}$  / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  / cm<sup>3</sup> 以下であることが好ましい。これらの金属元素は電気陰性度が小さく、酸化物半導体層中の酸素と結合しやすいため、酸化物半導体層中にキャリアパスが形成され低抵抗化 (N型化) してしまうおそれがある。

## 【0144】

なお、図5のトランジスタ 562 では、微細化に起因して素子間に生じるリーケを抑制するために、島状に加工された酸化物半導体層 544 を用いているが、島状に加工されていない構成を採用しても良い。酸化物半導体層 544 を島状に加工しない場合には、加工の際のエッティングによる酸化物半導体層 544 の汚染を防止できる。

## 【0145】

図5における保持容量 564 は、ソース電極またはドレイン電極 542a、酸化物半導体層 544、ゲート絶縁層 546、及び電極 548b、で構成される。すなわち、ソース電極またはドレイン電極 542a は、保持容量 564 の一方の電極として機能し、電極 548b は、保持容量 564 の他方の電極として機能することになる。

## 【0146】

なお、図5の保持容量 564 では、酸化物半導体層 544 とゲート絶縁層 546 を積層させることにより、ソース電極またはドレイン電極 542a と、電極 548b との間の絶縁性を十分に確保することができる。もちろん、十分な容量を確保するために、酸化物半導体層 544 を有しない構成の保持容量 564 を採用しても良い。また、絶縁層 543a と同様に形成される絶縁層を有する構成の保持容量 564 を採用しても良い。さらに、容量が不要の場合は、保持容量 564 を設けない構成とすることも可能である。

## 【0147】

なお、トランジスタ 562 及び保持容量 564 において、ソース電極またはドレイン電極 542a、及びソース電極またはドレイン電極 542b の端部は、テーパーであることが好ましい。ソース電極またはドレイン電極 542a、ソース電極またはドレイン電極 542b の端部をテーパーとすることにより、酸化物半導体層 544 の被覆性が向上し、段切れを防止することができるためである。ここで、テーパー角は、例えば、30°以上 60° 以下とする。なお、テーパー角とは、テーパー形状を有する層 (例えば、ソース電極ま

10

20

30

40

50

たはドレン電極 542a) を、その断面(基板の表面と直交する面)に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜角を示す。

【0148】

本実施の形態では、トランジスタ 562 及び保持容量 564 が、トランジスタ 560 と重畳するように設けられている。このような、平面レイアウトを採用することにより、高集積化が可能である。例えば、本発明の一態様の半導体回路において、不揮発性 FF の記憶回路が有する酸化物半導体を用いたトランジスタ及び保持容量を、揮発性 FF または不揮発性 FF の演算部が有するトランジスタと重畳することにより、酸化物半導体を用いたトランジスタ及び保持容量を、揮発性 FF または不揮発性 FF の演算部が有するトランジスタの横に配置した回路構成に比べ、平面面積を縮小することができる。したがって、本発明の一態様の回路を高集積化することができる。10

【0149】

トランジスタ 562 及び保持容量 564 の上には、絶縁層 550 が設けられており、絶縁層 550 上には絶縁層 552 が設けられている。そして、ゲート絶縁層 546、絶縁層 550、絶縁層 552 などに形成された開口には、電極 554 が設けられ、絶縁層 552 上には電極 554 と接続する配線 556 が形成される。なお、開示する発明はこれに限定されない。

【0150】

<半導体装置の作製方法>

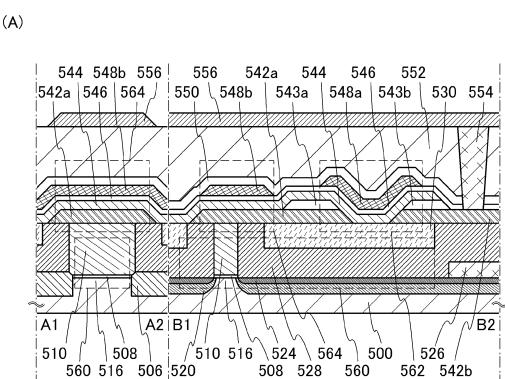

次に、上記半導体装置の作製方法の一例について説明する。以下では、はじめに下部のトランジスタ 560 の作製方法について図 6 及び図 7 を参照して説明し、その後、上部のトランジスタ 562 及び保持容量 564 の作製方法について図 8 及び図 9 を参照して説明する。20

【0151】

<下部のトランジスタの作製方法>

まず、半導体材料を含む基板 500 を用意する(図 6 (A) 参照)。半導体材料を含む基板 500 としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI 基板などを適用することができる。ここでは、半導体材料を含む基板 500 として、単結晶シリコン基板を用いる場合の一例について示すものとする。なお、一般に「SOI 基板」は、絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板も含むものとする。つまり、「SOI 基板」が有する半導体層は、シリコン半導体層に限定されない。また、SOI 基板には、ガラス基板などの絶縁基板上に絶縁層を介して半導体層が設けられた構成のものも含まれるものとする。30

【0152】

半導体材料を含む基板 500 として、特に、シリコンなどの単結晶半導体基板を用いる場合には、半導体装置の読み出し動作を高速化することができるため好適である。

【0153】

基板 500 上には、素子分離絶縁層を形成するためのマスクとなる保護層 502 を形成する(図 6 (A) 参照)。保護層 502 としては、例えば、酸化シリコンや窒化シリコン、酸窒化シリコンなどを材料とする絶縁層を用いることができる。なお、この工程の前後において、トランジスタのしきい値電圧を制御するために、n 型の導電性を付与する不純物元素や P 型の導電性を付与する不純物元素を基板 500 に添加してもよい。半導体がシリコンの場合、n 型の導電性を付与する不純物としては、例えば、リンや砒素などを用いることができる。また、P 型の導電性を付与する不純物としては、例えば、硼素、アルミニウム、ガリウムなどを用いることができる。40

【0154】

次に、上記の保護層 502 をマスクとしてエッティングを行い、保護層 502 に覆われていない領域(露出している領域)の、基板 500 の一部を除去する(図 6 (B) 参照)。当50

該エッチングには、ドライエッチングを用いるのが好適であるが、ウェットエッチングを用いても良い。エッチングガスやエッチング液については被エッチング材料に応じて適宜選択することができる。

【0155】

次に、半導体領域504を覆うように絶縁層を形成し、半導体領域504に重畳する領域の絶縁層を選択的に除去することで、素子分離絶縁層506を形成する。当該絶縁層は、酸化シリコンや窒化シリコン、酸窒化シリコンなどを用いて形成される。絶縁層の除去方法としては、CMP（化学的機械的研磨）などの研磨処理やエッチング処理などがあるが、そのいずれを用いても良い。これにより他の半導体領域と分離された半導体領域504が形成される。なお、半導体領域504の形成後、または、素子分離絶縁層506の形成後には、上記保護層502を除去する。

10

【0156】

なお、素子分離絶縁層506の形成方法として、絶縁層を選択的に除去する方法の他、酸素を打ち込むことにより絶縁性の領域を形成する方法などを用いることもできる。

【0157】

次に、半導体領域504の表面に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

【0158】

絶縁層は後のゲート絶縁層となるものであり、例えば、半導体領域504表面の熱処理（熱酸化処理や熱窒化処理など）によって形成することができる。熱処理に代えて、高密度プラズマ処理を適用しても良い。高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などのうちいずれかの混合ガスを用いて行うことができる。もちろん、CVD法やスパッタリング法等を用いて絶縁層を形成しても良い。当該絶縁層は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ )）、窒素が添加されたハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ )）、窒素が添加されたハフニウムアルミネート（ $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ )）等を含む単層構造または積層構造とすることが望ましい。また、絶縁層の厚さは、例えば、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

20

【0159】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料、これらの金属材料を含む合金材料、これらの金属材料または合金材料を積層した層を用いて形成することができる。例えば、銅マグネシウム-アルミニウム合金層に銅を含む金属層を積層した構成とすることによって密着性を高めることができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。

30

【0160】

その後、絶縁層及び導電材料を含む層を選択的にエッチングして、ゲート絶縁層508、ゲート電極510を形成する（図6（C）参照）。

40

【0161】

次に、半導体領域504にリン（P）やヒ素（As）などを添加して、チャネル形成領域516及び不純物領域520を形成する（図6（D）参照）。なお、ここではn型トランジスタを形成するためにリンやヒ素を添加しているが、p型トランジスタを形成する場合には、硼素（B）やアルミニウム（Al）などの不純物元素を添加すればよい。ここで、添加する不純物の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その濃度を高くすることが望ましい。

【0162】

50

なお、ゲート電極 510 の周囲にサイドウォール絶縁層を形成して、不純物元素が異なる濃度で添加された不純物領域を形成しても良い。

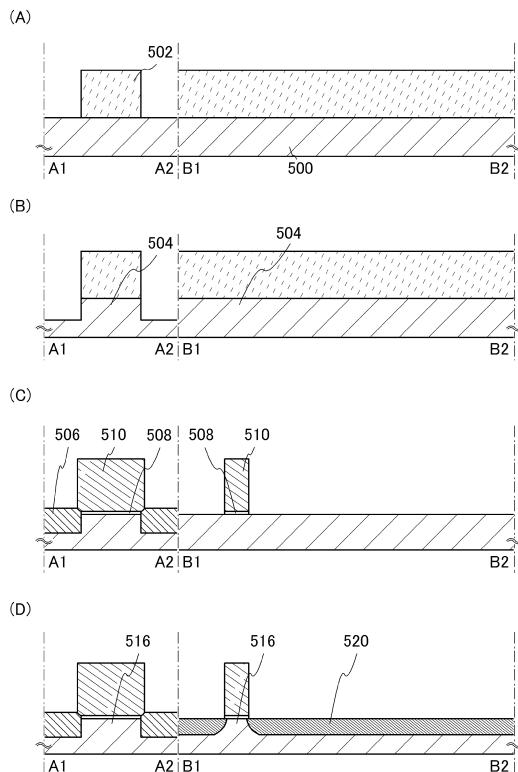

【0163】

次に、ゲート電極 510、不純物領域 520 等を覆うように金属層 522 を形成する（図 7（A）参照）。当該金属層 522 は、真空蒸着法やスパッタリング法、スピンドル法などの各種成膜方法を用いて形成することができる。金属層 522 は、半導体領域 504 を構成する半導体材料と反応することによって低抵抗な金属化合物となる金属材料を用いて形成することが望ましい。このような金属材料としては、例えば、チタン、タンタル、タンゲステン、ニッケル、コバルト、白金等がある。

【0164】

次に、熱処理を施して、上記金属層 522 と半導体材料とを反応させる。これにより、不純物領域 520 に接する金属化合物領域 524 が形成される（図 7（A）参照）。なお、ゲート電極 510 として多結晶シリコンなどを用いる場合には、ゲート電極 510 の金属層 522 と接触する部分にも、金属化合物領域が形成されることになる。

【0165】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、上記の金属化合物領域は、金属材料と半導体材料との反応により形成されるものであり、十分に導電性が高められた領域である。当該金属化合物領域を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。なお、金属化合物領域 524 を形成した後には、金属層 522 は除去する。

【0166】

次に、金属化合物領域 524 の一部と接する領域に、電極 526 を形成する（図 7（B）参照）。電極 526 は、例えば、導電材料を含む層を形成した後に、当該層を選択的にエッチングすることで形成される。導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タンゲステン等の金属材料、これらの金属材料を含む合金材料、これらの金属材料または合金材料を積層した層を用いて形成することができる。例えば、銅 マグネシウム - アルミニウム合金層に銅を含む金属層を積層した構成とすることによって密着性を高めることができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD 法、スパッタリング法、スピンドル法などの各種成膜方法を用いることができる。

【0167】

この場合、例えば、開口を含む領域に PVD 法によりチタン膜を薄く形成し、CVD 法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する方法を適用することができる。ここで、PVD 法により形成されるチタン膜は、被形成面の酸化膜（自然酸化膜など）を還元し、下部電極など（ここでは金属化合物領域 524）との接触抵抗を低減させる機能を有する。また、その後に形成される窒化チタン膜は、導電性材料の拡散を抑制するバリア機能を備える。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

【0168】

次に、上述の工程により形成された各構成を覆うように、絶縁層 528、絶縁層 530 を形成する（図 7（C）参照）。絶縁層 528 や絶縁層 530 は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。特に、絶縁層 528 や絶縁層 530 に誘電率の低い（low-k）材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁層 528 や絶縁層 530 には、これらの材料を用いた多孔性の絶縁層を適用しても良い。多孔性の絶縁層では、密度の高い絶縁層と比較して誘電率が低下するため、電極や配線に起因する容量をさらに低減することが可能である。また、絶縁層 528 や絶縁層 530 は、ポリイミド、アクリル等の有機絶縁材料を用いて形成する

10

20

30

40

50

ことも可能である。なお、ここでは、絶縁層 528 と絶縁層 530 の積層構造としているが、開示する発明の一態様はこれに限定されない。1層としても良いし、3層以上の積層構造としても良い。

【0169】

トランジスタ 562 及び保持容量 564 の形成前の処理として、絶縁層 528 や絶縁層 530 に CMP 処理を施して、ゲート電極 510 の上面を露出させる（図 7（D）参照）。ゲート電極 510 の上面を露出させる処理としては、CMP 処理の他にエッチング処理などを適用することも可能であるが、トランジスタ 562 の特性を向上させるために、絶縁層 528 や絶縁層 530 の表面は可能な限り平坦にしておくことが望ましい。

【0170】

以上により、半導体材料を含む基板 500 を用いたトランジスタ 560 が形成される。このようなトランジスタ 560 は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを揮発性 FF のトランジスタとして用いることで、半導体回路の通常動作を高速に行なうことができる。

【0171】

なお、上記の各工程の前後には、さらに電極や配線、半導体層、絶縁層などを形成する工程を含んでいても良い。例えば、配線の構造として、絶縁層及び導電層の積層構造である多層配線構造を採用して、高度に集積化した半導体装置を実現することも可能である。

【0172】

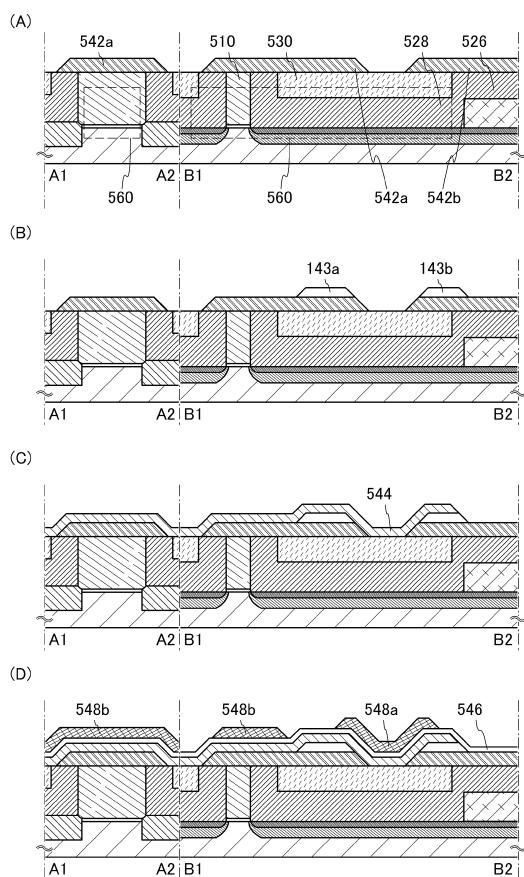

<上部のトランジスタの作製方法>

次に、ゲート電極 510、絶縁層 528、絶縁層 530 などの上に導電層を形成し、該導電層を選択的にエッチングして、ソース電極またはドレイン電極 542a、ソース電極またはドレイン電極 542b を形成する（図 8（A）参照）。

【0173】

導電層は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

【0174】

導電層は、単層構造であっても良いし、2 層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された 2 層構造、窒化チタン膜上にチタン膜が積層された 2 層構造、チタン膜とアルミニウム膜とチタン膜とが積層された 3 層構造などが挙げられる。なお、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有するソース電極またはドレイン電極 542a、及びソース電極またはドレイン電極 542b への加工が容易であるというメリットがある。

【0175】

また、導電層は、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、インジウムスズ酸化物（In<sub>2</sub>O<sub>3</sub> - SnO<sub>2</sub>）、インジウム亜鉛酸化物（In<sub>2</sub>O<sub>3</sub> - ZnO）、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

【0176】

導電層のエッチングは、形成されるソース電極またはドレイン電極 542a、及びソース電極またはドレイン電極 542b の端部が、テーパーとなるように行なうことが好ましい。ここで、テーパー角は、例えば、30° 以上 60° 以下であることが好ましい。ソース電極またはドレイン電極 542a、ソース電極またはドレイン電極 542b の端部をテーパーとなるようにエッチングすることにより、後に形成されるゲート絶縁層 546 の被覆性

10

20

30

40

50

を向上し、段切れを防止することができる。

【0177】

上部のトランジスタのチャネル長 (L) は、ソース電極またはドレイン電極 542a、及びソース電極またはドレイン電極 542b の下端部の間隔によって決定される。なお、チャネル長 (L) が 25 nm 未満のトランジスタを形成する場合に用いるマスク形成の露光を行う際には、数 nm ~ 数 10 nm と波長の短い超紫外線 (Extreme Ultraviolet) を用いるのが望ましい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長 (L) を、10 nm 以上 1000 nm (1 μm) 以下とすることも可能であり、回路の動作速度を高めることが可能である。また、微細化によって、半導体装置の消費電力を低減することも可能である。 10

【0178】

なお、絶縁層 528 や絶縁層 530 の上には、下地として機能する絶縁層を設けても良い。当該絶縁層は、PVD 法や CVD 法などを用いて形成することができる。

【0179】

次に、ソース電極またはドレイン電極 542a の上に絶縁層 543a を、ソース電極またはドレイン電極 542b の上に絶縁層 543b を、それぞれ形成する (図 8 (B) 参照)。絶縁層 543a 及び絶縁層 543b は、ソース電極またはドレイン電極 542a や、ソース電極またはドレイン電極 542b を覆う絶縁層を形成した後、当該絶縁層を選択的にエッチングすることにより形成できる。また、絶縁層 543a 及び絶縁層 543b は、後に形成されるゲート電極の一部と重畳するように形成する。このような絶縁層を設けることにより、ゲート電極と、ソース電極またはドレイン電極との間の容量を低減することが可能である。 20

【0180】

絶縁層 543a や絶縁層 543b は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。特に、絶縁層 543a や絶縁層 543b に誘電率の低い (low-k) 材料を用いることで、ゲート電極と、ソース電極またはドレイン電極との間の容量を十分に低減することが可能になるため好ましい。なお、絶縁層 543a や絶縁層 543b には、これらの材料を用いた多孔性の絶縁層を適用しても良い。多孔性の絶縁層では、密度の高い絶縁層と比較して誘電率が低下するため、ゲート電極と、ソース電極またはドレイン電極との間の容量をさらに低減することが可能である。 30

【0181】

なお、ゲート電極と、ソース電極またはドレイン電極との間の容量を低減させるという点では、絶縁層 543a 及び絶縁層 543b を形成するのが好適であるが、当該絶縁層を設けない構成とすることも可能である。

【0182】

次に、ソース電極またはドレイン電極 542a、及びソース電極またはドレイン電極 542b を覆うように酸化物半導体層を形成した後、当該酸化物半導体層を選択的にエッチングして酸化物半導体層 544 を形成する (図 8 (C) 参照)。 40

【0183】

酸化物半導体層に用いる酸化物半導体としては、四元系金属酸化物である In - Sn - Ga - Zn - O 系酸化物半導体や、三元系金属酸化物である In - Ga - Zn - O 系酸化物半導体、In - Sn - Zn - O 系酸化物半導体、In - Al - Zn - O 系酸化物半導体、Sn - Ga - Zn - O 系酸化物半導体、Al - Ga - Zn - O 系酸化物半導体、Sn - Al - Zn - O 系酸化物半導体や、二元系金属酸化物である In - Zn - O 系酸化物半導体、Sn - Zn - O 系酸化物半導体、Al - Zn - O 系酸化物半導体、Zn - Mg - O 系酸化物半導体、Sn - Mg - O 系酸化物半導体、In - Mg - O 系酸化物半導体、In - Ga - O 系酸化物半導体や、In - O 系酸化物半導体、Sn - O 系酸化物半導体、Zn - O 系酸化物半導体などを用いることができる。また、上記酸化物半導体層に酸化珪素を含ませてもよい。酸化物半導体層に結晶化を阻害する酸化珪素 (SiO<sub>x</sub> (X > 0)) を含ま 50

ることで、製造プロセス中において酸化物半導体層の形成後に加熱処理した場合に、結晶化してしまうのを抑制することができる。なお、酸化物半導体層は非晶質な状態であることが好ましく、一部結晶化していてもよい。ここで、例えば、In - Ga - Zn - O系酸化物半導体とは、インジウム (In)、ガリウム (Ga)、亜鉛 (Zn) を有する酸化物膜、という意味であり、その組成比はとくに問わない。また、InとGaとZn以外の元素を含んでもよい。

【0184】

また、酸化物半導体層 544 には、化学式  $InM O_3 (ZnO)_m$  ( $m > 0$ 、且つ  $m$  は自然数でない) で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、Mn 及びCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。また、酸化物半導体として、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、nは整数) で表記される材料を用いてもよい。

10

【0185】

酸化物半導体は、好ましくはInを含有する酸化物半導体、さらに好ましくは、In、及びGaを含有する酸化物半導体である。本実施の形態では、非晶質構造の酸化物半導体層を、In - Ga - Zn - O系の金属酸化物ターゲットを用いるスパッタ法により形成することとする。

【0186】

酸化物半導体層 544 をスパッタリング法で作製するためのターゲットとしては、例えば、 $In : Ga : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ ) あるいは  $In : Ga : Zn = 2 : 2 : 1$  ( $= 2/5 : 2/5 : 1/5$ ) の原子数比のIn - Ga - Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Sn : Zn = 2 : 1 : 3$  ( $= 1/3 : 1/6 : 1/2$ ) あるいは  $In : Sn : Zn = 2 : 1 : 5$  ( $= 1/4 : 1/8 : 5/8$ ) の原子数比のIn - Sn - Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

20

【0187】

なお、例えば、In、Ga、Znの原子数比が  $In : Ga : Zn = a : b : c$  ( $a + b + c = 1$ ) である酸化物の組成が、原子数比が  $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$ ) の酸化物の組成の近傍であるとは、a、b、cが、 $(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$  を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

30

【0188】

また、酸化物半導体としてIn - Zn - O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、 $In : Zn = 50 : 1 \sim 1 : 2$  (モル数比に換算すると  $In_2O_3 : ZnO = 25 : 1 \sim 1 : 4$ )、好ましくは  $In : Zn = 20 : 1 \sim 1 : 1$  (モル数比に換算すると  $In_2O_3 : ZnO = 10 : 1 \sim 1 : 2$ )、さらに好ましくは  $In : Zn = 1.5 : 1 \sim 1.5 : 1$  (モル数比に換算すると  $In_2O_3 : ZnO = 3 : 4 \sim 1.5 : 2$ ) とする。例えば、In - Zn - O系酸化物半導体の形成に用いるターゲットは、原子数比が  $In : Zn : O = X : Y : Z$  のとき、 $Z > 1.5X + Y$  とする。

40

【0189】

金属酸化物ターゲット中の金属酸化物の相対密度は80%以上、好ましくは95%以上、さらに好ましくは99.9%以上である。相対密度の高い金属酸化物ターゲットを用いることにより、緻密な構造の酸化物半導体層を形成することが可能である。また、ターゲットの純度は99.99%以上が好ましく、特にNa、Li等のアルカリ金属及びCaなどのアルカリ土類金属などの不純物は低減されているものが好ましい。

【0190】

酸化物半導体層の形成雰囲気は、希ガス (代表的にはアルゴン) 雰囲気、酸素雰囲気、または、希ガス (代表的にはアルゴン) と酸素との混合雰囲気とするのが好適である。具体的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度1ppm以下 (望ましくは濃度10ppb以下) にまで除去された高純度ガス雰囲気を用いるのが好適である

50

。具体的には、露点 - 60 以下の高純度ガスが好ましい。

【0191】

酸化物半導体層の形成の際には、例えば、減圧状態に保持された処理室内に被処理物を保持し、被処理物の温度が 100 以上 550 未満、好ましくは 200 以上 400 以下となるように被処理物を熱する。または、酸化物半導体層の形成の際の被処理物の温度は、室温 (25 ± (プラスマイナス) 10) としてもよい。そして、処理室内の水分を除去しつつ、水素や水などが除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体層を形成する。被処理物を熱しながら酸化物半導体層を形成することにより、酸化物半導体層に含まれる不純物を低減することができる。また、スパッタによる損傷を軽減することができる。処理室内の水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排気することで、処理室から水素や水などを除去することができるため、酸化物半導体層中の不純物濃度を低減できる。10

【0192】

また、スパッタリング装置の処理室のリークレートを  $1 \times 10^{-10} \text{ Pa} \cdot \text{m}^3 / \text{秒}$  以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として吸着型の真空ポンプを用いることで、排気系からアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等の逆流を低減することができる。20

【0193】

酸化物半導体層の形成条件としては、例えば、被処理物とターゲットとの間との距離が 170 nm、圧力が 0.4 Pa、直流 (DC) 電力が 0.5 kW、雰囲気が酸素 (酸素 100%) 雰囲気、またはアルゴン (アルゴン 100%) 雰囲気、または酸素とアルゴンの混合雰囲気、といった条件を適用することができる。

【0194】

なお、パルス直流 (DC) 電源を用いると、ごみ (成膜時に形成される粉状の物質など) を低減でき、膜厚分布も均一となるため好ましい。酸化物半導体層の厚さは、1 nm 以上 50 nm 以下、好ましくは 1 nm 以上 30 nm 以下、より好ましくは 1 nm 以上 10 nm 以下とする。このような厚さの酸化物半導体層を用いることで、微細化に伴う短チャネル効果を抑制することが可能である。ただし、適用する酸化物半導体材料や、半導体装置の用途などにより適切な厚さは異なるから、その厚さは、用いる材料や用途などに応じて選択することもできる。30

【0195】

なお、酸化物半導体層をスパッタ法により形成する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、形成表面 (例えば絶縁層 530 の表面) の付着物を除去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおいては、スパッタターゲットにイオンを衝突させるところを、逆に、基板の処理表面にイオンを衝突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を入力して、被処理物付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などによる雰囲気を適用してもよい。40

【0196】

その後、酸化物半導体層に対して、熱処理 (第 1 の熱処理) を行うことが望ましい。この第 1 の熱処理によって酸化物半導体層中の、過剰な水素 (水や水酸基を含む) を除去し、酸化物半導体層の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。第 1 の熱処理の温度は、例えば、150 以上 650 以下、好ましくは 200 以上 500 以下とする。

【0197】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、50

450 、1時間の条件で行うことができる。この間、酸化物半導体層は大気に触れさせず、水や水素の混入が生じないようにする。

【0198】

熱処理装置は電気炉に限らず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、G R T A ( G a s R a p i d T h e r m a l A n n e a l i n g ) 装置、L R T A ( L a m p R a p i d T h e r m a l A n n e a l i n g ) 装置等のR T A ( R a p i d T h e r m a l A n n e a l i n g ) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

【0199】

例えば、第1の熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出すG R T A 処理を行ってもよい。G R T A 処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。酸素を含む雰囲気において第1の熱処理を行うことで、酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである。

【0200】

なお、不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6 N ( 99.9999 % ) 以上、好ましくは7 N ( 99.99999 % ) 以上(すなわち、不純物濃度が1 ppm以下、好ましくは0.1 ppm以下)とする。

【0201】

ところで、上述の熱処理(第1の熱処理)には水素や水などを除去する効果があるから、当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該脱水化処理や、脱水素化処理は、酸化物半導体層の形成後やゲート絶縁層の形成後、ゲート電極の形成後、などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

【0202】

酸化物半導体層のエッティングは、上記熱処理の前、または上記熱処理の後のいずれにおいて行っても良い。また、素子の微細化という観点からはドライエッティングを用いるのが好適であるが、ウェットエッティングを用いても良い。エッティングガスやエッティング液については被エッティング材料に応じて適宜選択することができる。なお、素子におけるリークなどが問題とならない場合には、酸化物半導体層を島状に加工しないで用いても良い。

【0203】

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3 nm以上15 nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、酸素と希ガスの混合気体、窒素と希ガスの混合気体、窒素と酸素と希ガスの混合気体、または乾燥空気の雰囲気下で450以上850以下、好ましくは550以上750以下の第1の加熱処理を行い、表面を含む領域に結晶領域(板状結晶を含む)を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450以上850以下好ましくは600以上700以下の第2の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結

10

20

30

40

50

晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

【0204】

また、酸化物半導体層を成膜する際に、酸化物半導体がc軸に配向する温度に基板を加熱しながら成膜を行うことにより、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。このような成膜方法を用いることにより、プロセスを短縮することができる。基板を加熱する温度は、150以上450以下とするのがよい。ただし、成膜装置によって他の成膜条件が異なるためこれに合わせて適宜設定すればよいが、例えば、スパッタリング装置で成膜する際の基板温度を250以上として成膜すればよい。

【0205】

次に、酸化物半導体層544に接するゲート絶縁層546を形成し、その後、ゲート絶縁層546上において酸化物半導体層544と重畠する領域にゲート電極548aを形成し、ソース電極またはドレイン電極542aと重畠する領域に電極548bを形成する(図8(D)参照)。

【0206】

ゲート絶縁層546は、CVD法やスパッタ法等を用いて形成することができる。また、ゲート絶縁層546は、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>(x>0, y>0))、などを含むように形成するのが好適である。ゲート絶縁層546は、単層構造としても良いし、積層構造としても良い。また、その厚さは特に限定されないが、半導体装置を微細化する場合には、トランジスタの動作を確保するために薄くするのが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

【0207】

上述のように、ゲート絶縁層を薄くすると、トンネル効果などに起因するゲートリークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁層546に、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>(x>0, y>0))、などの高誘電率(high-k)材料を用いると良い。high-k材料をゲート絶縁層546に用いることで、電気的特性を確保しつつ、ゲートリークを抑制するために膜厚を大きくすることが可能になる。なお、high-k材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

【0208】

ゲート絶縁層546の形成後には、不活性ガス雰囲気下、または酸素雰囲気下で第2の熱処理を行うのが望ましい。熱処理の温度は、200以上450以下、好ましくは250以上350以下である。例えば、窒素雰囲気下で250、1時間の熱処理を行えばよい。第2の熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。また、ゲート絶縁層546が酸素を含む場合、酸化物半導体層544に酸素を供給し、該酸化物半導体層544の酸素欠損を補填することもできる。

【0209】

なお、本実施の形態では、ゲート絶縁層546の形成後に第2の熱処理を行っているが、第2の熱処理のタイミングはこれに限定されない。例えば、ゲート電極の形成後に第2の熱処理を行っても良い。また、第1の熱処理に続けて第2の熱処理を行っても良いし、第1の熱処理に第2の熱処理を兼ねさせても良いし、第2の熱処理に第1の熱処理を兼ねさせても良い。

【0210】

10

20

30

40

50

上述のように、第1の熱処理と第2の熱処理の少なくとも一方を適用することで、酸化物半導体層544を、その主成分以外の不純物が極力含まれないように高純度化することができる。

【0211】

ゲート電極548a及び電極548bは、ゲート絶縁層546上に導電層を形成した後に、当該導電層を選択的にエッチングすることによって形成することができる。ゲート電極548a及び電極548bとなる導電層は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形成することができる。詳細は、ソース電極またはドレイン電極542aなどの場合と同様であり、これらの記載を参照できる。

【0212】

次に、ゲート絶縁層546、ゲート電極548a、及び電極548b上に、絶縁層550及び絶縁層552を形成する(図9(A)参照)。絶縁層550及び絶縁層552は、PVD法やCVD法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。

【0213】

なお、絶縁層550や絶縁層552には、誘電率の低い材料や、誘電率の低い構造(多孔性の構造など)を用いることが望ましい。絶縁層550や絶縁層552の誘電率を低くすることにより、配線や電極などの間に生じる容量を低減し、動作の高速化を図ることができるためである。

【0214】

なお、本実施の形態では、絶縁層550と絶縁層552の積層構造としているが、開示する発明の一態様はこれに限定されない。1層としても良いし、3層以上の積層構造としても良い。また、絶縁層を設けない構成とすることも可能である。

【0215】

なお、上記絶縁層552は、その表面が平坦になるように形成することが望ましい。表面が平坦になるように絶縁層552を形成することで、半導体装置を微細化した場合などにおいても、絶縁層552上に、電極や配線などを好適に形成することができるためである。なお、絶縁層552の平坦化は、CMP(化学的機械的研磨)などの方法を用いて行うことができる。

【0216】

次に、ゲート絶縁層546、絶縁層550、絶縁層552に、ソース電極またはドレイン電極542bにまで達する開口を形成する(図9(B)参照)。当該開口の形成は、マスクなどを用いた選択的なエッチングにより行われる。

【0217】

その後、上記開口に電極554を形成し、絶縁層552上に電極554に接する配線556を形成する(図9(C)参照)。

【0218】

電極554は、例えば、開口を含む領域にPVD法やCVD法などを用いて導電層を形成した後、エッチング処理やCMPといった方法を用いて、上記導電層の一部を除去することにより形成することができる。

【0219】

より具体的には、例えば、開口を含む領域にPVD法によりチタン膜を薄く形成し、CVD法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、被形成面の酸化膜(自然酸化膜など)を還元し、下部電極など(ここではソース電極またはドレイン電極542b)との接触抵抗を低減させる機能を有する。また、その後に形成される窒化チタン膜は、導電性材料の拡散を抑制するバリア機能を備える。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

【0220】

10

20

30

40

50

なお、上記導電層の一部を除去して電極 554 を形成する際には、電極 554 の表面が平坦になるように加工することが望ましい。例えば、開口を含む領域にチタン膜や窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する場合には、その後の C M P 处理によって、不要なタンゲステン、チタン、窒化チタンなどを除去すると共に、電極 554 の表面の平坦性を向上させることができる。また、このような平坦性を向上させる処理によって、電極 554 の表面を含む表面全体を平坦化することができる。このように、電極 554 を含む表面全体を平坦化することにより、後の工程において、良好な電極、配線、絶縁層、半導体層などを形成することが可能となる。

【 0221 】

配線 556 は、スパッタ法をはじめとする P V D 法や、プラズマ C V D 法などの C V D 法を用いて導電層を形成した後、当該導電層をパターニングすることによって形成される。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は、ソース電極またはドレイン電極 542a などと同様である。

【 0222 】

以上により、酸化物半導体層 544 を用いたトランジスタ 562 、及び保持容量 564 が完成する(図 9 (C) 参照)。

【 0223 】

本実施の形態において示すトランジスタ 562 では、酸化物半導体層 544 の水素濃度は、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、望ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より望ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。また、酸化物半導体層 544 のキャリア密度は、一般的なシリコンウェハにおけるキャリア密度 ( $1 \times 10^{14}$  / cm<sup>3</sup> 程度) と比較して、十分に小さい値(例えば、 $1 \times 10^{12}$  / cm<sup>3</sup> 未満、より好ましくは、 $1.45 \times 10^{10}$  / cm<sup>3</sup> 未満)をとる。そして、トランジスタ 562 の室温(25)でのオフ電流(ここでは、単位チャネル幅(1 μm)あたりの値)は 100 zA (1 zA (ゼプトアンペア) は  $1 \times 10^{-21}$  A) 以下、望ましくは 10 zA 以下となる。

【 0224 】

このようなトランジスタを用いることで、オフ電流が低減され、電源を供給しなくとも、信号の保持ができる半導体回路が得られる。

【 0225 】

また、半導体層に酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとを重畳するように形成することで、回路面積の増大を抑制し、より一層の高集積化が実現される。また、本実施の形態において示す半導体回路では、配線を共通化することも可能であり、集積度が十分に高められた半導体回路を実現することができる。

【 0226 】

本実施の形態で示した回路構成を、実施の形態 2 で示した不揮発性 F F に用いることによって、酸化物半導体を半導体層に用いたトランジスタ及び保持容量を、他の半導体材料を半導体層に用いたトランジスタと積層して作製することができるので、不揮発性 F F を高集積化して作製することができる。

【 0227 】

同様にして、揮発性 F F が有する他の半導体材料を半導体層に用いたトランジスタと酸化物半導体材料を用いたトランジスタ、または、不揮発性 F F と揮発性 F F を積層して形成することも可能となり、揮発性 F F 每に不揮発性 F F を設けても、回路面積を増大させることのない回路を作製することができる。

【 0228 】

実施の形態 1 または実施の形態 2 で示した、半導体回路、不揮発性フリップフロップ、ま

10

20

30

40

50

たはそれらの回路の一部を本実施の形態のように積層して作製することで、回路面積を増大させることなく、揮発性F/Fに不揮発性F/Fを設けることができ、速やかに休止状態へ移行できる回路を高度な集積度で実現することができる。

#### 【0229】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0230】

##### (実施の形態4)

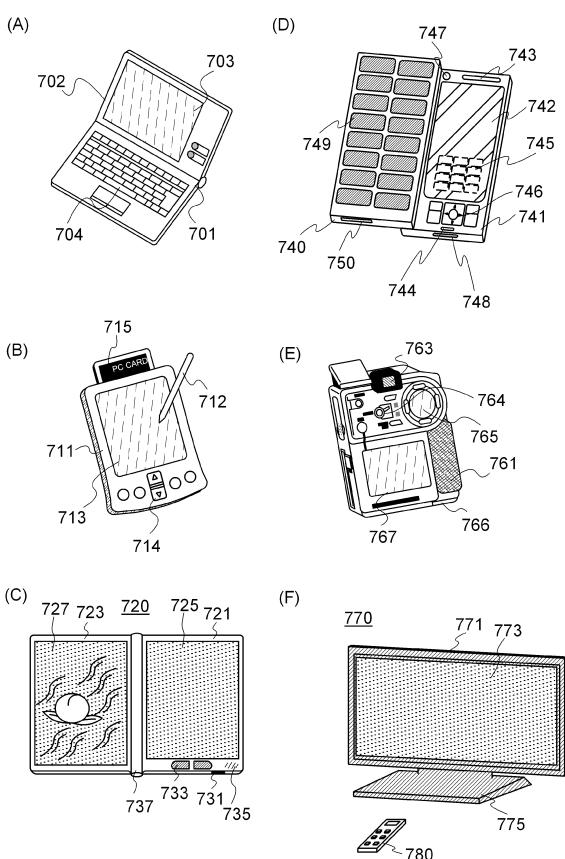

本実施の形態では、上述の実施の形態で説明した回路を用いた半導体装置について、図10を用いて説明する。本実施の形態では、コンピュータ、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯情報端末（携帯型ゲーム機、音響再生装置なども含む）、デジタルカメラ、デジタルビデオカメラなどのカメラ、電子ペーパー、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）などの半導体装置に、上述の回路を適用した場合について説明する。

10

#### 【0231】

図10(A)は、ノート型のパーソナルコンピュータであり、筐体701、筐体702、表示部703、キーボード704などによって構成されている。筐体701と筐体702の少なくとも一には、先の実施の形態に示す回路が設けられている。そのため、情報の書き込み及び読み出しが高速で、且つ消費電力が十分に低減されたノート型のパーソナルコンピュータが実現される。

20

#### 【0232】

図10(B)は、携帯情報端末(PDA)であり、本体711には、表示部713と、外部インターフェイス715と、操作ボタン714等が設けられている。また、携帯情報端末を操作するスティラス712などを備えている。本体711内には、先の実施の形態に示す回路が設けられている。そのため、情報の書き込み及び読み出しが高速で、且つ消費電力が十分に低減された携帯情報端末が実現される。

#### 【0233】

図10(C)は、電子ペーパーを実装した電子書籍720であり、筐体721と筐体723の2つの筐体で構成されている。筐体721及び筐体723には、それぞれ表示部725及び表示部727が設けられている。筐体721と筐体723は、軸部737により接続されており、該軸部737を軸として開閉動作を行うことができる。また、筐体721は、電源731、操作キー733、スピーカー735などを備えている。筐体721、筐体723の少なくとも一には、先の実施の形態に示す回路が設けられている。そのため、情報の書き込み及び読み出しが高速で、且つ消費電力が十分に低減された電子書籍が実現される。

30

#### 【0234】

図10(D)は、携帯電話機であり、筐体740と筐体741の2つの筐体で構成されている。さらに、筐体740と筐体741は、スライドし、図10(D)のように展開している状態から重なり合った状態とすることができます、携帯に適した小型化が可能である。また、筐体741は、表示パネル742、スピーカー743、マイクロフォン744、操作キー745、ポインティングデバイス746、カメラ用レンズ747、外部接続端子748などを備えている。また、筐体740は、携帯電話機の充電を行う太陽電池セル749、外部メモリスロット750などを備えている。また、アンテナは、筐体741に内蔵されている。筐体740と筐体741の少なくとも一には、先の実施の形態に示す回路が設けられている。そのため、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された携帯電話機が実現される。

40

#### 【0235】

図10(E)は、デジタルカメラであり、本体761、表示部767、接眼部763、操作スイッチ764、表示部765、バッテリー766などによって構成されている。本体761内には、先の実施の形態に示す回路が設けられている。そのため、情報の書き込み

50

及び読み出しが高速で、且つ消費電力が十分に低減されたデジタルカメラが実現される。

【0236】

図10(F)は、テレビジョン装置770であり、筐体771、表示部773、スタンド775などで構成されている。テレビジョン装置770の操作は、筐体771が備えるスイッチや、リモコン操作機780により行うことができる。筐体771及びリモコン操作機780には、先の実施の形態に示す回路が搭載されている。そのため、情報の書き込み及び読み出しが高速で、且つ消費電力が十分に低減されたテレビジョン装置が実現される。

【0237】

以上のように、本実施の形態に示す半導体装置には、先の実施の形態に係る回路が搭載されている。このため、消費電力を低減した半導体装置が実現される。

10

【符号の説明】

【0238】

|     |             |    |

|-----|-------------|----|

| 101 | 不揮発性FF      |    |

| 103 | 揮発性FF       |    |

| 105 | 選択回路        |    |

| 107 | インバータ回路     |    |

| 109 | NAND回路      |    |

| 200 | 不揮発性FF      | 20 |

| 201 | 第5のインバータ回路  |    |

| 203 | 第1のインバータ回路  |    |

| 205 | 第3のインバータ回路  |    |

| 207 | 第4のインバータ回路  |    |

| 209 | 第2のインバータ回路  |    |

| 211 | 第1のアナログスイッチ |    |

| 213 | 第2のアナログスイッチ |    |

| 215 | NAND回路      |    |

| 217 | NAND回路      |    |

| 219 | トランジスタ      |    |

| 220 | 第1のラッチ回路    | 30 |

| 221 | 保持容量        |    |

| 230 | 第2のラッチ回路    |    |

| 301 | 第5のインバータ回路  |    |

| 303 | 第1のアナログスイッチ |    |

| 305 | 第1のインバータ回路  |    |

| 307 | 第2のインバータ回路  |    |

| 309 | 第2のアナログスイッチ |    |

| 311 | 第3のインバータ回路  |    |

| 313 | 第4のインバータ回路  |    |

| 320 | 第1のラッチ回路    | 40 |

| 330 | 第2のラッチ回路    |    |

| 500 | 基板          |    |

| 502 | 保護層         |    |

| 504 | 半導体領域       |    |

| 506 | 素子分離絶縁層     |    |

| 508 | ゲート絶縁層      |    |

| 510 | ゲート電極       |    |

| 516 | チャネル形成領域    |    |

| 520 | 不純物領域       |    |

| 522 | 金属層         | 50 |

|         |                |    |

|---------|----------------|----|

| 5 2 4   | 金属化合物領域        |    |

| 5 2 6   | 電極             |    |

| 5 2 8   | 絶縁層            |    |

| 5 3 0   | 絶縁層            |    |

| 5 4 2 a | ソース電極またはドレイン電極 |    |

| 5 4 2 b | ソース電極またはドレイン電極 |    |

| 5 4 3 a | 絶縁層            |    |

| 5 4 3 b | 絶縁層            |    |

| 5 4 4   | 酸化物半導体層        |    |

| 5 4 6   | ゲート絶縁層         | 10 |

| 5 4 8 a | ゲート電極          |    |

| 5 4 8 b | 電極             |    |

| 5 5 0   | 絶縁層            |    |

| 5 5 2   | 絶縁層            |    |

| 5 5 4   | 電極             |    |

| 5 5 6   | 配線             |    |

| 5 6 0   | トランジスタ         |    |

| 5 6 2   | トランジスタ         |    |

| 5 6 4   | 保持容量           |    |

| 7 0 1   | 筐体             | 20 |

| 7 0 2   | 筐体             |    |

| 7 0 3   | 表示部            |    |

| 7 0 4   | キーボード          |    |

| 7 1 1   | 本体             |    |

| 7 1 2   | スタイルス          |    |

| 7 1 3   | 表示部            |    |

| 7 1 4   | 操作ボタン          |    |

| 7 1 5   | 外部インターフェイス     |    |

| 7 2 0   | 電子書籍           |    |

| 7 2 1   | 筐体             | 30 |

| 7 2 3   | 筐体             |    |

| 7 2 5   | 表示部            |    |

| 7 2 7   | 表示部            |    |

| 7 3 1   | 電源             |    |

| 7 3 3   | 操作キー           |    |

| 7 3 5   | スピーカー          |    |

| 7 3 7   | 軸部             |    |

| 7 4 0   | 筐体             |    |

| 7 4 1   | 筐体             |    |

| 7 4 2   | 表示パネル          | 40 |

| 7 4 3   | スピーカー          |    |

| 7 4 4   | マイクロフォン        |    |

| 7 4 5   | 操作キー           |    |

| 7 4 6   | ポインティングデバイス    |    |

| 7 4 7   | カメラ用レンズ        |    |

| 7 4 8   | 外部接続端子         |    |

| 7 4 9   | 太陽電池セル         |    |

| 7 5 0   | 外部メモリスロット      |    |

| 7 6 1   | 本体             |    |

| 7 6 3   | 接眼部            | 50 |

7 6 4 操作スイッチ

7 6 5 表示部

7 6 6 バッテリー

7 6 7 表示部

7 7 0 テレビジョン装置

7 7 1 筐体

7 7 3 表示部

7 7 5 スタンド

7 8 0 リモコン操作機

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特許第5 8 3 9 5 5 8 (JP, B2)

特開平0 6 - 0 2 9 3 0 7 (JP, A)

特開平1 0 - 3 3 4 6 7 1 (JP, A)

特開2 0 0 7 - 1 0 3 9 1 8 (JP, A)

特開2 0 0 9 - 2 0 6 9 4 2 (JP, A)

特開2 0 0 0 - 0 7 7 9 8 2 (JP, A)

特開平0 5 - 1 1 0 3 9 2 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| H 0 3 K | 3 / 3 5 6 2 |

| H 0 3 K | 3 / 0 3 7   |

| G 0 6 F | 1 / 3 0     |