(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6625491号

(P6625491)

(45) 発行日 令和1年12月25日(2019.12.25)

(24) 登録日 令和1年12月6日(2019.12.6)

(51) Int.Cl.

F 1

|            |           |            |   |

|------------|-----------|------------|---|

| HO1L 23/12 | (2006.01) | HO1L 23/12 | N |

| HO5K 3/46  | (2006.01) | HO5K 3/46  | Q |

| HO1L 25/04 | (2014.01) | HO5K 3/46  | N |

| HO1L 25/18 | (2006.01) | HO5K 3/46  | B |

|            |           | HO1L 25/04 | Z |

請求項の数 7 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2016-129022 (P2016-129022)

(22) 出願日

平成28年6月29日(2016.6.29)

(65) 公開番号

特開2018-6466 (P2018-6466A)

(43) 公開日

平成30年1月11日(2018.1.11)

審査請求日

平成30年12月19日(2018.12.19)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100105957

弁理士 恩田 誠

(74) 代理人 100068755

弁理士 恩田 博宣

(72) 発明者 反町 東夫

長野県長野市小島田町80番地 新光電気

工業 株式会社 内

審査官 河合 俊英

最終頁に続く

(54) 【発明の名称】配線基板、半導体装置、配線基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

それぞれ第1電極端子と第2電極端子を有する第1半導体素子と第2半導体素子が実装される配線基板であって、

上面に前記第1半導体素子の第1電極端子が接続される第1接続端子と前記第2半導体素子の第1電極端子が接続される第2接続端子とが露出して形成され、下面に内部接続端子が形成された配線部品と、

前記第1半導体素子の第2電極端子が接続される第3接続端子と、

前記第2半導体素子の第2電極端子が接続される第4接続端子と、

前記配線部品と前記第3接続端子と前記第4接続端子とが埋設された絶縁層と、

前記絶縁層の下面に形成され、前記絶縁層を貫通するビア配線を有し、前記ビア配線により前記内部接続端子に直接接続された配線層と、を有し、

前記第1～前記第4接続端子の上面は同一の平面上に位置しており、

前記絶縁層は、前記配線部品の外周側面から前記絶縁層の上面側に向かうにつれて拡開するテープ状の開口部を有し、

前記開口部と前記配線部品の間に配設され、前記配線部品の側面の一部を覆う接着剤を備えていること、を特徴とする配線基板。

## 【請求項 2】

前記第3接続端子と前記第4接続端子は前記絶縁層の厚さ方向に延びる柱状に形成され、前記絶縁層の厚さ方向において前記第3接続端子及び前記第4接続端子の長さは、前記

10

20

配線部品の前記上面から前記下面までの厚さと等しくなるように設定されていること、を特徴とする請求項 1 に記載の配線基板。

【請求項 3】

配線基板と、それぞれ第 1 電極端子と第 2 電極端子を有して前記配線基板に実装された第 1 半導体素子と第 2 半導体素子とを有し、

前記配線基板は、

上面に前記第 1 半導体素子の第 1 電極端子が接続される第 1 接続端子と前記第 2 半導体素子の第 1 電極端子が接続される第 2 接続端子とが露出して形成され、下面に内部接続端子が形成された配線部品と、

前記第 1 半導体素子の第 2 電極端子が接続される第 3 接続端子と、

10

前記第 2 半導体素子の第 2 電極端子が接続される第 4 接続端子と、

前記配線部品と前記第 3 接続端子と前記第 4 接続端子とが埋設された絶縁層と、

前記絶縁層の下面に形成され、前記絶縁層を貫通するビア配線を有し、前記ビア配線により前記内部接続端子に直接接続された配線層と、を有し、

前記第 1 ~ 前記第 4 接続端子の上面は同一の平面上に位置してあり、

前記絶縁層は、前記配線部品の外周側面から前記絶縁層の上面側に向かうにつれて拡開するテープ状の開口部を有し、

前記開口部と前記配線部品の間に配設され、前記配線部品の側面の一部を覆う接着剤を備えていること、を特徴とする半導体装置。

【請求項 4】

20

それぞれ第 1 電極端子と第 2 電極端子を有する第 1 半導体素子と第 2 半導体素子が実装される配線基板の製造方法であって、

第 1 の面に前記第 1 半導体素子の第 1 電極端子が接続される第 1 接続端子と前記第 2 半導体素子の第 1 電極端子が接続される第 2 接続端子とが露出して形成され、前記第 1 の面とは反対側の第 2 の面に内部接続端子が形成された配線部品と、前記第 1 の面を覆う金属箔とを有する構造体を形成する工程と、

第 1 支持基板の上面に搭載凹部を形成する工程と、

前記金属箔の上面を前記第 1 支持基板の上面と同一高さとするように、前記搭載凹部に前記構造体の前記金属箔を埋設して接着層により前記構造体を接着する工程と、

前記第 1 支持基板の上面に第 3 接続端子と第 4 接続端子とを形成する工程と、

30

前記構造体と前記第 3 接続端子と前記第 4 接続端子とを覆う絶縁層を形成する工程と、

前記絶縁層の上面に、前記内部接続端子と前記第 3 接続端子と前記第 4 接続端子とにそれぞれ接続された配線層を形成する工程と、

前記第 1 支持基板を除去する工程と、

前記金属箔を覆う前記接着層を除去する工程と、

前記構造体の前記金属箔を除去する工程と、

を有する配線基板の製造方法。

【請求項 5】

それぞれ第 1 電極端子と第 2 電極端子を有する第 1 半導体素子と第 2 半導体素子が実装される配線基板の製造方法であって、

40

第 1 の面に前記第 1 半導体素子の第 1 電極端子が接続される第 1 接続端子と前記第 2 半導体素子の第 1 電極端子が接続される第 2 接続端子とが露出して形成され、前記第 1 の面とは反対側の第 2 の面に内部接続端子が形成された配線部品と、前記第 1 の面を覆う金属箔とを有する構造体を形成する工程と、

第 1 支持基板の上面に、前記構造体の前記金属箔を接着層により接着する工程と、

前記第 1 支持基板の上面に、前記金属箔の上面と同一の高さの補助層を形成する工程と、

前記補助層の上に第 3 接続端子と第 4 接続端子とを形成する工程と、

前記構造体と前記第 3 接続端子と前記第 4 接続端子とを覆う絶縁層を形成する工程と、

前記絶縁層の上面に、前記内部接続端子と前記第 3 接続端子と前記第 4 接続端子とにそ

50

それぞれ接続された配線層を形成する工程と、

前記第1支持基板及び前記補助層を除去する工程と、

前記金属箔を覆う前記接着層を除去する工程と、

前記構造体の前記金属箔を除去する工程と、

を有する配線基板の製造方法。

【請求項6】

前記第1支持基板は、支持体と、前記支持体の上面に接着されたキャリア板と、前記キャリア板の上面に剥離層を介して積層された金属箔とを含み、

前記第1支持基板を除去する工程では、前記キャリア板を前記金属箔から剥離して前記支持体と前記キャリア板とを除去した後、前記金属箔をエッチングにより除去すること、

を特徴とする請求項4又は5に記載の配線基板の製造方法。

10

【請求項7】

前記構造体を形成する工程は、

キャリア板と、前記キャリア板の上面に剥離層を介して積層された金属箔とを含む第2支持基板を用い、前記金属箔の上面に第1接続端子と第2接続端子とを形成する工程と、

前記金属箔の上面側に、絶縁層と配線層とを交互に積層する工程と、

最上層の前記配線層をパターニングして内部接続端子を形成する工程と、

最上層の前記絶縁層の上面に第1支持層を形成する工程と、

前記キャリア板を前記金属箔から剥離する工程と、

前記金属箔の下面に第2支持層を形成した後、前記第1支持層を除去する工程と、

を有し、

20

前記金属箔から前記第2支持層を除去して前記構造体を前記第1支持基板に接着すること、を特徴とする請求項4～6のいずれか1項に記載の配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板、半導体装置、配線基板の製造方法に関する。

【背景技術】

【0002】

従来、電子機器に使用される半導体装置は、配線基板の上に電子部品が搭載されている。配線基板上に例えば2つの電子部品を横方向に並べて搭載する半導体装置では、2つの電子部品が配線を介して接続される。2つの電子部品を接続する方法としては、微細配線を内蔵する配線部品を配線基板に配置する方法、又は配線基板に微細配線を作り込む方法、等の各種の方法が提案されている（例えば、特許文献1～5参照）。

30

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006-261311号公報

【特許文献2】特表2011-515842号公報

【特許文献3】特開2013-243227号公報

【特許文献4】特開2014-99591号公報

【特許文献5】特開2014-179613号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、上記のように複数の電子部品を搭載する配線基板において、接続信頼性を確保することが求められている。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、それぞれ第1電極端子と第2電極端子を有する第1半導体素

50

子と第2半導体素子が実装される配線基板であって、上面に前記第1半導体素子の第1電極端子が接続される第1接続端子と前記第2半導体素子の第1電極端子が接続される第2接続端子とが露出して形成され、下面に内部接続端子が形成された配線部品と、前記第1半導体素子の第2電極端子が接続される第3接続端子と、前記第2半導体素子の第2電極端子が接続される第4接続端子と、前記配線部品と前記第3接続端子と前記第4接続端子とが埋設された絶縁層と、前記絶縁層の下面に形成され、前記絶縁層を貫通するビア配線を有し、前記ビア配線により前記内部接続端子に直接接続された配線層と、を有し、前記第1～前記第4接続端子の上面は同一の平面上に位置しており、前記絶縁層は、前記配線部品の外周側面から前記絶縁層の上面側に向かうにつれて拡開するテーパ状の開口部を有し、前記開口部と前記配線部品の間に配設され、前記配線部品の側面の一部を覆う接着剤を備えている。10

**【0006】**

本発明の別の一観点によれば、配線基板と、それぞれ第1電極端子と第2電極端子を有して前記配線基板に実装された第1半導体素子と第2半導体素子とを有し、前記配線基板は、上面に前記第1半導体素子の第1電極端子が接続される第1接続端子と前記第2半導体素子の第1電極端子が接続される第2接続端子とが露出して形成され、下面に内部接続端子が形成された配線部品と、前記第1半導体素子の第2電極端子が接続される第3接続端子と、前記第2半導体素子の第2電極端子が接続される第4接続端子と、前記配線部品と前記第3接続端子と前記第4接続端子とが埋設された絶縁層と、前記絶縁層の下面に形成され、前記絶縁層を貫通するビア配線を有し、前記ビア配線により前記内部接続端子に直接接続された配線層と、を有し、前記第1～前記第4接続端子の上面は同一の平面上に位置しており、前記絶縁層は、前記配線部品の外周側面から前記絶縁層の上面側に向かうにつれて拡開するテーパ状の開口部を有し、前記開口部と前記配線部品の間に配設され、前記配線部品の側面の一部を覆う接着剤を備えている。20

**【0007】**

また、本発明の別の一観点によれば、それぞれ第1電極端子と第2電極端子を有する第1半導体素子と第2半導体素子が実装される配線基板の製造方法は、第1の面上に前記第1半導体素子の第1電極端子が接続される第1接続端子と前記第2半導体素子の第1電極端子が接続される第2接続端子とが露出して形成され、前記第1の面とは反対側の第2の面上に内部接続端子が形成された配線部品と、前記第1の面を覆う金属箔とを有する構造体を形成する工程と、第1支持体の上面に搭載凹部を形成する工程と、前記金属箔の上面を前記第1支持体の上面と同一高さとするように、前記搭載凹部に前記構造体の前記金属箔を埋設して接着層により前記構造体を接着する工程と、前記第1支持体の上面に第3接続端子と第4接続端子とを形成する工程と、前記構造体と前記第3接続端子と前記第4接続端子とを覆う絶縁層を形成する工程と、前記絶縁層の上面に、前記内部接続端子と前記第3接続端子と前記第4接続端子とにそれぞれ接続された配線層を形成する工程と、前記第1支持体を除去する工程と、前記金属箔を覆う前記接着層を除去する工程と、前記構造体の前記金属箔を除去する工程と、を有する。30

**【0008】**

また、本発明の別の一観点によれば、それぞれ第1電極端子と第2電極端子を有する第1半導体素子と第2半導体素子が実装される配線基板の製造方法は、第1の面上に前記第1半導体素子の第1電極端子が接続される第1接続端子と前記第2半導体素子の第1電極端子が接続される第2接続端子とが露出して形成され、前記第1の面とは反対側の第2の面上に内部接続端子が形成された配線部品と、前記第1の面を覆う金属箔とを有する構造体を形成する工程と、第1支持体の上面に、前記構造体の前記金属箔を接着層により接着する工程と、前記第1支持体の上面に、前記金属箔の上面と同一の高さの補助層を形成する工程と、前記補助層の上に第3接続端子と第4接続端子とを形成する工程と、前記構造体と前記第3接続端子と前記第4接続端子とを覆う絶縁層を形成する工程と、前記絶縁層の上面に、前記内部接続端子と前記第3接続端子と前記第4接続端子とにそれぞれ接続された配線層を形成する工程と、前記第1支持体及び前記補助層を除去する工程と、前記金属箔4050

を覆う前記接着層を除去する工程と、前記構造体の前記金属箔を除去する工程と、を有する。

**【発明の効果】**

**【0009】**

本発明の一観点によれば、複数の電子部品を搭載する配線基板において、接続信頼性を確保することができる。

**【図面の簡単な説明】**

**【0010】**

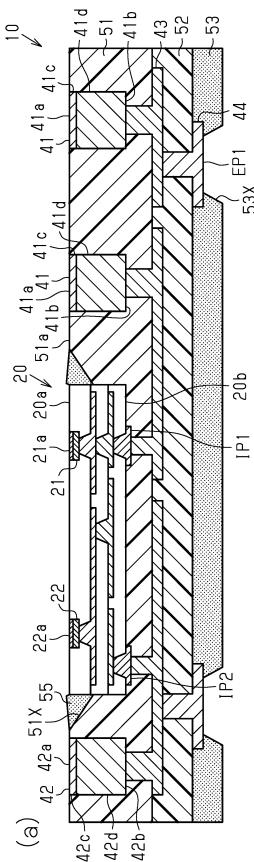

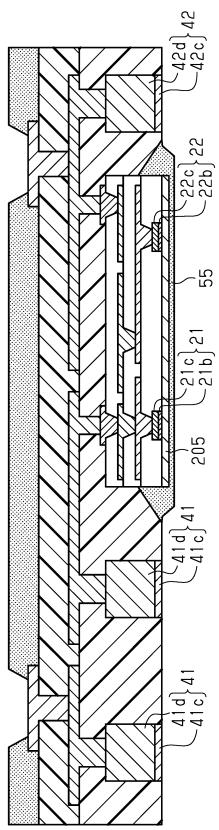

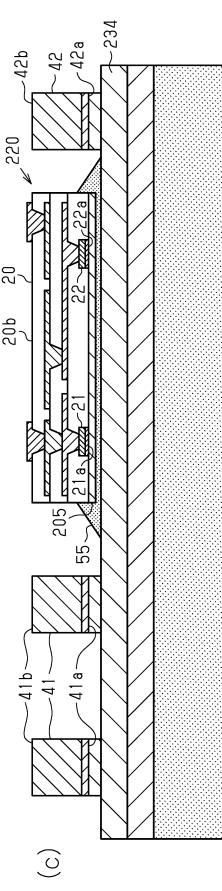

【図1】(a)は第1実施形態の配線基板を示す概略断面図、(b)は配線部品を示す概略断面図。10

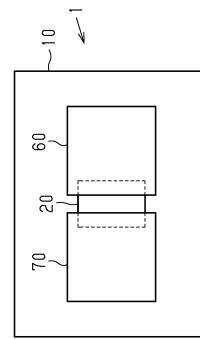

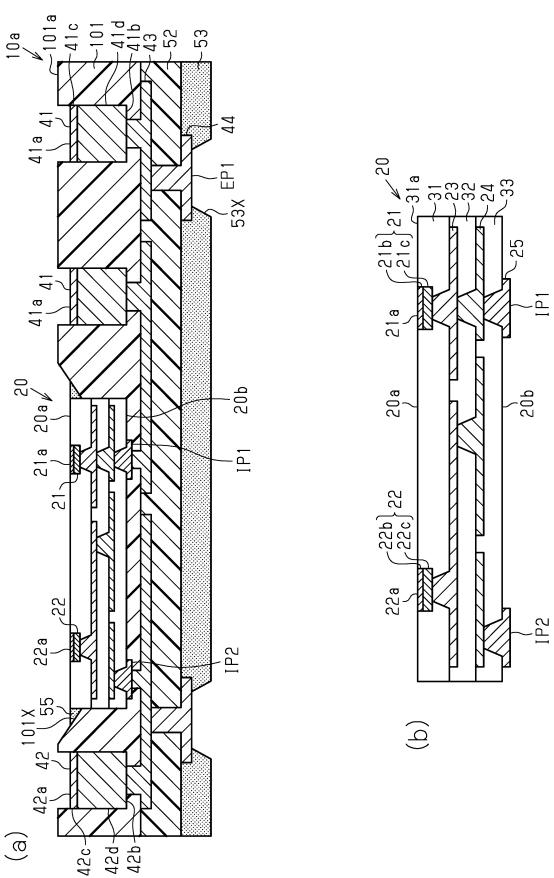

【図2】(a)は半導体装置を示す概略平面図、(b)は半導体装置を示す概略断面図。

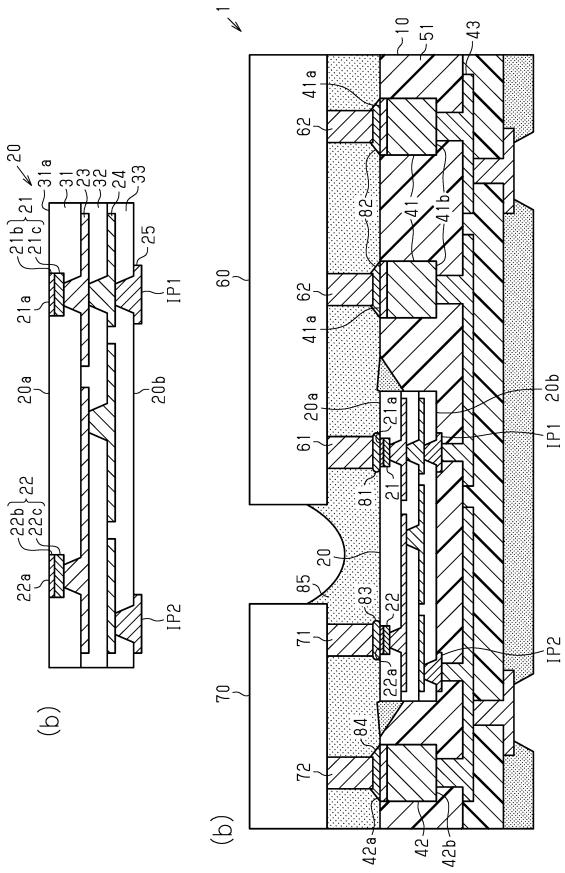

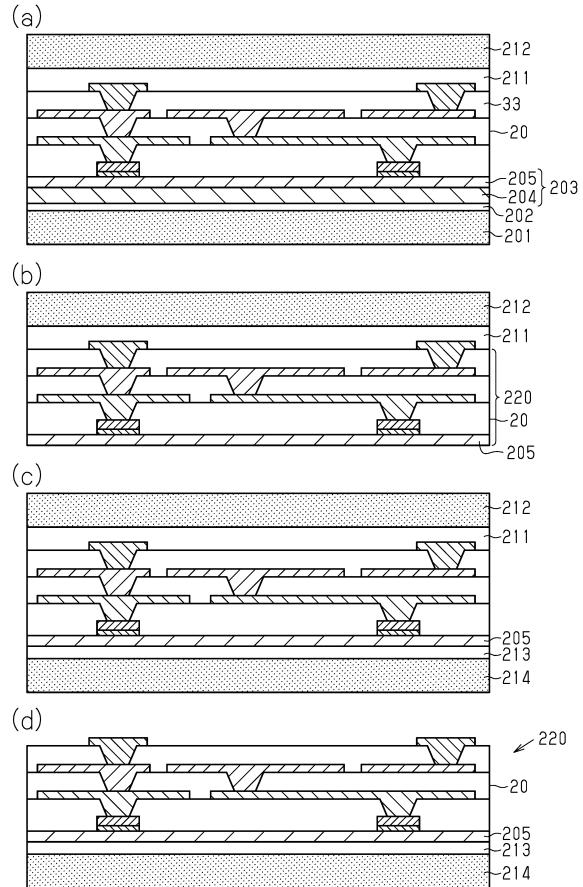

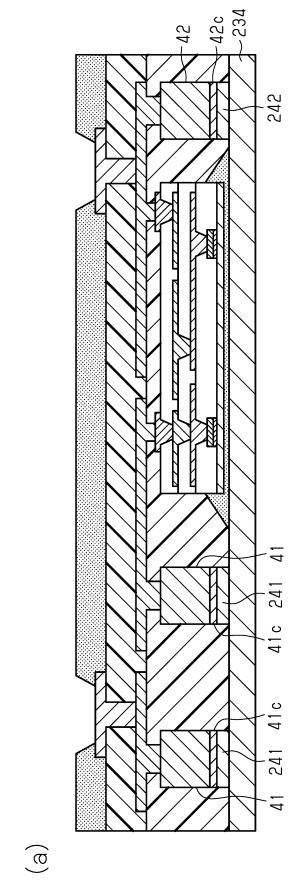

【図3】(a)～(e)は、配線部品の製造方法を示す概略断面図。

【図4】(a)～(d)は、配線部品の製造方法を示す概略断面図。

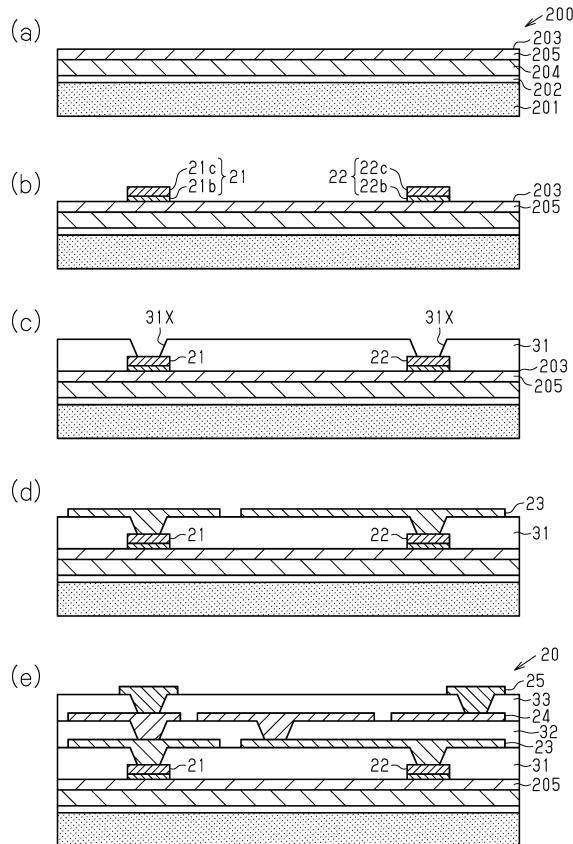

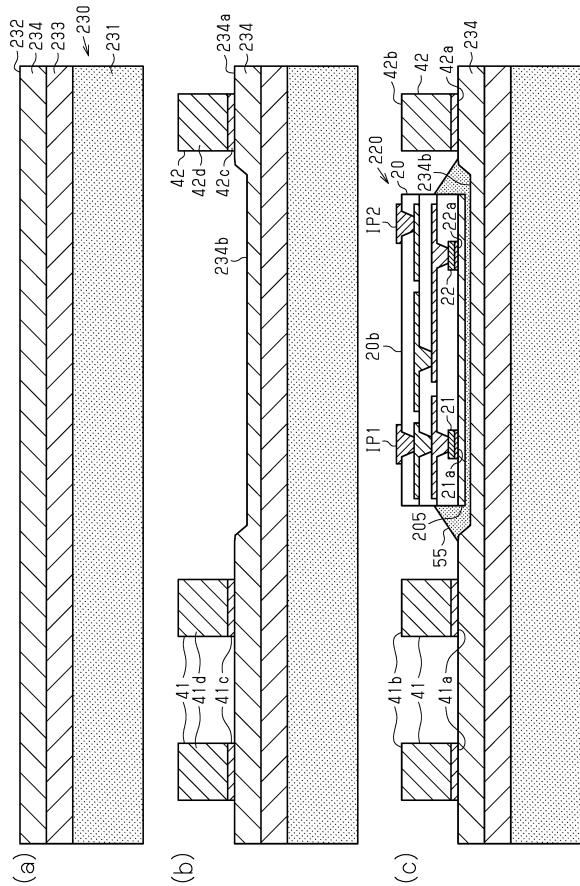

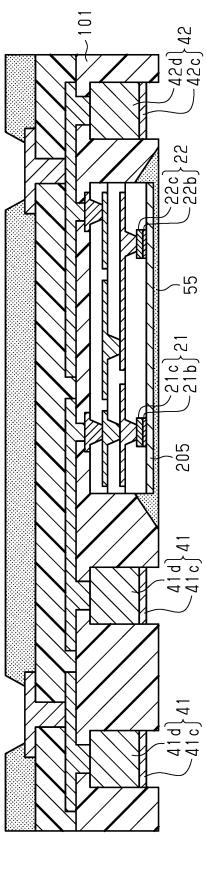

【図5】(a)～(c)は、第1実施形態の配線基板の製造方法を示す概略断面図。

【図6】第1実施形態の配線基板の製造方法を示す概略断面図。

【図7】(a),(b)は、第1実施形態の配線基板の製造方法を示す概略断面図。

【図8】(a),(b)は、第1実施形態の配線基板の製造方法を示す概略断面図。

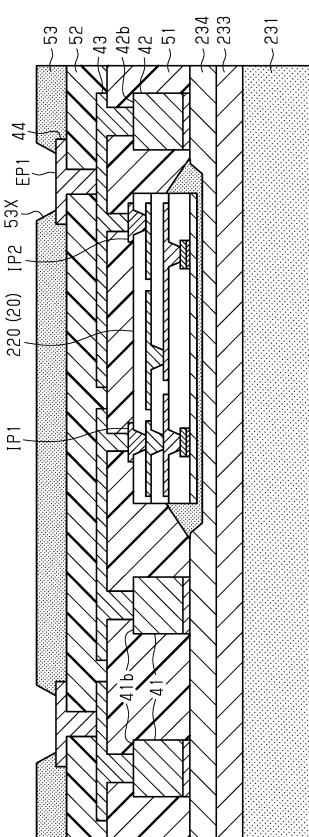

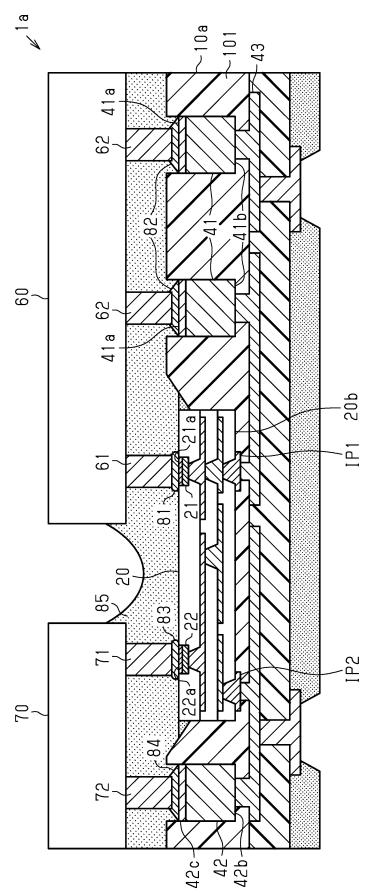

【図9】(a)は第2実施形態の配線基板を示す概略断面図、(b)は配線部品を示す概略断面図。20

【図10】半導体装置を示す概略断面図。

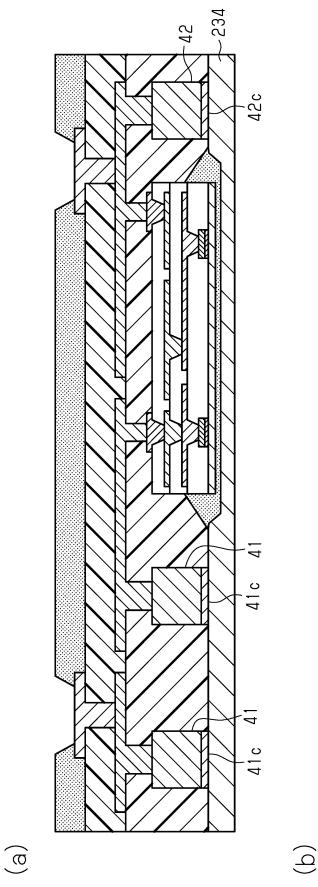

【図11】(a)～(c)は、第2実施形態の配線基板の製造方法を示す概略断面図。

【図12】第2実施形態の配線基板の製造方法を示す概略断面図。

【図13】(a),(b)は、第2実施形態の配線基板の製造方法を示す概略断面図。

【図14】(a),(b)は、第2実施形態の配線基板の製造方法を示す概略断面図。

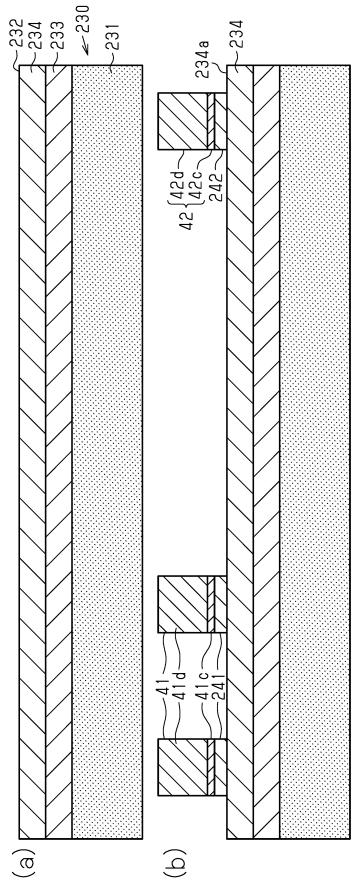

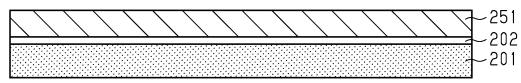

【図15】別の支持基板を示す断面図。

**【発明を実施するための形態】**

**【0011】**

以下、添付図面を参照して各実施形態を説明する。なお、添付図面は、便宜上、特徴を分かりやすくするために特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の部材のハッチングを梨地模様に代えて示し、一部の部材のハッチングを省略している。なお、本明細書において、「平面視」とは、対象物を図1等の鉛直方向(図中上下方向)から視ることを言い、「平面形状」とは、対象物を図1等の鉛直方向から視た形状のことを言う。30

**【0012】**

**(第1実施形態)**

以下、第1実施形態を図1～図8に従って説明する。

図2(a)に示すように、半導体装置1は、配線基板10と、配線基板10に実装された複数(図2(a)では2つ)の半導体素子60,70とを有している。配線基板10は、配線部品(ブリッジボード)20を有している。配線部品20は、平面視において、2つの半導体素子60,70の一部と重なるように配置されている。半導体素子60,70の一部の端子は、配線部品20に接続されている。配線部品20は、2つの半導体素子60,70の一部の端子を互いに接続する。40

**【0013】**

一方の半導体素子60(第1半導体素子)としては、例えば、C P U (Central Processing Unit)チップやG P U (Graphics Processing Unit)チップなどのロジックチップを用いることができる。そして、他方の半導体素子70(第2半導体素子)としては、例えば、D R A M (Dynamic Random Access Memory)チップ、S R A M (Static Random Access Memory)チップやフラッシュメモリチップなどのメモリチップを用いることができ50

る。なお、半導体素子 60, 70 として、大規模半導体回路を複数（例えば 2 つ）に分割して形成されたチップ（ダイ）を用いることもできる。

【0014】

図 2 (b) に示すように、半導体素子 60 は、複数の電極端子（ピラー）62（第 2 電極端子）を介して配線基板 10 に接続されている。同様に、半導体素子 70 は、複数の電極端子（ピラー）72（第 2 電極端子）を介して配線基板 10 に接続されている。半導体素子 60 は、電極端子 61（第 1 電極端子）を介して配線部品 20 に接続されている。同様に、半導体素子 70 は、電極端子 71（第 1 電極端子）を介して配線部品 20 に接続されている。電極端子 61, 62, 71, 72 の材料としては、例えば銅又は銅合金を用いることができる。なお、図 2 (b) は、半導体装置 1 の一部であり、2 つの半導体素子 60, 70 の間の接続部分を示している。10

【0015】

配線基板 10 と半導体素子 60, 70 との間には、アンダーフィル樹脂 85 が充填されている。アンダーフィル樹脂 85 は、配線基板 10 と半導体素子 60, 70 との間の接続部分の接続強度を向上させると共に、配線パターンの腐食やエレクトロマイグレーションの発生を抑制し、配線パターンの信頼性の低下を防ぐ。アンダーフィル樹脂 85 の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。

【0016】

次に、配線基板 10 について詳述する。

図 1 (a) に示すように、配線基板 10 は、配線部品 20、外部端子 41, 42、配線層 43, 44、絶縁層 51, 52、ソルダレジスト層 53 を有している。20

【0017】

配線部品 20 と外部端子 41, 42 は、絶縁層 51 に埋設されている。絶縁層 51 は、配線部品 20 の上面 20a と外部端子 41, 42 の上面 41a, 42a を露出するように形成されている。つまり、絶縁層 51 は、配線部品 20 の下面及び側面と、外部端子 41, 42 の下面及び側面を覆うように形成されている。

【0018】

図 1 (b) に示すように、配線部品 20 は、外部端子（パッド）21, 22、配線層 23, 24, 25、絶縁層 31, 32, 33 を有している。配線部品 20 は、例えばビルドアップ法を用いて形成されている。30

【0019】

外部端子 21, 22 は、配線部品 20 の最外層（ここでは、最上層）の絶縁層 31 に埋設されている。外部端子 21, 22 の上面 21a, 22a は、絶縁層 31 の上面 31a と同一平面上に位置する。従って、絶縁層 31 は、外部端子 21, 22 の下面及び側面を覆うように形成されている。

【0020】

外部端子 21, 22 は、例えば平面視円形の板状に形成されている。外部端子 21, 22 の大きさは、例えば直径を 15 ~ 30 マイクロメートル ( $\mu\text{m}$ ) とすることができます。外部端子 21（第 1 接続端子）は、複数（本実施形態では 2 つ）の金属層 21b, 21c により形成されている。同様に、外部端子 22（第 2 接続端子）は、複数（本実施形態では 2 つ）の金属層 22b, 22c により形成されている。上面側、つまり絶縁層 31 の上面 31a に露出する金属層 21b, 22b は、例えば金（Au）層である。埋設された金属層 21c, 22c は、例えばニッケル（Ni）層である。Au 層の厚さは、例えば 0.1 ~ 0.2  $\mu\text{m}$  とすることができます。Ni 層の厚さは例えば 2 ~ 6  $\mu\text{m}$  とすることができます。絶縁層 31 の厚さは、例えば 5 ~ 7  $\mu\text{m}$  とすることができます。40

【0021】

絶縁層 31 の下面には、配線層 23 が形成されている。

配線層 23 は、絶縁層 31 を厚み方向に貫通して外部端子 21, 22 に接続されたビア配線と、ビア配線を介して外部端子 21, 22 と接続され、絶縁層 31 の下面に形成された配線パターンと、を有している。配線パターンの厚さは、例えば 2 ~ 5  $\mu\text{m}$  とすること50

ができる。配線パターンの幅は、例えば2～5 μmとすることができます。配線パターンの間隔は、例えば2～5 μmとすることができます。

【0022】

絶縁層32は、絶縁層31の下面に、配線層23を覆うように形成されている。

配線層24は、絶縁層32の下面に形成されている。配線層24は、絶縁層32を厚み方向に貫通するビア配線と、そのビア配線を介して配線層23と接続され、絶縁層32の下面に形成された配線パターンとを有している。配線層24の大きさ（配線パターンの厚さ、配線幅、配線間隔）については、前述の配線層23と同様とすることができます。

【0023】

絶縁層33は、絶縁層32の下面に、配線層24を覆うように形成されている。

10

配線層25は、絶縁層33の下面に形成されている。配線層25は、絶縁層33を厚み方向に貫通するビア配線と、そのビア配線を介して配線層24と接続され、絶縁層33の下面に形成された配線パターンとを有している。この配線層25において、絶縁層33の下面に形成された配線パターンは、内部接続端子IP1・IP2として機能する。内部接続端子IP1・IP2は、例えば円形状に形成され、その大きさは例えば40 μmとすることができます。

【0024】

配線層23, 24, 25の材料としては、例えば銅又は銅合金を用いることができる。

絶縁層31, 32, 33の材料としては、例えば感光性を有する樹脂（例えば、ポリイミド樹脂、シリコーン樹脂、フェノール樹脂、等）を用いることができる。

20

【0025】

図1(a)に示すように、絶縁層51には、その絶縁層51の上面51aの側において、配線部品20の側面に対応する部分に、上面51a側に向かうにつれて拡開するテーパ状の開口部51Xが形成されている。開口部51Xと配線部品20との間には接着剤55が配設されている。接着剤55の材料としては、例えば、エポキシ樹脂やポリイミド樹脂等の絶縁樹脂を用いることができる。

【0026】

図1(a)に示す外部端子41, 42は、例えば円柱状に形成されている。外部端子41, 42の上面41a, 42aは、配線部品20に含まれる外部端子21, 22の上面21a, 22aと同一の平面上に位置している。そして、外部端子41, 42の下面41b, 42bは、配線部品20の下面20bとほぼ同一の平面上に位置している。

30

【0027】

外部端子41, 42の大きさは、例えば直径を40 μmとすることができます。外部端子41, 42の高さ（厚さ方向の長さ）は、配線部品20の厚さに応じて設定され、例えば15～21 μmとすることができます。

【0028】

外部端子41（第3接続端子）は、絶縁層51から露出する表面処理層41cと、表面処理層41cの下側にあって絶縁層51に埋設された金属ポスト41dとを含む。同様に、外部端子42（第4接続端子）は、絶縁層51から露出する表面処理層42cと、表面処理層42cの下側にあって絶縁層51に埋設された金属ポスト42dとを含む。

40

【0029】

金属ポスト41d, 42dの材料としては、例えば銅又は銅合金を用いることができる。表面処理層41c, 42cとしては、例えば、Ni/Au層（Ni層とAu層をこの順番で積層した金属層）とすることができます。Au層の厚さは例えば0.1～0.2 μm、Ni層の厚さは例えば2～5 μmとすることができます。なお、表面処理層41c, 42cとして、Au層、Ni/パラジウム（Pd）/Au層（Ni層とPd層とAu層をこの順番で積層した金属層）等を挙げることができる。また、OSP（Organic Solderability Preservative）処理などの酸化防止処理を施して表面処理層を形成するようにしてもよい。例えば、OSP処理を施した場合には、アゾール化合物やイミダゾール化合物等の有機被膜による表面処理層が形成される。

50

## 【0030】

絶縁層51の下面には、配線層43が形成されている。配線層43は、絶縁層51を厚み方向に貫通して外部端子41, 42、配線部品20の内部接続端子IP1. IP2に接続されたビア配線と、ビア配線を介して外部端子41, 42、内部接続端子IP1. IP2に接続され、絶縁層51の下面に形成された配線パターンとを有している。絶縁層52は、絶縁層51の下面に、配線層43を覆うように形成されている。配線層44は、絶縁層52を厚み方向に貫通して配線層43に接続されたビア配線と、ビア配線を介して配線層43に接続され、絶縁層52の下面に形成された配線パターンとを有している。

## 【0031】

配線層43, 44に含まれる配線パターンにおいて、配線幅や配線間隔は、配線部品20の配線層23, 24の配線幅や配線間隔と比べ、大きな値に設定されている。言い換えれば、配線層23, 24は、配線層43, 44と比較して微細に形成されている。つまり、配線部品20は、配線層43, 44と比較して微細に形成された配線層23, 24を有している。

## 【0032】

ソルダレジスト層53は、絶縁層52の下面に、配線層44の一部を被覆するように形成されている。ソルダレジスト層53には、配線層44の下面の一部を外部接続端子EP1として露出する開口部53Xが形成されている。外部接続端子EP1には、配線基板10、つまり図2(a)に示す半導体装置1を基板等に実装するために利用されるバンプ(例えばはんだバンプ)が形成される。

## 【0033】

配線層43, 44の材料としては、例えば銅又は銅合金を用いることができる。

絶縁層51, 52の材料としては、例えば、エポキシ樹脂やポリイミド樹脂などの絶縁性樹脂、又はこれら樹脂にシリカやアルミナ等のフィラーを混入した樹脂材を用いることができる。また、絶縁層51, 52の材料としては、例えば、ガラス、アラミド、LCP(Liquid Crystal Polymer)纖維の織布や不織布などの補強材に、エポキシ樹脂やポリイミド樹脂等を主成分とする熱硬化性樹脂を含浸させた補強材入りの絶縁性樹脂を用いることもできる。なお、絶縁層51, 52の材料としては、熱硬化性を有する絶縁性樹脂や感光性を有する絶縁性樹脂を用いることができる。

## 【0034】

ソルダレジスト層53の材料として、例えば感光性のドライフィルムレジスト又は液状のフォトレジスト(例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト)等が用いられる。例えば感光性のドライフィルムレジストを用いる場合には、絶縁層52と配線層44とを、熱圧着したドライフィルムによりラミネートし、そのドライフィルムをフォトリソグラフィ法によりパターニングして開口部53Xを有するソルダレジスト層53を形成する。また、液状のフォトレジストを用いる場合にも、同様の工程を経て、ソルダレジスト層53が形成される。

## 【0035】

次に、上記の配線基板10の製造方法を説明する。

なお、説明の便宜上、最終的に配線基板10の各構成要素となる部分には、最終的な構成要素の符号を付して説明する場合がある。

## 【0036】

先ず、配線部品20の製造方法を説明する。

図3(a)に示す工程では、支持体201の上面に、接着層202を介してキャリア付金属箔203(ピーラブル金属箔)が貼付された支持基板200(第2支持基板)を形成する。支持体201の厚さは、例えば0.5~1ミリメートル(mm)とすることができる。支持体201としては、ガラスやステンレス等を用いることができる。接着層202は、耐熱性を有する、例えばエポキシ系の接着剤である。接着層202の厚さは、例えば10~20μmとすることができます。

## 【0037】

10

20

30

40

50

キャリア付金属箔 203 は、キャリア板 204 と、キャリア板 204 の上面に剥離層(図示略)を介して積層された極薄の金属箔 205 とを有している。キャリア板 204 は、例えば 35 μm の銅箔である。金属箔 205 は例えば 5 μm の銅箔である。

#### 【0038】

図 3 (b) に示す工程では、キャリア付金属箔 203 (金属箔 205) の上面に外部端子 21, 22 を形成する。

詳述すると、金属箔 205 の上面に、所望の位置に開口部を有するレジスト層を形成する。開口部は、外部端子 21, 22 に対応する部分の支持体(金属箔 205)を露出するように形成される。レジスト層の材料としては、感光性のドライフィルムレジスト又は液状のフォトレジスト(例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト)等を用いることができる。例えば感光性のドライフィルムレジストを用いる場合には、金属箔 205 の上面にドライフィルムを熱圧着によりラミネートし、そのドライフィルムを露光・現像によりパターニングして、開口部を有するレジスト層を形成する。なお、液状のフォトレジストを用いる場合にも、同様の工程を経て、レジスト層を形成することができる。続いて、レジスト層をめっきマスクとして、金属箔 205 の上面に、金属箔 205 をめっき給電層に利用する電解めっき(電解金めっき)を施し、金属層 21b, 22b を形成する。さらに、電解めっき(電解ニッケルめっき)を施し、金属層 21c, 22c を形成する。そして、レジスト層を例えばアルカリ性の剥離液により除去する。

#### 【0039】

図 3 (c) に示す工程では、キャリア付金属箔 203 (金属箔 205) の上面に、外部端子 21, 22 を覆う絶縁材を塗布し、露光・現像・硬化を行って、ピアホール 31X を有する絶縁層 31 を形成する。絶縁材としては、例えば感光性を有する樹脂(例えば、ポリイミド樹脂、シリコーン樹脂、フェノール樹脂、等)を用いることができる。ピアホール 31X により、外部端子 21, 22 の上面が例えば直径が 5 ~ 15 μm の大きさにて露出される。ピアホール 31X は、例えば、底面側の径(外部端子 21, 22 の上面における径)よりも絶縁層 31 の上面側における径が大きい、円錐台状に形成される。

#### 【0040】

図 3 (d) に示す工程では、絶縁層 31 の上に、例えばセミアディティブ法によって配線層 23 を形成する。詳述すると、先ず絶縁層 31 の上面にシード層を形成する。シード層としては、例えば 0.1 μm の厚さのチタン(Ti)膜と 0.2 μm の厚さの Cu 膜を用いることができる。シード層は、例えばスパッタ法により形成することができる。次に、シード層上に所定の箇所に開口部を摇するレジスト層を形成する。レジスト層の材料としては、例えば耐めっき性を有する材料として、感光性のドライフィルム、液状のフォトレジスト(例えば、ノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト)等を用いることができる。そのレジスト層をめっきマスクとして、シード層をめっき給電層に利用する電解めっき(電解銅めっき)を施し、電解めっき層を形成する。レジスト層を例えばアルカリ性の剥離液にて除去した後、電解めっき層をエッティングマスクとして不要なシード層を除去する。これにより、配線層 23 が形成される。このような工程により、配線層 23 のピア配線は、底面側の径(外部端子 21, 22 の上面における径)よりも絶縁層 31 の上面側における径が大きい、円錐台状に形成される。

#### 【0041】

図 3 (e) に示す工程では、前述した絶縁層 31 を形成する工程と配線層 23 を形成する工程と同様の工程を繰り返す事により、絶縁層 32、配線層 24、絶縁層 33、及び配線層 25 を形成する。これにより、金属箔 205 の上に配線部品 20 が形成される。

#### 【0042】

図 4 (a) に示す工程では、絶縁層 33 の上面に、絶縁層 33 と配線層 25 を覆うように、接着剤 211 によってキャリアフィルム 212(第 1 支持層)を貼付する。接着剤 211 としては、例えば紫外線の照射によって接着力が低下するものを用いることができる。キャリアフィルム 212 としては、例えばダイシング用テープを用いることができる。

10

20

30

40

50

## 【0043】

図4(b)に示す工程では、図4(a)に示すキャリア付金属箔203のキャリア板204を剥離層より金属箔205から剥離し、支持体201と接着層202とキャリア板204とを除去する。これにより、配線部品20と、外部端子21, 22が形成された側の絶縁層31の面が金属箔205により覆われた構造体220が形成される。

## 【0044】

図4(c)に示す工程では、金属箔205の下面に、接着剤213を介してキャリアフィルム214(第2支持層)を貼付する。接着剤213としては、例えば紫外線の照射によって接着力が低下するものを用いることができる。キャリアフィルム214としては、例えばダイシング用テープを用いることができる。

10

## 【0045】

図4(d)に示す工程では、図4(c)に示す接着剤211に紫外線を照射して接着力を低下させ、キャリアフィルム212と接着剤211とを除去する。これにより、構造体220を、金属箔205を配設した側に貼付したキャリアフィルム214により支持する。図4(a)～図4(d)に示す工程は、支持体201を剥離することと、構造体220の支持を金属箔205の側にて行うようにするものである。これにより、図4(d)において、構造体220を上面側(図において上側)から搭載のための機器によって支持することにより、金属箔205を搭載対象に向けて構造体220を搭載することを可能とする。なお、複数の構造体220を面付けして形成した場合などのように、必要に応じてダイシングにより構造体220を個片化することもできる。

20

## 【0046】

図5(a)に示す工程では、支持体231の上面に、キャリア付金属箔232を積層した支持基板230(第1支持基板)を形成する。支持体231としては、例えば、ガラス、アラミド、LCP(Liquid Crystal Polymer)繊維の織布や不織布などの補強材に、エポキシ樹脂やポリイミド樹脂等の熱硬化性樹脂を含浸させたコア材を用いることができる。キャリア付金属箔232は、キャリア層233と、キャリア層233の上面に剥離層(図示略)を介して積層された金属箔234とを有している。キャリア層233は、図示しない接着層により支持体231の上面に貼着される。キャリア層233は、例えば、厚さが35μm程度の銅板である。金属箔234は、例えば、厚さが20～35μm程度の銅箔である。

30

## 【0047】

図5(b)に示す工程では、金属箔234に構造体220(図4(d)参照)を搭載する搭載凹部234bを形成し、金属箔234の上面234aに外部端子41, 42を形成する。搭載凹部234bの深さは、図4(d)に示す構造体220の外部端子21, 22の面21a, 22aを、金属箔234の上面234aと同一の平面上に位置するように設定される。例えば、構造体220に含まれる金属箔205と、この構造体220を金属箔234に接着する接着剤を搭載凹部234bに埋め込むように、搭載凹部234bの深さを設定する。搭載凹部234bの深さは、例えば15μmとすることができます。

## 【0048】

搭載凹部234bは、例えばエッチング処理(ハーフエッチ)により形成することができる。金属箔234の上面234aにレジスト層を形成する。レジスト層の材料としては、耐エッティング性がある感光性のドライフィルムレジスト又は液状のフォトレジスト(例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト)等を用いることができる。例えば感光性のドライフィルムレジストを用いる場合には、金属箔234の上面234aにドライフィルムを熱圧着によりラミネートし、そのドライフィルムを露光・現像によりパターニングして上記のレジスト層を形成する。そして、レジスト層をエッチングマスクとして、金属箔234にハーフエッチングを施し、搭載凹部234bを形成する。そして、レジスト層を例えばアルカリ性の剥離液を用いて除去する。

40

## 【0049】

外部端子41, 42は、例えば電解めっき法により形成することができる。

50

金属箔 234 の表面に、外部端子 41, 42 を形成する位置に開口部を有するレジスト層を形成する。レジスト層は、耐めっき性を有する感光性のドライフィルムレジスト（例えば、ノボラック系樹脂やアクリル系樹脂等のドライフィルムレジスト）等を用いることができる。金属箔 234 の表面をドライフィルムによりラミネートし、そのドライフィルムをフォトリソグラフィ法によりパターニングして上記開口部を有するレジスト層を形成する。なお、液状のフォトレジスト（例えば、ノボラック系樹脂やアクリル系樹脂等の液状レジスト）を用いてレジスト層を形成してもよい。

#### 【0050】

そして、レジスト層をめっきマスクとして、金属箔 234 の上面 234a に、金属箔 234 をめっき給電層に利用した電解めっき法を施し、開口部内に表面処理層 41c, 42c と金属ポスト 41d, 42d を順次形成する。例えば、表面処理層 41c, 42c が Au / Ni 層である場合には、金属箔 234 の上面 234a に、厚さが 0.1 ~ 0.2 μm の Au 層と、厚さが 2 ~ 5 μm の Ni 層とをこの順番で積層して表面処理層 41c, 42c を形成する。次いで、表面処理層 41c, 42c の上に、Cu 層を積層して金属ポスト 41d, 42d を形成する。そして、レジスト層を例えればアルカリ性の剥離液を用いて除去する。

#### 【0051】

図 5 (c) に示す工程では、搭載凹部 234b に接着剤 55（例えればフィルム状の接着剤）と構造体 220 とを配置する。接着剤 55 の材料としては、例えれば、エポキシ樹脂やポリイミド樹脂等の絶縁樹脂を用いることができる。そして、接着剤 55 を硬化し、金属箔 234 の上に構造体 220 を固定する。このとき、搭載凹部 234b により、構造体 220 に含まれる配線部品 20 において、外部端子 21, 22 の面 21a, 22a は、外部端子 41, 42 の面 41a, 42a と同一の平面上に位置する。外部端子 41, 42 の面 41b, 42b は、構造体 220 に含まれる配線部品 20 の下面 20b とほぼ同一の平面上に位置する。

#### 【0052】

図 6 に示す工程では、絶縁層 51、配線層 43、絶縁層 52、配線層 44、ソルダレジスト層 53 を形成する。

先ず、外部端子 41, 42 と構造体 220（配線部品 20）を覆う絶縁層 51 を形成する。次いで、絶縁層 51 を貫通し、外部端子 41, 42 の面 41b, 42b の一部と、内部接続端子 IP1, IP2 の上面の一部を露出するビアホールを形成する。ビアホールは、例えれば CO<sub>2</sub> レーザや YAG レーザ等によるレーザ加工法によって形成することができる。レーザ加工法によりビアホールを形成した場合、必要に応じてデスマニア処理を行う。このとき、外部端子 41, 42 の面 41b, 42b は、構造体 220 に含まれる配線部品 20 の下面 20b とほぼ同一の平面上に位置する。このため、レーザ加工法により形成するビアホールによって、外部端子 41, 42 の面 41b, 42b と、内部接続端子 IP1, IP2 の上面とを、ほぼ同じ処理時間にて容易に露出させることができる。

#### 【0053】

次いで、絶縁層 51 の上面に、例えればセミアディティブ法によって配線層 43 を形成する。詳述すると、先ず、絶縁層 51 の上面及びビアホールの内面に無電解めっき法又はスパッタ法により、銅などからなるシード層を形成する。次いで、所望の位置に開口部を有するレジスト層を形成する。そして、シード層をめっき給電層に利用する電解めっき法（電解銅めっき法）を施し、レジスト層の開口部に、銅などからなる金属めっき層を形成する。レジスト層を除去した後、不要なシード層をエッティングにより除去する。これにより、配線層 43 が形成される。

#### 【0054】

次いで、上記の絶縁層 51 と同様にして、絶縁層 52 を形成する。そして、上記の配線層 43 と同様にして、配線層 44 を形成する。

次いで、絶縁層 52 の上面に、開口部 53X を有するソルダレジスト層 53 を形成する。ソルダレジスト層 53 は、例えれば、感光性のソルダレジストフィルムをラミネートし、

10

20

30

40

50

又は液状のソルダレジストを塗布し、当該レジストをフォトリソグラフィ法により露光・現像して所要の形状にパターニングすることにより得られる。ソルダレジスト層 53 の開口部 53X により、配線層 44 の一部が外部接続端子 E P 1 として露出される。

【0055】

図 7 (a) に示す工程では、図 6 に示すキャリア層 233 を金属箔 234 から剥離し、支持体 231 及びキャリア層 233 を除去する。

図 7 (b) に示す工程では、図 7 (a) に示す金属箔 234 を、例えばエッチングにより除去する。この金属箔 234 に対するエッチング処理において、外部端子 41, 42 の表面処理層 41c, 42c がエッチングストップとして機能する。

【0056】

図 8 (a) に示す工程では、金属箔 205 を覆う接着剤 55 を除去し、金属箔 205 の表面(図では下面)を露出させる。例えば、接着剤 55 を除去する方法として、サンドブラスト、レーザ加工、機械研磨、等の方法を利用することができる。この工程において、接着剤 55 以外の部分は、レジスト層により被覆され、除去のための処理から保護されている。レジスト層は、処理後に除去される。

【0057】

図 8 (b) に示す工程では、図 8 (a) に示す金属箔 205 を、例えばエッチングにより除去する。外部端子 21, 22 は、表面側(図において下面側)に金属層(Au層)21b, 22b を有している。また、外部端子 41, 42 は、表面側(図において下面側)に、表面処理層 41c, 42c (Au / Ni 層) を有している。これらは、エッチングストップ層として機能するため、金属箔 205 を選択的にエッチングして除去することができる。このように、金属箔 205 を除去し、配線基板 10 が得られる。

【0058】

次に、上記の配線基板 10 の作用を説明する。

図 2 (a) に示すように、半導体装置 1 は、配線基板 10 と、配線基板 10 の上面に実装された半導体素子 60, 70 を有している。配線基板 10 は配線部品 20 を有し、配線部品 20 を介して半導体素子 60, 70 が互いに接続される。

【0059】

図 2 (b) に示すように、配線基板 10 に対して半導体素子 60, 70 が実装される。半導体素子 60 は、電極端子 61, 62 を有している。電極端子 61, 62 の大きさとしては、例えば直径が 20 ~ 30  $\mu\text{m}$ 、高さは直径の 1.5 倍程度とすることができます。電極端子 61, 62 の材料としては、例えば銅又は銅合金を用いることができる。

【0060】

半導体素子 60 の電極端子 61 は、はんだ 81 により配線部品 20 の外部端子 21 に接続される。そして、電極端子 62 は、はんだ 82 により配線基板 10 の外部端子 41 に接続される。はんだ 81, 82 の材料としては、例えばスズ(Sn)と銀(Ag)の合金、Sn と Au の合金、Sn と Cu の合金、Sn と Ag と Cu の合金、等を用いることができる。例えば、Sn - Ag 系のはんだを使用する場合、245 度程度の温度でリフロー加熱を行うことができる。

【0061】

配線部品 20 の外部端子 21 の上面 21a は、絶縁層 51 に埋設された外部端子 41 の上面 41a と同一の平面上に位置している。従って、半導体素子 60 において、電極端子 61 を配線部品 20 の外部端子 21 に対して接続するとともに、電極端子 62 を配線基板 10 の外部端子 41 に対して接続することができる。このため、配線基板 10 に対して、同じ長さの電極端子 61, 62 によって半導体素子 60 を歩留まりよく接続することができ、接続の信頼性を確保することができる。また、電極端子 61, 62 の高さが多少ばらつくとしても、各電極端子 61, 62 の先端のはんだ 81, 82 によってそのばらつきを吸収することができる。

【0062】

同様に、半導体素子 70 は、電極端子 71, 72 を有している。電極端子 71, 72 の

10

20

30

40

50

大きさとしては、例えば直径が 20 ~ 30 μm、高さは直径の 1.5 倍程度とすることができる。電極端子 71, 72 の材料としては、例えば銅又は銅合金を用いることができる。

#### 【0063】

半導体素子 70 の電極端子 71 は、はんだ 83 により配線部品 20 の外部端子 22 に接続される。そして、電極端子 72 は、はんだ 84 により配線基板 10 の外部端子 42 に接続される。はんだ 83, 84 の材料としては、例えばスズ (Sn) と銀 (Ag) の合金、Sn と Au の合金、Sn と Cu の合金、Sn と Ag と Cu の合金、等を用いることができる。例えば、Sn - Ag 系のはんだを使用する場合、245 度程度の温度でリフロー加熱を行うことができる。

10

#### 【0064】

配線部品 20 の外部端子 22 の上面 22a は、絶縁層 51 に埋設された外部端子 42 の上面 42a と同一の平面上に位置している。従って、半導体素子 70 において、電極端子 71 を配線部品 20 の外部端子 22 に対して接続するとともに、電極端子 72 を配線基板 10 の外部端子 42 に対して接続することができる。このため、配線基板 10 に対して、同じ長さの電極端子 71, 72 によって半導体素子 70 を歩留まりよく接続することができ、接続の信頼性を確保することができる。また、電極端子 71, 72 の高さが多少ばらつくとしても、各電極端子 71, 72 の先端のはんだ 83, 84 によってそのばらつきを吸収することができる。

#### 【0065】

そして、半導体素子 60 と半導体素子 70 は、配線部品 20 を介して互いに接続される。配線部品 20 は、配線層 43, 44 と比較して微細に形成された配線層 23, 24 を有している。このため、半導体素子 60, 70 を実装する配線基板の全体にわたって微細な配線を形成する場合と比べ、製造コストを低減することができる。

20

#### 【0066】

また、図 1 (a) に示すように、配線部品 20 は、下面に内部接続端子 IP1, IP2 を有している。内部接続端子 IP1, IP2 は、配線層 43 に接続される。このため、配線層 43 と内部接続端子 IP1, IP2 を介して配線部品 20 に対して所望の信号や電源を供給することができる。

#### 【0067】

配線部品 20 を搭載した支持体 231 (金属箔 234) に対して配線層 43, 44 等を形成した。このような製造方法では、配線基板の絶縁層に配線部品 20 を配置するキャビティを形成する場合と比べて工程数が少なく、製造コストの低減を図ることができる。

30

#### 【0068】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1-1) 配線基板 10 には、半導体素子 60, 70 が実装される。配線基板 10 は、配線部品 20 を有している。配線部品 20 は、半導体素子 60, 70 の一部の端子を互いに接続する。配線部品 20 は、半導体素子 60 の電極端子 61 が接続される外部端子 21 と、半導体素子 70 の電極端子 71 が接続される外部端子 22 とを有している。配線部品 20 は、外部端子 21, 22 が配設された上面 20a と反対側の下面 20b に内部接続端子 IP1, IP2 を有している。配線基板 10 は、半導体素子 60 の電極端子 62 が接続される外部端子 41 と、半導体素子 70 の電極端子 72 が接続される外部端子 42 とを有している。配線基板 10 の絶縁層 51 は、配線部品 20 と外部端子 41, 42 とを埋設する。絶縁層 51 の下面には、外部端子 41, 42 と配線部品 20 の内部接続端子 IP1, IP2 とに接続された配線層 43 が形成されている。

40

#### 【0069】

そして、配線部品 20 の外部端子 21, 22 の上面 21a, 22a と、外部端子 41, 42 の上面 41a, 42a は、同一平面上に位置している。このため、半導体素子 60 において、電極端子 61 を配線部品 20 の外部端子 21 に対して接続するとともに、電極端子 62 を配線基板 10 の外部端子 41 に対して接続することができる。このため、配線基

50

板 1 0 に対して、同じ長さの電極端子 6 1 , 6 2 によって半導体素子 6 0 を歩留まりよく接続することができ、接続の信頼性を確保することができる。また、電極端子 6 1 , 6 2 の高さが多少ばらつくとしても、各電極端子 6 1 , 6 2 の先端のはんだ 8 1 , 8 2 によってそのばらつきが吸収されるため、接続信頼性を確保することができる。半導体素子 7 0 においても同様であり、接続信頼性を確保することができる。

#### 【 0 0 7 0 】

( 1 - 2 ) 半導体素子 6 0 と半導体素子 7 0 は、配線部品 2 0 を介して互いに接続される。配線部品 2 0 は、微細に形成された配線層 2 3 , 2 4 を有している。このため、半導体素子 6 0 , 7 0 を実装する配線基板の全体にわたって微細な配線を形成する場合と比べ、製造コストを低減することができる。

10

#### 【 0 0 7 1 】

( 1 - 3 ) 配線部品 2 0 は、下面に内部接続端子 I P 1 , I P 2 を有している。内部接続端子 I P 1 , I P 2 は、配線層 4 3 に接続される。このため、配線層 4 3 と内部接続端子 I P 1 , I P 2 を介して配線部品 2 0 に対して所望の信号や電源を供給することができる。

#### 【 0 0 7 2 】

( 1 - 4 ) 配線部品 2 0 を搭載した支持体 2 3 1 ( 金属箔 2 3 4 ) に対して配線層 4 3 , 4 4 等を形成した。このような製造方法では、配線基板の絶縁層に配線部品 2 0 を配置するキャビティを形成する場合と比べて工程数が少なく、製造コストの低減を図ることができる。

20

#### 【 0 0 7 3 】

##### ( 第 2 実施形態 )

以下、第 2 実施形態を図 9 ~ 図 1 4 に従って説明する。

なお、この実施形態において、上記実施形態と同じ構成部材については同じ符号を付してその説明を省略する場合がある。

#### 【 0 0 7 4 】

図 1 0 に示すように、半導体装置 1 a は、配線基板 1 0 a と、配線基板 1 0 a に実装された複数 ( 図 1 0 では 2 つ ) の半導体素子 6 0 , 7 0 と、アンダーフィル樹脂 8 5 とを有している。なお、図 1 0 は、半導体装置 1 a の一部であり、2 つの半導体素子 6 0 , 7 0 の間の接続部分を示している。

30

#### 【 0 0 7 5 】

半導体素子 6 0 は、複数の電極端子 ( ピラー ) 6 2 を介して配線基板 1 0 a に接続されている。同様に、半導体素子 7 0 は、複数の電極端子 ( ピラー ) 7 2 を介して配線基板 1 0 a に接続されている。配線基板 1 0 a は、2 つの半導体素子 6 0 , 7 0 を互いに接続するための配線部品 ( ブリッジボード ) 2 0 を有している。半導体素子 6 0 は、電極端子 6 1 を介して配線部品 2 0 に接続されている。同様に、半導体素子 7 0 は、電極端子 7 1 を介して配線部品 2 0 に接続されている。電極端子 6 1 , 6 2 , 7 1 , 7 2 の材料としては、例えば銅又は銅合金を用いることができる。

#### 【 0 0 7 6 】

アンダーフィル樹脂 8 5 は、配線基板 1 0 a と半導体素子 6 0 , 7 0 の間を充填するよう設けられている。アンダーフィル樹脂 8 5 の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。

40

#### 【 0 0 7 7 】

図 9 ( a ) に示すように、配線基板 1 0 a は、配線部品 2 0 、外部端子 4 1 , 4 2 、配線層 4 3 , 4 4 、絶縁層 1 0 1 , 5 2 、ソルダレジスト層 5 3 を有している。

配線部品 2 0 と外部端子 4 1 , 4 2 は、絶縁層 1 0 1 に埋設されている。絶縁層 1 0 1 は、配線部品 2 0 の上面 2 0 a と外部端子 4 1 , 4 2 の面 4 1 a , 4 2 a を露出するように形成されている。つまり、絶縁層 1 0 1 は、配線部品 2 0 の下面及び側面と、外部端子 4 1 , 4 2 の下面及び側面を覆うように形成されている。

#### 【 0 0 7 8 】

50

そして、本実施形態において、配線部品20の上面20aと外部端子41, 42の面41a, 42aは、絶縁層101の上面101aより下側に位置している。

図9(b)に示すように、配線部品20は、外部端子(パッド)21, 22、配線層23, 24, 25、絶縁層31, 32, 33を有している。外部端子21は、複数(本実施形態では2つ)の金属層21b, 21cにより形成されている。同様に、外部端子22は、複数(本実施形態では2つ)の金属層22b, 22cにより形成されている。上面側、つまり絶縁層31の上面31aに露出する金属層21b, 22bは、例えば金(Au)層である。埋設された金属層21c, 22cは、例えばニッケル(Ni)層である。

#### 【0079】

絶縁層31の下面には、配線層23が形成されている。配線層23は、絶縁層31を厚み方向に貫通して外部端子21, 22に接続されたビア配線と、ビア配線を介して外部端子21, 22と接続され、絶縁層31の下面に形成された配線パターンと、を有している。

#### 【0080】

絶縁層32は、絶縁層31の下面に、配線層23を覆うように形成されている。配線層24は、絶縁層32の下面に形成されている。配線層24は、絶縁層32を厚み方向に貫通するビア配線と、そのビア配線を介して配線層23と接続され、絶縁層32の下面に形成された配線パターンとを有している。

#### 【0081】

絶縁層33は、絶縁層32の下面に、配線層24を覆うように形成されている。配線層25は、絶縁層33の下面に形成されている。配線層25は、絶縁層33を厚み方向に貫通するビア配線と、そのビア配線を介して配線層24と接続され、絶縁層33の下面に形成された配線パターンとを有している。この配線層25において、絶縁層33の下面に形成された配線パターンは、内部接続端子IP1, IP2として機能する。

#### 【0082】

配線層23, 24, 25の材料としては、例えば銅又は銅合金を用いることができる。絶縁層31, 32, 33の材料としては、例えば感光性を有する樹脂(例えば、ポリイミド樹脂、シリコーン樹脂、フェノール樹脂、等)を用いることができる。

#### 【0083】

図9(a)に示すように、絶縁層101には、その絶縁層101の上面101aの側において、配線部品20の側面に対応する部分に、上面101a側に向かうにつれて拡開するテーパ状の開口部101Xが形成されている。開口部101Xと配線部品20との間に接着剤55が配設されている。

#### 【0084】

図9(a)に示す外部端子41, 42は、例えば円柱状に形成されている。外部端子41, 42の面41a, 42aは、配線部品20に含まれる外部端子21, 22の面21a, 22aと同一の平面上に位置している。そして、外部端子41, 42の面41b, 42bは、配線部品20に含まれる内部接続端子IP1, IP2の下面とほぼ同一の平面上に位置している。

#### 【0085】

外部端子41は、金属ポスト41dと、金属ポスト41dの上面に形成された表面処理層41cとを含む。同様に、外部端子42は、金属ポスト42dと、金属ポスト42dの上面に形成された表面処理層42cとを含む。金属ポスト41d, 42dの材料としては、例えば銅又は銅合金を用いることができる。表面処理層41c, 42cとしては、例えば、Ni/Au層(Ni層とAu層をこの順番で積層した金属層)とすることができる。

#### 【0086】

絶縁層101の下面には、配線層43が形成されている。配線層43は、絶縁層101を厚み方向に貫通して外部端子41, 42、配線部品20の内部接続端子IP1, IP2に接続されたビア配線と、ビア配線を介して外部端子41, 42、内部接続端子IP1, IP2に接続され、絶縁層101の下面に形成された配線パターンとを有している。絶縁

10

20

30

40

50

層 5 2 は、絶縁層 1 0 1 の下面に、配線層 4 3 を覆うように形成されている。配線層 4 4 は、絶縁層 5 2 を厚み方向に貫通して配線層 4 3 に接続されたビア配線と、ビア配線を介して配線層 4 3 に接続され、絶縁層 5 2 の下面に形成された配線パターンとを有している。

【 0 0 8 7 】

ソルダレジスト層 5 3 は、絶縁層 5 2 の下面に、配線層 4 4 の一部を被覆するように形成されている。ソルダレジスト層 5 3 には、配線層 4 4 の下面の一部を外部接続端子 E P 1 として露出する開口部 5 3 X が形成されている。外部接続端子 E P 1 には、この配線基板 1 0 a ( 図 1 0 に示す半導体装置 1 a ) を基板等に実装するために利用されるバンプ ( 例えばはんだバンプ ) が形成される。

10

【 0 0 8 8 】

配線層 4 3 , 4 4 の材料としては、例えば銅又は銅合金を用いることができる。絶縁層 1 0 1 , 5 2 の材料としては、例えば、エポキシ樹脂やポリイミド樹脂などの絶縁性樹脂、又はこれら樹脂にシリカやアルミナ等のフィラーを混入した樹脂材を用いることができる。ソルダレジスト層 5 3 の材料として、例えば感光性のドライフィルムレジスト又は液状のフォトレジスト ( 例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト ) 等が用いられる。

【 0 0 8 9 】

次に、上記の配線基板 1 0 a の製造方法を説明する。

なお、配線部品 2 0 の製造方法については前述の第 1 実施形態と同じであるため、説明及び図面を省略する。

20

【 0 0 9 0 】

図 1 1 ( a ) に示す工程では、支持体 2 3 1 の上面に、キャリア付金属箔 2 3 2 を積層した支持基板 2 3 0 ( 第 1 支持基板 ) を形成する。支持体 2 3 1 としては、例えば、ガラス、アラミド、L C P ( Liquid Crystal Polymer ) 繊維の織布や不織布などの補強材に、エポキシ樹脂やポリイミド樹脂等の熱硬化性樹脂を含浸させたコア材を用いることができる。キャリア付金属箔 2 3 2 は、キャリア層 2 3 3 と、キャリア層 2 3 3 の上面に剥離層 ( 図示略 ) を介して積層された金属箔 2 3 4 とを有している。キャリア層 2 3 3 は、図示しない接着層により支持体 2 3 1 の上面に貼着される。キャリア層 2 3 3 は、例えば、厚さが 3 5  $\mu$  m 程度の銅板である。金属箔 2 3 4 は、例えば、厚さが 5  $\mu$  m 程度の銅箔である。

30

【 0 0 9 1 】

図 1 1 ( b ) に示す工程では、金属箔 2 3 4 の上面 2 3 4 a に、補助層 2 4 1 , 2 4 2 を形成し、それらの補助層 2 4 1 , 2 4 2 の上に外部端子 4 1 , 4 2 を形成する。補助層 2 4 1 , 2 4 2 の材料としては、例えば、金属箔 2 3 4 と同じ材質である銅 ( C u ) を用いることができる。

【 0 0 9 2 】

詳述すると、金属箔 2 3 4 の上面 2 3 4 a に、外部端子 4 1 , 4 2 を形成する位置に開口部を有するレジスト層を形成する。レジスト層は、耐めっき性を有する感光性のドライフィルムレジスト ( 例えば、ノボラック系樹脂やアクリル系樹脂等のドライフィルムレジスト ) 等を用いることができる。金属箔 2 3 4 の上面 2 3 4 a をドライフィルムによりラミネートし、そのドライフィルムをフォトリソグラフィ法によりパターニングして上記開口部を有するレジスト層を形成する。なお、液状のフォトレジスト ( 例えば、ノボラック系樹脂やアクリル系樹脂等の液状レジスト ) を用いてレジスト層を形成してもよい。

40

【 0 0 9 3 】

そして、レジスト層をめっきマスクとして、金属箔 2 3 4 の上面 2 3 4 a に、金属箔 2 3 4 をめっき給電層に利用した電解めっき法 ( 電解銅めっき法 ) を施し、開口部内に補助層 2 4 1 , 2 4 2 を形成する。補助層 2 4 1 , 2 4 2 の厚さとしては、構造体 2 2 0 の金属箔 2 0 5 の厚さと接着層の厚さとに応じて設定され、例えば 1 5  $\mu$  m とすることができます。

50

## 【0094】

さらに、補助層241, 242の上に、表面処理層41c, 42cと金属ポスト41d, 42dを順次形成する。例えば、表面処理層41c, 42cがAu/Ni層である場合には、補助層241, 242の上面に、厚さが0.1~0.2μmのAu層と、厚さが2~5μmのNi層とをこの順番で積層して表面処理層41c, 42cを形成する。次いで、表面処理層41c, 42cの上に、Cu層を積層して金属ポスト41d, 42dを形成する。そして、レジスト層を例えばアルカリ性の剥離液を用いて除去する。

## 【0095】

図11(c)に示す工程では、金属箔234の上面234aに、接着剤55(例えばフィルム状の接着剤)と構造体220とを配置する。そして、接着剤55を硬化し、金属箔234の上に構造体220を固定する。このとき、構造体220に含まれる配線部品20において、外部端子21, 22の面21a, 22aは、外部端子41, 42の面41a, 42aと同一の平面上に位置する。外部端子41, 42の面41b, 42bは、構造体220に含まれる配線部品20の内部接続端子IP1, IP2の上面とほぼ同一の平面上に位置する。

10

## 【0096】

図12に示す工程では、絶縁層101、配線層43、絶縁層52、配線層44、ソルダレジスト層53を形成する。

先ず、外部端子41, 42と構造体220(配線部品20)を覆う絶縁層101を形成する。次いで、絶縁層101を貫通し、外部端子41, 42の面41b, 42bの一部と、内部接続端子IP1, IP2の上面の一部を露出するビアホールを形成する。ビアホールは、例えばCO2レーザやYAGレーザ等によるレーザ加工法によって形成することができる。レーザ加工法によりビアホールを形成した場合、必要に応じてデスマニア処理を行う。このとき、外部端子41, 42の面41b, 42bは、構造体220に含まれる配線部品20の内部接続端子IP1, IP2の上面とほぼ同一の平面上に位置する。このため、レーザ加工法により形成するビアホールによって、外部端子41, 42の面41b, 42bと、内部接続端子IP1, IP2の上面とを、ほぼ同じ処理時間にて容易に露出させることができる。

20

## 【0097】

次いで、絶縁層101の上面に、例えばセミアディティブ法によって配線層43を形成する。詳述すると、先ず、絶縁層101の上面及びビアホールの内面に無電解めっき法又はスパッタ法により、銅などからなるシード層を形成する。次いで、所望の位置に開口部を有するレジスト層を形成する。そして、シード層をめっき給電層に利用する電解めっき法(電解銅めっき法)を施し、レジスト層の開口部に、銅などからなる金属めっき層を形成する。レジスト層を除去した後、不要なシード層をエッチングにより除去する。これにより、配線層43が形成される。

30

## 【0098】

次いで、上記の絶縁層101と同様にして、絶縁層52を形成する。そして、上記の配線層43と同様にして、配線層44を形成する。

次いで、絶縁層52の上面に、開口部53Xを有するソルダレジスト層53を形成する。ソルダレジスト層53は、例えば、感光性のソルダレジストフィルムをラミネートし、又は液状のソルダレジストを塗布し、当該レジストをフォトリソグラフィ法により露光・現像して所要の形状にパターニングすることにより得られる。ソルダレジスト層53の開口部53Xにより、配線層44の一部が外部接続端子EP1として露出される。

40

## 【0099】

図13(a)に示す工程では、図12に示すキャリア層233を金属箔234から剥離し、支持体231及びキャリア層233を除去する。

図13(b)に示す工程では、図13(a)に示す金属箔234と補助層241, 242とを、例えばエッチングにより除去する。この金属箔234と補助層241, 242に対するエッチング処理において、外部端子41, 42の表面処理層41c, 42cがエッ

50

チングストップとして機能する。

【0100】

図14(a)に示す工程では、金属箔205を覆う接着剤55を除去し、金属箔205の表面(図では下面)を露出させる。例えば、接着剤55を除去する方法として、サンドブラスト、レーザ加工、機械研磨、等の方法を利用することができる。この工程において、接着剤55以外の部分は、レジスト層により被覆され、除去のための処理から保護されている。レジスト層は、処理後に除去される。

【0101】

図14(b)に示す工程では、図14(a)に示す金属箔205を、例えばエッチングにより除去する。外部端子21, 22は、表面側(図において下面側)に金属層(Au層)21b, 22bを有している。また、外部端子41, 42は、表面側(図において下面側)に、表面処理層41c, 42c(Au/Ni層)を有している。これらは、エッチングストップ層として機能するため、金属箔205を選択的にエッチングして除去することができる。このように、金属箔205を除去し、配線基板10aが得られる。

【0102】

以上記述したように、本実施形態によれば、前述の第1実施形態の効果に加え、以下の効果を奏する。

(2-1) キャリア付金属箔232の金属箔234の上面234aに、接着剤55によって、配線部品20を含む構造体220を、その配線部品20の外部端子21, 22が形成された面を覆う金属箔205を、金属箔234の上面234aに向けて接着する。そして、金属箔234の上面234aに補助層241, 242を形成し、その補助層241, 242に対して外部端子41, 42を積層して形成するようにした。この結果、補助層241, 242により、外部端子41, 42の面41a, 42aと、配線部品20の外部端子21, 22の面21a, 22aとを同一の平面上に位置するように形成することができる。

【0103】

(2-2)

補助層241, 242は、外部端子41, 42を形成するレジスト層を用いて、外部端子41, 42に先立って、例えば電解めっき法により形成される。このため、前述した第1実施形態のように、搭載凹部234bを形成するエッチング工程が不要となり、工程間の移動等に要する時間がかかるない。このため、配線基板10aの製造に要する時間の短縮を図ることができる。

【0104】

尚、上記各実施形態は、以下の態様で実施してもよい。

・上記実施形態では、図3(a)に示すように、支持体201の上面にキャリア付金属箔203を貼付して配線部品20(図4(d)参照)を製造するようにした。これに限らず、例えば、図3(a)に示す支持体201の上下両面にキャリア付金属箔203を貼付して複数の配線部品20を製造するようにしてもよい。

【0105】

同様に、上記第1実施形態では、図5(a)に示すように、支持体231の上面にキャリア付金属箔232を貼付して配線基板10(図8(b)参照)を製造するようにした。これに限らず、例えば、図5(a)に示す支持体231の上下両面にキャリア付金属箔232を貼付して複数の配線基板10を製造するようにしてもよい。第2実施形態についても、第1実施形態と同様に、支持体231の両面に配線基板10aを形成するようにしてもよい。

【0106】

・上記各実施形態では、支持体201の上面にキャリア付金属箔203を接着層202により接着し、そのキャリア付金属箔203の上面に配線部品20を形成した。これに対し、図15に示すように、支持体201の上面に接着層202を介して金属箔(銅箔)251を貼付し、その金属箔251の上面に配線部品20を形成した後、支持体201から

10

20

30

40

50

、金属箔 251 と配線部品 20（図 1（b）参照）を含む構造体を剥離するようにしてもよい。

## 【符号の説明】

【 0 1 0 7 】

1 , 1 a 半導体装置

10, 10a 配線基板

20 配線部品

21, 22 接続端子

2 1 a , 2 2 a 上面

4 1 , 4 2 接続端子

4 1 a , 4 2 a 上面

5 1 , 1 0 1 絶縁層

### 4.3 配線層

6 0 , 7 0

6 1 , 6 2 , 7 1 , 7 2

## I P 1 , I P 2 内部接続端子

10

【 図 1 】

【 四 2 】

【図3】

【図4】

【図5】

【図6】

【 义 7 】

【 四 8 】

【図9】

【図10】

### 【図 1 1】

【図12】

### 【図13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 23/12 L

(56)参考文献 特開2016-081961(JP, A)

特開2016-100599(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 23 / 12

H 01 L 25 / 04

H 01 L 25 / 18

H 05 K 3 / 46