등록특허 10-2340679

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년12월17일

(11) 등록번호 10-2340679

(24) 등록일자 2021년12월14일

- (51) 국제특허분류(Int. Cl.)

*G06F 11/07* (2006.01) *G06F 11/30* (2006.01)

- (52) CPC특허분류

*G06F 11/0796* (2013.01)

*G06F 11/3058* (2013.01)

- (21) 출원번호 10-2019-7002812

- (22) 출원일자(국제) 2016년09월15일

심사청구일자 2021년09월15일

- (85) 번역문제출일자 2019년01월28일

- (65) 공개번호 10-2019-0018171

- (43) 공개일자 2019년02월21일

- (86) 국제출원번호 PCT/US2016/051814

- (87) 국제공개번호 WO 2018/013156

국제공개일자 2018년01월18일

- (30) 우선권주장

15/208,388 2016년07월12일 미국(US)

- (56) 선행기술조사문헌

US20120187991 A1

US20040119521 A1

JP2006504303 A

WO2011118012 A1

- (73) 특허권자

어드밴스드 마이크로 디바이시즈, 인코포레이티드

미국 캘리포니아 95054 산타 클라라 어거스틴 드

라이브 2485

- (72) 발명자

콤러쉬 스티븐

미국 80528-9558 콜로라도 포트 콜린스 스위트

300 이스트 하모니 로드 2950

- 페흐라 아미타브

미국 80528-9558 콜로라도 포트 콜린스 스위트

300 이스트 하모니 로드 2950

(뒷면에 계속)

- (74) 대리인

박장원

전체 청구항 수 : 총 16 항

심사관 : 김재준

## (54) 발명의 명칭 전압 드롭을 위한 클록 조정

**(57) 요 약**

프로세서(100)는 프로세서에서 전압 드롭에 응답하여 하나 이상의 클록 신호(230)의 주파수를 조정한다. 프로세서는 복수의 기준 클록 신호(220, 221, 222, 223, 224, 225, 226, 227)를 생성함으로써 적어도 하나의 클록 신호를 생성하고, 기준 클록 신호의 각각은 동일 주파수이지만 상이한 위상을 갖는다. 프로세서는 또한 복수의 인에이블 신호를 생성하고, 각각의 인에이블 신호는 기준 클록 신호 중 대응하는 하나가 클록 신호를 생성하도록 사용되는지를 관리한다. 따라서 인에이블 신호는 클록 신호의 주파수를 결정한다. 전압 드롭을 검출하는 것에 응답하여, 프로세서가 클록 신호를 생성하도록 사용된 인에이블 신호를 조정해서, 클록 신호(droop)의 주파수를 감소시킨다.

**대 표 도 - 도1**

(72) 발명자

본 리차드 마틴

미국 80528-9558 콜로라도 포트 콜린스 스위트 300

이스트 하모니 로드 2950

영 바비 디.

미국 80528-9558 콜로라도 포트 콜린스 스위트 300

이스트 하모니 로드 2950

---

## 명세서

### 청구범위

#### 청구항 1

방법으로서,

프로세서에서 전압 강하를 검출함에 응답하여, 전압 검출 모듈에 직접 연결된 스트레치 제어 모듈(stretch control module)로부터 제공된 스트레치 인에이블 신호들의 세트를 이용하여 인에이블 신호들(enable signals)의 수정된 제 1 세트를 생성하도록, 클록 제어 모듈로부터 제공된 인에이블 신호들의 제 1 세트를 수정하는 단계; 및

인에이블 신호들의 수정된 제 1 세트에 기초하여, 제 1 클록 신호를 생성하는 단계

를 포함하고, 상기 제 1 클록 신호를 생성하는 단계는,

인에이블 신호들의 수정된 제 1 세트에 기초하여, 복수의 클록 신호들을 선택하는 단계;

상기 제 1 클록 신호를 생성하도록 상기 선택된 복수의 클록 신호들을 논리적으로 결합하는 단계;

프로세서에서 전압 강하를 검출함에 응답하여, 인에이블 신호들의 수정된 제 2 세트를 생성하도록, 인에이블 신호들의 제 2 세트를 수정하는 단계; 및

인에이블 신호들의 수정된 제 2 세트에 기초하여 제 2 클록 신호를 생성하는 단계를 포함하는 것을 특징으로 하는 방법.

#### 청구항 2

제1항에 있어서,

상기 인에이블 신호들의 제 1 세트를 수정하는 단계는,

제 1 주파수로부터 제 2 주파수로 제 1 클록 신호의 주파수를 변경하도록 상기 인에이블 신호들의 제 1 세트를 수정하는 단계를 포함하는 것을 특징으로 하는 방법.

#### 청구항 3

제2항에 있어서,

상기 제 2 주파수는 상기 제 1 주파수 미만인 것을 특징으로 하는 방법.

#### 청구항 4

제1항에 있어서,

상기 프로세서에서 전압 강하를 검출한 이후에, 상기 프로세서에서 전압 증가를 검출함에 응답하여, 인에이블 신호들의 수정된 제 2 세트를 생성하도록 상기 인에이블 신호들의 수정된 제 1 세트를 수정하는 단계; 및

상기 인에이블 신호들의 수정된 제 2 세트에 기초하여 제 1 클록 신호를 생성하는 단계

를 더 포함하는 것을 특징으로 하는 방법.

#### 청구항 5

제1항에 있어서,

상기 제 1 클록 신호를 생성하는 단계는 제 1 주파수를 가진 제1 클록 신호를 생성하는 단계를 포함하고; 그리고

상기 제 2 클록 신호를 생성하는 단계는 상기 제 1 주파수와는 상이한 제 2 주파수를 가진 제 2 클록 신호를 생성하는 단계를 포함하는 것을 특징으로 하는 방법.

## 청구항 6

방법으로서,

클록 제어 모듈에서 인에이블 신호들의 제 1 세트를 생성하는 단계;

인에이블 신호들의 제 1 세트에 기초하여 제 1 주파수에서 제 1 클록 신호를 생성하는 단계;

제 1 주파수의 제 1 클록 신호를 프로세서에 제공하는 단계;

상기 프로세서에서 전압 강하를 검출함에 응답하여, 제 1 클록 신호의 주파수를 제 1 주파수로부터 제 2 주파수로 변경하도록 전압 검출 모듈에 직접 연결된 스트레치 제어 모듈로부터 제공된 스트레치 인에이블 신호들의 세트를 이용하여 인에이블 신호들의 제 1 세트를 수정하는 단계, 상기 제 2 주파수는 상기 제 1 주파수와 상이하며;

인에이블 신호들의 제 2 세트를 생성하는 단계;

인에이블 신호들의 제 2 세트에 기초하여 제 3 주파수에서 제 2 클록 신호를 생성하는 단계;

제 2 주파수의 제 2 클록 신호를 상기 프로세서에 제공하는 단계; 및

상기 프로세서에서 전압 강하를 검출함에 응답하여, 제 2 클록 신호의 주파수를 제 3 주파수로부터 제 4 주파수로 변경하도록 인에이블 신호들의 제 1 세트를 수정하는 단계를 포함하며, 상기 제 4 주파수는 상기 제 3 주파수와 상이한 것을 특징으로 하는 방법.

## 청구항 7

제6항에 있어서,

상기 전압 강하 이후에, 프로세서에서 전압 증가를 검출함에 응답하여, 제 1 클록 신호의 주파수를 제 2 주파수로부터 제 1 주파수로 변경하도록 인에이블 신호들의 제 1 세트를 수정하는 단계를 더 포함하는 것을 특징으로 하는 방법.

## 청구항 8

제6항에 있어서,

상기 전압 강하 이후에, 프로세서에서 전압 증가를 검출함에 응답하여, 제 1 클록 신호의 주파수를 제 2 주파수로부터 제 3 주파수로 변경하도록 인에이블 신호들의 제 1 세트를 수정하는 단계를 더 포함하며, 상기 제 3 주파수는 제 1 주파수와 다르며 제 2 주파수와도 다른 것을 특징으로 하는 방법.

## 청구항 9

제6항에 있어서,

상기 제 1 클록 신호를 상기 프로세서와 연관된 캐시에 제공하는 단계를 더 포함하는 것을 특징으로 하는 방법.

## 청구항 10

제6항에 있어서,

상기 제 1 클록 신호를 생성하는 단계는,

상기 인에이블 신호들의 제 1 세트에 기초하여, 복수의 클록 신호들 중에서 클록 신호들의 서브세트를 선택하는 단계; 및

상기 제 1 클록 신호를 생성하도록, 선택된 복수의 클록 신호들을 결합하는 단계를 포함하는 것을 특징으로 하는 방법.

## 청구항 11

프로세서로서,

상기 프로세서에서 전압 강하를 검출하기 위한 전압 검출 모듈;

클록 제어 모듈에 의해 출력된 인에이블 신호들의 제 1 세트 및 복수의 제 1 클록 신호들을 수신하는 제 1 클록 생성 모듈, 상기 제 1 클록 모듈은 상기 클록 제어 모듈로부터의 인에이블 신호들의 제 1 세트 및 복수의 클록 신호들에 기초하여 제 1 클록 신호를 생성하고;

상기 전압 검출 모듈이 전압 강하를 나타냄에 응답하여 상기 인에이블 신호들의 제 1 세트를 수정하도록, 상기 전압 검출 모듈에 직접 연결되고 상기 제 1 클록 모듈에 연결되는 스트레치 제어 모듈, 상기 인에이블 신호들의 제 1 세트를 수정하기 위하여, 상기 스트레치 제어 모듈은 스트레치 인에이블 신호들의 세트를 상기 제 1 클록 모듈의 입력에 제공하며;

인에이블 신호들의 제 2 세트 및 복수의 제 1 클록 신호들을 수신하는 제 2 클록 생성 모듈, 상기 제 2 클록 생성 모듈은 인에이블 신호들의 제 2 세트 및 복수의 클록 신호들에 기초하여 제 2 클록 신호를 생성하고; 그리고 상기 전압 검출 모듈이 전압 강하를 나타냄에 응답하여, 인에이블 신호들의 제 2 세트를 수정하는 상기 스트레치 제어 모듈을 포함하는 것을 특징으로 하는 프로세서.

### 청구항 12

제11항에 있어서,

상기 스트레치 제어 모듈은,

제 1 클록 신호의 주파수를 제 1 주파수로부터 제 2 주파수로 변화시키기 위하여 상기 인에이블 신호들의 제 1 세트를 수정하는 것을 특징으로 하는 프로세서.

### 청구항 13

제12항에 있어서,

상기 제 2 주파수는 상기 제 1 주파수 미만인 것을 특징으로 하는 프로세서.

### 청구항 14

제11항에 있어서,

상기 스트레치 제어 모듈은,

상기 전압 검출 모듈이 프로세서에서 전압의 증가를 나타냄에 응답하여, 인에이블 신호들의 수정된 제 2 세트를 생성하도록, 인에이블 신호들의 수정된 제 1 세트를 수정하는 것을 특징으로 하는 프로세서.

### 청구항 15

제11항에 있어서,

상기 제 1 클록 모듈은,

인에이블 신호들의 제 1 세트에 기초하여 복수의 클록 신호들의 서브세트를 선택하고; 그리고 제 1 클록 신호를 생성하도록 상기 선택된 복수의 클록 신호들을 논리적으로 결합하는 것을 특징으로 하는 프로세서.

### 청구항 16

제11항에 있어서,

상기 제 1 클록 모듈은 제 1 주파수를 갖는 제 1 클록 신호를 생성하고; 그리고

상기 제 2 클록 모듈은 상기 제 1 주파수와는 상이한 제 2 주파수를 갖는 제 2 클록 신호를 생성하는 것을 특징으로 하는 프로세서.

### 청구항 17

삭제

### 청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

## 발명의 설명

### 기술 분야

[0001]

본 발명의 프로세서에 관한 발명이며 특히, 프로세서에서 하나 이상의 클록 신호의 주파수를 조정하기 위한 방법 및 프로세서에 관한 발명이다.

### 배경 기술

[0002]

프로세서는 일반적으로 프로세서의 모듈에서의 논리 연산을 동기화하여, 에러, 예컨대, 셋업 에러, 경합 조건 등을 방지하도록 하나 이상의 클록 신호를 채용한다. 모듈에 적용될 수 있는 최대 클록 주파수는 모듈의 트랜지스터를 위해 전압 허용값을 관리하는 모듈에 제공된 공급 전압에 적어도 부분적으로 의존한다. 그러나, 프로세서 모듈은 때때로 공급 전압의 전압 드롭(voltage droop)으로 지칭되는, 일시적인 감소를 겪는다. 모듈을 위해 클록 주파수를 조정하는 것의 실패는 프로세서의 전체 작동의 에러를 야기할 수 있다. 일부 프로세서는 모듈 클록 신호의 공칭 클록 주파수에 비해 감소된 주파수의 "예비용(spare)" 클록 신호를 생성함으로써 전압 드롭을 설명하고, 그리고 전압 드롭을 검출하는 것에 응답하여 모듈 클록 신호를 예비용 클록 신호로 일시적으로 교체한다. 그러나, 클록 신호의 교체는 교체 동안 운용상의 에러를 야기할 수 있고 그리고 복잡한 회로가 구현되게 요구할 수 있다.

### 발명의 내용

#### 도면의 간단한 설명

[0003]

본 개시내용이 더 잘 이해될 수도 있고, 그리고 본 개시내용의 수많은 특징 및 이점이 첨부된 도면을 참조함으로써 당업자에게 분명해진다. 상이한 도면에서 동일한 참조 부호의 사용은 유사하거나 또는 동일한 항목을 나타낸다.

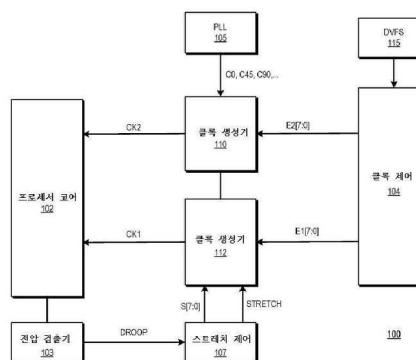

도 1은 일부 실시형태에 따른, 클록 신호를 생성하도록 사용된 인에이블 신호(enable signal)를 조정함으로써 전압 드롭에 응답하여 클록 신호를 조정하는 프로세서의 블록도.

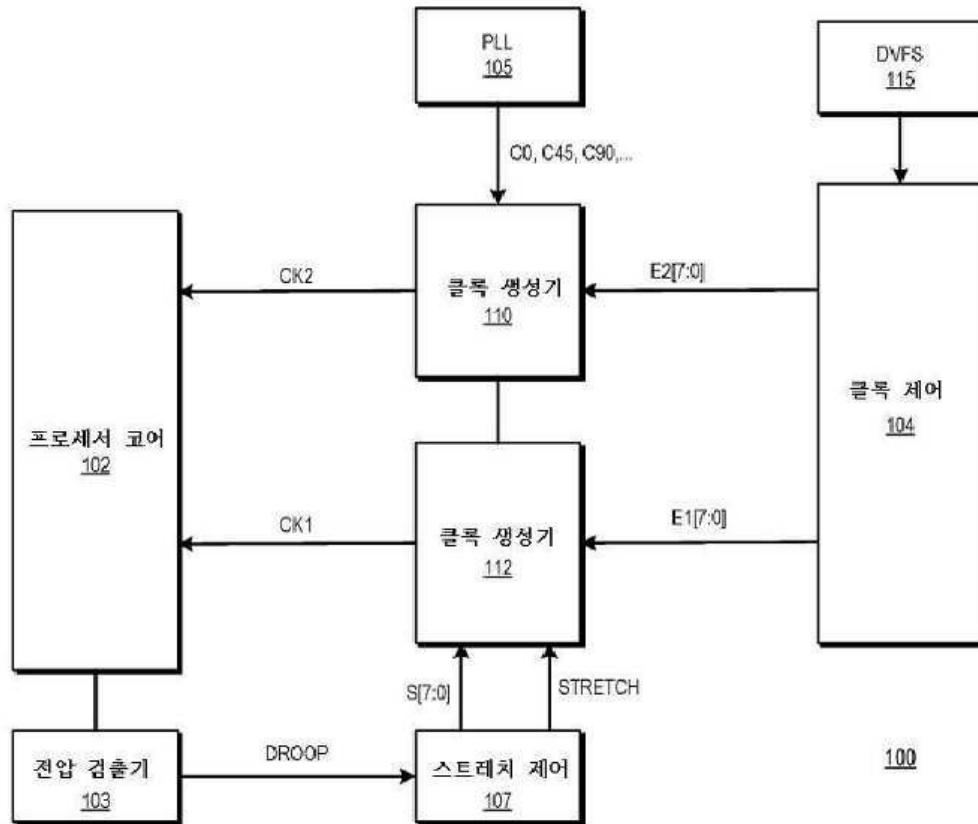

도 2는 일부 실시형태에 따른, 클록 신호를 생성하도록 사용된 인에이블 신호를 조정함으로써 도 1의 프로세서에서 클록 신호를 조정하는 실시예를 예시하는 도면.

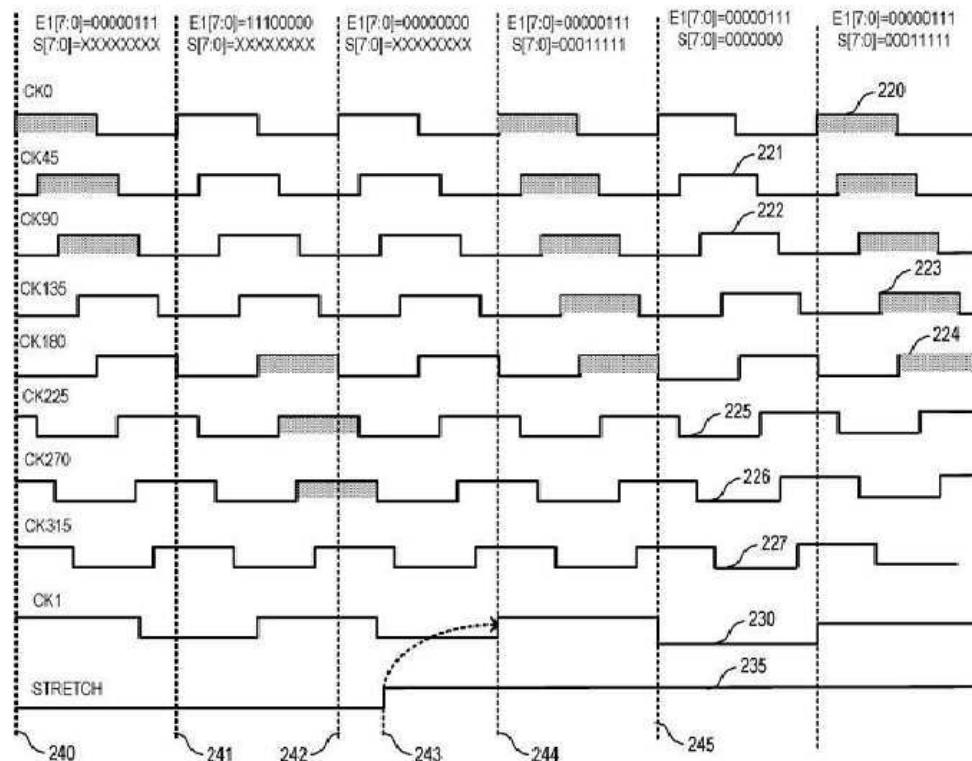

도 3은 일부 실시형태에 따른, 도 1의 프로세서의 클록 생성기의 부분을 예시하는 블록도.

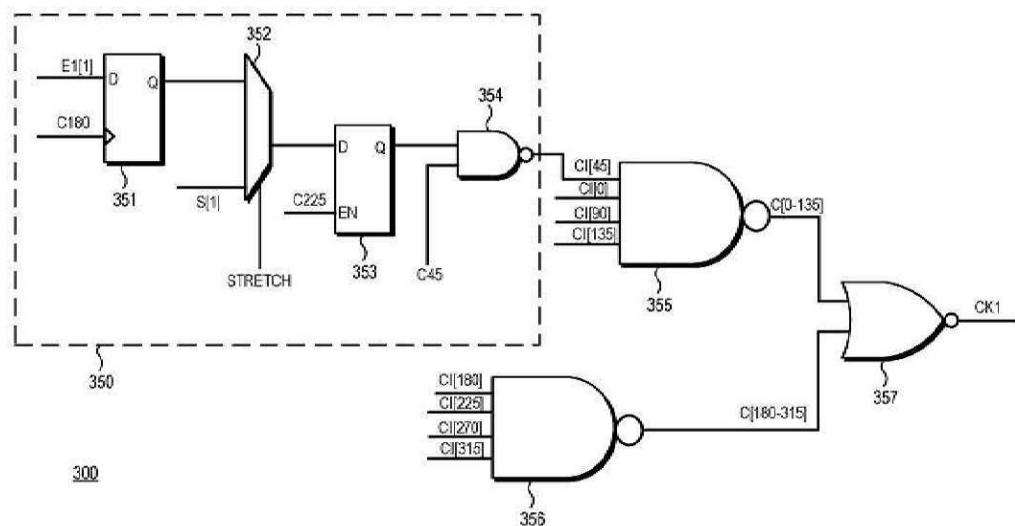

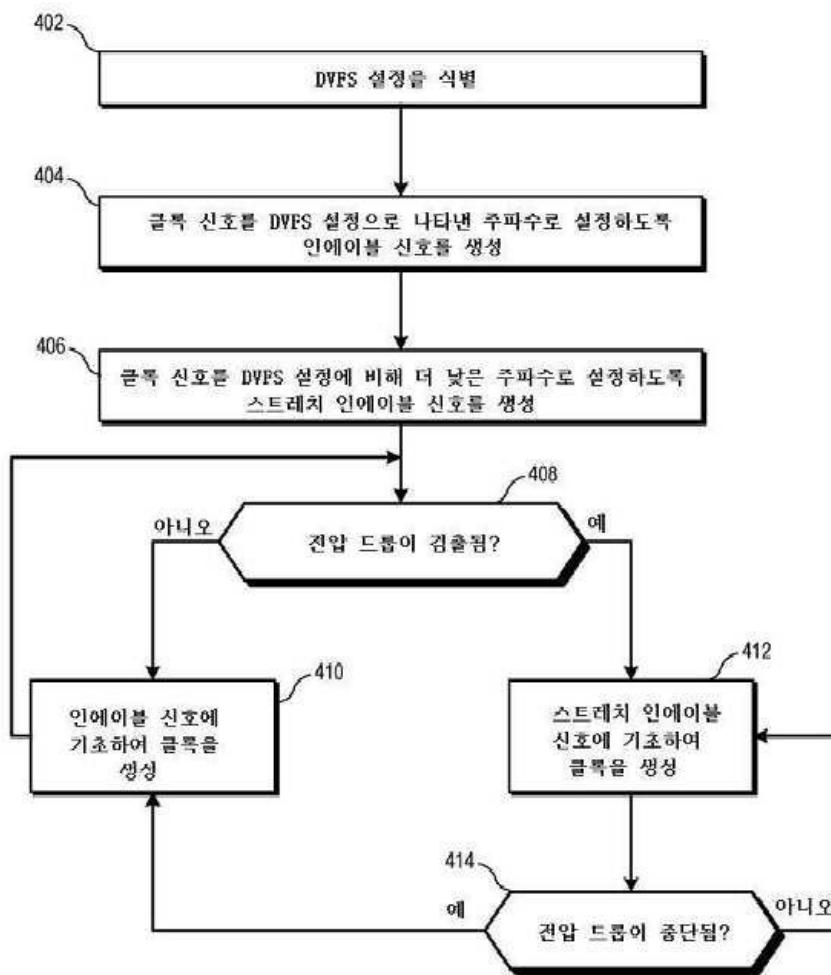

도 4는 일부 실시형태에 따른, 클록 신호를 생성하도록 사용된 인에이블 신호를 조정함으로써 전압 드롭에 응답하여 프로세서에서 클록 신호를 조정하는 방법의 흐름도.

### 발명을 실시하기 위한 구체적인 내용

[0004]

도 1 내지 도 4는 프로세서에서의 전압 드롭에 응답하여 프로세서에서 하나 이상의 클록 신호의 주파수를 조정하기 위한 기법을 개시한다. 프로세서는 복수의 기준 클록 신호(base clock signal)를 생성함으로써 적어도 하나의 클록 신호를 생성하고, 기준 클록 신호의 각각은 상이한 위상이지만 동일 주파수를 갖는다. 프로세서는 또한 복수의 인에이블 신호를 생성하고, 각각의 인에이블 신호는 기준 클록 신호 중 대응하는 하나가 클록 신호를 생성하도록 사용되는지를 관리한다. 따라서 인에이블 신호는 클록 신호의 주파수를 결정한다. 전압 드롭을 검출하는 것에 응답하여, 프로세서가 클록 신호를 생성하도록 사용된 인에이블 신호를 조정해서, 클록 신호의 주파수를 "스트레칭(stretching)" 또는 감소시키고 그리고 전압 드롭으로부터 발생된 에러를 감소시킨다.

[0005]

도 1은 일부 실시형태에 따른, 전압 드롭에 응답하여 클록 신호를 조정하는 프로세서(100)를 예시한다. 프로세

서(100)는 다양한 산출-가능 전자 디바이스, 예컨대, 서버, 데스크톱 컴퓨터, 노트북 컴퓨터, 태블릿 컴퓨터, 산출-가능 휴대용 핸드폰(예를 들어, "스마트 폰"), 산출-가능 시계 또는 다른 착용형 아이템, 개인용 정보 단말기(personal digital assistant: PDA), 게임 콘솔 등 중 임의의 것에 의해 구현될 수 있다. 도시된 실시예에서, 프로세서(100)는 프로세서 코어(102), 전압 검출기(103), 클록 제어 모듈(104), 위상 동기 루프(phase-locked loop: PLL)(105), 스트레치 제어 모듈(stretch control module)(107), 클록 생성기(110 및 112) 및 디지털 전압 및 주파수 스케일링(digital voltage and frequency scaling: DVFS) 모듈(115)을 포함한다.

[0006] 프로세서 코어(102)는 일반적으로 전자 디바이스 대신에 작동을 수행하도록 명령어(예를 들어, 컴퓨터 프로그램)의 세트를 실행하도록 구성된다. 명령어의 세트를 실행하도록, 프로세서 코어는 동기적 논리 구성요소, 논리 게이트 및 다른 컴포넌트로 각각 이루어진, 하나 이상의 모듈, 예컨대, 페치 스테이지(fetch stages), 디스패치 스테이지, 실행 장치, 메모리 제어기, 입력/출력 인터페이스, 캐시 등을 포함한다. 이 컴포넌트의 작동을 동기화하기 위해서, 프로세서 코어(102)는 하나 이상의 클록 신호를 채용한다. 도시된 실시예에서, 프로세서 코어(102)는 코어의 작동을 동기화하도록 "CK1" 및 "CK2"로 표기된 2개의 상이한 클록 신호를 채용한다. 일부 실시형태에서, 클록 신호(CK1 및 CK2)는 동시에 상이한 주파수일 수 있고, 그리고 프로세서 코어(102)의 상이한 모듈, 또는 모듈의 상이한 작동을 동기화하도록 사용될 수 있다.

[0007] 클록 신호(CK1 및 CK2)를 생성하기 위해서, 프로세서(100)는 클록 제어 모듈(104) 및 클록 생성기(110 및 112)와 함께 PLL(105)을 채용한다. 클록 제어 모듈(104)은 일반적으로 복수의 기준 중 임의의 기준에 기초하여 클록 신호(CK1 및 CK2)에 대한 주파수를 식별하도록 구성된다. 프로세서(100)의 실시예에서, DVFS 모듈(115)은 프로세서(100)에 대한 작동 조건에 기초하여 클록 신호(CK1 및 CK2)에 대한 주파수 정보를 공급하도록 구성된다. 예를 들어, 일부 실시형태에서 DVFS 모듈(115)은 프로세서(100)에 대한 전력 모드 정보를 수신하고, 전력 모드 정보는 복수의 전력 상태 중 하나의 선택을 나타낸다. 전력 모드 정보는 예를 들어, 프로세서 코어(102)의 성능 특성 등에 기초한 프로세서(100)의 성능 모니터(미도시)에 의해 공급된 정보에 기초하여, 프로세서 코어(102)에서 실행되는 작동 시스템에 의해 공급될 수 있다. 전력 모드 정보에 기초하여, DVFS 모듈(115)은 프로세서 코어(102)의 하나 이상의 모듈에 대한 기준 전압으로서 사용될 프로세서 코어(102)에 공급될 전압을 선택한다. 또한, 전력 모드에 기초하여, DVFS 모듈(115)은 선택된 전력 상태에 대응하는 클록 신호(CK1 및 CK2)에 대한 주파수를 나타내는 주파수 정보를 클록 제어 모듈(104)에 공급한다. 주파수 정보에 기초하여, 클록 제어 모듈(104)은 본 명세서에 더 설명된 바와 같이, 클록 신호(CK1 및 CK2)에 대한 주파수를 설정하도록 E1[7:0] 및 E2[7:0]로 표기된 인에이블 신호를 생성한다.

[0008] PLL(105)은 수정 발진기(미도시) 또는 다른 클록 공급원으로부터 기준 클록 신호(미도시)를 수신하고 그리고 기준 클록 신호에 기초하여 복수의 기준 클록 신호를 생성하도록 구성되고, 각각의 기준 클록 신호는 다른 기준 클록 신호와 위상이 다르다. 프로세서(100)의 실시예에서, PLL(105)은 C0, C45, C90, C135, C180, C225, C270 및 C315로 표기된, 그리고 집합적으로 C0 내지 C315로 지칭된, 8개의 기준 클록 신호를 생성한다고 가정된다. 기준 클록 신호(C0 내지 C315)의 각각은 다른 기준 클록 신호와 적어도 45도만큼 위상이 다르다. 특히, 기준 클록 신호(C45)는 기준 클록 신호(C0)와 45도만큼 위상이 다르고, 기준 클록 신호(C90)는 기준 클록 신호(C0)와 90도만큼 위상이 다르고, 기준 클록 신호(C135)는 기준 클록 신호(C0)와 135도만큼 위상이 다르고, 등이고, 클록 신호 지정 번호가 각도 수를 나타내는 것만큼 클록 신호는 클록 신호(C0)와 위상이 다르다.

[0009] 클록 생성기(110 및 112)는 인에이블 신호와 기준 신호(C0 내지 C315)의 세트를 수신하고, 그리고 수신된 인에이블 신호에 기초하여, 인에이블 신호에 기초한 주파수로 각각의 출력 클록 신호를 생성하기 위해서 기준 신호(C0 내지 C315)와 결합하도록 각각 구성된다. 따라서, 예를 들어, 클록 생성기(112)는 인에이블 신호(E1[7:0])를 수신하고 그리고 인에이블 신호에 기초하여 인에이블 신호(E1[7:0])에 기초한 주파수로 클록 신호(CK1)를 생성하기 위해서 기준 클록 신호(C0 내지 C315)와 결합한다. 일부 실시형태에서, 인에이블 신호(E1[7:0])의 각각은 클록 신호(C0 내지 C315) 중 상이한 클록 신호에 대응하고 그리고 인에이블 신호의 상태는 대응하는 클록 신호가 출력이 클록을 생성하도록 사용되는 하나 이상의 논리 게이트에 적용될지를 나타낸다. 이에 따라 클록 생성기(112)는 기준 클록 신호(C0 내지 C315)의 주파수(기저 주파수로서 지정됨)에 대한 주파수 분할기를 구현하여, 기저 주파수의 부분인 주파수를 갖게 클록 신호(C1)를 생성하고, 부분은 적어도 부분적으로 인에이블 신호(E1[7:0])에 의해 제어된다. 클록 생성기(110)는 기준 클록 신호(C0 내지 C315)에 기초하여 클록 신호(CK2)를 생성하도록 유사하게 구성되지만, 클록 신호의 주파수는 부분적으로 인에이블 신호(E2[7:0])에 의해 제어된다.

[0010] 프로세서 코어(102)에서 전압 드롭에 기인한 에러를 감소시키기 위해서, 프로세서(100)는 전압 검출기(103) 및 스트레치 제어 모듈(107)을 채용한다. 전압 검출기(103)는 프로세서 코어(102) 내의 하나 이상의 위치에서의 공급 전압을 모니터링하도록 구성된다. 모니터링된 전압이 명시된 문턱값까지 떨어진다고 검출하는 것에

응답하여, 전압 검출기(103)는 "DROOP"으로 표기된 출력 신호를 표명(assert)해서, 전압 드롭이 프로세서 코어(102)에서 검출된다는 것을 나타낸다.

[0011] 스트레치 제어 모듈(107)은 DROOP 신호의 표명(assertion)에 응답하여 신호의 2개의 세트를 생성하도록 구성된다. 특히, DROOP 신호의 표명에 응답하여, 스트레치 제어 모듈(107)은 클록 신호(CK1 및 CK2) 중 하나 또는 둘다가 "스트레칭"되어야 하거나 또는 전압 드롭에 응답하여 감소된 주파수를 갖는 것을 나타내도록 "STRETCH"로 표기된 신호를 표명한다. 또한, 스트레치 제어 모듈(107)은 S[7:0]로 표기된 스트레치 인에이블 신호의 세트를 생성한다. 일부 실시형태에서, 스트레치 인에이블 신호의 각각은 인에이블 신호(E2[7:0]) 또는 인에이블 신호(E1[7:0])에 대응한다. STRETCH 신호의 표명에 응답하여, 클록 생성기(112)가 인에이블 신호(E1[7:0])를 스트레치 인에이블 신호(S[7:0])로 교체해서, 검출된 전압 드롭에 응답하여 클록 신호(CK1)의 주파수를 변화시킨다. 유사하게, STRETCH 신호의 표명에 응답하여, 클록 생성기(110)가 인에이블 신호(E2[7:0])를 스트레치 인에이블 신호(S[7:0])로 교체해서, 따라서 클록 신호(CK2)의 주파수를 변화시킨다.

[0012] 적어도 하나의 실시형태에서, 스트레치 제어 모듈(107)은 인에이블 신호(E2[7:0])를 모니터링하고 그리고 스트레치 인에이블 신호(S[7:0])를 생성하여 클록 신호(CK1)의 주파수를 미리 결정된 양만큼 수정하도록 구성된다. 따라서, 예를 들어, 스트레치 제어 모듈(107)이 스트레치 인에이블 신호를 생성할 수 있어서 클록 신호(CK1)의 주파수가 전압 드롭에 응답하여, 인에이블 신호(E2[7:0])에 의해 설정된 바와 같이 클록 신호의 공칭 주파수에 비해 2로 분할된다. 일부 실시형태에서, 스트레치 제어 모듈은 신호(DROOP)로(또는 신호(DROOP)로 나타낸 복수의 제어 신호로) 나타낸 전압 드롭의 크기에 따라, 가변적인 양만큼 클록 신호(CK1)의 주파수를 변화시킨다. 따라서, 예를 들어, 프로세서 코어(102)에서 전압 드롭이 제1 문턱값을 초과한다면, 스트레치 제어 모듈(107)은 인에이블 신호(E1[7:0])에 의해 설정된 공칭 주파수에 비해, 클록 신호(CK1)의 주파수를 1.25로 분할하도록 스트레치 제어 신호(S[7:0])를 설정할 수 있고 그리고 프로세서 코어(102)에서 전압 드롭이 제2 문턱값을 초과한다면, 스트레치 제어 모듈(107)은 공칭 주파수에 비해, 클록 신호(CK1)의 주파수를 1.25로 분할하도록 스트레치 제어 신호(S[7:0])를 설정할 수 있다.

[0013] 전압 드롭 후에, 전압 검출기(103)는 프로세서 코어(102)에서 전압을 계속해서 모니터링한다. 모니터링된 전압이 전압의 드롭 전 레벨(pre-droop level)로 복귀되거나 또는 문턱값 레벨 위로 이동되는 것에 응답하여, 전압 검출기(103)는 DROOP 신호를 부정한다. 이에 응답하여, 스트레치 제어 모듈(107)이 STRETCH 신호를 부정해서, 클록 생성기(112)가 인에이블 신호(E1[7:0])에만 기초하여 CK1 클록 신호를 생성하는 것으로 복귀되고, 그리고 클록 생성기(110)가 인에이블 신호(E2[7:0])에만 기초하여 CK2 클록 신호를 생성하는 것으로 복귀되게 한다. 즉, 클록 신호(CK1 및 CK2)는 클록 제어 모듈(104)에 의해 설정된 바와 같은, 클록 신호의 전압-드롭 전 주파수(pre-voltage-droop frequency)로 복귀된다.

[0014] 위에 설명된 바와 같이, 프로세서 코어(102)에서의 전압 드롭에 응답하여, 프로세서(100)는 클록 신호를 생성하도록 사용된 인에이블 신호를 수정함으로써 프로세서 코어에 적용된 클록 신호의 클록 주파수를 감소시킨다. 이는 프로세서(100)가 원래의 클록 신호를 생성하도록 사용된 동일한 회로를 사용하여 전압 드롭에 응답하여 클록 주파수를 조정하게 해서, 전압 드롭을 조정하도록 필요한 회로의 양을 감소시킨다. 또한, 원래의 클록 신호를 생성하도록 사용된 동일한 회로를 채용함으로써, 프로세서(100)는 클록 주파수의 변화가 원래의 클록 신호의 위상과 동기화되는 것을 보장할 수 있어서, 클록 주파수가 프로세서 코어(102)에서의 활동의 중지를 필요로 하는 일 없이 변화되게 한다.

[0015] 일부 실시형태에서, 스트레치 제어 모듈(107)은 다른 클록 신호를 스트레칭되지 않은 상태로 유지하는 동안 클록 신호 중 하나를 스트레칭하는 것을 포함하여, 클록 신호(CK1 및 CK2)에 대한 주파수의 세트를 상이한 주파수로 조정할 수 있다는 것이 이해될 것이다. 예를 들어, 스트레치 제어 모듈(107)은 개별적으로 그리고 별도로 제어 가능한 스트레치 제어 신호(S1[7:0] 및 S2[7:0])의 2개의 세트를 생성할 수 있다. 또한, 일부 실시형태에서, 프로세서(100)는 프로세서(100)의 상이한 모듈에서 전압 드롭을 검출하기 위한 다수의 전압 검출기, 예컨대, 프로세서 코어에서 전압 드롭을 검출하기 위한 하나의 전압 검출기 및 캐시에서 전압 드롭을 검출하기 위한 상이한 전압 검출기를 포함할 수 있다. 상이한 전압 검출기에 의해 제공된 신호에 기초하여, 스트레치 제어 모듈(107)은 상이한 클록 신호의 주파수를 개별적으로 그리고 선택적으로 조정할 수 있다. 예를 들어, 전압 드롭이 프로세서 코어에서 검출되지 않기 때문에 프로세서 코어에 공급된 클록 신호를 스트레칭되지 않은 상태로 유지하는 동안, 캐시에서 전압 드롭을 검출하는 대응하는 전압 검출기에 응답하여 캐시에 공급된 클록 신호를 스트레칭한다.

[0016] 도 2는 일부 실시형태에 따른, 클록 생성기(110)의 예시적인 작동을 도면(200)을 예시한다. 도시된 실

시예에서, 도면(200)은 기준 클록 신호(C0 내지 C315) 중 상이한 하나에 각각 대응하는 파형(220 내지 227)을 예시한다. 따라서, 예를 들어, 파형(220)은 기준 클록 신호(C0)를 나타내고, 반면에 파형(221)은 기준 클록 신호(C45)를 나타낸다. 또한, 도면(200)은 클록 신호(CK1)를 나타내는 파형(230) 및 신호(STRETCH)를 나타내는 파형(235)을 예시한다.

[0017] 예시된 실시예에서, 시간(240)과 차후의 시간(243) 사이에서, STRETCH 신호는 전압 드롭이 프로세서 코어(102)에서 검출되지 않는 것을 나타내는, 부정 상태이다. 따라서, 시간(240)과 시간(244) 사이에서, 클록 신호(CK1)의 주파수는 클록 제어 모듈(104)에 의해 생성된 인에이블 신호(E1[7:0])에 의해 제어된다. 특히, 기준 클록 신호(CK180)의 제1 기간 동안, 시간(240)과 시간(241) 사이에서, 클록 제어 모듈(104)은 E1[7:0] 인에이블 신호를 값(00000111)으로 설정한다. 이에 응답하여, 시간(240)과 시간(241) 사이에서, 클록 생성기(110)는 CK1 클록 신호를 기준 클록 신호(CK0, CK45 및 CK90)의 논리적 "OR" 조합으로서 생성한다. 기준 클록 신호(CK180)의 차후의 기간 동안, 시간(241)과 시간(243) 사이에서, 클록 제어 모듈(104)은 E1[7:0] 인에이블 신호를 값(11100000)으로 설정한다. 이에 응답하여, 클록 생성기(110)는 CK1 클록 신호를 기준 클록 신호(CK180, CK225 및 CK270)의 논리적 "OR" 조합으로서 생성한다. 기준 클록 신호(CK180)의 다음의 기간 동안, 시간(242)과 시간(244) 사이에서, 클록 제어 모듈(104)이 E1[7:0] 인에이블 신호를 값(00000000)으로 설정해서, CK1 클록 신호가 부정된다.

[0018] 시간(240)과 시간(244) 사이에서 클록 제어 모듈(104)에 의해 생성될 때 인에이블 신호(E1[7:0])의 순 효과는 클록 생성기(110)가 1.75로 분할된 기준 클록 신호의 주파수와 같은 주파수를 가진 CK1 클록 신호를 생성하게 하는 것이다. 따라서, STRETCH 신호가 부정될 때, 클록 생성기(110)는 주파수 분할기로서 작동되고, 클록 생성기는 나눔수로 분할된 기준 클록 신호의 주파수와 같은 주파수를 가진 CK1 클록을 생성하고, 나눔수는 클록 생성기(110)에 의해 생성된 인에이블 신호의 시퀀스에 의해 설정된다. 클록 생성기(110)는 CK1 클록 신호를 DVFS 모듈(115)(도 1)에 의해 나타낸 주파수로 설정하도록, 인에이블 신호의 시퀀스를 조정함으로써 나눔수를 조정할 수 있다.

[0019] 도 2의 도시된 실시예에서, 시간(243)에서 STRETCH 신호가 표명되어, 전압 검출기(103)(도 1)가 프로세서 코어(102)에서 전압 드롭을 검출했다는 것을 나타낸다. 이에 응답하여, 기준 클록 신호(CK180)의 다음의 기간의 초반에(즉, 시간(244)에), 클록 생성기(110)는 클록 신호(CK1)를 생성하도록 E1[7:0] 인에이블 신호를 채용하는 것을 중단하고 그리고 스트레치 인에이블 신호(S[7:0])를 사용하기 시작한다. 또한, 스트레치 제어 모듈(107)이 시간(244) 전의 주파수에 비해 클록 신호(CK1)의 주파수를 감소시키도록 스트레치 인에이블 신호(S[7:0])를 생성하여, 전압 드롭을 조정한다.

[0020] 예시를 위해서, 시간(244)과 시간(245) 사이의 기준 클록 신호(CK180)의 기간 동안, 스트레치 제어 모듈(107)은 00011111의 값을 가진 스트레치 인에이블 신호(S[7:0])를 생성한다. 이에 응답하여, 시간(244)과 시간(245) 사이에서, 클록 생성기(110)는 CK1 클록 신호를 기준 클록 신호(CK0, CK45, CK90, CK135 및 CK180)의 논리적 "OR" 조합으로서 생성한다. 시간(245) 뒤를 잇는 기준 클록 신호(CK180)의 차후의 기간 동안, 스트레치 제어 모듈(107)이 00000000의 값을 가진 스트레치 인에이블 신호(S[7:0])를 생성하여, 클록 생성기(110)가 기준 클록 신호(CK180)의 이 기간 동안 클록 신호(CK1)를 부정하게 한다. STRETCH 신호가 표명되는 동안 기준 클록 신호(CK180)의 차후의 기간(도 2에 미도시) 동안, 스트레치 제어 모듈(107)은 스트레치 인에이블 신호(S[7:0])의 값을 00011111과 00000000 사이에서 교변한다. 스트레치 인에이블 신호에 대한 값의 이러한 시퀀싱은 클록 생성기(110)가 기준 클록 신호의 주파수의 절반인 주파수를 가진 클록 신호(CK1)를 생성하는 것을 발생시킨다. 즉, 스트레치 인에이블 신호(S[7:0])에 대한 값의 시퀀스는 클록 생성기(110)에 대한 나눔수를 2의 값을 갖도록 확립한다.

[0021] 도시된 실시예에서, 클록 제어 모듈(104)은 STRETCH 신호가 표명되는 동안 인에이블 신호(E1[7:0])에 대한 값을 계속해서 생성한다. 즉, 클록 제어 모듈(104)은 STRETCH 신호의 상태와 관계없이 인에이블 신호(E1[7:0])를 생성한다. 이것은 프로세서(100)가 전압 드롭의 개시 또는 중단에 응답하여, 클록 주파수 간에서 신속하게 전환되게 하고, 이러한 전환에 의해 인에이블 신호는 클록 신호(CK1)를 생성하도록 클록 생성기(110)에 의해 채용된다. 게다가, 이것은 클록 생성기(110)가 클록 신호(CK1)의 기간과 주파수의 임의의 변화를 동기화하게 하여, 프로세서 코어(102)가 주파수의 변화 동안 작동을 계속하게 한다. 이것은 클록 신호의 주파수가 전압 드롭의 개시 또는 중단에 응답하여 변화되는 동안 프로세서 코어(102)가 작동을 중단하게 하도록 요구되는 종래의 디자인에 비해 처리 및 전력 효율을 개선시킬 수 있다.

[0022] 일부 실시형태에서, STRETCH 신호의 표명에 응답하여 클록 신호의 상승 에지에서 클록 신호(CK1)의 기간을 변화시키기보다는, 클록 생성기(110)가 클록 신호(CK1)의 하강 에지에서 기간을 변화시킬 수 있어서, 클록 신호

(CK1)의 제1 스트레칭된 단계가 부정 단계 동안 이루어진다. 일부 프로세서에 대해, 하강 에지 동안 클록 신호의 기간을 변화시키는 것이 클록 생성기(110)가 클록 신호(CK1)의 스트레칭된 기간을 더 신속하게 시작하게 할 수 있어서, 부가적인 전력을 절약한다.

[0023] 또한, 일부 실시형태에서 STRETCH 신호가 부정될 때, 스트레치 제어 모듈(107)은 클록 신호(CK1)와 위상-정렬되는 S[7:0] 신호를 제공한다. 유사하게, STRETCH 신호가 표명될 때, 클록 제어 모듈(104)은 위상-정렬된 신호로서 E1[7:0] 신호를 스트레칭된 클록 신호(CK1)에 제공한다. S[7:0] 신호와 E1[7:0] 신호를 클록 신호(CK1)에 위상 정렬시킴으로써(각각, 스트레칭되지 않을 때 그리고 스트레칭될 때), 클록 신호(CK1)의 기간이 클록 에지에서 변화될 수 있어서, 클록 신호(CK1)의 변화로부터 발생된 에러를 감소시킨다.

[0024] 도 3은 일부 실시형태에 따른, 클록 생성기(110)의 부분(300)의 블록도를 예시한다. 부분(300)은 클록 하위-회로(350), NAND 게이트(355 및 356) 및 NOR 게이트(357)를 포함한다. 하위-회로(350)는 래치(351), 멀티플렉서(352), 래치(353) 및 NAND 게이트(354)를 포함한다. 래치(351)는 인에이블 신호(E1[1])를 수신하기 위한 데이터 입력부, 기준 클록 신호(C180)를 수신하기 위한 클록 입력부 및 출력부를 포함한다. 멀티플렉서(352)는 래치(351)의 출력부에 연결된 데이터 입력부, 스트레치 인에이블 신호(S[1])를 수신하기 위한 데이터 입력부 및 STRETCH 신호를 수신하기 위한 제어 입력부 및 출력부를 포함한다. 래치(353)는 멀티플렉서(352)의 출력부에 연결된 데이터 입력부, 기준 클록 신호(C225)를 수신하기 위한 인에이블 입력부 및 출력부를 포함한다. NAND 게이트(354)는 래치(353)의 출력부에 연결된 입력부, 클록 신호(C45)를 수신하기 위한 입력부 및 출력부를 포함한다.

[0025] 작동 시, 하위-회로(350)는 일반적으로 하위-회로(350)에 대한 적용 가능한 인에이블 신호로서 인에이블 신호(E1[1]) 또는 스트레치 인에이블 신호(S[1]) 중 하나를 선택하도록 그리고 기준 클록 신호(C45)가 클록 신호(CK1)의 기반 중 하나로서 사용되는지를 선택하도록 구성된다. 예시를 위해서, 래치(351)는 일반적으로 기준 클록 신호(C180)의 표명에 응답하여 인에이블 신호(E1[1])의 값을 래치하도록 구성된다. 멀티플렉서(352)는 STRETCH 신호의 상태에 기초하여 적용 가능한 인에이블 신호를 선택하도록 구성된다. 특히, STRETCH 신호가 부정된 것에 응답하여, 멀티플렉서(352)는 래치의 출력부에서 래치(351)의 출력을 적용한다. 따라서, STRETCH 신호가 부정된다면, 인에이블 신호(E1[1])의 래치된 값은 래치(353)의 입력부에 적용된다. 대조적으로, STRETCH 신호가 표명된다면, 멀티플렉서(352)는 스트레치 인에이블 신호(S[1])를 래치(353)의 입력부에 적용한다.

[0026] NAND 게이트(354)는 래치(353)에서 래치될 때 적용 가능한 인에이블 신호의 상태에 기초하여 그 출력부에서 기준 클록 신호(C45)를 선택적으로 적용하도록 구성된다. 따라서, 래치된 적용 가능한 인에이블 신호의 값이 부정된다면, 기준 클록 신호(C45)를 나타내는 것은 CK1 클록 신호의 기반으로서 사용되지 않고, NAND 게이트(354)는 그 출력을 표명된 상태로 유지한다. 래치된 적용 가능한 인에이블 신호의 값이 표명된다면, NAND 게이트의 출력은 기준 클록 신호(C45)의 반전된 표현일 것이다.

[0027] 클록 생성기(110)는 하위-회로(350)와 유사한 부가적인 하위-회로를 포함하고 그리고 명료성을 위해 부분(300)에서 예시되지 않는다. 특히, 클록 생성기(110)는 각각의 기준 클록 신호(C0 내지 C315)에 대한 대응하는 하위-회로를 포함하고, 각각의 하위-회로는 인에이블 신호(E1[7:0]) 중 상이한 하나 및 스트레치 인에이블 신호(S[7:0]) 중 상이한 대응하는 하나를 수신한다. 각각의 하위-회로는 STRETCH 신호의 상태에 기초하여 적용 가능한 인에이블 신호를 선택함으로써 그리고 대응하는 적용 가능한 인에이블 신호의 상태에 기초하여, 대응하는 클록 신호가 클록 신호(CK1)의 기반 중 하나로서 사용되는지를 선택함으로써 하위-회로(350)와 유사하게 작동된다.

[0028] NAND 게이트(355)는 기준 클록 신호(C0, C45, C90 및 C135)에 대한 하위-회로 중 상이한 하나에 각각 연결된 복수의 입력부 및 출력부를 포함한다. NAND 게이트(356)는 기준 클록 신호(C180, C225, C270 및 C315)에 대한 하위-회로 중 상이한 하나에 각각 연결된 복수의 입력부를 포함한다. NOR 게이트(357)는 NAND 게이트(355)의 출력부에 연결된 입력부, NAND 게이트(356)의 출력부에 연결된 입력부 및 클록 신호(CK1)를 제공하기 위한 출력부를 포함한다. 하위-회로(예를 들어, 하위-회로(350)), NAND 게이트(355 및 356) 및 NOR 게이트(357)의 구성 및 연결에 기초하여, CK1 클록 신호는 STRETCH 신호의 상태로 나타낸 바와 같이, 적용 가능한 인에이블 신호의 상태에 기초하여 그리고 적용 가능한 인에이블 신호에 의해 선택된 기준 클록 신호에 기초하여 생성된다.

[0029] 도 4는 적어도 하나의 실시형태에 따른, 프로세서 코어에서 전압 드롭을 검출하는 것에 응답하여 클록 신호의 주파수를 조정하는 방법(400)의 흐름도를 예시한다. 설명을 위해서, 방법(400)은 도 1의 프로세서(100)에서의 예시적인 구현예에 대하여 설명된다. 블록(402)에서, 클록 제어 모듈(104)은 DVFS 모듈(115)로부터 수신된 정보에 기초하여, 클록 신호(CK1 및 CK2)에 대한 공칭 주파수 설정을 식별한다. 블록(404)에서, 클록 제어 모듈

(104)은 CK2 및 CK1 클록 신호를 그 각각의 공칭 주파수 설정으로 설정하도록 E2[7:0] 및 E1[7:0] 인에이블 신호를 생성한다. 블록(406)에서, 스트레치 제어 모듈(107)은 CK1 및 CK2 클록 신호를 그 공칭 주파수에 비해 더 낮은 주파수로 설정하도록 스트레치 인에이블 신호(S[7:0])를 생성한다.

[0030] 블록(408)에서, 전압 검출기(103)는 전압 드롭이 존재하는지를 식별하도록 프로세서 코어(102)의 지점 중 하나 이상에서 전압을 모니터링한다. 만약 그렇지 않다면, 전압 검출기(103)는 DROOP 신호를 부정 상태로 유지하고 그리고 스트레치 제어 모듈(107)은 결국 STRETCH 신호를 부정 상태로 유지한다. 이에 응답하여, 방법 흐름이 블록(410)으로 이동되고, 그리고 클록 생성기(110 및 112)가 E2[7:0] 및 E1[7:0] 인에이블 신호에 기초하여 CK2 및 CK1 클록 신호를 생성하여, 클록 신호를 클록 신호의 각각의 공칭 주파수로 생성한다. 이어서 방법 흐름은 전압 검출기(103)가 프로세서 코어(102)에서 전압을 계속해서 모니터링하기 때문에 블록(408)으로 복귀된다.

[0031] 블록(408)으로 복귀해서, 전압 드롭을 검출하는 것에 응답하여, 전압 검출기(103)가 DROOP 신호를 표명하여, 스트레치 제어 모듈(107)이 STRETCH 신호를 표명하게 한다. 이에 응답하여, 방법 흐름이 블록(412)로 이동되고 그리고 클록 생성기(110 및 112)가 S[7:0] 스트레치 인에이블 신호에 기초하여 CK2 및 CK1 클록 신호를 생성하여, 따라서 클록 신호를 클록 신호의 더 느린 주파수로 생성한다. 방법 흐름이 블록(414)로 진행되고 그리고 전압 검출기(103)는 프로세서 코어(102)에서 전압이 전압의 공칭 레벨 또는 범위로 복귀되었는지를 모니터링한다. 만약 그렇지 않다면, 방법은 클록 생성기(110 및 112)가 CK2 및 CK1 클록 신호를 클록 신호의 더 느린 주파수로 유지할 때 블록(412)으로 복귀된다. 블록(414)에서, 전압 검출기(103)가 모니터링된 전압이 전압의 공칭 레벨 또는 범위로 복귀되었다고 식별한다면, 방법 흐름은 스트레치 제어 모듈(107)이 STRETCH 신호를 부정해서, 클록 생성기(110 및 112)가 E2[7:0] 및 E1[7:0] 인에이블 신호에 기초하여 CK2 및 CK1 클록 신호를 생성하는 것으로 복귀되게 하는, 블록(410)으로 진행된다.

[0032] 일부 실시형태에서, 위에서 설명된 기법의 특정한 양상은 소프트웨어를 실행하는 처리 시스템의 하나 이상의 프로세서에 의해 구현될 수 있다. 소프트웨어는 비일시적인 컴퓨터 관독가능 저장 매체에 저장되거나 또는 그렇지 않으면 명백히 포함된 실행 가능한 명령어의 하나 이상의 세트를 포함한다. 소프트웨어는 하나 이상의 프로세서에 의해 실행될 때, 위에서 설명된 기법의 하나 이상의 양상을 수행하도록 하나 이상의 프로세서를 조작하는, 명령어 및 특정한 데이터를 포함할 수 있다. 비일시적인 컴퓨터 관독가능 저장 매체는 예를 들어, 자기 또는 광 디스크 저장 디바이스, 고상 저장 디바이스, 예컨대, 플래시 메모리, 캐시, 임의 접근 메모리(random access memory: RAM) 또는 다른 비휘발성 메모리 디바이스 또는 디바이스들 등을 포함할 수 있다. 비일시적인 컴퓨터 관독가능 저장 매체에 저장된 실행 가능한 명령어는 하나 이상의 프로세서에 의해 해석되거나 또는 그렇지 않으면 실행 가능한 원시 코드, 어셈블리 언어 코드, 목적 코드 또는 다른 명령어 포맷일 수도 있다.

[0033] 전체 설명에서 위에서 설명된 모든 활동 또는 구성요소가 요구되진 않고, 특정한 활동 또는 디바이스의 일부가 요구되지 않을 수도 있고 그리고 설명된 것 외에, 하나 이상의 추가의 활동이 수행될 수도 있거나 또는 구성요소가 포함될 수도 있음에 유의해야 한다. 여전히 또한, 활동이 나열되는 순서가 반드시 활동이 수행되는 순서는 아니다. 또한, 개념이 특정한 실시형태를 참조하여 설명되었다. 그러나, 당업자는 다양한 수정 및 변화가 아래의 청구항에 제시된 바와 같이 본 개시내용의 범위로부터 벗어나는 일 없이 행해질 수 있다는 것을 이해한다. 따라서, 명세서 및 도면이 제한적인 의미라기보다는 예시적인 것으로 간주되고 그리고 모든 이러한 수정이 본 개시내용의 범위 내에 포함되는 것으로 의도된다.

[0034] 이득, 다른 이점 및 문제에 대한 해결책이 특정한 실시형태와 관련하여 위에 설명되었다. 그러나, 이득, 이점, 문제에 대한 해결책, 및 임의의 이득, 이점 또는 해결책이 발생되거나 또는 더 표명되게 할 수 있는 임의의 피처(들)는 임의의 또는 모든 청구항의 중요한, 필요한 또는 필수적인 피처로서 해석되지 않는다. 게다가, 위에 개시된 특정한 실시형태는 개시된 주제가 본 명세서의 교시내용의 이득을 가진 당업자에게 분명한, 상이하지만 등가의 방식으로 수정 및 실행될 수 있기 때문에 단지 예시적이다. 아래의 청구항에 설명된 것 외에, 본 명세서에 도시된 구성 또는 디자인의 상세사항에 대한 제한이 의도되지 않는다. 따라서 위에 개시된 특정한 실시형태가 수정 또는 수정될 수도 있고 그리고 모든 이러한 변동이 개시된 주제의 범위 내에 있는 것으로 간주되는 것이 분명하다. 따라서, 본 명세서에서 요구되는 보호는 아래의 청구항에 제시된 바와 같다.

## 도면

## 도면1

## 도면2

200

## 도면3

## 도면4

400