**【特許請求の範囲】****【請求項 1】**

第1の電圧を供給する電源制御回路と、

前記電源制御回路と第1の基準ノードとの間に直列に接続される第1および第2のトランジスタと、

前記第1のトランジスタと第2のトランジスタとの接続ノードと第2の基準ノードとの間に接続される第3および第4のトランジスタとを備え、

前記第1のトランジスタは、前記電源制御回路と前記第2のトランジスタとの間に接続され、第1の信号をゲートに受け、

前記第2のトランジスタは、前記第1のトランジスタと前記第1の基準ノードとの間に接続され、前記第1の信号に対応する第2の信号をゲートに受け、 10

前記第3のトランジスタは、前記第2の基準ノードと前記第4のトランジスタとの間に接続され、第3の信号をゲートに受け、

前記第4のトランジスタは、前記第3のトランジスタと前記接続ノードとの間に接続され、前記第3の信号に対応する第4の信号をゲートに受け、

前記第1の電圧と前記第1の基準ノードとの電位差は、前記第1の基準ノードと前記第2の基準ノードとの電位差よりも小さい

ことを特徴とするデコーダ回路。

**【請求項 2】**

第1の基準ノードと第2の基準ノードとの間に直列に接続される第1および第2のトランジスタと、 20

前記第1のトランジスタと第2のトランジスタとの接続ノードと前記第2の基準ノードとの間に直列に接続される第3および第4のトランジスタとを備え、

前記第1のトランジスタは、前記第2の基準ノードと前記第2のトランジスタとの間に接続され、第1の信号をゲートに受け、

前記第2のトランジスタは、前記第1のトランジスタと前記第1の基準ノードとの間に接続され、前記第1の信号に対応する第2の信号をゲートに受け、

前記第3のトランジスタは、前記第2の基準ノードと前記第4のトランジスタとの間に接続され、第3の信号をゲートに受け、

前記第4のトランジスタは、前記第3のトランジスタと前記接続ノードとの間に接続され、前記第3の信号に対応する第4の信号をゲートに受け、 30

前記第1, 第2, および第4のトランジスタの各々は、互いに同極性であることを特徴とするデコーダ回路。

**【請求項 3】**

請求項2において、

前記第1のトランジスタは、前記第2の基準ノードと前記第2のトランジスタとの間に直列に接続された複数のトランジスタによって構成され、

前記複数のトランジスタの各々は、前記第1の信号をゲートに受けることを特徴とするデコーダ回路。

**【請求項 4】**

請求項2において、

逆バイアス電圧を出力する基板制御回路をさらに備え、

前記第1のトランジスタは、前記基板制御回路からの逆バイアス電圧を基板に受けることを特徴とするデコーダ回路。

**【請求項 5】**

請求項4において、

前記基板制御回路は、前記第1の信号の信号レベルに応じて、順バイアス電圧および逆バイアス電圧のうちいずれか一方を出力し、

前記第1および第4のトランジスタの各々は、前記基板制御回路からの出力を基板に受け、 50

ことを特徴とするデコーダ回路。

【請求項 6】

第1の基準ノードと第2の基準ノードとの間に直列に接続される第1および第2のトランジスタと、

前記第1のトランジスタと前記第2のトランジスタとの接続ノードと前記第2の基準ノードとの間に直列に接続される第3および第4のトランジスタとを備え、

前記第1のトランジスタは、前記第2の基準ノードと前記第2のトランジスタとの間に接続され、第1の信号をゲートに受け、

前記第2のトランジスタは、前記第1のトランジスタと前記第1の基準ノードとの間に接続され、前記第1の信号に対応する第2の信号をゲートに受け、

前記第3のトランジスタは、前記第2の基準ノードと前記第4のトランジスタとの間に接続され、第3の信号をゲートに受け、

前記第4のトランジスタは、前記第3のトランジスタと前記接続ノードとの間に接続され、前記第3の信号に対応する第4の信号をゲートに受け、

前記第1のトランジスタは、

オンになった後、前記接続ノードの電位が前記第2の基準ノードの電位に達する前にオフになる

ことを特徴とするデコーダ回路。

【請求項 7】

請求項6において、

前記第1のトランジスタがオンであり前記第2のトランジスタがオフである期間は、前記第1のトランジスタがオフであり前記第2のトランジスタがオンである期間よりも短いことを特徴とするデコーダ回路。

【請求項 8】

請求項6において、

前記第1のトランジスタのゲート幅 / ゲート長比 (W / L 比) は、前記第2のトランジスタのゲート幅 / ゲート長比 (W / L 比) の2倍以下である

ことを特徴とするデコーダ回路。

【請求項 9】

第1の基準ノードと第2の基準ノードとの間に直列に接続される第1, 第2, および第3のトランジスタを備え、

前記第1のトランジスタは、前記第1の基準ノードと前記第2のトランジスタとの間に接続され、第1の信号をゲートに受け、

前記第2のトランジスタは、前記第1のトランジスタと前記第3のトランジスタとの間に接続され、第2の信号をゲートに受け、

前記第3のトランジスタは、前記第2のトランジスタと前記第2の基準ノードとの間に接続され、前記第2の信号に対応する第3の信号をゲートに受け、

前記第1のトランジスタは、前記第2のトランジスタと同極性である

ことを特徴とするデコーダ回路。

【請求項 10】

第1および第2のモードと、当該第1のモードから当該第2のモードへ移行するときまたは当該第2のモードから第1のモードへ移行するときに実行される第3のモードとを有するデコーダ回路であって、

第1の電位を受ける第1の基準ノードと接続ノードとの間に接続され、第1の信号をゲートに受ける第1のトランジスタと、

第2の電位を受ける第2の基準ノードと前記接続ノードとの間に接続され、前記第1の信号に対応する第2の信号をゲートに受ける第2のトランジスタと、

前記接続ノードと前記第2の基準ノードとの間に直列に接続される第3および第4のトランジスタと、

前記接続ノードにおける電位が前記第2の電位と所定電位との間であると前記第1およ

10

20

30

40

50

び第2のトランジスタの各々と前記接続ノードとを接続し、前記接続ノードにおける電位が前記第1の電位と前記所定電位との間であると前記第1および第2のトランジスタの各々と前記接続ノードとを非接続するスイッチ回路と、

前記第1または第2の電位に応じた電荷が蓄積される蓄積ノードと、

前記接続ノードと前記蓄積ノードとを接続または非接続するイコライズ回路とを備え、前記所定電位は、前記第1の電位と前記第2の電位との間の電位であり、

前記第3のトランジスタは、前記第2の基準ノードと前記第4のトランジスタとの間に接続され、第3の信号をゲートに受け、

前記第4のトランジスタは、前記第3のトランジスタと前記接続ノードとの間に接続され、前記第3の信号に対応する第4の信号をゲートに受け、

前記第1のモードになると、

前記イコライズ回路は非接続状態になり、前記第1のトランジスタはオンになり、前記第2のトランジスタはオフになり、前記蓄積ノードは前記第1の電位に応じた電荷が蓄積され、

前記第2のモードになると、

前記イコライズ回路は非接続状態になり、前記第1のトランジスタはオフになり、前記第2のトランジスタはオンになり、前記蓄積ノードは前記第2の電位に応じた電荷が蓄積され、

前記第3のモードになると、前記イコライズ回路は接続状態になることを特徴とするデコーダ回路。

#### 【請求項11】

請求項1、請求項2、請求項6、請求項10のうちいずれか1つにおいて、

前記第1および第2のトランジスタは、

第1および第2のモードと、

前記第1のモードから前記第2のモードへ移行するとき、または、前記第2のモードから前記第1のモードへ移行するときに実行される第3のモードとを有し、

前記第1のモードになると、前記第1のトランジスタはオンになり、前記第2のトランジスタはオフになり、

前記第2のモードになると、前記第1のトランジスタはオフになり、前記第2のトランジスタはオンになり、

前記第3のモードになると、前記第1および第2のトランジスタはオフになることを特徴とするデコーダ回路。

#### 【請求項12】

請求項1、請求項2、請求項6、請求項10のうちいずれか1つにおいて、

前記接続ノードにおける電位の変動に応じて、センスアンプを駆動するためのタイミング信号を出力するセンスアンプタイミング生成回路をさらに備えることを特徴とするデコーダ回路。

#### 【請求項13】

請求項9において、

前記第1のトランジスタと前記第2のトランジスタとの接続ノードにおける電位の変動に応じて、センスアンプを駆動するためのタイミング信号を出力するセンスアンプタイミング生成回路をさらに備えることを特徴とするデコーダ回路。

#### 【請求項14】

請求項1において、

前記電源制御回路と前記第1の基準ノードとの間に直列に接続される第1および第2のレプリカ用トランジスタと、

前記第1のレプリカ用トランジスタと前記第2のレプリカ用トランジスタとのレプリカ用接続ノードと前記第1の基準ノードとの間に直列に接続される第3および第4のレプリカ用トランジスタと、

10

20

30

40

50

前記レプリカ用接続ノードにおける電位の変動に応じて、センスアンプを駆動するためのタイミング信号を出力するセンスアンプタイミング生成回路とをさらに備え、

前記第1のレプリカ用トランジスタは、前記第1のトランジスタと同様の特性を有し、且つ、前記電源制御回路と前記第2のレプリカ用トランジスタとの間に接続され、前記第1の信号をゲートに受け、

前記第2のレプリカ用トランジスタは、前記第2のトランジスタと同様の特性を有し、且つ、前記第1のレプリカ用トランジスタと前記第1の基準ノードとの間に接続され、前記第2の信号をゲートに受け、

前記第3のレプリカ用トランジスタは、前記第3のトランジスタと同様の特性を有し、且つ、前記第2の基準ノードと前記第4のレプリカ用トランジスタとの間に接続され、前記第3の信号をゲートに受け、

前記第4のレプリカ用トランジスタは、前記第4のトランジスタと同様の特性を有し、且つ、前記第3のレプリカ用トランジスタと前記レプリカ接続ノードとの間に接続され、前記第4の信号をゲートに受けけることを特徴とするデコーダ回路。

#### 【請求項15】

請求項2、請求項6、請求項10のうちいずれか1つにおいて、

前記第1の基準ノードと前記第2の基準ノードとの間に直列に接続される第1および第2のレプリカ用トランジスタと、

前記第1のレプリカ用トランジスタと前記第2のレプリカ用トランジスタとのレプリカ用接続ノードと前記第2の基準ノードとの間に直列に接続される第3および第4のレプリカ用トランジスタと、

前記レプリカ用接続ノードにおける電位の変動に応じて、センスアンプを駆動するためのタイミング信号を出力するセンスアンプタイミング生成回路とを含み、

前記第1のレプリカ用トランジスタは、前記第1のトランジスタと同様の特性を有し、且つ、前記第2の基準ノードと前記第2のレプリカ用トランジスタとの間に接続され、前記第1の信号をゲートに受け、

前記第2のレプリカ用トランジスタは、前記第2のトランジスタと同様の特性を有し、且つ、前記第1のレプリカ用トランジスタと前記第1の基準ノードとの間に接続され、前記第2の信号をゲートに受け、

前記第3のレプリカ用トランジスタは、前記第3のトランジスタと同様の特性を有し、且つ、前記第2の基準ノードと前記第4のレプリカ用トランジスタとの間に接続され、前記第3の信号をゲートに受け、

前記第4のレプリカ用トランジスタは、前記第4のトランジスタと同様の特性を有し、且つ、前記第3のレプリカ用トランジスタと前記レプリカ用接続ノードとの間に接続され、前記第4の信号をゲートに受けけることを特徴とするデコーダ回路。

#### 【請求項16】

請求項9において、

前記第1の基準ノードと前記第2の基準ノードとの間に直列に接続される第1、第2、および第3のレプリカ用トランジスタと、

前記第1のレプリカ用トランジスタと第2のレプリカ用トランジスタとのレプリカ用接続ノードにおける電位の変動に応じて、センスアンプを駆動するためのタイミング信号を出力するセンスアンプタイミング生成回路とをさらに備え、

前記第1のレプリカトランジスタは、前記第1のトランジスタと同様の特性を有し、前記第1の基準ノードと前記第2のレプリカ用トランジスタとの間に接続され、前記第1の信号をゲートに受け、

前記第2のレプリカ用トランジスタは、前記第1のレプリカ用トランジスタと前記第3のレプリカ用トランジスタとの間に接続され、前記第2の信号をゲートに受け、

前記第3のレプリカ用トランジスタは、前記第2のレプリカ用トランジスタと前記第2

10

20

30

40

50

の基準ノードとの間に接続され、前記第3の信号をゲートに受けることを特徴とするデコーダ回路。

【請求項17】

請求項14または請求項15において、

前記第1および第3のレプリカ用トランジスタの各々の閾値電圧に応じた制御電圧を出力する基板制御回路をさらに備え、

前記第1および第3のレプリカ用トランジスタの各々は、前記基板制御回路からの制御電圧を基板に受ける

ことを特徴とするデコーダ回路。

【請求項18】

請求項1、請求項2、請求項6、請求項10のうちいずれか1つにおいて、

前記第3のトランジスタは、

半導体基板に形成され、且つ、所定の間隔で互いに平行に延びる第1、第2、第3の拡散層と、

前記半導体基板の上に形成され、当該第1および第2の拡散層に沿って延びる第1のゲート電極と、

前記半導体基板の上に形成され、当該第2および第3の拡散層に沿って延びる第2のゲート電極と、

前記第2の拡散層の上に形成され、且つ、前記第1のゲート電極と前記第2のゲート電極との間に位置し、当該第2の拡散層に沿って延びる第1層配線と、

前記第1および第2のゲート電極と前記第1層配線との上に形成され、かつ、当該第1層配線と電気的に接続され、前記第1および第2のゲート電極には電気的に接続されない第2層配線とを含む

ことを特徴とするデコーダ回路。

【請求項19】

請求項9において、

前記第2のトランジスタは、

半導体基板に形成され、且つ、所定の間隔で互いに平行に延びる第1、第2、第3の拡散層と、

前記半導体基板の上に形成され、当該第1および第2の拡散層に沿って延びる第1のゲート電極と、

前記半導体基板の上に形成され、当該第2および第3の拡散層に沿って延びる第2のゲート電極と、

前記第2の拡散層と電気的に接続され、且つ、前記第1のゲート電極と前記第2のゲート電極との間に位置し、当該第2の拡散層に沿って延びる第1層配線と、

前記第1および第2のゲート電極と前記第1層配線との上に形成され、かつ、当該第1層配線と電気的に接続され、前記第1および第2のゲート電極には電気的に接続されない第2層配線とを含む

ことを特徴とするデコーダ回路。

【請求項20】

請求項18または請求項19において、

前記第1層配線の長さは、

( (ゲート幅 × 0.1) / ゲート電極の分割数 ) 以上であり、

( (ゲート幅 × 1.0) / ゲート電極の分割数 ) 以下である

ことを特徴とするデコーダ回路。

【請求項21】

請求項1、請求項2、請求項6、請求項10において、

前記第4のトランジスタが有する閾値電圧の電圧値は、前記第1のトランジスタが有する閾値電圧の電圧値以上である

ことを特徴とするデコーダ回路。

10

20

30

40

50

**【請求項 22】**

請求項 9 において、

前記第 2 のトランジスタが有する閾値電圧の電圧値は、前記第 1 のトランジスタが有する閾値電圧の電圧値以上であることを特徴とするデコーダ回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、デコーダ回路に関し、さらに詳しくは、半導体記憶装置のワード線を駆動するためのデコーダ回路に関する。 10

**【背景技術】****【0002】**

従来、半導体記憶装置は、ワード線を駆動するためのデコーダ回路（ロウデコーダ）を備えている。特開平 8 - 236718 号公報（特許文献 1）に開示されたように、デコーダ回路（ロウデコーダ）は、第 1 デコーダ（デコーダ回路）と、第 2 デコーダ（ワード線ドライバ）とを含む。第 1 デコーダは、第 1 アドレス信号に応じて動作する。第 2 デコーダは、第 1 デコーダからの出力、および第 2 アドレス信号に応じて動作する。第 2 デコーダは、第 1 デコーダの出力を受けるノードと接地電圧を受ける接地ノードとの間に直列に接続された PMOS トランジスタ、NMOS トランジスタを有する。PMOS トランジスタおよび NMOS トランジスタの各々のゲートは、第 1 デコーダに入力される第 1 アドレス信号とは異なる第 2 アドレス信号を受ける。また、これらのトランジスタの接続ノードに発生する電圧は、ワード線駆動電圧として出力される。 20

**【特許文献 1】特開平 8 - 236718 号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

従来では、デコーダ回路を駆動させるために、第 2 デコーダの出力だけでなく、第 1 デコーダの出力も電源電位 Vdd から接地電位 Vss まで振幅する。ここで、デコーダ回路の駆動速度を速くしたり、デコーダ回路によって消費される電荷量を削減したりするためには、第 1 デコーダの出力の振幅を電源電位 Vdd から接地電位 Vss までの振幅よりも小さくすることが求められる。 30

**【0004】**

本発明は、処理速度を高速化し、かつ、電荷消費量の少なくすることを目的とする。

**【課題を解決するための手段】****【0005】**

この発明の 1 つの局面に従うと、デコーダ回路は、電源制御回路と、第 1 ~ 第 4 のトランジスタとを備える。電源制御回路は、第 1 の電圧を供給する。第 1 および第 2 のトランジスタは、電源制御回路と第 1 の基準ノードとの間に直列に接続される。第 3 および第 4 のトランジスタは、第 1 のトランジスタと第 2 のトランジスタとの接続ノードと第 2 の基準ノードとの間に接続される。第 1 のトランジスタは、電源制御回路と第 2 のトランジスタとの間に接続され、第 1 の信号をゲートに受ける。第 2 のトランジスタは、第 1 のトランジスタと第 1 の基準ノードとの間に接続され、第 1 の信号に対応する第 2 の信号をゲートに受ける。第 3 のトランジスタは、第 2 の基準ノードと第 4 のトランジスタとの間に接続され、第 3 の信号をゲートに受ける。第 4 のトランジスタは、第 3 のトランジスタと接続ノードとの間に接続され、第 3 の信号に対応する第 4 の信号をゲートに受ける。第 1 の電圧と第 1 の基準ノードとの電位差は、第 1 の基準ノードと第 2 の基準ノードとの電位差よりも小さい。 40

**【0006】**

上記デコーダ回路では、第 1 のトランジスタと第 2 のトランジスタとの接続ノード（第 1 の接続ノード）における電位の振幅を小さくすることができる。したがって、第 1 の接

続ノードへ充電される電荷量または第1の接続ノードから放電される電荷量を削減することができる。また、第1の接続ノードを充放電するために要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

#### 【0007】

この発明のもう1つの局面に従うと、デコーダ回路は、第1～第4のトランジスタを備える。第1および第2のトランジスタは、第1の基準ノードと第2の基準ノードとの間に直列に接続される。第3および第4のトランジスタは、第1のトランジスタと第2のトランジスタとの接続ノードと第2の基準ノードとの間に直列に接続される。第1のトランジスタは、第2の基準ノードと第2のトランジスタとの間に接続され、第1の信号をゲートに受ける。第2のトランジスタは、第1のトランジスタと第1の基準ノードとの間に接続され、第1の信号に対応する第2の信号をゲートに受ける。第3のトランジスタは、第2の基準ノードと第4のトランジスタとの間に接続され、第3の信号をゲートに受ける。第4のトランジスタは、第3のトランジスタと接続ノードとの間に接続され、第3の信号に対応する第4の信号をゲートに受ける。第1、第2、および第4のトランジスタの各々は、互いに同電極である。

#### 【0008】

上記デコーダ回路では、第1および第2のトランジスタを第4のトランジスタと同極性にすることによって、第1のトランジスタと第2のトランジスタとの接続ノードにおける電位の振幅を小さくすることができる。したがって、接続ノードに充電される電荷量または接続ノードから放電される電荷量を削減することができる。また、接続ノードを充放電するのに要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

#### 【0009】

この発明のさらにもう1つの局面に従うと、デコーダ回路は、第1～第4のトランジスタを備える。第1および第2のトランジスタは、第1の基準ノードと第2の基準ノードとの間に直列に接続される。第3および第4のトランジスタは、第1のトランジスタと第2のトランジスタとの接続ノードと第2の基準ノードとの間に直列に接続される。第1のトランジスタは、第2の基準ノードと第2のトランジスタとの間に接続され、第1の信号をゲートに受ける。第2のトランジスタは、第1のトランジスタと第1の基準ノードとの間に接続され、第1の信号に対応する第2の信号をゲートに受ける。第3のトランジスタは、第2の基準ノードと第4のトランジスタとの間に接続され、第3の信号をゲートに受ける。第4のトランジスタは、第3のトランジスタと接続ノードとの間に接続され、第3の信号に対応する第4の信号をゲートに受ける。第1のトランジスタは、オンになった後、接続ノードの電位が第2の基準ノードの電位に達する前にオフになる。

#### 【0010】

上記デコーダ回路では、第1のトランジスタと第2のトランジスタとの接続ノードの電位が第2の基準ノードの電位に達する前に第1のトランジスタをオフにすることによって、接続ノードに充電される電荷量または接続ノードから放電される電荷量を削減することができる。また、接続ノードを充放電するのに要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

#### 【0011】

この発明のさらにもう1つの局面に従うと、デコーダ回路は、第1の基準ノードと第2の基準ノードとの間に直列に接続される第1、第2、および第3のトランジスタを備える。第1のトランジスタは、第1の基準ノードと第2のトランジスタとの間に接続され、第1の信号をゲートに受ける。第2のトランジスタは、第1のトランジスタと第3のトランジスタとの間に接続され、第2の信号をゲートに受ける。第3のトランジスタは、第2のトランジスタと第2の基準ノードとの間に接続され、第2の信号に対応する第3の信号をゲートに受ける。

#### 【0012】

上記デコーダ回路では、第1のトランジスタと第2のトランジスタとの接続ノード（第

10

20

30

40

50

1の接続ノード)と第2のトランジスタと第3のトランジスタの接続ノード(第2の接続ノード)との間で電荷を分配することによって、各々の接続ノードの電位が調整される。また、第1の接続ノードにおける電位の振幅を小さくすることができる。したがって、第1の接続ノードに充電される電荷量または第1の接続ノードから放電される電荷量を削減することができる。また、第1の接続ノードを充放電するのに要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

#### 【0013】

この発明のさらにもう1つの局面に従うと、デコーダ回路は、第1～第3のモードを有する。第3のモードは、第1のモードから第2のモードへ移行するとき、または、第2のモードから第1のモードへ移行するときに実行される。デコーダ回路は、第1～第4のトランジスタと、スイッチ回路と、蓄積ノードと、イコライズ回路とを備える。第1のトランジスタは、第1の電位を受ける第1の基準ノードと接続ノードとの間に接続され、第1の信号をゲートに受ける。第2のトランジスタは、第2の電位を受ける第2の基準ノードと接続ノードとの間に接続され、第1の信号に対応する第2の信号をゲートに受ける。第3および第4のトランジスタは、接続ノードと第2の基準ノードとの間に直列に接続される。スイッチ回路は、接続ノードの電位が第2の電位と所定電位との間であると、第1および第2のトランジスタの各々と接続ノードとを接続する。所定電位は、第1の電位と第2の電位との間の電位である。また、スイッチ回路は、接続ノードの電位が第1の電位と所定電位との間であると、第1および第2のトランジスタの各々と接続ノードとを非接続する。蓄積ノードは、第1または第2の電位に応じた電荷が蓄積される。イコライズ回路は、接続ノードと蓄積ノードとを接続または非接続する。第3のトランジスタは、第2の基準ノードと第4のトランジスタとの間に接続され、第3の信号をゲートに受ける。第4のトランジスタは、第3のトランジスタと接続ノードとの間に接続され、第3の信号に対応する第4の信号をゲートに受ける。第1のモードになると、イコライズ回路は、非接続状態になる。第1のトランジスタはオンになり、第2のトランジスタはオフになる。蓄積ノードは、第1の電位に応じた電荷が蓄積される。第2のモードになると、イコライズ回路は、非接続状態になる。第1のトランジスタはオフになり、第2のトランジスタはオンになる。蓄積ノードは、第2の電位に応じた電荷が蓄積される。第3のモードになると、イコライズ回路は接続状態になる。

#### 【0014】

上記デコーダ回路では、第1のモードにおいて、接続ノードには第2の電位に応じた電荷が蓄積される。第2のモードにおいて、接続ノードには第1の電位に応じた電荷が蓄積される。第3のモードにおいて、接続ノードと蓄積ノードとが接続されるので、接続ノードの電位を第1の電位と第2の電位との間の値にすることができる。よって、接続ノードにおける電位の振幅を小さくすることができる。したがって、接続ノードに充電される電荷量または接続ノードから放電される電荷量を削減することができる。また、接続ノードを充放電するのに要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

#### 【発明の効果】

#### 【0015】

以上のように、第1のトランジスタと第2のトランジスタとの接続ノードにおける電位の振幅を小さくすることができる。したがって、接続ノードへ充電される電荷量または接続ノードから放電される電荷量を削減することができる。また、接続ノードを充放電するために要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、この発明の実施の形態を図面を参照して詳しく説明する。なお、図中同一または相当部分には同一の符号を付しその説明は繰り返さない。

#### 【0017】

10

20

30

40

50

## (第1の実施形態)

## &lt;構成&gt;

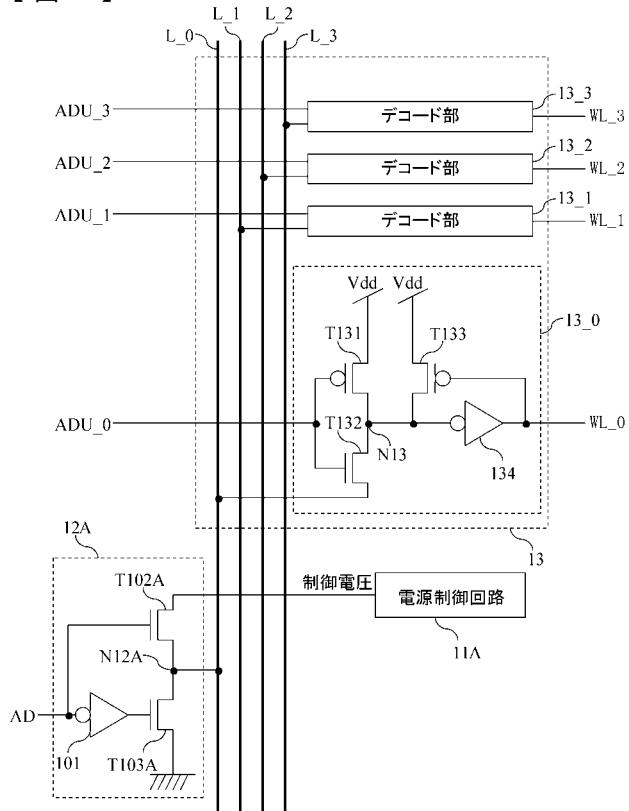

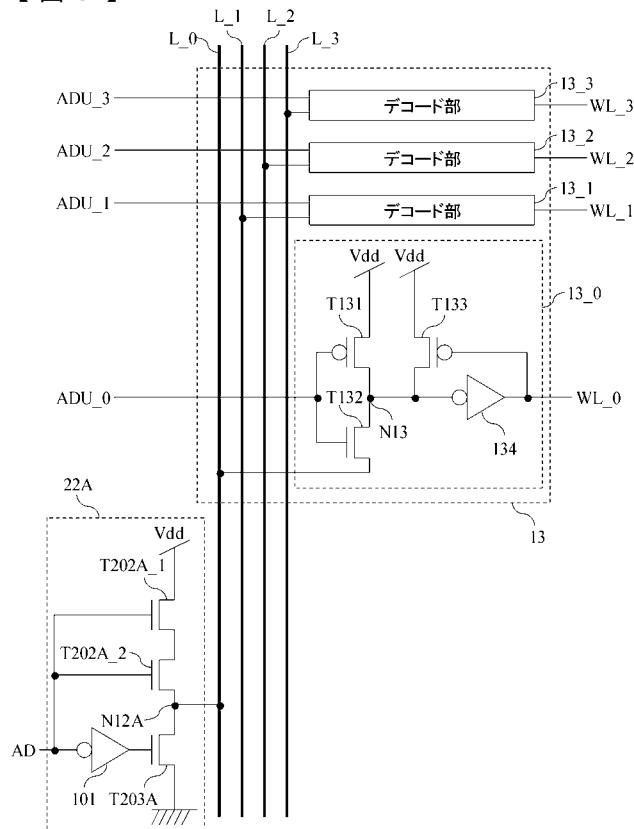

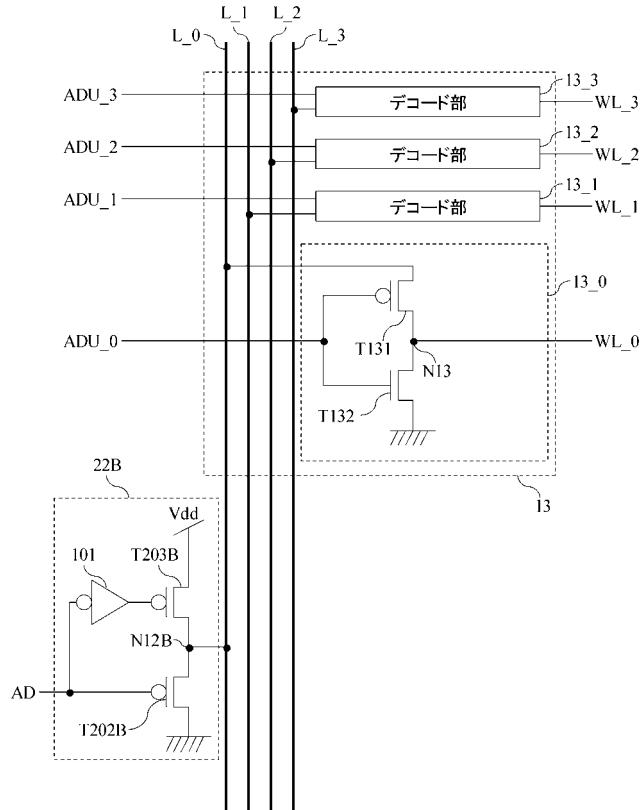

図1は、この発明の第1の実施形態によるデコーダ回路の構成を示す。デコーダ回路は、電源制御回路11Aと、プリデコーダ12Aと、ロウデコーダ13とを備える。この回路は、外部からのアドレス信号ADU\_0, ADU\_1, ADU\_2, ADU\_3と外部からのアドレス信号ADとに応じて、駆動信号WL\_0, WL\_1, WL\_2, WL\_3を出力する。例えば、アドレス信号ADU\_0～ADU\_3は上位ビットアドレスを示し、アドレス信号ADは下位ビットアドレスを示す。また、駆動信号WL\_0～WL\_3は、例えば、メモリアレイのワード線を駆動するための信号として利用される。

## 【0018】

電源制御回路11Aは、制御電圧を出力する。制御電圧の電圧値「Vdd1」は、電源ノードの電位「Vdd」よりも低い。

## 【0019】

プリデコーダ12Aは、配線L\_0に接続され、外部からのアドレス信号ADに応じて動作する。プリデコーダ12Aは、インバータ101と、トランジスタT102Aと、トランジスタT103Aとを含む。インバータ101は、アドレス信号ADを反転して出力する。トランジスタT102A, T103Aは、電源制御回路11Aと接地ノードとの間に直列に接続される。トランジスタT102Aは、電源制御回路11AとトランジスタT103Aとの間に接続され、アドレス信号ADをゲートに受ける。トランジスタT103Aは、トランジスタT102Aと接地ノードとの間に接続され、インバータ101の出力をゲートに受ける。また、トランジスタT102AとトランジスタT103Aとの接続ノードN12Aは、配線L\_0に接続される。

## 【0020】

ロウデコーダ13は、配線の本数に応じた個数（ここでは4つ）のデコード部13\_0, 13\_1, 13\_2, 13\_3を含む。デコード部13\_0～13\_3は、配線L\_0～L\_3に接続され、外部からのアドレス信号ADU\_0～ADU\_3に応じて駆動信号WL\_0～WL\_3を出力する。デコード部13\_0～13\_3は同様の内部構成を有するので、ここでは、代表してデコード部13\_0について説明する。

## 【0021】

デコード部13\_0は、トランジスタT131, T132, T133と、インバータ134とを含む。トランジスタT131, T132は、電源ノードとデコード部13\_0に対応する配線L\_0との間に直列に接続される。トランジスタT131は、電源ノードとトランジスタT132との間に接続され、外部からのアドレス信号ADU\_0をゲートに受ける。トランジスタT132は、トランジスタT131と配線L\_0との間に接続され、外部からのアドレス信号ADU\_0をゲートに受ける。トランジスタT133およびインバータ134は、トランジスタT131とトランジスタT132との接続ノードN13に発生する電圧を増幅させて、駆動信号WL\_0として出力するために設けられている。

## 【0022】

## &lt;動作&gt;

次に、図1に示したデコーダ回路による動作について説明する。なお、ここでは、トランジスタの各々の閾値電圧は考慮しないものとして説明する。

## 〔デコード部〕

アドレス信号ADU\_0が「Lレベル」である場合、トランジスタT131はオンになり、トランジスタT132はオフになる。したがって、接続ノードN13の電位は、電源ノードの電位「Vdd」と等しくなる。一方、アドレス信号ADU\_0が「Hレベル」である場合、トランジスタT131はオフになり、トランジスタT132はオンになる。したがって、接続ノードN13の電位は、接続ノードN12Aの電位と等しくなる。

## 〔プリデコーダ〕

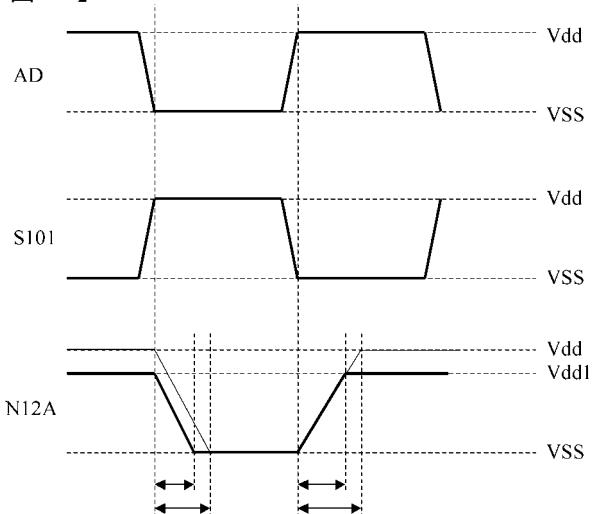

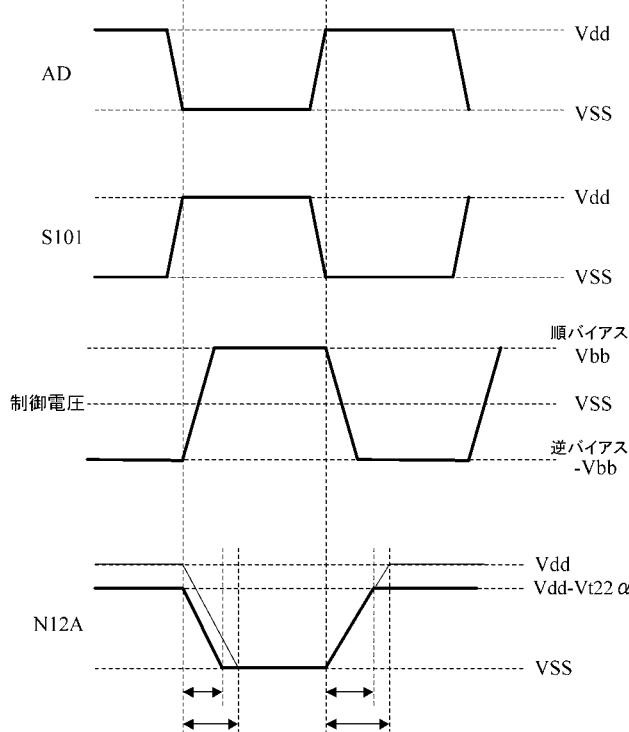

図2のように、アドレス信号ADが「Hレベル」である場合、インバータ101からの出力S101は「Lレベル」になる。したがって、トランジスタT102Aがオンになり

10

20

30

40

50

トランジスタ T 103A がオフになる。これにより、接続ノード N 12A の電位は、電源制御回路 11 からの制御電圧の電圧値「Vdd1」と等しくなる。このとき、アドレス信号 ADU\_0 が「H レベル」であっても、接続ノード N 13 の電位は「Vdd1」になり、接地ノードの電位「VSS」よりも高くなる。

【0023】

一方、アドレス信号 AD が「L レベル」である場合、インバータ 101 からの出力 S 1 0 1 は「H レベル」になる。したがって、トランジスタ T 102A がオフになりトランジスタ T 103A がオンになる。これにより、接続ノード N 12A の電位は、接地ノードの電位「VSS」と等しくなる。このとき、アドレス信号 ADU\_0 が「H レベル」であれば、接続ノード N 13 の電位は、接地ノードの電位「VSS」になる。

10

【0024】

ここで、トランジスタ T 102A が電源ノードとトランジスタ T 103A との間に接続されている場合（ケース 1）と比較すると、本実施形態では、接続ノード N 12A に蓄積される電荷量が少ないので、放電時間および充電時間が短くなる。

【0025】

<効果>

以上のように、トランジスタ T 102A の一端に供給される電圧を電源ノードの電位「Vdd」よりも低くすることによって、接続ノード N 12A における電位の振幅を小さくすることができる。したがって、接続ノード N 12A へ充電される電荷量を削減することができる。また、接続ノード N 12A を充放電するために要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

20

【0026】

また、本実施形態では、プリデコーダが配線 L\_0 に接続されている例について説明したが、他の配線 L\_1, L\_2, L\_3 の各々にプリデコーダが 1 つずつ接続されている場合も、各々の配線において同様の効果を得ることができる。

【0027】

また、図 1 では、デコーダ回路は 1 つのデコーダ回路を備えているが、2 つ以上のデコーダ回路を備えていても良い。つまり、本実施形態では、1 つの配線に対して 1 つのデコード部が接続されているが、1 つの配線に対して 2 つ以上のデコード部が接続されていても良い。

30

【0028】

また、図 1 では、トランジスタ T 102A, T 103A は「N 型」のトランジスタであるが、「P 型」のトランジスタであっても構わない。

【0029】

（第 2 の実施形態）

<構成>

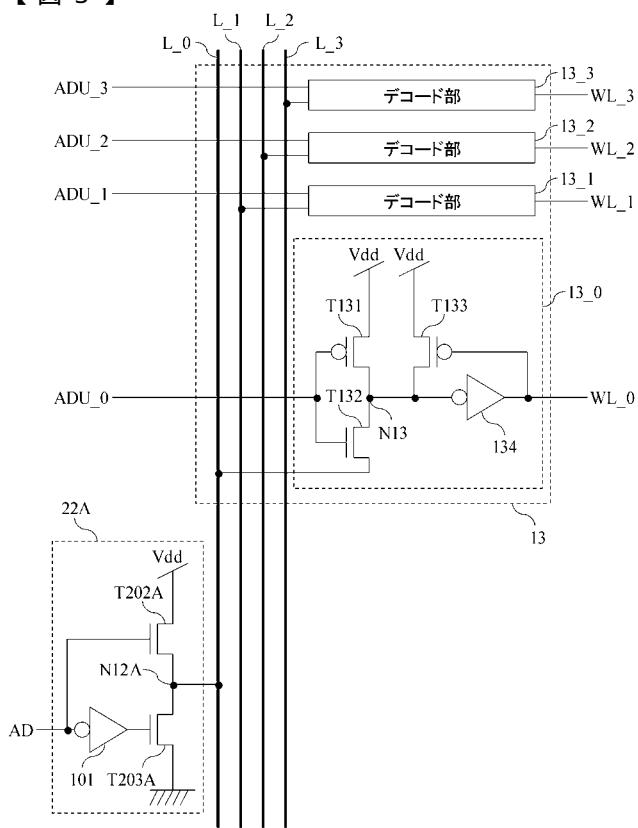

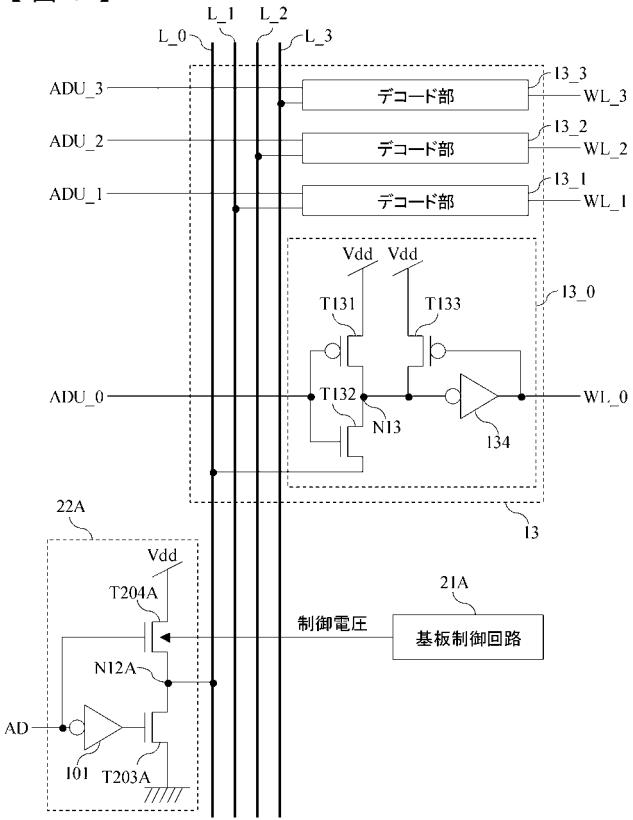

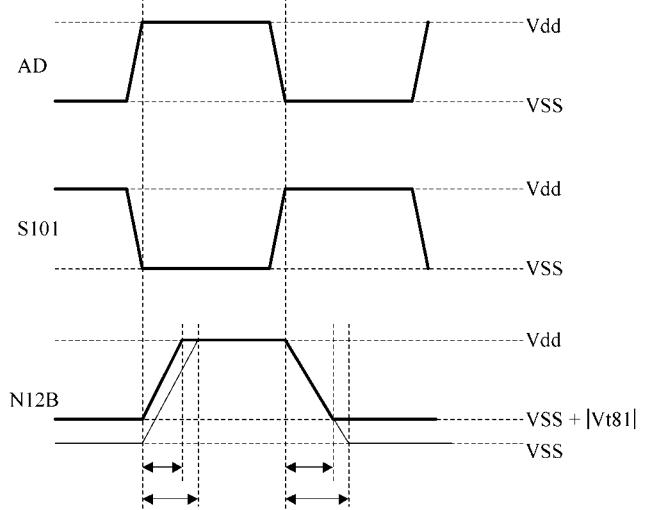

図 3 は、この発明の第 2 の実施形態によるデコーダ回路の構成を示す。この回路は、図 1 に示した電源制御回路 11A, プリデコーダ 12A に代えて、プリデコーダ 22A を備える。その他の構成は図 1 と同様である。プリデコーダ 22A は、図 1 に示したトランジスタ T 102A, T 103A に代えて、トランジスタ T 202A, T 203A を含む。その他の構成は、図 1 と同様である。トランジスタ T 202A, T 203A の各々は、トランジスタ T 102A, T 103A と同極性である。例えば、トランジスタ T 102A が「N 型」であれば、トランジスタ T 202A, T 203A も「N 型」である。

40

【0030】

<動作>

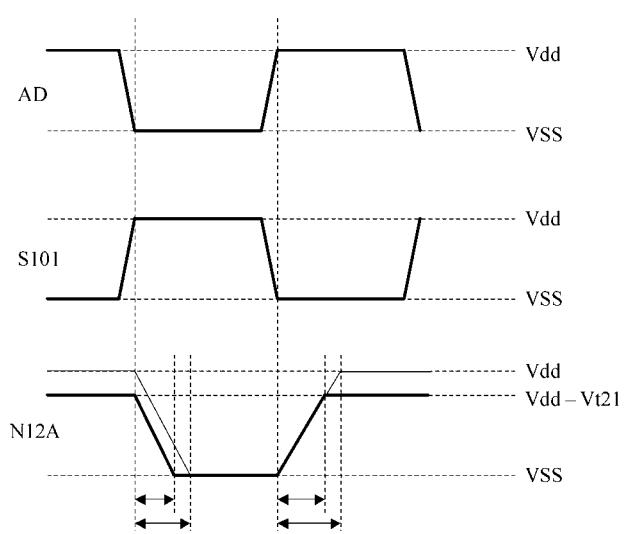

次に、図 3 に示したプリデコーダ 22A による動作について説明する。なお、ここでは、トランジスタ T 202A の閾値電圧を「Vt21」とし、トランジスタ T 203A, T 103A の閾値電圧は考慮しないものとする。

【0031】

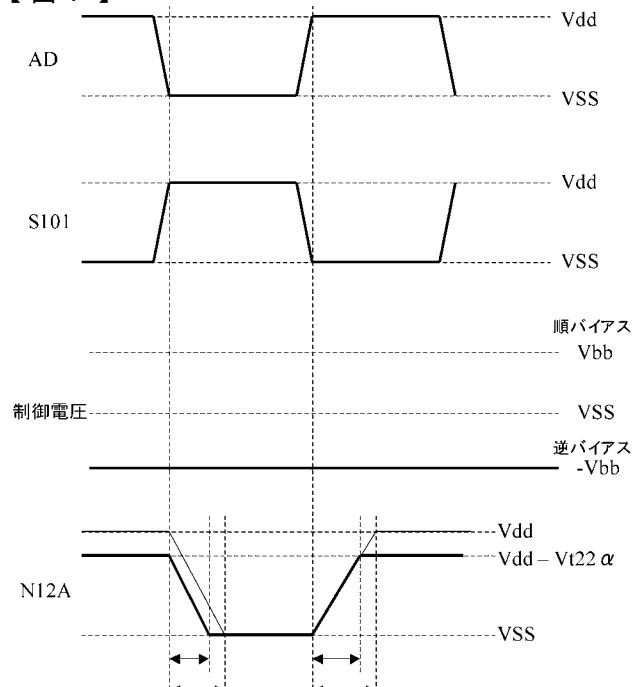

図 4 のように、アドレス信号 AD が「H レベル」である場合、インバータ 101 からの

50

出力 S 1 0 1 は「 L レベル」になる。したがって、トランジスタ T 2 0 2 A がオンになりトランジスタ T 2 0 3 A がオフになる。ここで、接続ノード N 1 2 A の電位は、電源ノードの電位からトランジスタ T 2 0 2 A の閾値電圧を引いた値「 V d d - V t 2 1 」になる。このとき、アドレス信号 A D U \_ 0 が「 H レベル」であっても、接続ノード N 1 3 の電位は「 V d d - V t 2 1 」になり、接地ノードの電位「 V S S 」よりも高くなる。

#### 【 0 0 3 2 】

一方、アドレス信号 A D が「 L レベル」である場合、インバータ 1 0 1 からの出力 S 1 0 1 は「 H レベル」になる。したがって、トランジスタ T 2 0 2 A がオフになりトランジスタ T 2 0 3 A がオンになる。ここで、接続ノード N 1 2 A の電位は、接地ノードの電位「 V S S 」と等しくなる。このとき、アドレス信号 A D U \_ 0 が「 H レベル」であれば、接続ノード N 1 3 の電位は、接地ノードの電位「 V S S 」になる。

#### 【 0 0 3 3 】

ここで、トランジスタ T 1 3 2 とトランジスタ T 2 0 3 A とが同極性でありトランジスタ T 1 3 2 とトランジスタ T 2 0 2 A とが異極性である場合（ケース 2 ）と比較すると、本実施形態では、接続ノード N 1 2 A に蓄積される電荷量が少ないので、放電時間および充電時間が短くなる。

#### 【 0 0 3 4 】

##### ＜効果＞

以上のように、プリデコーダに含まれるトランジスタ T 2 0 2 A , T 2 0 3 A の極性をデコード部に含まれるトランジスタ T 1 3 2 の極性と等しくすることによって、接続ノード N 1 2 A における電位の振幅を小さくすることができる。したがって、接続ノード N 1 2 A に充電される電荷量を削減することができる。また、接続ノード N 1 2 A を充放電するのに要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

#### 【 0 0 3 5 】

##### 〔変形例 1 〕

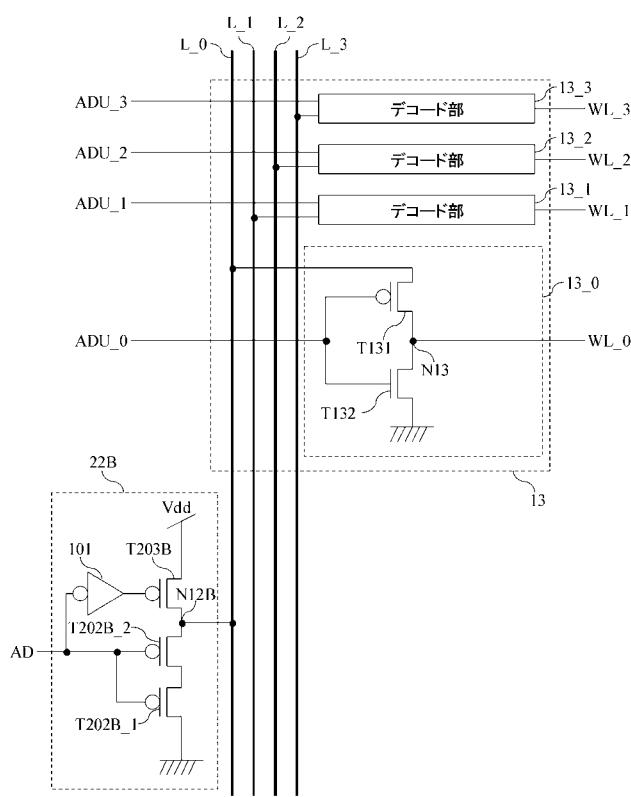

また、図 5 のように、プリデコーダ 2 2 A が、図 3 に示したトランジスタ T 2 0 2 A に代えて、トランジスタ T 2 0 2 A \_ 1 , T 2 0 2 A \_ 2 を含む場合でも、同様の効果を得ることができる。トランジスタ T 2 0 2 A \_ 1 , T 2 0 2 A \_ 2 は、電源ノードと接続ノード N 1 2 A との間に直列に接続され、各々のゲートにはアドレス信号 A D が入力される。また、トランジスタ T 2 0 2 A \_ 1 , T 2 0 2 A \_ 2 の各々の極性は、トランジスタ T 1 3 2 と同極性である。

#### 【 0 0 3 6 】

ここで、アドレス信号 A D が「 H レベル」になると、接続ノード N 1 2 A の電位は、電源ノードの電位からトランジスタ T 2 0 2 A \_ 1 , T 2 0 2 A \_ 2 の各々の閾値電圧（ V t 2 1 1 , V t 2 1 2 ）を引き、さらにバックバイアス効果による電圧降下（ - ）が考慮された値（ V d d - ( V t 2 1 1 + V t 2 1 2 + - ) ）になる。つまり、充電電位（接続ノード N 1 2 A を充電した場合の電位）を電源ノードの電位「 V d d 」よりも低くすることができる。

#### 【 0 0 3 7 】

##### 〔変形例 2 〕

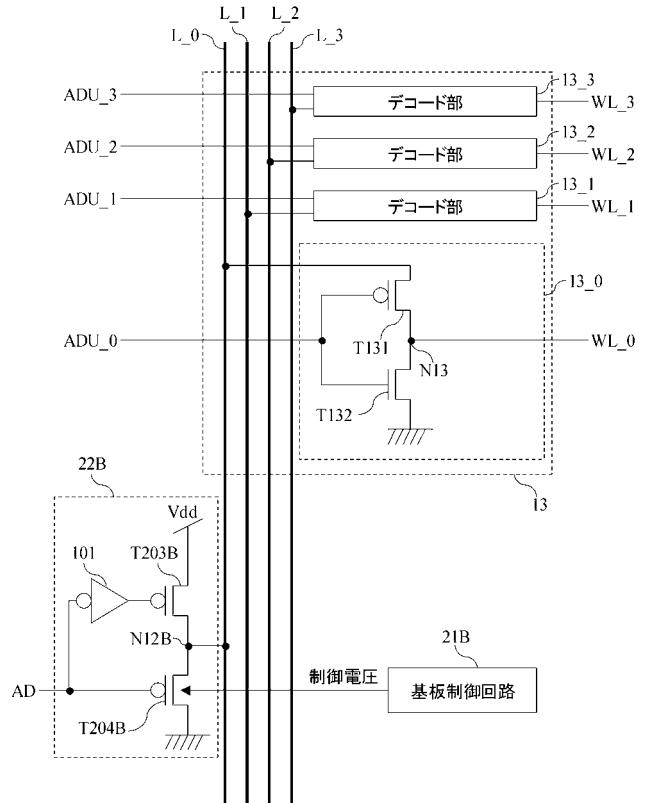

また、図 6 のように、デコーダ回路が、基板制御回路 2 1 A をさらに備えていても良い。基板制御回路 2 1 A は、制御電圧を出力する。また、プリデコーダ 2 2 A は、図 3 に示したトランジスタ T 2 0 2 A に代えて、トランジスタ T 2 0 4 A を含む。トランジスタ T 2 0 4 A は、基板制御回路 2 1 A からの制御電圧を基板に受ける。また、トランジスタ T 2 0 4 A は、トランジスタ T 1 3 2 と同極性である。制御電圧が接地ノードの電位「 V S S 」と等しいとき、トランジスタ T 2 0 4 A の閾値電圧は「 V t 2 2 」になる。制御電圧が逆バイアス（ - V b b ）であるとき、トランジスタ T 2 0 4 A の閾値電圧は「 V t 2 2 」よりも高い「 V t 2 2 」になる。

#### 【 0 0 3 8 】

10

20

30

40

50

図7のように、トランジスタT204Aは、基板制御回路21Aからの逆バイアス(-V<sub>bb</sub>)を基板に受ける。ここで、アドレス信号ADが「Hレベル」になると、接続ノードN12Aの電位は、電源ノードの電位からトランジスタT204Aの閾値電圧を引いた値(V<sub>dd</sub>-V<sub>t22</sub>)になる。つまり、充電電位を電源ノードの電位「V<sub>dd</sub>」よりも低くすることができる。

#### 【0039】

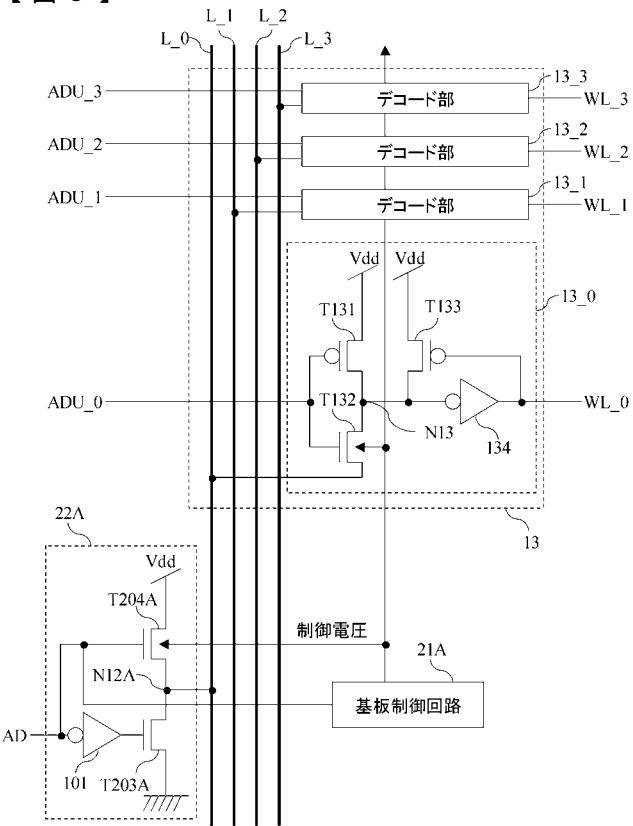

##### 〔変形例3〕

さらに、図8のように、基板制御回路21Aがアドレス信号ADに応じて、制御電圧を出力しても良い。プリデコーダ22AのトランジスタT204A、デコード部13\_0のトランジスタT132の各々は、基板制御回路21Aからの制御電圧を基板に受ける。トランジスタT204A、T132の各々において、制御電圧が順バイアス(V<sub>bb</sub>)であるときの閾値電圧は、制御電圧が接地ノードの電位「V<sub>SS</sub>」と等しいときの閾値電圧よりも低い。

#### 【0040】

図9のように、アドレス信号ADが「Hレベル」である場合には、基板制御回路21Aは、逆バイアス(-V<sub>bb</sub>)である制御電圧を出力する。これにより、トランジスタT204Aの閾値電圧は「V<sub>t22</sub>」よりも高い「V<sub>t22</sub>」になるので、接続ノードN12Aの電位は「V<sub>dd</sub>-V<sub>t22</sub>」よりも高くならない。また、閾値電圧が高くなることによって、充電速度が遅くなる。これにより、接続ノードN12Aに充電される電荷量を削減することができる。一方、アドレス信号ADが「Lレベル」である場合には、基板制御回路21Aは、順バイアス(V<sub>bb</sub>)である制御電圧を出力する。これにより、トランジスタT132の閾値電圧は低くなるので、接続ノードN12Aの放電に要する時間を短縮することができる。

#### 【0041】

##### 〔第3の実施形態〕

###### 〈構成〉

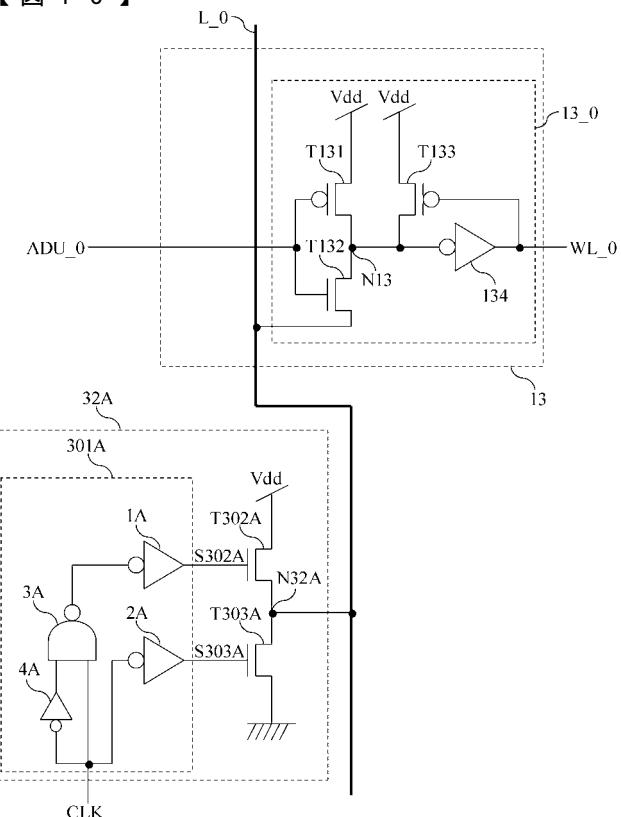

図10は、この発明の第3の実施形態によるデコーダ回路の構成を示す。デコーダ回路は、図3に示したプリデコーダ22Aに代えて、プリデコーダ32Aを備える。その他の構成は図1と同様である。なお、ここでは、プリデコーダ32A、配線L\_0、およびロウデコーダ13のデコード部13\_0のみを図示する。この回路は、外部からのアドレス信号ADU\_0とクロックCLKとに応じて、駆動信号WL\_0を出力する。例えば、クロックCLKは源信である。プリデコーダ32Aは、タイミング制御回路301Aと、トランジスタT302A、T303Aとを含む。タイミング制御回路301Aは、複数の論理素子(ここでは、インバータ1A、2A、NAND回路3A、遅延回路4A)によって構成される。タイミング制御回路301Aは、外部からのクロックCLKに応じて制御信号S302A、S303Aを出力する。トランジスタT302A、T303Aは、電源ノードと接地ノードとの間に直列に接続される。トランジスタT302Aは、電源ノードとトランジスタT303Aとの間に接続され、インバータ1Aからの出力(制御信号S302A)をゲートに受ける。トランジスタT303Aは、トランジスタT302Aと接地ノードとの間に接続され、インバータ2Aからの出力(制御信号S303A)をゲートに受ける。トランジスタT302AとトランジスタT303Aとの接続ノードN32Aは、配線L\_0に接続される。また、プリデコーダ32Aの出力は、例えば、イネーブル信号として利用される。

#### 【0042】

###### 〈動作〉

次に、図10に示したデコーダ回路による動作について図11を参照しつつ説明する。なお、ここでは、各々のトランジスタの閾値電圧は考慮しないものとする。

#### 【0043】

時刻t1になると、クロックCLKが「Lレベル」から「Hレベル」になる。これにより、制御信号S302Aは「Lレベル」から「Hレベル」になるので、トランジスタT3

10

20

30

40

50

02Aはオフからオンになる。一方、制御信号S303Aは「Hレベル」から「Lレベル」になるので、トランジスタT303Aはオンからオフになる。したがって、接続ノードN32Aの電位は、接地ノードの電位「VSS」から上昇していく。

#### 【0044】

時刻t2になると、遅延回路4Aからの出力CLKPLSが「Hレベル」から「Lレベル」になる。これにより、制御信号S302Aは「Hレベル」から「Lレベル」になるので、トランジスタT302Aはオンからオフになる。一方、制御信号S303Aは「Lレベル」のままであるので、トランジスタT303Aはオフの状態を維持する。したがって、接続ノードN32Aが充電されなくなり、接続ノードN32Aの電位は、電源ノードの電位「Vdd」よりも低い「Vdd-」になる。

10

#### 【0045】

時刻t3になると、クロックCLKは「Hレベル」から「Lレベル」になる。これにより、制御信号S303Aは「Lレベル」から「Hレベル」になるので、トランジスタT303Aはオフからオンになる。一方、制御信号S302Aは「Lレベル」のままであるので、トランジスタT302Aはオフの状態を維持する。したがって、接続ノードN32Aの電位は、接地ノードの電位「VSS」へ下降していく。

#### 【0046】

##### <効果>

以上のように、接続ノードN32Aの電位が電源ノードの電位「Vdd」に達する前にトランジスタT302Aをオフにすることによって、接続ノードN32Aにおける電位の振幅を小さくすることができる。したがって、接続ノードN32Aに充電される電荷量を削減することができる。また、接続ノードN32Aを充放電するのに要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

20

#### 【0047】

なお、図10では、トランジスタT302A, T132は「N型」のトランジスタであるが、「P型」のトランジスタであっても構わない。

#### 【0048】

##### (第4の実施形態)

##### <構成>

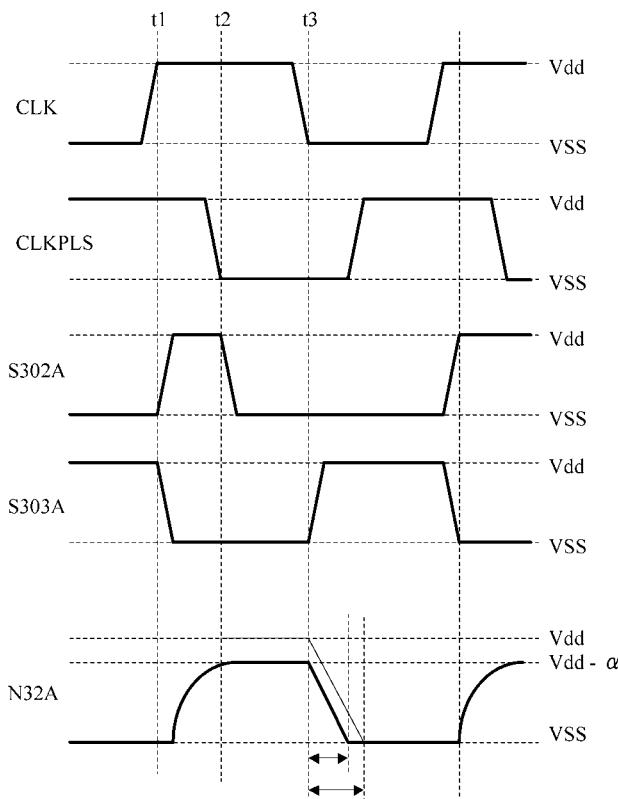

図12は、この発明の第4の実施形態によるデコーダ回路の構成を示す。この回路は、図10に示したプリデコーダ32Aに代えて、プリデコーダ42Aを備える。その他の構成は図10と同様である。プリデコーダ42Aは、トランジスタT402A, T403Aを含む。トランジスタT402A, T403Aは、電源ノードと接地ノードとの間に直列に接続される。トランジスタT402Aは、電源ノードとトランジスタT403Aとの間に接続され、外部からのクロックCLKをゲートに受ける。トランジスタT403Aは、トランジスタT402Aと接地ノードとの間に接続され、外部からのクロックCLKをゲートに受ける。トランジスタT402AとトランジスタT403Aとの接続ノードN42Aは、配線L\_0に接続される。

30

#### 【0049】

トランジスタT402AのW/L比は、トランジスタT403AのW/L比の2倍以下である。例えば、トランジスタT402A, T403Aの各々のゲート長が互いに等しいとすると、トランジスタT402Aのゲート幅は、トランジスタT403Aのゲート幅の2倍以下である。また、トランジスタT402A, T403Aの各々のゲート幅が互いに等しいとすると、トランジスタT402Aのゲート長は、トランジスタT403Aのゲート長を(1/2)倍以上である。このような構成により、トランジスタT402Aを単位時間当たりに流れる電流量を、トランジスタT403Aを単位時間当たりに流れる電流量よりも少なくすることができる。つまり、トランジスタT402Aの電流能力は、トランジスタT403Aの電流能力よりも弱い。また、トランジスタT403Aの電流能力は、従来と同様であっても良い。

40

#### 【0050】

50

## &lt;動作&gt;

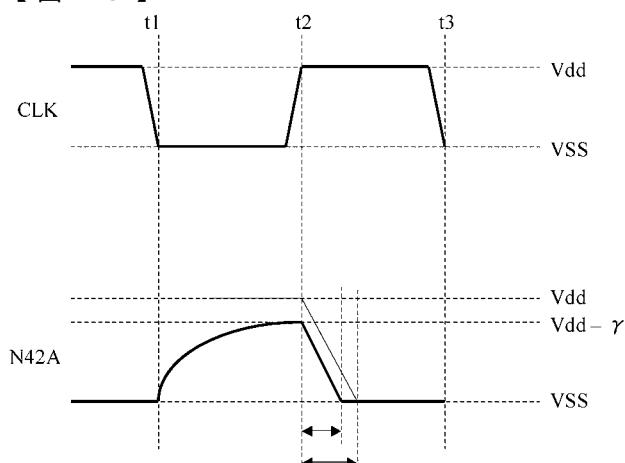

次に、図12に示したデコーダ回路による動作について図13を参照しつつ説明する。

## 【0051】

時刻 $t_1$ になると、クロックCLKは「Hレベル」から「Lレベル」になる。これにより、トランジスタT402Aはオフからオンになり、トランジスタT403Aはオンからオフになる。したがって、接続ノードN42Aの電位は、接地ノードの電位「VSS」から上昇していく。

## 【0052】

時刻 $t_2$ になると、クロックCLKは「Lレベル」から「Hレベル」になる。これにより、トランジスタT402Aはオンからオフになる。このとき、トランジスタT402Aの電流能力は比較的弱いので、接続ノードN42Aの電位は、電源ノードの電位Vddに達していない（「Vdd-」になる）。また、トランジスタT403Aはオフからオンになる。したがって、接続ノードN42Aの電位は、「Vdd-」から下降していく。

## 【0053】

時刻 $t_3$ になると、クロックCLKは「Hレベル」から「Lレベル」になる。これにより、トランジスタT402Aはオフからオンになり、トランジスタT403Aはオンからオフになる。このとき、トランジスタT403Aの電流能力は比較的強いので、接続ノードN42Aの電位は、接地ノードの電位「VSS」に達している。

## 【0054】

## &lt;効果&gt;

以上のように、接続ノードN42Aの電位が電源ノードの電位「Vdd」に達する前にトランジスタT402Aをオフにすることによって、接続ノードN42Aにおける電位の振幅を小さくすることができる。したがって、接続ノードN42Aに充電される電荷量を削減することができる。また、接続ノードN42Aを充放電するのに要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

## 【0055】

## (第5の実施形態)

## &lt;構成&gt;

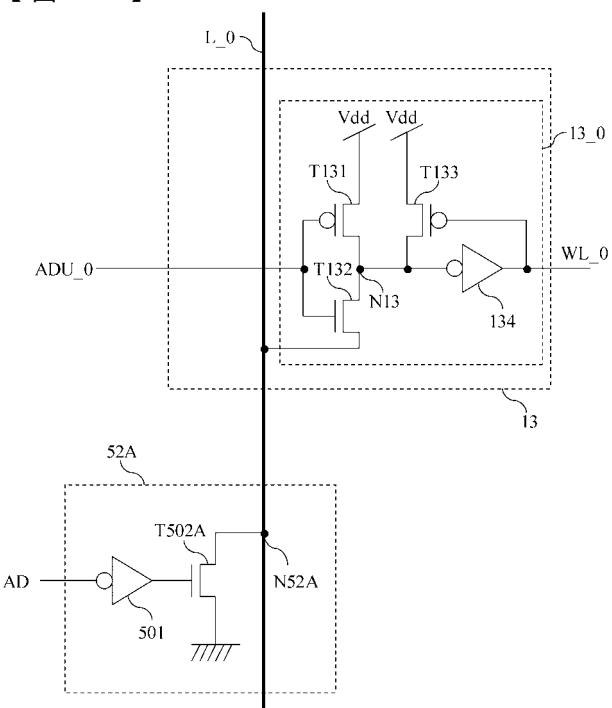

図14は、この発明の発明の第5の実施形態によるデコーダ回路の構成を示す。この回路は、図10に示したプリデコーダ32Aに代えて、プリデコーダ52Aを備える。その他の構成は図10と同様である。プリデコーダ52Aは、インバータ501と、トランジスタT502Aとを備える。トランジスタT502Aは、配線L\_0と接地ノードとの間に接続され、インバータ501からの出力をゲートに受ける。トランジスタT502Aは、トランジスタT132と同極性である。

## 【0056】

## &lt;動作&gt;

次に、図14に示したデコーダ回路による動作について図15を参照しつつ説明する。なお、ここでは、トランジスタT502Aの閾値電圧を「Vt51」とする。

## 【0057】

時刻 $t_1$ になると、トランジスタT131はオンからオフになり、トランジスタT132はオフからオンになる。したがって、接続ノードN13は、電源ノードから切り離され、配線L\_0（接続ノードN52A）に接続される。このとき、接続ノードN52Aの電位が「Vdd - Vt51」であるので、接続ノードN13の電位は、電源ノードの電位「Vdd」のままである。

## 【0058】

時刻 $t_2$ になると、トランジスタT502Aはオフからオンになる。したがって、接続ノードN52Aは、接地ノードに接続される。これにより、接続ノードN52Aの電位は、「Vdd - Vt51」から接地ノードの電位「VSS」に下降していく。また、接続ノードN13の電位も、「Vdd」から接地ノードの電位「VSS」に下降していく。

## 【0059】

10

20

30

40

50

時刻  $t_3$  になると、トランジスタ T 131 はオフからオンになり、トランジスタ T 132 はオンからオフになる。したがって、接続ノード N 13 は、接続ノード N 52A から切り離され、電源ノードに接続される。これにより、接続ノード N 13 の電位は、接地ノードの電位「VSS」から電源ノードの電位「Vdd」に上昇していく。

#### 【0060】

時刻  $t_4$  になると、トランジスタ T 502A はオンからオフになる。したがって、接続ノード N 52A は、接地ノードから切り離される。

#### 【0061】

時刻  $t_5$  になると、トランジスタ T 131 はオンからオフになり、トランジスタ T 132 はオフからオンになる。したがって、接続ノード N 13 は、電源ノードから切り離され、接続ノード N 52A に接続される。ここで、接続ノード N 13 の電位は「Vdd」であり、接続ノード N 52A の電位は「VSS」であるので、接続ノード N 13 に充電された電荷が接続ノード N 52A に分配される。これにより、接続ノード N 13, N 52A の各々電位は、「Vdd - Vt51」になる。

10

#### 【0062】

時刻  $t_6$  になると、トランジスタ T 502A はオフからオンになる。したがって、接続ノード N 52A は、接地ノードに接続される。これにより、接続ノード N 52A の電位は、「Vdd - Vt51」から接地ノードの電位「VSS」に下降する。また、接続ノード N 13 の電位も、「Vdd - Vt51」から接地ノードの電位「VSS」に下降する。

20

#### 【0063】

なお、分配された電荷による電位は「Vdd - Vt51」に限定されない。

#### 【0064】

##### <効果>

以上のように、接続ノード N 13 に充電された電荷を接続ノード N 52A に分配することによって、接続ノード N 13 の電位が調整される。また、接続ノード N 52A の電位を「Vdd - Vt51」を超えないようにすることができる。したがって、接続ノード N 52A における電位の振幅を小さくすることができる。よって、接続ノード N 52A に充電される電荷量を削減することができる。また、接続ノード N 52A を充放電するのに要する時間を短縮することができる。これにより、高速動作と低消費電力化が可能となる。

30

#### 【0065】

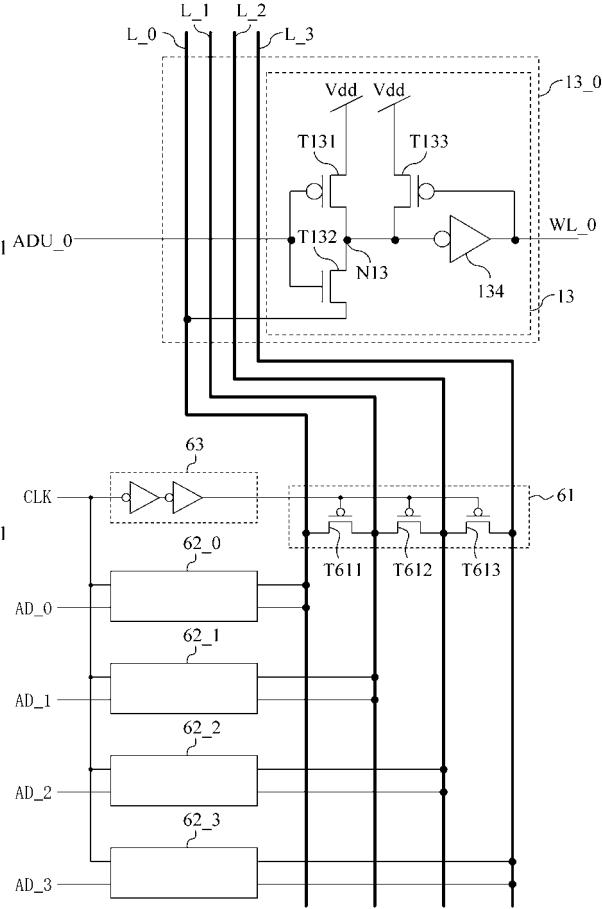

##### (第6の実施形態)

##### <構成>

図 16 は、この発明の第6の実施形態によるデコーダ回路の構成を示す。この回路は、図 1 に示したプリデコーダ 12A に代えて、イコライズ回路 61 と、プリデコーダ 62\_0, 62\_1, 62\_2, 62\_3 と、遅延回路 63 とを備える。その他の構成は図 1 と同様である。なお、ここでは、ロウデコーダ 13 のデコード部のうち配線 L\_0 に接続されるデコード部 13\_0 のみを図示している。

40

#### 【0066】

イコライズ回路 61 は、遅延回路 63 からの出力を受ける。イコライズ回路 61 は、クロック CLK が「L レベル」のときには配線 L\_0 ~ L\_3 を互いに接続し、クロック CLK が「H レベル」のときには配線 L\_0 ~ L\_3 の各々を互いに切り離す。イコライズ回路 61 は、トランジスタ T 611, T 612, T 613 を含む。トランジスタ T 611, T 612, T 613 の各々は、クロック CLK が「L レベル」のときにはオンになり、クロック CLK が「H レベル」のときにはオフになる。

40

#### 【0067】

プリデコーダ 62\_0 ~ 62\_3 は同様の構成であるので、代表して、プリデコーダ 62\_0 について説明する。プリデコーダ 62\_0 は、自己に対応するアドレス信号 AD\_0 が「H レベル」でありクロック CLK が「H レベル」であり自己に対応する配線が「H レベル」であるときには、自己に対応する配線 L\_0 に対して放電処理を実行する。また、プリデコーダ 62\_0 は、自己に対応するアドレス信号 AD\_0 が「L レベル」であり

50

自己に対応する配線 L\_0 が「H レベル」であるときには、自己に対応する配線 L\_0 に対して充電処理を実行する。

【0068】

< プリデコーダの内部構成 >

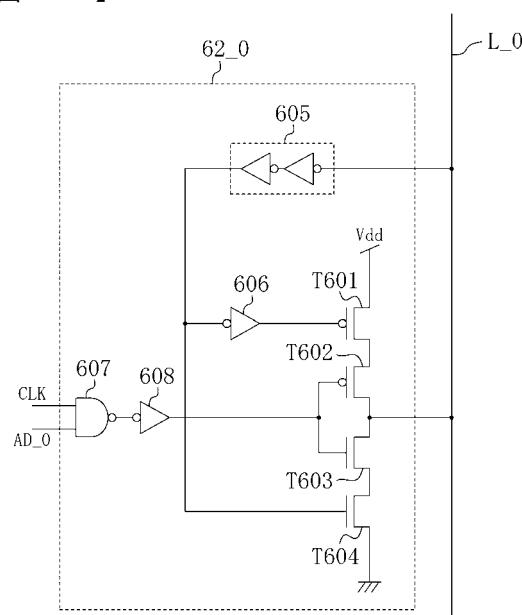

図16に示したプリデコーダ62\_0の内部構成を図17に示す。プリデコーダ62\_0は、トランジスタT601, T602, T603, T604と、遅延回路605と、インバータ606と、NAND回路607と、インバータ608とを含む。トランジスタT601～T604は、電源ノードと接地ノードとの間に直列に接続される。遅延回路605は、配線L\_0の電位を受ける。インバータ606は、遅延回路605からの出力を反転して出力する。トランジスタT601は、インバータ606からの出力をゲートに受ける。トランジスタT602, T603の各々は、インバータ608からの出力をゲートに受ける。トランジスタT604は遅延回路605からの出力をゲートに受ける。

10

【0069】

ここで、配線L\_0の電位が「H レベル」である場合（配線の電位が「(3/4) × Vdd」以上である場合）、トランジスタT601, T604は、オンになる。このとき、アドレス信号AD\_0が「H レベル」でありクロックCLKが「H レベル」であると、トランジスタT602がオフになりトランジスタT603がオンになる。これにより、配線L\_0と接地ノードとが接続されて、配線L\_0に対して放電処理が実行される。

【0070】

また、配線L\_0の電位が「H レベル」である場合、アドレス信号AD\_0およびクロックCLKのうち少なくとも一方が「L レベル」であると、トランジスタT602がオンになりトランジスタT603がオフになる。これにより、配線L\_0と電源ノードとが接続されて、配線L\_0に対して充電処理が実行される。

20

【0071】

一方、配線L\_0の電位が「L レベル」である場合（配線の電位が「VSS」である場合）、トランジスタT601, T604は、オフになる。したがって、アドレス信号AD\_0が「H レベル」でありクロックCLKが「H レベル」であっても、放電処理および充電処理は、実行されない。

【0072】

< 動作 >

30

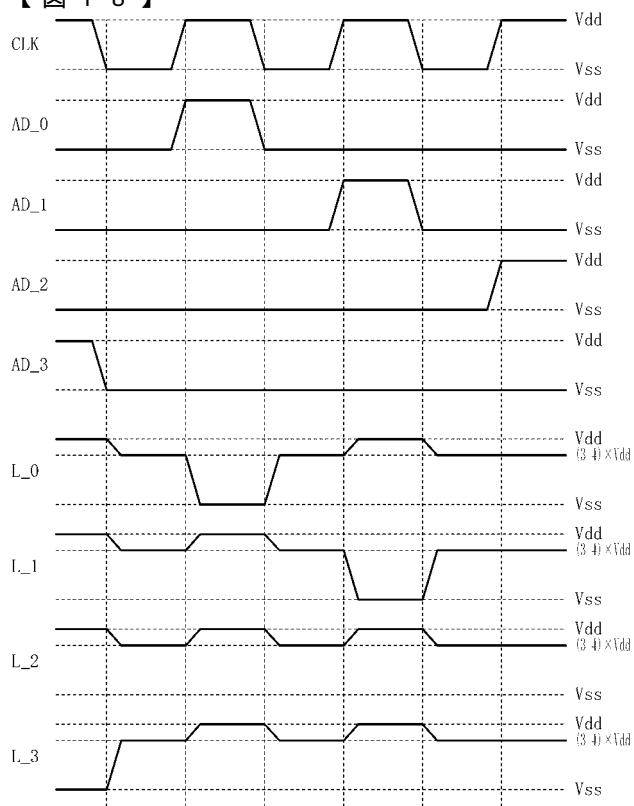

次に、図16に示したデコーダ回路による動作について図18を参照しつつ説明する。

【0073】

まず、クロックCLKが「H レベル」であるとする。このとき、イコライズ回路61では、トランジスタT611～T613の各々はオフになっている。また、アドレス信号AD\_0～AD\_2の各々が「L レベル」であり、アドレス信号AD\_3が「H レベル」であるとする。このとき、プリデコーダ62\_0～62\_2の各々では、そのデコーダに対応する配線と電源ノードとが接続されている。したがって、配線L\_0～L\_2の各々の電位は「Vdd」になっている。一方、配線L\_3の電位は「VSS」になっており、プリデコーダ62\_3では、トランジスタT601, T604がオフになっている。

40

【0074】

次に、アドレス信号AD\_3が「L レベル」になる。プリデコーダ62\_3では、トランジスタT602がオンになり、トランジスタT603がオフになる。また、クロックCLKが「L レベル」になる。イコライズ回路61では、トランジスタT611～T613の各々はオンになる。これにより、配線L\_0～L\_2の各々の電位は「Vdd」から低下していき、配線L\_3の電位は「VSS」から上昇していく。

【0075】

次に、クロックCLKが「H レベル」になる。イコライズ回路61では、トランジスタT611～T613の各々がオフになる。このとき、配線L\_0～L\_3の各々の電位は、「(3/4) × Vdd」になる。また、アドレス信号AD\_1～AD\_3の各々は「L レベル」であるので、プリデコーダ62\_1～62\_3の各々では、トランジスタT60

50

2がオンでありトランジスタT603がオフである。したがって、配線L\_1～L\_3の各々の電位は、「(3/4)×Vdd」から「Vdd」になる。一方、アドレス信号AD\_0は「Hレベル」になる。プリデコーダ62\_0では、トランジスタT602がオフになり、トランジスタT603がオンになる。したがって、配線L\_0の電位は「(3/4)×Vdd」から「VSS」になる。

## 【0076】

次に、アドレス信号AD\_0が「Lレベル」になる。プリデコーダ62\_0では、トランジスタT602がオンになり、トランジスタT603がオフになる。また、クロックCLKが「Lレベル」になる。イコライズ回路61では、トランジスタT611～T613の各々はオンになる。これにより、配線L\_1～L\_3の各々の電位は「Vdd」から下降していき、配線L\_0の電位は「VSS」から上昇していく。

10

## 【0077】

このように、クロックCLKが「Hレベル」である期間では、配線L\_0～L\_3のうちいずれか1つに対して放電処理が実行される。一方、クロックCLKが「Lレベル」である期間では、配線L\_0～L\_3の各々はイコライズされる。つまり、充電処理または放電処理が実行される前に、配線L\_0～L\_3がイコライズされる。

## 【0078】

## &lt;効果&gt;

以上のように、充電時において、電荷が引き抜かれた配線(L\_0)に対して電源ノードの電位「Vdd」まで電荷が充電された配線(L\_1, L\_2, L\_3)がイコライズされることによって、配線(L\_0)の電位を「(3/4)×Vdd」に設定することができる。つまり、充電電位を電源ノードの電位「Vdd」よりも低い「(3/4)×Vdd」に抑えることができ、配線に充電される電荷量を削減することができる。また、配線を充放電するのに要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

20

## 【0079】

## (第7の実施形態)

## &lt;構成&gt;

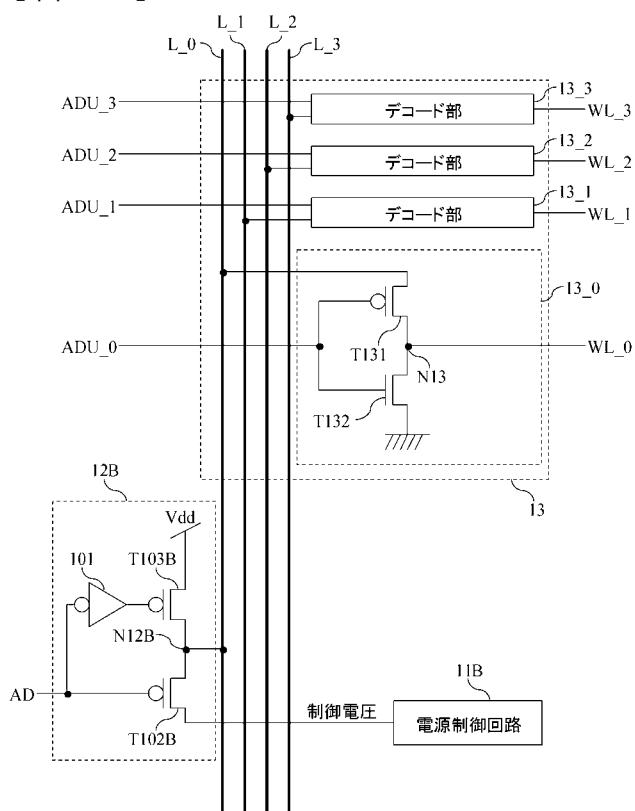

図19は、この発明の第7の実施形態によるデコーダ回路の構成を示す。この回路は、電源制御回路11Bと、プリデコーダ12Bと、ロウデコーダ13とを備える。

30

## 【0080】

電源制御回路11Bは、プリデコーダ12Bへ制御電圧を出力する。制御電圧の電圧値「VSS1」は、接地ノードの電位「VSS」よりも高い。

## 【0081】

プリデコーダ12Bは、配線L\_0に接続され、アドレス信号ADに応じて動作する。プリデコーダ12Bは、インバータ101と、トランジスタT102Bと、トランジスタT103Bとを含む。トランジスタT102B, T103Bは、電源制御回路11Bと電源ノードとの間に直列に接続される。トランジスタT102Bは、電源制御回路11BとトランジスタT103Bとの間に接続され、アドレス信号ADをゲートに受ける。トランジスタT103Bは、トランジスタT102Bと電源ノードとの間に接続され、インバータ101の出力をゲートに受ける。また、トランジスタT102BとトランジスタT103Bとの接続ノードN12Bは、配線L\_0に接続される。

40

## 【0082】

ロウデコーダ13は、図1に示した構成と同様であるが、デコード部13\_0～13\_3の構成が異なる。ここでは、代表してデコード部13\_0について説明する。

## 【0083】

デコード部13\_0は、トランジスタT131, T132を含む。トランジスタT131, T132は、接地ノードと配線L\_0との間に直列に接続される。トランジスタT131は、配線L\_0とトランジスタT132との間に接続され、外部からのアドレス信号ADU\_0をゲートに受ける。トランジスタT132は、トランジスタT131と接地ノ

50

ードとの間に接続され、外部からのアドレス信号 A D U \_ 0 をゲートに受ける。トランジスタ T 1 3 1 とトランジスタ T 1 3 2 との接続ノード N 1 3 に生じる電圧は、駆動信号 W L \_ 0 として出力される。

【 0 0 8 4 】

＜動作＞

次に、図 1 9 に示したデコーダ回路による動作について説明する。なお、ここでは、各々のトランジスタの閾値電圧は考慮しないものとして説明する。

〔デコード部〕

アドレス信号 A D U \_ 0 が「 L レベル」である場合、トランジスタ T 1 3 1 はオンになります、トランジスタ T 1 3 2 はオフになります。したがって、接続ノード N 1 3 の電位は、接続ノード N 1 2 B の電位と等しくなる。一方、アドレス信号 A D U \_ 0 が「 H レベル」である場合、トランジスタ T 1 3 1 はオフになります、トランジスタ T 1 3 2 はオンになります。したがって、接続ノード N 1 3 の電位は、接地ノード N 1 2 B の電位と等しくなる。

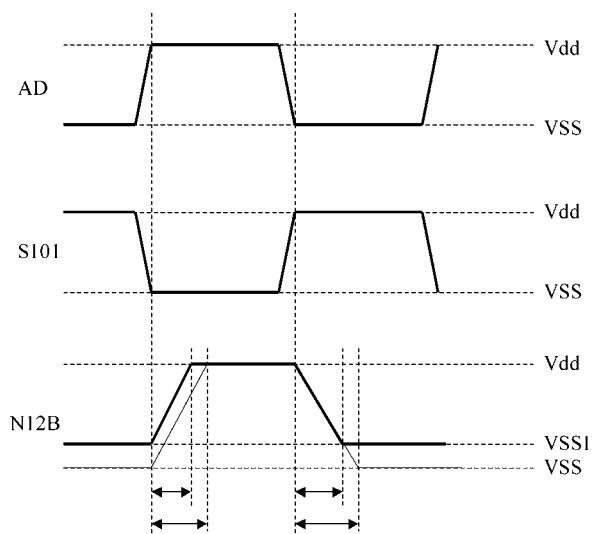

〔プリデコーダ〕

図 2 0 のように、アドレス信号 A D が「 L レベル」である場合、インバータ 1 0 1 からの出力 S 1 0 1 は「 H レベル」になります。したがって、トランジスタ T 1 0 2 B がオンになりますトランジスタ T 1 0 3 B がオフになります。これにより、接続ノード N 1 2 B の電位は、電源制御回路 1 1 B からの制御電圧の電圧値「 V S S 1 」と等しくなる。このとき、アドレス信号 A D U \_ 0 が「 L レベル」であっても、接続ノード N 1 3 の電位は「 V S S 1 」になります、接地ノードの電位「 V d d 」よりも低くなる。

【 0 0 8 5 】

一方、アドレス信号 A D が「 H レベル」である場合、インバータ 1 0 1 からの出力 S 1 0 1 は「 L レベル」になります。したがって、トランジスタ T 1 0 2 B がオフになりますトランジスタ T 1 0 3 B がオンになります。これにより、接続ノード N 1 2 B の電位は、電源ノードの電位「 V d d 」と等しくなる。このとき、アドレス信号 A D U \_ 0 が「 L レベル」であれば、接続ノード N 1 3 の電位は、電源ノードの電位「 V d d 」になります。

【 0 0 8 6 】

＜効果＞

以上のように、トランジスタ T 1 0 2 B の一端に供給される電圧を接地ノードの電位「 V S S 」よりも高くすることによって、接続ノード N 1 2 B における電位の振幅を小さくすることができます。したがって、接続ノード N 1 2 B から放電される電荷量を削減することができます。また、接続ノード N 1 2 B を充放電するために要する時間を短縮することができます。このように、高速動作と低消費電力化が可能となる。

【 0 0 8 7 】

また、図 1 9 では、トランジスタ T 1 0 3 B , T 1 3 1 は「 P 型」のトランジスタであるが、「 N 型」のトランジスタであっても構わない。

【 0 0 8 8 】

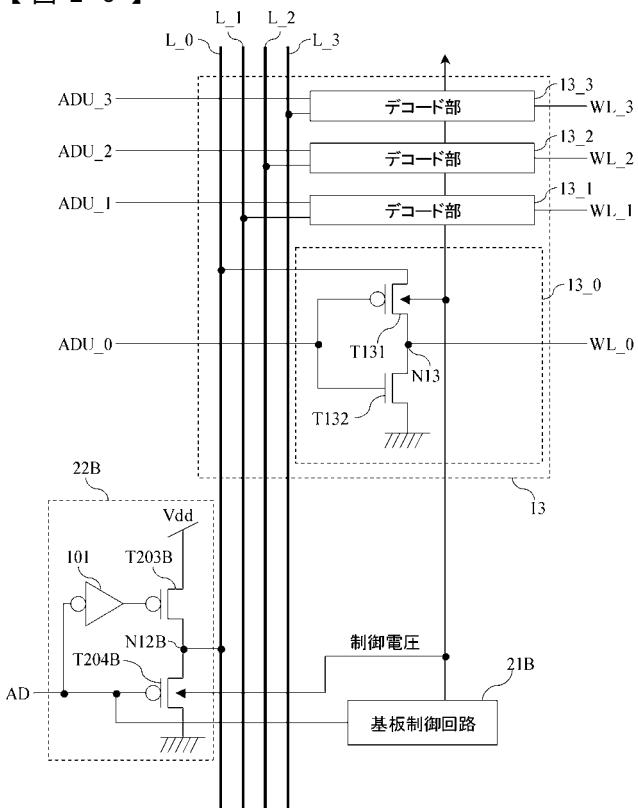

( 第 8 の実施形態 )

＜構成＞

図 2 1 は、この発明の第 2 の実施形態によるデコーダ回路の構成を示す。この回路は、図 1 9 に示した電源制御回路 1 1 B , プリデコーダ 1 2 B に代えて、プリデコーダ 2 2 B を備える。その他の構成は図 1 9 と同様である。プリデコーダ 2 2 B は、図 1 9 に示したトランジスタ T 1 0 2 B , T 1 0 3 B に代えて、トランジスタ T 2 0 2 B , T 2 0 3 B を含む。その他の構成は、図 1 9 と同様である。トランジスタ T 2 0 2 B , T 2 0 3 B の各々は、トランジスタ T 1 3 1 と同極性である。例えば、トランジスタ T 1 3 1 が「 P 型」であれば、トランジスタ T 2 0 2 B , T 2 0 3 B も「 P 型」である。

【 0 0 8 9 】

＜動作＞

次に、図 2 1 に示したデコーダ回路による動作について説明する。なお、ここでは、トランジスタ T 2 0 2 B の閾値電圧の絶対値を「 | V t 8 1 | 」とし、トランジスタ T 2 0

10

20

30

40

50

3 B, T 1 3 1 の閾値電圧は考慮しないものとする。

【0090】

図22のように、アドレス信号A Dが「Lレベル」である場合、インバータ1 0 1からの出力は「Hレベル」になる。したがって、トランジスタT 2 0 2 BがオンになりトランジスタT 2 0 3 Bがオフになる。ここで、接続ノードN 1 2 Bの電位は、接地ノードの電位にトランジスタT 2 0 2 Bの閾値電圧を足した値( $V_{SS} + |V_{t81}|$ )になる。このとき、アドレス信号A D U \_ 0が「Lレベル」であっても、接続ノードN 1 3の電位は「V d d」にならず、「 $V_{SS} + |V_{t81}|$ 」になる。

【0091】

一方、アドレス信号A Dが「Hレベル」である場合、インバータ1 0 1からの出力S 1 10 0 1は「Lレベル」になる。したがって、トランジスタT 2 0 2 BがオフになりトランジスタT 2 0 3 Bがオンになる。ここで、接続ノードN 1 2 Bの電位は、電源ノードの電位「V d d」と等しくなる。このとき、アドレス信号A D U \_ 0が「Lレベル」であれば、接続ノードN 1 3の電位は、電源ノードの電位「V d d」になる。

【0092】

<効果>

以上のように、プリデコーダに含まれるトランジスタT 2 0 2 B, T 2 0 3 Bの極性をデコード部に含まれるトランジスタT 1 3 1の極性と等しくすることによって、接続ノードN 1 2 Bにおける電位の振幅を小さくすることができる。したがって、接続ノードN 1 2 Bから放電される電荷量を削減することができる。また、接続ノードN 1 2 Bを充放電するのに要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

【0093】

[変形例1]

また、図23のように、プリデコーダ2 2 Bが、図21に示したトランジスタT 2 0 2 Bに代えて、トランジスタT 2 0 2 B \_ 1, T 2 0 2 B \_ 2を含む場合でも、同様の効果を得ることができる。トランジスタT 2 0 2 B \_ 1, T 2 0 2 B \_ 2は、トランジスタT 2 0 3 Bと接地ノードとの間に直列に接続され、各々のゲートにはアドレス信号A Dが入力される。また、トランジスタT 2 0 2 B \_ 1, T 2 0 2 B \_ 2の各々の極性は、トランジスタT 1 3 1と同極性である。

【0094】

ここで、アドレス信号A Dが「Lレベル」になると、接続ノードN 1 2 Bの電位は、接地ノードの電位にトランジスタT 2 0 2 B \_ 1, T 2 0 2 B \_ 2の各々の閾値電圧( $|V_{t811}|, |V_{t812}|$ )を足し、さらにバックバイアス効果による電圧降下( )が考慮された値( $V_{SS} + |V_{t811}| + |V_{t812}| + \dots$ )になる。つまり、放電電位(接続ノードN 1 2 Bを放電した場合の電位)を接地ノードの電位「V SS」よりも高くすることができる。

【0095】

[変形例2]

また、図24のように、デコーダ回路が、基板制御回路2 1 Bをさらに備えていても良い。基板制御回路2 1 Bは、制御電圧を出力する。また、プリデコーダ2 2 Bは、図21に示したトランジスタT 2 0 2 Bに代えて、トランジスタT 2 0 4 Bを含む。トランジスタT 2 0 4 Bは、基板制御回路2 1 Bからの制御電圧を基板に受ける。制御電圧が接地ノードの電位「V SS」であるとき、トランジスタT 2 0 4 Aの閾値電圧の絶対値は「 $|V_{t82}|$ 」になる。制御電圧が「逆バイアス(V b b)」であるとき、トランジスタT 2 0 4 Aの閾値電圧の絶対値は「 $|V_{t82}|$ 」よりも大きい「 $|V_{t82}|$ 」になる。

【0096】

図25のように、アドレス信号A Dが「Lレベル」になると、接続ノードN 1 2 Bの電位は、接地ノードの電位にトランジスタT 2 0 4 Aの閾値電圧を足した値( $V_{SS} + |V_{t82}|$ )になる。つまり、放電電位を接地ノードの電位「V SS」よりも高くするこ

10

20

30

40

50

とができる。

【0097】

〔変形例3〕

さらに、図26のように、基板制御回路21Bがアドレス信号ADに応じて、制御電圧を出力しても良い。プリデコーダ22BのトランジスタT204B、デコード部13\_0のトランジスタT131の各々は、基板制御回路21Bからの制御電圧を基板に受ける。トランジスタT204B、T131の各々において、制御電圧が順バイアス(Vbb)であるときの閾値電圧の絶対値は、制御電圧が接地ノードの電位「VSS」と等しいときの閾値電圧の絶対値よりも小さい。

【0098】

図27のように、基板制御回路21Bは、アドレス信号ADが「Lレベル」である場合には、基板制御回路21Bは、逆バイアス(Vbb)である制御電圧を出力する。これにより、トランジスタT204Bの閾値電圧の絶対値は「|Vt82|」よりも大きい「|Vt82+|」になるので、接続ノードN12Bの電位は「VSS+|Vt82+|」以下にならない。また、閾値電圧の絶対値が大きくなることによって放電速度が遅くなる。これにより、接続ノードN12Bから放電される電荷量を削減することができる。一方、アドレス信号ADが「Hレベル」である場合には、基板制御回路21Bは、順バイアス(-Vbb)である制御電圧を出力する。これにより、トランジスタT131の閾値電圧の絶対値が小さくなるので、接続ノードN12Bの充電に要する時間を短縮することができる。

【0099】

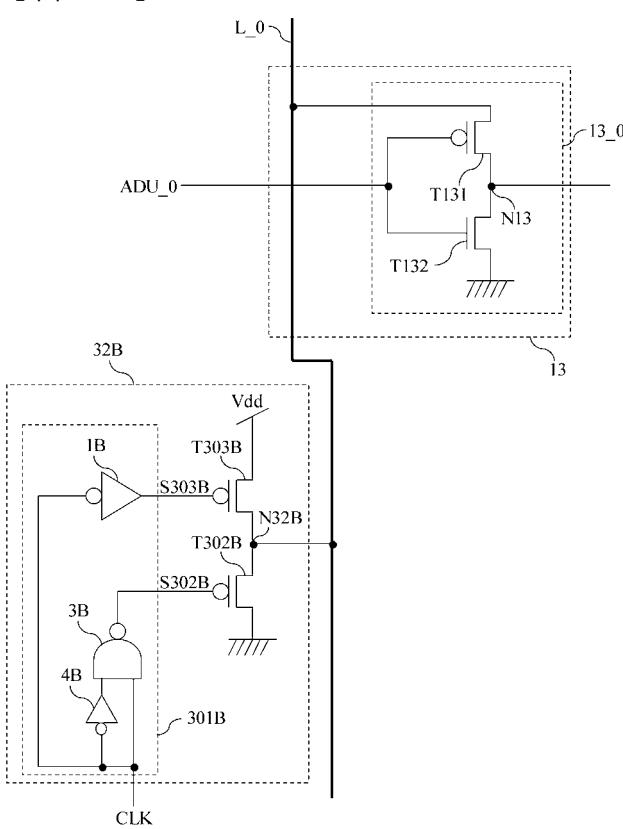

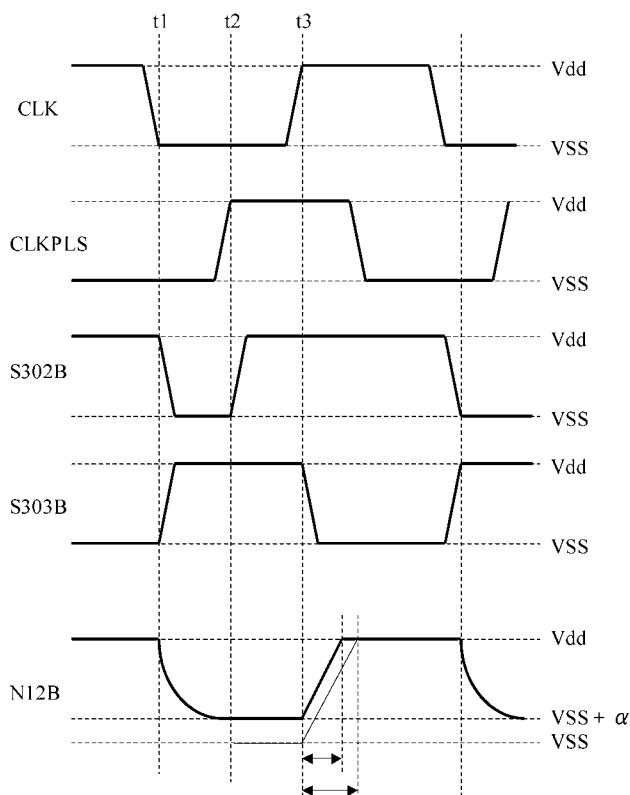

(第9の実施形態)

〈構成〉

図28は、この発明の第9の実施形態によるデコーダ回路の構成を示す。この回路は、図21に示したプリデコーダ22Bに代えて、プリデコーダ32Bを備える。その他の構成は図21と同様である。なお、ここでは、プリデコーダ32Bと、配線L\_0と、ロウデコーダ13のデコード部13\_0のみを図示する。プリデコーダ32Bは、タイミング制御回路301Bと、トランジスタT302B、T303Bとを含む。タイミング制御回路301Bは、複数の論理素子(ここでは、インバータ1B、NAND回路3B、遅延回路4B)によって構成される。タイミング制御回路301Bは、外部からのクロックCLKに応じて制御信号S302B、S303Bを出力する。トランジスタT302B、T303Bは、電源ノードと接地ノードとの間に直列に接続される。トランジスタT302Bは、接地ノードとトランジスタT303Bとの間に接続され、NAND回路3Bからの出力(制御信号S302B)をゲートに受ける。トランジスタT303Bは、トランジスタT302Bと電源ノードとの間に接続され、インバータ1Bからの出力(制御信号S303B)をゲートに受ける。トランジスタT302BとトランジスタT303Bとの接続ノードN32Bは、配線L\_0に接続される。

【0100】

〈動作〉

次に、図28に示したデコーダ回路による動作について図29を参照しつつ説明する。なお、ここでは、各々のトランジスタの閾値電圧を考慮しないものとする。

【0101】

時刻t1になると、クロックCLKが「Hレベル」から「Lレベル」になる。これにより、制御信号S302Bは「Hレベル」から「Lレベル」になるので、トランジスタT302Bはオフからオンになる。一方、制御信号S303Bは「Lレベル」から「Hレベル」になるので、トランジスタT303Bはオンからオフになる。したがって、接続ノードN32Bの電位は、電源ノードの電位「Vdd」から下降していく。

【0102】

時刻t2になると、遅延回路4Bからの出力CLKPLSが「Lレベル」から「Hレベル」になる。これにより、制御信号S302Bは「Lレベル」から「Hレベル」になるの

10

20

30

40

50

で、トランジスタ T 3 0 2 B はオンからオフになる。一方、制御信号 S 3 0 3 B は「H レベル」のままであるので、トランジスタ T 3 0 3 B はオフの状態を維持する。したがって、接続ノード N 3 2 B の電位は、接地ノードの電位「VSS」よりも高い電位「VSS+」になる。

#### 【0103】

時刻 t 3 になると、クロック CLK は「L レベル」から「H レベル」になる。これにより、制御信号 S 3 0 3 B は「H レベル」から「L レベル」になるので、トランジスタ T 3 0 3 B はオフからオンになる。一方、制御信号 S 3 0 2 B は「H レベル」のままであるので、トランジスタ T 3 0 2 B はオフの状態を維持する。したがって、接続ノード N 3 2 B の電位は、電源ノードの電位「Vdd」へ上昇していく。

10

#### 【0104】

##### <効果>

以上のように、接続ノード N 3 2 B の電位が接地ノードの電位「VSS」に達する前にトランジスタ T 3 0 2 B をオフにすることによって、接続ノード N 3 2 B における電位の振幅を小さくすることができる。したがって、接続ノード N 3 2 B から放電される電荷量を削減することができる。また、接続ノード N 3 2 B を充放電するのに要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

#### 【0105】

なお、図 28 では、トランジスタ T 3 0 3 B, T 1 3 1 は「P型」のトランジスタであるが、「N型」のトランジスタであっても構わない。

20

#### 【0106】

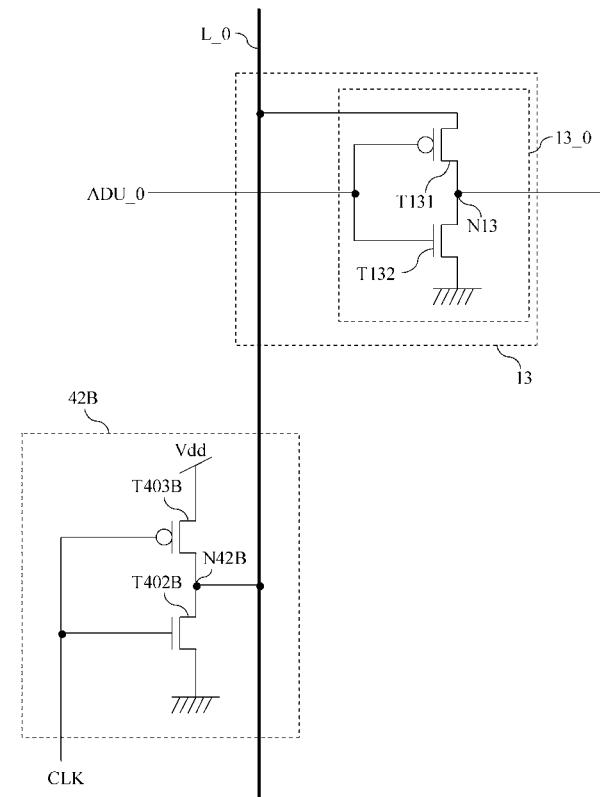

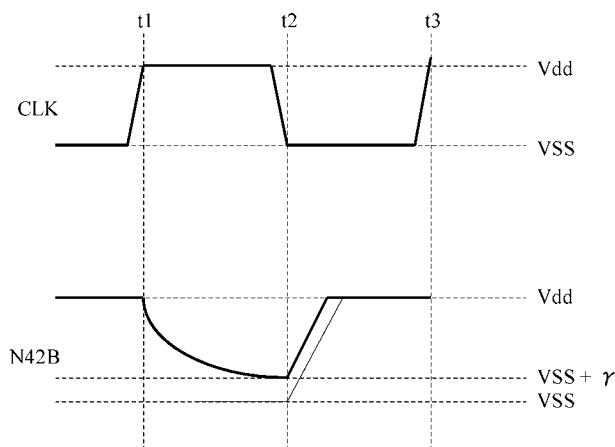

##### (第10の実施形態)

##### <構成>

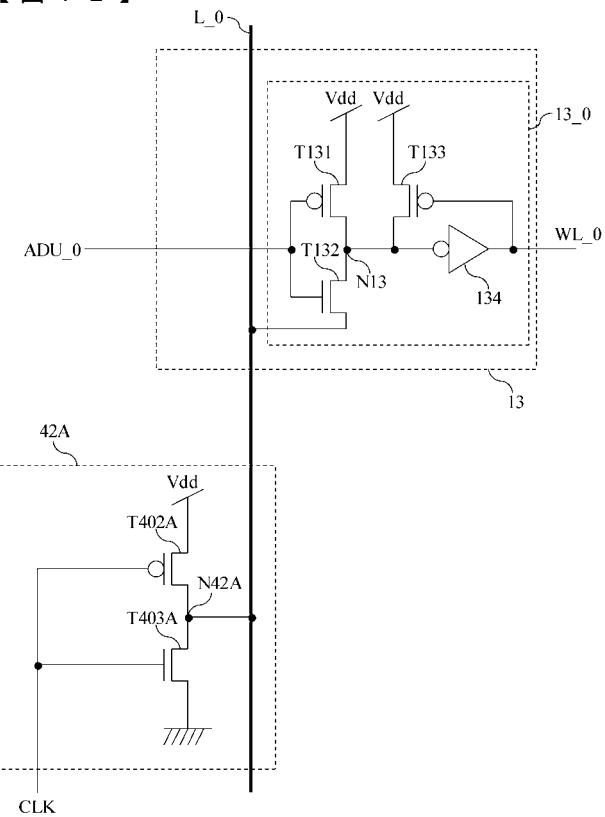

図 30 は、この発明の第10の実施形態によるデコーダ回路の構成を示す。この回路は、図 28 に示したプリデコーダ 3 2 B に代えて、プリデコーダ 4 2 B を備える。その他の構成は図 28 と同様である。プリデコーダ 4 2 B は、トランジスタ T 4 0 2 B, T 4 0 3 B を含む。トランジスタ T 4 0 2 B, T 4 0 3 B は、電源ノードと接地ノードとの間に直列に接続される。トランジスタ T 4 0 2 B は、接地ノードとトランジスタ T 4 0 3 Bとの間に接続され、外部からのクロック CLK をゲートに受ける。トランジスタ T 4 0 3 B は、トランジスタ T 4 0 2 B と電源ノードとの間に接続され、外部からのクロック CLK をゲートに受ける。トランジスタ T 4 0 2 B とトランジスタ T 4 0 3 B との接続ノード N 4 2 B は、配線 L\_0 に接続される。

30

#### 【0107】

トランジスタ T 4 0 2 B の W / L 比は、トランジスタ T 4 0 3 B の W / L 比の 2 倍以下である。例えば、トランジスタ T 4 0 2 B, T 4 0 3 B の各々のゲート長が互いに等しいとすると、トランジスタ T 4 0 2 B のゲート幅は、トランジスタ T 4 0 3 B のゲート幅を 2 倍以下である。また、トランジスタ T 4 0 2 B, T 4 0 3 B の各々のゲート幅が互いに等しいとすると、トランジスタ T 4 0 2 B のゲート長は、トランジスタ T 4 0 3 B のゲート長を (1 / 2) 倍以上である。このような構成により、トランジスタ T 4 0 2 B を単位時間当たりに流れる電流量を、トランジスタ T 4 0 3 B を単位時間当たりに流れる電流量よりも少なくすることができる。つまり、トランジスタ T 4 0 2 B の電流能力は、トランジスタ T 4 0 3 B の電流能力よりも弱い。また、トランジスタ T 4 0 3 B の電流能力は従来と同様であっても良い。

40

#### 【0108】

##### <動作>

次に、図 30 に示したデコーダ回路による動作について図 31 を参照しつつ説明する。

#### 【0109】

時刻 t 1 になると、クロック CLK は「L レベル」から「H レベル」になる。これにより、トランジスタ T 4 0 2 B はオフからオンになり、トランジスタ T 4 0 3 B はオンからオフになる。したがって、接続ノード N 4 2 B の電位は、電源ノードの電位「Vdd」か

50

ら下降していく。

【0110】

時刻  $t_2$  になると、クロック CLK は「H レベル」から「L レベル」になる。これにより、トランジスタ T402B はオンからオフになる。このとき、トランジスタ T402B の電流能力は比較的弱いので、接続ノード N42B の電位は、接地ノードの電位「VSS」に達していない（「VSS+」になる）。また、トランジスタ T403B はオフからオンになる。したがって、接続ノード N42B の電位は、「VSS+」から上昇していく。

【0111】

時刻  $t_3$  になると、クロック CLK は「L レベル」から「H レベル」になる。これにより、トランジスタ T402B はオフからオンになり、トランジスタ T403B はオンからオフになる。このとき、トランジスタ T403B の電流能力は比較的強いので、接続ノード N42B の電位は、電源ノードの電位「Vdd」に達している。

【0112】

<効果>

以上のように、接続ノード N42B の電位が接地ノードの電位「VSS」に達する前にトランジスタ T402B をオフにすることによって、接続ノード N42B における電位の振幅を小さくすることができる。したがって、接続ノード N42B から放電される電荷量を削減することができる。また、接続ノード N42B を充放電するのに要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

【0113】

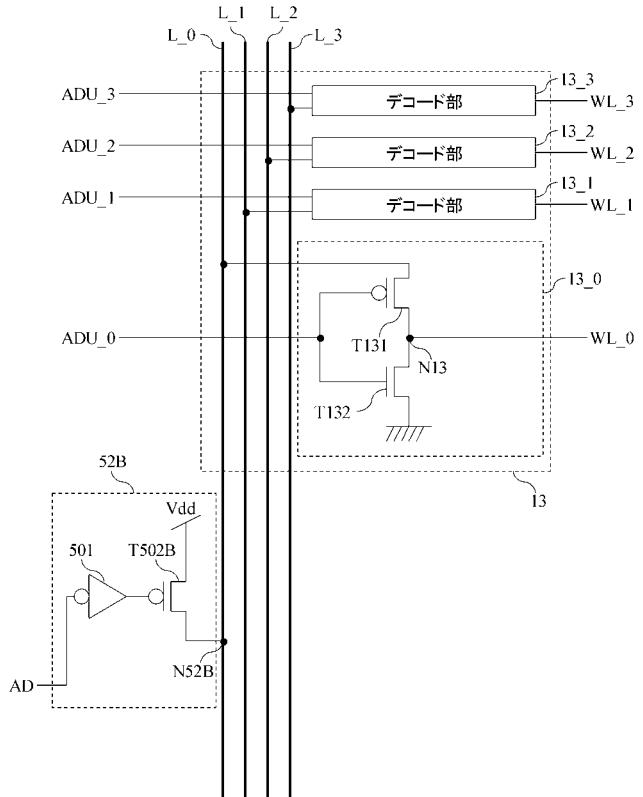

(第11の実施形態)

<構成>

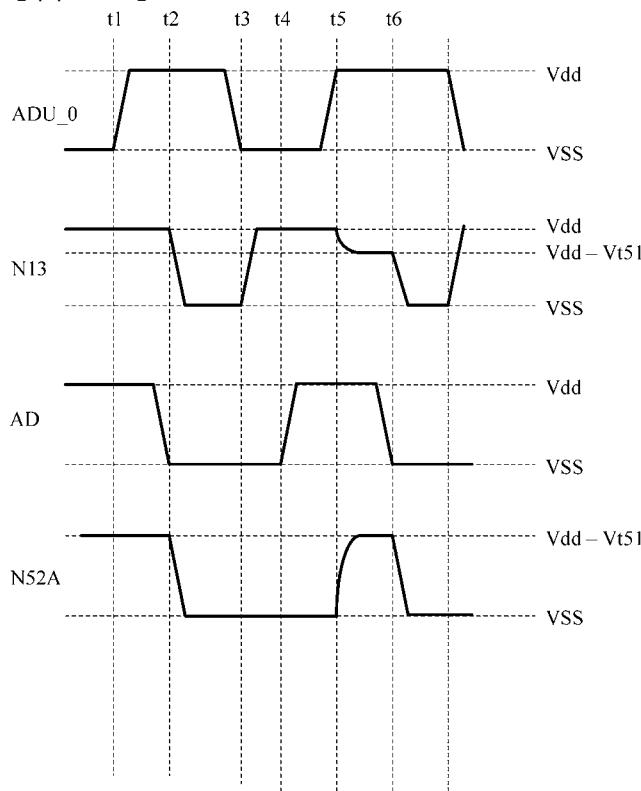

図32は、この発明の発明の第11の実施形態によるデコーダ回路の構成を示す。この回路は、図28に示したプリデコーダ32Bに代えて、プリデコーダ52Bを備える。その他の構成は図28と同様である。プリデコーダ52Bは、インバータ501と、トランジスタ T502B とを備える。トランジスタ T502B は、配線 L\_0 と電源ノードとの間に接続され、インバータ501からの出力をゲートに受ける。トランジスタ T502B は、トランジスタ T131 と同極性である。

【0114】

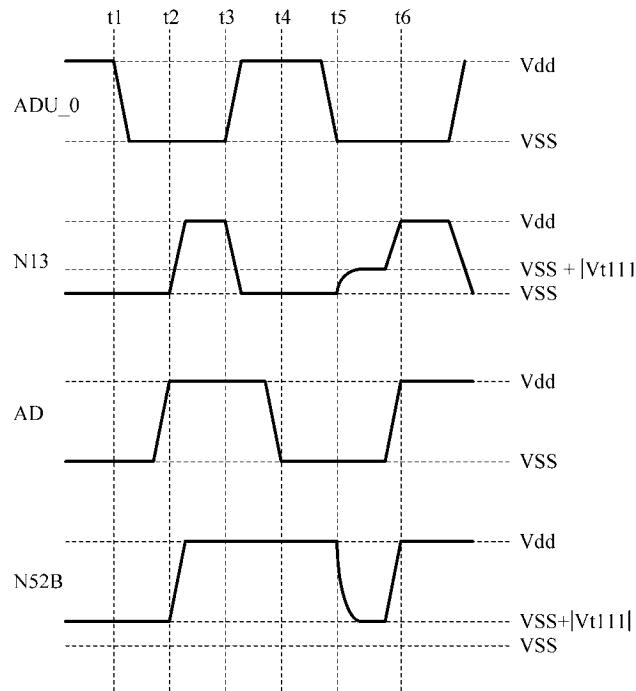

<動作>

次に、図32に示したデコーダ回路による動作について図33を参照しつつ説明する。なお、ここでは、トランジスタ T502B の閾値電圧の絶対値を「|Vt111|」とする。

【0115】

時刻  $t_1$  になると、トランジスタ T131 はオフからオンになり、トランジスタ T132 はオンからオフになる。したがって、接続ノード N13 は、接地ノードから切り離され、接続ノード N52B に接続される。このとき、接続ノード N52B の電位が「VSS+|Vt111|」であるので、接続ノード N13 の電位は、接地ノードの電位「VSS」のままである。

【0116】

時刻  $t_2$  になると、トランジスタ T502B はオフからオンになる。したがって、接続ノード N52B は、電源ノードに接続される。これにより、接続ノード N52B の電位は、「VSS+|Vt111|」から電源ノードの電位「Vdd」に上昇していく。また、接続ノード N13 の電位も、「VSS」から電源ノードの電位「Vdd」に上昇していく。

【0117】

時刻  $t_3$  になると、トランジスタ T131 はオンからオフになり、トランジスタ T132 はオフからオンになる。したがって、接続ノード N13 は、接続ノード N52B から切り離され、接地ノードに接続される。これにより、接続ノード N13 の電位は、電源ノード

10

20

30

40

50

ドの電位「 $V_{dd}$ 」から接地ノードの電位「 $V_{SS}$ 」に下降していく。

【0118】

時刻 $t_4$ になると、トランジスタT502Bはオンからオフになる。したがって、接続ノードN52Bは、電源ノードから切り離される。

【0119】

時刻 $t_5$ になると、トランジスタT131はオフからオンになり、トランジスタT132はオンからオフになる。したがって、接続ノードN13は、接地ノードから切り離され、接続ノードN52Bに接続される。ここで、接続ノードN13の電位は「 $V_{SS}$ 」であり、接続ノードN52Bの電位は「 $V_{dd}$ 」であるので、接続ノードN52Bに充電された電荷が接続ノードN13に分配される。これにより、接続ノードN13, N52Bの各自電位は、「 $V_{SS} + |V_{t111}|$ 」になる。

【0120】

時刻 $t_6$ になると、トランジスタT502Bはオフからオンになる。したがって、接続ノードN52Bは、電源ノードに接続される。これにより、接続ノードN52Bの電位は、「 $V_{SS} + |V_{t111}|$ 」から電源ノードの電位「 $V_{dd}$ 」に上昇する。また、接続ノードN13の電位も、「 $V_{SS} + |V_{t111}|$ 」から電源ノードの電位「 $V_{dd}$ 」に上昇する。

【0121】

<効果>

以上のように、接続ノードN13と接続ノードN52Bとの間で電荷を分配することによって、接続ノードN13の電位が調整される。また、接続ノードN52Aの電位を「 $V_{SS} + |V_{t111}|$ 」を下回らないようにすることができます。したがって、接続ノードN52Bにおける電位の振幅を小さくすることができる。よって、接続ノードN52Bから放電される電荷量を削減することができる。また、接続ノードN52Bを充放電するために要する時間を短縮することができる。このように、高速動作と低消費電力化が可能となる。

【0122】

(第12の実施形態)

<構成>

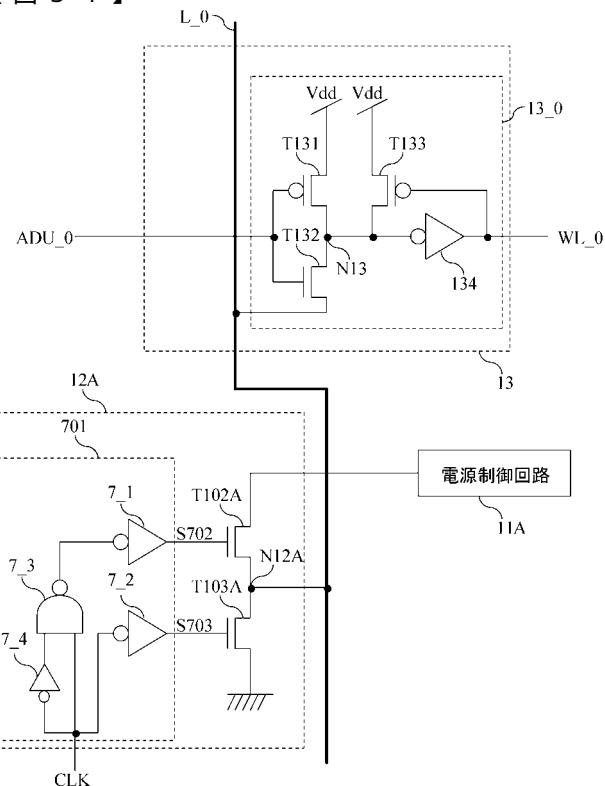

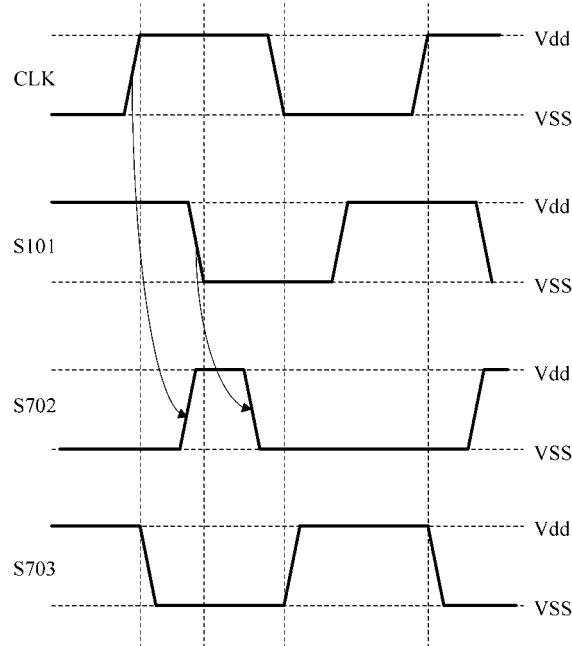

図34は、この発明の第12の実施形態によるデコーダ回路の構成を示す。この回路は、図1と同様であるが、プリデコーダ12Aの内部構成が異なる。なお、ここでは、配線L\_0に接続されるデコード部13\_0のみを図示している。

【0123】

プリデコーダ12Aは、図1に示したインバータ101に代えて、タイミング制御回路701を含む。タイミング制御回路701は、複数の演算素子（ここでは、インバータ7\_1, 7\_2と、NAND回路7\_3と、遅延回路7\_4）から構成される。トランジスタT102Aは、インバータ7\_1からの出力（制御信号S702）をゲートに受ける。トランジスタT103Aは、インバータ7\_2からの出力（制御信号S703）をゲートに受ける。

【0124】

<動作>

次に、図34に示したデコーダ回路による動作について図35を参照しつつ説明する。

【0125】

タイミング制御回路701は、制御信号S703を「Hレベル」から「Lレベル」にした後に制御信号S702を「Lレベル」から「Hレベル」にし、制御信号S702を「Hレベル」から「Lレベル」にした後に制御信号S703を「Lレベル」から「Hレベル」にする。また、タイミング制御回路701は、制御信号S702を「Hレベル」から「Lレベル」にした後に制御信号S703を「Lレベル」から「Hレベル」にし、制御信号S703を「Hレベル」から「Lレベル」にした後に制御信号S702を「Lレベル」から「Hレベル」にする。つまり、制御信号S702, S703の両方が「Lレベル」になる

10

20

30

40

50

期間が設けられている。

【0126】

このようなタイミングを実現するためには、例えば、NAND回路7\_3やインバータ7\_4における遅延量と調整すれば良い。

【0127】

<効果>

以上のように、トランジスタT102A, T103Aの両方がオフになる期間を設けることによって、電源ノードからトランジスタT102A, T103Aを介して接地ノードへ流れる貫通電流を防止することができる。

【0128】

なお、他の実施形態においても、図34に示したタイミング制御回路701を用いて、プリデコーダに含まれるトランジスタのオンオフを調整すれば、同様の効果を得ることができる。

【0129】

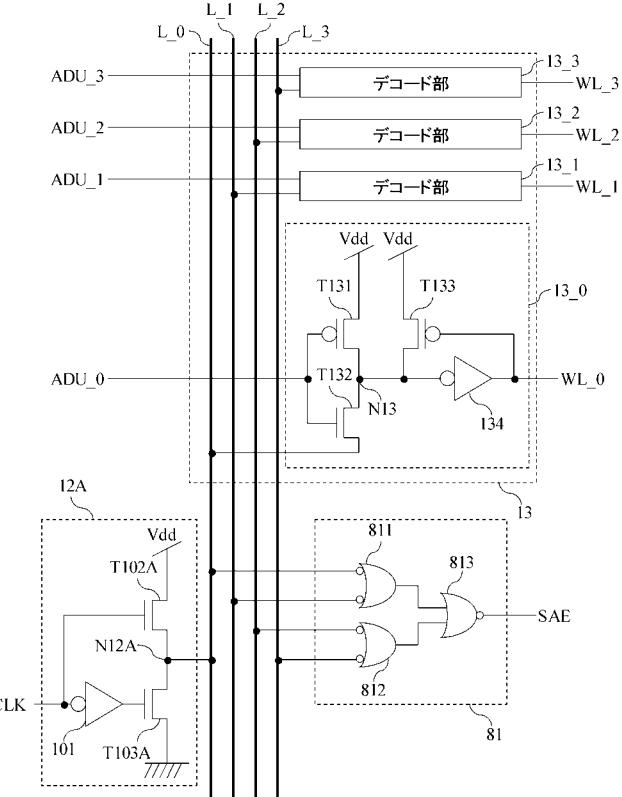

(第13の実施形態)

<構成>

図36は、この発明の第13の実施形態によるデコーダ回路の構成を示す。この回路は、図1に示したデコーダ回路に加えて、センスアンプタイミング生成回路81を備える。センスアンプタイミング生成回路81は、NAND回路811, 812と、NOR回路813とを含む。センスアンプタイミング生成回路81は、配線L\_0, L\_1, L\_2, L\_3の各々における電位に応じて、タイミング信号SAEを「Hレベル」にする。タイミング信号SAEは、センスアンプ(図示せず)を駆動させるために利用される。

【0130】

<動作>

次に、図36に示したデコーダ回路による動作について図37を参照しつつ説明する。

【0131】

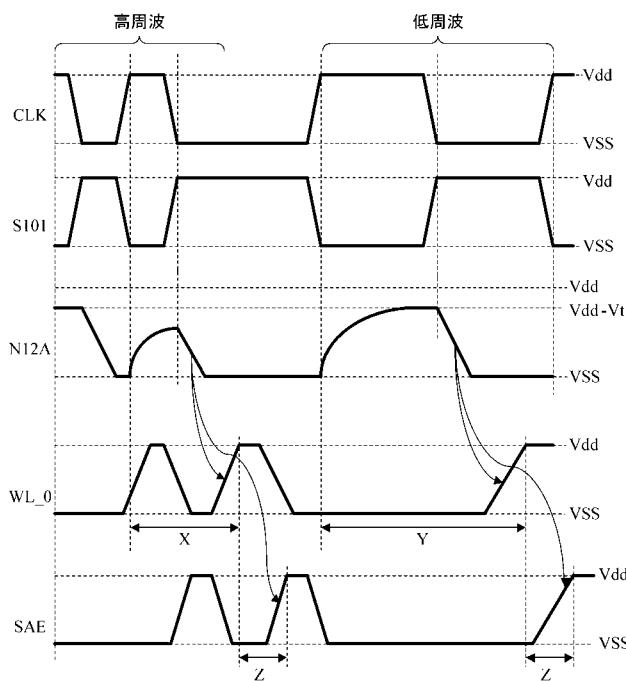

クロックCLKが高周波である場合、接続ノードN12Aに充電される電荷量は、低周波数時と比較して少ない。この場合、クロックCLKが「Hレベル」になってから駆動電圧WL\_0が「Hレベル」になるまでの時間が短い。一方、クロックCLKが低周波数である場合、接続ノードN12Aに充電される電荷量が高周波時と比較して多い。このため、クロックCLKが「Hレベル」になってから駆動電圧WL\_0が「Hレベル」になるまでの時間が長い。

【0132】

ここで、低周波時においてクロックCLKが「Hレベル」になってから駆動電圧WL\_0が「Hレベル」になるまでの時間を「X」とし、高周波時においてクロックCLKが「Hレベル」になってから駆動電圧WL\_0が「Hレベル」になるまでの時間を「Y」とすると、時間Yは時間Xよりも長くなる。センスアンプによって駆動電圧WL\_0を正常に検知するためには、駆動電圧WL\_0の立ち上がり時にセンスアンプが駆動している必要がある。しかし、一般的なセンスアンプは、源信であるクロックCLKに応じて動作するので、クロックCLKが「Hレベル」になってから駆動電圧WL\_0が「Hレベル」になるまでの時間がばらつくと、センスアンプは安定して動作しないおそれがある。

【0133】

センスアンプタイミング生成回路81は、配線L\_0～L\_3の全てが「Hレベル」になると、タイミング信号SAEを「Hレベル」にする。センスアンプ(図示せず)は、センスアンプタイミング生成回路81からのタイミング信号SAEが「Hレベル」になると、駆動する。図37のように、センスアンプタイミング生成回路81からのタイミング信号が一定のタイミング(時間Z)で「Hレベル」になるので、センスアンプ(図示せず)は、ロウデコーダ13から出力される駆動電圧WL\_0を正常に感知することができる。

【0134】

<効果>

10

20

30

40

50

以上のように、タイミング信号を生成することによって、周波数に依存することなく、センスアンプを駆動させることができる。これにより、安定した動作を保証することができる。

【0135】

なお、本実施形態では、図1に示したデコーダ回路にセンスアンプタイミング生成回路81を加えた例について説明したが、他の実施形態にも適用可能である。

【0136】

(第14の実施形態)

<構成>

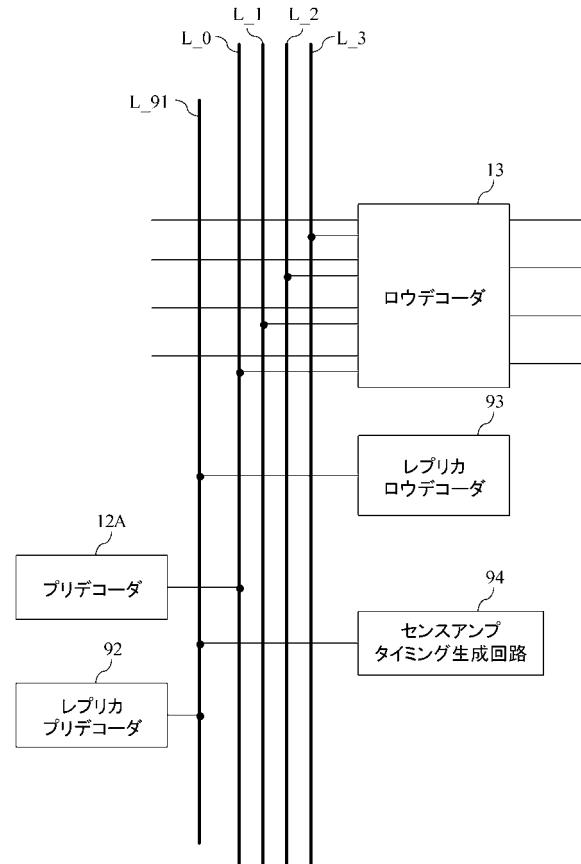

図38は、この発明の第14の実施形態によるデコーダ回路の構成を示す。この回路は、図1に示したデコーダ回路に加えて、配線L\_91と、レプリカプリデコーダ92と、レプリカロウデコーダ93と、センスアンプタイミング生成回路94とを備える。

【0137】

レプリカプリデコーダ92は、プリデコーダ12Aと同様の構成である。レプリカロウデコーダ93は、ロウデコーダ13に含まれる1つのデコード部(ここでは、デコード部13\_0)と同様の構成である。レプリカプリデコーダ92、レプリカロウデコーダ93、およびセンスアンプタイミング生成回路94の各々は、配線L\_91に接続される。

【0138】

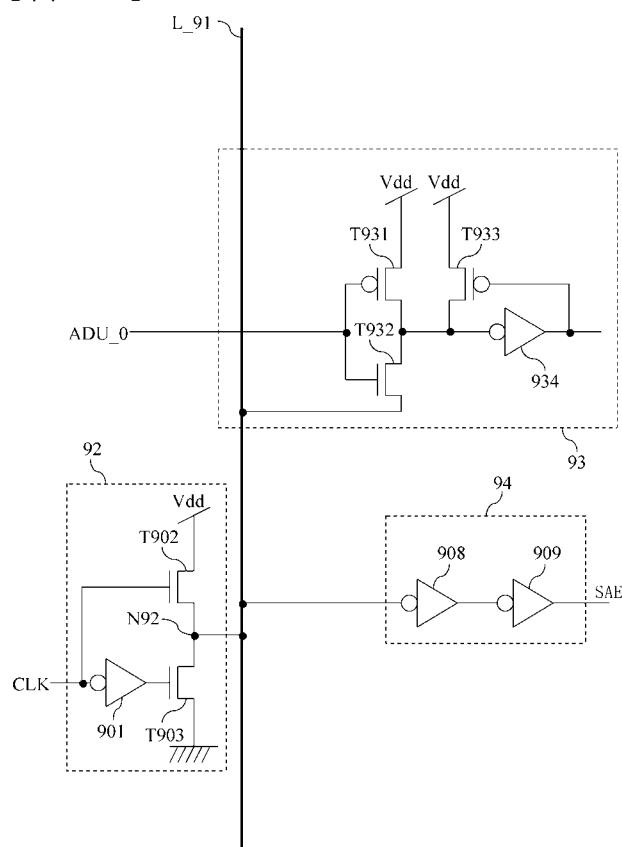

図39は、図38に示したレプリカプリデコーダ92、レプリカロウデコーダ93、およびセンスアンプタイミング生成回路94の内部構成を示す。

【0139】

レプリカプリデコーダ92は、インバータ901と、トランジスタT902、T903とを含む。インバータ901は、図1のインバータ101に対応する。トランジスタT902は、図1のトランジスタT102Aに対応し、トランジスタT102と同様の特性(例えば、閾値電圧、W/L比、電流能力など)を有する。トランジスタT903は、トランジスタT103Aに対応し、トランジスタT103Aと同様の特性を有する。

【0140】

レプリカロウデコーダ93は、トランジスタT931、T932、T933と、インバータ934とを含む。トランジスタT931は、図1のトランジスタT131に対応し、トランジスタT131と同様の特性を有する。トランジスタT932は、図1のトランジスタT132に対応し、トランジスタT132と同様の特性を有する。トランジスタT933、インバータ934は、図1のトランジスタT133、インバータ134に対応し、トランジスタT133、インバータ134と同様の特性を有する。

【0141】

センスアンプタイミング生成回路94は、遅延回路908、909を含む。センスアンプタイミング生成回路94は、接続ノードN92における電位の変動に応じて、タイミング信号SAEを出力する。

【0142】

<効果>

以上のように、センスアンプを駆動させるタイミングを生成するための構成を別に設けることによって、論理素子によって信号が遅延することを防止することができる。これにより、センスアンプを素早く動作させることができる。

【0143】

なお、他の実施形態(例えば、第2の実施形態(図3))にレプリカプリデコーダを適用するためには、レプリカプリデコーダ92の内部構成は、その実施形態におけるプリデコーダの内部構成(例えば、図3のプリデコーダ22A)と同様にすれば良い。さらに、第7~第11の実施形態にレプリカロウデコーダ93を適用するためには、レプリカロウデコーダ93の内部構成は、図19に示したロウデコーダ13と同様にすれば良い。

【0144】

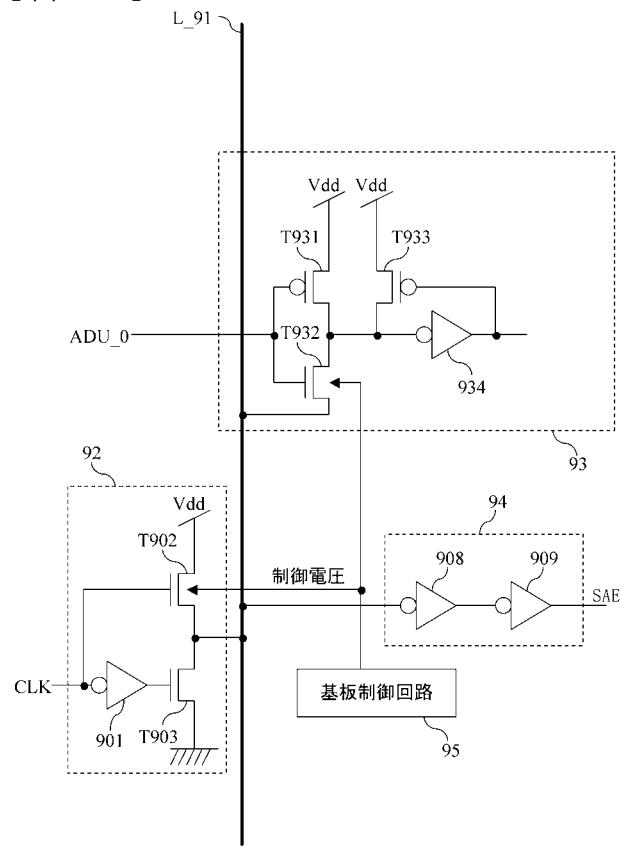

また、図40のように、デコーダ回路が、基板制御回路95を備えていても良い。基板

10

20

30

40

50

制御回路 95 は、基板電圧を出力する。レプリカプリデコーダ 92 のトランジスタ T902 およびレプリカロウデコーダ 93 のトランジスタ T932 の各々は、基板制御回路 95 からの制御電圧を基板に受ける。ここで、基板制御回路 95 は、トランジスタ T902, T932 における閾値電圧のばらつきの下限と等しい値を有する制御電圧を出力すると、トランジスタ T902, T932 の各々の閾値電圧を低くすることができる。これにより、プリデコーダによる高速な電荷の充電や、ロウデコーダから配線 L\_0 へ充電される電荷量の増加を再現することができる。したがって、閾値ばらつきに対して安定した動作を保証することができる。

#### 【0145】

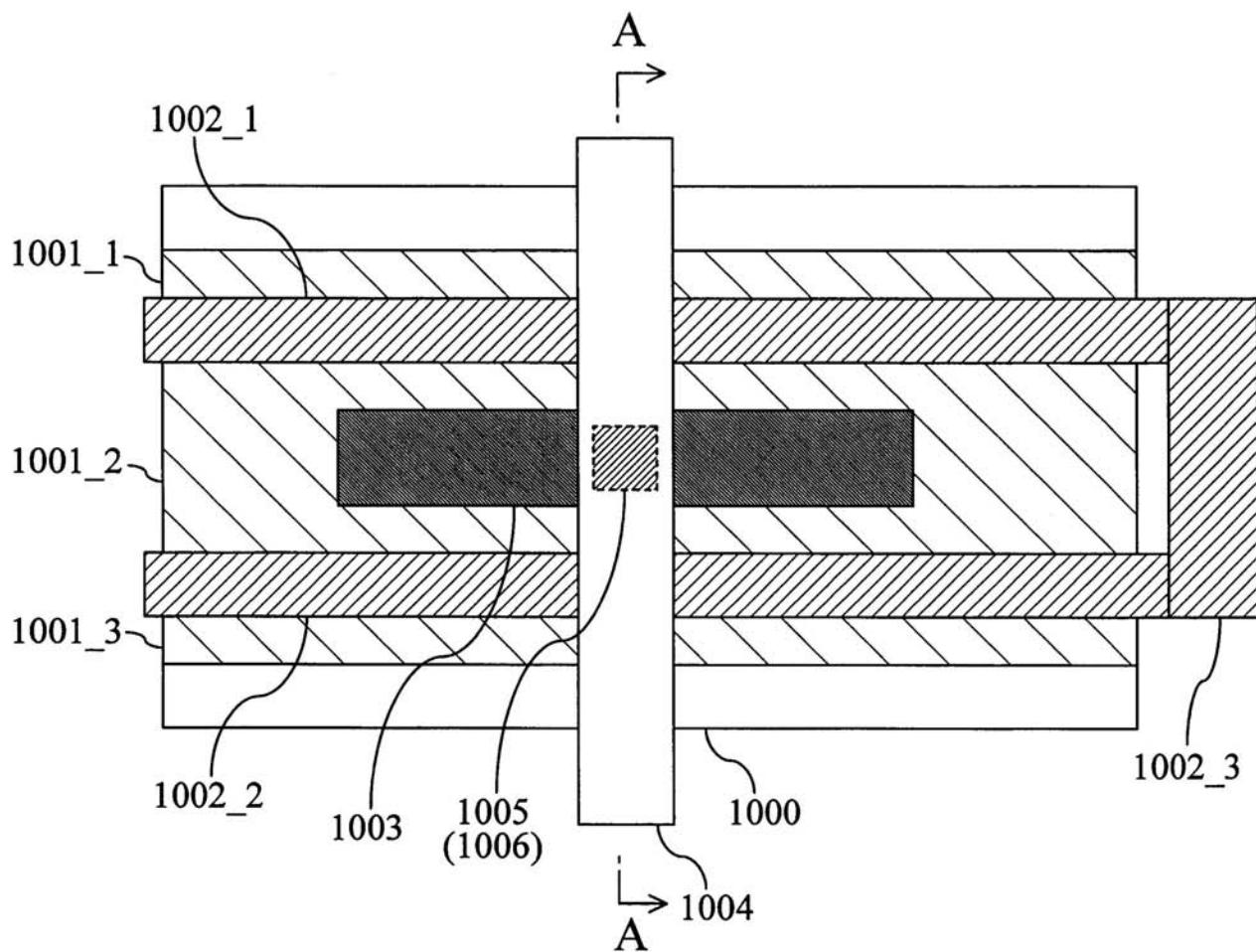

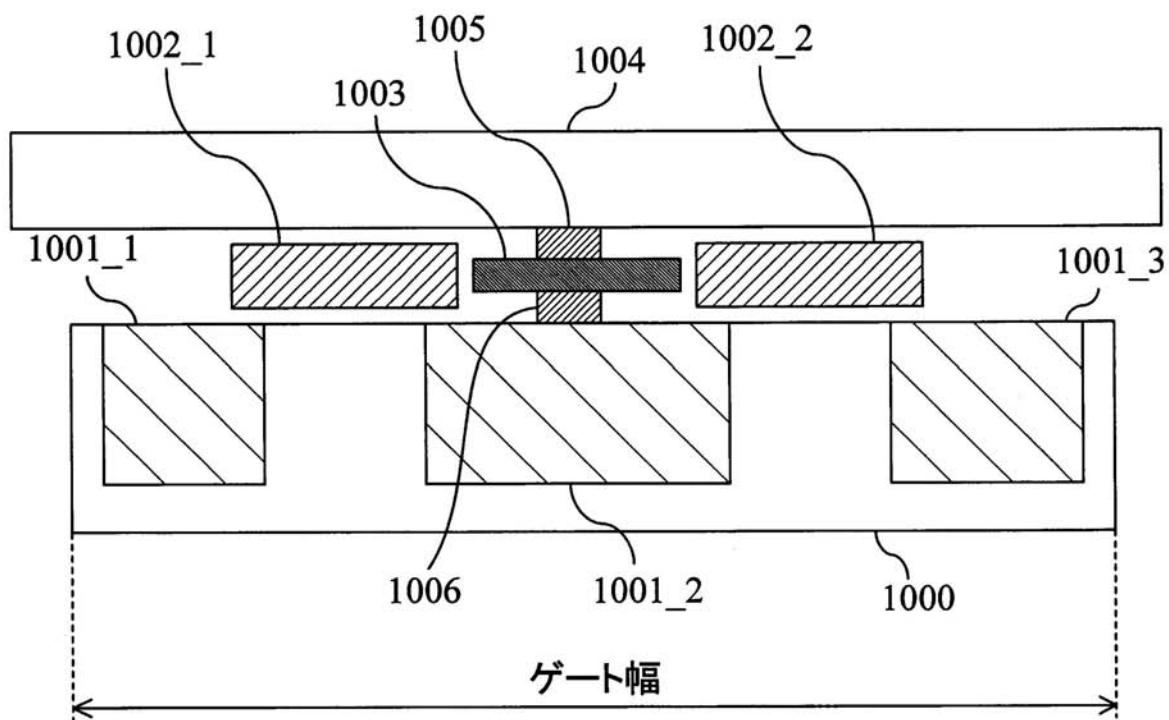

##### (トランジスタの構造)

以上の各実施形態におけるトランジスタ T132 の構造例について図 41, 図 42 を参考しつつ説明する。図 41 はトランジスタ T132 の上面図を示し、図 42 はトランジスタ T132 の断面図を示す。トランジスタ T132 は、半導体基板 1000 と、拡散層 1001\_1, 1001\_2, 1001\_3 と、ゲート電極 1002\_1, 1002\_2 と、1 層配線 1003 と、2 層配線 1004 と、1-2 層間ビア 1005 と、CA1006 とを含む。拡散層 1001\_1, 1001\_2, 1001\_3 の各々は、半導体基板 1000 に形成される。ゲート電極 1002\_1 は、幅方向の両端部が拡散層 1001\_1, 1001\_2 にオーバーラップするように、半導体基板 1000 の上に形成される。ゲート電極 1002\_2 は、幅方向の両端部が拡散層 1001\_2, 1001\_3 にオーバーラップするように、半導体基板 1000 の上に形成される。1 層配線 1003 は、拡散層 1001\_2 の上に形成される。2 層配線 1004 は、1 層配線 1003, ゲート電極 1002\_1, 1002\_2 の上に形成される。1-2 層間ビア 1005 は、1 層配線 1003 と 2 層配線 1004 とを電気的に接続する。CA1006 は、拡散層 1001\_2 と 1 層配線 1003 とを電気的に接続する。また、ゲート電極 1002\_1, 1002\_2 は、ゲート電極接続部 1002\_3 を介して電気的に接続される。図 41 では、ゲート電極 1002\_1, 1002\_2 とゲート電極接続部 1002\_3 とは一体になっており、1 つのコの字状のゲート電極が形成されている。

#### 【0146】

拡散層 1001\_1, 1001\_2, 1001\_3 の各々は、互いに平行に延びるよう 30 に、半導体基板 1000 に形成される。ゲート電極 1002\_1 は、拡散層 1001\_1, 1001\_2 に沿って延びる。ゲート電極 1002\_2 は、拡散層 1001\_2, 1001\_3 に沿って延びる。1 層配線 1003 は、ゲート電極 1002\_1 とゲート電極 1002\_2 との間に位置する。

#### 【0147】

なお、1 層配線 1003 の長さは、

$$\begin{aligned} & ((\text{ゲート幅} \times 0.1) / \text{ゲート電極の分割数}) \text{ 以上であり,} \\ & ((\text{ゲート幅} \times 1.0) / \text{ゲート電極の分割数}) \text{ 以下である。} \end{aligned}$$

#### 【0148】

このような構造にすることによって、拡散容量を半減することができる。また、配線容量を減少させることができる。これにより、高速動作が可能となる。

#### 【0149】

なお、トランジスタ T132 だけでなく、他のトランジスタも上述のような構造であっても良い。

#### 【0150】

##### <トランジスタ T132 の閾値電圧>

以上の各実施形態におけるトランジスタ T132 の閾値電圧について説明する。例えば、図 1 (第 1 の実施形態)において、トランジスタ T132 の閾値電圧がトランジスタ T102A の閾値電圧よりも極端に小さい場合、トランジスタ T102A を介して接続ノード N12A へ電荷を充電しやすくなるが、トランジスタ T132 においてグリッヂが生じやすくなる。したがって、駆動電圧 WL\_0 を受ける回路において多重選択などの誤動作

10

20

30

40

50

が生じてしまう可能性がある。そこで、トランジスタ T132 の閾値電圧をトランジスタ T102A の閾値電圧よりも高くすることによって、トランジスタ T132 におけるグリッヂを抑制することができる。また、その他の実施形態においても、トランジスタ T132 の閾値電圧を高くすれば、同様の効果を得ることができる。

【0151】

以上の各実施形態では、プリデコーダが配線 L\_0 に接続されている例について説明したが、他の配線 L\_1, L\_2, L\_3 の各々にプリデコーダが 1 つずつ接続されている場合も、各々において同様の効果を得ることができる。また、ロウデコーダは 2 つ以上設けられていても良い。この場合、各々のロウデコーダにおいて、各々のデコード部が対応する配線に接続されていれば、同様の効果を得ることができる。

10

【産業上の利用可能性】

【0152】

以上のように、本発明のデコーダ回路は、高速動作や低消費電力化を行いつつ、安定な動作を保証することができるので、ワード線を駆動するデコーダ回路やイネーブル機能付きデコーダ回路等として有用である。

【図面の簡単な説明】

【0153】

【図 1】この発明の第 1 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 2】図 1 に示したデコーダ回路による動作を説明するためのタイミングチャートである。

20

【図 3】この発明の第 2 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 4】図 3 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図 5】図 3 に示したデコーダ回路の変形例の構成を示す回路図である。

【図 6】図 3 に示したデコーダ回路の変形例の構成を示す回路図である。

【図 7】図 6 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

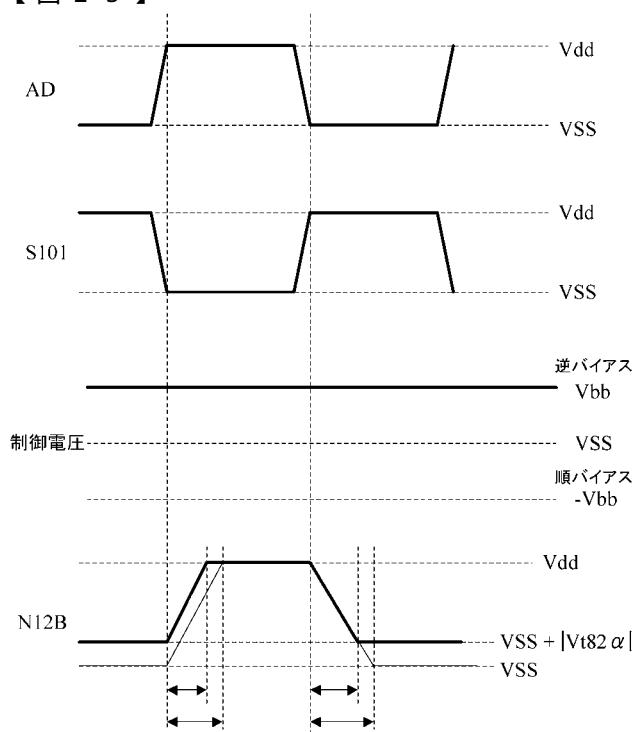

【図 8】図 3 に示したデコーダ回路の変形例の構成を示す回路図である。

【図 9】図 8 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

30

【図 10】この発明の第 3 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 11】図 10 に示したデコーダ回路による動作を説明するためのタイミングチャートである。

【図 12】この発明の第 4 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 13】図 12 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図 14】この発明の第 5 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 15】図 14 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

40

【図 16】この発明の第 6 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 17】図 16 に示したプリデコーダの内部構成を示す回路図である。

【図 18】図 16 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図 19】この発明の第 7 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 20】図 19 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図 21】この発明の第 8 の実施形態によるデコーダ回路の構成を示す回路図である。

【図 22】図 21 に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図 23】図 21 に示したデコーダ回路の変形例の構成を示す回路図である。

50

【図24】図21に示したデコーダ回路の変形例の構成を示す回路図である。

【図25】図21に示したデコーダ回路による動作について説明するためのタイミングチャートである。

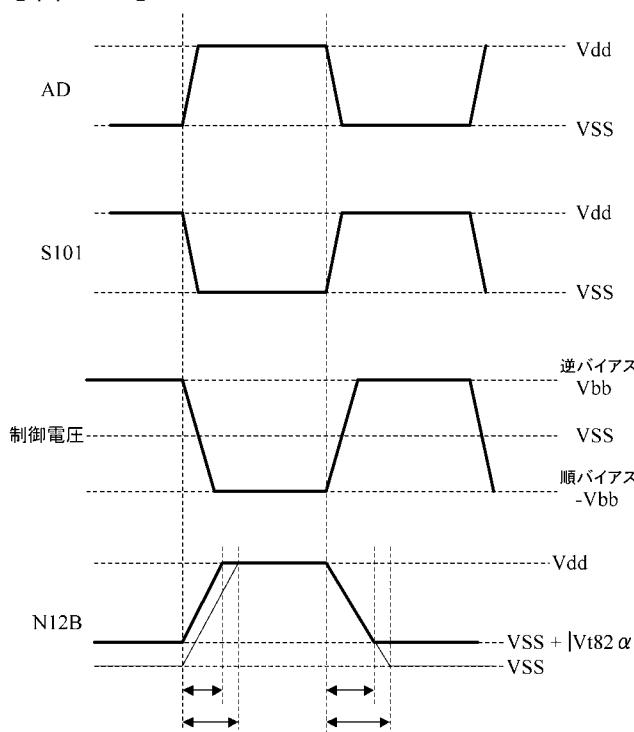

【図26】図20に示したデコーダ回路の変形例の構成を示す回路図である。

【図27】図26に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図28】この発明の第9の実施形態によるデコーダ回路の構成を示す回路図である。

【図29】図28に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図30】この発明の第10の実施形態によるデコーダ回路の構成を示す回路図である。 10

【図31】図30に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図32】この発明の第11の実施形態によるデコーダ回路の構成を示す回路図である。

【図33】図32に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図34】この発明の第12の実施形態によるデコーダ回路の構成を示す回路図である。

【図35】図34に示したデコーダ回路による動作について説明するためのタイミングチャートである。

【図36】この発明の第13の実施形態によるデコーダ回路の構成を示す回路図である。

【図37】図36に示したデコーダ回路による動作について説明するためのタイミングチャートである。 20

【図38】この発明の第14の実施形態によるデコーダ回路の構成を示す回路図である。

【図39】図38に示したレプリカロウデコーダ、レプリカプリデコーダ、センスアンプタイミング制御回路の構成を示す回路図である。

【図40】図38に示したデコーダ回路の変形例について説明するための回路図である。

【図41】本実施形態におけるトランジスタの上面図である。

【図42】本実施形態におけるトランジスタの断面図である。

【符号の説明】

【0154】

11A, 11B 電源制御回路

12A, 22A, 32A, 42A, 52A, 62A, 12B, 22B, 32B, 42B,

52B プリデコーダ

13 ロウデコーダ

13\_0 ~ 13\_3 デコード部

21A, 21B 基板制御回路

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図3-3】

【図3-4】

【図3-5】

【図3-6】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

## フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 増尾 昭

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 法邑 茂夫

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 角谷 範彦

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5B015 HH01 HH03 JJ03 JJ23 KB44

5J055 AX02 AX12 BX42 CX27 DX12 DX56 DX72 DX73 DX83 EX02

EY21 EZ07 EZ12 EZ22 EZ38 EZ50 FX05 FX18 FX20 FX37

GX01 GX02 GX04 GX05

5J056 AA04 BB02 BB17 CC00 CC05 DD12 DD29 EE06 EE07 EE13

FF01 FF07 FF10 GG09 KK01