(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4933944号

(P4933944)

(45) 発行日 平成24年5月16日(2012.5.16)

(24) 登録日 平成24年2月24日(2012.2.24)

(51) Int.Cl.

F 1

**A61B 5/00 (2006.01)**

**A61B 5/01 (2006.01)**

**A61B 5/0245 (2006.01)**

A 61 B 5/00 N

A 61 B 5/00 1 O 1 E

A 61 B 5/00 1 O 2 C

A 61 B 5/02 3 2 O B

A 61 B 5/02 3 2 O Q

請求項の数 15 (全 42 頁)

(21) 出願番号 特願2007-106991 (P2007-106991)

(22) 出願日 平成19年4月16日 (2007.4.16)

(65) 公開番号 特開2007-313299 (P2007-313299A)

(43) 公開日 平成19年12月6日 (2007.12.6)

審査請求日 平成22年3月15日 (2010.3.15)

(31) 優先権主張番号 特願2006-124784 (P2006-124784)

(32) 優先日 平成18年4月28日 (2006.4.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 荒井 康行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小森 美帆

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 遠藤 孝徳

最終頁に続く

(54) 【発明の名称】生体情報検出センサ装置

## (57) 【特許請求の範囲】

## 【請求項1】

生体情報検出センサと、前記生体情報検出センサに接続されたアンテナと、一方の面が表面であり、他方の面が粘着面である粘着テープと、を有し、前記アンテナは、前記粘着テープに設けられた溝を介して、前記粘着テープの粘着面から前記粘着テープの表面に取り出されていることを特徴とする生体情報検出センサ装置。

## 【請求項2】

請求項1において、前記粘着テープの表面には固定機構が設けられていることを特徴とする生体情報検出センサ装置。

10

## 【請求項3】

請求項2において、前記固定機構は、前記粘着テープの表面に設けられた溝部であることを特徴とする生体情報検出センサ装置。

## 【請求項4】

請求項3において、前記溝部が複数設けられていることを特徴とする生体情報検出センサ装置。

## 【請求項5】

請求項3又は請求項4において、

20

前記溝部の底面に粘着材料が設けられていることを特徴とする生体情報検出センサ装置

【請求項 6】

請求項 3 又は請求項 4 において、

前記溝部の側面に突出部が設けられていることを特徴とする生体情報検出センサ装置。

【請求項 7】

複数の薄膜トランジスタが設けられた可撓性の生体情報検出センサと、

前記生体情報検出センサに接続された可撓性のアンテナと、

一方の面が表面であり、他方の面が粘着面である可撓性の粘着テープと、を有し、

前記アンテナは、前記粘着テープに設けられた溝を介して、前記粘着テープの粘着面から前記粘着テープの表面に取り出されていることを特徴とする生体情報検出センサ装置。

10

【請求項 8】

請求項 7 において、

前記生体情報検出センサ装置は曲面に設けられ、

前記複数の薄膜トランジスタのキャリアの移動方向と前記生体情報検出センサ装置の曲がる方向とが揃っていることを特徴とする生体情報検出センサ装置。

【請求項 9】

請求項 7 又は請求項 8 において、

前記粘着テープの表面には固定機構が設けられていることを特徴とする生体情報検出センサ装置。

20

【請求項 10】

請求項 9 において、

前記固定機構は、前記粘着テープの表面に設けられた溝部であることを特徴とする生体情報検出センサ装置。

【請求項 11】

請求項 10 において、

前記溝部が複数設けられていることを特徴とする生体情報検出センサ装置。

【請求項 12】

請求項 10 又は請求項 11 において、

前記溝部の底面に粘着材料が設けられていることを特徴とする生体情報検出センサ装置

30

。 【請求項 13】

請求項 10 又は請求項 11 において、

前記溝部の側面に突出部が設けられていることを特徴とする生体情報検出センサ装置。

【請求項 14】

請求項 1 乃至請求項 13 のいずれか一項において、

前記生体情報検出センサは、一対の電極間に吸湿性の誘電体が介在した素子を有するこ

とを特徴とする生体情報検出センサ装置。

【請求項 15】

請求項 1 乃至請求項 14 のいずれか一に記載の生体情報検出センサ装置は腕に巻かれて

いることを特徴とする生体情報検出センサ装置。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、人体の生体情報（電気信号）を、人体に取り付けられた生体情報検出センサで検出し、検出した生体情報を送信し、検出もしくは送信された生体情報について、外部機器と通信することができる生体情報処理装置に関する。

【背景技術】

【0002】

近年、健康チェック等の要望に応えるため、使用者の検出部位に装着され、生体情報を

50

検出する生体情報検出センサが開発され、電子デバイスの小型化と相まって生体情報検出センサの小型化が進みつつある（特許文献1参照）。

【特許文献1】特開2003-275183号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

生体情報検出センサを常に人体に接触させておくのは、不衛生であり、人体の皮膚に悪い影響を及ぼす恐れがある。

【0004】

そこで本発明においては、簡単に取り替えることのできる生体情報検出センサ装置を提供することを課題とする。 10

【課題を解決するための手段】

【0005】

本発明は、粘着材料が設けられた粘着面と、前記粘着材料が設けられない表面を有する粘着テープと、前記粘着テープの粘着面側に取り付けられた、生体情報検出部と、メモリ部と、演算処理回路部と、通信回路部とを含む生体情報検出センサと、前記生体情報検出センサに接続され、前記粘着テープに設けられた溝を介して、前記粘着テープの粘着面から表面に取り出されたアンテナとを有し、前記メモリ部には、生体情報が記憶されることを特徴とする生体情報検出センサ装置に関するものである。

【0006】

20

また本発明は、粘着材料が設けられた粘着面と、前記粘着材料が設けられない表面を有する粘着テープと、前記粘着テープの粘着面側に取り付けられた、生体情報検出部と、絶縁表面に形成され島状に分割形成された半導体層でチャネル領域が形成される薄膜トランジスタで形成された、メモリ部と、演算処理回路部と、通信回路部とを含む生体情報検出センサと、前記生体情報検出センサに接続され、前記粘着テープに設けられた溝を介して、前記粘着テープの粘着面から表面に取り出されたアンテナとを有し、前記メモリ部には、生体情報が記憶されることを特徴とする生体情報検出センサ装置に関するものである。

【0007】

本発明において、前記粘着テープの表面に溝部を設け、該溝部の底面に粘着材料を埋設し、前記粘着材料によって前記アンテナが固定されているものである。 30

【0008】

本発明において、前記粘着テープの表面に溝部を設け、該溝部の側面に突起部を設け、前記アンテナが嵌装されているものである。

【0009】

また本発明は、粘着材料が設けられた粘着面と、粘着材料が設けられない表面を有する粘着テープと、前記粘着テープの粘着面側に取り付けられ、IDチップ（ICチップ、IDタグ、ICタグ、RFID、無線タグともいう）と生体情報検出部を有する生体情報検出センサと、前記生体情報検出センサに接続され、前記粘着テープに設けられた溝を介して、前記粘着テープの粘着面から表面に取り出されたアンテナとを有し、前記IDチップには、生体情報が記憶されることを特徴とする生体情報検出センサ装置に関するものである。 40

【0010】

本発明において、前記アンテナにより、IDチップに記憶される情報及びセンサによって検出される情報の送受信を行うものである。

【0011】

本発明において、前記アンテナは、前記粘着テープの表面に設けられた固定機構により、前記粘着テープの表面に固定され、前記固定機構とは、前記粘着テープの表面に溝を設け、溝の底面に粘着材料を設け、前記アンテナを貼り付ける機構、もしくは、前記粘着テープの表面に溝を設け、前記溝の側面に突起部を設けて前記アンテナをはめ込む機構である。 50

**【発明の効果】****【0012】**

本発明の生体情報検出センサ装置は、直接に人間の皮膚と接触させるものであるので、汗などで外側がすぐ汚れてしまう恐れがある。あるいは、生体情報検出センサ装置に含まれるトランジスタの半導体層が、汗に含まれているアルカリ金属元素によって汚染されてしまい、トランジスタの電気特性が低下する恐れもある。しかしながら、本発明によれば、生体情報検出センサが汚れたとしてもすぐ新しいものに取り替えることができ、衛生的である。

**【0013】**

かつ、本発明の生体情報検出センサシステムは、製造コストが安いので、新しいものに取り替えることが簡単であり、常に衛生的な生体情報検出センサを身につけることが可能となる。10

**【発明を実施するための最良の形態】****【0014】**

本実施の形態を、図1(A)～図1(B)、図2(A)～図2(B)、図3を用いて説明する。20

**【0015】**

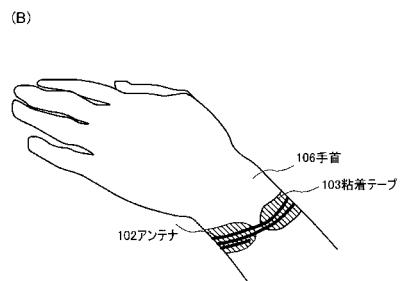

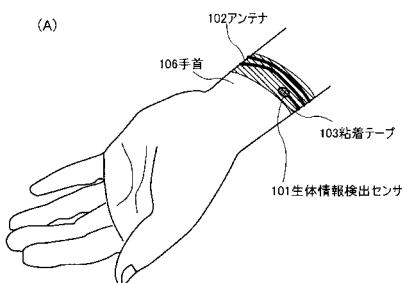

人間の手首106の脈のふれる部分に、生体情報検出センサ101を、粘着テープ103により貼り付ける。粘着テープ103は、粘着材料が設けられている粘着面と、粘着材料が設けられていない表面を有しており、生体情報検出センサ101は、粘着面に設けられた粘着材料によって、人間の手首106に貼り付けられる。生体情報検出センサ101には、湿度センサ、体温センサ、脈拍センサ、個人情報が記録されたIDチップ等が内蔵されている(図1参照)。本明細書では、生体情報検出センサ101とそれを貼り付ける粘着テープ103の組み合わせを生体情報検出センサ装置あるいは生体情報検出センサシステムと呼ぶことにする。なお図1では生体情報検出センサ101を手首に貼り付けてあるが、生体情報検出センサ101を貼り付ける場所は手首に限らず、足や耳や首等、必要に応じて場所を変えてよい。20

**【0016】**

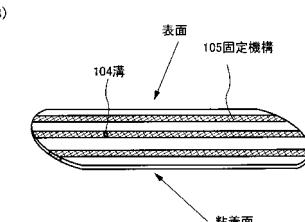

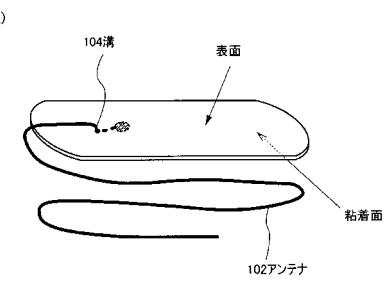

生体情報検出センサ101には、情報の送信または受信のためのアンテナ102が設かれている。アンテナ102は、粘着テープ103の粘着面から、溝104を介して、粘着材料が設けられていない表面に取り出される。粘着テープ103の表面には、アンテナ102を固定する固定機構105があり、粘着テープ103を手首106に固定した後、アンテナ102は粘着テープ103の表面に固定される(図2参照)。30

**【0017】**

固定機構105は、例えば粘着テープ103の表面に溝を設け、溝の底面に粘着材料を設け、アンテナ102を貼り付けるようにしてもよい。また、例えば粘着テープ103の表面に溝を設け、溝の側面に突起部を設けてアンテナ102をはめ込むようにしてもよい。

**【0018】**

もしアンテナ102が長くて粘着テープ103表面の固定機構に収まりきらない場合は、別の粘着テープを用いて腕に貼り付ければよい。40

**【0019】**

粘着テープ103の表面に、アンテナ102の固定機構があるので、アンテナ102が日常の生活行動に対して邪魔にならない。

**【0020】**

生体情報検出センサ101に内蔵されたIDチップには、その人物の名前、性別、血液型、生年月日、既往症、身長体重等のデータがあらかじめ記録されている。

**【0021】**

生体情報検出センサ101に内蔵された脈拍センサは、検出した脈拍データをアンテナ102を介して、外部メモリに送る。送られた脈拍データは、あらかじめ外部メモリに登50

録されている脈拍データと比較され、正常か異常か判断される。

【0022】

体温に関しても、脈拍と同様に、生体情報検出センサ101に内蔵された体温センサは、検出した体温データをアンテナ102を介して、外部メモリに送る。送られた体温データは、あらかじめ外部メモリに登録されている体温データと比較され、正常か異常か判断される。

【0023】

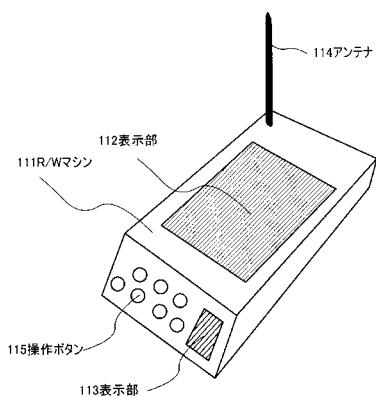

検出された脈拍データ及び体温データは、アンテナ102を介して送られるが、それらデータは、読み込み(R)/書き込み(W)マシン(以下「R/Wマシン」という)111のアンテナ114を介してR/Wマシン111に取り込まれる。取り込まれたデータは、R/Wマシン111に内蔵されている内部メモリに蓄積される。R/Wマシン111の内蔵メモリにはあらかじめ脈拍データや体温データ等が登録されており、生体情報検出センサ101から送られてくるデータと比較検証される(図3参照)。

【0024】

データの比較が行われ、送られてきたデータが異常だと判断されると、R/Wマシン111の表示部112に、アラームが表示され、異常を知らせる。このとき異常であるデータの数値が正常な数値とどのくらいかけ離れているのかを表示してもよい。

【0025】

R/Wマシン111は、もう1つ表示部113を有しており、R/Wマシン111の状態そのものを表示する。また操作ボタン115は、必要に応じて表示の切り替えを行ったり、アラームを止めたり、電源をオン/オフするための操作ボタンである。

【0026】

またR/Wマシン111は、生体情報検出センサ101に内蔵されたIDチップの記録された情報に変更があれば、その情報を書き換えることができる。例えば、IDチップに蓄えられている情報のうち、身長体重、既往症等に変更があれば、書き換えることができる。

【0027】

書き換えの方法は、操作ボタン115によりデータを作製し、アンテナ114より無線信号にて、生体情報検出センサ101に送る。アンテナ102を介して受け取った情報により、生体情報検出センサ101内のIDチップの内部情報を書き換える。

【0028】

またR/Wマシン111で直接情報を作製せず、別のコンピュータ等でデータを作製し、そのデータをR/Wマシン111を介してIDチップに送ってもよい。

【0029】

R/Wマシン111は、携帯型のものが好ましく、生体情報検出センサ101を装着している人間の側に置いておくことが好ましい。

【0030】

なお本実施の形態は、必要があれば実施例と組み合わせることが可能である。

【実施例1】

【0031】

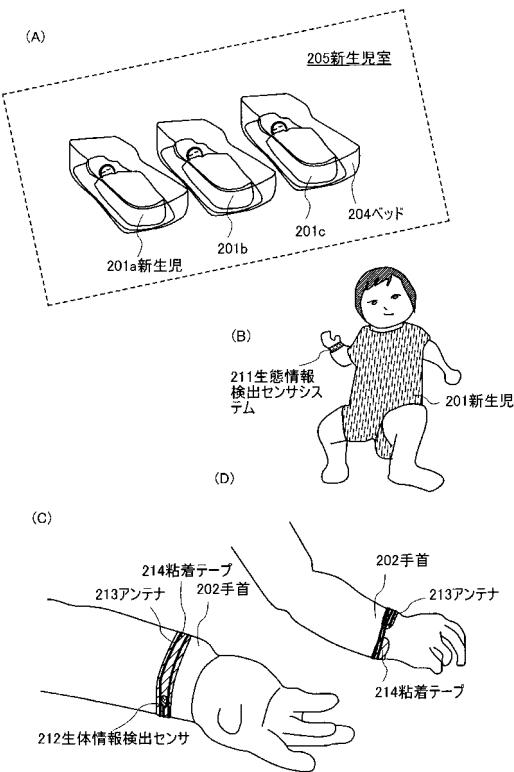

本実施例では、本発明の生体情報検出センサを新生児を含む乳幼児に適用した例について、図4(A)~図4(D)を用いて説明する。

【0032】

病院の新生児室205に置かれているベッド204には新生児201(201a、201b、201c、...)が寝かされており(図4(A)参照)、新生児201の手首202には、生体情報検出センサシステム211が貼り付けられている(図4(B)参照)。

【0033】

生体情報検出センサシステム211は、実施の形態で述べた構成をしている、すなわち、生体情報検出センサ212は、粘着テープ214により手首202に貼り付けられている。また生体情報検出センサ212には送受信用のアンテナ213が取り付けられており

10

20

30

40

50

、アンテナ 213 は粘着テープ 214 に設けられた溝を通って、粘着面から表面に取り出され、粘着テープ 214 の表面に設けられた固定機構により、粘着テープ 214 の表面に固定される。

【0034】

また実施の形態で述べたように、粘着テープの表面に溝部を設け、溝部の底面に粘着材料を埋設してアンテナを固定してもよいし、溝部の側面に突起部を設け、アンテナを嵌装してもよい。

【0035】

生体情報検出センサ 212 には、湿度センサ、体温センサ、脈拍センサ、個人情報が記録された ID チップが内蔵されている。個人情報とは、生年月日、性別、血液型、親の名前、身長体重等で、あらかじめ ID チップに記憶させてから生体情報検出センサ 212 を装着してもよいし、身長体重など変化するものは、測定ごとに書き換えてよい。また血液型など後から検査して判明するものなどについては、生体情報検出センサ 212 を装着した後に記憶させてもよい。

10

【0036】

個人情報を生体情報検出センサ 212 中の ID チップに記憶させておくことにより、新生児 201 の識別を容易にし、万が一の取り違いを防止することができる。また身長体重、血液型等の情報を、簡単に知ることができる。

【0037】

また生体情報検出センサ 212 に内蔵されている湿度センサ、体温センサ、脈拍センサなどの各種センサにより、新生児 201 の体調管理を行うことができる。例えば、体温センサにより体温を常時観察し、一定の温度以上を示したら警告を出すようにして、体調に異常があった場合でもすぐに対応することが可能となる。

20

【0038】

新生児を含む乳幼児は新陳代謝が激しく、皮膚もあまり強くないので、頻繁に簡単に取り替えることのできる本実施例の生体情報検出センサシステムは、衛生的かつ簡便であるという利点がある。

【0039】

また必要であれば生体情報検出センサ 212 に、位置情報を発信するような装置を内蔵してもよい、生体情報検出センサ 212 に設けられた発信装置と、発信装置を検知する検知装置を用いることにより、新生児室 205 にいるか、病院内の親の病室にいるか、あるいは親の病室の外にいるか、病院内のどこにいるかを瞬時に把握することができる。

30

【0040】

なお本実施例は、必要があれば実施の形態、実施例と組み合わせることが可能である。

【実施例 2】

【0041】

本実施例では、本発明を用いて ID チップ (IC タグ、IC チップともいう) を作製した例を図 5 (A) ~ 図 5 (B) 、図 6 (A) ~ 図 6 (B) 、図 7 (A) ~ 図 7 (B) 及び図 8 (A) ~ 図 8 (B) を用いて示す。

40

【0042】

本実施例では、半導体素子として絶縁分離された TFT を例示するが、集積回路に用いられる半導体素子はこれに限定されず、あらゆる回路素子を用いることができる。例えば、TFT の他に、記憶素子、ダイオード、光電変換素子、抵抗素子、コイル、容量素子、インダクタなどが代表的に挙げられる。

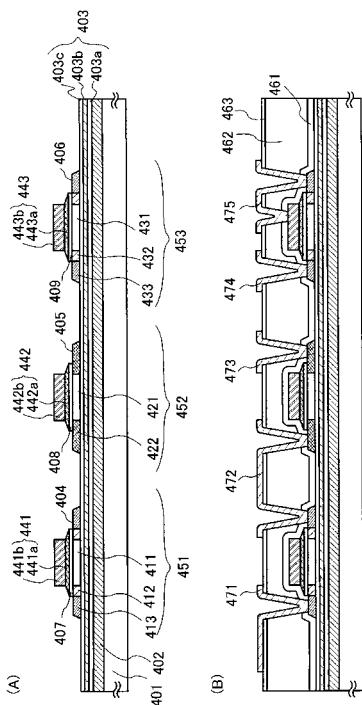

【0043】

まずスパッタ法を用いて耐熱性を有する基板 (第 1 の基板) 401 上に剥離層 402 を形成する。第 1 の基板 401 として、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレス基板を含む金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基

50

板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

#### 【0044】

剥離層402は、非晶質シリコン、多結晶シリコン、単結晶シリコン、微結晶シリコン（セミアモルファスシリコンを含む）等、シリコンを主成分とする層を用いることができる。剥離層402は、スパッタ法、減圧CVD法、プラズマCVD法等を用いて形成することができる。本実施例では、膜厚50nm程度の非晶質シリコンを減圧CVD法で形成し、剥離層402として用いる。なお剥離層402はシリコンに限定されず、エッチングにより選択的に除去できる材料で形成すれば良い。剥離層402の膜厚は、50～60nmとするのが望ましい。セミアモルファスシリコンに関しては、30～50nmとしてもよい。10

#### 【0045】

なおセミアモルファスシリコンに代表されるセミアモルファス半導体とは、非晶質半導体と結晶構造を有する半導体（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。このセミアモルファス半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5～20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。

#### 【0046】

また、未結合手（ダングリングボンド）を終端化させる材料として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体（SAS）と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。20

#### 【0047】

セミアモルファスシリコンは、そのラマンスペクトルが $520\text{ cm}^{-1}$ よりも低波数側にシフトしており、またX線回折では珪素（Si）結晶格子に由来するとされる（111）、（220）の回折ピークが観測される。

#### 【0048】

またセミアモルファスシリコンは珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、 $\text{SiH}_4$ であり、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素を含む気体を希釈して用いることで、セミアモルファスシリコンの形成を容易なものとすることができます。希釈率は2倍～1000倍の範囲で珪素を含む気体を希釈することが好ましい。30

#### 【0049】

次に、剥離層402上に、下地膜403を形成する。下地膜403は第1の基板401中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、TFTなどの半導体素子の電気特性に悪影響を及ぼすのを防ぐために設ける。また下地膜403は、後の半導体素子を剥離する工程において、半導体素子を保護する役目も有している。下地膜403は单層であっても複数の絶縁膜を積層したものであっても良い。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる酸化珪素や、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素などの絶縁膜を用いて形成する。40

#### 【0050】

本実施例では、下層下地膜403aとして膜厚100nmの窒素を含む酸化珪素膜、中層下地膜403bとして膜厚50nmの酸素を含む窒化珪素膜、上層下地膜403cとして膜厚100nmの窒素を含む酸化珪素膜を順に積層して下地膜403を形成するが、各膜の材質、膜厚、積層数は、これに限定されるものではない。例えば、下層下地膜403aの窒素を含む酸化珪素膜に代えて、膜厚0.5～3μmのシロキサン系樹脂をスピンドル法、スリットコーティング法、液滴吐出法などによって形成しても良い。また、中層下地50

膜403bの酸素を含む窒化珪素膜に代えて、窒化珪素膜(Si<sub>3</sub>N<sub>4</sub>等)を用いてもよい。また、上層下地膜403cの窒素を含む酸化珪素膜に代えて、酸化珪素膜を用いてても良い。また、それぞれの膜厚は、0.05~3μmとするのが望ましく、その範囲から自由に選択することができる。

#### 【0051】

或いは、剥離層402に最も近い、下地膜403の下層下地膜403aを窒素を含む酸化珪素膜または酸化珪素膜で形成し、中層下地膜403bをシロキサン系樹脂で形成し、上層下地膜403cを酸化珪素膜で形成しても良い。

#### 【0052】

ここで、酸化珪素膜は、SiH<sub>4</sub>とO<sub>2</sub>、又はTEOS(テトラエトキシシラン)とO<sub>2</sub>等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の方法によって形成することができる。また、窒化珪素膜は、代表的には、SiH<sub>4</sub>とNH<sub>3</sub>の混合ガスを用い、プラズマCVDによって形成することができる。また、窒素を含む酸化珪素膜(組成比O>N)、酸素を含む窒化珪素膜(組成比N>O)は、代表的には、SiH<sub>4</sub>とN<sub>2</sub>Oの混合ガスを用い、プラズマCVDによって形成することができる。

#### 【0053】

次に、下地膜403上に半導体膜を形成する。半導体膜は、下地膜403を形成した後、大気に曝さずに形成することが望ましい。半導体膜の膜厚は20~200nm(望ましくは40~170nm、好ましくは50~150nm)とする。なお半導体膜は、非晶質半導体であっても良いし、セミアモルファス半導体であっても良いし、多結晶半導体であっても良い。また半導体は珪素だけではなくシリコンゲルマニウムも用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01~4.5atom%程度であることが好ましい。

#### 【0054】

非晶質半導体は、珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>が挙げられる。この珪素を含む気体を、水素、あるいは水素とヘリウムで希釈して用いても良い。

#### 【0055】

なお上述したようにセミアモルファス半導体は、珪素を含む気体をグロー放電分解することにより得ることができが、珪素を含む気体中に、CH<sub>4</sub>、C<sub>2</sub>H<sub>6</sub>などの炭化物気体、GeH<sub>4</sub>、GeF<sub>4</sub>などのゲルマニウム化気体、F<sub>2</sub>などを混入させて、エネルギーバンド幅を1.5~2.4eV、若しくは0.9~1.1eVに調節しても良い。

#### 【0056】

例えば、SiH<sub>4</sub>にH<sub>2</sub>を添加したガスを用いる場合、或いはSiH<sub>4</sub>にF<sub>2</sub>を添加したガスを用いる場合、形成したセミアモルファス半導体を用いてTFTを作製すると、該TFTのサブスレッショルド係数(S値)を0.35V/dec以下、代表的には0.25~0.09V/decとし、移動度を10cm<sup>2</sup>/Vsecとすることができる。そして上記セミアモルファス半導体を用いたTFTで、例えば19段リングオシレータを形成した場合、電源電圧3~5Vにおいて、その発振周波数は1MHz以上、好ましくは100MHz以上の特性を得ることができる。また電源電圧3~5Vにおいて、インバータ1段あたりの遅延時間は26ns、好ましくは0.26ns以下とすることができます。

#### 【0057】

そして半導体膜を、レーザを用いて結晶化する。或いは、触媒元素を用いる結晶化法と、レーザを用いたレーザ結晶化法とを組み合わせも良い。

#### 【0058】

レーザ結晶化を行なう場合、レーザ結晶化の前に、レーザに対する半導体膜の耐性を高めるために、500~1時間の加熱処理を該半導体膜に加えてもよい。

#### 【0059】

レーザ結晶化は、連続発振のレーザ(CWレーザ)、または擬似CWレーザとして、発

10

20

30

40

50

振周波数が 10 MHz 以上、好ましくは 80 MHz 以上のパルス発振レーザを用いることができる。

#### 【0060】

具体的には、連続発振のレーザとして、Ar レーザ、Kr レーザ、CO<sub>2</sub> レーザ、YAG レーザ、YVO<sub>4</sub> レーザ、フォルステライト (Mg<sub>2</sub>SiO<sub>4</sub>) レーザ、YLF レーザ、YAlO<sub>3</sub> レーザ、GdVO<sub>4</sub> レーザ、Y<sub>2</sub>O<sub>3</sub> レーザ、アレキサンドライトレーザ、Ti : サファイアレーザ、ヘリウムカドミウムレーザ、多結晶 (セラミック) の YAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub> にドーパントとして Nd、Yb、Cr、Ti、Ho、Er、Tm、Ta のうち 1 種または複数種添加されているものを媒質とするレーザなどが挙げられる。

10

#### 【0061】

また擬似 CW レーザとして、発振周波数が 10 MHz 以上、好ましくは 80 MHz 以上のパルス発振させることができるのであれば、Ar レーザ、Kr レーザ、エキシマレーザ、CO<sub>2</sub> レーザ、YAG レーザ、Y<sub>2</sub>O<sub>3</sub> レーザ、YVO<sub>4</sub> レーザ、フォルステライト (Mg<sub>2</sub>SiO<sub>4</sub>) レーザ、YLF レーザ、YAlO<sub>3</sub> レーザ、GdVO<sub>4</sub> レーザ、アレキサンドライトレーザ、Ti : サファイアレーザ、銅蒸気レーザまたは金蒸気レーザ、多結晶 (セラミック) の YAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub> にドーパントとして Nd、Yb、Cr、Ti、Ho、Er、Tm、Ta のうち 1 種または複数種添加されているものを媒質とするレーザのようなパルス発振レーザを用いることができる。

20

#### 【0062】

このようなパルス発振レーザは、発振周波数を増加させていくと、いずれは連続発振レーザと同等の効果を示すものである。

#### 【0063】

例えば連続発振が可能な固体レーザを用いる場合、第 2 高調波～第 4 高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。代表的には、YAG レーザ（基本波 1064 nm）の第 2 高調波（532 nm）や第 3 高調波（355 nm）を用いるのが望ましい。例えば、連続発振の YAG レーザから射出されたレーザ光を非線形光学素子により高調波に変換して、半導体膜に照射する。エネルギー密度は 0.01 ~ 100 MW/cm<sup>2</sup> 程度（好ましくは 0.1 ~ 10 MW/cm<sup>2</sup>）とすれば良い。そして走査速度を 10 ~ 2000 cm/sec 程度として照射する。

30

#### 【0064】

なお、単結晶の YAG、YVO<sub>4</sub>、フォルステライト (Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶 (セラミック) の YAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub> に、ドーパントとして Nd、Yb、Cr、Ti、Ho、Er、Tm、Ta のうち 1 種または複数種添加されているものを媒質とするレーザ、Ar レーザ、Kr レーザ、または Ti : サファイアレーザは、連続発振をさせることができるものであり、Q スイッチ動作やモード同期などを行うことによってパルス発振をさせることも可能である。10 MHz 以上の発振周波数でレーザビームを発振させると、半導体膜がレーザによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。

40

#### 【0065】

媒質としてセラミック（多結晶）を用いると、短時間かつ低コストで自由な形状に媒質を形成することが可能である。単結晶を用いる場合、通常、直径数 mm、長さ数十 mm の円柱状の媒質が用いられているが、セラミックを用いる場合はさらに大きいものを作ることが可能である。

#### 【0066】

発光に直接寄与する媒質中の Nd、Yb などのドーパントの濃度は、単結晶中でも多結晶中でも大きくは変えられないため、濃度を増加させることによるレーザの出力向上には

50

ある程度限界がある。しかしながら、セラミックの場合、単結晶と比較して媒質の大きさを著しく大きくすることができるため大幅な出力が向上する可能性がある。

#### 【0067】

さらに、セラミックの場合では、平行六面体形状や直方体形状の媒質を容易に形成することが可能である。このような形状の媒質を用いて、発振光を媒質の内部でジグザグに進行させると、発振光路を長くとることができる。そのため、增幅が大きくなり、大出力で発振させることができるとなる。また、このような形状の媒質から射出されるレーザビームは射出時の断面形状が四角形状であるため、丸状のビームと比較すると、線状ビームに整形するのに有利である。このように射出されたレーザビームを、光学系を用いて整形することによって、短辺の長さ 1 mm 以下、長辺の長さ数 mm ~ 数 m の線状ビームを容易に得ることが可能となる。また、励起光を媒質に均一に照射することにより、線状ビームは長辺方向にエネルギー分布の均一なものとなる。10

#### 【0068】

この線状ビームを半導体膜に照射することによって、半導体膜の全面をより均一にアニールすることが可能になる。線状ビームの両端まで均一なアニールが必要な場合は、その両端にスリットを配置し、エネルギーの減衰部を遮光するなどの工夫が必要となる。

#### 【0069】

上述した半導体膜へのレーザ光の照射により、結晶性がより高められた結晶性半導体膜が形成される。

#### 【0070】

次に、結晶性半導体膜を用いて、島状半導体膜 404 ~ 406 が形成される。この島状半導体膜 404 ~ 406 は、TFT の活性層となる。20

#### 【0071】

次に島状半導体膜にしきい値制御のための不純物を導入する。本実施例においてはジボラン (B<sub>2</sub>H<sub>6</sub>) をドープすることによってボロン (B) を島状半導体膜中に導入する。

#### 【0072】

次に島状半導体膜 404 ~ 406 を覆うように絶縁膜を成膜する。絶縁膜には、例えば酸化珪素、窒化珪素または窒素を含んだ酸化珪素等を用いることができる。また成膜方法は、プラズマ CVD 法、スパッタ法などを用いることができる。

#### 【0073】

次に、絶縁膜上に導電膜を成膜した後、導電膜を用いてゲート電極 441 ~ 443 を形成する。30

#### 【0074】

ゲート電極 441 ~ 443 は、導電膜を単層または 2 層以上積層させた構造を用いて形成する。導電膜を 2 層以上積層させている場合は、タンタル (Ta)、タングステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al) から選ばれた元素、または前記元素を主成分とする合金材料、若しくは化合物材料を積層させてゲート電極 441 ~ 443 を形成してもよい。また、リン (P) 等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてゲート電極を形成してもよい。

#### 【0075】

本実施例では、ゲート電極 441 ~ 443 は以下のようにして形成される。まず第 1 の導電膜として、例えば窒化タンタル (TaN) 膜を 10 ~ 50 nm、例えば 30 nm の膜厚で形成する。そして第 1 の導電膜上に第 2 の導電膜として、例えばタングステン (W) 膜を 200 ~ 400 nm、例えば 370 nm の膜厚で形成し、第 1 の導電膜及び第 2 の導電膜の積層膜を形成する。40

#### 【0076】

次に第 2 の導電膜を異方性エッチングでエッチングし、上層ゲート電極 441b ~ 443b を形成する。次いで第 1 の導電膜を等方性エッチングでエッチングし、下層ゲート電極 441a ~ 443a を形成する。以上よりゲート電極 441 ~ 443 を形成する。

#### 【0077】

10

20

30

40

50

ゲート電極 441～443は、ゲート配線の一部として形成してもよいし、別にゲート配線を形成して、そのゲート配線にゲート電極441～443を接続してもよい。

#### 【0078】

そして、ゲート電極441～443や、あるいはレジストをマスクとして用い、島状半導体膜404～406それぞれに一導電性（n型またはp型の導電性）を付与する不純物を添加し、ソース領域、ドレイン領域、さらには低濃度不純物領域等を形成する。

#### 【0079】

まず、フォスフィン（PH<sub>3</sub>）を用いて、リン（P）を、加速電圧を60～120keV、ドーズ量を $1 \times 10^{13} \sim 1 \times 10^{15}$ cm<sup>-2</sup>として島状半導体膜中に導入する。この不純物導入の際にnチャネル型TFT451のチャネル形成領域411、及びnチャネル型TFT453のチャネル形成領域431が形成される。10

#### 【0080】

またpチャネル型TFT452を作製するために、ジボラン（B<sub>2</sub>H<sub>6</sub>）を印加電圧60～100keV、例えば80keV、ドーズ量 $1 \times 10^{13} \sim 5 \times 10^{15}$ cm<sup>-2</sup>、例えば $3 \times 10^{15}$ cm<sup>-2</sup>の条件で、島状半導体膜中にボロン（B）を導入する。これによりpチャネル型TFT452のソース領域またはドレイン領域422、またこの不純物導入の際にチャネル形成領域421が形成される。

#### 【0081】

次に絶縁膜を用いてゲート絶縁膜407～409を形成する。

#### 【0082】

ゲート絶縁膜407～409形成後、nチャネル型TFT451及び453となる島状半導体膜中に、フォスフィン（PH<sub>3</sub>）を用いて、印加電圧40～80keV、例えば50keV、ドーズ量 $1.0 \times 10^{15} \sim 2.5 \times 10^{16}$ cm<sup>-2</sup>、例えば $3.0 \times 10^{15}$ cm<sup>-2</sup>で、リン（P）を導入する。これによりnチャネル型TFT451の低濃度不純物領域412、及びソース領域またはドレイン領域413、並びにnチャネル型TFT453の低濃度不純物領域432及び、ソース領域またはドレイン領域433が形成される。20

#### 【0083】

本実施例においては、nチャネル型TFT451のソース領域またはドレイン領域413、及びnチャネル型TFT453のソース領域またはドレイン領域433のそれぞれには、 $1 \times 10^{19} \sim 5 \times 10^{21}$ cm<sup>-3</sup>の濃度でリン（P）が含まれることとなる。またnチャネル型TFT451の低濃度不純物領域412、及びnチャネル型TFT453の低濃度不純物領域432のそれぞれには、 $1 \times 10^{18} \sim 5 \times 10^{19}$ cm<sup>-3</sup>の濃度でリン（P）が含まれる。さらに、pチャネル型TFT452のソース領域またはドレイン領域422には、 $1 \times 10^{19} \sim 5 \times 10^{21}$ cm<sup>-3</sup>の濃度でボロン（B）が含まれる。30

#### 【0084】

以上により、nチャネル型TFT451、pチャネル型TFT452、nチャネル型TFT453が形成される（図5（A）参照）。なお、本実施例では、TFT451～453をトップゲート構造としたが、ボトムゲート構造（逆スタガ構造）としてもよい。40

#### 【0085】

nチャネル型TFT451は、上層下地膜403c上に島状半導体膜404、ゲート絶縁膜407、下層ゲート電極441a及び上層ゲート電極441bからなるゲート電極441を有している。島状半導体膜404には、チャネル形成領域411、低濃度不純物領域412、及びソース領域またはドレイン領域413が形成される。

#### 【0086】

pチャネル型TFT452は、上層下地膜403c上に島状半導体膜405、ゲート絶縁膜408、下層ゲート電極442a及び上層ゲート電極442bからなるゲート電極442を有している。島状半導体膜405には、チャネル形成領域421、及びソース領域またはドレイン領域422が形成される。50

## 【0087】

nチャネル型TFT453は、上層下地膜403c上に島状半導体膜406、ゲート絶縁膜409、下層ゲート電極443a及び上層ゲート電極443bからなるゲート電極443を有している。島状半導体膜406には、チャネル形成領域431、低濃度不純物領域432、及びソース領域またはドレイン領域433が形成される。

## 【0088】

さらに、この後、TFT451～453を保護するためのパッシベーション膜461を形成しても良い。パッシベーション膜461は、アルカリ金属やアルカリ土類金属のTFT451～453への侵入を防ぐことができる、窒化珪素、窒素を含む酸化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素などを用いるのが望ましい。具体的には、例えば膜厚600nm程度の窒素を含む酸化珪素膜を、パッシベーション膜461として用いることができる。この場合、水素化処理工程は、該窒素を含む酸化珪素膜形成後に行っても良い。上記構成を用いることで、TFT451～453が下地膜403とパッシベーション膜461とで覆われるため、Naなどのアルカリ金属やアルカリ土類金属が、半導体素子に用いられている半導体膜中に拡散し、半導体素子の電気特性に悪影響を及ぼすのをより防ぐことができる。

10

## 【0089】

次にTFT451～453及びパッシベーション膜461を覆うように、第1の層間絶縁膜462を形成する。第1の層間絶縁膜462は、ポリイミド、アクリル、ポリアミド等の、耐熱性を有する有機樹脂を用いることができる。また上記有機樹脂の他に、低誘電率材料(LOW-k材料)、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂(以下、シロキサン系樹脂と呼ぶ)等を用いることができる。

20

## 【0090】

シロキサンとは、シリコン(Si)と酸素(O)との結合で骨格構造で構成され、置換基として、少なくとも水素を含む有機基(例えばアルキル基、アリール基)が用いられるものである。また置換基として、フルオロ基を用いてもよい。さらに置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

## 【0091】

第1の層間絶縁膜462の形成には、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を採用することができる。また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、酸窒化珪素、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜等を用いることができる。なお、これらの絶縁膜を積層させて、第1の層間絶縁膜462を形成しても良い。

30

## 【0092】

さらに本実施例では、第1の層間絶縁膜462上に、第2の層間絶縁膜463を形成する。第2の層間絶縁膜463としては、 DLC(ダイヤモンドライクカーボン)或いは窒化炭素(CN)等の炭素を有する膜、又は、酸化珪素膜、窒化珪素膜或いは窒素を含む酸化珪素膜等を用いることができる。形成方法としては、プラズマCVD法や、大気圧プラズマ法等を用いることができる。あるいは、ポリイミド、アクリル、ポリアミド、レジスト又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シロキサン系樹脂等を用いてもよい。

40

## 【0093】

なお、第1の層間絶縁膜462又は第2の層間絶縁膜463と、後に形成される配線を構成する導電材料等との熱膨張率の差から生じる応力によって、第1の層間絶縁膜462又は第2の層間絶縁膜463の膜剥がれや割れが生じるのを防ぐために、第1の層間絶縁膜462又は第2の層間絶縁膜463中にフィラーを混入させておいても良い。

## 【0094】

次に、第1の層間絶縁膜462及び第2の層間絶縁膜463にコンタクトホールを形成

50

し、TFT451～453に接続する電極又は配線471～475を形成する。本実施例では電極と配線を一体形成するが、電極と配線を別々に形成して電気的に接続させてもよい。コンタクトホール形成時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。本実施例では、電極又は配線471～475を、Ti、TiN、Al-Si、Ti、TiNを積層して5層構造とし、スパッタ法によって成膜したものを用いて形成する。

#### 【0095】

なお、アルミニウム膜(Al膜)において、珪素(Si)を混入させる(本明細書では「Al-Si」と呼ぶこともある)ことにより、配線形成時のレジストベークにおけるヒロックの発生を防止することができる。また、Siの代わりに、0.5%程度の銅(Cu)を混入させても良い。また、チタン(Ti)や窒化チタン(TiN)でAl-Si層をサンドイッチすることにより、耐ヒロック性がさらに向上する。なお、エッチング時には、窒素を含む酸化珪素等からなる上記ハードマスクを用いるのが望ましい。なお、配線の材料や、形成方法はこれらに限定されるものではなく、前述したゲート電極に用いられる材料を採用しても良い。

#### 【0096】

またこの電極又は配線471～475を、ニッケル、コバルト、鉄のうち少なくとも1種の元素、及び炭素を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜は、シリコンと接触してもシリコンとアルミニウムの相互拡散が防止できる。またこのようなアルミニウム合金膜は、透明導電膜、例えばITO(Indium Tin Oxide、インジウム錫酸化物)膜と接触しても酸化還元反応が起こらないため、両者を直接接触させることができる。さらにこのようなアルミ合金膜は、比抵抗が低く耐熱性にも優れているので、配線材料としては有用である。

#### 【0097】

なお、電極又は配線471、電極又は配線472は、nチャネル型TFT451のソース領域またはドレイン領域413に接続されている。電極又は配線472、電極又は配線473は、pチャネル型TFT452のソース領域またはドレイン領域422に接続されている。電極又は配線474、電極又は配線475は、nチャネル型TFT453のソース領域またはドレイン領域433に接続されている。さらに電極又は配線475は、nチャネル型TFT453のゲート電極443にも接続されている。nチャネル型TFT453は、乱数ROMのメモリ素子として用いることができる(図5(B)参照)。

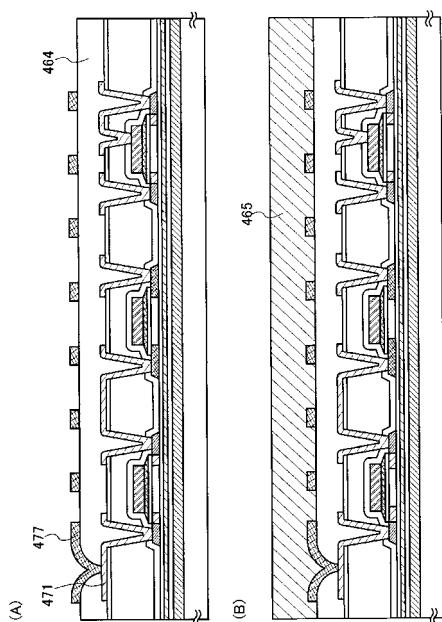

#### 【0098】

次に電極又は配線471～475を覆うように、第2の層間絶縁膜463上に第3の層間絶縁膜464を形成する。第3の層間絶縁膜464は、電極又は配線471が一部露出する様な位置に開口部を有するように形成する。なお第3の層間絶縁膜464は、第1の層間絶縁膜462と同様の材料を用いて形成することが可能である。

#### 【0099】

次に、第3の層間絶縁膜464上にアンテナ477を形成する(図6(A)参照)。アンテナ477は、Ag、Au、Cu、Pd、Cr、Mo、Ti、Ta、W、Al、Fe、Co、Zn、Sn、Niなどの金属、金属化合物を1つまたは複数有する導電材料を用いることができる。そしてアンテナ477は、電極又は配線471と接続されている。なお図6(A)では、アンテナ477が電極又は配線471と直接接続されているが、本発明のIDチップはこの構成に限定されない。例えば別途形成した配線を用いて、アンテナ477と電極又は配線471とを電気的に接続するようにしても良い。

#### 【0100】

アンテナ477は印刷法、フォトリソグラフィ法、蒸着法または液滴吐出法などを用いて形成することができる。本実施例では、アンテナ477が単層の導電膜で形成されているが、複数の導電膜が積層されたアンテナ477を形成することも可能である。例えば、Niなどで形成した配線に、Cuを無電解めっきでコーティングして、アンテナ477を形成しても良い。

10

20

30

40

50

## 【0101】

なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。また印刷法にはスクリーン印刷法、オフセット印刷法などが含まれる。印刷法、液滴吐出法を用いることで、露光用のマスクを用いずに、アンテナ477を形成することが可能になる。また、液滴吐出法、印刷法だと、フォトリソグラフィ法と異なり、エッチングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、IDチップの作製に費やされるコストを抑えることができる。

## 【0102】

液滴吐出法または各種印刷法を用いる場合、例えば、CuをAgでコートした導電粒子なども用いることが可能である。なお液滴吐出法を用いてアンテナ477を形成する場合、該アンテナ477の密着性が高まるような処理を、第3の層間絶縁膜464の表面に施すことが望ましい。10

## 【0103】

密着性を高めることができる方法として、具体的には、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を第3の層間絶縁膜464の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属、金属化合物を第3の層間絶縁膜464の表面に付着させる方法、第3の層間絶縁膜464の表面に大気圧下または減圧下においてプラズマ処理を施し、表面改質を行なう方法などが挙げられる。また、上記導電膜または絶縁膜との密着性が高い金属として、チタン、チタン酸化物の他、3d遷移元素であるSc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Znなどが挙げられる。また金属化合物として、上述した金属の酸化物、窒化物、酸窒化物などが挙げられる。上記有機系の絶縁膜として、例えばポリイミド、シロキサン系樹脂等が挙げられる。20

## 【0104】

第3の層間絶縁膜464に付着させる金属または金属化合物が導電性を有する場合、アンテナの正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば1~10nmとなるように制御する、あるいは該金属または金属化合物を酸化により部分的に、または全体的に絶縁化すれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッチングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させるのではなく、液滴吐出法、印刷法、ゾル-ゲル法などを用いて特定の領域にのみ選択的に付着させてても良い。なお金属または金属化合物は、第3の層間絶縁膜464の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であっても良い。30

## 【0105】

そして図6(B)に示すように、アンテナ477を形成した後、アンテナ477を覆うように、第3の層間絶縁膜464上に保護層465を形成する。保護層465は、後に剥離層402をエッチングにより除去する際に、アンテナ477を保護することができる材料を用いる。例えば、水またはアルコール類に可溶なエポキシ系、アクリレート系、シリコンを含む樹脂を全面に塗布することで保護層465を形成することができる。40

## 【0106】

本実施例では、スピンドルコート法で水溶性樹脂(東亜合成製:VL-WSHL10)を膜厚30μmとなるように塗布し、仮硬化するために2分間の露光を行ったあと、UV光を裏面から2.5分、表面から10分、合計12.5分の露光を行って本硬化させて、保護層465を形成する。なお、複数の有機樹脂を積層する場合、有機樹脂同士では使用している溶媒によって塗布または焼成時に一部溶解する懼れや、密着性が高くなりすぎたりする懼れがある。従って、第3の層間絶縁膜464と保護層465を共に同じ溶媒に可溶な有機樹脂を用いる場合、後の工程において保護層465の除去がスムーズに行なわれるよう、第3の層間絶縁膜464を覆うように、無機絶縁膜(窒化珪素膜、酸素を含む窒50

化珪素膜、窒素を含む酸化珪素膜、窒化アルミニウム膜、または酸素を含む窒化アルミニウム膜、窒素を含む酸化アルミニウム膜)を形成しておくことが好ましい。

#### 【0107】

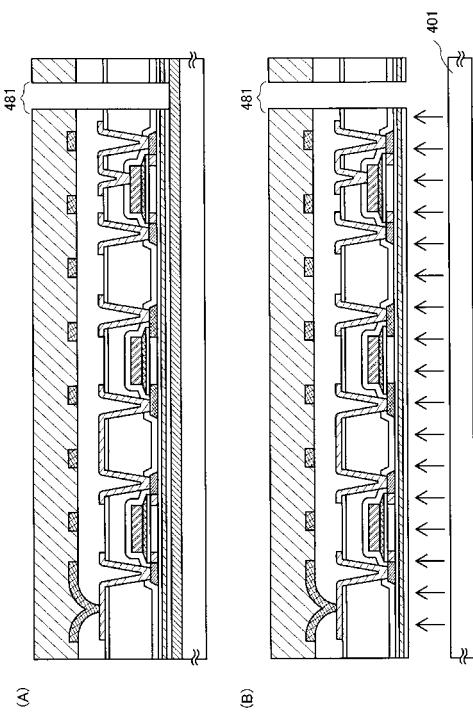

次に図7(A)に示すように、IDチップどうしを分離するために開口部(溝ともいう)481を形成する。開口部481は、剥離層402が露出する程度であれば良い。開口部481の形成は、ダイシング、スクライビングなどを用いることができる。なお、第1の基板401上に形成されているIDチップを分離する必要がない場合、必ずしも開口部481を形成する必要はない。

#### 【0108】

次に図7(B)に示すように、剥離層402をエッティングにより除去する。本実施例では、エッティングガスとしてフッ化ハロゲンを用い、該ガスを開口部481から導入する。本実施例では、例えばC<sub>1</sub>F<sub>3</sub>(三フッ化塩素)を用い、温度:350℃、流量:300sccm、気圧:798パスカル(798Pa)、時間:3hの条件で行なう。また、C<sub>1</sub>F<sub>3</sub>ガスに窒素を混ぜたガスを用いても良い。C<sub>1</sub>F<sub>3</sub>等のフッ化ハロゲンを用いることで、剥離層402が選択的にエッティングされ、第1の基板401をTFT451~453から剥離することができる。なおフッ化ハロゲンは、気体であっても液体であってもどちらでも良い。

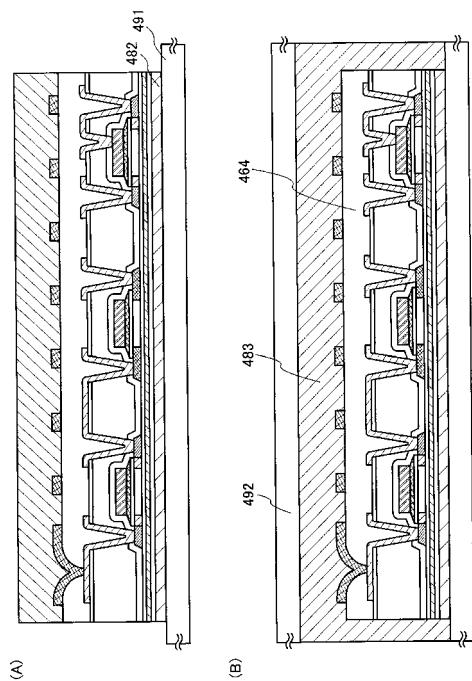

#### 【0109】

次に図8(A)に示すように、剥離されたTFT451~453及びアンテナ477を、接着剤482を用いて第2の基板491に貼り合わせる。接着剤482は、第2の基板491と下地膜403とを貼り合わせることができる材料を用いる。接着剤482は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0110】

第2の基板491として、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。または第2の基板491として、フレキシブル無機材料を用いていても良い。プラスチック基板は、極性基のついたポリノルボルネンからなるARTON(JSR製)を用いることができる。また、ポリエチレンテレフタレート(PET)に代表されるポリエステル、ポリエーテルスルホン(PES)、ポリエチレンナフタレート(PEN)、ポリカーボネット(PC)、ナイロン、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。第2の基板491は集積回路において発生した熱を拡散させるために、2~30W/mK程度の高い熱伝導率を有する方が望ましい。

#### 【0111】

次に図8(B)に示すように、保護層465を除去した後、アンテナ477を覆うように接着剤483を第3の層間絶縁膜464上に塗布し、カバー材492を貼り合わせる。カバー材492は第2の基板491と同様に、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。接着剤483の厚さは、例えば10~200μmとすれば良い。

#### 【0112】

また接着剤483は、カバー材492と第3の層間絶縁膜464及びアンテナ477とを貼り合わせることができる材料を用いる。接着剤483は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0113】

上述した各工程を経て、IDチップが完成する。上記作製方法によって、トータルの膜厚0.3μm以上3μm以下、代表的には2μm程度の飛躍的に薄い集積回路を第2の基板491とカバー材492との間に形成することができる。なお集積回路の厚さは、半導

10

20

30

40

50

体素子自体の厚さのみならず、接着剤482と接着剤483間に形成された各種絶縁膜及び層間絶縁膜の厚さを含めるものとする。またIDチップが有する集積回路の占める面積を、5mm四方(25mm<sup>2</sup>)以下、より望ましくは0.3mm四方(0.09mm<sup>2</sup>)～4mm四方(16mm<sup>2</sup>)程度とすることができる。

#### 【0114】

なお集積回路を、第2の基板491とカバー材492の間のより中央に位置させることで、IDチップの機械的強度を高めることができる。具体的には、第2の基板491とカバー材492の間の距離をdとすると、第2の基板491と、集積回路の厚さ方向における中心との距離xが、以下の数1を満たすように、接着剤482、接着剤483の厚さを制御することが望ましい。

10

#### 【0115】

##### 【数1】

$$\frac{1}{2}d - 30\mu m < x < \frac{1}{2}d + 30\mu m$$

#### 【0116】

また好ましくは、以下の数2を満たすように、接着剤482、接着剤483の厚さを制御する。

#### 【0117】

##### 【数2】

20

$$\frac{1}{2}d - 10\mu m < x < \frac{1}{2}d + 10\mu m$$

#### 【0118】

なお図8(B)では、カバー材492を用いる例を示しているが、本発明はこの構成に限定されない。例えば図8(A)に示した工程までで終了としても良い。

#### 【0119】

なお本実施例では、耐熱性の高い第1の基板401と集積回路の間に剥離層を設け、エッティングにより該剥離層を除去することで基板と集積回路とを剥離する方法について示したが、本発明のIDチップの作製方法は、この構成に限定されない。例えば、耐熱性の高い基板と集積回路の間に金属酸化膜を設け、該金属酸化膜を結晶化により脆弱化して集積回路を剥離しても良い。或いは、耐熱性の高い基板と集積回路の間に、水素を含む非晶質半導体膜を用いた剥離層を設け、レーザ光の照射により該剥離層を除去することで基板と集積回路とを剥離しても良い。或いは、集積回路が形成された耐熱性の高い基板を機械的に削除または溶液やガスによるエッティングで除去することで集積回路を基板から切り離しても良い。

30

#### 【0120】

またIDチップの可撓性を確保するために、下地膜403に接する接着剤482に有機樹脂を用いる場合、下地膜403として窒化珪素膜または窒素を含む酸化珪素膜を用いることで、有機樹脂からNaなどのアルカリ金属やアルカリ土類金属が半導体膜中に拡散するのを防ぐことができる。

40

#### 【0121】

また対象物の表面が曲面を有しており、それにより該曲面貼り合わされたIDチップの第2の基板491が、錐面、柱面など母線の移動によって描かれる曲面を有するように曲がってしまう場合、該母線の方向とTFT451～453のキャリアが移動する方向とを揃えておくことが望ましい。上記構成により、第2の基板491が曲がっても、それによってTFT451～453の電気特性に影響が出るのを抑えることができる。また、島状の半導体膜が集積回路内において占める面積の割合を、1～30%とすることで、第2の基板491が曲がっても、それによってTFT451～453の電気特性に影響が出るのをより抑えることができる。

50

**【0122】**

なお本実施例では、アンテナを集積回路と同じ基板上に形成している例について説明したが、本発明はこの構成に限定されない。別の基板上に形成したアンテナと集積回路とを、後に貼り合わせることで、電気的に接続するようにしても良い。

**【0123】**

なお一般的にIDチップで用いられている電波の周波数は、13.56MHz、2.45GHzが多く、該周波数の電波を検波できるようにIDチップを形成することが、汎用性を高める上で非常に重要である。

**【0124】**

また本実施例のIDチップでは、半導体基板を用いて形成されたIDチップよりも電波が遮蔽されにくく、電波の遮蔽により信号が減衰するのを防ぐことができるというメリットを有している。よって、半導体基板を用いずに済むので、IDチップのコストを大幅に低くすることができる。例えば、直径12インチのシリコン基板を用いた場合と、 $730 \times 920 \text{ mm}^2$ のガラス基板を用いた場合とを比較する。前者のシリコン基板の面積は約 $730000 \text{ mm}^2$ であるが、後者のガラス基板の面積は約 $672000 \text{ mm}^2$ であり、ガラス基板はシリコン基板の約9.2倍に相当する。後者のガラス基板の面積は約 $672000 \text{ mm}^2$ では、基板の分断により消費される面積を無視すると、1mm四方のIDチップが約672000個形成できる計算になり、該個数はシリコン基板の約9.2倍の数に相当する。そしてIDチップの量産化を行なうための設備投資は、 $730 \times 920 \text{ mm}^2$ のガラス基板を用いた場合の方が直径12インチのシリコン基板を用いた場合よりも工程数が少なくて済むため、額を3分の1で済ませることができる。さらに本発明では、集積回路を剥離した後、ガラス基板を再び利用できる。よって、破損したガラス基板を補填する、あるいはガラス基板の表面を清浄化する費用を踏まえても、シリコン基板を用いる場合より大幅にコストを抑えることができる。またガラス基板を再利用せずに廃棄していくとしても、 $730 \times 920 \text{ mm}^2$ のガラス基板の値段は、直径12インチのシリコン基板の半分程度で済むので、IDチップのコストを大幅に低くすることができることがわかる。

10

20

**【0125】**

従って、 $730 \times 920 \text{ mm}^2$ のガラス基板を用いた場合、直径12インチのシリコン基板を用いた場合よりも、IDチップの値段を約30分の1程度に抑えることができることがわかる。IDチップは、使い捨てを前提とした用途も考えられるので、コストを大幅に低くすることができる本発明のIDチップは上記用途に非常に有用である。

30

**【0126】**

なお本実施例では、集積回路を剥離して、可撓性を有する基板に貼り合わせる例について説明したが、本発明はこの構成に限定されない。例えばガラス基板のように、集積回路の作製工程における熱処理に耐えうるような、耐熱温度を有している基板を用いる場合、必ずしも集積回路を剥離する必要はない。

**【0127】**

また、本実施例は、必要であれば実施の形態及び他の実施例と自由に組み合わせることが可能である。

40

**【実施例3】****【0128】**

本実施例では、本発明の生体情報検出センサに組み込まれるIDチップ（ICチップ、ICタグともいう）において、実施例2とは異なる構成のものを作製した例を、図9（A）～図9（B）、図10（A）～図10（B）、図11（A）～図11（B）及び図12（A）～図12（B）を用いて示す。

**【0129】**

本実施例では、半導体素子として絶縁分離されたTFTを例示するが、集積回路に用いられる半導体素子はこれに限定されず、あらゆる回路素子を用いることができる。例えば、TFTの他に、記憶素子、ダイオード、光電変換素子、抵抗素子、コイル、容量素子、

50

インダクタなどが代表的に挙げられる。

**【0130】**

まず、スパッタ法を用いて耐熱性を有する基板（第1の基板）601上に剥離層602を形成する。第1の基板601として、例えばバリウムホウケイ酸ガラスや、アルミニウムホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレス基板を含む金属基板または半導体基板の表面に絶縁膜を形成したもの用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

**【0131】**

剥離層602は、非晶質シリコン、多結晶シリコン、単結晶シリコン、微結晶シリコン（セミアモルファスシリコンを含む）等、シリコンを主成分とする層を用いることができる。剥離層602は、スパッタ法、減圧CVD法、プラズマCVD法等を用いて形成することができる。本実施例では、膜厚50nm程度の非晶質シリコンを減圧CVD法で形成し、剥離層602として用いる。なお剥離層602はシリコンに限定されず、エッチングにより選択的に除去できる材料で形成すれば良い。剥離層602の膜厚は、50～60nmとするのが望ましい。セミアモルファスシリコンに関しては、30～50nmとしてもよい。

**【0132】**

なおセミアモルファスシリコンに代表されるセミアモルファス半導体とは、非晶質半導体と結晶構造を有する半導体（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。このセミアモルファス半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5～20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。

**【0133】**

また、未結合手（ダングリングボンド）のを終端化させる材料として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体（SAS）と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。

**【0134】**

セミアモルファスシリコンは、そのラマンスペクトルが $520\text{ cm}^{-1}$ よりも低波数側にシフトしており、またX線回折ではSi結晶格子に由来するとされる（111）、（220）の回折ピークが観測される。

**【0135】**

またセミアモルファスシリコンは珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、 $\text{SiH}_4$ であり、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素を含む気体を希釈して用いることで、セミアモルファスシリコンの形成を容易なものとすることができます。希釈率は2倍～1000倍の範囲で珪素を含む気体を希釈することが好ましい。

**【0136】**

次に、剥離層602上に、下地膜603を形成する。下地膜603は第1の基板601中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、TFTなどの半導体素子の電気特性に悪影響を及ぼすのを防ぐために設ける。また下地膜603は、後の半導体素子を剥離する工程において、半導体素子を保護する役目も有している。下地膜603は单層であっても複数の絶縁膜を積層したものであっても良い。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる酸化珪素や、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素などの絶縁膜を用いて形成する。

10

20

30

40

50

## 【0137】

本実施例では、下層下地膜603aとして膜厚100nmの窒素を含む酸化珪素膜、中層下地膜603bとして膜厚50nmの酸素を含む窒化珪素膜、上層下地膜603cとして膜厚100nmの窒素を含む酸化珪素膜を順に積層して下地膜603を形成するが、各膜の材質、膜厚、積層数は、これに限定されるものではない。例えば、下層下地膜603aの窒素を含む酸化珪素膜に代えて、膜厚0.5~3μmのシロキサン系樹脂をスピンドル法、スリットコーティング法、液滴吐出法などによって形成しても良い。また、中層下地膜603bの酸素を含む窒化珪素膜に代えて、窒化珪素膜(Si<sub>3</sub>N<sub>4</sub>等)を用いてもよい。また、上層下地膜603cの窒素を含む酸化珪素膜に代えて、酸化珪素膜を用いてても良い。また、それぞれの膜厚は、0.05~3μmとするのが望ましく、その範囲から自由に選択することができる。

## 【0138】

或いは、剥離層602に最も近い、下地膜603の下層下地膜603aを窒素を含む酸化珪素膜または酸化珪素膜で形成し、中層下地膜603bをシロキサン系樹脂で形成し、上層下地膜603cを酸化珪素膜で形成しても良い。

## 【0139】

ここで、酸化珪素膜は、SiH<sub>4</sub>とO<sub>2</sub>、又はTEOS(テトラエトキシシラン)とO<sub>2</sub>等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR-CVD等の方法によって形成することができる。また、窒化珪素膜は、代表的には、SiH<sub>4</sub>とNH<sub>3</sub>の混合ガスを用い、プラズマCVDによって形成することができる。また、窒素を含む酸化珪素膜(組成比O>N)、酸素を含む窒化珪素(組成比N>O)は、代表的には、SiH<sub>4</sub>とN<sub>2</sub>Oの混合ガスを用い、プラズマCVDによって形成することができる。

## 【0140】

次に、下地膜603上に半導体膜を形成する。半導体膜は、下地膜603を形成した後、大気に曝さずに形成することが望ましい。半導体膜の膜厚は20~200nm(望ましくは40~170nm、好ましくは50~150nm)とする。なお半導体膜は、非晶質半導体であっても良いし、セミアモルファス半導体であっても良いし、多結晶半導体であっても良い。また半導体は珪素だけではなくシリコンゲルマニウムも用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01~4.5atom%程度であることが好ましい。

## 【0141】

非晶質半導体は、珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>が挙げられる。この珪素を含む気体を、水素、あるいは水素とヘリウムで希釈して用いても良い。

## 【0142】

なお上述したようにセミアモルファス半導体は、珪素を含む気体をグロー放電分解することにより得ることができが、珪素を含む気体中に、CH<sub>4</sub>、C<sub>2</sub>H<sub>6</sub>などの炭化物気体、GeH<sub>4</sub>、GeF<sub>4</sub>などのゲルマニウム化気体、F<sub>2</sub>などを混入させて、エネルギーバンド幅を1.5~2.4eV、若しくは0.9~1.1eVに調節しても良い。

## 【0143】

例えば、SiH<sub>4</sub>にH<sub>2</sub>を添加したガスを用いる場合、或いはSiH<sub>4</sub>にF<sub>2</sub>を添加したガスを用いる場合、形成したセミアモルファス半導体を用いてTFTを作製すると、該TFTのサブスレッショルド係数(S値)を0.35V/dec以下、代表的には0.25~0.09V/decとし、移動度を10cm<sup>2</sup>/Vsecとすることができる。そして上記セミアモルファス半導体を用いたTFTで、例えば19段リングオシレータを形成した場合、電源電圧3~5Vにおいて、その発振周波数は1MHz以上、好ましくは100MHz以上の特性を得ることができる。また電源電圧3~5Vにおいて、インバータ1段あたりの遅延時間は26ns、好ましくは0.26ns以下とすることができます。

## 【0144】

次に半導体膜にレーザ照射装置から線状ビームを照射し、結晶化を行なう。

10

20

30

40

50

## 【0145】

レーザ結晶化を行なう場合、レーザ結晶化の前に、レーザに対する半導体膜の耐性を高めるために、500、1時間の加熱処理を半導体膜に加えてよい。

## 【0146】

レーザ結晶化は、連続発振のレーザ(CWレーザ)、または擬似CWレーザとして、発振周波数が10MHz以上、好ましくは80MHz以上のパルス発振レーザを用いることができる。

## 【0147】

具体的には、連続発振のレーザとして、Arレーザ、Krレーザ、CO<sub>2</sub>レーザ、YAGレーザ、YVO<sub>4</sub>レーザ、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、ヘリウムカドミウムレーザ、多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>にドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザなどが挙げられる。

10

## 【0148】

また擬似CWレーザとして、発振周波数が10MHz以上、好ましくは80MHz以上のパルス発振させることができるのであれば、Arレーザ、Krレーザ、エキシマレーザ、CO<sub>2</sub>レーザ、YAGレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、YVO<sub>4</sub>レーザ、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、銅蒸気レーザまたは金蒸気レーザ、多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>にドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザのようなパルス発振レーザを用いることができる。

20

## 【0149】

このようなパルス発振レーザは、発振周波数を増加させていくと、いずれは連続発振レーザと同等の効果を示すものである。

## 【0150】

例えば連続発振が可能な固体レーザを用いる場合、第2高調波～第4高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。代表的には、YAGレーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いるのが望ましい。例えば、連続発振のYAGレーザから射出されたレーザ光を非線形光学素子により高調波に変換して、半導体膜に照射する。エネルギー密度は0.01～100MW/cm<sup>2</sup>程度(好ましくは0.1～10MW/cm<sup>2</sup>)とすれば良い。そして走査速度を10～2000cm/sec程度として照射する。

30

## 【0151】

なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arレーザ、Krレーザ、またはTi:サファイアレーザは、連続発振をさせることができるものであり、Qスイッチ動作やモード同期などを行うことによってパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザビームを発振させると、半導体膜がレーザによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。

40

## 【0152】

媒質としてセラミック(多結晶)を用いると、短時間かつ低コストで自由な形状に媒質を形成することが可能である。単結晶を用いる場合、通常、直径数mm、長さ数十mmの

50

円柱状の媒質が用いられているが、セラミックを用いる場合はさらに大きいものを作ることが可能である。

#### 【0153】

発光に直接寄与する媒質中のNd、Ybなどのドーパントの濃度は、単結晶中でも多結晶中でも大きくは変えられないため、濃度を増加させることによるレーザの出力向上にはある程度限界がある。しかしながら、セラミックの場合、単結晶と比較して媒質の大きさを著しく大きくすることができるため大幅な出力が向上する可能性がある。

#### 【0154】

さらに、セラミックの場合では、平行六面体形状や直方体形状の媒質を容易に形成することが可能である。このような形状の媒質を用いて、発振光を媒質の内部でジグザグに進行させると、発振光路を長くとることができる。そのため、增幅が大きくなり、大出力で発振させることができるとなる。また、このような形状の媒質から射出されるレーザビームは射出時の断面形状が四角形状であるため、丸状のビームと比較すると、線状ビームに整形するのに有利である。このように射出されたレーザビームを、光学系を用いて整形することによって、短辺の長さ1mm以下、長辺の長さ数mm～数mの線状ビームを容易に得ることが可能となる。また、励起光を媒質に均一に照射することにより、線状ビームは長辺方向にエネルギー分布の均一なものとなる。

#### 【0155】

この線状ビームを半導体膜に照射することによって、半導体膜の全面をより均一にアニールすることが可能になる。線状ビームの両端まで均一なアニールが必要な場合は、その両端にスリットを配置し、エネルギーの減衰部を遮光するなどの工夫が必要となる。

#### 【0156】

上述した半導体膜へのレーザ光の照射により、結晶性がより高められた結晶性半導体膜が形成される。

#### 【0157】

次に、得られた結晶性半導体膜を用いて島状半導体膜621～623を形成する。この島状半導体膜は、以降の工程で形成されるTFTの活性層となる。

#### 【0158】

次に島状半導体膜621～623にしきい値制御のための不純物を導入する。本実施例においてはジボラン(B<sub>2</sub>H<sub>6</sub>)をドープすることによってボロン(B)を島状半導体膜621～623中に導入する。

#### 【0159】

次に島状半導体膜621～623を覆うように絶縁膜を成膜する。絶縁膜には、例えば酸化珪素、窒化珪素または窒素を含んだ酸化珪素等を用いることができる。また成膜方法は、プラズマCVD法、スパッタ法などを用いることができる。

#### 【0160】

次に、絶縁膜を用いて、島状半導体膜621～623上にそれぞれ、ゲート絶縁膜661～663を形成する。

#### 【0161】

島状半導体膜621～623、並びにゲート絶縁膜661～663を覆って、第1の導電膜及び第2の導電膜を形成する。

#### 【0162】

第1の導電膜及び第2の導電膜は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)から選ばれた元素、または前記元素を主成分とする合金材料、若しくは化合物材料を積層させる。

#### 【0163】

本実施例では、第1の導電膜として、例えば窒化タンタル(TaN)膜を10～50nm、例えば30nmの膜厚で形成する。そして第1の導電膜上に第2の導電膜として、例えばタンゲステン(W)膜を200～400nm、例えば370nmの膜厚で形成し、第1の導電膜及び第2の導電膜の積層膜を形成する。

10

20

30

40

50

## 【0164】

次に第2の導電膜を異方性エッティングでエッティングし、上層ゲート電極671b～673bを形成する。次いで第1の導電膜を等方性エッティングでエッティングし、下層ゲート電極671a～673aを形成する。以上よりゲート電極671～673を形成する。

## 【0165】

ゲート電極671～673は、ゲート配線の一部として形成してもよいし、別にゲート配線を形成して、そのゲート配線にゲート電極671～673を接続してもよい。

## 【0166】

次いで、pチャネル型TFT612の活性層となる島状半導体膜622、ゲート絶縁膜662及びゲート電極672を覆ってレジストを形成する。

10

## 【0167】

そして、ゲート電極671及びゲート絶縁膜661をマスクとして用い、島状半導体膜621にn型を付与する不純物を添加し、チャネル形成領域631、低濃度不純物領域632、ソース領域またはドレイン領域633を形成する。また同時に、ゲート電極673及びゲート絶縁膜663をマスクとして用い、島状半導体膜623にn型を付与する不純物を添加し、チャネル形成領域651、低濃度不純物領域652、ソース領域またはドレイン領域653を形成する。

## 【0168】

まず、n型を付与する元素としてリンを用い、フォスフィン( $\text{PH}_3$ )を用いて、リン(P)を、加速電圧を40～100keV、例えば60keV、ドーズ量を $1 \times 10^{13}$ ～ $1 \times 10^{15} \text{ cm}^{-2}$ 、例えば $2.6 \times 10^{13} \text{ cm}^{-2}$ として島状半導体膜621及び623中に導入する。この不純物導入の際にnチャネル型TFT611のチャネル形成領域631及びnチャネル型TFT613のチャネル形成領域651が形成される。

20

## 【0169】

次いで島状半導体膜621及び623中に、フォスフィン( $\text{PH}_3$ )を用いて、印加電圧10～60keV、例えば20keV、ドーズ量 $5.0 \times 10^{14}$ ～ $2.5 \times 10^{16} \text{ cm}^{-2}$ 、例えば $3.0 \times 10^{15} \text{ cm}^{-2}$ で、リン(P)を導入する。これによりnチャネル型TFT611の低濃度不純物領域632、ソース領域またはドレイン領域633が形成される。またnチャネル型TFT613の低濃度不純物領域652、ソース領域またはドレイン領域653が形成される。

30

## 【0170】

本実施例においては、nチャネル型TFT611のソース領域またはドレイン領域633、並びにnチャネル型TFT613のソース領域またはドレイン領域653には、それぞれ $1 \times 10^{19}$ ～ $5 \times 10^{21} \text{ cm}^{-3}$ の濃度でリン(P)が含まれることとなる。またnチャネル型TFT611の低濃度不純物領域632、並びにnチャネル型TFT613の低濃度不純物領域652には、それぞれ $1 \times 10^{18}$ ～ $5 \times 10^{19} \text{ cm}^{-3}$ の濃度でリン(P)が含まれる。

## 【0171】

次いで島状半導体膜622、ゲート絶縁膜662及びゲート電極672上のレジストを除去し、島状半導体膜621、ゲート絶縁膜661及びゲート電極671、並びに、島状半導体膜623、ゲート絶縁膜663及びゲート電極673を覆って、それぞれレジストを形成する。

40

## 【0172】

pチャネル型TFT612を作製するために、ジボラン( $\text{B}_2\text{H}_6$ )を印加電圧60～100keV、例えば80keV、ドーズ量 $1 \times 10^{13}$ ～ $5 \times 10^{15} \text{ cm}^{-2}$ 、例えば $3 \times 10^{15} \text{ cm}^{-2}$ の条件で、島状半導体膜622中にホウ素(B)を導入する。これによりpチャネル型TFTのソース領域またはドレイン領域642、またこの不純物導入の際にチャネル形成領域641が形成される。

## 【0173】

なおpチャネル型TFT612について、ホウ素の導入に際しては、印加電圧が高いた

50

めに、下層ゲート電極 672a 及びゲート絶縁膜 662 を通しても、ソース領域またはドレイン領域 642 を形成するために十分なホウ素が島状半導体膜 622 中に添加される。

#### 【0174】

p チャネル型 TFT 612 のソース領域またはドレイン領域 642 には、 $1 \times 10^{-19}$  ~  $5 \times 10^{-21} \text{ cm}^{-3}$  の濃度でボロン (B) が含まれる。

#### 【0175】

次いで、レジストを除去後、島状半導体膜 621 ~ 623、ゲート絶縁膜 661 ~ 663、ゲート電極 671 ~ 673 を覆うように、サイドウォールを形成するための絶縁膜を形成する。

#### 【0176】

この絶縁膜は、プラズマ CVD 法や減圧 CVD (LPCVD) 法により、酸化珪素膜や窒素を含む酸化珪素膜を用いて形成することができる。本実施例では、プラズマ CVD 法により酸化珪素膜を膜厚 50 ~ 200 nm、好ましくは 100 nm で成膜する。

#### 【0177】

次いで絶縁膜をエッチングすることにより、ゲート絶縁膜 661 及びゲート電極 671 の側面にサイドウォール 665 を形成し、ゲート絶縁膜 662 及びゲート電極 672 の側面にサイドウォール 666 を形成し、ゲート絶縁膜 663 及びゲート電極 673 の側面にサイドウォール 667 を形成する。サイドウォール 665 ~ 667 は、テーパー状や矩形状になるように形成し、本実施例では、テーパー状のサイドウォール 665 ~ 667 を形成する。

#### 【0178】

次に島状半導体膜 621 ~ 623、ゲート絶縁膜 661 ~ 663、ゲート電極 671 ~ 673、並びにサイドウォール 665 ~ 667 を覆って、金属膜を形成する。

#### 【0179】

金属膜として、チタン (Ti)、ニッケル (Ni)、コバルト (Co)、タングステン (W)、白金 (Pt) 等を用いることができる。本実施例では、金属膜として、ニッケル膜を 10 nm の厚さで成膜する。

#### 【0180】

次いで、金属膜を形成した島状半導体膜 621 ~ 623 を、ファーネスアニール炉を用いる熱アニール法、レーザーアニール法、またはラピッドサーマルアニール法 (RTA 法) を適用して加熱する。これにより島状半導体膜 621 中にシリサイド領域 635、島状半導体膜 622 中にシリサイド領域 645、島状半導体膜 623 中にシリサイド領域 655 が形成される。本実施例では、ラピッドサーマルアニール法により 350 以上の温度で加熱することによりシリサイド領域 635、645 及び 655 を形成する。

#### 【0181】

シリサイド領域 635、645 及び 655 を形成したら、未反応の金属膜を、硫酸や硝酸等の薬液によりエッチングして除去する。

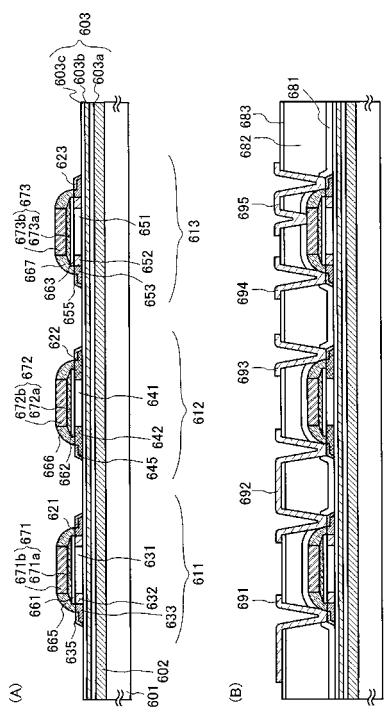

#### 【0182】

以上により、n チャネル型 TFT 611、p チャネル型 TFT 612、n チャネル型 TFT 613 が形成される (図 9 (A) 参照)。なお、本実施例では、TFT 611 ~ 613 をトップゲート構造としたが、ボトムゲート構造 (逆スタガ構造) としてもよい。

#### 【0183】

n チャネル型 TFT 611 は、上層下地膜 603c 上に島状半導体膜 621、ゲート絶縁膜 661、下層ゲート電極 671a 及び上層ゲート電極 671b からなるゲート電極 671 を有している。島状半導体膜 621 には、チャネル形成領域 631、低濃度不純物領域 632、ソース領域またはドレイン領域 633、シリサイド領域 635 が形成される。シリサイド領域 635 は、ソース領域またはドレイン領域 633 の一部の中に形成される。またサイドウォール 665 が、ゲート絶縁膜 661 及びゲート電極 671 の側面に形成されている。

#### 【0184】

10

20

30

40

50

p チャネル型 TFT 612 は、上層下地膜 603c 上に島状半導体膜 622、ゲート絶縁膜 662、下層ゲート電極 672a 及び上層ゲート電極 672b からなるゲート電極 672 を有している。島状半導体膜 622 には、チャネル形成領域 641、ソース領域またはドレイン領域 642、シリサイド領域 645 が形成される。シリサイド領域 645 は、ソース領域またはドレイン領域 642 の一部の中に形成される。またサイドウォール 666 が、ゲート絶縁膜 662 及びゲート電極 672 の側面に形成されている。

#### 【0185】

n チャネル型 TFT 613 は、上層下地膜 603c 上に島状半導体膜 623、ゲート絶縁膜 663、下層ゲート電極 673a 及び上層ゲート電極 673b からなるゲート電極 673 を有している。島状半導体膜 623 には、チャネル形成領域 651、低濃度不純物領域 652、ソース領域またはドレイン領域 653、シリサイド領域 655 が形成される。シリサイド領域 655 は、ソース領域またはドレイン領域 653 の一部の中に形成される。またサイドウォール 667 が、ゲート絶縁膜 663 及びゲート電極 673 の側面に形成されている。

#### 【0186】

さらに、この後、TFT 611 ~ TFT 613 を保護するためのパッシベーション膜 681 を形成しても良い。パッシベーション膜 681 は、アルカリ金属やアルカリ土類金属の TFT 611 ~ TFT 613 への侵入を防ぐことができる、窒化珪素、窒素を含む酸化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素などを用いるのが望ましい。具体的には、例えば膜厚 600 nm 程度の窒素を含む酸化珪素膜を、パッシベーション膜として用いることができる。この場合、水素化処理工程は、該窒素を含む酸化珪素膜形成後に行っても良い。上記構成を用いることで、TFT 611 ~ TFT 613 が下地膜 603 とパッシベーション膜 681 とで覆われるため、Na などのアルカリ金属やアルカリ土類金属が、半導体素子に用いられている半導体膜中に拡散し、半導体素子の電気特性に悪影響を及ぼすのをより防ぐことができる。

#### 【0187】

次に TFT 611 ~ TFT 613 及びパッシベーション膜 681 を覆うように、第 1 の層間絶縁膜 682 を形成する。第 1 の層間絶縁膜 682 は、ポリイミド、アクリル、ポリアミド等の、耐熱性を有する有機樹脂を用いることができる。また上記有機樹脂の他に、低誘電率材料 (low-k 材料)、シロキサン系材料を出発材料として形成された Si-O-Si 結合を含む樹脂（以下、シロキサン系樹脂と呼ぶ）等を用いることができる。

#### 【0188】

シロキサンとは、シリコン (Si) と酸素 (O) との結合で骨格構造で構成され、置換基として、少なくとも水素を含む有機基（例えばアルキル基、アリール基）が用いられるものである。また置換基として、フルオロ基を用いてもよい。さらに置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

#### 【0189】

第 1 の層間絶縁膜 682 の形成には、その材料に応じて、スピンコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を採用することができる。また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、酸窒化珪素、PSG（リンガラス）、BPSG（リンボロンガラス）、アルミナ膜等を用いることができる。なお、これらの絶縁膜を積層させて、第 1 の層間絶縁膜 682 を形成しても良い。

#### 【0190】

さらに本実施例では、第 1 の層間絶縁膜 682 上に、第 2 の層間絶縁膜 683 を形成する。第 2 の層間絶縁膜 683 としては、DLC（ダイヤモンドライクカーボン）或いは窒化炭素（CN）等の炭素を有する膜、又は、酸化珪素膜、窒化珪素膜或いは窒素を含む酸化珪素膜等を用いることができる。形成方法としては、プラズマ CVD 法や、大気圧プラズマ等を用いることができる。あるいは、ポリイミド、アクリル、ポリアミド、レジスト

10

20

30

40

50

又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シリコサン系樹脂等を用いてもよい。

#### 【0191】

なお、第1の層間絶縁膜682又は第2の層間絶縁膜683と、後に形成される配線を構成する導電材料等との熱膨張率の差から生じる応力によって、第1の層間絶縁膜682又は第2の層間絶縁膜683の膜剥がれや割れが生じるのを防ぐために、第1の層間絶縁膜682又は第2の層間絶縁膜683中にフィラーを混入させておいても良い。

#### 【0192】

次に、第1の層間絶縁膜682及び第2の層間絶縁膜683にコンタクトホールを形成する。次いでコンタクトホールを介して、TFT611～TFT613に接続する電極又は配線691～695を形成する。本実施例では電極と配線を一体形成するが、電極と配線を別々に形成して電気的に接続させてもよい。コンタクトホール形成時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。本実施例では、チタン(Ti)膜、窒化チタン(TiN)膜、珪素を含むアルミニウム(Al-Si)膜、チタン(Ti)膜、窒化チタン(TiN)膜を積層して5層構造とし、スパッタ法によって形成したものを用いて、電極又は配線691～695を形成する。

#### 【0193】

なお、アルミニウム(Al)膜において、珪素(Si)を混入させる(本明細書では「Al-Si」と呼ぶこともある)ことにより、配線形成時のレジストベークにおけるヒロックの発生を防止することができる。また、Siの代わりに、0.5%程度のCuを混入させても良い。また、チタン(Ti)や窒化チタン(TiN)でAl-Si層をサンドイッチすることにより、耐ヒロック性がさらに向上する。なお、エッチング時には、窒素を含む酸化珪素等からなる上記ハードマスクを用いるのが望ましい。なお、配線の材料や、形成方法はこれらに限定されるものではなく、前述したゲート電極に用いられる材料を採用しても良い。

#### 【0194】

またこの電極又は配線691～695を、ニッケル、コバルト、鉄のうち少なくとも1種の元素、及び炭素を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜は、シリコンと接触してもシリコンとアルミニウムの相互拡散が防止できる。またこのようなアルミニウム合金膜は、透明導電膜、例えばITO(Inium Tin Oxide、インジウム錫酸化物)膜と接触しても酸化還元反応が起こらないため、両者を直接接触させることができる。さらにこのようなアルミ合金膜は、比抵抗が低く耐熱性にも優れているので、配線材料としては有用である。

#### 【0195】

なお、電極又は配線691、並びに電極又は配線692はnチャネル型TFT611のソース領域またはドレイン領域633中のシリサイド領域に、電気的に接続されている。電極又は配線692、並びに電極又は配線693はpチャネル型TFT612のソース領域またはドレイン領域642中のシリサイド領域に電気的に接続されている。電極又は配線694、並びに電極又は配線695はnチャネル型TFT613のソース領域またはドレイン領域653中のシリサイド領域に、電気的に接続されている。さらに電極又は配線695は、nチャネル型TFT613のゲート電極673にも接続されている。nチャネル型TFT613は、乱数ROMのメモリ素子として用いることができる(図9(B)参照)。

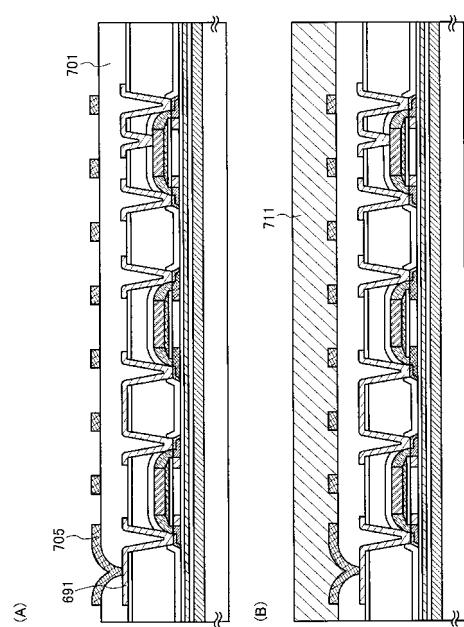

#### 【0196】

次に電極又は配線691～695を覆うように、第2の層間絶縁膜683上に第3の層間絶縁膜701を形成する。第3の層間絶縁膜701は、電極又は配線691が一部露出する様な位置に開口部を有するように形成する。なお第3の層間絶縁膜701は、第1の層間絶縁膜682と同様の材料を用いて形成することが可能である。

#### 【0197】

10

20

30

40

50

次に、第3の層間絶縁膜701上にアンテナ705を形成する(図10(A)参照)。アンテナ705は、Ag、Au、Cu、Pd、Cr、Mo、Ti、Ta、W、Al、Fe、Co、Zn、Sn、Niなどの金属、金属化合物を1つまたは複数有する導電材料を用いることができる。そしてアンテナ705は、電極又は配線691と接続されている。なお図10(A)では、アンテナ705が電極又は配線691と直接接続されているが、本発明のIDチップはこの構成に限定されない。例えば別途形成した配線を用いて、アンテナ705と電極又は配線691とを電気的に接続するようにしても良い。

#### 【0198】

アンテナ705は印刷法、フォトリソグラフィ法、蒸着法または液滴吐出法などを用いて形成することができる。本実施例では、アンテナ705が単層の導電膜で形成されているが、複数の導電膜が積層されたアンテナ705を形成することも可能である。例えば、Niなどで形成した配線に、Cuを無電解めっきでコーティングして、アンテナ705を形成しても良い。

#### 【0199】

なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。また印刷法にはスクリーン印刷法、オフセット印刷法などが含まれる。印刷法、液滴吐出法を用いることで、露光用のマスクを用いずとも、アンテナ705を形成することが可能になる。また、液滴吐出法、印刷法だと、フォトリソグラフィ法と異なり、エッチャングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、IDチップの作製に費やされるコストを抑えることができる。

#### 【0200】

液滴吐出法または各種印刷法を用いる場合、例えば、CuをAgでコートした導電粒子なども用いることが可能である。なお液滴吐出法を用いてアンテナ705を形成する場合、該アンテナ705の密着性が高まるような処理を、第3の層間絶縁膜701の表面に施すことが望ましい。

#### 【0201】

密着性を高めることができる方法として、具体的には、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を第3の層間絶縁膜701の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属、金属化合物を第3の層間絶縁膜701の表面に大気圧下または減圧下においてプラズマ処理を施し、表面改質を行なう方法などが挙げられる。また、上記導電膜または絶縁膜との密着性が高い金属として、チタン、チタン酸化物の他、3d遷移元素であるSc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Znなどが挙げられる。また金属化合物として、上述した金属の酸化物、窒化物、酸窒化物などが挙げられる。上記有機系の絶縁膜として、例えばポリイミド、シロキサンを含む樹脂等が挙げられる。

#### 【0202】

第3の層間絶縁膜701に付着させる金属または金属化合物が導電性を有する場合、アンテナの正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば1~10nmとなるように制御する、あるいは該金属または金属化合物を酸化により部分的に、または全体的に絶縁化すれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッチャングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させるのではなく、液滴吐出法、印刷法、ゾル-ゲル法などを用いて特定の領域にのみ選択的に付着させてても良い。なお金属または金属化合物は、第3の層間絶縁膜701の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であっても良い。

#### 【0203】

そして図10(B)に示すように、アンテナ705を形成した後、アンテナ705を覆

10

20

30

40

50

うように、第3の層間絶縁膜701上に保護層711を形成する。保護層711は、後に剥離層602をエッティングにより除去する際に、アンテナ705を保護することができる材料を用いる。例えば、水またはアルコール類に可溶なエポキシ系、アクリレート系、シリコンを含む樹脂を全面に塗布することで保護層711を形成することができる。

#### 【0204】

本実施例では、スピンドルコート法で水溶性樹脂（東亜合成製：V L - W S H L 1 0）を膜厚30μmとなるように塗布し、仮硬化させるために2分間の露光を行ったあと、UV光を裏面から2.5分、表面から10分、合計12.5分の露光を行って本硬化させて、保護層711を形成する。なお、複数の有機樹脂を積層する場合、有機樹脂同士では使用している溶媒によって塗布または焼成時に一部溶解する恐れや、密着性が高くなりすぎたりする恐れがある。従って、第3の層間絶縁膜701と保護層711を共に同じ溶媒に可溶な有機樹脂を用いる場合、後の工程において保護層711の除去がスムーズに行なわれるよう、第3の層間絶縁膜701を覆うように、無機絶縁膜（窒化珪素膜、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜、窒化アルミニウム膜、または酸素を含む窒化アルミニウム膜、窒素を含む酸化アルミニウム膜）を形成しておくことが好ましい。10

#### 【0205】

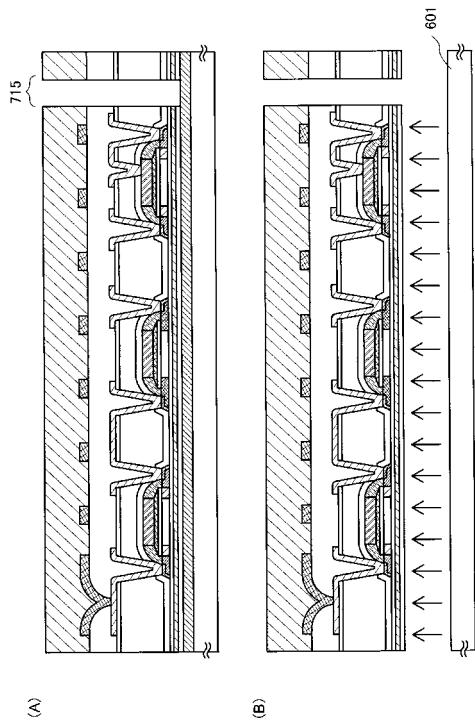

次に図11(A)に示すように、IDチップどうしを分離するために開口部（溝ともいう）715を形成する。開口部715は、剥離層602が露出する程度であれば良い。開口部715の形成は、ダイシング、スクライビングなどを用いることができる。なお、第1の基板601上に形成されているIDチップを分離する必要がない場合、必ずしも開口部715を形成する必要はない。20

#### 【0206】

次に図12(B)に示すように、剥離層602をエッティングにより除去する。本実施例では、エッティングガスとしてフッ化ハロゲンを用い、該ガスを開口部715から導入する。本実施例では、例えばC1F<sub>3</sub>（三フッ化塩素）を用い、温度：350、流量：300sccm、気圧：798パスカル（798Pa）、時間：3hの条件で行なう。また、C1F<sub>3</sub>ガスに窒素を混ぜたガスを用いても良い。C1F<sub>3</sub>等のフッ化ハロゲンを用いることで、剥離層602が選択的にエッティングされ、第1の基板601をTFT611～TFT613から剥離することができる。なおフッ化ハロゲンは、気体であっても液体であってもどちらでも良い。30

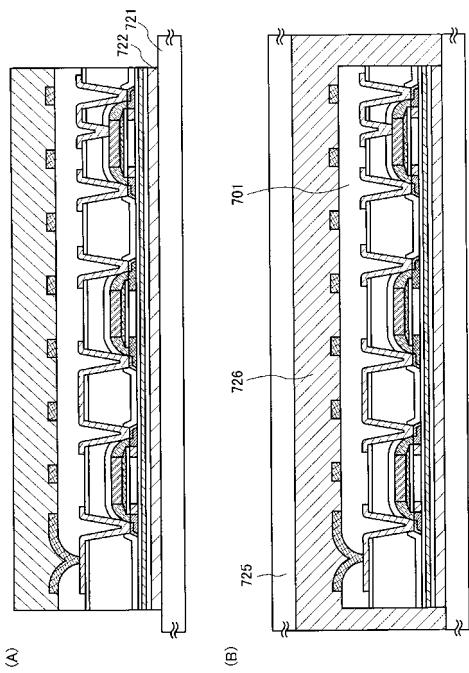

#### 【0207】

次に図12(A)に示すように、剥離されたTFT611～TFT613及びアンテナ705を、接着剤722を用いて第2の基板721に貼り合わせる。接着剤722は、第2の基板721と下地膜603とを貼り合わせることができる材料を用いる。接着剤722は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0208】

第2の基板721として、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。または第2の基板721として、フレキシブル無機材料を用いていても良い。プラスチック基板は、極性基のついたポリノルボルネンからなるARTON(USR製)を用いることができる。また、ポリエチレンテレフタレート(PET)に代表されるポリエステル、ポリエーテルスルホン(PES)、ポリエチレンナフタレート(PEN)、ポリカーボネット(PC)、ナイロン、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。第2の基板721は集積回路において発生した熱を拡散させるために、2～30W/mK程度の高い熱伝導率を有する方が望ましい。40

#### 【0209】

次に図12(B)に示すように、保護層711を除去した後、アンテナ705を覆うよ50

うに接着剤 726 を第3の層間絶縁膜 701 上に塗布し、カバー材 725 を貼り合わせる。カバー材 725 は第2の基板 721 と同様に、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。接着剤 726 の厚さは、例えば 10 ~ 200 μm とすれば良い。

#### 【0210】

また接着剤 726 は、カバー材 725 と第3の層間絶縁膜 701 及びアンテナ 705 とを貼り合わせることができる材料を用いる。接着剤 726 は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0211】

上述した各工程を経て、IDチップが完成する。上記作製方法によって、トータルの膜厚 0.3 μm 以上 3 μm 以下、代表的には 2 μm 程度の飛躍的に薄い集積回路を第2の基板 721 とカバー材 725 との間に形成することができる。なお集積回路の厚さは、半導体素子自体の厚さのみならず、接着剤 722 と接着剤 726 間に形成された各種絶縁膜及び層間絶縁膜の厚さを含めるものとする。また IDチップが有する集積回路の占める面積を、5 mm四方 (25 mm<sup>2</sup>) 以下、より望ましくは 0.3 mm四方 (0.09 mm<sup>2</sup>) ~ 4 mm四方 (16 mm<sup>2</sup>) 程度とすることができる。

10

#### 【0212】

なお集積回路を、第2の基板 721 とカバー材 725 の間のより中央に位置させることで、IDチップの機械的強度を高めることができる。具体的には、第2の基板 721 とカバー材 725 の間の距離を d とすると、第2の基板 721 と、集積回路の厚さ方向における中心との距離 x が、以下の数3を満たすように、接着剤 722、接着剤 726 の厚さを制御することが望ましい。

20

#### 【0213】

#### 【数3】

$$\frac{1}{2}d - 30 \mu m < x < \frac{1}{2}d + 30 \mu m$$

#### 【0214】

また好ましくは、以下の数4を満たすように、接着剤 722、接着剤 726 の厚さを制御する。

30

#### 【0215】

#### 【数4】

$$\frac{1}{2}d - 10 \mu m < x < \frac{1}{2}d + 10 \mu m$$

#### 【0216】

なお図12(B)では、カバー材 725 を用いる例を示しているが、本発明はこの構成に限定されない。例えば図12(A)に示した工程までで終了としても良い。

#### 【0217】

40

なお本実施例では、耐熱性の高い第1の基板 601 と集積回路の間に剥離層を設け、エッティングにより該剥離層を除去することで基板と集積回路とを剥離する方法について示したが、本発明のIDチップの作製方法は、この構成に限定されない。例えば、耐熱性の高い基板と集積回路の間に金属酸化膜を設け、該金属酸化膜を結晶化により脆弱化して集積回路を剥離しても良い。或いは、耐熱性の高い基板と集積回路の間に、水素を含む非晶質半導体膜を用いた剥離層を設け、レーザ光の照射により該剥離層を除去することで基板と集積回路とを剥離しても良い。或いは、集積回路が形成された耐熱性の高い基板を機械的に削除または溶液やガスによるエッティングで除去することで集積回路を基板から切り離しても良い。

#### 【0218】

50

またIDチップの可撓性を確保するために、下地膜603に接する接着剤722に有機樹脂を用いる場合、下地膜603として窒化珪素膜または窒素を含む酸化珪素膜を用いることで、有機樹脂からNaなどのアルカリ金属やアルカリ土類金属が半導体膜中に拡散するのを防ぐことができる。

#### 【0219】

また対象物の表面が曲面を有しており、それにより該曲面に貼り合わされたIDチップの第2の基板721が、錐面、柱面など母線の移動によって描かれる曲面を有するよう曲がってしまう場合、該母線の方向とTFT611～TFT613のキャリアが移動する方向とを揃えておくことが望ましい。上記構成により、第2の基板721が曲がっても、それによってTFT611～TFT613の電気特性に影響が出るのを抑えることができる。また、島状の半導体膜が集積回路内において占める面積の割合を、1～30%とすることで、第2の基板721が曲がっても、それによってTFT611～TFT613の電気特性に影響が出るのをより抑えることができる。10

#### 【0220】

なお本実施例では、アンテナを集積回路と同じ基板上に形成している例について説明したが、本発明はこの構成に限定されない。別の基板上に形成したアンテナと集積回路とを、後に貼り合わせることで、電気的に接続するようにしても良い。

#### 【0221】

なお一般的にIDチップで用いられている電波の周波数は、13.56MHz、2.45GHzが多く、該周波数の電波を検波できるようにIDチップを形成することが、汎用性を高める上で非常に重要である。20

#### 【0222】

また本実施例のIDチップでは、半導体基板を用いて形成されたIDチップよりも電波が遮蔽されにくく、電波の遮蔽により信号が減衰するのを防ぐことができるというメリットを有している。よって、半導体基板を用いずに済むので、IDチップのコストを大幅に低くすることができる。例えば、直径12インチのシリコン基板を用いた場合と、730×920mm<sup>2</sup>のガラス基板を用いた場合とを比較する。前者のシリコン基板の面積は約730000mm<sup>2</sup>であるが、後者のガラス基板の面積は約672000mm<sup>2</sup>であり、ガラス基板はシリコン基板の約9.2倍に相当する。後者のガラス基板の面積は約672000mm<sup>2</sup>では、基板の分断により消費される面積を無視すると、1mm四方のIDチップが約672000個形成できる計算になり、該個数はシリコン基板の約9.2倍の数に相当する。そしてIDチップの量産化を行なうための設備投資は、730×920mm<sup>2</sup>のガラス基板を用いた場合の方が直径12インチのシリコン基板を用いた場合よりも工程数が少なくて済むため、額を3分の1で済ませることができる。さらに本発明では、集積回路を剥離した後、ガラス基板を再び利用できる。よって、破損したガラス基板を補填する、あるいはガラス基板の表面を清浄化する費用を踏まえても、シリコン基板を用いる場合より大幅にコストを抑えることができる。またガラス基板を再利用せずに廃棄していくとしても、730×920mm<sup>2</sup>のガラス基板の値段は、直径12インチのシリコン基板の半分程度で済むので、IDチップのコストを大幅に低くすることができることがわかる。30

#### 【0223】

従って、730×920mm<sup>2</sup>のガラス基板を用いた場合、直径12インチのシリコン基板を用いた場合よりも、IDチップの値段を約30分の1程度に抑えることができることがわかる。IDチップは、使い捨てを前提とした用途も考えられるので、コストを大幅に低くすることができる本発明のIDチップは上記用途に非常に有用である。

#### 【0224】

なお本実施例では、集積回路を剥離して、可撓性を有する基板に貼り合わせる例について説明したが、本発明はこの構成に限定されない。例えばガラス基板のように、集積回路の作製工程における熱処理に耐えうるような、耐熱温度を有している基板を用いる場合、必ずしも集積回路を剥離する必要はない。50

**【0225】**

また、本実施例は、必要であれば実施の形態及び他の実施例と自由に組み合わせることが可能である。

**【実施例4】****【0226】**

本実施例では、本発明の生体情報検出センサに用いられるIDチップ及びセンサの構成を、図13～図19を用いて説明する。

**【0227】**

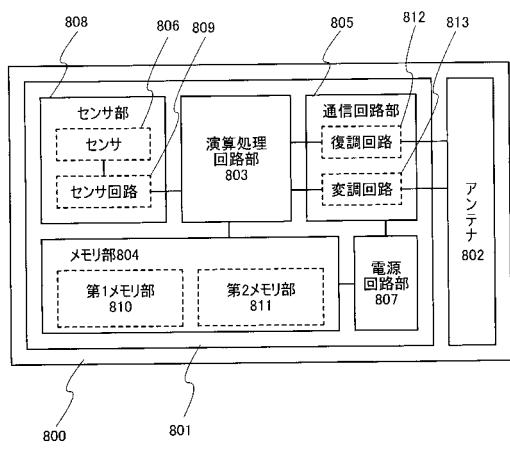

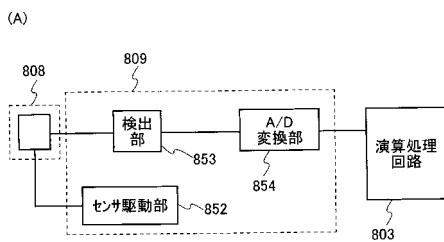

図13に、集積回路部801とアンテナ802を備えたIDチップ800の構成を示す。集積回路部801は、温度、湿度、照度、その他の特性を物理的又は化学的手段により検出するセンサ部(生体情報検出部)806を備えている。センサ部806は、センサ808とそれを制御するセンサ回路809が含まれている。センサ808は抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、圧電素子、トランジスタ、サーミスタ、ダイオードなどの半導体素子で形成される。センサ808の構成は、生体情報に対し何を検出するかで選択すれば良い。例えば、脈拍を検出したい場合には、圧電素子を用いれば良い。また、体温を測定するには熱起電力素子や抵抗素子を用いれば良い。センサ回路809はインピーダンス、リアクタンス、インダクタンス、電圧又は電流の変化を検出し、アナログ/デジタル変換(A/D変換)して演算処理回路部803に信号を出力する。

**【0228】**

メモリ部804は、読み出し専用メモリや、書き換え可能メモリの一方若しくは双方を備えている。メモリ部804は、スタティックRAM(Static RAM)、EEPROM(Electrically Erasable Programmable Read-Only Memory)、フラッシュメモリなどで構成することで、センサ部806及びアンテナ802を経由して受信した外部からの情報を隨時記録することができる。メモリ部804は、センサ部806で検知した信号を格納する第1メモリ部810と、リーダ/ライタ装置から書き込まれた情報を記録する第2メモリ部811に分けて構成することもできる。また、マスクROMやプログラマブルROMで読み出し専用メモリ部を設けておいても良い。

**【0229】**

第1メモリ部810はセンサ部806で検知した生体情報を記録するために、逐次書き込みを可能とともに、データが消失しないフラッシュメモリなどで構成することが好ましい。また、フローティングゲート構造の記憶素子であって、一度だけ書き込み可能な記憶素子を適用することが好ましい。

**【0230】**

通信回路部805は、復調回路812、変調回路813を含んでいる。復調回路812は、アンテナ802を経由して入力される信号を復調して、演算処理回路部803に出力する。信号にはセンサ部806を制御する信号や、メモリ部804に記憶させる情報を含んでいる。また、センサ回路809から出力される信号や、メモリ部804から読み出された情報は、演算処理回路部803を通して変調回路813に出力される。変調回路813は、この信号を無線通信可能な信号に変調して、アンテナ802を介して外部装置に出力する。

**【0231】**

演算処理回路部803、センサ部806、メモリ部804及び通信回路部805を動作させるのに必要な電力は、アンテナ802を介して供給される。アンテナ802は、リーダ/ライタと呼ばれる外部装置から供給される電磁波を受信して、必要な電力を電源回路部807で発生させている。アンテナ802は通信する周波数帯に応じて適宜設計すれば良い。電磁波の周波数帯は、135kHzまでの長波帯、6~60MHz(代表的には13.56MHz)の短波帯、400~950MHzの超短波帯、2~25GHzのマイクロ波帯などを使用することができる。長波帯や短波帯のアンテナは、ループアンテナによ

10

20

30

40

50

る電磁誘導を利用したものが利用される。その他に相互誘導作用（電磁結合方式）又は静電気による誘導作用（静電結合方式）を利用したものであっても良い。電力は電源回路部 807 で生成する。アンテナ 802 はデータ通信用アンテナと、電力供給用アンテナを分離して設けても良い。

#### 【0232】

このようなアンテナ 802 は、アルミニウム、銅、銀を含む金属材料で形成する。例えば、銅又は銀のペースト状組成物を、スクリーン印刷、オフセット印刷、インクジェット方式の印刷法でアンテナ 802 形成することができる。また、スパッタリングなどでアルミニウム膜を形成し、エッチング加工によりアンテナ 802 を形成しても良い。その他、電解メッキ法、無電解メッキ法を用いてアンテナ 802 を形成しても良い。もちろん実施例 2 のアンテナ 477、実施例 3 のアンテナ 705 と同様の材料、同様の作製工程で形成してもよい。10

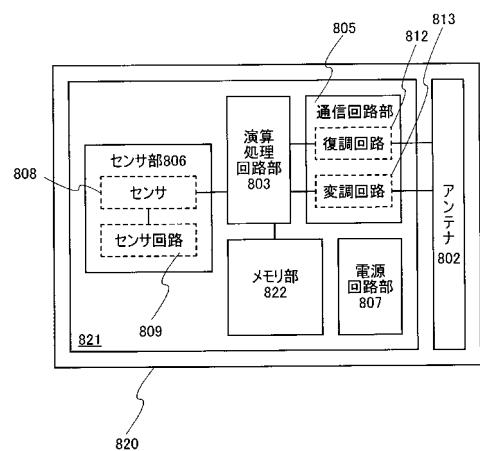

#### 【0233】

図 13 で示す ID チップ 800において、メモリ部 804 の構成を変更した ID チップ 820 を図 14 に示す。集積回路部 821 はメモリ部 822 を逐次書き込みを可能とするとともに、データが消失しないフローティングゲート構造の記憶素子で構成したものである。特に、フローティングゲート構造の記憶素子であって、一度だけ書き込み可能な記憶素子を適用することが好ましい。この構成の ID チップ 820 はセンサ 808 で検出したデータを記録して、読み出す機能のみを持っている。機能を単純化することにより、ID チップ 820 を小型化することができる。また、省電力化することができる。20

#### 【0234】

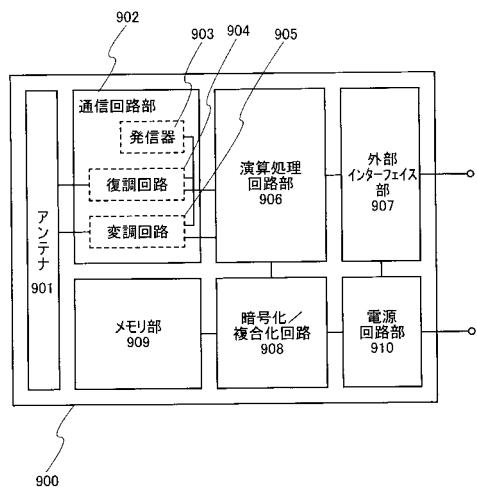

図 15 は、ID チップ 800 と情報の送受信を行うリーダ / ライタモジュール 900 の一例を示す。リーダ / ライタモジュール 900 は、アンテナ 901 と、発振器 903、復調回路 904、変調回路 905 を備えた通信回路部 902 を備えている。その他に演算処理回路部 906、外部インターフェイス部 907 を備えコンピュータなどの情報処理装置と接続可能となっている。制御信号を暗号化して送受信するには、暗号化 / 復号化回路部 908 とメモリ部 909 を備えておけば良い。電源回路部 910 は各回路に電力を供給するものとなっている。

#### 【0235】

図 13 で示す ID チップ 800 及び図 14 で示す ID チップ 820 は、単結晶半導体で作製するトランジスタ、多結晶半導体膜を用いて作製する TFT など、その他の能動素子と受動素子を組み合わせて構成する。もちろん実施例 2 または実施例 3 の記載に基づいて ID チップを形成してもよい。30

#### 【0236】

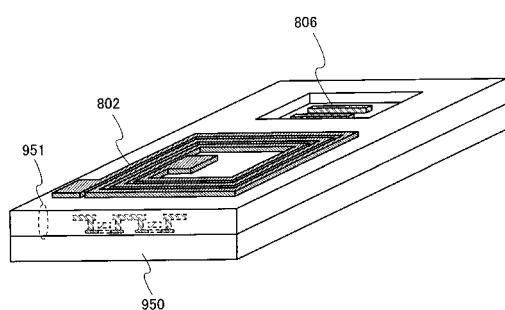

図 16 は基板 950、素子形成層 951 及びアンテナ 802 を積層した ID チップ 800 若しくは ID チップ 820 の一構成例を斜視図で示している。基板 950 は、例えば実施例 2 の基板 491、実施例 3 の基板 721 と同様のものであればよい。

素子形成層 951 は、例えば、図 8 (B) に示す下地膜 403、島状半導体膜 404 ~ 406、ゲート絶縁膜 407 ~ 409、ゲート電極 441 ~ 443、パッシベーション膜 461、層間絶縁膜 462、層間絶縁膜 463、電極又は配線 471 が含まれている。また素子形成層 951 には、図 12 (B) に示す下地膜 603、島状半導体膜 621 ~ 623、ゲート絶縁膜 661 ~ 663、サイドウォール 665 ~ 667、ゲート電極 671 ~ 673、パッシベーション膜 681、層間絶縁膜 682、層間絶縁膜 683、電極又は配線 691 ~ 695 が含まれていてもよい。アンテナ 802 は TFT で形成される回路と接続している。アンテナ 802 の上には、さらに無機絶縁材料又は有機絶縁材料により保護膜が形成されていても良い。このように、素子形成層 951 とアンテナ 802 を一体形成することにより ID チップの小型化を図ることができる。ID チップ 800 若しくは ID チップ 820 には、センサ部 806 が設けられている。センサ部 806 の構成は、光導入窓や静電容量を測定するための電極が設けられ、それが露出した状態にしてあっても良い。40

#### 【0237】

50

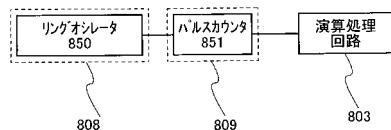

図17はセンサ部806の一例を示している。このセンサ部806は温度を検知するセンサである。センサ808はTFTを用いた複数段のリングオシレータ850で形成されている。これは、リングオシレータ850の発振周波数が温度に依存して変化することを利用したものである。TFTのしきい値電圧は、温度の上昇に伴って低下する。しきい値電圧の低下によりオン電流が増加する。リングオシレータ850は、TFTのオン電流が大きい程、発振周波数が高くなるという特性を持っている。この特性を利用して、リングオシレータ850を温度センサとして利用することができる。リングオシレータ850の発振周波数は、センサ回路809のパルスカウンタ851で計測することが可能である。パルスカウンタ851の信号は、そのまま、若しくはレベルシフトして演算処理回路部803に出力すれば良い。この温度を検知するセンサにより人体の体温を測定することができる。10

#### 【0238】

図18(A)は光の有無を検知するセンサの一例を示している。センサ808は、フォトダイオード、フォトトランジスタなどで形成されている。センサ回路809は、センサ駆動部852、検出部853及びA/D変換部854を含んでいる。フォトダイオード、フォトトランジスタなどで、例えば、人体が紫外線に曝露している時間を検出することができる。

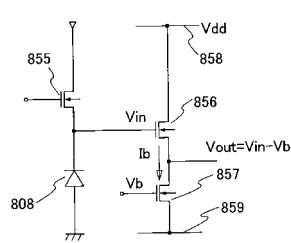

#### 【0239】

図18(B)は検出部853を説明する回路図である。リセット用TFT855を導通状態にするとセンサ808には逆バイアス電圧が印加される。ここで、センサ808のマイナス側端子の電位が電源電圧の電位まで充電される動作を「リセット」と呼ぶ。その後、リセット用TFT855を非導通状態にする。そのとき、センサ808の起電力により、時間が経過するに従い電位状態が変化する。すなわち、電源電圧の電位まで充電されていたセンサ808のマイナス側端子の電位が、光電変換によって発生した電荷によって徐々に低下する。ある一定時間を経過した後、バイアス用TFT857を導通状態とすると、增幅用TFT856を通じて出力側に信号が出力される。この場合、增幅用TFT856とバイアス用TFT857は所謂ソースフォロワ回路として動作する。20

#### 【0240】

図18(B)ではソースフォロワ回路をnチャネル型TFTで形成した例で示されているが、勿論、pチャネル型TFTでも形成することができる。增幅側電源線858には電源電圧Vddが加えられている。バイアス側電源線859は基準電位0ボルトが与えられている。增幅用TFT856のドレイン端子は増幅側電源線858に接続され、增幅用TFT856のソース端子はバイアス用TFT857のドレイン端子に接続されている。バイアス用TFT857のソース端子はバイアス側電源線859に接続されている。バイアス用TFT857のゲート端子にはバイアス電圧Vbが印加され、このTFTにはバイアス電流Ibが流れる。バイアス用TFT857は基本的には定電流源として動作する。增幅用TFT856のゲート端子には入力電圧Vinが加えられ、ソース端子が出力端子となる。このソースフォロワ回路の入出力関係は、Vout = Vin - Vbとなる。この出力電圧VoutはA/D変換部854によりデジタル信号に変換する。デジタル信号は演算処理回路部803に出力する。30

#### 【0241】

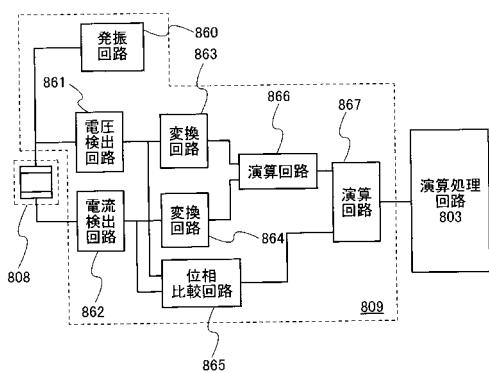

図19はセンサ808に静電容量を検出する素子を設けた一例を示している。静電容量を検出する素子は、一対の電極を備えている。電極間に液体又は気体などの媒体が充填されるようになっている。この一対の電極間の、静電容量の変化を検知することで、例えば人体の体温や脈拍や筋肉の動きを検出する。また、一対の電極間にポリイミド、アクリルその他吸湿性の誘電体を介在させて、電気抵抗の微小な変化を読み取ることにより人体の発汗を検知することもできる。40

#### 【0242】

センサ回路809は、以下に示す構成となっている。発振回路(パルスジェネレータ)860は測定基準信号を生成し、センサ808の電極にその信号を入力する。このときの50

電圧は電圧検出回路 861 にも入力される。電圧検出回路 861 により検出された基準信号は、変換回路 863 で実効値を示す電圧信号に変換される。センサ 808 の電極間に流れる電流は、電流検出回路 862 により検出する。電流検出回路 862 により検出された信号は、変換回路 864 により実効値を示す電流信号に変換される。演算回路 866 は、変換回路 863 の出力である電圧信号と、変換回路 864 の出力である電流信号を演算処理してインピーダンス若しくはアドミタンスなどの電気パラメータを算出する。また、電圧検出回路 861 の出力と電流検出回路 862 の出力は、位相比較回路 865 に入力される。位相比較回路 865 はこの両者の信号の位相差を、演算回路 867 に出力する。演算回路 867 は、演算回路 866 と位相比較回路 865 の出力信号を用いて静電容量を算出する。そして、その信号を演算処理回路部 803 に出力する。

10

## 【0243】

なお本実施例では、センサ部（生体情報検出部）108 を ID チップに内蔵する構成を示しているが、センサ部は ID チップと別に形成して外付けとする構成にしてもよい。

## 【0244】

また、本実施例は、必要であれば実施の形態及び他の実施例と自由に組み合わせることが可能である。

## 【産業上の利用可能性】

## 【0245】

本発明により、衛生的で簡単に取り替えることのできる生体情報検出センサを得ることが可能である。

20

## 【図面の簡単な説明】

## 【0246】

【図 1】本発明の生体情報検出センサを示す図。

【図 2】本発明の生体情報検出センサを示す図。

【図 3】本発明の生体情報検出センサを示す図。

【図 4】本発明の生体情報検出センサを示す図。

【図 5】本発明の ID チップの作製工程を示す図。

【図 6】本発明の ID チップの作製工程を示す図。

【図 7】本発明の ID チップの作製工程を示す図。

【図 8】本発明の ID チップの作製工程を示す図。

30

【図 9】本発明の ID チップの作製工程を示す図。

【図 10】本発明の ID チップの作製工程を示す図。

【図 11】本発明の ID チップの作製工程を示す図。

【図 12】本発明の ID チップの作製工程を示す図。

【図 13】本発明の ID チップの構成を示す図。

【図 14】本発明の ID チップの構成を示す図。

【図 15】本発明のリーダ／ライタモジュールの構成を示す図。

【図 16】本発明の ID チップの一構成例を示す斜視図。

【図 17】本発明のセンサ部の構成を説明するブロック図。

【図 18】本発明のセンサ部の構成を説明するブロック図及び回路図。

40

【図 19】本発明のセンサ部の構成を説明するブロック図。

## 【符号の説明】

## 【0247】

101 生体情報検出センサ

102 アンテナ

103 粘着テープ

104 溝

105 固定機構

106 手首

108 センサ部

50

|         |                |    |

|---------|----------------|----|

| 1 1 1   | R / W マシン      |    |

| 1 1 2   | 表示部            |    |

| 1 1 3   | 表示部            |    |

| 1 1 4   | アンテナ           |    |

| 1 1 5   | 操作ボタン          |    |

| 2 0 1   | 新生児            |    |

| 2 0 1 a | 新生児            |    |

| 2 0 1 b | 新生児            |    |

| 2 0 1 c | 新生児            |    |

| 2 0 2   | 手首             | 10 |

| 2 0 4   | ベッド            |    |

| 2 0 5   | 新生児室           |    |

| 2 1 1   | 生体情報検出センサシステム  |    |

| 2 1 2   | 生体情報検出センサ      |    |

| 2 1 3   | アンテナ           |    |

| 2 1 4   | 粘着テープ          |    |

| 4 0 1   | 基板             |    |

| 4 0 2   | 剥離層            |    |

| 4 0 3   | 下地膜            |    |

| 4 0 3 a | 下層下地膜          | 20 |

| 4 0 3 b | 中層下地膜          |    |

| 4 0 3 c | 上層下地膜          |    |

| 4 0 4   | 島状半導体膜         |    |

| 4 0 5   | 島状半導体膜         |    |

| 4 0 6   | 島状半導体膜         |    |

| 4 0 7   | ゲート絶縁膜         |    |

| 4 0 8   | ゲート絶縁膜         |    |

| 4 0 9   | ゲート絶縁膜         |    |

| 4 1 1   | チャネル形成領域       |    |

| 4 1 2   | 低濃度不純物領域       | 30 |

| 4 1 3   | ソース領域またはドレイン領域 |    |

| 4 2 1   | チャネル形成領域       |    |

| 4 2 2   | ソース領域またはドレイン領域 |    |

| 4 3 1   | チャネル形成領域       |    |

| 4 3 2   | 低濃度不純物領域       |    |

| 4 3 3   | ソース領域またはドレイン領域 |    |

| 4 4 1   | ゲート電極          |    |

| 4 4 1 a | 下層ゲート電極        |    |

| 4 4 1 b | 上層ゲート電極        |    |

| 4 4 2   | ゲート電極          | 40 |

| 4 4 2 a | 下層ゲート電極        |    |

| 4 4 2 b | 上層ゲート電極        |    |

| 4 4 3   | ゲート電極          |    |

| 4 4 3 a | 下層ゲート電極        |    |

| 4 4 3 b | 上層ゲート電極        |    |

| 4 5 1   | T F T          |    |

| 4 5 2   | T F T          |    |

| 4 5 3   | T F T          |    |

| 4 6 1   | パッシベーション膜      |    |

| 4 6 2   | 層間絶縁膜          | 50 |

|         |                |    |

|---------|----------------|----|

| 4 6 3   | 層間絶縁膜          |    |

| 4 6 4   | 層間絶縁膜          |    |

| 4 6 5   | 保護層            |    |

| 4 7 1   | 電極又は配線         |    |

| 4 7 2   | 電極又は配線         |    |

| 4 7 3   | 電極又は配線         |    |

| 4 7 4   | 電極又は配線         |    |

| 4 7 5   | 電極又は配線         |    |

| 4 7 7   | アンテナ           |    |

| 4 8 1   | 開口部            | 10 |

| 4 8 2   | 接着剤            |    |

| 4 8 3   | 接着剤            |    |

| 4 9 1   | 基板             |    |

| 4 9 2   | カバー材           |    |

| 6 0 1   | 基板             |    |

| 6 0 2   | 剥離層            |    |

| 6 0 3   | 下地膜            |    |

| 6 0 3 a | 下層下地膜          |    |

| 6 0 3 b | 中層下地膜          |    |

| 6 0 3 c | 上層下地膜          | 20 |

| 6 1 1   | T F T          |    |

| 6 1 2   | T F T          |    |

| 6 1 3   | T F T          |    |

| 6 2 1   | 島状半導体膜         |    |

| 6 2 2   | 島状半導体膜         |    |

| 6 2 3   | 島状半導体膜         |    |

| 6 3 1   | チャネル形成領域       |    |

| 6 3 2   | 低濃度不純物領域       |    |

| 6 3 3   | ソース領域またはドレイン領域 |    |

| 6 3 5   | シリサイド領域        | 30 |

| 6 4 1   | チャネル形成領域       |    |

| 6 4 2   | ソース領域またはドレイン領域 |    |

| 6 4 5   | シリサイド領域        |    |

| 6 5 1   | チャネル形成領域       |    |

| 6 5 2   | 低濃度不純物領域       |    |

| 6 5 3   | ソース領域またはドレイン領域 |    |

| 6 5 5   | シリサイド領域        |    |

| 6 6 1   | ゲート絶縁膜         |    |

| 6 6 2   | ゲート絶縁膜         |    |

| 6 6 3   | ゲート絶縁膜         | 40 |

| 6 6 5   | サイドウォール        |    |

| 6 6 6   | サイドウォール        |    |

| 6 6 7   | サイドウォール        |    |

| 6 7 1   | ゲート電極          |    |

| 6 7 1 a | 下層ゲート電極        |    |

| 6 7 1 b | 上層ゲート電極        |    |

| 6 7 2   | ゲート電極          |    |

| 6 7 2 a | 下層ゲート電極        |    |

| 6 7 2 b | 上層ゲート電極        |    |

| 6 7 3   | ゲート電極          | 50 |

|         |           |    |

|---------|-----------|----|

| 6 7 3 a | 下層ゲート電極   |    |

| 6 7 3 b | 上層ゲート電極   |    |

| 6 8 1   | パッシベーション膜 |    |

| 6 8 2   | 層間絶縁膜     |    |

| 6 8 3   | 層間絶縁膜     |    |

| 6 9 1   | 電極又は配線    |    |

| 6 9 2   | 電極又は配線    |    |

| 6 9 3   | 電極又は配線    |    |

| 6 9 4   | 電極又は配線    |    |

| 6 9 5   | 電極又は配線    | 10 |

| 7 0 1   | 層間絶縁膜     |    |

| 7 0 5   | アンテナ      |    |

| 7 1 1   | 保護層       |    |

| 7 1 5   | 開口部       |    |

| 7 2 1   | 基板        |    |

| 7 2 2   | 接着剤       |    |

| 7 2 5   | カバー材      |    |

| 7 2 6   | 接着剤       |    |

| 8 0 0   | IDチップ     |    |

| 8 0 1   | 集積回路部     | 20 |

| 8 0 2   | アンテナ      |    |

| 8 0 3   | 演算処理回路部   |    |

| 8 0 4   | メモリ部      |    |

| 8 0 5   | 通信回路部     |    |

| 8 0 6   | センサ部      |    |

| 8 0 7   | 電源回路部     |    |

| 8 0 8   | センサ       |    |

| 8 0 9   | センサ回路     |    |

| 8 1 0   | 第1メモリ部    |    |

| 8 1 1   | 第2メモリ部    | 30 |

| 8 1 2   | 復調回路      |    |

| 8 1 3   | 変調回路      |    |

| 8 2 0   | IDチップ     |    |

| 8 2 1   | 集積回路部     |    |

| 8 2 2   | メモリ部      |    |

| 8 5 0   | リングオシレータ  |    |

| 8 5 1   | パルスカウンタ   |    |

| 8 5 2   | センサ駆動部    |    |

| 8 5 3   | 検出部       |    |

| 8 5 4   | A/D変換部    | 40 |

| 8 5 5   | リセット用TFT  |    |

| 8 5 6   | 增幅用TFT    |    |

| 8 5 7   | バイアス用TFT  |    |

| 8 5 8   | 增幅側電源線    |    |

| 8 5 9   | バイアス側電源線  |    |

| 8 6 0   | 発振回路      |    |

| 8 6 1   | 電圧検出回路    |    |

| 8 6 2   | 電流検出回路    |    |

| 8 6 3   | 変換回路      |    |

| 8 6 4   | 変換回路      | 50 |

|       |                |    |

|-------|----------------|----|

| 8 6 5 | 位相比較回路         |    |

| 8 6 6 | 演算回路           |    |

| 8 6 7 | 演算回路           |    |

| 9 0 0 | リーダ / ライタモジュール |    |

| 9 0 1 | アンテナ           |    |

| 9 0 2 | 通信回路部          |    |

| 9 0 3 | 発振器            |    |

| 9 0 4 | 復調回路           |    |

| 9 0 5 | 変調回路           |    |

| 9 0 6 | 演算処理回路部        | 10 |

| 9 0 7 | 外部インターフェイス部    |    |

| 9 0 8 | 暗号化 / 復号化回路部   |    |

| 9 0 9 | メモリ部           |    |

| 9 1 0 | 電源回路部          |    |

| 9 5 0 | 基板             |    |

| 9 5 1 | 素子形成層          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【図10】

【図 1 1】

(A)

(B)

【図 1 2】

(A)

(B)

【図 1 3】

【図 1 4】

【図15】

【図16】

【図19】

【図17】

【図18】

(B)

---

フロントページの続き

(56)参考文献 特開平9-89676(JP,A)

特開2006-58263(JP,A)

特開2002-296229(JP,A)

特表2006-507855(JP,A)

特許第2708757(JP,B2)

特開昭63-49134(JP,A)

特公平6-26599(JP,B2)

特表2004-520898(JP,A)

特開2006-51343(JP,A)

特開2003-275183(JP,A)

国際公開第2005/074161(WO,A1)

(58)調査した分野(Int.Cl., DB名)

A61B 5/00 - 5/22

A61N 1/00 - 1/44

JSTPlus/JMEDPlus/JST7580(JDreamII)