(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6228119号

(P6228119)

(45) 発行日 平成29年11月8日(2017.11.8)

(24) 登録日 平成29年10月20日(2017.10.20)

(51) Int.Cl.

H01L 31/074 (2012.01)

F 1

H01L 31/06 440

請求項の数 15 (全 19 頁)

(21) 出願番号 特願2014-527730 (P2014-527730)

(86) (22) 出願日 平成24年8月14日 (2012.8.14)

(65) 公表番号 特表2014-527725 (P2014-527725A)

(43) 公表日 平成26年10月16日 (2014.10.16)

(86) 國際出願番号 PCT/GB2012/051982

(87) 國際公開番号 WO2013/030531

(87) 國際公開日 平成25年3月7日 (2013.3.7)

審査請求日 平成27年8月13日 (2015.8.13)

(31) 優先権主張番号 61/528,650

(32) 優先日 平成23年8月29日 (2011.8.29)

(33) 優先権主張国 米国(US)

(73) 特許権者 514051257

アイキューイー パブリック リミテッド

カンパニー

I Q E P L C.

イギリス国 シーエフ3 Oエルダブリュ

ウェールズ, カーディフ, セント

メロンズ, パスカル クローズ

P a s c a l C l o s e, S t M e

l l o n s, C a r d i f f, W a l

e s C F 3 O L W G B

(74) 代理人 100090022

弁理士 長門 侃二

最終頁に続く

(54) 【発明の名称】光起電デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコン以外のⅢV族半導体材料層(1, 4, 7, 10)と、

少なくとも1種類のⅢⅢⅠ族の原子と少なくとも1種類のV族の原子とから生成され、

前記ⅢV族半導体材料層との界面(8)を有し、ⅢV族半導体材料層がⅢⅢⅠ-V族半導

体材料へ格子整合している、ⅢⅢⅠ-V族半導体材料層(3, 9)と、

前記V族原子が前記ⅢV族半導体材料層に拡散することをコントロールするために、前

記ⅢⅢⅠ-V族半導体材料層と前記ⅢV族半導体材料層の間の前記界面か、または、前記

界面から離間した、前記ⅢV族半導体材料層か、または前記ⅢⅢⅠ-V族半導体材料層に

おけるシリコン層(6)と、

前記界面と接し、かつ前記ⅢⅢⅠ-V族半導体材料の層からシリコン層を介して拡散し

たV族原子によってドープされた、前記ⅢV族半導体材料層におけるV族でドープされた

n型の領域と、

を備えることを特徴とする半導体材料。

## 【請求項 2】

請求項1に記載の半導体材料において、

前記ⅢV族半導体材料層における前記V族でドープされた領域は、前記ⅢV族半導体材

料層において、p型領域を有するp-n接合部(2)となることを特徴とする半導体材料

。

## 【請求項 3】

10

20

請求項 1 に記載の半導体材料において、

前記 I V 族半導体材料層における前記 V 族でドープされた領域と前記 I I I - V 族半導体材料層とは、前記界面におけるトンネルダイオードを形成することを特徴とする半導体材料。

**【請求項 4】**

請求項 1 乃至 3 いずれか 1 項に記載の半導体材料において、前記 I V 族半導体材料層は、ゲルマニウムであることを特徴とする半導体材料。

**【請求項 5】**

請求項 1 乃至 4 のいずれか 1 項に記載の半導体材料において、

前記 I V 族半導体材料層は、シリコン - ゲルマニウムかまたはシリコン - ゲルマニウム 10 - 錫であることを特徴とする半導体材料。

**【請求項 6】**

請求項 1 乃至 5 のいずれか 1 項に記載の半導体材料において、

前記 I I I - V 族半導体材料層は、Al, Ga, In の内の 1 つ以上の I I I 族原子を含み、P, As, Sb, Bi の内の 1 つ以上の V 族原子を含むことを特徴とする半導体材料。

**【請求項 7】**

請求項 1 乃至 6 のいずれか 1 項に記載の半導体材料において、

前記 I V 族半導体材料層 (10) は、前記シリコン層 (6) と前記 I I I - V 族半導体材料層 (3) との間のエピタキシャル I V 族半導体材料層 (7) を備えることを特徴とする半導体材料。 20

**【請求項 8】**

請求項 1 乃至 7 のいずれか 1 項に記載の半導体材料において、

前記 I V 族半導体材料層は、基板層 (1) と当該基板層の上に成長されたエピタキシャル層 (10) とを備えることを特徴とする半導体材料。

**【請求項 9】**

請求項 1 乃至 8 のいずれか 1 項に記載の半導体材料において、

前記シリコン層 (6) は、7.5 以下の厚さを有することを特徴とする半導体材料。

**【請求項 10】**

第 1 の I I I - V 族層 (3) との界面 (8) に対し前記 I V 族層の反対側にある、前記 I V 族半導体材料層 (10) との界面を有する第 2 の I I I - V 族半導体材料層 (1) を備え、当該第 2 の I I I - V 族半導体材料層と前記 I V 族半導体材料層との間に第 2 のシリコン層 (14) を備えることを特徴とする、請求項 1 乃至 9 のいずれか 1 項に記載の半導体材料。 30

**【請求項 11】**

前記 半導体材料は、太陽電池セルであることを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の 半導体材料。

**【請求項 12】**

半導体材料を製造する方法であって、

シリコン以外の I V 族半導体材料層 (1, 4, 7, 10) を準備するステップと、

少なくとも 1 種類の I I I 族の原子と少なくとも 1 種類の V 族の原子とから生成され、前記 I V 族半導体材料層との界面 (8) を有する I I I - V 族半導体材料層 (3, 9) を設けるステップと、

前記 I I I - V 族半導体材料層の間の界面か、または、当該界面から離間した、前記 I V 族半導体材料層か、または前記 I I I - V 族半導体材料層におけるシリコン層 (6) を設けるステップと、

前記 I I I - V 族半導体材料層からの V 族原子をシリコン層を通じて拡散して前記 I V 族半導体材料層にドープし、前記界面と接する前記 I V 族半導体材料層において、V 族でドープされた n 型領域を形成する、V 族原子を拡散するステップと、

を備えることを特徴とする方法。 50

**【請求項 1 3】**

請求項 1 2 に記載の方法において、

前記 V 族原子を拡散するステップは、前記 I V 族半導体材料層における p - n 接合部(2)を形成することを特徴とする方法。

**【請求項 1 4】**

請求項 1 2 に記載の方法において、

前記 V 族原子の拡散は、既に n 型となっている前記 I V 族半導体材料層の領域で行われ、高濃度の n 型ドーパントを有する、n 型ドープ領域が形成されることを特徴とする方法。

**【請求項 1 5】**

太陽光から電力を生成する方法であって、

請求項 1 1 に記載の太陽電池セルを準備するステップか、または請求項 1 2 乃至 1 4 のいずれか 1 項に記載の方法で製造される半導体材料からなる太陽電池を準備するステップと、

前記太陽電池に太陽光を照射するステップと、

を備えることを特徴とする方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、太陽電池を含む光起電デバイスに関する。

10

**【背景技術】****【0 0 0 2】**

光起電装置のよく知られた 1 つのタイプは、直列に接続された 2 つ以上のセルを有し、半導体材料の垂直方向の積層体から形成されており、各々のセルは、異なるバンドギャップを有する p - n 接合部を含んでおり、これらの接合部は、このデバイスに当たる光のスペクトルの異なる部分を吸収するのに用いられている（タンデムセル）。多接合光起電デバイスは、現在使用されているものはゲルマニウム基板に作製されている。

**【0 0 0 3】**

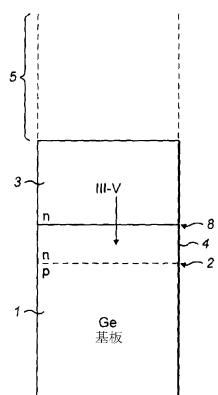

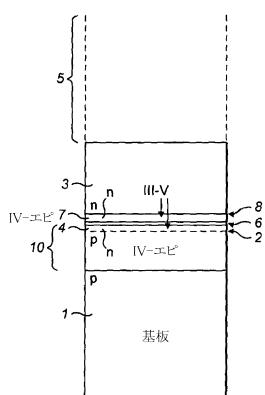

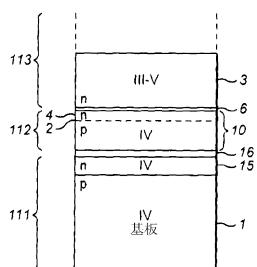

図 1 は、このようなデバイスの下側のセルの典型的な構造を示す。p 型ゲルマニウム(Ge)基板 1 が準備され、このデバイスの第 1 の p - n 接合部 2 が、III-V 族の半導体材料の層 3 をこのゲルマニウム基板の上に成長させ、これら 2 つの層は界面 8 で接している。この層 3 は、この技術分野では核形成層と呼ばれている。プロセス中に用いられる高い温度では、V 族の原子は、この核形成層 3 から界面を通過してゲルマニウム基板に拡散し、ゲルマニウムの表面の下の位置で p - n 接合部 2 を形成する。V 属の原子は、ゲルマニウム中で n 型のドーパントとして機能するので、これらが充分な濃度で拡散すると n 型領域 4 が形成され、この接合部が形成される。（n 型領域 4 のもう一方の境界は、当然ながら III-V 族の材料と IV 族の材料との間の界面 8 である。）III-V 族の層 3 は、n 型であるので、これと IV 族の n 型領域 4 との間は低抵抗のコンタクト部となっている。V 族の原子の拡散深さのコントロールは、p - n 接合部の品質を決定する重要な点であり、浅い接合部であることが好ましい。拡散は、さらなる他の半導体層 5 の核形成層 3 と共にこれらの成長およびアニーリング（および他の処理）の温度および時間でコントロールされる。このさらなる半導体の層 5 は、スペクトルの異なる部分を吸収するための 1 つ以上のさらなる p - n 接合部を形成するために設けられる。図 1 のようなボトムセルを有する多接合太陽電池の例は、特許文献 1 および 2 に記載されている。

20

**【0 0 0 4】**

非特許文献 1 は、1990 年に発行されている。非特許文献 1（論文）の著者は、フォトトランジスタおよび空孔に基づいてドーピングを変化させた構造に興味をもっており、この論文自体は、ゲルマニウムで過成長したガリウム - 硅素エピタキシャル層で形成されたダイオードの研究について論じている。この基本的なダイオードは、マイクロプラズマによって助長される、低品質な試料の非均質性によって引き起こされ、マイクロプラズマ

40

50

によって助長される絶縁破壊により損傷されるが、著者らはこれは GaAs の空孔（これは逆に Ga および As の Ge への外方拡散で生じる）によると示唆している。これを回避するために厚さ 10 nm の疑似モルフィックなシリコンの中間層が設けられた。（ゲルマニウムは p 型であり、 Ga が  $5 \times 10^{18} \text{ cm}^{-3}$  の濃度でドープされた。接合部での GaAs は、これより低く、シリコンを用いて  $5 \times 10^{16} \text{ cm}^{-3}$  の濃度にドープされた。）とりわけこれは所定の深さとなるようにコントロールされてよい。

#### 【0005】

太陽電池セルは、電力を発生するのに用いられ、好ましくは太陽光で発生される。これらの太陽電池セルには、太陽光が直接照射され、または効率を改善するための、太陽光をセルに集光する集光器を用いて照射される。

10

#### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【特許文献 1】米国特許第 6 3 8 0 6 0 1 号

【特許文献 2】米国特許公開公報 2 0 0 2 / 0 0 4 0 7 2 7 号

##### 【非特許文献】

##### 【0007】

【非特許文献 1】論文 "Si as a diffusion barrier in Ge / GeAs heterojunctions"、著者 S. Strite, M.S.Unlu, K. Adomi, and H. Morkoc (Appl. Phys Lett. 56(17))

20

##### 【発明の概要】

##### 【0008】

本発明によれば、半導体材料が準備され、この半導体材料は、シリコン以外の I V 族半導体材料層と、少なくとも 1 種類の I II I 族の原子と少なくとも 1 種類の V 族の原子とから生成され、I V 族半導体層との界面を有する I II I - V 族半導体材料層と、I II I - V 族半導体層と I V 族半導体層の間の界面か、または、この界面から離間した、I V 族半導体層か、または I II I - V 族半導体層におけるシリコン層と、この界面と接しあつ I II I - V 族半導体層を形成する、少なくとも 1 種類の V 族原子でドープされた I V 族半導体層における V 族でドープされた n 型の領域と、を備える。

##### 【0009】

このシリコン層は、V 族原子が I V 族層へ拡散することを（これを低減することによって）コントロールし、これによって I V 族層のドーピングをその深さおよび濃度に関してコントロールする。さらに、Si 層の厚さを変えることにより、異なる条件でドーピングを変化させることができる。このようにして、I V 族層のドーピングは、所望にコントロールすることができる。

30

##### 【0010】

この I V 族半導体層における、V 族でドープされた n 型の領域の部分は、シリコン層の特定の側にあり、このシリコン層の反対側にある I II I - V 族半導体層部分を形成するものの少なくとも 1 種類の V 族原子でドープされてよい。

##### 【0011】

このシリコン層の特定の側にある I V 族半導体層の部分をドーピングする、V 族原子の少なくとも一部は、このシリコン層の反対側にある I II I - V 族層の部分からもたらされてよい。

40

##### 【0012】

I V 族半導体層における、V 族でドープされた n 型領域は、界面と接する I II I - V 族半導体層の領域を形成する V 族原子の少なくとも 1 種類でドープされてよい。

##### 【0013】

半導体層における V 族でドープされた領域は、I V 族の層における p 型領域を有する p - n 接合部となってよい。

##### 【0014】

界面における I II I - V 族材料は、n 型であってよい。

50

## 【0015】

このIII-V族材料層は、n型であってよい。

## 【0016】

代替として、IV族層においてV族でドープされた領域とIII-V族層とは、界面におけるトンネルダイオードを形成してよい。界面におけるIII-V族材料は、p型でドープされていてよい。

## 【0017】

IV族半導体材料層は、ゲルマニウムであってよく、またはシリコン-ゲルマニウムであってよく、またはシリコン-ゲルマニウム-錫であってよい。

## 【0018】

III-V族材料は、Al, Ga, Inの内の1つ以上のIII族原子を含んでよく、P, As, Sb, Biの内の1つ以上のV族原子を含んでよい。このIII-V族材料は、InGaAsP, AlGaAs, AlGaAsP, GaAs, GaAsP, AlAs, InGaP, InGaAs, AlInGaAs, AlInGaPからなるグループから選択された材料を含んでよい。

## 【0019】

IV族層は、シリコン層とIII-V族半導体層との間に、IV族のエピタキシャル半導体層を備えてよい。

## 【0020】

III-V族半導体層は、シリコン層とIV族半導体層との間に、III-V族のエピタキシャル半導体層を備えてよい。

## 【0021】

IV族半導体層は、基板層と、この基板層の上に成長したエピタキシャル層とを備えてよい。

## 【0022】

好ましくは、シリコン層は7.5以下かまたは3原子層以下の厚さを有する。このシリコン層は、1原子層以下であってよく、あるいは1原子層未満であってよい。

## 【0023】

界面と接するIII-V族半導体層のドーピング濃度は、1cm<sup>3</sup>当りの原子数が1×10<sup>17</sup>個より多くてよく、または1cm<sup>3</sup>当りの原子数が1×10<sup>18</sup>個より多くてよく、または1cm<sup>3</sup>当りの原子数が1×10<sup>18</sup>個と5×10<sup>18</sup>個の間であってよい。

## 【0024】

IV族半導体層における、V族でドープされたn型領域のV族原子のドーピング濃度は、1cm<sup>3</sup>当りの原子数が1×10<sup>17</sup>個より多くてよく、または1cm<sup>3</sup>当りの原子数が1×10<sup>18</sup>個より多くてよく、または1cm<sup>3</sup>当りの原子数が6×10<sup>18</sup>個より多くてよい。

## 【0025】

V族原子でドープされていないIV族半導体層のドーピング濃度は、1cm<sup>3</sup>当りの原子数が4×10<sup>18</sup>個より少なくてよく、または1cm<sup>3</sup>当りの原子数が5×10<sup>16</sup>個と2×10<sup>18</sup>個との間であってよく、または1cm<sup>3</sup>当りの原子数が1×10<sup>17</sup>個と1×10<sup>18</sup>個との間であってよい。

## 【0026】

本発明による半導体材料は、第1のIII-V族層との界面に対しIV族層の反対側にある、IV族半導体層との界面を有する第2のIII-V族半導体材料の層を備えてよく、この第2のIII-V族半導体層とIV族半導体層との間の界面に第2のシリコン層を備えてよい。

## 【0027】

また本発明は、本発明による半導体材料を備えた、光を吸収する光起電デバイスを提供する。

## 【0028】

10

20

30

40

50

この光起電デバイスは、複数の光吸収セルを備えてよく、これらの中1つ以上は本発明による半導体材料を備えている。この複数のセルの1つは、この複数のセルの他の1つと異なるバンドギャップを有してよい。この光吸収セルは、光を吸収するp-nダイオードであってよい。この光起電デバイスは、太陽電池であってよい。

#### 【0029】

本発明は、さらに半導体材料を製造する、以下のステップを含む方法を提供する。

- シリコン以外のI-V族半導体材料層を準備するステップ。

- 少なくとも1種類のI-II族の原子と少なくとも1種類のV族の原子とから生成され、I-V族半導体層との界面を有するI-II-I-V族半導体材料層を設けるステップ。

- I-II-I-V族半導体層とI-V族半導体層との間の界面か、または、この界面から離れた、I-V族半導体層か、またはI-II-I-V族半導体層においてシリコン層を設けるステップ。

10

- I-II-I-V材料層からのV族原子をシリコン層を通じてI-V族材料にドープし、界面と接するI-V族半導体層において、V族でドープされたn型領域を形成するステップ。

#### 【0030】

V族原子の拡散は、I-V族層におけるp-n接合部を形成してよい。

#### 【0031】

V族原子の拡散は、既にn型となっているI-V族層の領域で行われてよく、高濃度のn型ドーパントを有する、n型ドープ領域が形成される。

#### 【0032】

I-II-I-V族層は、I-V族層の上あるいはシリコン層の上に直接成長されてよい。

20

#### 【0033】

本発明による材料あるいは、本発明の方法によって製造された材料は、以下のステップによる太陽光を用いた発電に使用される。

- これらの材料で形成された太陽電池セルを準備するステップ。

- この太陽電池に太陽光を照射するステップ。この方法は太陽電池に照射するための太陽光を集光するステップを備えてよい。

#### 【0034】

本発明の第2の態様においては、半導体層から形成された2つ以上の光吸収セルを有する多接合光起電デバイスが提供され、このデバイスは以下のものを備える。

30

- シリコンゲルマニウムまたはシリコンゲルマニウム錫の材料からなる第1のセル。

- シリコンゲルマニウム錫からなる第2のセル。

ここで第1のセルのシリコンゲルマニウムまたはシリコン-ゲルマニウム錫、および第2のセルのシリコンゲルマニウム錫は、ガリウム砒素に格子整合されている。

#### 【0035】

多接合光起電デバイスは、さらにガリウム砒素材料のセルを備えてよい。

#### 【0036】

この多接合光起電デバイスは、さらにガリウム砒素に格子整合されたインジウムガリウム焼のセルを備えてよい。

#### 【0037】

この多接合光起電デバイスは、さらに、ガリウム砒素に格子整合されたアルミニウムインジウム砒素のセル、あるいはガリウム砒素に格子整合されたアルミニウムインジウムガリウムリンのセルを備えてよい。

40

#### 【0038】

この多接合光起電デバイスは、ガリウム砒素の基板を備えてよく、セルの半導体層はこの基板の上に格子整合されている。代替として、この多接合光起電デバイスは、ガリウム砒素に格子整合された基板を備えてよく、半導体層はこの基板の上に格子整合されている。

#### 【0039】

この光起電デバイスは、太陽電池であってよい。

50

**【0040】**

好ましくは、第1のセルはシリコンゲルマニウム材料からなる。

**【0041】**

また本発明のこの第2の態様は、以下のステップを備える多接合光起電デバイスの製造方法を提供する。

- ガリウム砒素の基板またはガリウム砒素に格子整合された他の材料を準備するステップ。

- シリコンゲルマニウムまたは上記基板に格子整合されたシリコンゲルマニウム錫からなる第1のセルを成長させるステップ。

- この第1の光吸收セルに格子整合されたシリコンゲルマニウム錫からなる第2のセルを成長させるステップ。 10

**【0042】**

この方法は、ガリウム砒素のセルを成長させるステップを備えてよい。

**【0043】**

この方法は、ガリウム砒素に格子整合されたインジウムガリウムリンのセルを成長させるステップを備えてよい。

**【0044】**

この方法は、ガリウム砒素に格子整合されたアルミニウムガリウム砒素の光吸收層を成長させるステップを備えてよい。 20

**【0045】**

この方法は、ガリウム砒素に格子整合されたアルミニウムインジウムガリウム燐のセルを成長させるステップを備えてよい。

**【0046】**

この方法は、2つの隣接する上記のセルの間に少なくともさらにもう1つの層を設けるステップを備えてよく、この少なくともさらにもう1つの層は、ガリウム砒素に格子整合されている。

**【0047】**

この方法は、基板を除去するステップを備えてよい。

**【図面の簡単な説明】****【0048】**

本発明の実施例を、これに付随する以下の図を参照して説明する。 30

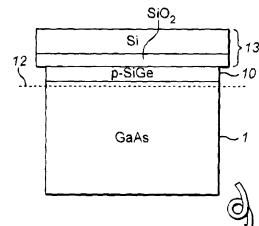

【図1】公知の多接合光起電デバイスセルの下側のセルの半導体層の断面を示す図である。

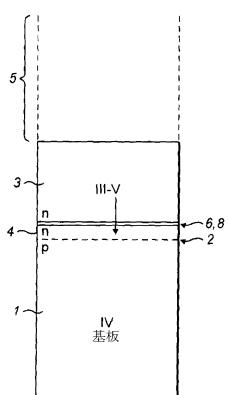

【図2】本発明による多接合光起電デバイスセルの第1の実施例の下側のセルの半導体層の断面を示す図である。

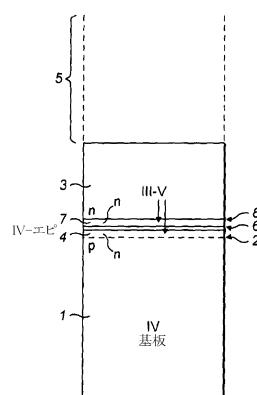

【図3】本発明による多接合光起電デバイスセルの第2の実施例の下側のセルの半導体層の断面を示す図である。

【図4】本発明による多接合光起電デバイスセルの第3の実施例の下側のセルの半導体層の断面を示す図である。

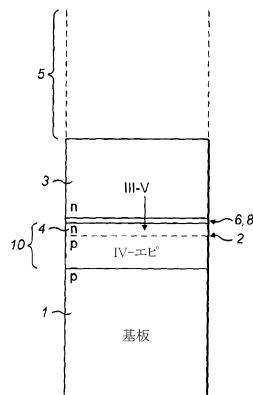

【図5】本発明による多接合光起電デバイスセルの第4の実施例の下側のセルの半導体層の断面を示す図である。 40

【図6】本発明による多接合光起電デバイスセルの第5の実施例の下側のセルの半導体層の断面を示す図である。

【図7】本発明による多接合光起電デバイスセルの第6の実施例の下側のセルの半導体層の断面を示す図である。

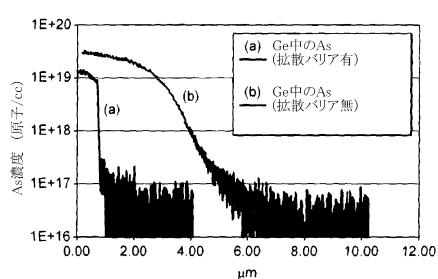

【図8】本発明によるシリコン層を有する半導体層構造とこのシリコン層を有しない半導体層構造とを比較する2次イオン分析図である。

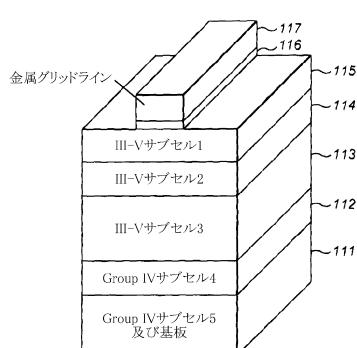

【図9】本発明によるデバイスのもう1つの実施例を示す図である。

【図9A】図9Aは、図9のデバイスのセルにおける本発明の使用の実施例を示す図である。 50

【図 9 B】図 9 B は、図 9 のデバイスのセルにおける本発明の使用の実施例を示す図である。

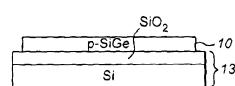

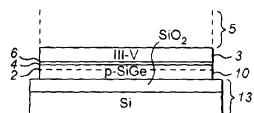

【図 10 A】基板間に SiGe 層のトランスファ層を有する本発明の実施例を形成する方法を示す図である。

【図 10 B】基板間に SiGe 層のトランスファ層を有する本発明の実施例を形成する方法を示す図である。

【図 10 C】基板間に SiGe 層のトランスファ層を有する本発明の実施例を形成する方法を示す図である。

【図 10 D】基板間に SiGe 層のトランスファ層を有する本発明の実施例を形成する方法を示す図である。 10

【図 11】本発明のデバイスを用いたもう 1 つの実施例を示す図である。

【図 11 A】本発明の方法の使用の実施例を示す図である。

【図 11 B】本発明の方法の使用の実施例を示す図である。

【図 11 C】本発明の方法の使用の実施例を示す図である。

【図 11 D】本発明の方法の使用の実施例を示す図である。

【図 12】本発明を用いたトンネルダイオードの実施例を示す図である。

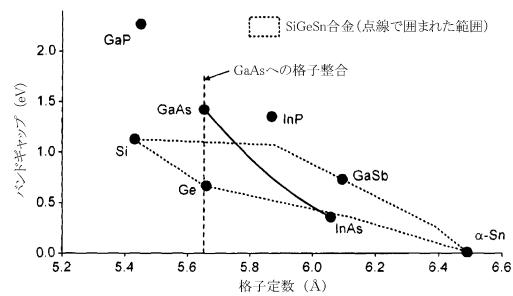

【図 13】SiGeSn 合金のバンドギャップおよび格子定数を示すグラフであり、GaAs および Ge に格子整合され得ることを示すとともに、これにより生じるバンドギャップを示している。 20

#### 【発明を実施するための形態】

##### 【0049】

本発明による光起電デバイスの第 1 の実施例が図 2 に示されている。この図は、点線で示す 1 つ以上の p - n 接合部を形成する半導体層 5（もしこれが存在すれば）をさらに含む、下側のセルの層の断面を示す。全般的に、この構造は図 1 に示すものと類似している。たとえばゲルマニウムである、p 型の III-V 族半導体基板 1 が、この基板上に成長された n 型の III-V 族半導体の層 3 と共に準備され、これら 2 つの層は再び界面 8 で面している。また、ここでも V 族原子は III-V 族層 3 から界面 8 に隣接する n 型領域 4 を形成する III-V 族層に拡散し、これによりその領域が残りの III-V 族材料の p 型部分と面するような p - n 接合部 2 を生成する。しかしながら、まず薄いシリコン層 6 が、層 3 と III-V 族基板 1 との間に設けられる。（特定の III-V 族半導体材料の可能性については後述するが、材料はシリコンそのものではない。III-V 族材料の可能性についても後述する。） 30

##### 【0050】

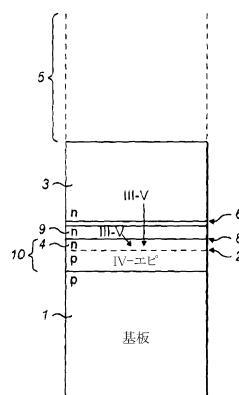

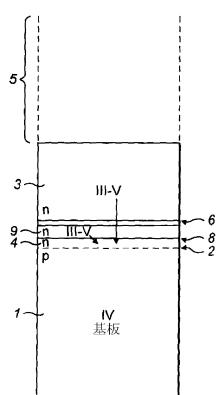

図 3 は、第 2 の実施例を示し、ここでは III-V 族材料の核形成層 3 が Si 層 6 の上に成長される前に、まず III-V 族半導体（シリコン以外）のエピタキシャル層 7 がこの Si 層の上に成長される。通常この層 7 は、この層が成長する時に最初に p 型または n 型でドープされてよい。

##### 【0051】

これら 2 つの実施例では、シリコン層 6 は、V 族原子が層 3 から III-V 族材料に拡散することをコントロールしている。このシリコンは、V 族の拡散に対するバリヤとして機能し、デバイスを形成するのに使用される同じプロセス条件の組み合わせでは、この p - n 接合部 2 は浅くなる。すなわちこの p - n 接合部の位置は、III-V 族半導体と核形成層との間の界面 8 にさらに近くなる。このバリヤは完全ではない。このバリヤは、V 族が V 族原子の供給源である III-V 族の材料から、Si バリヤの反対側にある III-V 族材料への拡散を排除するというよりむしろ低減するものである。このバリヤの厚さの設定は、p - n 接合部 2 の深さのコントロールに用いることができる。 40

##### 【0052】

これら 2 つの実施例において、バリヤ 6 の好ましい厚さはシリコンの 3 単原子層（7.5）以下である。実際には、これは完全な 1 单原子層より薄くともよい。シリコン層には張力が発生する（これはシリコン層が III-V 族半導体の格子定数と整合しようとするためである）ので、この 3 原子单層は、シリコン層の好ましい最大厚である。上記の限界厚の 50

上では、転位がシリコンにおける張力を緩和するように形成され、これらの転位はデバイス性能に対し不利となり得る。また、3原子単層までの範囲は、光起電デバイスに好適な接合深さとなる。

#### 【0053】

第2の実施例(図3)では、IV族のエピ層7の厚さは、好ましくはV族原子がデバイスのプロセス中に、IV属半導体材料の材料を拡散通過する距離を越えないようにすべきである。これはこの距離を越えると、Siバリヤを横断するV族原子が極小となるからである。通常この距離は1μm未満であり、使用されるV族種およびデバイスを処理するステップの温度に依存する。

(なお、図3の実施例に関し、通常p-n接合部2は、シリコンバリヤ6のIII-V層側と反対の側にあり、本発明は通常バリヤ6がV族原子の拡散を制限するが、このバリヤを通過してIV族材料をn型に変換するには十分でない場合を含むものであり、このp-n接合部は、このバリヤかまたはこのバリヤの近傍<sup>\*</sup>にある。( \* p-n接合部はもちろん数単原子層のバリヤより大きい領域を有している。))

#### 【0054】

図4および5は、それぞれ第1および第2の実施例と同じ層(図2および3)を有する第3および第4の実施例を示すが、IV族半導体のp型エピタキシャル層10は、まずシリコン層6およびIII-V層3が成長される前に設けられる。この特定の実施例では、エピ層10は、基板1の上に成長されるが、中間層を有することが可能である。エピ層として層10を有することは、またIV族半導体における接合部のドーピングの厚さおよびプロファイルを正確にコントロールするのに役立つ。好ましくは、ここに示すように、層10は基板1(またはIV族材料の中間層)におけるよりもむしろこのIV族層でp-n接合部2がエピ層を形成するのに十分な厚さであるが、前者を排除するものではない。なお、しかしながら、IV族エピ層10は他の材料の上でも成長され得るので、基板1は必ずしもIV族である必要はない。

#### 【0055】

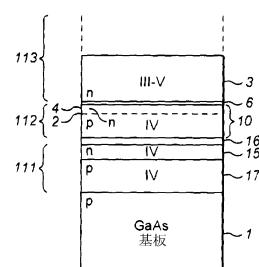

図6および7は、それぞれ第1および第3の実施例(図2および4)と同じ層を有する第5および第6の実施例であるが、シリコン層6およびIII-V族の主層3が成長される前に、まず最初にIII-V族半導体材料のn型エピタキシャル層9が設けられる。ここでもシリコン層はV族原子の拡散をコントロールするバリヤ6として機能し、V族原子が層3からこのバリヤ6の反対側にあるIV族材料に拡散することをコントロールする。IV族材料はまた、層9からのV族原子によってもドープされる。このSiバリヤは、このバリヤの他の側のIII-V族層からのIV族層へのドーピングレベルに対し顕著な差を設けるために存在するのであり、このためこのIII-V族エピ層9は、デバイスのプロセス条件下V族原子が層3から層9を通って拡散するような距離より薄くなるはずである。

#### 【0056】

p-n接合部が形成される材料として用いられるIV族半導体材料の例はゲルマニウムである。ゲルマニウム基板もまた容易に入手可能である。基板としてのゲルマニウムの方位は僅かに(100)および(111)からずれていることが好ましい。(正確な結晶面からずらされた基板は従来技術で知られている。)

#### 【0057】

ゲルマニウム以外のIV族半導体が使用されてもよく、シリコン-ゲルマニウムおよびシリコン-ゲルマニウム-錫のように用いてよい。SiGeおよびSiGeSnは、ベース基板としては入手できないが、GaAsに格子整合して成長させることができる。このようなSiGeまたはSiGeSnは、本発明で用いる前に、元のGaAs基板から取り外して、より安価な基板にとりつけてよい。このプロセスの例を以下に後述する。少なくとも0.04に達する成分量xを有し、場合によってはx=0.06以上であるSi<sub>x</sub>Ge<sub>1-x</sub>が用いられてよいが、好ましくはxは0.01×0.03の範囲である。これに対応したSi<sub>x</sub>Ge<sub>1-x</sub>のGaAsとの格子不整合は、約x=0.018における格子

10

20

30

40

50

整合条件から離れる方向で  $\times$  の 0 . 0 1 の変化に対し約 0 . 0 4 %となる。図 13 は、 $\text{SiGeSn}$  合金のバンドギャップおよび格子定数を示すグラフであり、 $\text{SiGeSn}$  のバンドギャップ範囲 0 . 6 6 - 1 . 1 eV で  $\text{GaAs}$  に格子整合され得ることを示している。これはまた  $\text{SiGeSn}$  が  $\text{Ge}$  に格子整合され得ることを示し、 $\text{Ge}$  の格子定数が極めて  $\text{GaAs}$  の格子定数に近いため、 $\text{SiGeSn}$  が  $\text{Ge}$  に格子整合され得るバンドギャップ範囲は、上記の  $\text{SiGeSn}$  の  $\text{GaAs}$  への格子整合の場合と類似している。 $\text{SiGeSn}$  は、 $\text{Si}$  の  $\text{Sn}$  に対する比が約 4 : 1 のところで  $\text{GaAs}$  に格子整合される。たとえば  $\text{Si}$  の割合が 2 %で、 $\text{Sn}$  の割合が 0 . 5 %のところでは、これらは  $\text{GaAs}$  に格子整合された場合より大きなバンドギャップをもたらし、 $\text{Si}$  の割合が 8 %で、 $\text{Sn}$  の割合が 2 %のところでは、このバンドギャップは大きくなり、これらの割合がさらに大きくなると、このバンドギャップはさらに大きくなり、たとえば限界値である 80 %の  $\text{Si}$  および 20 %の  $\text{Sn}$  では、この材料のバンドギャップは約 1 . 1 eV となる。

## 【0058】

従来技術で知られているように、核形成層 3 は、 $\text{InGaAs}$  や  $\text{InGaP}$  のような、種々の III - V 族材料から製造することができる。他の材料には、 $\text{InGaAsP}$ ,  $\text{AlGaAs}$ ,  $\text{AlGaAsP}$ ,  $\text{GaAs}$ ,  $\text{GaAsP}$ ,  $\text{AlAs}$ ,  $\text{InGaP}$ ,  $\text{InGaAs}$ ,  $\text{AlInGaAs}$ ,  $\text{AlInGaP}$ , 等がある。これらはまた、 $\text{Sb}$  ( または  $\text{Bi}$  でもよい ) を材料の V 族原子 ( の 1 つ ) として含むようなものを含む。従来技術で知られているように、これらの材料の殆どは、ゲルマニウム、シリコン、またはシリコン - ゲルマニウム、シリコン - ゲルマニウム - 錫の少なくとも 1 つに格子整合あるいはほぼ格子整合されて成長され得る。

## 【0059】

これらの材料の多くは、V 族原子として  $\text{As}$  および / または  $\text{P}$  を含んでいる。なお、 $\text{As}$  および  $\text{P}$  は共に III - V 族材料から IV 族材料に拡散し、IV 族材料に対し、少なくとも  $\text{Ge}$  に対しては  $\text{As}$  は  $\text{P}$  よりも遠くまでかつ速く拡散する。2 つ以上の III - V 族エピタキシャル層があるところ ( たとえば図 6 および 7 の実施例はエピタキシャル層 3 および 9 を有する ) では、これらの層が、ベース材料を形成し、かつまた堆積中に行われるドーピングにおける III - V 族および V 族の原子に関して同じ組成を有していることが好ましい。しかしながら、異なる組成も可能であり、これは IV 族領域でのドーピングプロファイルをコントロールするのに有用である。実際、層中の異なる組成もまた除外されるものではない。

## 【0060】

同様に、2 つ以上の IV 族エピタキシャル層があるところ ( たとえば図 5 の実施例 ) では、上述のたとえば IV 族材料の堆積中における V 族の拡散の前のこれらの層が、ベース材料を形成し、かつまた堆積中に行われるドーピングにおける IV 族の原子に関して同じ組成を有することが好ましい。しかしながら、異なる組成も可能である。実際、層中の異なる組成および / またはドーピングもまた除外されるものではない。

## 【0061】

しかしながら、従来技術でエピタキシャル層に対してしばしば行われるように、このエピ層および基板が同じベース材料であった場合でも、IV 族エピ層および基板 ( 図 4 , 5 、および 7 ) では異なるドーピングであることが好ましい。

## 【0062】

上記の  $\text{GaAs}$  上に成長された  $\text{SiGe}$  および  $\text{SiGeSn}$  の例で示唆されているように、IV 族層 10 の材料は、非 IV 族材料の基板の上に成長されることができる。

## 【0063】

使用可能または好ましい幾つかのドーピング濃度は以下の通りである。IV 族層との界面にある III - V 族層では、このドーピング濃度は通常  $1 \text{ cm}^3$ 当たりの原子数が  $1 \times 10^{17}$  個であり、さらに好ましくは  $1 \text{ cm}^3$ 当たりの原子数が  $1 \times 10^{18}$  個であり、さらにもっと好ましくは  $1 \text{ cm}^3$ 当たりの原子数が  $1 \times 10^{18}$  個と  $5 \times 10^{18}$  個の間である。

IV 族半導体層におけるドーピングを形成する、拡散された V 族原子の数は、通常  $1 \text{ cm}^3$

10

20

30

40

50

<sup>3</sup>当りの原子数が  $1 \times 10^{17}$  個より多く、好ましくは  $1 \text{ cm}^3$  当りの原子数が  $1 \times 10^{18}$  個より多く、そして  $1 \text{ cm}^3$  当りの原子数が  $6 \times 10^{18}$  個より多くてよい。IV族層の残りの（V族原子が顕著に拡散していない）部分については、ドーピング濃度は、通常  $1 \text{ cm}^3$  当りの原子数が  $4 \times 10^{18}$  個より小さく、好ましくは、 $1 \text{ cm}^3$  当りの原子数が  $5 \times 10^{16}$  個と  $2 \times 10^{18}$  個の間であり、さらに好ましくは  $1 \times 10^{17}$  個と  $1 \times 10^{18}$  個の間である。

#### 【0064】

このシリコン層6および他の層は、従来の技術を用いて成長させることができる。以下のように幾つかの方法は可能である。

#### 【0065】

たとえばこのシリコン層は、III-V族層のエピタキシーに用いられる従来のMOCVD反応炉（このような装置は多接合光起電デバイスのIII-V族のエピタキシに従来より用いられている）で成長させることができる。（IV族半導体材料の例として）ゲルマニウム基板は、直接MOCVD反応炉に設置でき、またシリコンおよびIII-V族層と共に成長させるのに使用することができるので、この方法は、とりわけ第1の実施例（図2）に適合しているが、この実施例に限定するものではない。シリコンはこのような反応炉においてドーパント源として用いられており、したがって、直接ゲルマニウム基板にシリコンを堆積するために、III-V族核形成層を堆積する前に、シリコンを堆積することができる。

#### 【0066】

シリコン層6は、ゲルマニウム、シリコンおよびシリコン-ゲルマニウムまたはシリコン-ゲルマニウム-錫を成長させるCVD堆積装置でエピタキシャル成長させることができる。ゲルマニウム等の基板は、まずこの装置に設置され、またさらにシリコンおよびGeエピタキシャル層6および7を成長させることができるので、この方法は、とりわけ第2の実施例（図3）に適合しているが、この実施例に限定するものではない。次に加工対象物は、MOCVD反応炉（好ましくはマルチチャンバシステム（cluster tool arrangement）を用いてゲルマニウムエピタキシャル層7が清浄なままとなるようにする）に移動されてIII-V族層3が堆積される。

#### 【0067】

MBEをIII-V族材料またはシリコンの堆積に用いてもよい。

#### 【0068】

図8は、2次イオン質量分析器を用いて、InGaAs/Ge接合部を有する多接合タンデムセルデバイスの試料で、直接界面に本発明によるシリコン層を有するボトムセル（a）とこれを有しないボトムセル（b）とを比較してプロットしたものである。縦軸は、GeにおけるAs原子の濃度を  $1 \text{ cm}^3$  当たりの原子数で示しており、横軸は、Ge層の深さを  $\mu\text{m}$  で示している。このグラフは、シリコン層を有する場合は、InGaAs層に拡散するAsドーパント濃度がGe層の  $1 \mu\text{m}$  の深さに閉じ込められていることを示しており（（a））、これに対してSi層を用いないコントロールの場合（ただし他のプロセス条件は同一）は、As原子が約  $4 \mu\text{m}$  を貫通していることを示している（（b））。さらに、As原子の濃度は、Si層を有している試料では低くなっている。これらの所見は、Si層がAsの拡散のバリヤとして機能することを示している。同様の結果は、異なるV族原子を有するIII-V族半導体材料を用いても得られる。

#### 【0069】

本発明によるシリコン層を有する三重接合光起電構造の試料は、シリコン層を有しない場合に比べて  $1 \text{ sun}$  で照射された場合の最大出力および開路電圧（ $V_{OC}$ ）を増加させることに有効であると評価されている。

#### 【0070】

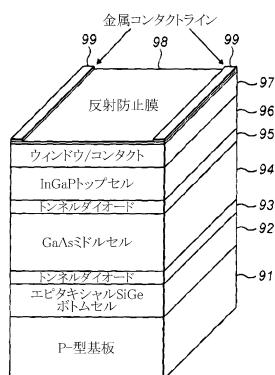

図9は、本発明を用いた、多接合太陽電池のもう1つの実施例を示し、ここでは全てのセルが示されている。この図は本発明のデバイスのセルのタンデム構成を示している（各々のセルは様々な半導体層で出来ているが、これら詳細は示されていない）。このデバイ

10

20

30

40

50

スは、GaN基板91からスタートし、本発明に基づいて、この基板にSiGeセル92が成長される（したがってp-n接合部、Si拡散バリヤ層およびこの上のドーピングを行うIII-V族層（たとえばGaInP）を有するSiGe層を備えるが、これらのいずれも図のセル92には詳細には示されていない）。この上にGaNセル94およびInGaNセル96が設けられる。トンネルダイオード93および95はそれぞれ、SiGeセルとGaNセルとの間、およびGaNセルとInGaNセルとの間でセル間の抵抗を低減する。最後のウインドウ層97は、デバイスを保護するが、光入射を可能とし、デバイスの金属コンタクトライン99は、デバイスで生成された電流を集電する。最後に反射防止膜98が、このウインドウを被覆する。

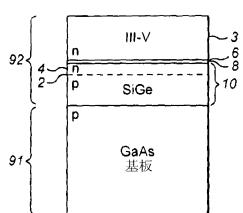

## 【0071】

10

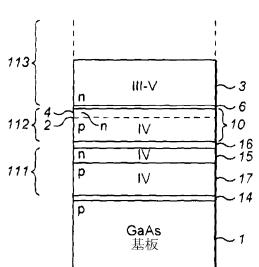

図9Aは、図9のボトムセル92および基板91の例を詳細に示す（ただしもちろんこの例を使用することは、図9の特定な実施例に限定することではない。）。この例は図4の実施例の構造を有し、GaNの基板1を有している。この上にGaNに概ね（または正確に）格子整合されたp型SiGeのエピ層10が成長される。この上にSi拡散バリヤ6が成長され、この上にIII-V族核形成層3が成長され、これもまた概ね（または正確に）SiGeに格子整合される。V族原子は、層3の堆積およびこれに続く処理のステップの条件下で、バリヤ6でコントロールされて層3からSiGeに拡散し、このSiGeをドーピングして界面8に隣接したn型領域4を形成し、これによりSiGe層10にp-n接合部2が形成される。このSiGe層10の同様な例として、代わりにこの層はSiGeSnで形成される。

20

## 【0072】

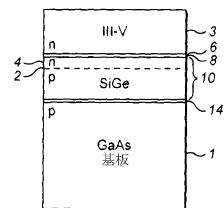

このデバイスでは、GaN基板1からのV族原子を用いたSiGe（またはSiGeSn）のドーピングに、潜在的な問題がある。すなわちAs原子によってSiGeがp型からn型にオーバードーピングされて、SiGe層10と基板1との間の界面の近傍でp-n接合部を形成するのである。

## 【0073】

この対策は以下の2つの方法で行われる。第一の方法では、SiGeがp型のままであるように、拡散を抑えるように、もう1つのSiバリヤ14が、界面に設けられてよい。（このSiバリヤには、7.5または3原子層の厚さが好ましい。この制限は、上記の試料のように、SiがGeに良く似たGaN基板の格子定数に対して成長されることによる。）

30

## 【0074】

この問題を回避するもう1つの方法は、以降の処理のステップが実行される前に、SiGeを異なる基板の上にトランスファすることである。このトランスファは、以下に説明するように、発明者らの国際特許出願の国際公報WO2010094919で2010年8月26日に公開されており、この内容は本発明に組み込まれるものである。

## 【0075】

この方法では、Geを含む先駆体（たとえばGeH<sub>4</sub>, GeCl<sub>4</sub>, 等）およびSiを含む先駆体（たとえばSiH<sub>4</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, SiHCl<sub>3</sub>, ジシラン, 等）のキャリヤガスとの混合ガスを用いて、SiGe層10をGaN基板1の上にエピタキシープロセスを用いて格子整合されて成長させることができる。このSiGe層10は、これに限定するものではないが、ジボランを含む、ガス状または固体のドーピング源を用いて処理中（in-situ）にドープされてよい。この層10は、たとえば、大気圧または1~1000 Torrに減圧され、温度350~800で成長されてよい。GaNの基板の範囲として、p型, n型および準絶縁体を含むものが用いられてよく、ウェーハはエピタキシーの前にこの処理とは別に（ex-situ）または処理中にクリーニングされてよい。SiGe層10の結晶度特性は、たとえば格子整合の検査は、X線回析技術を用いて測定されてよく、層の厚さは通常角度可変のエリプソメータ分光を用いて測定されてよいが、また他の方法も可能である。

40

## 【0076】

50

このプロセスでは、G a A s 基板とS i G e層10との間の材料組成交換が、良好なエッティング停止部として機能するヘテロ界面を生成し、G a A s 基板が都合よく除去され、S i G e層10の滑らかな表面が的確に生じることを可能にする。G a A s 基板の一部は、もしこれが速やかなあるいは容易または安価な製造プロセスであれば、機械的手段によって除去されてよい。たとえば、G a A s 基板が500μm厚であれば、約400μmは、研磨によって除去されてよく、これによってG a A s 材料はさらに容易に回収されて再利用することができる。最後の100μmは、選択的ウェットエッティングにより除去されてよい。

#### 【0077】

この方法を使用して生成される光起電セル構造は、基板の厚みが取り除かれているために、軽量にすることができる。これはとりわけ宇宙分野での応用に重要である。適合する可撓性、熱特性、または他の所望の機械的または電気的特性を有する他の分野にも提供することができる。基板をヒートシンクに交換すると、基板は熱流を低減するように機能しないので、デバイスからの熱伝導をさらに効率的にすることができます。このヒートシンクまたは他の金属ベース層は、そのままデバイス底部への導電性電極として機能する。

10

#### 【0078】

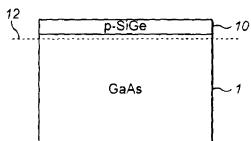

図10A～10Dに1つの特定の方法を示す。G a A s 基板1からスタートし、上記で説明したように、また図10Aに示すように、S i G e層10がエピタキシャル成長される。次にG a A s 基板以外の薄層以外を除去するためにトランスファ技術が用いられる。この層トランスファは、スマートカット(Smart Cut；登録商標)等の特許の剥離技術を用いて行われ、G a A s 基板の開裂面12が丁度S i G e層10の下に形成される。この開裂面12は、イオンビーム打ち込み技術を用いて、水素またはヘリウム原子を、このビームエネルギーで規定される正確な深さ、たとえば1.5μmまでの深さに堆積させて形成されてよく、本発明の条件ではS i G e層の厚さがほぼこの厚さである場合にこの技術が実用的となる。

20

#### 【0079】

次に代替ベース13がS i G e層10に貼り付けられる。図10Bに示すように、この代替ベースは、S i G e層がS i O 2層に貼り付けられるように、酸化されたシリコンウェーハであってよい。ただし他のベースとして上述のような金属ヒートシンクが用いられてもよい。使用可能な他のベースの一部としては金属製、ガラスおよび半導体のベースがあり、これらはそれ自体が既に、金属、半導体および絶縁体の材料から選択された2つ以上の層を備えてよく、光起電接合部のような能動素子を1つ以上有していてよい。次にこのG a A s バルク基板は、この構造体から分離され、僅かに残ったG a A s 層が、たとえば選択ウェットエッティングにより除去され、上記で説明した酸化シリコンウェーハのような代替ベースの上に、図10Cに示すようにS i G e層10が残る。次にこのデバイスの後の層、たとえばS i バリヤ6およびI I I - V族層3およびこれに続く層5が、図10Dに示すように形成される。

30

#### 【0080】

上記で説明した技術の変形例の1つには、下側のS i G e層内で、基板の界面の真上の開裂面を形成することがある。層トランスファの後で、このトランスファされたS i G eは、さらなる必要な処理のために既に露出されている。G a A s 基板の上に残っている残渣S i G eは、S i G eに選択的に作用しかつG a A s には作用しないウェットエッチを用いて、少なくとも部分的に除去されてよく、再使用可能なG a A s 基板が残される。

40

#### 【0081】

多種多様な異なった代替ベースが図10Dの構造に可能であり、これらはそれ自体が既に、金属、半導体および絶縁体の材料から選択された2つ以上の層を備えてよく、光起電接合部のような能動素子を1つ以上有していてよい。初期に形成されたG a A s 基板上のS i G e層は、開裂または剥離に続く残渣G a A s の正確な除去の理想的なエッティング停止部となる。

#### 【0082】

50

図11は、本発明を用いた多接合太陽電池セルのもう1つの例を示す。これは5個の太陽電池セルを示しており、ここでも全セルはタンデム型に接続されている。これらは、基板から順番に、Geセル111、もう1つのGeセル112、GaInAsセル113、AlGaInAsセル114およびAlGaInPセル115（高濃度n型コンタクト層116および金属ライン117）である。このデバイスでは、本発明はGeセル112を形成することに使用されており、このセルは上のセル113のIII-V族材料との界面を有し、Si拡散バリヤ6がセル112とセル113との間の界面に設けられるように、V族ドーパントを供給する。

#### 【0083】

図11Aは、図11のボトムセルの例111、112の例を詳細に示すが、ただしもちろんこの例を使用することは、図11の特定な実施例に限定することではない。 10

#### 【0084】

最下部のセル111は、p型のIV族基板1（たとえばGe）を有し、この上にn型のIV族エピ層（たとえばGe）が成長されて第1のp-n接合部を形成する。次のセル112への低抵抗コンタクトを設けるために、次にトンネルダイオードの層16が堆積される。この上にp型のIV族材料（たとえばGe）のエピ層10が形成され、これに続いてシリコン拡散バリヤ6およびIII-V族エピ層3が形成されて、上記の例のように、エピ層3からバリヤ6を通じて拡散されたV族原子でドープされたエピ層10のn型材料4と、IV族層10の残渣との間にp-n接合部を形成し、これによってセル112が形成される。 20

#### 【0085】

図11Bは、図11Aと類似したもう1つの例を示す。この例ではしかしながら、第1のセルは、基板を含んでいないが、基板1の上にp型で（通常は基板に格子整合されて）成長された、追加のIV族エピ層17とこの上に成長されたn型のIV族層15とから出来ており、この第1のセルのp-n接合部を形成する。

#### 【0086】

図11Bの例で示す特定の例では、基板の材料は（図11B（および図11C）に記載されているように）GaAsである。これらのIV族層は、好ましくは通常この基板に格子整合されて成長され、この例ではSiGeおよびSiGeSnである。SiGeは、格子がGaAsに整合された場合は、0.66eVのバンドギャップを与え、SiGeSnは、これより大きい、~1.1eVまでのバンドギャップを与える。もし、GaAsへの格子整合を維持したまま、0.66eVより大きい2つのバンドギャップが必要であれば、最下部のセル111およびこの次のセル112は共にSiGeSnで作ることができると、必要なバンドギャップをもたらすように互いに異なる組成で作られる。 30

#### 【0087】

図11Cは、さらにもう1つの例を示す。この例は、図11Bに類似しているが、基板がIII-V族材料である場合にIV族材料層17における好ましくないp-n接合部の形成を避けるために、追加のSi拡散バリヤ14が（図9Bの例のように）設けられている。

#### 【0088】

図11Dは、多接合太陽電池のもう1つの例を示す。図11Bおよび11Cの例のように、SiGeまたはSiGeSnの第1のセルがGaAs基板の上に設けられ、この上にSiGeSnの第2のセルが設けられている。この例では、さらに3つのセルが設けられており、これらもタンデム型で設けられている。第2のセルの上の第3のGaAsセル、この第3のセルの上の第4のInGaPセル、およびこの第4のセルの上の第5のAlInGaPセルである。これらのセルは全てGaAs基板に格子整合されている。（AlGaAsは、厳密にはGaAsと同じ格子定数を有していないが、充分に格子整合できるように殆ど同じ格子定数となっており、このAlGaAs層は、歪みが転位により開放されることが起きるような臨界厚より薄くなっているので、僅かな歪みとなっている。これはガリウムに対するアルミニウムの割合の成分範囲の全てで適用される。この例では、他の 40

材料は GaAs と正確に格子整合する成分となっており、この成分が優先的に用いられる。) 例として、これらのセルのバンドギャップは第1のセルから最後のセルまで順番に、0.7 eV, 1.0 eV, 1.4 eV, 1.8 eV, 2.0 eV である。したがって、各々のセルはデバイスに当たる光のスペクトルの異なる部分を吸収する。必要があれば、このデバイスには、他の例で説明したように、Si バリヤ、トンネルダイオード、ウインドウ層等が設けられる。また、図 10A ~ 10D を参照して説明したように、この基板は除去されてよい。さらに、これらのセルの材料は、GaAs そのものの上に成長されなくともよく、GaAs に格子整合された他の基板の上に成長されてよい。他の層がこれらの光吸収セルの間に用いられてよく、これらはたとえば、トンネルダイオードであり、好ましくはこれらのセルと格子整合されており、また同様に好ましくは基板と格子整合されている。

10

#### 【0089】

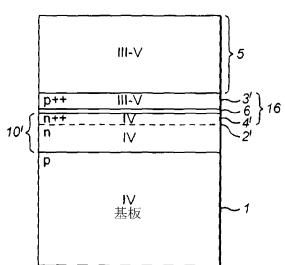

図 12 は本発明のもう 1 つの態様の例の層を示す。ここでは、IV 族層 10' と III-V 族層 3' との間の Si 拡散バリヤ 6 は、V 族原子がこのバリヤを通って IV 族材料に拡散することをコントロールする。この IV 族材料は既に n 型であり、したがって、生成される拡散領域 4' は高濃度で n 型ドープされている。この例では、層 3' および層 4' はトンネルダイオードを形成する。

#### 【0090】

図 12 に示す例は、IV 族の光電セルに組み合わせたトンネルダイオードを示す。p 型の IV 族基板 1 が準備され、この上に n 型の IV 族エピ層 10' が成長され、この接合部は光起電セルとなる。この上に薄い Si 拡散バリヤ 6 が設けられ、この上に高濃度ドープされた III-V 族層 3' が設けられる。この III-V 族層 3' の V 族原子は、バリヤを通じて拡散し、高濃度ドープされた n++ 領域 4' を形成する。この上に他の層 5、たとえば他の太陽電池セルがたとえば III-V 族材料で成長されてよい。高濃度ドープされた IV 族 n++ 領域 4' および高濃度ドープされた III-V 族 p++ 層 3' は、低抵抗トンネルダイオード 16 を形成し、これは、層 1 と層 10' との間の p-n 接合部で生成された光電流が、大きな抵抗損失を受けずに上の層に導電されることを可能にする。

20

#### 【0091】

上記の例と同様に、このシリコンバリヤは必ずしも厳密に IV 族材料と III-V 族材料との間の界面にある必要はなく、V 族原子の拡散に影響を与えるように一方の側に距離を置いて設けられてよい。

30

#### 【0092】

上記の例においては、これらのサブセルは、GaAs 基板(すなわち、GaAs に格子整合された基板、またはこの構造の格子定数に適合した他の基板)の上に逆順に設けられてよく、大きなバンドギャップのセルからスタートし、これに続くセルでは順にバンドギャップが小さくなり、最後がたとえば SiGe / SiGeSn セルとなる。最も大きなギャップのセルと基板との間に、犠牲層が設けられ、これらのセルが取り外されて適合した手段またはヒートシンクにトランスマルチアされてよく、最も狭いバンドギャップのセルが基板に隣接し、最も広いバンドギャップのセルが入射光を最初に受けるように反転されてよい。

40

#### 【0093】

典型的には太陽電池セルである、これらの材料を用いたデバイスは、通常は最初に必要な層または少なくともそれらの一部を有する半導体材料が準備されて製造される。材料は、通常半導体ウェーハ全体に渡り均一に製造されている。この材料は次にリソグラフィー技術により加工され、個々のデバイスおよび接続部が形成される。材料の製造はしばしば、リソグラフィー工程およびパッケージ工程を行う製造者と異なる製造者によって行われる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図9A】

【図9B】

【図10A】

【図10B】

【図10C】

【図10D】

【図11】

【図11A】

【図11B】

【図11C】

【図 1 1 D】

【図 1 3】

【図 1 2】

---

フロントページの続き

(72)発明者 ジョンソン , アンドリュー

イギリス国 エヌピー 18 2ジェイイー ウェールズ , ニューポート , ラングストン , ブ

ライアリー ウェイ 27

(72)発明者 ネルソン , アンドリュー , ウィリアム

イギリス国 シーエフ 71 7アールダブリュ ウェールズ , ヴェイル オブ グラモーガン ,

カウブリッジ , シティ , ランサナー

(72)発明者 ハーパー , ロバート キャメロン

イギリス国 エヌピー 10 9エーエクス ウェールズ , ニューポート , ロジャーストン ,

マイナー チェイス , ビーコンズ クローズ 6

審査官 濱田 聖司

(56)参考文献 国際公開第 2010 / 102345 (WO , A1 )

特表 2002 - 540635 (JP , A )

特表 2010 - 500741 (JP , A )

英国特許出願公開第 2467934 (GB , A )

S.Strite , "Si as a diffusion for Ge/GaAs heterojunctions" , Applied Physics Letters , Vo

l.56, No.17 (1990) , pp.1673-1675

(58)調査した分野(Int.Cl. , DB名)

H 01 L 31 / 00 - 31 / 20