(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5103056号

(P5103056)

(45) 発行日 平成24年12月19日(2012.12.19)

(24) 登録日 平成24年10月5日(2012.10.5)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| H 01 L 21/336 (2006.01) | H 01 L 29/78 3 O 1 G |

| H 01 L 29/78 (2006.01)  | H 01 L 21/316 X      |

| H 01 L 21/316 (2006.01) | H 01 L 21/316 S      |

| C 23 C 16/40 (2006.01)  | H 01 L 21/316 M      |

|                         | C 23 C 16/40         |

請求項の数 19 (全 14 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-128692 (P2007-128692)  |

| (22) 出願日  | 平成19年5月15日 (2007.5.15)        |

| (65) 公開番号 | 特開2008-288227 (P2008-288227A) |

| (43) 公開日  | 平成20年11月27日 (2008.11.27)      |

| 審査請求日     | 平成22年4月26日 (2010.4.26)        |

(出願人による申告) 国等の委託研究の成果に係る特許出願 (平成16年度独立行政法人新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基盤(MIRAI)」委託研究、産業活力再生特別措置法第30条の適用を受けるもの)

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100080001<br>弁理士 筒井 大和                               |

| (72) 発明者  | 生田目 俊秀<br>東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内           |

| 審査官       | 儀同 孝信                                                |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上にMISトランジスタのゲート絶縁膜を形成し、前記ゲート絶縁膜上に前記MISトランジスタのゲート電極を形成する工程を含む半導体装置の製造方法であって、

前記半導体基板上に前記ゲート絶縁膜を形成する工程は、

(a) 前記半導体基板の主面上に、酸化シリコンより高い比誘電率の酸化物から構成される第1層を形成する工程と、

(b) 前記工程(a)の後、前記半導体基板の主面を非酸化性雰囲気中で熱処理する工程と、

(c) 前記第1層上に、前記工程(b)直後の第1層中に占める酸素の割合より高い酸化物から構成される第2層を形成する工程と、

(d) 前記第2層上に、酸素が拡散するのを抑制する金属から構成されるキャップ層を形成する工程と、

(e) 前記工程(d)の後、前記半導体基板の主面を熱処理する工程と、

を含むことを特徴とする半導体装置の製造方法。

## 【請求項2】

前記工程(c)では、前記第2層を構成する酸化ハフニウム膜を、酸素原料として水を用いたALD法によって、前記第1層上に形成することを特徴とする請求項1記載の半導体装置の製造方法。

**【請求項 3】**

前記工程 (c) では、前記第2層を構成する酸化アルミニウム膜を、酸素原料として水を用いたALD法によって、前記第1層上に形成することを特徴とする請求項1記載の半導体装置の製造方法。

**【請求項 4】**

前記工程 (c) では、前記第2層を構成する酸化タンタル膜を、酸素原料として水を用いたALD法によって、前記第1層上に形成することを特徴とする請求項1記載の半導体装置の製造方法。

**【請求項 5】**

(f) 前記キャップ層をバターニングすることによって、前記キャップ層から構成される前記ゲート電極を形成する工程と、

を含むことを特徴とする請求項1記載の半導体装置の製造方法。 10

**【請求項 6】**

前記工程 (b) では、前記第1層を緻密化することを特徴とする請求項1記載の半導体装置の製造方法。

**【請求項 7】**

前記工程 (e) では、前記第2層から前記第1層へ酸素を供給することを特徴とする請求項1記載の半導体装置の製造方法。

**【請求項 8】**

(a) 半導体基板上に第1層を形成する工程と、

(b) 前記第1層上に第2層を形成する工程と、

(c) 前記第2層上にキャップ層を形成する工程と、

(d) 前記工程 (a) ~ (c) 後に、前記半導体基板の主面を熱処理する工程、

を有し、 20

前記第1及び第2層はMISトランジスタのゲート絶縁膜を構成しており、

前記キャップ層は前記MISトランジスタのゲート電極を構成しており、

前記第1層はハフニウムと酸素を含んで構成されており、

前記第2層はアルミニウムと酸素、または、タンタルと酸素を含んで構成されており、

前記第2層の膜厚は、前記第1層の膜厚よりも薄いことを特徴とする半導体装置の製造方法。 30

**【請求項 9】**

前記工程 (d) によって、前記第2層から前記第1層に酸素が供給されることを特徴とする請求項8に記載の半導体装置の製造方法。

**【請求項 10】**

前記工程 (a) と前記工程 (b)との間に、(e) 前記半導体基板の主面を非酸化性雰囲気中で熱処理する工程、を更に有することを特徴とする請求項8または9の何れか1項に記載の半導体装置の製造方法。

**【請求項 11】**

前記工程 (e) によって、前記第1層が緻密化されることを特徴とする請求項10に記載の半導体装置の製造方法。 40

**【請求項 12】**

前記工程 (b) で形成される前記第2層は、前記工程 (a) 直後の前記第1層中に占める酸素の割合より高い酸化物から構成されることを特徴とする請求項10または11の何れか1項に記載の半導体装置の製造方法。

**【請求項 13】**

前記工程 (b) で、前記第2層はALD法によって形成されることを特徴とする請求項8~12の何れか1項に記載の半導体装置の製造方法。

**【請求項 14】**

前記工程 (a) で、前記第1層はALD法によって形成されることを特徴とする請求項8~13の何れか1項に記載の半導体装置の製造方法。 50

**【請求項 15】**

前記工程 (a) 前に、(f) 前記半導体基板上に酸化シリコン膜を形成する工程、を更に有し、

前記酸化シリコン膜の膜厚は、前記第1層の膜厚よりも薄いことを特徴とする請求項8～14の何れか1項に記載の半導体装置の製造方法。

**【請求項 16】**

前記第2層の膜厚は、前記酸化シリコン膜の膜厚よりも薄いことを特徴とする請求項15に記載の半導体装置の製造方法。

**【請求項 17】**

前記キャップ層は、金属から構成されていることを特徴とする請求項8～16の何れか1項に記載の半導体装置の製造方法。

**【請求項 18】**

前記MISトランジスタはnチャネル型MISトランジスタであり、

前記キャップ層は、窒化タンタル、アルミニウム、チタン、または、タンタルによって構成されていることを特徴とする請求項8～16の何れか1項に記載の半導体装置の製造方法。

**【請求項 19】**

前記MISトランジスタはpチャネル型MISトランジスタであり、

前記キャップ層は、ルテニウム、プラチナ、または、ニッケルによって構成されていることを特徴とする請求項8～16の何れか1項に記載の半導体装置の製造方法。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の製造技術に関し、特に、酸化シリコン( $\text{SiO}_2$ )よりも比誘電率が高い酸化物を含んで構成されたゲート絶縁膜を有するMIS(Metal Insulator Semiconductor)トランジスタを備えた半導体装置の製造に適用して有効な技術に関する。

**【背景技術】****【0002】**

近年、半導体集積回路を構成するMISトランジスタの微細化に伴って、酸化シリコンから構成されるゲート絶縁膜の薄膜化が急速に進んでいる。しかし、ゲート絶縁膜の膜厚が2nm程度まで薄くなると、ダイレクトトンネリングと呼ばれる量子効果によって、シリコン基板中の電子がゲート絶縁膜を通り抜けてゲート電極に逃げるゲート・リーク現象が顕著になってくる。

20

**【0003】**

そこで、ゲート絶縁膜材料を酸化シリコン( $\text{SiO}_2$ )よりも比誘電率の高い絶縁材料(高誘電体材料)に置き換える検討が進められている。これは、ゲート絶縁膜を高誘電体膜で構成した場合、酸化シリコン膜厚換算容量が同じであっても、実際の物理膜厚を(高誘電体膜の誘電率/酸化シリコン膜の誘電率)倍だけ厚くできるので、結果としてゲート・リーク電流を低減することができるからである。高誘電体材料としては、 $\text{Hf-O}$ 、 $\text{Hf-Si-O}$ 、 $\text{Hf-Si-O-N}$ 、 $\text{Hf-Al-O}$ 、 $\text{Hf-Al-O-N}$ などのハフニウム系酸化物に代表される酸化物が検討されている。

30

**【0004】**

なお、本発明者は、発明した結果に基づき、高誘電体材料から構成されるゲート絶縁膜と金属材料から構成されるゲート電極を形成する第1の観点、および、ゲート絶縁膜を構成する高誘電体材料をキャップする第2の観点、で先行技術調査を行った。その結果、第1の観点では、特開2006-080133号公報(特許文献1)が抽出され、第2の観点では、特開2006-310801号公報(特許文献2)が抽出された。

40

**【0005】**

特開2006-080133号公報(特許文献1)は、全体として、ゲート絶縁膜を高誘電体材料の酸化ハフニウムを用いた上で、nチャネル型MISトランジスタおよびpチ

50

ヤネル型M I Sトランジスタのゲート電極を、それぞれの仕事関数に合ったゲート電極材料を用いて形成することを主題とするものであり、そのために金属材料を用いることが記載されている。なお、ゲート絶縁膜を構成する高誘電体膜をキャップするという観点についての記載はない。

#### 【0006】

特開2006-310801号公報（特許文献2）は、全体として、高誘電体膜とゲート電極を構成する多結晶シリコン膜との界面で生じるトラッピングの問題を解決することを主題とするものであり、そのためにゲート電極を形成する前に中間層（いわゆる緩衝層）でゲート絶縁膜上をキャップすることが記載されている。

【特許文献1】特開2006-080133号公報

10

【特許文献2】特開2006-310801号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

高誘電体材料としてのハフニウム系酸化物などの酸化物から構成されるゲート絶縁膜は、原子層制御成膜（ALD：Atomic Layer Deposition）法、CVD（Chemical Vapor Deposition）法またはスパッタリング法を用いて半導体基板上に堆積される。しかし、このようにして堆積された膜は、原料に起因した炭素等の不純物やH<sub>2</sub>O酸化剤に起因したOH等の不純物が膜中に残存するために比較的密度が低くなり、その結果、誘電率が低くなってしまう。そこで、酸化物から構成されるゲート絶縁膜の製造では、例えば、酸化物膜を成膜した後に非酸化性雰囲気で急速加熱処理をする、または酸化物膜を成膜した後に酸素雰囲気中で低温度の熱処理をする必要がある。

20

#### 【0008】

ところが、非酸化性雰囲気で急速加熱処理して形成した酸化物膜は、緻密化が図られている反面、移動度などのトランジスタ特性（トランジスタ特性）の低下の原因となる欠陥サイトの一つとなりうる酸素欠損を有するという問題がある。一方、酸素雰囲気で熱処理をして形成した酸化物膜は、熱処理における酸素欠損を抑制できる反面、酸素が酸化物中を拡散してシリコン基板にまで到達して界面酸化シリコン層を形成し、その結果、酸化シリコン膜厚換算容量が増大してしまうという問題がある。

#### 【0009】

30

このように、半導体基板上に堆積された酸化物を含んで構成されるゲート絶縁膜は、高誘電率化と酸素欠損の低減化とを両立させることが困難であることが本発明者の検討によつて明らかとなった。

#### 【0010】

本発明の目的は、酸化シリコンより比誘電率の高い酸化物を含んで構成されるゲート絶縁膜を備えたM I Sトランジスタのトランジスタ特性を向上することのできる技術を提供することにある。

#### 【0011】

本発明の他の目的は、酸化物膜の高誘電率化と、酸化物膜中の酸素欠損の低減化と、界面酸化シリコン成長の抑制化を達成させる技術を提供することにある。

40

#### 【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0014】

本発明の一実施の形態は、まず、（a）半導体基板の主面上に、酸化シリコンより高い比誘電率の酸化物から構成される高誘電体層を形成する。次いで、（b）前記半導体基板

50

の正面を非酸化性雰囲気中で熱処理する。次いで、(c)前記高誘電体層上に、前記工程(b)直後の前記高誘電体層中に占める酸素の割合より高い酸化物から構成される酸素供給層を形成する。次いで、(d)前記酸素供給層上に、酸素が拡散するのを抑制する金属から構成されるキャップ層を形成する。次いで、(e)前記半導体基板の正面を熱処理する。

#### 【0015】

この手段によれば、工程(b)の熱処理によって、前記高誘電体層を緻密化するので、比誘電率の高い前記高誘電体層が得られる。また、工程(e)の熱処理によって、前記酸素供給層中の酸素を前記高誘電体層に供給するので、酸素欠損が低減した前記高誘電体層が得られる。すなわち、酸化物膜の高誘電率化と、酸化物膜中の酸素欠損の低減化と、界面酸化シリコン成長の抑制化を達成した酸化物が得られる。10

#### 【0016】

なお、特開2006-080133号公報（特許文献1）および特開2006-310801号公報（特許文献2）には、前記高誘電体層に酸素を供給するための前記酸素供給層を形成する記載はない。また、前記キャップ層は、特開2006-310801号公報（特許文献2）のように、ゲート絶縁膜とゲート電極との界面で生じるトラッピングを防止するための中間層（いわゆる緩衝層）として用いるものではなく、前記酸素供給層中の酸素が、高誘電体層側とは反対の雰囲気中に拡散するのを防止するためのものである。前記キャップ層によって雰囲気中に酸素が拡散しないため、前記酸素供給層中の酸素が前記高誘電体層に供給されるのである。20

#### 【発明の効果】

#### 【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

#### 【0018】

この一実施の形態によれば、酸化シリコンより比誘電率の高い酸化物を含んで構成されるゲート絶縁膜を備えたMISトランジスタのトランジスタ特性を向上することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。30

#### 【0020】

##### （実施の形態1）

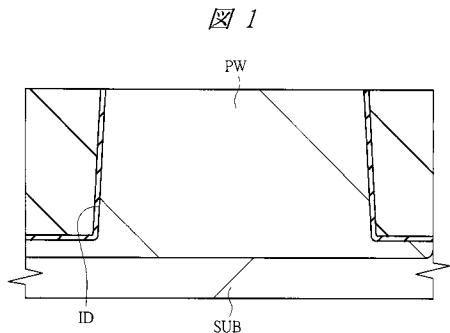

本実施の形態1では、本発明をnチャネル型MISトランジスタの製造方法に適用し、図1～図9を参照して説明する。図1～図9は製造工程中の半導体装置を模式的に示す断面図であり、このうち図2～図6は要部を拡大して示している。なお、pチャネル型MISトランジスタはnチャネル型MISトランジスタの極性を反対にしたものであり、本発明はpチャネル型MISトランジスタの製造方法にも適用することができる。40

#### 【0021】

まず、図1に示すように、例えばp型の単結晶シリコンから構成される半導体基板（以下、「基板」という）SUBの正面（素子形成面）に周知のSTI（Shallow Trench Isolation）技術を用いて素子分離溝IDを形成する。次いで、基板SUBのnチャネル型MISトランジスタ形成領域にホウ素をイオン注入した後、MISトランジスタのしきい値電圧を調整するための不純物をイオン注入する。次いで、基板SUBの正面を熱処理し、上記不純物を基板SUB中に拡散させることによって、基板SUBの正面にp型ウエルPWを形成する。次いで、フッ酸などのウェットエッチング液を用い、基板SUB（p型ウエルPW）の表面の自然酸化膜を除去することによって、基板SUBの表面（シリコン面）を露出させる。50

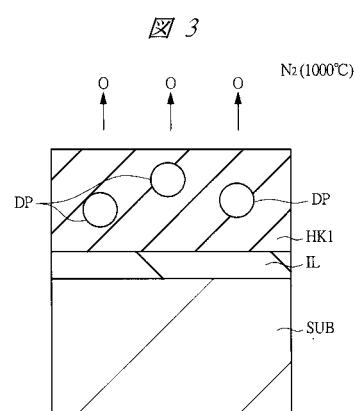

## 【0022】

続いて、図2に示すように、基板SUBの正面(p型ウエルPWの表面)上に酸化シリコン(SiO<sub>2</sub>)から構成される界面層ILを形成した後、界面層IL上に酸化シリコンより高い比誘電率の酸化物から構成される高誘電体層HK1を形成する。この高誘電体層HK1は、nチャネル型MISトランジスタのゲート絶縁膜を構成するものであり、例えば酸化ハフニウム(HfO<sub>2</sub>)から構成される。界面層ILは、基板SUB(単結晶シリコン)上に直接高誘電体層HK1(酸化ハフニウム)を形成した時に発生する欠陥を低減するために、本実施の形態1では設けられている。また、この界面層ILはゲート絶縁膜に含まれてしまうため、高い比誘電率のゲート絶縁膜を得るためにには、その膜厚はできるだけ薄い方が良い。

10

## 【0023】

本実施の形態1では、界面層ILを構成する酸化シリコン(SiO<sub>2</sub>)は、例えば、希釈フッ酸溶液で自然酸化膜を除去した後に、基板SUBの正面を950以上的高温度熱処理酸化することによって形成され、その膜厚は例えば0.3nmである。

## 【0024】

また、高誘電体層HK1を構成する酸化ハフニウム(HfO<sub>2</sub>)は、例えば、H<sub>2</sub>O(水)のO(酸素)原料とTDMAH(Tetrakis-Dimethylamido-Hafnium: Hf(NMe<sub>2</sub>)<sub>4</sub>)のHf(ハフニウム)原料を用いた原子層制御成膜(ALD: Atomic Layer Deposition)法によって堆積され、その膜厚は例えば2.4nmである。

20

## 【0025】

ここで、高誘電体層HK1は、酸化ハフニウム(Hf-O)の他に、例えば、Hf-Si-O、Hf-Si-O-N、Hf-Al-O、Hf-Al-O-N、Hf-Ta-O、Hf-Ti-O、Hf-La-O、Hf-Y-O、Hf-Ta-Si-O、Hf-Ti-Si-O、Hf-La-Si-O、Hf-Y-Si-Oなどの酸化物も適用することができる。このような酸素(O)とハフニウム(Hf)を含み、酸化シリコン(SiO<sub>2</sub>)より高い比誘電率のものを本願においては「ハフニウム系酸化物」と称している。

## 【0026】

ハフニウム系酸化物を形成するにあたりALD法を用いた場合、H<sub>2</sub>OガスのO原料とTDMAH(Hf(NMe<sub>2</sub>)<sub>4</sub>)のHf原料の他に、それぞれの原料が用いられる。Si(シリコン)原料としては、例えばTDMAS(Trisdimethylaminosilane: HSi(NMe<sub>2</sub>)<sub>3</sub>)である。Al(アルミニウム)原料としては、例えばTMA(Trimethylaluminum: AlMe<sub>3</sub>)である。Ta(タンタル)原料としては、例えばTAIDEAT(tertiaryamylimidotris(dimethylamido)tantalum: EtMe<sub>2</sub>CNTa(NMe<sub>2</sub>)<sub>3</sub>)である。Ti(チタン)原料としては、例えばTDMAT(Tetrakisdimethylaminotitanium: Ti(NMe<sub>2</sub>)<sub>3</sub>)である。Y(イットリウム)原料としては、例えばTriethylcyclopentadienylttrium: Y(EtCp)<sub>3</sub>である。La(ランタン)原料としては、例えばTriethylcyclopentadienyllanthanum: La(EtCp)<sub>3</sub>である。また、Hf-Si-O-N及びHf-Al-O-Nの窒化は、Hf-Si-O、Hf-Al-O膜をALD法で堆積した後に、プラズマ窒素による窒化及びアンモニアガスを用いた熱処理による窒化によって作製される。

30

## 【0027】

また、本実施の形態1では、高誘電体層HK1の形成にあたりALD法を適用しているが、これに限らず、スペッタリング法、CVD法によって形成されても良い。なお、後の工程でも、ハフニウム系酸化物を堆積して酸素供給層を構成するが、このハフニウム系酸化物は、スペッタリング法、CVD法を適用せず、ALD法を適用している。

40

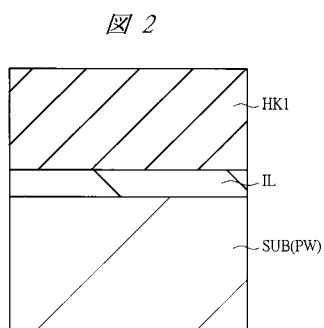

## 【0028】

続いて、図3に示すように、酸素濃度がppm(parts per million)以下の非酸化性雰囲気(例えば窒素、水素、アルゴンなど)中において600~1000の範囲で基板SUBの正面を熱処理する。この工程では高誘電体層HK1を緻密化する。なお、本願においては、高誘電体層HK1を緻密化する熱処理を「緻密化アニール」という。

50

## 【0029】

堆積されたままの高誘電体層H K 1は、原料に起因した炭素等の不純物やH<sub>2</sub>O酸化剤に起因したOH等の不純物が膜中に残存するために比較的密度が低くなり、その結果、誘電率が低い。そこで、成膜後に緻密化アニールを行うことによって、高誘電体層H K 1の緻密化および高誘電率化を図ることができる。

## 【0030】

また、非酸化性雰囲気中で緻密化アニールを行うことによって、基板S U B（単結晶シリコン）界面におけるSi-O結合の形成を防止することができる。酸素(O)を含む雰囲気中で緻密化アニールを行った場合は、外部から酸素が酸化ハフニウムから構成される高誘電体層H K 1中を拡散して酸素が単結晶シリコンから構成される基板S U Bまで到達して、単結晶シリコンから構成される基板S U Bとの界面でSi-O結合を形成する。その結果、ゲート絶縁膜の一部が酸化シリコン膜になる、すなわち酸化シリコンから構成される界面層I Lが厚くなり、ゲート絶縁膜の誘電率が低下してしまう。そこで、非酸化性雰囲気中で緻密化アニールを行うことによって、界面におけるSi-O結合の形成を防止することができるのである。10

## 【0031】

さらに、緻密化アニール工程を行うにあたり、非酸化性雰囲気中で、かつ急加熱・急冷(例えば、1000 / sec)の急速加熱処理(P D A : Post Deposition Annealing)で行う場合、酸化シリコンから構成される界面層I Lの膜厚をより厚くすることなく、高誘電体層H K 1を緻密化することができる。20

## 【0032】

しかしながら、この緻密化アニールを行うことによって、緻密化を保持したまま酸素(O)が欠損してしまう。図3では、欠損した酸素が雰囲気中に放出されて、高誘電体層H K 1中に酸素欠損部D Pが発生する様子が示されている。なお、後述の工程(酸素供給アニール工程)で、この酸素欠損部D Pを低減する処理が行われる。

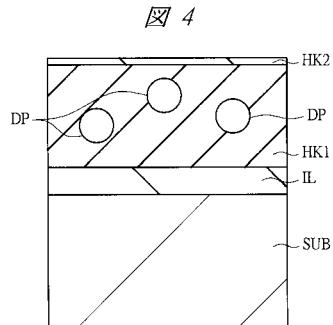

## 【0033】

続いて、図4に示すように、緻密化アニール直後の高誘電体層H K 1中に占める酸素の割合より高い酸化物から構成される酸素供給層H K 2を形成する。本実施の形態1では、緻密化アニール直後の酸素欠損している高誘電体層H K 1中に占める酸素の割合より高い酸素供給層H K 2として、例えばH<sub>2</sub>OのO(酸素)原料とT D M A H(Hf(NMe<sub>2</sub>)<sub>4</sub>)のHf(ハフニウム)原料を用いたA L D法によって堆積されたハフニウム系酸化物膜を適用することができる。A L D法はチャンバー内に設置した基板S U B上に、原料化合物の分子をモノレイヤごとに表面へ吸着、反応による成膜、ページによる余剰分子の取り除き、H<sub>2</sub>O酸化材との反応による成膜、ページによる余剰分子の取り除き、のサイクルを繰り返し行うことによって、原子層を一層ずつ堆積する方法である。このためサイクル数によってハフニウム系酸化物膜から構成される酸素供給層H K 2の膜厚を制御することができる。30

## 【0034】

A L D法によって堆積されたハフニウム系酸化物膜中には、定量的に残留OH基が含まれる。このため緻密化アニール直後の酸素欠損しているハフニウム系酸化物膜(高誘電体層H K 1)中に占める酸素の割合よりハフニウム系酸化物膜(酸素供給層H K 2)中に占める酸素の割合が高いこととなる。残留した酸素が後述の工程で、高誘電体層H K 1で欠損している酸素を補う(供給する)役割をし、すなわち酸素供給層H K 2は酸素供給源として働き、その膜厚で絶対供給量を調整することができる。このため原子レベルで膜厚を制御することができるA L D法は、酸素供給層H K 2の形成には有効となる。40

## 【0035】

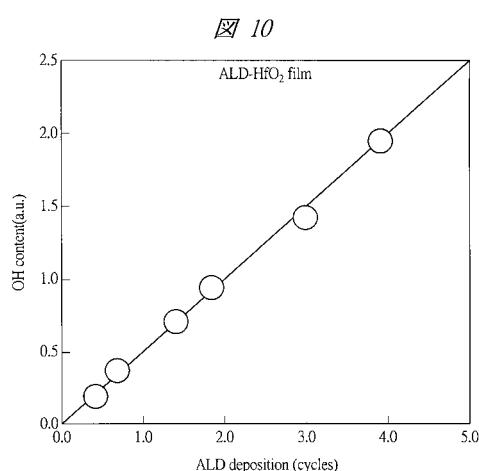

例えば、A L D法によって堆積された酸化ハフニウム膜中には、原料としてH<sub>2</sub>Oを用いるため、約0.5%の残留OH基が含まれる。図10にA L D法によって堆積された酸化ハフニウム膜の厚さに対する残留OH基の含有量を示す。図10に示すように、サイクル数が増加するに従い、すなわち膜厚が厚くなるに従い、酸化ハフニウム膜中に含まれる50

O H 基が増加することがわかる。したがって、緻密化アニールによって酸素欠損が生じた高誘電体層H K 1に対して充分に酸素を供給できるように、A L D法によって堆積された酸化ハフニウムから構成される酸素供給層H K 2の膜厚で、絶対供給量を調整する。本実施の形態1では、A L D法によって堆積された酸化ハフニウム膜から構成される酸素供給層H K 2の膜厚を例えば4 nmと調整している。

#### 【0036】

ところで、ハフニウム系酸化物を形成する方法にはA L D法の他に、スパッタリング法あるいはC V D法などがある。しかしながら、スパッタリング法あるいはC V D法では、堆積された膜中の酸素が過剰とはならず、緻密化アニール直後の酸素欠損している高誘電体層H K 1中に占める酸素の割合より高い酸素供給層H K 2を形成することができない。このため、H<sub>2</sub>Oを原料としたA L D法を用いている。

10

#### 【0037】

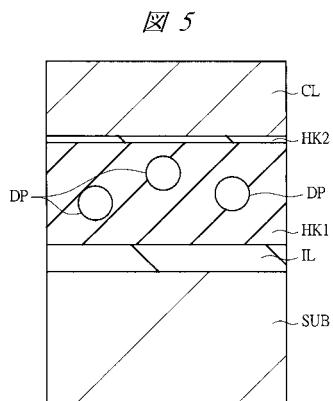

続いて、図5に示すように、酸素供給層H K 2上に、酸素が拡散するのを防止する金属から構成されるキャップ層C Lを形成する。言い換えると、酸素供給層H K 2をキャップ層C Lによってキャップする。キャップ層C Lは、後の工程（酸素供給アニール工程）で基板S U Bの正面を熱処理した場合において、熱処理時の雰囲気中に酸素が放出しないようにする（バリヤする）ために設けられる金属膜（バリアメタル膜）から構成されるものである。本実施の形態1では、キャップ層C Lは、例えばスパッタリング法を用いて形成された窒化タンタル（Ta N）から構成され、その膜厚は例えば20 nmである。

#### 【0038】

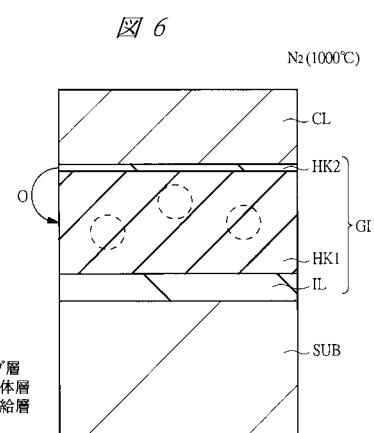

続いて、図6に示すように、例えば窒素（N<sub>2</sub>）雰囲気中で950～1150 °Cの範囲で基板S U Bの正面を熱処理する。この工程では、酸素供給層H K 2中で残存している酸素を、高誘電体層H K 1に供給し、高誘電体層H K 1の酸素欠損を補う。すなわち、図3で説明した緻密化アニールを行うことによって生じた酸素欠損部D Pを低減する。なお、本願においては、高誘電体層H K 1に酸素を供給する熱処理を「酸素供給アニール」という。

20

#### 【0039】

このようにして酸素が補われた高誘電体層H K 1は、界面層I L、酸素供給層H K 2も含み、ゲート絶縁膜G Iを構成する。本実施の形態1では、酸素供給層H K 2として、ハフニウム系酸化物を用いているが、緻密化アニール直後の高誘電体層H K 1中に占める酸素の割合より高い酸化物であれば良い。しかしながら、高誘電率のゲート絶縁膜G Iを得るためにハフニウム系酸化物のように、酸素供給層H K 2も酸化シリコンより高い比誘電率の酸化物が望ましい。

30

#### 【0040】

緻密化アニールによって高誘電体層H K 1は緻密化を図れる反面、酸素が欠損してしまい、酸素が低密度な膜となる。ゲート絶縁膜G Iにこのような酸素が低密度な膜を適用した場合、高密度な膜の場合と比較して高いゲート・リーク電流が流れてしまう。そこで、酸素供給アニールを行うことによって、高誘電体層H K 1の酸素欠損を補い、高密度な膜を形成することができ、ゲート・リーク電流が流れるのを抑制することができる。また、酸素供給アニールにおいて、酸素供給層H K 2の膜厚、すなわち酸素供給量は調整されるため、例えば基板S U B（単結晶シリコン）界面にまで酸素が到達せず、界面層I Lの厚さを厚くしないこともできる。

40

#### 【0041】

これまでの緻密化アニールおよび酸素供給アニールを含む工程によって、ゲート絶縁膜G Iを構成する高誘電体層H K 1の高誘電率化と、酸素欠損の低減化とを両立することができる。

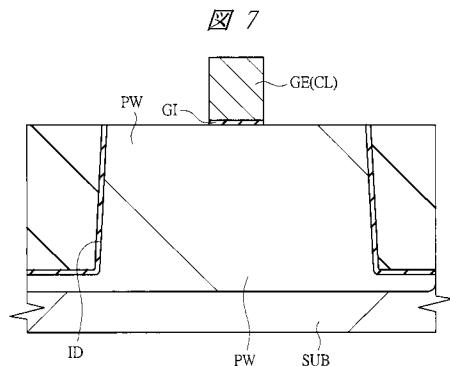

#### 【0042】

続いて、図7に示すように、キャップ層C Lを構成するバリアメタル膜をパターニングすることによって、バリアメタル膜から構成されるゲート電極G Eを形成し、また、ゲート電極G E下以外のゲート絶縁膜G Iを除去する。なお、本実施の形態1では、酸素供給

50

アニール後に、ゲート電極 G E 形成のパターニングを行ったが、その順番が逆になつても良い。

#### 【 0 0 4 3 】

本実施の形態 1 では、キャップ層 C L を構成するバリアメタル膜をパターニングしてゲート電極 G E を形成する。このため、キャップ層 C L には、酸素が拡散するのを抑制させる役割をし、ゲート電極 G E の仕事関数に適したバリアメタルであれば良い。 $n$  チャネル型 M I S トランジスタのキャップ層 C L としては窒化タンタルの他に、アルミニウム (A l) 、チタン (T i) 、タンタル (T a) などを適用することができる。また、 $p$  チャネル型 M I S トランジスタのキャップ層 C L としては、ルテニウム (R u) 、白金 (P t) 、ニッケル (N i) などを適用することができる。

10

#### 【 0 0 4 4 】

また、本実施の形態 1 では、キャップ層 C L およびゲート電極 G E とも窒化タンタルから構成したが、キャップ層 C L に窒化タンタルを用いて酸素供給アニールをした後、その窒化タンタルを除去した後、最適な仕事関数の金属材料からゲート電極 G E を形成しても良い。

#### 【 0 0 4 5 】

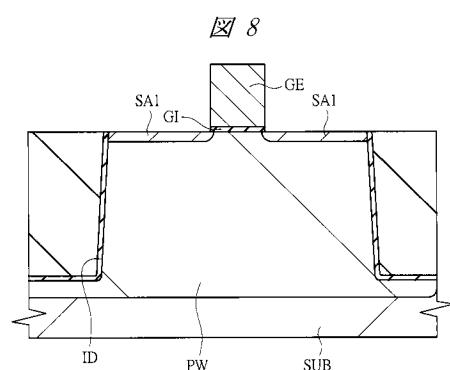

続いて、図 8 に示すように、 $p$  型ウエル P W にリンまたはヒ素をイオン注入して  $n^-$  型半導体領域 S A 1 を形成する。 $n^-$  型半導体領域 S A 1 は、 $n$  チャネル型 M I S トランジスタを L D D (Lightly Doped Drain) 構造にするために形成する。

20

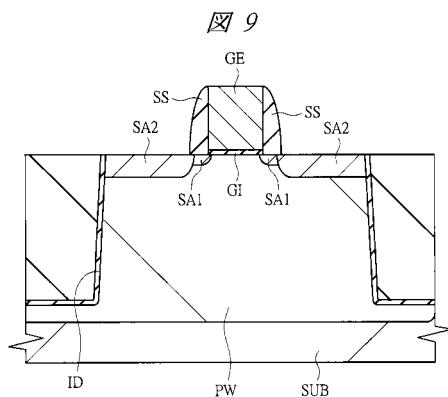

#### 【 0 0 4 6 】

続いて、図 9 に示すように、ゲート電極 G E の側壁にサイドウォールスペーサ S S を形成する。サイドウォールスペーサ S S は、基板 S U B 上に C V D 法で酸化シリコン膜を堆積した後、この酸化シリコン膜を異方性エッチングすることによって形成される。次いで、 $p$  型ウエル P W にリンまたはヒ素をイオン注入した後、基板 S U B の正面を熱処理してこれらの不純物を拡散させることにより、 $p$  型ウエル P W に  $n^+$  型半導体領域 (ソース・ドレイン) S A 2 を形成する。その後、配線工程を経て、最終に水素雰囲気下で 400 の熱処理 (F G A : Forming Gas Annealing) を行い、 $n$  チャネル型 M I S トランジスタを備えた半導体装置が完成する。

#### 【 0 0 4 7 】

図 11 は、本実施の形態 1 における  $n$  チャネル型 M I S トランジスタ (図 11 の説明にあたり Q n とする) と、本発明者が検討した  $n$  チャネル型 M I S トランジスタ (Q' n とする) のトランジスタ特性を比較した表である。なお、Q' n は、Q n の製造工程のうち酸素供給層 H K 2 (A L D 法によって堆積された膜厚 4 の酸化ハフニウム膜) を形成する工程を省略した以外は、同様の工程で製造されたものである。

30

#### 【 0 0 4 8 】

図 11 に示すように、Q n および Q' n のゲート絶縁膜 G I の酸化シリコン換算膜厚 (E O T) は、それぞれ 1.1 nm および 1.0 nm と同程度である。したがって、Q n および Q' n のトランジスタ特性を比較することができる。トランジスタ特性として、ゲート・リーク電流 (J g) および電子移動度 ( $\mu$ ) の比較した場合、Q' n に対して Q n ではゲート・リーク電流が 3 枠程度低く、電子移動度が 2 倍程度高い。

40

#### 【 0 0 4 9 】

このように実施の形態 1 による M I S トランジスタは、緻密化アニールおよび酸素供給アニールを含む工程によって、ゲート絶縁膜 G I を構成する高誘電体層 H K 1 の高誘電率化と酸素欠損の低減化とを両立することができる。また、酸素欠損を抑制したゲート絶縁膜 G I を有する M I S トランジスタを形成することによって、トランジスタ特性を向上することができる。さらに、酸素供給アニール時において、界面層 I L の成長を抑制することができるために、E O T が 1 nm 以下のゲート絶縁膜 G I を有する M I S トランジスタを形成することもできる。

#### 【 0 0 5 0 】

(実施の形態 2 )

50

前記実施の形態1では、酸素供給層を形成する工程では、ALD法によって堆積したハフニウム系酸化物を適用して形成する場合について説明したが、本実施の形態2では、ALD法によって堆積した酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、または、ALD法によって堆積した酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)を適用して形成する場合について説明する。なお、その他の工程は前記実施の形態1と同様である。

#### 【0051】

前記実施の形態1で説明したように、酸素供給層HK2は、高誘電体層HK1で欠損している酸素分を補うために、酸素供給アニール時に酸素を高誘電体層HK1へ供給するものである。このため酸素供給層HK2には、酸素供給層HK2中に占める酸素の割合が緻密化アニール直後の酸素欠損している高誘電体層HK1中に占める酸素濃度より高いものを適用すれば良い。そこで、H<sub>2</sub>Oを原料として用いるALD法によって酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)または酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)を堆積することによって、酸素供給層HK2を構成する。10

#### 【0052】

本実施の形態2では、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)を、例えば、H<sub>2</sub>OのO(酸素)原料とAl(アルミニウム)原料のTMA(Trimethylaluminum: AlMe<sub>3</sub>)を用いたALD法によって堆積する。または、酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)を、例えば、H<sub>2</sub>OのO(酸素)原料とTa(タンタル)原料のTAIDEAT(Tertiaryamylimidotris(dimethylamido)tantalum: EtMe<sub>2</sub>CNTa(NMe<sub>2</sub>)<sub>3</sub>)を用いたALD法によって堆積する。20

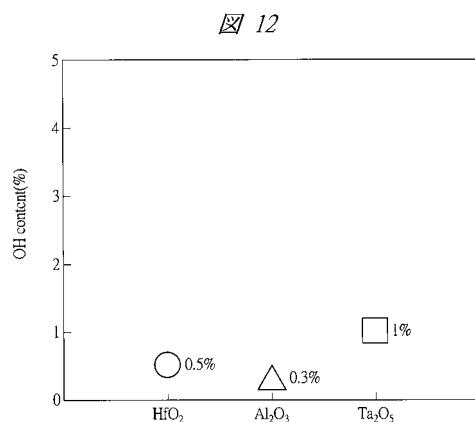

#### 【0053】

図12は、ALD法によって堆積された酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)および酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)に含まれるOH基の含有量を示すグラフである。また、前記実施の形態1において酸素供給層HK2として用いた酸化ハフニウム(HfO<sub>2</sub>)に含まれるOH基の含有量も合わせて示す。

#### 【0054】

図12に示すように、HfO<sub>2</sub>には約0.5%、Al<sub>2</sub>O<sub>3</sub>には約0.3%、Ta<sub>2</sub>O<sub>5</sub>には約1%のOH基が含まれることがわかる。これが酸素供給源として働き、緻密化アニール直後の高誘電体層HK1のある酸素欠損量に対して、膜厚で絶対供給量を調整することができる。なお、ある酸素欠損量の高誘電体層HK1に対して酸素を供給する場合、約0.5%のOH基が含まれるHfO<sub>2</sub>に対して約1%のOH基が含まれるTa<sub>2</sub>O<sub>5</sub>は、膜厚がHfO<sub>2</sub>の半分程度で良い。30

#### 【0055】

緻密化アニールによって高誘電体層HK1は緻密化を図れる反面、酸素が欠損してしまい、酸素が低密度な膜となる。酸素供給アニールを行うことによって、高誘電体層HK1の酸素欠損を補い、高密度な膜を形成することができ、ゲート・リーケ電流が流れるのを抑制することができる。すなわち、酸素欠損を抑制したゲート絶縁膜GIを形成することによって、トランジスタ特性を向上することができる。

#### 【0056】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。40

#### 【0057】

例えば、前記実施の形態では、高誘電体層としてハフニウム系酸化物(Hf-O)を例示したが、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)、酸化チタン(TiO<sub>2</sub>)、酸化ランタン(La<sub>2</sub>O<sub>3</sub>)、酸化ジルコニア(ZrO<sub>2</sub>)から構成される高誘電体層とした場合にも適用することができる。酸化アルミニウム、酸化タンタル、酸化チタン、酸化ランタン、および酸化ジルコニアは、前記実施の形態で示したハフニウム系酸化物と同様に、熱処理によって酸素欠損が発生してしまう。しかしながら、酸素供給層中の酸素が、高誘電体層を構成する酸化アルミニウム、酸化タンタル、酸化チタ50

ン、酸化ランタン、および酸化ジルコニウムに供給されることによって、高誘電体層の高誘電率化と、高誘電体層中の酸素欠損の低減化とを両立することができる。

【産業上の利用可能性】

【0058】

本発明は、半導体装置の製造業に幅広く利用されるものであり、特に、32nmテクノロジ以降のトランジスタ特性に優れた半導体装置の製造に利用されるものである。

【図面の簡単な説明】

【0059】

【図1】本発明の実施の形態1における半導体装置の製造工程中の断面図である。

【図2】図1に続く半導体装置の製造工程中における拡大断面図である。 10

【図3】図2に続く半導体装置の製造工程中における拡大断面図である。

【図4】図3に続く半導体装置の製造工程中における拡大断面図である。

【図5】図4に続く半導体装置の製造工程中における拡大断面図である。

【図6】図5に続く半導体装置の製造工程中における拡大断面図である。

【図7】図6に続く半導体装置の製造工程中における断面図である。

【図8】図7に続く半導体装置の製造工程中における断面図である。

【図9】図8に続く半導体装置の製造工程中における断面図である。

【図10】ALD法によって堆積された酸化ハフニウム膜の厚さに対する残留OH基の含有量を示すグラフである。 20

【図11】本実施の形態1におけるnチャネル型MISトランジスタ(Qn)と、本発明者が検討したnチャネル型MISトランジスタ(Q'n)のトランジスタ特性を比較した表である。

【図12】本発明の実施の形態2におけるALD法によって堆積された種々の酸化物に含まれるOH基の含有量を示すグラフである。

【符号の説明】

【0060】

C L キャップ層

D P 酸素欠損部

G E ゲート電極

G I ゲート絶縁膜

H K 1 高誘電体層

H K 2 酸素供給層

I D 素子分離溝

I L 界面層

P W p型ウエル

S A 1 n<sup>-</sup>型半導体領域

S A 2 n<sup>+</sup>型半導体領域(ソース・ドレイン)

S S サイドウォールスペーサ

S U B 基板

10

20

30

【図1】

【図3】

【図2】

【図4】

【図6】

【図5】

【図7】

【図9】

【図8】

【図10】

【図12】

【図11】

図11

|                               | Qn                   | Q'n |

|-------------------------------|----------------------|-----|

| EOT(nm)                       | 1.1                  | 1.0 |

| Jg(A / cm)                    | $7.0 \times 10^{-2}$ | 20  |

| $\mu$ (cm <sup>2</sup> / V·s) | 225                  | 120 |

---

フロントページの続き

(56)参考文献 特開2002-043565(JP,A)

特開2005-064052(JP,A)

特開2001-284345(JP,A)

特開2003-110100(JP,A)

特開2006-278488(JP,A)

特開2004-088078(JP,A)

再公表特許第2004/066376(JP,A1)

特開2006-086511(JP,A)

国際公開第2005/117086(WO,A1)

特開2001-185548(JP,A)

再公表特許第2005/074037(JP,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

C23C 16/40

H01L 21/316

H01L 29/78