(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-77349

(P2005-77349A)

(43) 公開日 平成17年3月24日(2005.3.24)

(51) Int.Cl.<sup>7</sup>

G O 1 P 15/08

G O 1 P 15/125

H O 1 L 29/84

F 1

G O 1 P 15/08

G O 1 P 15/125

H O 1 L 29/84

テーマコード(参考)

4 M 1 1 2

Z

Z

審査請求 未請求 請求項の数 4 O L (全 9 頁)

(21) 出願番号

特願2003-311066 (P2003-311066)

(22) 出願日

平成15年9月3日 (2003.9.3)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目2番3号

(74) 代理人 100086405

弁理士 河宮 治

(74) 代理人 100101454

弁理士 山田 卓二

(72) 発明者 山口 靖雄

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72) 発明者 中村 邦宏

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 4M112 AA02 BA07 CA21 CA24 DA06

DA09 DA18 EA03 EA06 EA07

EA11 FA08 GA01

(54) 【発明の名称】 加速度センサ

## (57) 【要約】

【課題】 外力によるクラックの伝播を防止つつ加速度センサの半導体基板主面方向に関する寸法の小型化を図る。

【解決手段】 加速度センサ2は、半導体基板6と、半導体基板6上に配設された、加速度センサ素子3および該センサ素子3を囲む枠部8と、枠部8上に配設された中間層34, 36と、中間層34, 36と接合され、これにより加速度センサ素子3を封止するキャップ部5とを備える。枠部8および中間層34, 36にはそれぞれ、半導体基板6主面方向に関し略同一の位置に枠状の溝が設けられ、全体として枠状溝38が形成されている。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

基板と、

基板上に配設された、加速度センサ素子および該センサ素子を囲む枠部と、

枠部上に配設された中間層と、

中間層と接合され、これにより加速度センサ素子を封止するキャップ部とを備え、

枠部および中間層にはそれぞれ、基板主面方向に関し略同一の位置に枠状の溝が設けてあることを特徴とする加速度センサ。

**【請求項 2】**

枠部および中間層にそれぞれ設けた溝が貫通溝であることを特徴とする請求項 1 の加速度センサ。 10

**【請求項 3】**

キャップ部には、中間層との接合領域において、上記枠部および中間層の溝と基板主面方向に関し略同一の位置に溝が設けてあることを特徴とする請求項 1 または 2 の加速度センサ。

**【請求項 4】**

基板と、

基板上に配設された、加速度センサ素子および該センサ素子を囲む枠部と、

枠部上に配設された中間層と、

中間層と接合され、これにより加速度センサ素子を封止するキャップ部とを備え、

枠部は、中間層とキャップ部との接合領域よりも加速度センサ素子側に延在する延在部を有し、該延在部に加速度センサ素子を囲むように枠状の溝が設けてあることを特徴とする加速度センサ。 20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は加速度センサに関する。

**【背景技術】****【0002】**

従来、加速度センサ素子および該センサ素子を囲む枠部を半導体基板上に備え、キャップを枠部に接合することで加速度センサ素子を気密封止した加速度センサが知られている(例えは、特許文献 1 参照。)。 30

**【特許文献 1】特開 2002-134759 号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

しかしながら、上記構成では、半導体基板上に加速度センサ素子および枠部とともに形成されているため、外力によるキャップと枠部の接合領域でのクラック、あるいは、接合領域でキャップと枠部の材料が異なる場合に両者の熱膨張係数の違いによって存在する残留応力が加速度センサ素子に伝播し易く、その結果、加速度センサの特性変動を引き起こすことがあった。 40

**【0004】**

そこで、本発明は、外力や残留応力によって特性変動の起きにくい加速度センサを提供することを目的とする。

**【課題を解決するための手段】****【0005】**

上記目的を達成するために、本発明に係る加速度センサの第 1 の態様は、

基板と、

基板上に配設された、加速度センサ素子および該センサ素子を囲む枠部と、

枠部上に配設された中間層と、

50

中間層と接合され、これにより加速度センサ素子を封止するキャップ部とを備え、

枠部および中間層にはそれぞれ、基板主面方向に関し略同一の位置に枠状の溝が設けて

あることを特徴とする。

#### 【0006】

本発明に係る加速度センサの第2の態様は、

基板と、

基板上に配設された、加速度センサ素子および該センサ素子を囲む枠部と、

枠部上に配設された中間層と、

中間層と接合され、これにより加速度センサ素子を封止するキャップ部とを備え、

枠部は、中間層とキャップ部との接合領域よりも加速度センサ素子側に延在する延在部

を有し、該延在部に加速度センサ素子を囲むように枠状の溝が設けてあることを特徴とす

る。

#### 【発明の効果】

#### 【0007】

本発明に係る第1の態様によれば、中間層と枠部に枠状の溝を設けることで、外力によ

ってキャップ部と枠部の接合領域でクラックが発生しても、溝でクラックの進行が止まる

ので、加速度センサの気密性が保たれ加速度センサ素子の特性変動は生じない。さらに、

中間層と枠部の枠状溝の位置を基板主面方向に関し略同一に設定してあるので、加速度セ

ンサの基板主面方向に関する寸法の小型化を図ることができる。

#### 【0008】

本発明に係る第2の態様によれば、枠部の延在部に加速度センサ素子を囲むように枠状

の溝を設けることで、中間層とキャップ部との接合における残留応力が溝を超えて伝播す

ることがなく、したがって加速度センサ素子の特性変動を防止できる。

#### 【発明を実施するための最良の形態】

#### 【0009】

以下、添付図面を参照して本発明に係る実施の形態を説明する。

#### 【0010】

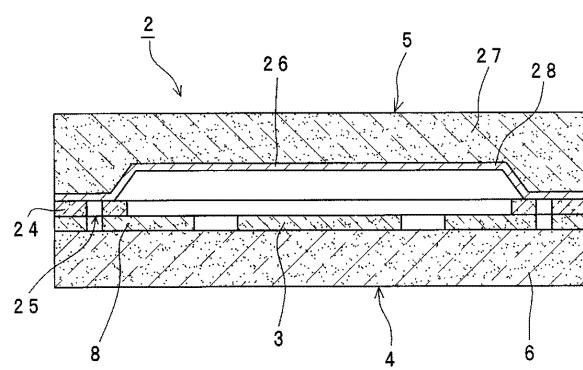

実施の形態1.

図1は、本発明に係る加速度センサの実施の形態1を示す断面図である。この加速度セ

ンサ2は、加速度センサ素子3を載置するためのベース部4と、ベース部4と接合してセ

ンサ素子3を気密封止するためのキャップ部5とを備える。

#### 【0011】

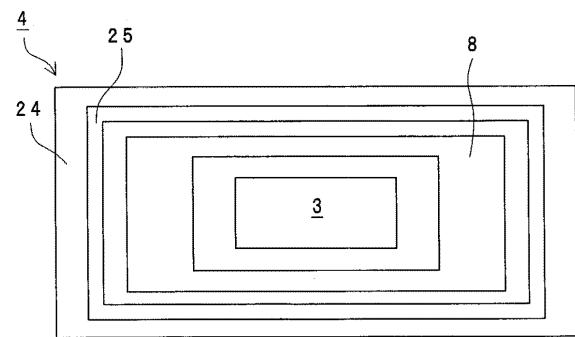

図2に上面図を示すベース部4は、矩形状のシリコン半導体基板6（広義には基板）を

備え、該基板6の主面上には、加速度を検出するためのセンサ素子3と該センサ素子3を

囲む枠部8とが設けてある。なお、枠部8は矩形状が一般的であるが、その形状は本発明

を限定しない。加速度センサ素子3および枠部8は、例えば、半導体基板6上に、不純物

としてリンがドーピングされたポリシリコン層を堆積した後、ポリシリコンをエッチング

などにより選択的に除去して形成される。ドーパントとして、リン以外に例えばガリウム

、ボロン、ヒ素などでもよい。

#### 【0012】

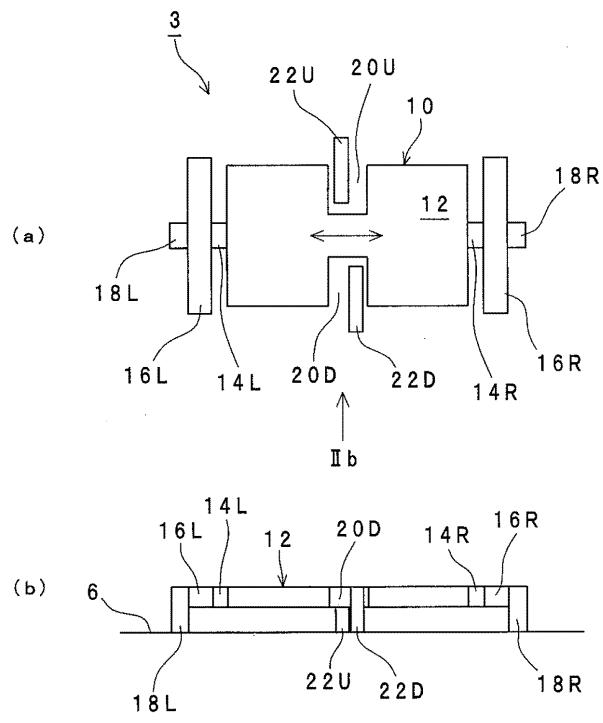

図3(a), (b)は、加速度センサ素子3を示す拡大図である。加速度センサ素子3

は容量式の加速度センサ素子で、外力によって変位する重り部10を備える。重り部10

は、半導体基板6主面と所定の間隔をあけて図3(a)左右方向を長手方向、上下方向を

短手方向とした略矩形状の可動電極12を有する。可動電極12は、各短辺から長手方向

にそれぞれ突出した突出部14L, 14R、さらに短手方向に伸びた梁部16L, 16Rを介して、

半導体基板6主面上に固定された支持部18L, 18Rに連結されている。梁部16L, 16Rは、

図3(a)上下方向長さに比べて左右方向長さ（幅）が短く左右方向に僅かに伸縮可能で、

その結果、加速度センサ2が左右方向に外力を受けた場合に、可動電極12が左右方向に

変位できるようになっている。可動電極12には、各長辺中央からそれぞれ短手方向に

伸びた所定の大きさの溝20U, 20Dが形成されている。

10

20

30

40

50

各溝 20U, 20D 内にはそれぞれ、半導体基板 6 主面上に固定された固定電極 22U, 22D が配置されている。加速度センサ 2 が外力を受けて固定電極 22U と溝 20U を形成する可動電極 12 部分内面の隙間および固定電極 22D と溝 20D を形成する可動電極 12 部分内面の隙間が変化することで、可動電極 12 と各固定電極 22U, 22D の間の静電容量が変化する（上述したように、可動電極 12 および固定電極 22U, 22D を形成するポリシリコンには、電気的導通を図るためにリソーフィングされている。）。静電容量の変化は、電気信号として外部の容量計測回路（図示せず）に出力される。

#### 【0013】

加速度センサ素子 3 の構成は本発明を限定するものではなく、例えば可動電極が半導体基板 6 の主面方向に垂直な方向に変位できるものでもよい。また、容量式に限らず、ピエゾ抵抗式でもよい。10

#### 【0014】

図 1, 2 に戻って、枠部 8 上にはノンドープのポリシリコン層 24 が形成されている。ポリシリコン層 24 は、例えば CVD 法により成膜した例えはシリコン酸化膜で、枠部 8 を形成するポリシリコンに含まれるリソーフィングが拡散してポリシリコン層 24 とキャップ部 5 との接合界面に到達して析出することがないようにその厚みが設定されている。ポリシリコン層 24 は、枠部 8 とキャップ部 5 との間の中間層を構成する。枠部 8 とポリシリコン層 24 には、主面方向に関して略同一位置に枠状の貫通溝がそれぞれ形成され、全体として枠状の溝 25 を構成している。

#### 【0015】

キャップ部 5 は、シリコンの矩形状半導体基板から例えはザグリ加工により凹部 26 が形成されたキャップ（本体）27 を備え、凹部 26 を形成する側の主面には金属層 28 が形成されている。金属層 28 は、キャップ 27 に、例えはチタン膜、続いてニッケル膜を例えは蒸着やスパッタリングで形成する。チタン膜とニッケル膜の厚さは、ポリシリコン層 24 との間の接合の強さおよび膜形成に伴って生じる残留応力を考慮して、それぞれ数十 nm、数百 nm が適当である。20

#### 【0016】

加速度センサ 2 の製造時、ベース部 4 のポリシリコン層 24 とキャップ部 5 の金属層 28 を重ね合わせる。この状態で、真空下あるいは不活性ガス下の加熱炉内にベース部 4 およびキャップ部 5 を入れ、400°C で数十分から数時間加熱する。その結果、ポリシリコン層 24 のポリシリコンと金属層 28 のニッケルとが共晶合金を形成し、ベース部 4 とキャップ部 5 の接合が行われる。このとき、ベース部 4 のドーピングされた枠部 8 と金属層 28 の間にはノンドープのポリシリコン層 24 が介在されているので、枠部 8 を形成するポリシリコンに含まれるリソーフィングは、ノンドープのポリシリコン層 24 に拡散してもポリシリコン層 24 と金属層 28 との接合界面にリソーフィングが到達して析出することはない。その結果、ベース部 4 とキャップ部 5 の接合不良を防止できる。30

#### 【0017】

かかる構成を備えた加速度センサ 2 は、ベース部 4 とキャップ部 5 との接合領域が多層構造となっているために、外力の影響を受けやすい。例えば、加速度センサ 2 を金属フレーム（図示せず）上に熱を加えてダイボンドする場合、シリコン半導体基板 6 と金属フレームの接着となるため両者の熱膨張係数の差から生じる残留応力、ダイボンド工程後に加速度センサ 2 等を封止するためのモールド工程時には、モールド樹脂を射出する圧力、加速度センサ 2 を搭載したデバイスの完成後には、加速度センサ 2 が置かれる環境（例えは熱履歴や湿気）によるモールドやダイボンドの劣化に伴う応力の変化などが外力として挙げられる。40

#### 【0018】

溝 25 を有さない従来の構成では、上記外力により接合領域の各層間（半導体基板 6 と枠部 8 の間および枠部 8 とポリシリコン層 24 の間）でクラックが発生して、気密封止が破れ、加速度センサ素子 3 の特性が変動する場合がある。また、クラックに到らなくても、応力が枠部 8 や半導体基板 6 を通じて加速度センサ素子 3 まで伝播し、加速度センサ素50

子 3 の特性変動を引き起こす可能性がある。

【 0 0 1 9 】

これに対し、本実施形態の構成では、外力によりクラックが生じた場合でも溝 2 5 でクラックの進行が止まるので、センサ 2 の気密性は保たれセンサ素子 3 の特性変動は生じない。応力もまた、溝 2 5 を超えて伝播しないので、センサ素子 3 の特性変動に影響を与えない。したがって、溝 2 5 を設けることで高信頼性の加速度センサ 2 を提供できる。

【 0 0 2 0 】

本実施形態ではまた、枠部 8 に設けた枠状の溝とポリシリコン層 2 4 に設けた枠状の溝は、互いに重なる位置に配設しているので、加速度センサ 2 の半導体基板 6 の主面方向に関する寸法の小型化を図ることができる。

10

【 0 0 2 1 】

実施の形態 2 .

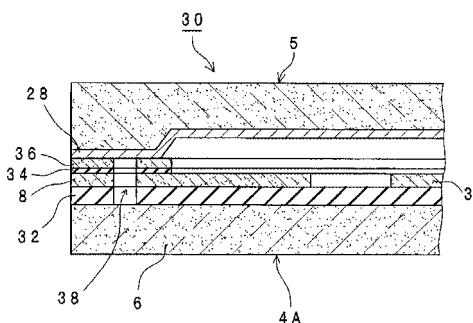

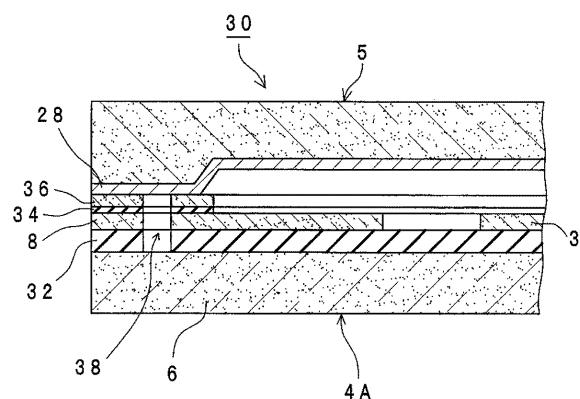

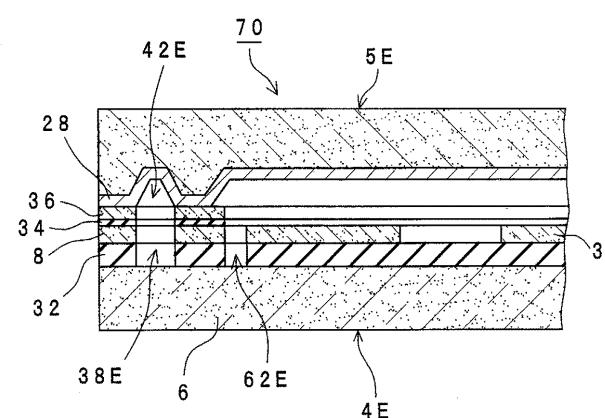

図 4 は、本発明に係る加速度センサの実施の形態 2 を示す部分拡大断面図である。以下の説明では、実施の形態 1 と同一または類似の構成要素は同一の符号または同一の符号に適当な添字を付して表す。

【 0 0 2 2 】

本実施形態に係る加速度センサ 3 0において、半導体基板 6 の主面上には絶縁層 3 2 が形成されている。絶縁層 3 2 は、半導体基板 6 上に、例えばまずシリコン酸化膜、続いてシリコン窒化膜を例えば C V D 法を用いて形成する。加速度センサ素子 3 と枠部 8 はこの絶縁層 3 2 上に形成され、これらの間が電気的に絶縁されている。

20

【 0 0 2 3 】

金属層 2 8 と枠部 8 の間には、実施の形態 1 のように所定の厚みのポリシリコン層 2 4 を介在させる代わりに、拡散防止層としての絶縁層 3 4 およびノンドープのポリシリコン層 3 6 (これら層 3 4 、 3 6 が枠部 8 とキャップ部 5 の間の中間層を構成する。)を介在させる。このために、ベース部 4 A の製造工程時、枠部 8 上に絶縁層 3 4 を例えば C V D 法により、続いてポリシリコン層 3 6 を例えばスパッタリングにより形成する。次に、ベース部 4 A のポリシリコン層 3 6 とキャップ部 5 の金属層 2 8 を重ね合わせる。この状態で、実施の形態 1 と同様にして、ポリシリコン層 3 6 のポリシリコンと金属層 2 8 のニッケルとが共晶合金を形成するように加熱し、ベース部 4 A とキャップ部 5 の接合を行わせる。ポリシリコン層 3 6 と枠部 8 の間には拡散防止層 3 4 が介在されているので、枠部 8 を形成するシリコンに含まれるリンがノンドープのポリシリコン層 3 6 に拡散してポリシリコン層 3 6 と金属層 2 8 の界面に析出するのを防止できる。

30

【 0 0 2 4 】

絶縁層 3 2 、枠部 8 、絶縁層 3 4 、およびポリシリコン層 3 6 には、主面方向に関して略同一位置に枠状の貫通溝がそれぞれ形成され、全体として枠状の溝 3 8 を構成している。

【 0 0 2 5 】

かかる構成を備えた加速度センサ 3 0 は、ベース部 4 A とキャップ部 5 の接合領域が多層構造となっているために外力の影響を受けやすいが、外力によりクラックが生じた場合でも溝 3 8 でクラックの進行が止まるので、加速度センサ 3 0 の気密性は保たれ加速度センサ素子 3 の特性変動は生じない。応力もまた、溝 3 8 を超えて伝播しないので、加速度センサ素子 3 の特性変動に影響を与えない。したがって、溝 3 8 を設けることで高信頼性の加速度センサ 3 0 を提供できる。

40

【 0 0 2 6 】

本実施形態ではまた、絶縁層 3 2 、枠部 8 、絶縁層 3 4 、およびポリシリコン層 3 6 にそれぞれ設けた枠状の溝は、互いに重なる位置に配設しているので、加速度センサ 3 0 の半導体基板 6 の主面方向に関する寸法の小型化を図ることができる。

【 0 0 2 7 】

半導体基板 6 にも絶縁層 3 2 、枠部 8 、絶縁層 3 4 、およびポリシリコン層 3 6 と主面方向に関して略同一位置に枠状の溝を形成し、これにより、各層 3 2 , 8 , 3 4 , 3 6 と

50

ともに枠状の溝 3 8 を構成するようにしてもよい。溝 3 8 が半導体基板 6 まで至る構成は、応力の伝播距離が絶縁層 3 2 まで溝を設けた場合より長くなり、したがって上述の応力の伝播を防止する効果を増すことができるだけでなく、絶縁層 3 2 と半導体基板 6 との間で発生し得るクラックの進行および応力の伝播を防止する効果を有する。

#### 【 0 0 2 8 】

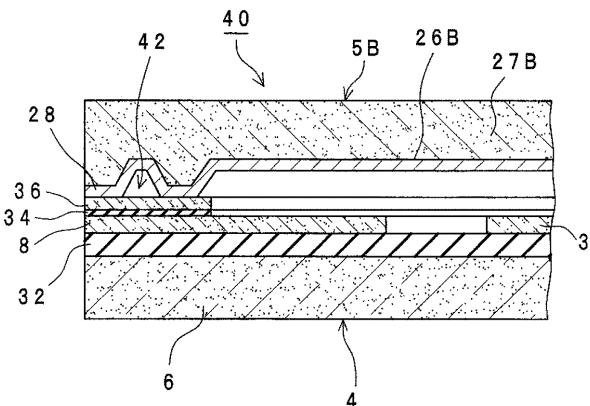

実施の形態 3 .

図 5 は、本発明に係る加速度センサの実施の形態 3 を示す部分拡大断面図である。本実施形態に係る加速度センサ 4 0 は、実施の形態 2 の加速度センサ 3 0 の構成と類似しているが、ベース部 4 に溝 3 8 を設ける代わりに、キャップ本体 2 7 B の接合領域に枠状の溝 4 2 を設ける。溝 4 2 は、凹部 2 6 B と同一工程（例えばザグリ加工）で形成してもよい 10 し、別工程（例えばエッティング）で形成してもよい。

#### 【 0 0 2 9 】

応力はキャップ部 5 B 側を伝播する場合もあるが、本実施形態のように溝 4 2 を設けることで、応力は溝 4 2 を超えて伝播しないので、センサ素子 3 の特性変動に影響を与えず、したがって高信頼性の加速度センサ 4 0 を提供できる。

#### 【 0 0 3 0 】

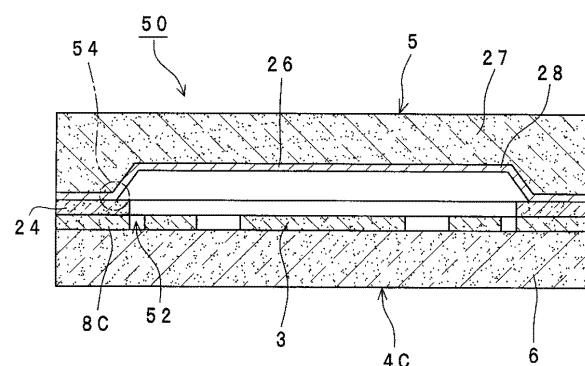

実施の形態 4 .

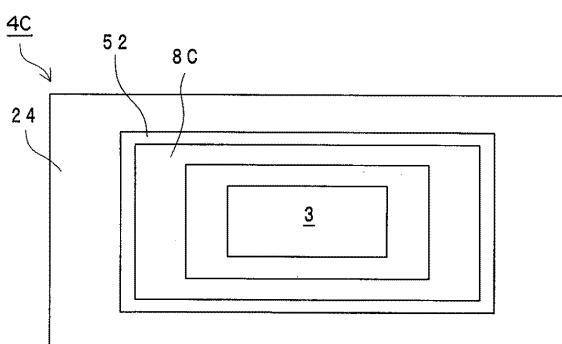

図 6 は、本発明に係る加速度センサの実施の形態 4 を示す断面図である。図 7 は、本実施形態に係る加速度センサ 5 0 のベース部 4 C の上面図である。速度センサ 5 0 は、実施の形態 1 の加速度センサ 2 と類似の構成を有するが、ベース部とキャップ部との接合領域に溝 2 5 を設ける代わりに、接合領域よりも加速度センサ素子 3 側に延在した枠部 8 C 部分（すなわち接合領域と加速度センサ素子 3 との間）に枠状の溝 5 2 を設けたものである。

20

#### 【 0 0 3 1 】

ベース部 4 C とキャップ部 5 の接合においてポリシリコン層 2 4 と金属層 2 8 の材料（シリコンとニッケル）の熱膨張係数の差により生じる残留応力は、ポリシリコン層 2 4 と金属層 2 8 の接合端部 5 4 が最大となる。したがって、溝 5 2 を設けない場合、残留応力が枠部 8 C 続いて半導体基板 6 を介して加速度センサ素子 3 に伝播し、該センサ素子 3 の特性変動が引き起こされる場合あるが、溝 5 2 を設けることで、応力は溝 5 2 を超えて伝播しないので、センサ素子 3 の特性変動に影響を与えず、したがって高信頼性の加速度センサ 5 0 を提供できる。

30

#### 【 0 0 3 2 】

半導体基板 6 にも枠部 8 C の枠状溝 5 2 と主面方向に関して略同一位置に枠状の溝を形成してもよい。

#### 【 0 0 3 3 】

実施の形態 5 .

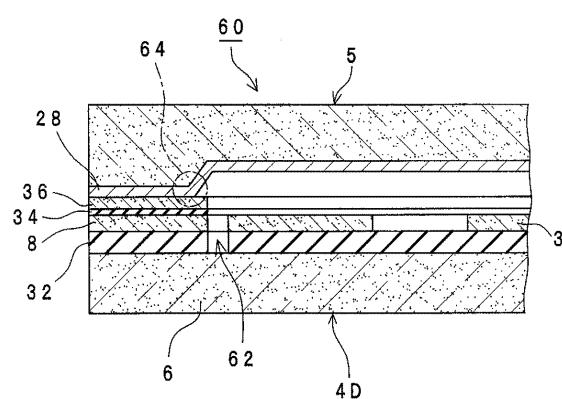

図 8 は、本発明に係る加速度センサの実施の形態 5 を示す断面図である。本実施形態に係る加速度センサ 6 0 は、実施の形態 2 の加速度センサ 3 0 と類似の構成を有するが、キャップ部とベース部との接合領域に溝 3 8 を設ける代わりに、接合領域よりも加速度センサ素子 3 側に延在した枠部 8 D 部分および絶縁層 3 2 （すなわち接合領域と加速度センサ素子 3 との間）に枠状の溝 6 2 を設けたものである。

40

#### 【 0 0 3 4 】

キャップ部 5 の金属層 2 8 とベース部 4 D のポリシリコン層 3 6 の接合においてニッケルとシリコンの熱膨張係数の差により生じる残留応力は、金属層 2 8 とポリシリコン層 3 6 の接合端部 6 4 が最大となる。したがって、溝 6 2 を設けない場合、残留応力がポリシリコン層 3 6 、絶縁層 3 4 、枠部 8 、絶縁層 3 2 、続いて半導体基板 6 を介して加速度センサ素子 3 に伝播し、該センサ素子 3 の特性変動が引き起こされる場合あるが、溝 6 2 を設けることで、応力は溝 6 2 を超えて伝播しないので、加速度センサ素子 3 の特性変動に影響を与えず、したがって高信頼性の加速度センサ 6 0 を提供できる。

#### 【 0 0 3 5 】

10

20

30

40

50

半導体基板 6 にも絶縁層 3 2、枠部 8 D と正面方向に関して略同一位置に枠状の溝を形成し、これにより、各層 3 2, 8 D とともに枠状の溝 6 2 を構成するようにしてもよい。

### 【0036】

#### 実施の形態 6 .

図 9 は、本発明に係る加速度センサの実施の形態 6 を示す断面図である。本実施形態に係る加速度センサ 7 0 は、実施の形態 2, 3, 5 と同様の溝 3 8 E, 4 2 E, 6 2 E を備えたものである。ベース部 4 E の溝 3 8 E とキャップ部 5 E の溝 4 2 E は、半導体基板 6 の正面方向に関して略同一位置に形成され、加速度センサ 7 0 の正面方向に関する寸法の小型化が図られている。

### 【0037】

溝 6 2 E を設ければ、溝 3 8 E, 4 2 E を設けなくても加速度センサ素子 3 への応力の伝播は防止できるが、溝 3 8 E, 4 2 E は主としてクラックによって加速度センサ 7 0 の気密封止が破れるのを防止するためのものである。

### 【0038】

以上、本発明の具体的な実施形態を説明したが、本発明はこれらに限らず種々改変可能である。例えば、枠部および枠部 - キャップ部間に配置される中間層（例えば、実施の形態 1 であればポリシリコン層 2 4 であり、実施の形態 2 であれば少なくとも絶縁層 3 4 を含む層）にそれぞれ形成する枠状の溝は、半導体基板正面方向に関して略同一の位置に配設するのであれば、連通していない場合（中間層に形成する枠状溝が貫通溝でない場合）も本発明の範囲内に含まれる。但し、別工程で作製したベース部とキャップ部を接合する点や溝の形成のし易さの点などを考慮して、中間層に形成する溝は、中間層とキャップ部との接合界面に開放されているのが好ましい。また、ベース部とキャップ部との接合領域の各層間に発生し得るクラックや残留応力に対応するために、枠部および中間層の各溝は貫通溝であるのが好ましい。これは、溝の形成のし易さの点からも有利である。

### 【0039】

さらに、実施の形態 2, 6 において半導体基板に直に形成する絶縁層に溝を設けない構成も、本発明の範囲内に含まれる。

### 【0040】

加えて、中間層とキャップとの接合領域よりも内側に延在する部分に形成する枠状の溝は、貫通溝でない構成も本発明の範囲内に含まれる。

### 【図面の簡単な説明】

#### 【0041】

【図 1】本発明に係る加速度センサの実施の形態 1 を示す断面図。

【図 2】図 1 のベース部を示す上面図。

【図 3】( a ) 図 1 の加速度センサ素子を示す上面図。( b ) 図 3 ( a ) の I I I b 方向から見た加速度センサ素子の側面図。

【図 4】本発明に係る加速度センサの実施の形態 2 を示す部分拡大断面図。

【図 5】本発明に係る加速度センサの実施の形態 3 を示す部分拡大断面図。

【図 6】本発明に係る加速度センサの実施の形態 4 を示す断面図。

【図 7】図 6 のベース部を示す上面図。

【図 8】本発明に係る加速度センサの実施の形態 5 を示す部分拡大断面図。

【図 9】本発明に係る加速度センサの実施の形態 6 を示す部分拡大断面図。

### 【符号の説明】

#### 【0042】

3 加速度センサ素子

4 A ベース部

5 キャップ部

6 半導体基板

8 枠部

2 8 金属層

3 0 加速度センサ

3 4 絶縁層

3 6 ノンドープのポリシリコン層

3 8 枠状の溝

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】