(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5309672号

(P5309672)

(45) 発行日 平成25年10月9日(2013.10.9)

(24) 登録日 平成25年7月12日(2013.7.12)

|                |                      |

|----------------|----------------------|

| (51) Int.Cl.   | F 1                  |

| HO 1 L 21/336  | (2006.01)            |

| HO 1 L 29/786  | (2006.01)            |

| HO 1 L 21/768  | (2006.01)            |

| HO 1 L 21/3205 | (2006.01)            |

| HO 1 L 23/522  | (2006.01)            |

|                | HO 1 L 29/78 6 1 2 D |

|                | HO 1 L 29/78 6 2 6 C |

|                | HO 1 L 29/78 6 1 9 A |

|                | HO 1 L 29/78 6 2 7 D |

|                | HO 1 L 21/88 Z       |

請求項の数 16 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2008-109998 (P2008-109998)

(22) 出願日 平成20年4月21日 (2008.4.21)

(65) 公開番号 特開2009-260166 (P2009-260166A)

(43) 公開日 平成21年11月5日 (2009.11.5)

審査請求日 平成22年11月10日 (2010.11.10)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(72) 発明者 保苅 一志

東京都羽村市栄町3丁目2番1号

カシオ計算機株式会社

羽村技術センター内

審査官 井上 弘亘

(56) 参考文献 特開平10-206896 (JP, A)

特開2004-349513 (JP, A)

最終頁に続く

(54) 【発明の名称】薄膜素子およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の貫通孔を有する絶縁膜と、

前記第1の貫通孔の内壁面に付着するように設けられた有底筒状の領域を有した薄膜と、

前記薄膜上及び前記絶縁膜上に設けられた補強膜と、

前記補強膜上に接着層を介して設けられた基板と、

を備え、

前記絶縁膜は、下地絶縁膜及び当該下地絶縁膜上に設けられたゲート絶縁膜を有し、

前記下地絶縁膜上に、ゲート電極及び当該ゲート電極に接続されたゲート配線が設けられ、

前記ゲート絶縁膜上に、前記ゲート絶縁膜に設けられたコンタクトホールを介して前記ゲート配線の一端部で接続されたゲート配線用中継配線及び当該ゲート配線用中継配線に接続されたゲート配線用外部接続端子が設けられ、

前記ゲート配線用外部接続端子は、前記ゲート絶縁膜及び前記下地絶縁膜に設けられた第3の貫通孔の内壁面、当該第3の貫通孔の下部及び当該第3の貫通孔の周囲における前記ゲート絶縁膜の上面に設けられ、

前記ゲート配線用外部接続端子上及び前記ゲート絶縁膜上に前記補強膜が設けられ、

前記第3の貫通孔の下部に設けられた前記ゲート配線用外部接続端子は、前記下地絶縁膜の下側に突出されている、

10

20

ことを特徴とする薄膜素子。

【請求項 2】

前記ゲート電極上における前記ゲート絶縁膜上に半導体薄膜が設けられ、

前記半導体薄膜上にソース電極及びドレイン電極が設けられ、

前記ゲート絶縁膜及び前記下地絶縁膜に前記第1の貫通孔が設けられ、

前記第1の貫通孔の内壁面、前記第1の貫通孔の下部及び前記第1の貫通孔の周囲における前記ゲート絶縁膜の上面に前記薄膜としての画素電極が前記ソース電極に接続されて設けられ、

前記画素電極上、前記ソース電極上、前記ドレイン電極上及び前記ゲート絶縁膜上に前記補強膜が設けられている、

ことを特徴とする請求項1に記載の薄膜素子。

10

【請求項 3】

前記ゲート絶縁膜上に前記ドレイン電極に接続されたドレイン配線及び当該ドレイン配線の一端部で接続されたドレイン配線用外部接続端子が設けられ、

前記ドレイン配線用外部接続端子は前記ゲート絶縁膜及び前記下地絶縁膜に設けられた第2の貫通孔の内壁面、当該第2の貫通孔の下部及び当該第2の貫通孔の周囲における前記ゲート絶縁膜の上面に設けられ、

前記ドレイン配線用外部接続端子上及び前記ゲート絶縁膜上に前記補強膜が設けられ、

前記第2の貫通孔の下部に設けられた前記ドレイン配線用外部接続端子は前記下地絶縁膜の下側に突出されている、

20

ことを特徴とする請求項2に記載の薄膜素子。

【請求項 4】

前記第1の貫通孔の下部に設けられた前記画素電極は前記下地絶縁膜の下側に突出されている、

ことを特徴とする請求項2に記載の薄膜素子。

【請求項 5】

前記第1の貫通孔の下部に設けられた前記画素電極の突出部分の下面は平坦となっている、

ことを特徴とする請求項4に記載の薄膜素子。

【請求項 6】

前記補強膜は無機材料を有する、

ことを特徴とする請求項1乃至5のいずれかに記載の薄膜素子。

30

【請求項 7】

前記基板はフィルム基板である、

ことを特徴とする請求項1乃至6のいずれかに記載の薄膜素子。

【請求項 8】

仮基板上に分離層を形成する工程と、

前記分離層上に絶縁膜を形成する工程と、

前記絶縁膜に第1の貫通孔を形成し、且つ、当該第1の貫通孔に対応する部分における前記分離層の上面側に第1の凹部を形成する工程と、

40

前記第1の貫通孔の内壁面に付着することで前記貫通孔に対応する領域が有底筒状になるように薄膜を形成する工程と、

前記薄膜上及び前記絶縁膜上に補強膜を形成する工程と、

前記補強膜上に接着層を介して基板を接着する工程と、

前記仮基板及び前記分離層を除去する工程と、

を有し、

前記絶縁膜を形成する工程は、前記分離層上に下地絶縁膜を形成し、当該下地絶縁膜上にゲート電極及び当該ゲート電極に接続されたゲート配線を形成し、当該ゲート電極上、当該ゲート配線上及び当該下地絶縁膜上にゲート絶縁膜を形成する工程を含み、

前記ゲート電極上における前記ゲート絶縁膜上に半導体薄膜を形成する工程を有し、

50

前記半導体薄膜上にソース電極及びドレイン電極を形成する工程を有し、

前記第1の貫通孔及び前記第1の凹部を形成する工程は、前記ゲート絶縁膜及び前記下地絶縁膜に第3の貫通孔を形成し、且つ、前記第3の貫通孔に対応する部分における前記分離層の上面側に第3の凹部を形成し、さらに、前記ゲート配線の一端部に対応する部分における前記ゲート絶縁膜にコンタクトホールを形成する工程を含み、

前記ソース電極及び前記ドレイン電極を形成する工程は、前記ゲート絶縁膜上に前記コンタクトホールを介して前記ゲート配線の一端部で接続されたゲート配線用中継配線を形成し、且つ、前記第3の貫通孔の内壁面、前記第3の凹部及び前記第3の貫通孔の周囲における前記ゲート絶縁膜の上面に前記ゲート配線用中継配線に接続されたゲート配線用外部接続端子を形成する工程を含み、

前記補強膜を形成する工程は、前記ソース電極上、前記ドレイン電極上、前記ゲート配線用外部接続端子上及び前記ゲート絶縁膜上に前記補強膜を形成する工程を含む、

ことを特徴とする薄膜素子の製造方法。

【請求項9】

前記第1の貫通孔及び前記第1の凹部を形成する工程は、前記ゲート絶縁膜及び前記下地絶縁膜に前記第1の貫通孔を形成し、且つ、前記第1の貫通孔に対応する部分における前記分離層の上面側に前記第1の凹部を形成する工程であり、

前記薄膜を形成する工程は、前記第1の貫通孔の内壁面、前記第1の凹部内及び前記第1の貫通孔の周囲における前記ゲート絶縁膜の上面に前記薄膜としての画素電極を前記ソース電極に接続させて形成する工程であり、

前記補強膜を形成する工程は、前記画素電極上及び前記ゲート絶縁膜上に前記補強膜を形成する工程を含む、

ことを特徴とする請求項8に記載の薄膜素子の製造方法。

【請求項10】

前記第1の貫通孔及び前記第1の凹部を形成する工程は、前記ゲート絶縁膜及び前記下地絶縁膜に第2の貫通孔を形成し、且つ、前記第2の貫通孔に対応する部分における前記分離層の上面側に第2の凹部を形成する工程を含み、

前記ソース電極及び前記ドレイン電極を形成する工程は、前記ゲート絶縁膜上に前記ドレイン電極に接続されたドレイン配線を形成し、且つ、前記第2の貫通孔の内壁面、前記第2の凹部内及び前記第2の貫通孔の周囲における前記ゲート絶縁膜の上面に前記ドレイン配線の一端部で接続されたドレイン配線用外部接続端子を形成する工程を含み、

前記補強膜を形成する工程は、前記ドレイン配線用外部接続端子上及び前記ゲート絶縁膜上に前記補強膜を形成する工程を含む、

ことを特徴とする請求項9に記載の薄膜素子の製造方法。

【請求項11】

前記補強膜は無機材料によって形成する、

ことを特徴とする請求項8乃至10のいずれかに記載の薄膜素子の製造方法。

【請求項12】

前記補強膜はプラズマCVD法により形成する、

ことを特徴とする請求項8乃至11のいずれかに記載の薄膜素子の製造方法。

【請求項13】

前記分離層はアモルファスシリコンによって形成し、

前記仮基板及び前記分離層を除去する工程は、

前記仮基板の下側からレーザビームを照射して前記分離層から前記仮基板を剥離可能な状態とする工程と、

前記分離層から前記仮基板を剥離して除去する工程と、

前記分離層をエッティングして除去する工程と、

を含む、

ことを特徴とする請求項8乃至12のいずれかに記載の薄膜素子の製造方法。

【請求項14】

10

20

30

40

50

前記分離層は酸化亜鉛によって形成し、

前記仮基板及び前記分離層を除去する工程は、前記分離層をエッチングして除去することにより、前記仮基板を自然に剥離して除去する工程である、

ことを特徴とする請求項 8 乃至 12 のいずれかに記載の薄膜素子の製造方法。

**【請求項 15】**

前記仮基板はガラス基板である、

ことを特徴とする請求項 8 乃至 14 のいずれかに記載の薄膜素子の製造方法。

**【請求項 16】**

前記基板はフィルム基板である、

ことを特徴とする請求項 8 乃至 15 のいずれかに記載の薄膜素子の製造方法。

10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は薄膜素子およびその製造方法に関する。

**【背景技術】**

**【0002】**

従来の薄膜素子には、基板として、製造工程時の温度に耐えることができない材料によって形成したものを用いたものがある（例えば、特許文献1参照）。この場合の製造方法としては、まず、製造工程時の温度に耐えることができる材料からなる仮基板上に分離層を形成している。次に、分離層上に薄膜素子構成体を形成している。次に、薄膜素子構成体上に、製造工程時の温度に耐えることができない材料からなる基板を接着層を介して接着している。次に、仮基板および分離層を除去している。

20

**【0003】**

**【特許文献1】特開2004-140382号公報**

**【0004】**

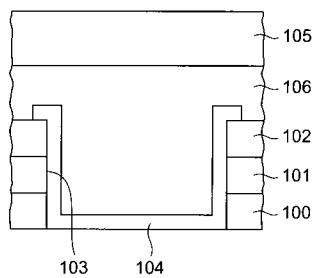

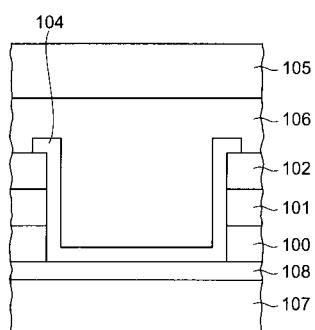

ところで、特許文献1には、液晶表示装置の薄膜トランジスタパネルに適用したものが記載されている（特許文献1の図23～図27参照）。この薄膜トランジスタパネルの完成した状態における画素電極の部分は、本願の図21に示すような構造となっている。すなわち、酸化シリコンからなる下地絶縁膜100の上面には酸化シリコンからなる層間絶縁膜101が設けられている。層間絶縁膜101の上面には酸化シリコンからなる保護膜102が設けられている。

30

**【0005】**

保護膜102、層間絶縁膜101および下地絶縁膜100の所定の箇所には貫通孔103が設けられている。貫通孔103の内壁面、貫通孔103の下部および貫通孔103の周囲における保護膜102の上面には有底筒状の画素電極（薄膜）104が設けられている。画素電極104および保護膜102の上面には、製造工程時の温度に耐えることができない材料からなる基板105が接着層106を介して接着されている。

30

**【0006】**

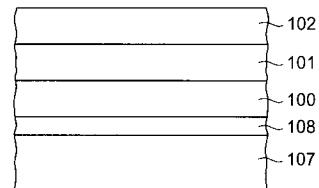

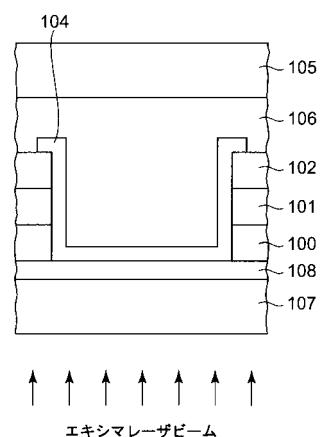

次に、この薄膜トランジスタパネルの画素電極104の部分の製造方法について説明する。まず、図22に示すように、製造工程時の温度に耐えることができる材料からなる仮基板107の上面にアモルファスシリコンからなる分離層108、酸化シリコンからなる下地絶縁膜100、酸化シリコンからなる層間絶縁膜101および酸化シリコンからなる保護膜102を形成する。

40

**【0007】**

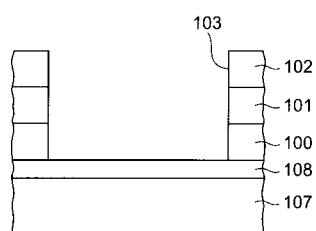

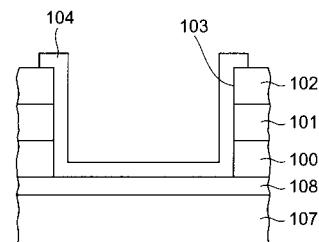

次に、図23に示すように、保護膜102、層間絶縁膜101および下地絶縁膜100の所定の箇所に、フォトリソグラフィ法により、貫通孔103を形成する。次に、図24に示すように、貫通孔103の内壁面、貫通孔103の下部および貫通孔103の周囲における保護膜102の上面に有底筒状の画素電極104をパターン形成する。

**【0008】**

次に、図25に示すように、画素電極104および保護膜102の上面に基板105を

50

接着層 106 を介して接着する。次に、図 26 に示すように、仮基板 107 の下側からエキシマレーザビームを照射することにより、分離層 108 から仮基板 107 を剥離可能な状態とする。次に、分離層 108 から仮基板 107 を剥離して除去する。次に、分離層 108 をエッティングして除去する。かくして、図 21 に示すものが得られる。

【発明の開示】

【発明が解決しようとする課題】

【0009】

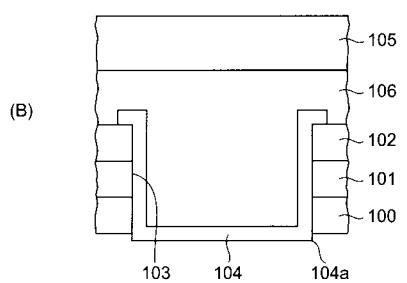

ところで、図 23 に示すように、保護膜 102、層間絶縁膜 101 および下地絶縁膜 100 の所定の箇所に、フォトリソグラフィ法により、貫通孔 103 を形成するとき、保護膜 102 等の材料である酸化シリコンと分離層 108 の材料であるアモルファスシリコンとの間にさほどエッティング選択比がとれないため、実際には、図 27 (A) に示すように、貫通孔 103 に対応する部分における分離層 108 の上面側にある程度の深さの凹部 109 が形成される。

【0010】

この結果、図 27 (B) に示すように、完成した状態では、貫通孔 103 の下部に形成された画素電極 104 は下地絶縁膜 100 の下側にやや突出される。この状態では、貫通孔 103 内に形成された有底筒状の画素電極 104 の内部には接着層 106 が充填されている。しかしながら、有底筒状の画素電極 104 の内底部周辺部まで接着層 106 が確実に充填されないおそれがある。このような場合には、画素電極 104 の厚さが例えは 0.05  $\mu\text{m}$  程度と極めて薄く、且つ、画素電極 104 の底部の面積が比較的大きいので、画素電極 104 の底部周辺部 104a が機械的に弱くなり、破損するおそれがあるという問題がある。

【0011】

そこで、この発明は、貫通孔内に設けられた有底筒状の薄膜の底部周辺部が破損しにくくすることができる薄膜素子およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

前記目的を果たすため、本発明の薄膜素子の一態様は、第 1 の貫通孔を有する絶縁膜と、前記第 1 の貫通孔の内壁面に付着するように設けられた有底筒状の領域を有した薄膜と、前記薄膜上及び前記絶縁膜上に設けられた補強膜と、前記補強膜上に接着層を介して設けられた基板と、を備え、前記絶縁膜は、下地絶縁膜及び当該下地絶縁膜上に設けられたゲート絶縁膜を有し、前記下地絶縁膜上に、ゲート電極及び当該ゲート電極に接続されたゲート配線が設けられ、前記ゲート絶縁膜上に、前記ゲート絶縁膜に設けられたコンタクトホールを介して前記ゲート配線の一端部で接続されたゲート配線用中継配線及び当該ゲート配線用中継配線に接続されたゲート配線用外部接続端子が設けられ、前記ゲート配線用外部接続端子は、前記ゲート絶縁膜及び前記下地絶縁膜に設けられた第 3 の貫通孔の内壁面、当該第 3 の貫通孔の下部及び当該第 3 の貫通孔の周囲における前記ゲート絶縁膜の上面に設けられ、前記ゲート配線用外部接続端子上及び前記ゲート絶縁膜上に前記補強膜が設けられ、前記第 3 の貫通孔の下部に設けられた前記ゲート配線用外部接続端子は、前記下地絶縁膜の下側に突出されている、ことを特徴とする。

また、前記目的を果たすため、本発明の薄膜素子の製造方法の一態様は、仮基板上に分離層を形成する工程と、前記分離層上に絶縁膜を形成する工程と、前記絶縁膜に第 1 の貫通孔を形成し、且つ、当該第 1 の貫通孔に対応する部分における前記分離層の上面側に第 1 の凹部を形成する工程と、前記第 1 の貫通孔の内壁面に付着することで前記貫通孔に対応する領域が有底筒状になるように薄膜を形成する工程と、前記薄膜上及び前記絶縁膜上に補強膜を形成する工程と、前記補強膜上に接着層を介して基板を接着する工程と、前記仮基板及び前記分離層を除去する工程と、を有し、前記絶縁膜を形成する工程は、前記分離層上に下地絶縁膜を形成し、当該下地絶縁膜上にゲート電極及び当該ゲート電極に接続されたゲート配線を形成し、当該ゲート電極上、当該ゲート配線上及び当該下地絶縁膜上にゲート絶縁膜を形成する工程を含み、前記ゲート電極上における前記ゲート絶縁膜上に

10

20

30

40

50

半導体薄膜を形成する工程を有し、前記半導体薄膜上にソース電極及びドレイン電極を形成する工程を有し、前記第1の貫通孔及び前記第1の凹部を形成する工程は、前記ゲート絶縁膜及び前記下地絶縁膜に第3の貫通孔を形成し、且つ、前記第3の貫通孔に対応する部分における前記分離層の上面側に第3の凹部を形成し、さらに、前記ゲート配線の一端部に対応する部分における前記ゲート絶縁膜にコンタクトホールを形成する工程を含み、前記ソース電極及び前記ドレイン電極を形成する工程は、前記ゲート絶縁膜上に前記コンタクトホールを介して前記ゲート配線の一端部で接続されたゲート配線用中継配線を形成し、且つ、前記第3の貫通孔の内壁面、前記第3の凹部及び前記第3の貫通孔の周囲における前記ゲート絶縁膜の上面に前記ゲート配線用中継配線に接続されたゲート配線用外部接続端子を形成する工程を含み、前記補強膜を形成する工程は、前記ソース電極上、前記ドレイン電極上、前記ゲート配線用外部接続端子上及び前記ゲート絶縁膜上に前記補強膜を形成する工程を含む、ことを特徴とする。10

【発明の効果】

【0013】

この発明によれば、貫通孔内に設けられた有底筒状の薄膜の底部周辺部が破損しにくいようにすることができる。

【発明を実施するための最良の形態】

【0014】

(第1実施形態)

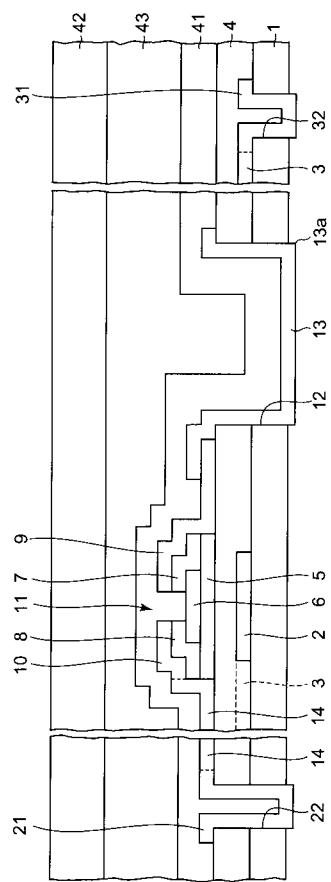

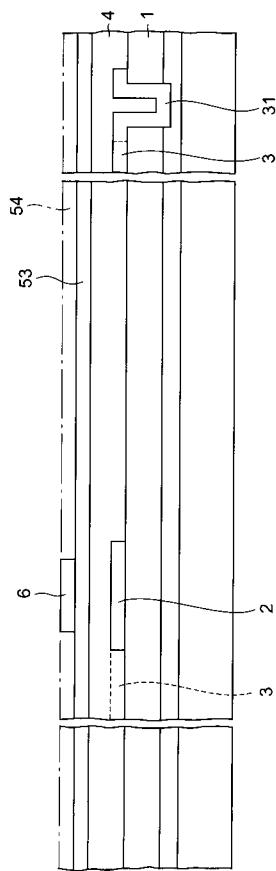

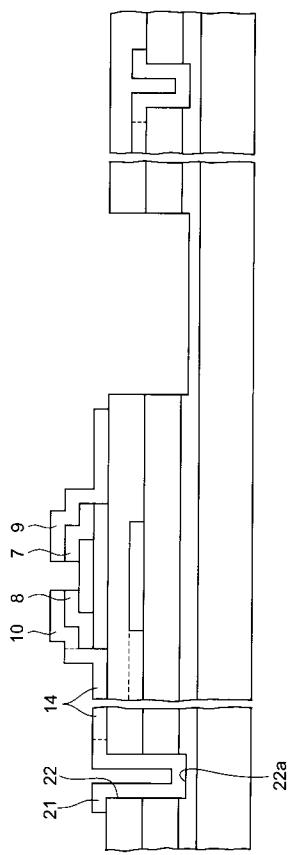

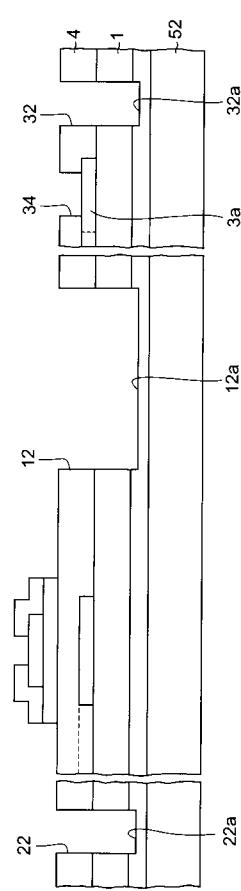

図1はこの発明の第1実施形態としての薄膜トランジスタパネルの要部の断面図を示す。この場合、図1の左側から右側に向かって、ドレン配線用外部接続端子21の部分の断面図、画素電極13を含む薄膜トランジスタ11の部分の断面図、ゲート配線用外部接続端子31の部分の断面図を示す。20

【0015】

まず、画素電極13を含む薄膜トランジスタ11の部分について説明する。窒化シリコン等の無機材料からなる下地絶縁膜1の上面の所定の箇所にはクロム等からなるゲート電極2および該ゲート電極2に接続されたゲート配線3が設けられている。ゲート電極2およびゲート配線3を含む下地絶縁膜1の上面には窒化シリコン等の無機材料からなるゲート絶縁膜4が設けられている。

【0016】

ゲート電極2上におけるゲート絶縁膜4の上面の所定の箇所には真性アモルファスシリコンからなる半導体薄膜5が設けられている。半導体薄膜5の上面ほぼ中央部には窒化シリコン等の無機材料からなるチャネル保護膜6が設けられている。チャネル保護膜6の上面両側およびその両側における半導体薄膜5の上面にはn型アモルファスシリコンからなるオーミックコンタクト層7、8が設けられている。30

【0017】

一方のオーミックコンタクト層7の上面およびその近傍におけるゲート絶縁膜4の上面にはクロム等からなるソース電極9が設けられている。他方のオーミックコンタクト層8の上面にはクロム等からなるドレン電極10が設けられている。ここで、ゲート電極2、ゲート絶縁膜4、半導体薄膜5、チャネル保護膜6、オーミックコンタクト層7、8、ソース電極9およびドレン電極10により、薄膜トランジスタ11が構成されている。40

【0018】

薄膜トランジスタ11の近傍におけるゲート絶縁膜4および下地絶縁膜1の所定の箇所には第1の貫通孔12が設けられている。第1の貫通孔12の内壁面、第1の貫通孔12の下部および第1の貫通孔12の周囲におけるゲート絶縁膜4の上面にはITOからなる有底筒状の画素電極(薄膜)13がソース電極9に接続されて設けられている。この場合、第1の貫通孔12の下部に設けられた画素電極13は下地絶縁膜1の下側にやや突出され、この突出部分の下面は平坦となっている。ゲート絶縁膜4の上面の所定の箇所にはクロム等からなるドレン配線14がドレン電極10に接続されて設けられている。

【0019】

次に、ドレイン配線用外部接続端子 2 1 の部分について説明する。ドレイン配線用外部接続端子 2 1 は、ゲート絶縁膜 4 および下地絶縁膜 1 の所定の箇所に設けられた第 2 の貫通孔 2 2 の内壁面、第 2 の貫通孔 2 2 の下部および第 2 の貫通孔 2 2 の周囲におけるゲート絶縁膜 4 の上面に設けられている。この場合、第 2 の貫通孔 2 2 の下部に設けられたドレイン配線用外部接続端子 2 1 は下地絶縁膜 1 の下側にやや突出され、この突出部分の下面是平坦となっている。ドレイン配線用外部接続端子 2 1 はドレイン配線 1 4 の一端部に接続されている。

【 0 0 2 0 】

次に、ゲート配線用外部接続端子 3 1 の部分について説明する。ゲート配線用外部接続端子 3 1 は、下地絶縁膜 1 の所定の箇所に設けられた第 3 の貫通孔 3 2 の内壁面、第 3 の貫通孔 3 2 の下部および第 3 の貫通孔 3 2 の周囲における下地絶縁膜 1 の上面に設けられている。この場合、第 3 の貫通孔 3 2 の下部に設けられたゲート配線用外部接続端子 3 1 は下地絶縁膜 1 の下側にやや突出され、この突出部分の下面是平坦となっている。ゲート配線用外部接続端子 3 1 はゲート配線 3 の一端部に接続されている。ゲート配線 3 を含むゲート配線用外部接続端子 3 1 の上面にはゲート絶縁膜 4 が設けられている。

【 0 0 2 1 】

次に、図 1 に示す全体について説明する。薄膜トランジスタ 1 1、画素電極 1 3、ドレイン配線 1 4、ドレイン配線用外部接続端子 2 1 およびゲート絶縁膜 4 の上面には窒化シリコン等の無機材料からなる補強膜 4 1 が設けられている。補強膜 4 1 の上面には、製造工程時の温度に耐えることができない材料であるポリイミド系樹脂等の有機樹脂からなるフィルム基板 4 2 の下面がエポキシ系樹脂等からなる接着層 4 3 を介して接着されている。

【 0 0 2 2 】

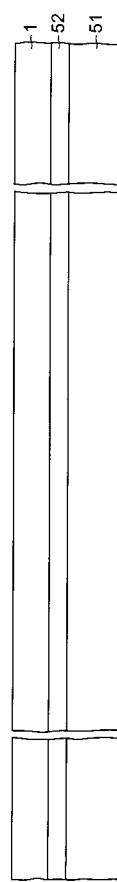

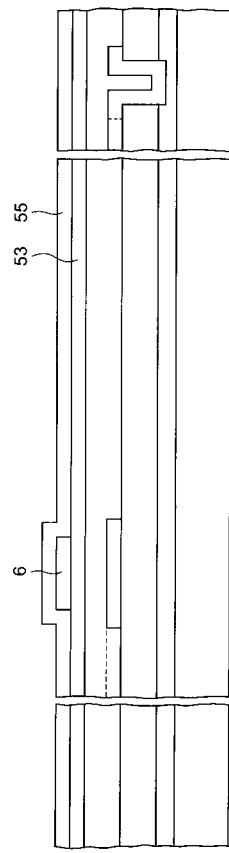

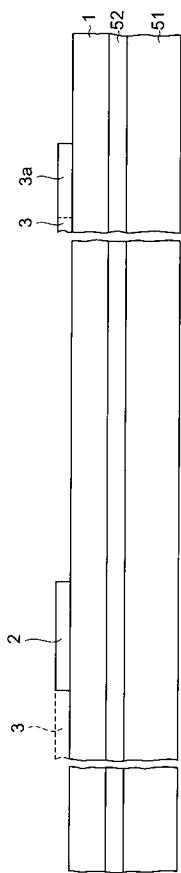

次に、この薄膜トランジスタバネルの製造方法の一例について説明する。まず、図 2 に示すように、製造工程時の温度に耐えることができる材料であるガラス基板等からなる仮基板 5 1 の上面に、プラズマ CVD 法により、アモルファスシリコンからなる分離層 5 2 および窒化シリコン等の無機材料からなる下地絶縁膜 1 を連続して成膜する。

【 0 0 2 3 】

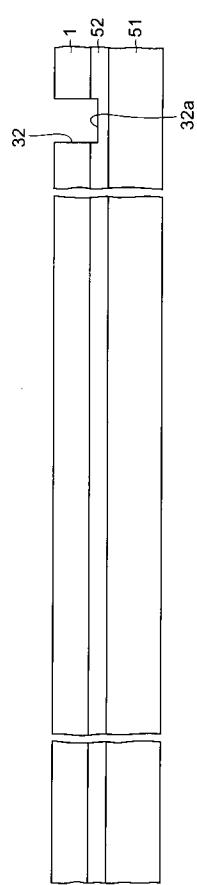

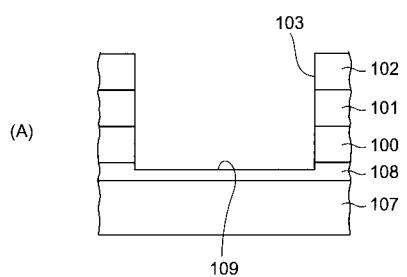

次に、図 3 に示すように、フォトリソグラフィ法により、下地絶縁膜 1 の所定の箇所に第 3 の貫通孔 3 2 を形成する。この場合、下地絶縁膜 1 の材料である例えば窒化シリコンと分離層 5 2 の材料であるアモルファスシリコンとの間にさほどエッチング選択比がとれないため、第 3 の貫通孔 3 2 に対応する部分における分離層 5 2 の上面側にある程度の深さの第 3 の凹部 3 2 a が形成される。

【 0 0 2 4 】

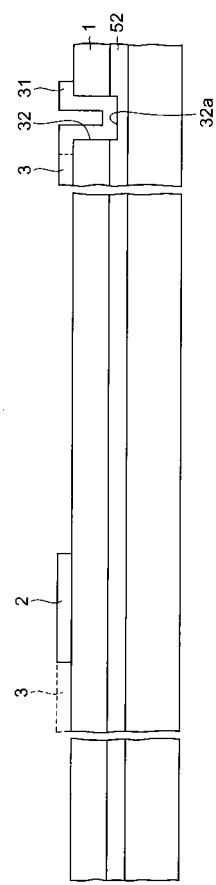

次に、図 4 に示すように、第 3 の貫通孔 3 2 内および第 3 の凹部 3 2 a 内を含む下地絶縁膜 1 の上面の所定の箇所に、スパッタ法により成膜されたクロム等からなる金属膜をフォトリソグラフィ法によりパターニングすることにより、ゲート電極 2 、該ゲート電極 2 に接続されたゲート配線 3 および該ゲート配線 3 の一端部に接続されたゲート配線用外部接続端子 3 1 を形成する。

【 0 0 2 5 】

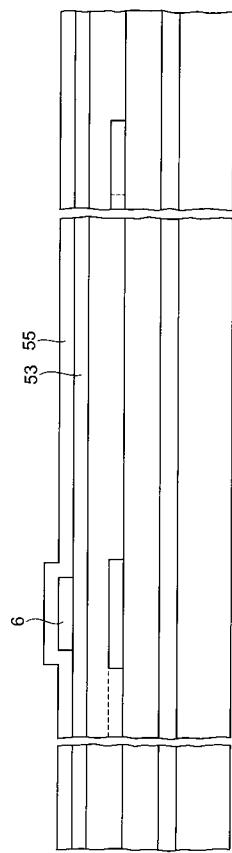

次に、図 5 に示すように、ゲート電極 2 、ゲート配線 3 およびゲート配線用外部接続端子 3 1 を含む下地絶縁膜 1 の上面に、プラズマ CVD 法により、窒化シリコン等の無機材料からなるゲート絶縁膜 4 、真性アモルファスシリコン膜 5 3 および窒化シリコン等の無機材料からなるチャネル保護膜形成用膜 5 4 を連続して成膜する。次に、チャネル保護膜形成用膜 5 4 をフォトリソグラフィ法によりパターニングすることにより、チャネル保護膜 6 を形成する。

【 0 0 2 6 】

次に、図 6 に示すように、チャネル保護膜 6 を含む真性アモルファスシリコン膜 5 3 の上面に、プラズマ CVD 法により、n 型アモルファスシリコン膜 5 5 を成膜する。次に、n 型アモルファスシリコン膜 5 5 および真性アモルファスシリコン膜 5 3 をフォトリソグ

10

20

30

40

50

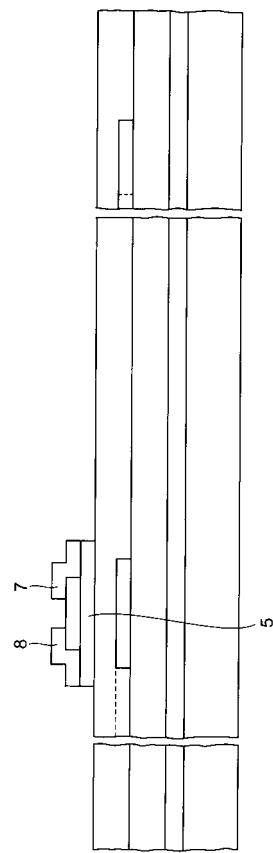

ラフィ法により連続してパターニングすると、図7に示すように、オーミックコンタクト層7、8および半導体薄膜5が形成される。

【0027】

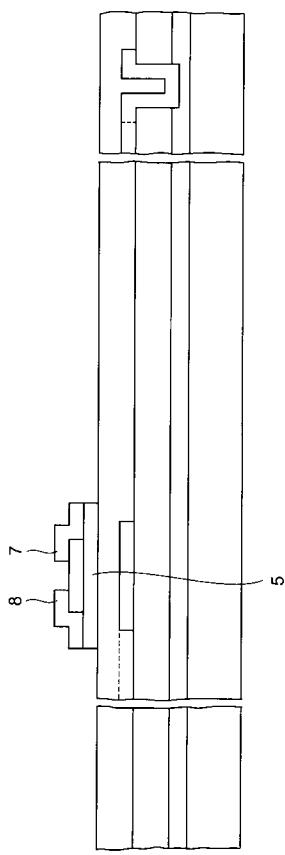

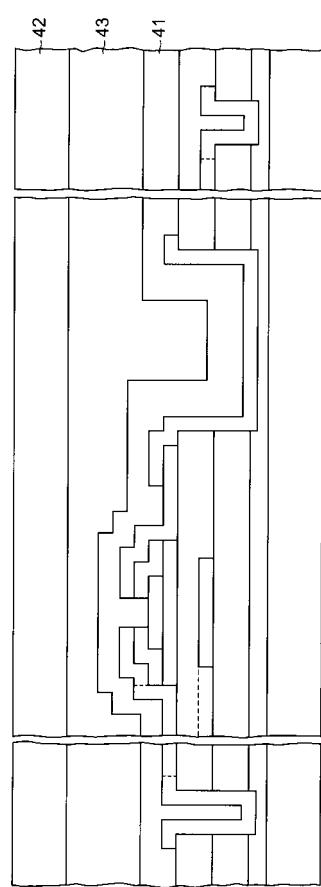

次に、図8に示すように、フォトリソグラフィ法により、ゲート絶縁膜4および下地絶縁膜1の所定の箇所に第1、第2の貫通孔12、22を形成する。この場合も、ゲート絶縁膜4および下地絶縁膜1の材料である例えば窒化シリコンと分離層52の材料であるアモルファスシリコンとの間にさほどエッチング選択比がとれないため、第1、第2の貫通孔12、22に対応する部分における分離層52の上面側にある程度の深さの第1、第2の凹部12a、22aが形成される。

【0028】

次に、図9に示すように、第2の貫通孔22内および第2の凹部22a内を含むオーミックコンタクト層7、8およびゲート絶縁膜4の上面の所定の箇所に、スパッタ法により成膜されたクロム等からなる金属膜をフォトリソグラフィ法によりパターニングすることにより、ソース電極9、ドレイン電極10、該ドレイン電極10に接続されたドレイン配線14および該ドレイン配線14の一端部に接続されたドレイン配線用外部接続端子21が形成される。

10

【0029】

次に、図10に示すように、第2の貫通孔22内および第2の凹部22a内を含むオーミックコンタクト層7、8およびゲート絶縁膜4の上面の所定の箇所に、スパッタ法により成膜されたITO膜をフォトリソグラフィ法によりパターニングすることにより、画素電極13をソース電極9に接続させて形成する。

20

【0030】

次に、図11に示すように、薄膜トランジスタ11、画素電極13、ドレイン配線14、ドレイン配線用外部接続端子21およびゲート絶縁膜4の上面に、プラズマCVD法により、窒化シリコン等の無機材料からなる補強膜41を成膜する。次に、図12に示すように、補強膜41の上面に、透明なエポキシ樹脂をスピンドル法あるいはスクリーン印刷法等を用いて、上面が平坦な接着層43を形成し、該接着層43上に、製造工程時の温度に耐えることができない材料であるポリイミド系樹脂等の有機樹脂からなるフィルム基板42を接着する。この場合、補強膜41上に透明なアクリル系樹脂をスピンドル法あるいはスクリーン印刷法等を用いて上面が平坦な絶縁層を形成し、該絶縁層上に接着層を形成して該接着層上にフィルム基板42を接着するようにしてもよい。

30

【0031】

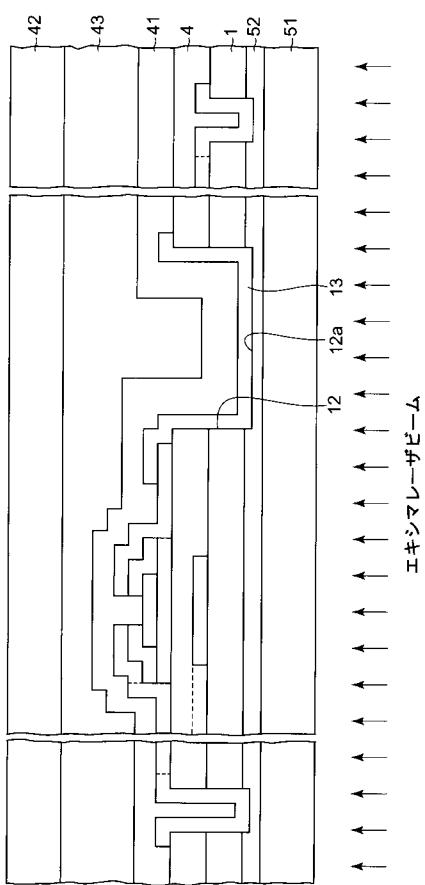

次に、図13に示すように、仮基板51の下側からエキシマレーザビームを照射することにより、分離層52から仮基板51を剥離可能な状態とする。分離層52を水素を含有するアモルファスシリコンによって形成した場合には、エキシマレーザビームの照射により、水素が気体となって放出され、剥離が促進される。次に、分離層52から仮基板51を剥離して除去する。次に、分離層52をエッチングして除去する。かくして、図1に示す薄膜トランジスタパネルが得られる。

【0032】

ところで、図11に示すように、窒化シリコン等の無機材料からなる補強膜41をプラズマCVD法により成膜するため、第1の貫通孔12および第1の凹部12aの内部に形成された有底筒状の画素電極13の内底部周辺部まで補強膜41を確実に成膜することができる。この結果、図1に示す薄膜トランジスタパネルにおいて、画素電極13の厚さが例えば0.05μm程度と極めて薄く、且つ、画素電極13の底部の面積が比較的大きくても、下地絶縁膜1の下側に突出された画素電極13の底部周辺部13aが破損しにくいようにすることができる。

40

【0033】

ところで、上記薄膜トランジスタパネルの製造方法では、図3に示すように、第3の貫通孔32を形成する工程と、図8に示すように、第1、第2の貫通孔12、22を形成する工程とが別々であるので、フォトリソグラフィ法による工程数が多くなってしまう。そ

50

ここで、次に、フォトリソグラフィ法による工程数を少なくすることができる実施形態について説明する。

【0034】

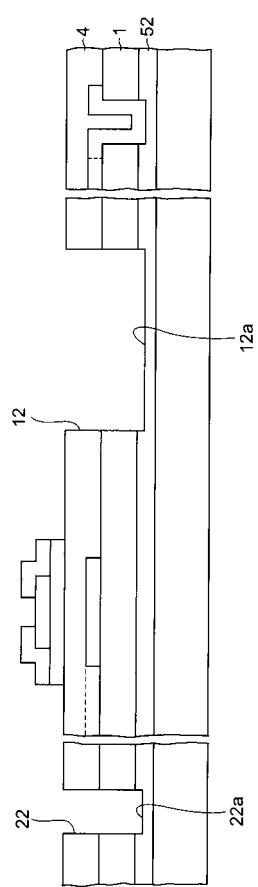

(第2実施形態)

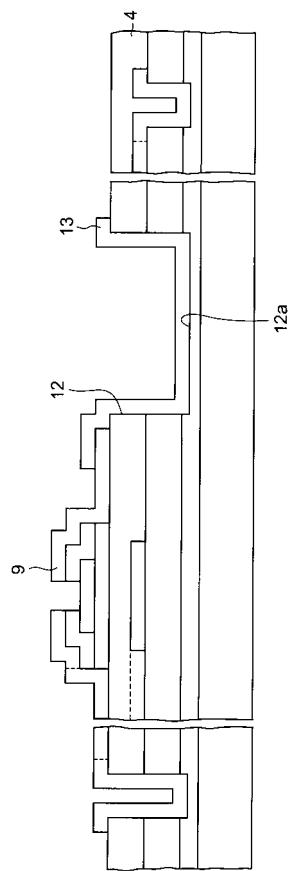

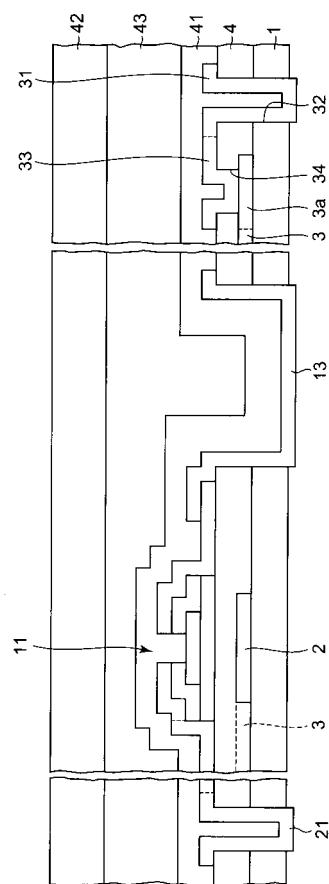

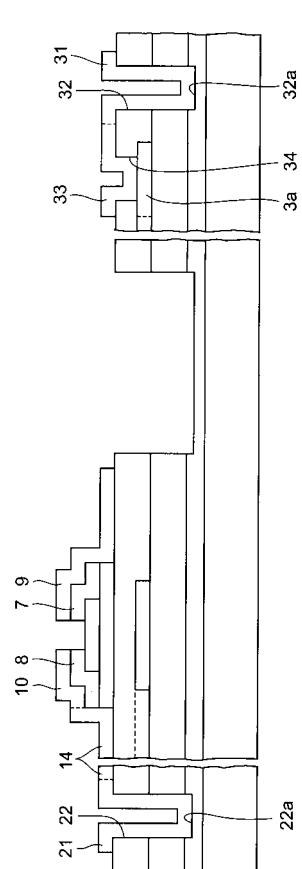

図14はこの発明の第2実施形態としての薄膜トランジスタパネルの要部の断面図を示す。この薄膜トランジスタパネルにおいて、図1に示す薄膜トランジスタパネルと異なる点は、ゲート配線用外部接続端子31の部分を異なる構造とした点である。すなわち、下地絶縁膜1の上面の所定の箇所には、ゲート配線3の一端部からなるゲート配線用接続パッド部3aが設けられている。ゲート絶縁膜4の上面の所定の箇所にはゲート配線用中継配線33がゲート絶縁膜4に設けられたコンタクトホール34を介してゲート配線用接続パッド部3aに接続されて設けられている。

【0035】

ゲート配線用外部接続端子31は、ゲート絶縁膜4および下地絶縁膜1の所定の箇所に設けられた第3の貫通孔32の内壁面、第3の貫通孔32の下部および第3の貫通孔32の周囲におけるゲート絶縁膜4の上面に設けられている。この場合も、第3の貫通孔32の下部に設けられたゲート配線用外部接続端子31は下地絶縁膜1の下側にやや突出され、この突出部分の下面是平坦となっている。ゲート配線用外部接続端子31はゲート配線用中継配線33の一端部に接続されている。

【0036】

次に、この薄膜トランジスタパネルの製造方法の一例について説明する。まず、図15に示すように、製造工程時の温度に耐えることができる材料であるガラス基板等からなる仮基板51の上面に、プラズマCVD法により、アモルファスシリコンからなる分離層52および窒化シリコン等の無機材料からなる下地絶縁膜1を連続して成膜する。

【0037】

次に、下地絶縁膜1の上面の所定の箇所に、スパッタ法により成膜されたクロム等からなる金属膜をフォトリソグラフィ法によりパターニングすることにより、ゲート電極2および該ゲート電極2に接続されたゲート配線3を形成する。この場合、ゲート配線3の一端部はゲート配線用接続パッド部3aとなっている。

【0038】

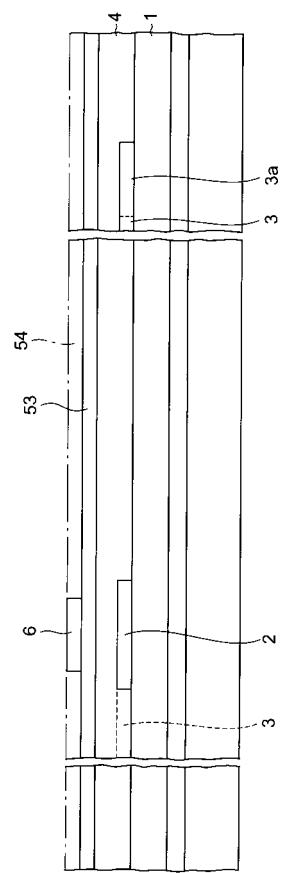

次に、図16に示すように、ゲート電極2およびゲート配線3(ゲート配線用接続パッド部3aを含む)を含む下地絶縁膜1の上面に、プラズマCVD法により、窒化シリコン等の無機材料からなるゲート絶縁膜4、真性アモルファスシリコン膜53および窒化シリコン等の無機材料からなるチャネル保護膜形成用膜54を連続して成膜する。次に、チャネル保護膜形成用膜54をフォトリソグラフィ法によりパターニングすることにより、チャネル保護膜6を形成する。

【0039】

次に、図17に示すように、チャネル保護膜6を含む真性アモルファスシリコン膜53の上面に、プラズマCVD法により、n型アモルファスシリコン膜55を成膜する。次に、n型アモルファスシリコン膜55および真性アモルファスシリコン膜53をフォトリソグラフィ法により連続してパターニングすると、図18に示すように、オーミックコンタクト層7、8および半導体薄膜5が形成される。

【0040】

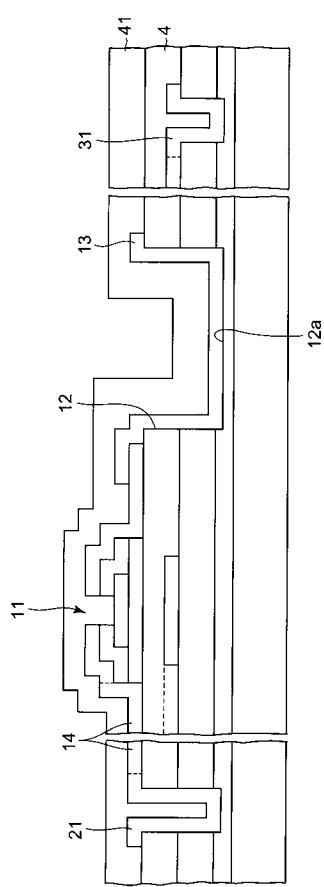

次に、図19に示すように、フォトリソグラフィ法により、ゲート絶縁膜4および下地絶縁膜1の所定の箇所に第1、第2、第3の貫通孔12、22、32を形成し、且つ、ゲート配線用接続パッド部3aに対応する部分におけるゲート絶縁膜4にコンタクトホール34を形成する。この場合も、ゲート絶縁膜4および下地絶縁膜1の材料である例えは窒化シリコンと分離層52の材料であるアモルファスシリコンとの間にさほどエッチング選択比がとれないため、第1、第2、第3の貫通孔12、22、32に対応する部分における分離層52の上面側にある程度の深さの第1、第2、第3の凹部12a、22a、32aが形成される。

## 【0041】

次に、図20に示すように、スパッタ法により成膜されたクロム等からなる金属膜をフォトリソグラフィ法によりパターニングすることにより、第2の貫通孔22内および第2の凹部22a内を含むオーミックコンタクト層7、8およびゲート絶縁膜4の上面の所定の箇所に、ソース電極9、ドレイン電極10、該ドレイン電極10に接続されたドレイン配線14および該ドレイン配線14の一端部に接続されたドレイン配線用外部接続端子21を形成し、且つ、第3の貫通孔32内および第3の凹部322a内を含むゲート絶縁膜4の上面の所定の箇所にゲート配線用外部接続端子31を形成し、さらに、コンタクトホール34を介して露出されたゲート配線用接続パッド部3aを含むゲート絶縁膜4の上面の所定の箇所にゲート配線用中継配線33をゲート配線用外部接続端子31に接続させて形成する。

10

## 【0042】

以下、上記第1実施形態の場合と同様の工程を経ると、図14に示す薄膜トランジスタパネルが得られる。以上のように、この薄膜トランジスタパネルの製造方法では、図19に示すように、第1、第2、第3の貫通孔12、22、32およびコンタクトホール34を同一の工程で形成しているので、上記第1実施形態の場合と比較して、フォトリソグラフィ法による工程を1回だけ少なくすることができる。

## 【0043】

(その他の実施形態)

上記各実施形態では、分離層52をアモルファスシリコンによって形成した場合について説明したが、これに限定されるものではない。例えば、分離層52を酸化亜鉛によって形成するようにしてもよい。この場合、例えば、図12に示す工程後に、エッティング液(例えば、0.5w%酢酸水溶液)に浸すと、酸化亜鉛からなる分離層52が溶解して除去され、仮基板51が自然に剥離して除去される。

20

## 【図面の簡単な説明】

## 【0044】

【図1】この発明の第1実施形態としての薄膜トランジスタパネルの要部の断面図。

【図2】図1に示す薄膜トランジスタパネルの製造に際し、当初の工程の断面図。

【図3】図2に続く工程の断面図。

【図4】図3に続く工程の断面図。

30

【図5】図4に続く工程の断面図。

【図6】図5に続く工程の断面図。

【図7】図6に続く工程の断面図。

【図8】図7に続く工程の断面図。

【図9】図8に続く工程の断面図。

【図10】図9に続く工程の断面図。

【図11】図10に続く工程の断面図。

【図12】図11に続く工程の断面図。

【図13】図12に続く工程の断面図。

【図14】この発明の第2実施形態としての薄膜トランジスタパネルの要部の断面図。

40

【図15】図14に示す薄膜トランジスタパネルの製造に際し、当初の工程の断面図。

【図16】図15に続く工程の断面図。

【図17】図16に続く工程の断面図。

【図18】図17に続く工程の断面図。

【図19】図18に続く工程の断面図。

【図20】図19に続く工程の断面図。

【図21】従来の薄膜トランジスタパネルの画素電極の部分の断面図。

【図22】図21に示す薄膜トランジスタパネルの製造に際し、当初の工程の断面図。

【図23】図22に続く工程の断面図。

【図24】図23に続く工程の断面図。

50

【図25】図24に続く工程の断面図。

【図26】図25に続く工程の断面図。

【図27】(A)、(B)は従来の薄膜トランジスタパネルの画素電極の部分の問題点を説明するために示す断面図。

【符号の説明】

【0045】

- |      |               |    |

|------|---------------|----|

| 1    | 下地絶縁膜         | 10 |

| 2    | ゲート電極         |    |

| 3    | ゲート配線         |    |

| 3 a  | 変色層           |    |

| 4    | ゲート絶縁膜        |    |

| 5    | 半導体薄膜         |    |

| 6    | チャネル保護膜       |    |

| 7、8  | オーミックコンタクト層   |    |

| 9    | ソース電極         |    |

| 10   | ドレイン電極        |    |

| 11   | 薄膜トランジスタ      |    |

| 12   | 第1の貫通孔        |    |

| 12 a | 第1の凹部         |    |

| 13   | 画素電極          | 20 |

| 14   | ドレイン配線        |    |

| 21   | ドレイン配線用外部接続端子 |    |

| 22   | 第2の貫通孔        |    |

| 22 a | 第1の凹部         |    |

| 31   | ゲート配線用外部接続端子  |    |

| 32   | 第3の貫通孔        |    |

| 32 a | 第1の凹部         |    |

| 41   | 補強膜           |    |

| 42   | フィルム基板        |    |

| 43   | 接着層           | 30 |

| 51   | 仮基板           |    |

| 52   | 分離層           |    |

| 53   | 真性アモルファスシリコン膜 |    |

| 54   | チャネル保護膜形成用膜   |    |

| 55   | n型アモルファスシリコン膜 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

---

フロントページの続き

| (51) Int.Cl. |                  | F I                |

|--------------|------------------|--------------------|

| H 0 1 L      | 21/02 (2006.01)  | H 0 1 L 27/12 B    |

| H 0 1 L      | 27/12 (2006.01)  | G 0 9 F 9/30 3 3 8 |

| G 0 9 F      | 9/30 (2006.01)   | G 0 2 F 1/1368     |

| G 0 2 F      | 1/1368 (2006.01) |                    |

(58)調査した分野(Int.Cl. , DB名)

|         |               |

|---------|---------------|

| H 0 1 L | 2 1 / 3 3 6   |

| G 0 2 F | 1 / 1 3 6 8   |

| G 0 9 F | 9 / 3 0       |

| H 0 1 L | 2 1 / 0 2     |

| H 0 1 L | 2 1 / 3 2 0 5 |

| H 0 1 L | 2 1 / 7 6 8   |

| H 0 1 L | 2 3 / 5 2 2   |

| H 0 1 L | 2 7 / 1 2     |

| H 0 1 L | 2 9 / 7 8 6   |