(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5036096号

(P5036096)

(45) 発行日 平成24年9月26日(2012.9.26)

(24) 登録日 平成24年7月13日(2012.7.13)

|               |                     |

|---------------|---------------------|

| (51) Int.Cl.  | F 1                 |

| HO 1 L 23/522 | (2006.01)           |

| HO 1 L 21/768 | (2006.01)           |

| HO 1 L 21/304 | (2006.01)           |

| HO 1 L 21/306 | (2006.01)           |

| HO 1 L 21/321 | (2006.01)           |

|               | HO 1 L 21/90 D      |

|               | HO 1 L 21/304 622 X |

|               | HO 1 L 21/304 622 R |

|               | HO 1 L 21/306 M     |

|               | HO 1 L 21/88 K      |

請求項の数 2 (全 10 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2000-238080 (P2000-238080) |

| (22) 出願日  | 平成12年8月7日(2000.8.7)          |

| (65) 公開番号 | 特開2002-50689 (P2002-50689A)  |

| (43) 公開日  | 平成14年2月15日(2002.2.15)        |

| 審査請求日     | 平成19年8月6日(2007.8.6)          |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100064746<br>弁理士 深見 久郎                               |

| (74) 代理人  | 100085132<br>弁理士 森田 俊雄                               |

| (74) 代理人  | 100083703<br>弁理士 仲村 義平                               |

| (74) 代理人  | 100096781<br>弁理士 堀井 豊                                |

| (74) 代理人  | 100109162<br>弁理士 酒井 将行                               |

| (74) 代理人  | 100111246<br>弁理士 荒川 伸夫                               |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜中に単位面積当たりの数が異なる複数のコンタクトホールを形成する工程と、前記コンタクトホールの上部に面取り部を形成する工程と、前記コンタクトホール内及び前記絶縁膜上に導電膜を形成する工程と、C M P を施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程とを備えた半導体装置の製造方法において、

前記 C M P を施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程が、前記単位面積当たりの前記コンタクトホール数の多い領域の前記コンタクトホール上部の前記面取り部を除去するようにしたことを特徴とし、

前記面取り部を除去した後に、前記単位面積当たりの前記コンタクトホール数の多い領域の前記導電膜を埋込んだ前記コンタクトホール内及び前記絶縁膜上に、上部導電膜を堆積する工程と、前記絶縁膜上の前記上部導電膜を除去して、前記単位面積当たりの前記コンタクトホール数の多い領域の前記導電膜を埋込んだ前記コンタクトホール内に、前記上部導電膜を埋込む工程とを備えた事を特徴とする半導体装置の製造方法。

## 【請求項 2】

シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜中に単位面積当たりの数が異なる複数のコンタクトホールを形成する工程と、前記コンタクトホールの上部に面取り部を形成する工程と、前記コンタクトホール内及び前記絶縁膜上に導電膜を形成する工程と、C M P を施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導

10

20

電膜を残す工程とを備えた半導体装置の製造方法において、

前記 C M P を施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程が、前記単位面積当たりの前記コンタクトホール数の多い領域の前記コンタクトホール上部の前記面取り部を除去するようにしたことを特徴とし、

前記面取り部を除去した後に、前記単位面積当たりの前記コンタクトホール数の多い領域の前記導電膜を埋込んだ前記コンタクトホール内及び前記絶縁膜上に、上部導電膜を堆積する工程と、前記上部導電膜をパターニングして、前記導電膜上に上部配線を形成する工程とを備えたことを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

10

##### 【発明の属する技術分野】

この発明は半導体装置およびその製造方法に関し、特にコンタクトホール部の構造およびその製造方法に関するものである。

##### 【0002】

##### 【従来の技術】

近年、半導体装置の高集積化には目覚ましいものがある。それに伴い、微細加工技術の研究開発はとどまる所を知らず、コンタクトホール部の微細化も例外ではない。

##### 【0003】

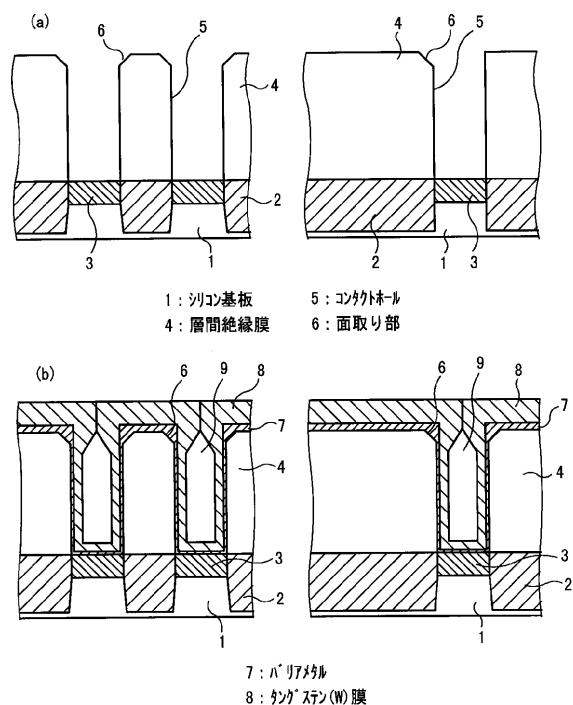

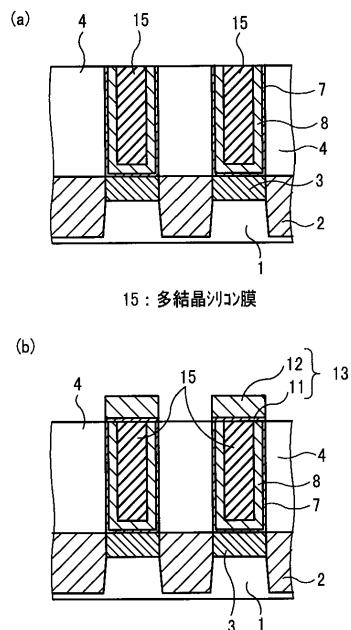

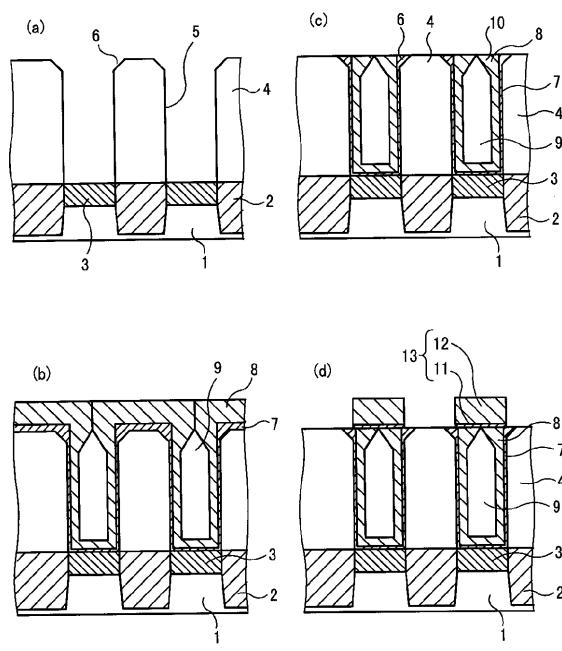

図 7 ( a ) ~ ( d ) は従来のコンタクトホール部の製造方法を示す工程断面図である。図に従って順次説明を行なう。

20

まず、図 7 ( a ) に示すように、シリコン基板 1 上に素子分離領域 2 を形成する。その後、シリコン基板 1 にシリコン基板 1 と逆導電型のイオン注入を行ない、シリコン基板 1 と逆導電型の導電層 3 を形成する。更に全面に層間絶縁膜 4 を形成して、導電層 3 上の層間絶縁膜 4 をエッティングして導電層 3 上に至るコンタクトホール 5 を形成する。アルゴンなどのスパッタエッティングを施すことにより、コンタクトホール 5 上部に面取り部 6 を形成する。この面取り部 6 はアスペクト比の高いコンタクトホール 5 内への埋込み特性を向上させるために設けている。

##### 【0004】

次に、図 7 ( b ) に示すように、全面にスパッタまたは C V D 法により T i N 等のバリアメタル 7 を形成する。続いて、全面に W F 6 、 H 2 ガス等を用いて、 W - C V D 法によりタンゲステン ( W ) 膜 8 を形成する。この時、コンタクトホール 5 の上部には面取り部 6 を設け、コンタクトホール 5 内への埋込み特性を向上させてはいるが、コンタクトホール 5 内のバリアメタル 7 および W 膜 8 のカバレッジは 100 % とはならず、コンタクトホール 5 内にボイド 9 が形成されてしまう。

30

##### 【0005】

次に、図 7 ( c ) に示すように、全面に C M P ( C hemical M echanical P o l i s h ) を施し、層間絶縁膜 4 上のバリアメタル 7 および W 膜 8 を除去してコンタクトホール 5 内にのみ W 膜 8 を埋込んで W プラグ 10 を形成する。

##### 【0006】

次に、図 7 ( d ) に示すように、全面に T i N などのバリアメタル 11 、 W などの導電膜 12 をスパッタまたは C V D 法で堆積する。その後、バリアメタル 11 および導電膜 12 に所望のパターニングを施して上部配線 13 を形成する。

40

##### 【0007】

##### 【発明が解決しようとする課題】

従来のコンタクトホール部の製造方法は以上のようにあったので、図 7 に示すように、コンタクトホール 5 上部に面取り部 6 を設けている。この面取り部 6 はアスペクト比の高いコンタクトホール 5 内への埋込み特性を向上させることができるとともに、面取り部 6 の形成と同時に導電層 3 上の自然酸化膜等の絶縁膜を除去できるという効果がある。

##### 【0008】

ところが、コンタクトホール 5 間の距離が小さい場合、面取り部 6 によってコンタクトホ

50

ール 5 上部のコンタクトホール 5 径が大きくなってしまい、上部配線 1 3 間の分離、コンタクトホール 5 間の分離が難しくなり、微細化の妨げとなるという問題点があった。

#### 【 0 0 0 9 】

また、コンタクトホール 5 内に発生しているボイド 9 によりコンタクトホール 5 内側壁の W 膜 8 の膜厚が薄くなってしまい、W プラグ 10 の垂直方向の抵抗が上昇するという問題点があった。

更に、後工程において、エッティング等に使用される薬液がボイド 9 内に浸入して W 膜 8 を腐食させるという問題点があった。

#### 【 0 0 1 0 】

この発明は上記のような問題点を解消するためになされたもので、コンタクトホール間の距離が縮小しても良好な上部配線およびコンタクトホールの分離ができるとともに、アスペクト比の高いコンタクトホール内への良好な埋込みのできる半導体装置およびその製造方法を提供することを目的としている。 10

#### 【 0 0 1 6 】

##### 【課題を解決するための手段】

この発明の請求項 1 に係る半導体装置の製造方法は、全面に C M P を施して、絶縁膜上の導電膜を除去してコンタクトホール内に上記導電膜を残す工程が、上記 C M P を行なう時間を制御することによって、単位面積当たりのコンタクトホール数の多い領域の上記コンタクトホール上部の上記面取り部を除去するようにしたものである。単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した後に、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内及び絶縁膜上に、上部導電膜を堆積する工程と、絶縁膜上の上記上部導電膜を除去して、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内に、上記上部導電膜を埋込む工程とを備えるようにしたものである。 20

#### 【 0 0 1 7 】

この発明の請求項 2 に係る半導体装置の製造方法は、全面に C M P を施して、絶縁膜上の導電膜を除去してコンタクトホール内に上記導電膜を残す工程が、上記 C M P を行なう時間を制御することによって、単位面積当たりのコンタクトホール数の多い領域の上記コンタクトホール上部の上記面取り部を除去するようにしたものである。単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した後に、単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内及び絶縁膜上に、上部導電膜を堆積する工程と、上記上部導電膜をパターニングして、単位面積当たりのコンタクトホール数の多少にかかわらず、上記導電膜上に上部配線を形成する工程とを備えるようにしたものである。 30

#### 【 0 0 1 9 】

##### 【発明の実施の形態】

###### 実施の形態 1 .

図 1 および 2 はこの発明のコンタクトホール部の製造方法を示す工程断面図であり、各図において、左側の図は単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域を示し、右側の図は左側の図と同一ウエハ内で単位面積当たりのコンタクトホール数が比較的少ない領域を示している。図に従って順次説明を行なう。 40

#### 【 0 0 2 0 】

まず図 1 ( a ) に示すように、シリコン基板 1 上に素子分離領域 2 を形成する。その後、シリコン基板 1 にシリコン基板 1 と逆導電型のイオン注入を行ない、シリコン基板 1 と逆導電型の導電層 3 を形成する。更に全面に層間絶縁膜 4 を形成して、導電層 3 上の層間絶縁膜 4 をエッティングして導電層 3 上に至るコンタクトホール 5 を形成する。アルゴンなどのスパッタエッティングを施すことにより、コンタクトホール 5 上部に面取り部 6 を形成する。この面取り部 6 はアスペクト比の高いコンタクトホール 5 内への埋込み特性を向上させるために設けている。 50

**【 0 0 2 1 】**

次に、図1（b）に示すように、全面にスパッタまたはCVD法により導電膜であるTiN等のバリアメタル7を形成する。続いて、全面にWF6、H2ガス等を用いて、W-CVD法により導電膜であるW膜8を形成する。この時、コンタクトホール5の上部には面取り部6を設け、コンタクトホール5内への埋込み特性を向上させてはいるが、コンタクトホール5内のバリアメタル7およびW膜8のカバレッジは100%とはならず、コンタクトホール5内にボイド9が形成されてしまう。ここまで工程では、左側の図と右側の図とのコンタクトホール部の構造は同じである。

**【 0 0 2 2 】**

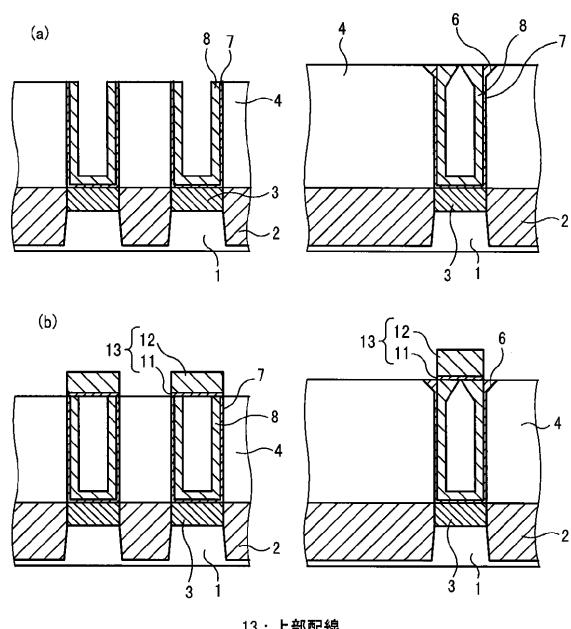

次に、図2（a）に示すように、全面にCMPを施し、層間絶縁膜4上のバリアメタル7およびW膜8を除去してコンタクトホール5内にのみバリアメタル7およびW膜8を埋込んでWプラグ10を形成するのであるが、この時、CMPを行なう時間を長くして、左側の図においてのみコンタクトホール5上部に面取り部6がなくなるまでCMPを行なう。

10

**【 0 0 2 3 】**

一般に、CMPはコンタクトホールの占有面積が多い部分ではコンタクトホールの占有面積が少ない部分に比べて研磨される速度が早いので、同じ時間でCMPを行なうと、コンタクトホールの占有面積が多い部分が沢山削られることになる。

**【 0 0 2 4 】**

従って、全面にCMPを行なう時間を延長すれば、単位面積当たりのコンタクトホール5数が多く、コンタクトホール5の占有面積が多い左側の図では、単位面積当たりのコンタクトホール5数が比較的少ない右側の図よりも削れる量が多くなる。

20

つまり、左側の図で、面取り部6がなくなるように時間を制御して全面にCMPを行なうと、右側の図では面取り部6は消失せずに残存する。

**【 0 0 2 5 】**

次に、図2（b）に示すように、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。この時、左側の図にはコンタクトホール5上部の面取り部6は存在せず、コンタクトホール5間の距離を確保することができ上部配線13間の分離を確実に行える。右側の図にはコンタクトホール5上部の面取り部6が残存しているが、コンタクトホール5間の距離は最初から充分にあるので問題はない。

30

**【 0 0 2 6 】**

以上のように、コンタクトホール5内へW膜8を埋込んでWプラグ10を形成する際に、CMPを通常よりも長く行なうことによって、単位面積当たりのコンタクトホール5が多い領域の面取り部6をなくすことができ、上部配線13間の分離、コンタクトホール5間の分離を確実に行なうことができる。したがって、更にコンタクトホール5間の距離を縮小することができ、半導体装置の高集積化を図ることができる。

**【 0 0 2 7 】**

また、バリアメタル7、11はWN、TaN等でも良い。更に、導電膜12はアルミ合金、高融点金属、高融点金属のシリサイドでも良く、導電層3とバリアメタル7との界面にTiSi、CoSi等の高融点金属シリサイドを形成しても良い。上記いずれの場合も同様の効果が得られる。

40

**【 0 0 2 8 】**

実施の形態2.

上記実施の形態1では単位面積当たりのコンタクトホールの多い領域において、コンタクトホール上部の面取り部を完全に除去する場合について説明をしたが、ここでは、単位面積当たりのコンタクトホールの多い領域においても面取り部を一部残す場合について説明する。

**【 0 0 2 9 】**

図3（a）（b）はこの発明の実施の形態2のコンタクトホール部の製造方法を示す断面

50

図であり、左側の図は単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域を示し、右側の図は左側の図と同一ウエハ内で単位面積当たりのコンタクトホール数が比較的少ない領域を示している。14は層間絶縁膜4中に形成された下層配線である。

図3に至るまでは上記実施の形態1の図1(a)(b)と同様に行なう。

#### 【0030】

図3(a)に示すように、右側の図は実施の形態1の図2(a)の右側の図と同様である。左側の図は実施の形態1の図2(a)の左側の図とは異なり、コンタクトホール5上部の面取り部6を完全に除去するのではなく、後に形成される上部配線13間およびコンタクトホール5間が分離できる程度にCMPの時間を制御して行ない、コンタクトホール5上部の面取り部6の一部を残存させている。10

#### 【0031】

次に、図3(b)に示すように、図2(b)と同様にして、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。この時、左側の図ではコンタクトホール5上部の面取り部6はコンタクトホール5間の距離を確保することができる程度に存在し、上部配線13間の分離を確実に行える。

#### 【0032】

従って、上記実施の形態1と同様の効果を有するとともに、CMPを行なう時間を上記実施の形態1の場合よりも短く設定でき、単位面積当たりのコンタクトホール5が多い領域においてCMPによって削れる量を少なくすることができる。これにより、CMP工程後の平坦度は上記実施の形態1よりも高くすることができる。また、層間絶縁膜4中に下層配線14等が存在していても、CMPによって削られる可能性を低くおさえられる。20

#### 【0033】

実施の形態3.

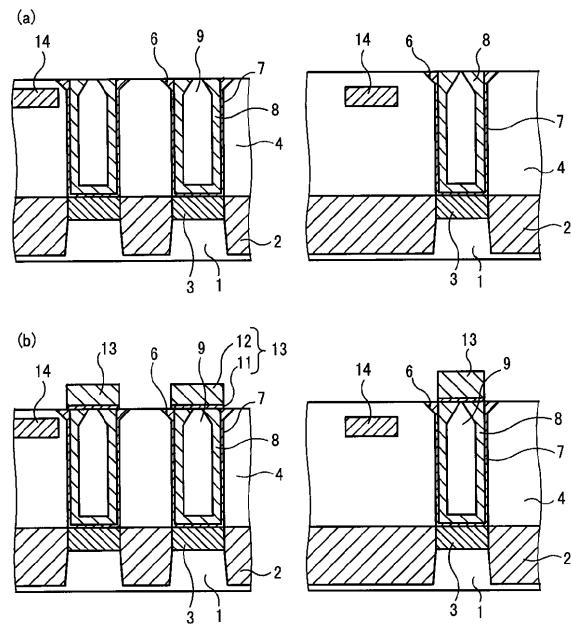

上記実施の形態1ではCMP後ボイドを塞ぐことなく、上部配線を形成していたが、ここではCMP後コンタクトホール内にさらに導電膜を埋込む場合について説明する。

#### 【0034】

図4(a)(b)はこの発明の実施の形態3のコンタクトホール部の製造方法を示す断面図であり、単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域の断面図である。30

図4に至るまでは上記実施の形態1の図1(a)(b)図2(a)と同様に行なう。

#### 【0035】

図4(a)に示すように、CMPを行なう時間を長くすることによって、単位面積当たりのコンタクトホール数の多い領域ではコンタクトホール5上部の面取り部6を除去すると同時にコンタクトホール5上部に埋込まれていたW膜8が除去され、コンタクトホール5内のボイド9が開口する。

#### 【0036】

この開口を含む全面に上部導電膜である不純物をドープした多結晶シリコン膜15をCVD法で堆積した後、CMPを施すことにより層間絶縁膜4上の多結晶シリコン膜15を除去してボイド9内にのみ多結晶シリコン膜15を埋込む。40

#### 【0037】

次に、図4(b)に示すように、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。

#### 【0038】

この様にすれば、ボイド9を塞ぐことができるので、後処理によるボイド9への薬液の染み込みを防止することができる。また、ボイド9を多結晶シリコン膜15で埋込んだので、コンタクトホール5の垂直方向の抵抗を下げることができる。

#### 【0039】

10

20

30

40

50

#### 実施の形態 4 .

上記実施の形態 3 ではボイド 9 内に多結晶シリコン膜 1 5 を埋込む場合について説明を行なったが、ここでは更に低抵抗な導電膜を埋込む場合について説明する。

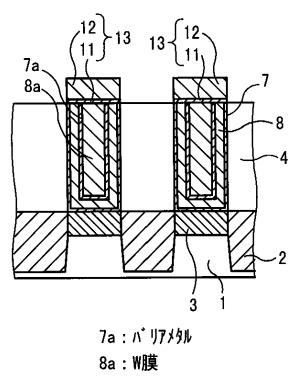

##### 【 0 0 4 0 】

図 5 はこの発明の実施の形態 4 のコンタクトホール部を示す断面図であり、単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域の断面図である。

図 5 に至るまでは上記実施の形態 1 の図 1 ( a ) ( b ) 図 2 ( a ) と同様に行なう。

##### 【 0 0 4 1 】

図 5 に示すように、C M P によって開口したボイド 9 内を含む全面にスパッタまたは C V D 法により上部導電膜である T i N 等のバリアメタル 7 a を形成する。続いて、全面に W F 6 、 H 2 ガス等を用いて、W - C V D 法により上部導電膜である W 膜 8 a を形成する。その後全面に C M P を施し、層間絶縁膜 4 上のバリアメタル 7 a および W 膜 8 a を除去してボイド 9 内にのみバリアメタル 7 a および W 膜 8 a を埋込む。

10

##### 【 0 0 4 2 】

その後、全面に T i N などのバリアメタル 1 1 、 W などの導電膜 1 2 をスパッタまたは C V D 法で堆積する。その後、バリアメタル 1 1 および導電膜 1 2 に所望のパターニングを施して上部配線 1 3 を形成する。

##### 【 0 0 4 3 】

この様にすれば、より低抵抗なバリアメタル 7 a および W 膜 8 a でコンタクトホール 5 内のボイド 9 を塞ぐことができ、コンタクトホール 5 の垂直方向の抵抗をさらに下げる

20 ことができる。

##### 【 0 0 4 4 】

#### 実施の形態 5 .

上記実施の形態 4 では上部配線 1 3 の形成とコンタクトホール 5 内の埋込みとを別々に行なっていたがここでは一度に形成する方法について説明する。

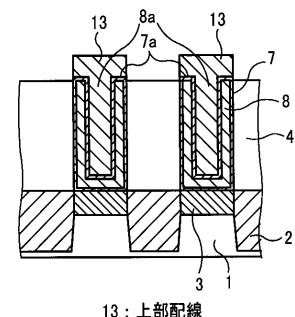

##### 【 0 0 4 5 】

図 6 はこの発明の実施の形態 4 のコンタクトホール部を示す断面図であり、単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域の断面図である。

図 6 に至るまでは上記実施の形態 1 の図 1 ( a ) ( b ) 図 2 ( a ) と同様に行なう。

##### 【 0 0 4 6 】

図 6 に示すように、C M P によって開口したボイド 9 内を含む全面にスパッタまたは C V D 法により T i N 等のバリアメタル 7 a を形成する。続いて、全面に W F 6 、 H 2 ガス等を用いて、W - C V D 法により W 膜 8 a を形成する。その後、上部配線 1 3 用のパターニングを行ない W 膜 8 a からなる上部配線 1 3 を形成する。

30

##### 【 0 0 4 7 】

この様にすれば、上記実施の形態 4 に比べて、C M P 、バリアメタル 1 1 の形成、導電膜 1 2 の形成工程を省略することができ、製造工程数を減らすことができる。又、上部配線 1 3 とコンタクトホール 5 内との界面などの導電膜間の界面を減少させることができるのでより低抵抗なコンタクトホールを形成することができる。

##### 【 0 0 4 8 】

#### 【 発明の効果 】

以上のようにこの発明によれば、各コンタクトホールのうち、単位面積当たりの上記コンタクトホール数の少ない領域に形成されたコンタクトホールは、その上部に面取り部を備え、単位面積当たりの上記コンタクトホール数の多い領域に形成されたコンタクトホールは、その上部に上記面取り部を備えないようにしたので、単位面積当たりのコンタクトホール数の多い領域において、コンタクトホール間の分離が良好に行え、コンタクトホール間の距離をさらに縮小することができる。

##### 【 0 0 4 9 】

また、各コンタクトホールのうち、単位面積当たりの上記コンタクトホール数の多い領域に形成されたコンタクトホールは、単位面積当たりの上記コンタクトホール数の少ない領

50

域に形成されたコンタクトホールよりも小さな面取り部を備えるようにしたので、コンタクトホール間の分離が良好に行えるとともに、ウエハの平坦度が向上し、層間絶縁膜中の下部配線を損なうこともない。

#### 【0050】

また、単位面積当たりのコンタクトホール数の多い領域に形成された導電膜を有するコンタクトホールにおいて、上記導電膜上に上部導電膜を設け、上記導電膜がバリアメタルとタンゲステン膜とから成り、上記上部導電膜が多結晶シリコン膜から成り、上記コンタクトホール内に、上記バリアメタルと上記タンゲステン膜と上記多結晶シリコン膜との三層を備えるようにしたので、コンタクトホール内のボイドを塞ぐことができ、コンタクトホール内の垂直方向の抵抗を低くできる。

10

#### 【0051】

単位面積当たりのコンタクトホール数の多い領域に形成された導電膜を有するコンタクトホールにおいて、上記導電膜上に上部導電膜を設け、上記導電膜および上記上部導電膜がともにバリアメタルとタンゲステン膜とから成り、上記コンタクトホール内に、上記バリアメタルと上記タンゲステン膜と上記バリアメタルと上記タンゲステン膜との四層を備えるようにしたので、コンタクトホール内の抵抗をより低くすることができる。

#### 【0052】

コンタクトホールの導電膜上に上部配線を備えるようにしたので、上部配線の分離を良好に行える。

#### 【0053】

全面にCMPを施して、絶縁膜上の導電膜を除去してコンタクトホール内にのみ上記導電膜を埋込む工程が、上記CMPを行なう時間を制御することによって、単位面積当たりのコンタクトホール数の少ない領域の上記コンタクトホール上部の上記面取り部の大きさより、単位面積当たりのコンタクトホール数の多い領域の上記コンタクトホール上部の上記面取り部の大きさを小さくまたは除去するようにしたので、コンタクトホール間の距離に応じて面取り部の大きさを選択することができ、素子に応じて面取り部の大きさを選択する自由度が広がる。

20

#### 【0054】

単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した場合、この除去を行なった後に、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内を含む全面に、上部導電膜を堆積する工程と、絶縁膜上の上記上部導電膜を除去して、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内に、上記上部導電膜を埋込む工程とを備えるようにしたもので、コンタクトホール内のボイドを塞ぐことができ、コンタクトホール内の垂直方向の抵抗を低くできる。

30

#### 【0055】

単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した場合、この除去を行なった後に、単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内を含む全面に、上部導電膜を堆積する工程と、上記上部導電膜をパターニングして、単位面積当たりのコンタクトホール数の多少にかかわらず、上記導電膜上に上部配線を形成する工程とを備えるようにしたので、上部配線の形成とコンタクトホール内の埋込みを一度で行なうことができ、製造工程数を減少させることができる。

40

#### 【図面の簡単な説明】

【図1】 この発明のコンタクトホール部の製造方法を示す工程断面図である。

【図2】 この発明のコンタクトホール部の製造方法を示す工程断面図である。

【図3】 この発明の実施の形態2のコンタクトホール部の製造方法を示す工程断面図である。

【図4】 この発明の実施の形態3のコンタクトホール部の製造方法を示す工程断面図である。

50

【図5】 この発明の実施の形態4のコンタクトホール部を示す断面図である。

【図6】 この発明の実施の形態5のコンタクトホール部を示す断面図である。

【図7】 従来のコンタクトホール部の製造方法示す工程断面図である。

【符号の説明】

1 シリコン基板、4 層間絶縁膜、5 コンタクトホール、6 面取り部、7, 7a バリアメタル、8, 8a W膜、13 上部配線、15 多結晶シリコン膜。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(74)代理人 100098316

弁理士 野田 久登

(72)発明者 塚本 和宏

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 仲間 晃

(56)参考文献 特開平10-163207(JP,A)

特開2000-003912(JP,A)

特開2000-164595(JP,A)

特開平10-284492(JP,A)

特開平09-148431(JP,A)

特表平11-500272(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/768

H01L 21/304

H01L 21/306

H01L 21/321

H01L 23/522