(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5501583号

(P5501583)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月20日(2014.3.20)

(51) Int.Cl.

H01L 31/10 (2006.01)

F 1

H01L 31/10

G

請求項の数 14 (全 27 頁)

(21) 出願番号 特願2008-205425 (P2008-205425)

(22) 出願日 平成20年8月8日 (2008.8.8)

(65) 公開番号 特開2010-40981 (P2010-40981A)

(43) 公開日 平成22年2月18日 (2010.2.18)

審査請求日 平成23年8月3日 (2011.8.3)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 山本 元彦

最終頁に続く

(54) 【発明の名称】光電変換装置、及び当該光電変換装置を具備する電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の光電変換素子と、

前記第1の光電変換素子の出力電流を増幅した第1の電流を出力する第1の増幅回路と、

前記第1の光電変換素子とは異なる分光感度特性を有する第2の光電変換素子と、

前記第2の光電変換素子の出力電流を増幅した第2の電流を出力する第2の増幅回路と、

オンである第1のスイッチを介して一方の電極に供給される第1の電位に応じて第1の電荷を蓄積し、オンである第2のスイッチを介して一方の電極に供給される前記第1の電流に応じて前記第1の電荷を放電する第1の容量素子と、

前記第1の容量素子の一方の電極の電位と第2の電位とを比較する第1のコンパレータと、

第1のクロック信号を生成する第1のクロック生成回路と、

前記第1のクロック信号をカウントアップして得られる第1のカウント値を出力する第1のカウンター回路と、

前記第1のコンパレータより出力される信号に応じて前記第1のカウント値をラッチし、前記ラッチした前記第1のカウント値を第1のデジタル信号として出力する第1のラッチ回路と、

オンである第3のスイッチを介して一方の電極に供給される前記第1の電位に応じて第

10

20

2の電荷を蓄積し、オンである第4のスイッチを介して一方の電極に供給される前記第2の電流に応じて前記第2の電荷を放電する第2の容量素子と、

前記第2の容量素子の一方の電極の電位と前記第2の電位とを比較する第2のコンパレータと、

第2のクロック信号を生成する第2のクロック生成回路と、

前記第2のクロック信号をカウントアップして得られる第2のカウント値を出力する第2のカウンター回路と、

前記第2のコンパレータより出力される信号に応じて前記第2のカウント値をラッチし、前記ラッチした前記第2のカウント値を第2のデジタル信号として出力する第2のラッチ回路と、

前記第1のデジタル信号と前記第2のデジタル信号との差分を出力するための減算回路と、を有し、

前記第1のラッチ回路は、前記第1のカウント値が最大値に達した場合に、前記第1のカウント値をラッチし、

前記第2のラッチ回路は、前記第2のカウント値が最大値に達した場合に、前記第2のカウント値をラッチすることを特徴とする光電変換装置。

#### 【請求項2】

請求項1において、

前記第1の電流は、前記第1の容量素子から前記第1の増幅回路への方向であり、

前記第2の電流は、前記第2の容量素子から前記第2の増幅回路への方向であることを特徴とする光電変換装置。

#### 【請求項3】

第1の光電変換素子と、

前記第1の光電変換素子の出力電流を増幅した第1の電流を出力する第1の増幅回路と、

前記第1の光電変換素子とは異なる分光感度特性を有する第2の光電変換素子と、

前記第2の光電変換素子の出力電流を増幅した第2の電流を出力する第2の増幅回路と、

前記第1の電流と前記第2の電流との差分を電圧値として出力する減算回路と、

前記電圧値に応じた第3の電流を出力する電圧電流変換回路と、

オンである第1のスイッチを介して一方の電極に供給される第1の電位に応じて電荷を蓄積し、オンである第2のスイッチを介して一方の電極に供給される前記第3の電流に応じて前記電荷を放電する容量素子と、

前記容量素子の一方の電極の電位と第2の電位とを比較するコンパレータと、クロック信号を生成するクロック生成回路と、

前記クロック信号をカウントアップして得られるカウント値を出力するカウンター回路と、

前記コンパレータより出力される信号に応じて、前記カウント値をラッチして出力するラッチ回路と、を有し、

前記ラッチ回路は、前記カウント値が最大値に達した場合に、前記カウント値をラッチすることを特徴とする光電変換装置。

#### 【請求項4】

第1の光電変換素子と、

前記第1の光電変換素子の出力電流を増幅した第1の電流を出力する第1の増幅回路と、

前記第1の光電変換素子とは異なる分光感度特性を有する第2の光電変換素子と、

前記第2の光電変換素子の出力電流を増幅した第2の電流を出力する第2の増幅回路と、

前記第2の電流を、前記第1の増幅回路に向けて流れるように変換するカレントミラーレンジ回路と、

10

20

30

40

50

オンである第1のスイッチを介して一方の電極に供給される第1の電位に応じて電荷を蓄積し、オンである第2のスイッチを介して一方の電極に供給される第3の電流に応じて前記電荷を放電する容量素子と、

前記容量素子の一方の電極の電位と第2の電位とを比較するコンパレータと、

クロック信号を生成するクロック生成回路と、

前記クロック信号をカウントアップして得られるカウント値を出力するカウンター回路と、

前記コンパレータより出力される信号に応じて、前記カウント値をラッチして出力するラッチ回路と、を有し、

前記第3の電流は、前記第1の電流と前記カレントミラー回路により変換された前記第2の電流との差分であり、10

前記ラッチ回路は、前記カウント値が最大値に達した場合に、前記カウント値をラッチすることを特徴とする光電変換装置。

#### 【請求項5】

請求項3又は4において、

前記第3の電流の向きは、前記容量素子から前記第1のスイッチの方向に流れることを特徴とする光電変換装置。

#### 【請求項6】

請求項1乃至請求項5のいずれか一において、

前記第1の增幅回路は、nチャネル型トランジスタを有し、20

前記nチャネル型トランジスタは、酸化物半導体を有し、

前記酸化物半導体は、前記第1の光電変換素子と重なる領域を有することを特徴とする光電変換装置。

#### 【請求項7】

請求項1乃至請求項6のいずれか一において、

前記第1の增幅回路は、第1のカレントミラー回路を有し、

前記第2の増幅回路は、第2のカレントミラー回路を有し、

前記第1の光電変換素子は、前記第1のカレントミラー回路とトランジスタを介さずに電気的に接続されており、

前記第2の光電変換素子は、前記第2のカレントミラー回路とトランジスタを介さずに電気的に接続されていることを特徴とする光電変換装置。30

#### 【請求項8】

請求項1乃至請求項7のいずれか一において、

前記第1の光電変換素子及び前記第2の光電変換素子は単結晶シリコン基板に形成されたものであることを特徴とする光電変換装置。

#### 【請求項9】

請求項1乃至請求項8のいずれか一において、

前記第1の増幅回路および前記第2の増幅回路は、照度に応じて増幅率を切り替える機能を有することを特徴とする光電変換装置。

#### 【請求項10】

請求項1乃至請求項9のいずれか一において、

前記第1の増幅回路および前記第2の増幅回路のそれぞれは、複数の増幅回路を有し、前記第1の増幅回路および前記第2の増幅回路のそれぞれにおいて、

前記複数の増幅回路の増幅率は、それぞれ異なっており、

前記複数の増幅回路は、照度に応じて切り替えられることを特徴とする光電変換装置。40

#### 【請求項11】

請求項1乃至請求項10のいずれか一において、

前記第1の光電変換素子及び前記第2の光電変換素子は、同じ大きさの開口部を有することを特徴とする光電変換装置。

#### 【請求項12】

50

請求項 1 乃至請求項 1 1 のいずれか一において、

前記第 2 の光電変換素子の光が入射される側には、赤外光透過フィルタが設けられていることを特徴とする光電変換装置。

【請求項 1 3】

請求項 1 乃至請求項 1 2 のいずれか一において、

前記第 2 の電位は、前記第 1 の電位よりも低いことを特徴とする光電変換装置。

【請求項 1 4】

請求項 1 乃至請求項 1 3 のいずれか一に記載の光電変換装置を具備することを特徴とする電子機器。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、光電変換装置に関する。また、当該光電変換装置を具備する電子機器に関する。特にデジタル信号を出力する光電変換装置及び当該光電変換装置を具備する電子機器に関する。

【背景技術】

【0002】

光を検知するための用途に用いられる光電変換装置は数多く知られており、例えば可視光センサ等が実用化されている。光電変換装置は、人間の生活環境に応じて照度調整や、オンまたはオフの制御などが必要な機器類に数多く用いられている。

20

【0003】

表示装置では、表示装置の周囲の明るさを検出し、その表示輝度を調整することが行なわれているものもある。光電変換装置により、周囲の明るさを検出して適度な表示輝度を得ることによって、視認性を向上させ、表示装置の無駄な電力を減らすことができるからである。例えば、輝度調整用の光センサを具備する表示装置としては、携帯電話、表示部付きコンピュータが挙げられる。

【0004】

光電変換装置は、光のセンシング部分にフォトダイオードなどの光電変換素子を用い、光電変換素子に流れる電流量に基づいて照度を検出することができる。特許文献 1 には電荷蓄積型の光センサについて、入射光量に応じてフォトダイオードから流れる電流によりコンデンサ（容量素子）に蓄積された電荷を定電流回路（定電流源）により放電されることで変化する電位をコンパレータで検出し、コンパレータで検出した電位の変化に要する時間をカウンター回路及びラッチ回路によってデジタル信号として出力する構成について記載している。また特許文献 2 には、シリコン基板を用い、シリコン基板上の第 1 のフォトダイオードと第 2 のフォトダイオードとで分光感度特性に応じた物理量の差分を取ることにより、視感度に近い分光感度特性を得る光電変換装置について記載している。

30

【特許文献 1】特開平 6 - 313840 号公報

【特許文献 2】特開 2006 - 332226 号公報

【発明の開示】

【発明が解決しようとする課題】

40

【0005】

特許文献 1 の光電変換装置では、入射光量に応じてフォトダイオードより流れる電流が小さい場合、容量素子に入射光量の検出が可能な程度の電荷が蓄積できず、照度の検出が難しくなるといった課題がある。また特許文献 2 の光電変換装置では、視感度に近い分光感度特性が得られるものの、入射光量に応じてフォトダイオードより流れる電流が小さい場合、第 1 のフォトダイオードと第 2 のフォトダイオードとで分光感度特性に応じた物理量の差分を取ることできず、照度の検出が難しくなるといった課題がある。

【0006】

また、表示装置の技術の進歩に伴い、液晶表示装置ではバックライトの輝度、エレクトロルミネッセンス素子（EL 素子）を具備する表示装置では EL 素子の輝度が向上している

50

。輝度の向上は、高画質化を図る上で重要なものの、消費電力の増加が問題となる。消費電力増加の問題に対しては、室内等の暗い場所で表示装置の輝度を、視認性を低減させない程度に、小さくすることが有効である。そのため、表示装置周辺の明るさを検知する光電変換装置には、特に低照度領域での分解能を高めた検知が求められている。

【0007】

なお分解能とは、単位照度区間における測定分解能のことという。

【0008】

本発明の課題の一は、視感度に近い分光感度特性を得ることができるとともに、低照度領域での照度の分解能を向上させた光電変換装置を提供することである。

【課題を解決するための手段】

10

【0009】

本発明の一は、第1の光電変換素子と、前記第1の光電変換素子の光電流を增幅した第1の電流を流すための第1の增幅回路と、第1の光電変換素子とは異なる分光感度特性を有する第2の光電変換素子と、前記第2の光電変換素子の光電流を增幅した第2の電流を流すための第2の增幅回路と、前記第1の増幅回路に向けて前記第1の電流が流れることで第1のデジタル信号を出力する第1のA/D変換回路と、前記第2の増幅回路に向けて前記第2の電流が流れることで第2のデジタル信号を出力する第2のA/D変換回路と、前記第1のデジタル信号と前記第2のデジタル信号との差分を出力するための減算回路と、を有し、前記第1のA/D変換回路及び第2のA/D変換回路は、第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して前記第1の電流及び第2の電流に応じた放電がなされる容量素子と、前記容量素子の一方の電極の電位と第2の電位を比較するコンパレータと、クロック信号を生成し、出力するクロック生成回路と、前記クロック信号によりカウント値をカウントアップし、前記カウント値を出力するカウンター回路と、前記コンパレータより出力される信号に応じて、前記カウント値をラッチして出力するラッチ回路と、を有する光電変換装置である。

20

【0010】

また本発明の一は、第1の光電変換素子と、前記第1の光電変換素子の出力電流を增幅した第1の電流を流すための第1の増幅回路と、第1の光電変換素子とは異なる分光感度特性を有する第2の光電変換素子と、前記第2の光電変換素子の出力電流を增幅した第2の電流を流すための第2の増幅回路と、前記第1の電流と前記第2の電流との差分を電圧値として出力するための減算回路と、前記電圧値に応じた第3の電流を流すための電圧電流変換回路と、前記電圧電流変換回路に向けて前記第3の電流が流れることで、デジタル信号を出力するA/D変換回路と、を有し、前記A/D変換回路は、第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して前記第1の電流及び第2の電流に応じた放電がなされる容量素子と、前記容量素子の一方の電極の電位と第2の電位を比較するコンパレータと、クロック信号を生成し、出力するクロック生成回路と、前記クロック信号によりカウント値をカウントアップし、前記カウント値を出力するカウンター回路と、前記コンパレータより出力される信号に応じて、前記カウント値をラッチして出力するラッチ回路と、を有する光電変換装置である。

30

【0011】

また本発明の一は、第1の光電変換素子と、前記第1の光電変換素子の出力電流を增幅した第1の電流を流すための第1の増幅回路と、前記第1の光電変換素子とは異なる分光感度特性を有する第2の光電変換素子と、前記第2の光電変換素子の出力電流を增幅した第2の電流を流すための第2の増幅回路と、前記第2の電流を、前記第1の電流が流れる前記第1の増幅回路に向けて流れるようにして、前記第1の電流と前記第2の電流との差分に応じた第3の電流を得るためにカレントミラー回路と、前記第1の増幅回路に向けて前記第3の電流が流れることで、デジタル信号を出力するためのA/D変換回路と、を有し、前記A/D変換回路は、第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して前記第1の電流及び第2の電流に応じた放電がなされる容量素子と、前記容量素子の一方の電極の電位と第2の電位を比較するコンパレータと、クロック信号を生成し、出

40

50

力するクロック生成回路と、前記クロック信号によりカウント値をカウントアップし、前記カウント値を出力するカウンター回路と、前記コンパレータより出力される信号に応じて、前記カウント値をラッチして出力するラッチ回路と、を有する光電変換装置である。

#### 【発明の効果】

##### 【0012】

本発明の光電変換装置により、視感度に近い分光感度特性を得ることができると共に、低照度領域での照度の分解能を向上させた光電変換装置を提供することができる。

#### 【発明を実施するための最良の形態】

##### 【0013】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

10

##### 【0014】

#### (実施の形態1)

本実施の形態では、本発明の光電変換装置の構成及びその動作について説明する。なお、本実施の形態で説明する光電変換装置は、光電変換素子により得られる照度に関するアナログの信号（以下、アナログ信号という）をデジタルの信号（以下、デジタル信号という）に変換して出力する回路（以下、アナログデジタル変換回路：A/D変換回路という）である。

20

##### 【0015】

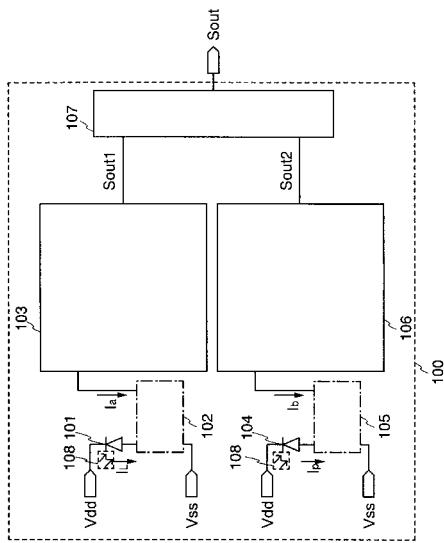

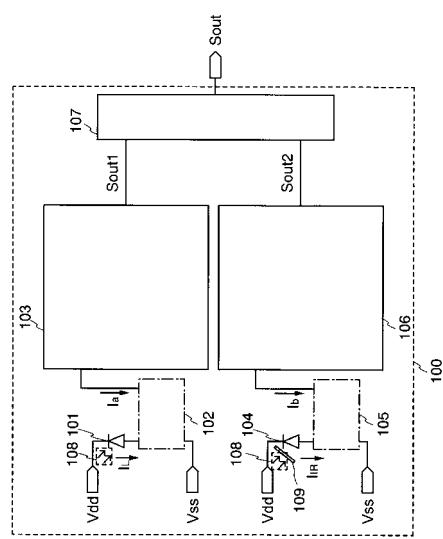

まず本発明の光電変換装置における回路図について説明する。図1に示す光電変換装置100は、第1の光電変換素子101、第1の増幅回路102、第1のA/D変換回路103、第2の光電変換素子104、第2の増幅回路105、第2のA/D変換回路106、及び減算回路107を有する。第1の光電変換素子101は、一方の端子（陰極側）に高電源電位（Vdd）が供給され、他方の端子（陽極側）が第1の増幅回路102に電気的に接続されている。第1の増幅回路102は、第1の光電変換素子101より出力される光電流I\_Lを増幅した第1の電流I\_aを低電源電位（Vss）に向けて流すための回路である。また、第1の増幅回路102は低電源電位Vssが供給されている。また、第1のA/D変換回路103は、第1の増幅回路102に向けて流れる第1の電流I\_aに応じて、第1のデジタル信号Sout1を出力する回路である。第2の光電変換素子104は、一方の端子に高電源電位Vddが供給され、他方の端子が第2の増幅回路105に電気的に接続されている。第2の増幅回路105は、第2の光電変換素子104より出力される光電流I\_pを増幅した第2の電流I\_bを低電源電位Vssに向けて流すための回路である。また、第2の増幅回路105は低電源電位Vssが供給されている。また、第2のA/D変換回路106は、第2の増幅回路105に向けて流れる第2の電流I\_bに応じて、第2のデジタル信号Sout2を出力する回路である。減算回路107は、第1のA/D変換回路103より出力される第1のデジタル信号Sout1と、第2のA/D変換回路106より出力される第2のデジタル信号Sout2との差分を演算して、デジタル信号Soutとして出力するための回路である。また図1中矢印108は、第1の光電変換素子101及び第2の光電変換素子104に入射される外光を表すものである。

30

##### 【0016】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

40

##### 【0017】

なお本明細書において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気

50

的に接続されているとは、AとBとの間に何らかの電気的作用を有する対象物が存在するとき、対象物を介してAとBとが概略同一ノードとなる場合を表すものとする。

#### 【0018】

具体的には、トランジスタをはじめとするスイッチング素子を介してAとBとが接続され、該スイッチング素子の導通によって、AとBとが概略同電位となる場合や、抵抗素子を介してAとBとが接続され、該抵抗素子の両端に発生する電位差が、AとBとを含む回路の動作に影響しない程度となっている場合など、回路動作を考えた場合、AとBとが同一ノードとして捉えて差し支えない状態である場合を表す。

#### 【0019】

第1の光電変換素子101の分光感度特性は、第2の光電変換素子104の分光感度特性の波長領域より広いものであるとする。一例として第1の光電変換素子101は、単結晶シリコン基板または多結晶シリコン等を用いて作製された光電変換素子のような、可視光の波長領域からはずれた分光感度を有する素子とする。本明細書では、単結晶シリコン基板で第1の光電変換素子を形成するものとして説明していく。単結晶シリコン基板で形成された光電変換素子は、可視光の波長領域である360以上830nmの波長領域とは異なり、赤外領域である900nm付近で高い量子効率を有する。そのため、第1の光電変換素子101の外光の分光感度は、可視光領域から赤外領域にかけて広範囲で得られることとなる。そして単結晶シリコンの分光感度に応じた光電流 $I_L$ が流れることとなる。

10

#### 【0020】

また第2の光電変換素子104は、第1の光電変換素子101とは異なる分光感度特性を有するものである。一例として、第2の光電変換素子104は、第1の光電変換素子101とモノリシックに作られており、ここでは単結晶シリコン基板を用いて作られているものとする。そして第2の光電変換素子の入射される外光を、可視光を除いた赤外領域の光とする構成とすることにより、第1の光電変換素子101とは異なる分光感度特性を得るものとする。そのため、第2の光電変換素子104の分光感度は、赤外領域の光の強度に応じたものとなり、第2の光電変換素子104では、赤外光の分光感度に応じた光電流 $I_P$ が流れることとなる。

20

#### 【0021】

なお本実施の形態では一例として、第2の光電変換素子104で第1の光電変換素子101とは異なる分光感度特性を得るために、図17に示すように、光が入射される側に赤外領域の光を透過するフィルタ（以下、赤外光透過フィルタ109）を設ける構成とする。これは、第1の光電変換素子101及び第2の光電変換素子104より得られるデジタル信号より差分を演算することで、特許文献2にあるように、可視光の強度となるように赤外光を透過するフィルタを選択したことによるものである。本実施の形態では、第1の光電変換素子101より得られる分光感度特性に応じた物理量と、第2の光電変換素子104より得られる分光感度特性より得られる物理量の差分を演算することにより所望の分光感度に応じた物理量が得られるものとして説明を行う。なお、差分を演算することによりデジタル信号Soutが可視光の強度である照度を得られる構成であれば、光フィルタの有無は問わない。

30

#### 【0022】

なお、第1の光電変換素子101及び第2の光電変換素子104には、PINフォトダイオードを適用すればよい。また第1の光電変換素子101及び第2の光電変換素子104として、PINフォトダイオードの代わりに、PNフォトダイオードを用いても良い。また第1の光電変換素子101及び第2の光電変換素子104は、同じ大きさの開口部により外部からの同じ強度の光が照射される構成とすることがよい。同じ強度の光を第1の光電変換素子101及び第2の光電変換素子104で共に受光し、そして電気的な信号の差分を演算することで、正確な照度の算出を行うことができるからである。なお、第1の光電変換素子101と第2の光電変換素子104とを異なる大きさにして形成した際には、遮光部を設けることにより、受光状態を同じ程度にすることができる、好適である。

40

#### 【0023】

50

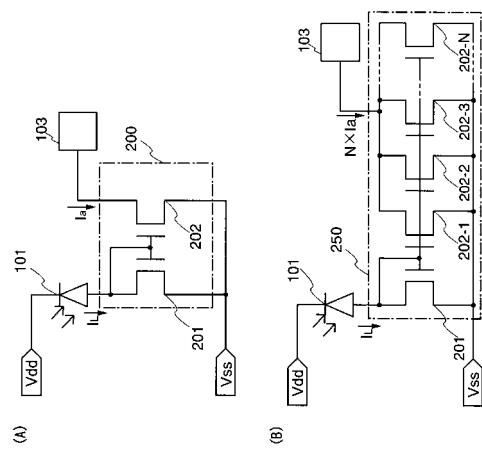

第1の増幅回路102は、第1の光電変換素子101から出力される光電流 $I_L$ を増幅した第1の電流 $I_a$ を生成するための回路である。また第2の増幅回路105は、第2の光電変換素子104から出力される光電流 $I_p$ を増幅した第2の電流 $I_b$ を生成するための回路である。図2(A)に第1の増幅回路102及び第2の増幅回路105に適用される増幅回路200の一例を示す。図2(A)は示すように増幅回路200はカレントミラー回路で構成されており、第1のnチャネル型トランジスタ201及び第2のnチャネル型トランジスタ202を有する。第1のnチャネル型トランジスタ201の第1端子は第1の光電変換素子101の陽極に電気的に接続されている。第1のnチャネル型トランジスタ201及び第2のnチャネル型トランジスタ202のゲート端子は互いに電気的に接続されており、第1のnチャネル型トランジスタ201の第1端子は第1のnチャネル型トランジスタ201及び第2のnチャネル型トランジスタ202のゲート端子に電気的に接続されている。第1のnチャネル型トランジスタ201及び第2のnチャネル型トランジスタ202の第2端子には低電源電位 $V_{SS}$ が供給されている。

10

#### 【0024】

また、第1の増幅回路102及び第2の増幅回路105に適用されるカレントミラー回路は、図2(A)で示した第2のnチャネル型トランジスタ202を、図2(B)に示すように電気的に並列に複数配設する構成としてもよい。図2(B)に示すように増幅回路250として、第2のnチャネル型トランジスタ202-1乃至202-N(Nは2以上の自然数)と複数設けることにより、第1の電流 $I_a$ 及び第2の電流 $I_b$ をN倍にして第2のnチャネル型トランジスタ202-1乃至202-Nの側で流すことができる。そのため、第1の光電変換素子101及び第2の光電変換素子104への入射光量が小さい場合であっても十分な電流を流すことができる。また第2のnチャネル型トランジスタ201のチャネル幅を長くする、またはチャネル長を短くすることでも、十分な電流を流すことができる。

20

#### 【0025】

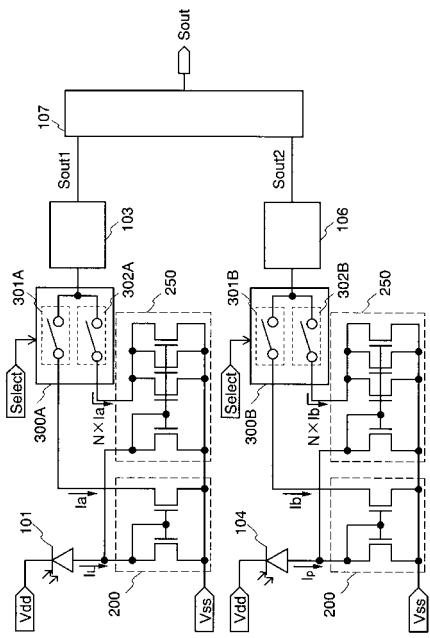

また図1で示した第1の増幅回路102及び第2の増幅回路105は、入力電流(光電流 $I_L$ 及び光電流 $I_p$ )に対する増幅率を照度に応じて切り替える構成としてもよい。図3に、照度に応じて光電流 $I_L$ 及び光電流 $I_p$ の増幅率を切り替える構成について示す。図3では、一例としては、第1の光電変換素子101からの光電流 $I_L$ 及び第2の光電変換素子104からの光電流 $I_p$ を増幅する回路を、図2(A)、(B)で示す増幅回路200と増幅回路250とし、選択信号Selectによって光電流 $I_L$ 及び光電流 $I_p$ を増幅する回路を切り替える切り替え回路300A及び300Bを有する。切り替え回路300Aは第1のスイッチ301A及び301Bを有し、切り替え回路300Bは第2のスイッチ302A及び302Bを有し、選択信号Selectによって第1のAD変換回路103及び第2のAD変換回路106に電気的に接続される増幅回路を切り替える。なお、複数の異なる増幅率が得られる増幅回路を配し、切り替え回路300A及び300Bにより入力電流に対する増幅率を照度に応じて切り替える構成とすることで照度に応じた光電流 $I_L$ 及び光電流 $I_p$ の増幅率を最適化することができる。

30

#### 【0026】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難な場合もある。そこで、本実施の形態においては、ソース及びドレインとして機能する領域のそれぞれを、第1端子、第2端子と表記するものとする。またゲートとして機能する端子については、ゲート端子と表記するものとする。

40

#### 【0027】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタとして、様々な形態のトランジスタを用いることができる。例えば、光電変換素子と同じ

50

基板上に形成する単結晶シリコンを用いて作製されたトランジスタを用いることができる。また別途形成した、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有するトランジスタなどを用いることもできる。また、チャネル形成領域に用いる半導体として、化合物半導体、より好ましくは酸化物半導体を用いてもよい。酸化物半導体として、例えば、酸化亜鉛（ZnO）、酸化チタン（TiO<sub>2</sub>）、酸化マグネシウム亜鉛（Mg<sub>(x)</sub>Zn<sub>(1-x)</sub>O）、酸化カドミウム亜鉛（Cd<sub>x</sub>Zn<sub>(1-x)</sub>O）、酸化カドミウム（CdO）、またはIn-Ga-Zn-O系のアモルファス酸化物半導体（a-IGZO）等を用いればよい。酸化物半導体は、透明であるため、光電変換素子と重畠して設けることができ、光電変換装置の小型化を図ることができる。

10

### 【0028】

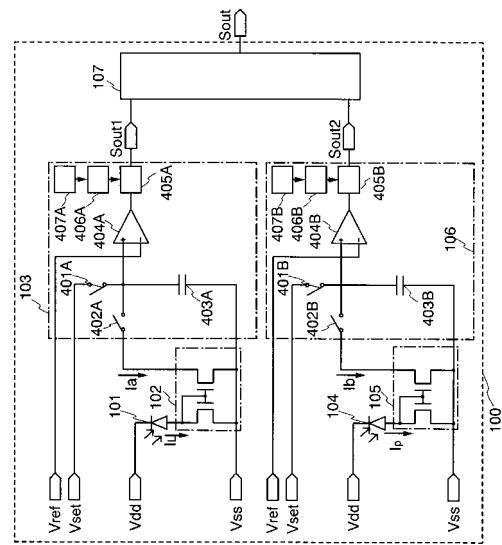

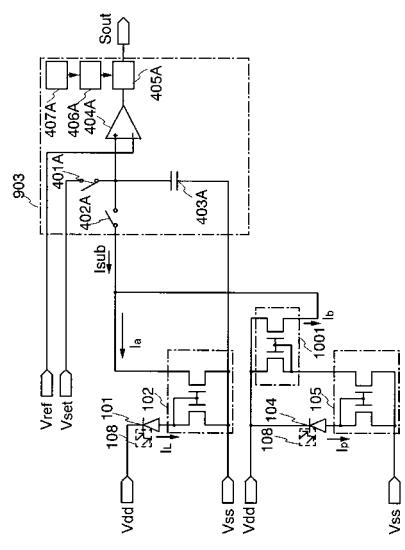

次に図4を用いて、図1で示した光電変換装置100を具体化した装置を説明する。図4に示す光電変換装置100は、図1で示した第1の增幅回路102、第2の增幅回路105、第1のAD変換回路103、第2のAD変換回路106について具体的な回路構成について示している。第1の増幅回路102及び第2の増幅回路105は、図2(A)に示すようにカレントミラー回路で構成されている。第1のAD変換回路103は、第1のスイッチ401A、第2のスイッチ402A、容量素子403A、コンパレータ404A、ラッチ回路405A、カウンター回路406A、クロック生成回路407Aを有する。第2のAD変換回路106は、第1のスイッチ401B、第2のスイッチ402B、容量素子403B、コンパレータ404B（比較回路ともいう）、ラッチ回路405B、カウンター回路406B、クロック生成回路407Bを有する。

20

### 【0029】

第1のAD変換回路103において、第1のスイッチ401Aの一方の端子は第1の電位（充電電位、またはV<sub>set</sub>ともいう）が供給され、第2の端子は容量素子403Aの一方の電極、第2のスイッチ402Aの一方の端子、及びコンパレータ404Aの非反転入力端子に電気的に接続されている。容量素子403Aの他方の電極には、低電源電位V<sub>ss</sub>が供給されている。第2のスイッチ402Aの第2の端子は第1の増幅回路102の第2のnチャネル型トランジスタ202の第1端子に電気的に接続されている。コンパレータ404Aの反転入力端子には第2の電位（参照電位、またはV<sub>ref</sub>ともいう）が供給されている。クロック生成回路407Aは、カウンター回路406Aにクロック信号を供給している。カウンター回路406Aはクロック信号の波数をカウントし、得られるカウント値をラッチ回路405Aに供給する。ラッチ回路405Aは、カウンター回路406Aより取得するカウント値を、コンパレータ404Aからの信号に応じてラッチ（保持）し、第1のAD変換回路103からのデジタル信号S<sub>out1</sub>として出力する。

30

### 【0030】

また第2のAD変換回路106において、第1のスイッチ401Bの一方の端子は第1の電位が供給され、第2の端子は容量素子403Bの一方の電極、第2のスイッチ402Bの一方の端子、及びコンパレータ404Bの非反転入力端子に電気的に接続されている。容量素子403Bの他方の電極には、低電源電位V<sub>ss</sub>が供給されている。第2のスイッチ402Bの第2の端子は第1の増幅回路102の第2のnチャネル型トランジスタ202の第1端子に電気的に接続されている。コンパレータ404Bの反転入力端子には第2の電位が供給されている。クロック生成回路407Bは、カウンター回路406Bにクロック信号を供給している。カウンター回路406Bはクロック信号の波数をカウントし、得られるカウント値をラッチ回路405Bに供給する。ラッチ回路405Bは、カウンター回路406Bより取得するカウント値を、コンパレータ404Bからの信号に応じてラッチし、第2のAD変換回路106からのデジタル信号S<sub>out2</sub>として出力する。

40

### 【0031】

なお本明細書において、スイッチは、一方の端子と他方の端子との導通または非導通を制御できるものであればよく、特定のものに限定されない。スイッチとしては、電気的スイッチや機械的なスイッチなどがあり、一例として電界効果トランジスタを用いて構成す

50

ればよい。

#### 【0032】

なお図4では、第1のスイッチ401Aとしてpチャネル型トランジスタ、第2のスイッチ402Aとして、アナログスイッチを用いることが好ましい。第1のスイッチ401Aは一方が固定電位である第1の電位V<sub>set</sub>に電気的に接続されるためpチャネル型トランジスタを用いることが好ましい。また第2のスイッチ402Aは両端の端子の電位が共に変動するため、オンまたはオフを確実に制御するためにアナログスイッチを用いることが好ましい。また、第1のスイッチ401Aと第2のスイッチ402Aとは、交互にオンまたはオフの動作をさせることが好ましい。その結果、第1のスイッチ401A及び第2のスイッチ402Aを光電変換装置100の外部にある制御回路からの信号が一つで動作させることができるため、製造コストを低減することができる。

10

#### 【0033】

なお容量素子403Aは、第1のスイッチ401Aがオンになることで第1の電位V<sub>set</sub>により充電がなされ、その後第2のスイッチ402Aがオンになり、第1の增幅回路102に流れる電流に応じて放電するものである。そのため、第1の増幅回路102の第2のnチャネル型トランジスタ202に電荷が放電される際の時間を考慮して、容量素子403Aの静電容量は電荷を充電できる容量を備えておくことが望ましい。また、第1の電位V<sub>set</sub>は、高電源電位V<sub>dd</sub>以下で、低電源電位V<sub>ss</sub>よりも大きい値に設定することが好ましい。なお、第1の電位V<sub>set</sub>を高電源電位V<sub>dd</sub>と同じ値にする場合には、高電源電位V<sub>dd</sub>が固定電位であることが望ましい。

20

#### 【0034】

またコンパレータ404Aの反転入力端子に供給される第2の電位V<sub>ref</sub>は、第1のスイッチ401Aがオンになることで第1の電位V<sub>set</sub>による充電がなされ、その後第1の増幅回路102による放電がなされた際の容量素子403Aの一方の電極の電位と、比較することで出力端子よりコンパレータの出力信号を得るための電位である。第2の電位V<sub>ref</sub>としては、第1の電位V<sub>set</sub>よりも小さく、低電位電源V<sub>ss</sub>よりも大きい値に設定することが好ましい。コンパレータの出力信号としては、Hレベルの信号またはLレベルの信号が出力されることとなる。

#### 【0035】

なおラッチ回路405Aは、コンパレータ404Aの出力信号に応じて、カウンターレジスタ406Aより取得したカウント値をラッチしてするための回路である。ラッチ回路405Aで保持されたカウント値は、第1のAD変換回路103からのデジタル信号Sout1として減算回路107に出力する。なお出力されるデジタル信号Soutは、ビット数に応じたバス線にて、ラッチ回路405Aから減算回路107に出力される。

30

#### 【0036】

またカウンターレジスタ406Aは、クロック生成回路407Aより出力されるクロック信号の波数をカウントするための回路である。カウンターレジスタ406Aで得られるカウント値はラッチ回路405Aに供給される。

#### 【0037】

またクロック生成回路407Aは、カウンターレジスタ406Aでカウントをするためのクロック信号をカウンターレジスタ406Aに出力するための回路である。クロック生成回路としては、一例としては、固体振動子発振回路、またはCR発振回路、リングオシレータ等を用いて構成すればよい。

40

#### 【0038】

なお第2のAD変換回路106における第1のスイッチ401B、第2のスイッチ402B、容量素子403B、コンパレータ404B、クロック生成回路407B、カウンターレジスタ406B、及びラッチ回路405Bについては、第1のAD変換回路103で説明した各構成と同様であり、説明を省略する。

#### 【0039】

なお第1のAD変換回路103及び第2のAD変換回路106は、上記説明した構成とは

50

別に、高電源電位  $V_{dd}$ 、低電源電位  $V_{ss}$ 、第1の電位  $V_{set}$  及び第2の電位  $V_{ref}$  等の複数の電位を生成するための定電圧回路を有する。また第1のAD変換回路103及び第2のAD変換回路106は、上記説明した構成とは別に、第1のスイッチ401A及び401B並びに第2のスイッチ402A及び402Bのオンまたはオフを切り替え、ラッチ回路405A及び405B並びにカウンター回路406A及び406Bをリセットするための制御回路を有する。

#### 【0040】

減算回路107は、デジタル信号  $S_{out1}$  とデジタル信号  $S_{out2}$ との差分を演算するための回路である。具体的には、各ビットに応じたバス線毎に論理回路を設けることにより、差分を演算する構成とすればよい。デジタル信号  $S_{out1}$  からデジタル信号  $S_{out2}$  の差分をとったデジタル値の信号は、単結晶シリコンの分光感度特性より赤外光の分光感度特性が減算された値であり、そしてこのデジタル値の信号は視感度に近い可視光領域の分光感度に応じたデジタル信号  $S_{out}$  として出力され、照度の出力を得ることができる。

#### 【0041】

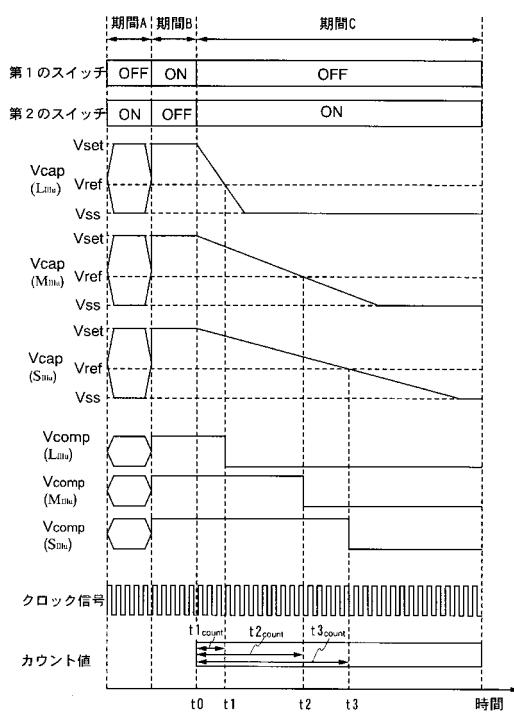

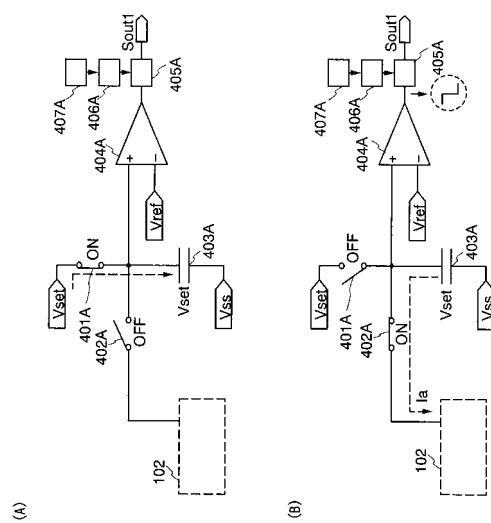

次に図4で示した光電変換装置100での第1のAD変換回路103及び第2のAD変換回路106の具体的な動作について、図5、図6(A)、及び図6(B)を用いて説明する。なお図5、図6(A)、及び図6(B)では、第1のAD変換回路103の動作を一例として説明する。図5には、第1のスイッチ401A及び第2のスイッチ402Aのオンまたはオフを切り替えた際の容量素子403Aの一方の電極の電位  $V_{cap}$ 、及びコンパレータ404Aの出力信号の電位  $V_{comp}$ 、クロック信号、及びカウント値についてのタイミングチャートについて示したものである。なお、 $V_{cap}$  及び  $V_{comp}$  については、第1の光電変換素子101に光が照射された際の照度の大きさを  $L_{I11u}$ (大)、 $M_{I11u}$ (中)、 $S_{I11u}$ (小)の3段階に分けて説明する。また、図5に示すように、第1のAD変換回路103の動作は、期間A、B、Cの3つの期間で異なる。

#### 【0042】

まず図5に示した、第1のスイッチ401Aがオフの状態、第2のスイッチ402Aがオンの状態である期間Aでの第1のAD変換回路103の動作を説明する。期間Aにおいて容量素子403Aの一方の電極の電位  $V_{cap}$  は、光電流  $I_L$  を増幅した第1の電流  $I_a$  の大きさに応じて変動し続け、電位の定まらない状態となる。また期間Aにおいて、コンパレータ404Aの出力信号の電位  $V_{comp}$  は  $V_{cap}$  の電位に応じて変動し続け、電位の定まらない状態となる。なおクロック信号は、期間Aでクロック生成回路407Aよりカウンター回路406Aへ出力される。そのためカウンター回路406Aでは、カウント値がカウントアップされるものの、カウント値は期間Aでラッチ回路405Aに保持されない。

#### 【0043】

次に第1のスイッチ401Aがオンの状態、第2のスイッチ402Aがオフの状態にある期間Bについて説明する。期間Bにおいて、容量素子403Aの一方の電極の電位  $V_{cap}$  は、光電流  $I_L$  を増幅した第1の電流  $I_a$  の大きさに関わらず第1の電位  $V_{set}$  となるものである。また期間Bにおいて、コンパレータ404Aの出力信号の電位  $V_{comp}$  は照度の大きさに関わらず、第1の電位  $V_{set}$  が第2の電位  $V_{ref}$  を上回るため、Hレベルの信号が出力されるものである。

#### 【0044】

期間Bにおける各スイッチのオンまたはオフ、電荷の流れについて、図6(A)に模式的に示す。容量素子403Aは、第1のスイッチ401Aがオンになることによって、第1の電位  $V_{set}$  が供給される。また、第2のスイッチ402Aがオフになっているため、容量素子403Aから第1の増幅回路102への電荷の移動はない。

#### 【0045】

次に第1のスイッチ401Aがオフの状態、第2のスイッチ402Aがオンの状態にある期間Cについて説明する。まず期間Cにおいて、第1の光電変換素子101への照度が大

10

20

30

40

50

きい場合(図5中  $L_{I11u}$ )、第1の增幅回路102に向けて流れる第1の電流 $I_a$ が大きくなり、容量素子403Aの一方の電極の電位 $V_{cap}$ は下降する。そのため、時間 $t_0$ (時間 $t_0 < \text{時間 } t_1 < \text{時間 } t_2 < \text{時間 } t_3$ )で容量素子403Aの電位 $V_{cap}$ が $V_{set}$ であったのが時間 $t_1$ で電位 $V_{ref}$ となり、その後容量素子403Aからの放電が完了することで電位 $V_{ss}$ となる。このとき、コンパレータ404Aの出力信号の電位 $V_{comp}$ は、容量素子403Aの電位 $V_{cap}$ が第1の電位 $V_{set}$ から第2の電位 $V_{ref}$ をとなつた際に、Lレベルの信号を出力する。そして、当該信号でラッチ回路405Aは、入力されるカウント値を保持する。なお期間Cになる時間 $t_0$ と同時に、カウンター回路406Aおよびラッチ回路405Aがリセットされ、カウンター回路406Aでクロック信号に基づくカウントアップがなされる。そして、時間 $t_1$ にコンパレータ404Aの出力信号の電位 $V_{out}$ がラッチ回路405Aに入力されることで時間 $t_0$ から時間 $t_1$ の間の期間のクロック信号に基づいたカウント値 $t_{1count}$ が得られることとなる。

10

#### 【0046】

また第1のスイッチ401Aがオフの状態、第2のスイッチ402Aがオンの状態にある期間Cであって、第1の光電変換素子101への照度が中程度の場合(図5中  $M_{I11u}$ )、第1の增幅回路102に向けて流れる第1の電流 $I_a$ が大きい場合に比べて小さいため、容量素子403Aの一方の電極の電位 $V_{cap}$ は減少の割合は小さいものの下降していく。そのため、時間 $t_0$ で容量素子403Aの電位 $V_{cap}$ が $V_{set}$ であったのが時間 $t_2$ で電位 $V_{ref}$ となり、その後容量素子403Aからの放電が完了することで電位 $V_{ss}$ となる。このとき、コンパレータ404Aの出力信号の電位 $V_{comp}$ は、容量素子403Aの電位 $V_{cap}$ が第1の電位 $V_{set}$ から第2の電位 $V_{ref}$ となつた際に、Lレベルの信号を出力する。そして、当該信号でラッチ回路405Aは、入力されるカウント値を保持する。なお期間Cになる時間 $t_0$ と同時に、カウンター回路406Aおよびラッチ回路405Aがリセットされ、カウンター回路406Aでクロック信号に基づくカウントアップがなされる。そして、時間 $t_2$ にコンパレータ404Aの出力信号の電位 $V_{comp}$ がラッチ回路405Aに入力されることで時間 $t_0$ から時間 $t_2$ の間の期間のクロック信号に基づいたカウント値 $t_{2count}$ が得られることとなる。

20

#### 【0047】

また第1のスイッチ401Aがオフの状態、第2のスイッチ402Aがオンの状態にある期間Cであって、第1の光電変換素子101への照度が小さい場合(図5中  $S_{I11u}$ )、第1の增幅回路102に向けて流れる第1の電流 $I_a$ も小さく減少の割合も小さいものの、容量素子403Aの一方の電極の電位 $V_{cap}$ は下降していく。そのため、時間 $t_0$ で容量素子403Aの電位 $V_{cap}$ が $V_{set}$ であったのが時間 $t_3$ で電位 $V_{ref}$ となり、その後容量素子403Aからの放電が完了することで電位 $V_{ss}$ となる。このとき、コンパレータ404Aの出力信号の電位 $V_{comp}$ は、容量素子403Aの電位 $V_{cap}$ が第1の電位 $V_{set}$ から第2の電位 $V_{ref}$ となつた際に、Lレベルの信号を出力する。そして、当該信号でラッチ回路405Aは、入力されるカウント値を保持する。なお期間Cになる時間 $t_0$ と同時に、カウンター回路406Aおよびラッチ回路405Aがリセットされ、カウンター回路406Aでクロック信号に基づくカウントアップがなされる。そして、時間 $t_3$ にコンパレータ404Aの出力信号の電位 $V_{comp}$ がラッチ回路405Aに入力されることで時間 $t_0$ から時間 $t_3$ の間の期間のクロック信号に基づいたカウント値 $t_{3count}$ が得られることとなる。

30

40

#### 【0048】

期間Cにおける各スイッチのオンまたはオフ、電荷の流れについて、図6(B)に模式的に示す。容量素子403Aは、第1のスイッチ401Aがオフになることによって、新たに第1の電位 $V_{set}$ が供給されることはない。一方、第2のスイッチ402Aがオンになっているため、容量素子403Aから第1の増幅回路102へ第1の電流 $I_a$ が流れ、容量素子403Aの放電が行われる。なお、第1の増幅回路102に流れる第1の電流 $I_a$ は、第1の増幅回路102が図2(A)で説明したようにカレントミラー回路を形成し

50

ていることにより、光電流  $I_L$  に比例した大きさとなる。

#### 【0049】

なお、第1のスイッチ 401A がオフの状態、第2のスイッチ 402A がオンの状態にある期間 C であって、第1の光電変換素子 101 に光が照射されず光電流  $I_L$  が流れない場合、容量素子 403A の一方の電極の電位  $V_{cap}$  は、第1の增幅回路 102 に流れる第1の電流  $I_a$  が生じないため、ほとんど減少しない。そのため、時間  $t_0$  で容量素子 403A の電位  $V_{cap}$  が  $V_{set}$  であるものの、時間の経過に伴う電位  $V_{ref}$  への変化がない。このとき、コンパレータ 404A の出力信号の電位  $V_{comp}$  は、容量素子 403A の電位  $V_{cap}$  が第1の電位  $V_{set}$  から第2の電位  $V_{ref}$  に変化しないため、H レベルの信号が出力し続けるものである。またクロック信号は、期間 C になった時間  $t_0$  より、カウンター回路 406A への出力がなされる。そのため上述のように照度に応じたカウント値を得ることが出来ず、カウント値はカウンター回路 406A の最大値に達してしまう。この場合、カウント値の最大値をラッチ回路に出力することが好ましい。

10

#### 【0050】

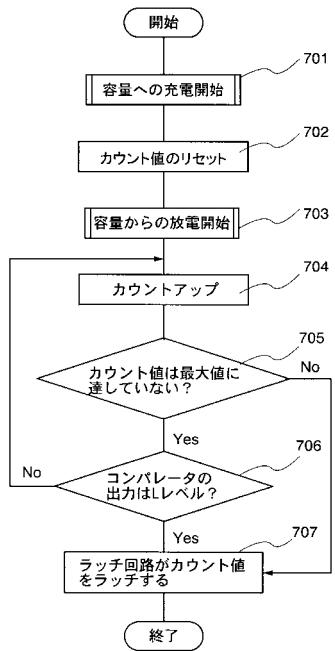

図5、図6(A)、図6(B)で説明した光電変換装置 100 での第1のAD変換回路 103 及び第2のAD変換回路 106 の具体的な動作について、図7に示すフローチャートを用いて説明する。

#### 【0051】

まず光電変換装置 100 は容量素子 403A への電荷の充電(リセット)を開始する(ステップ 701)。容量素子 403A への電荷の充電は、上述したように第1のスイッチ 401A をオン、第2のスイッチ 402A をオフにすることにより、第1の電位  $V_{set}$  が供給された配線と容量素子 403A とを電気的に接続させることによって行われる。またステップ 701 では容量素子 403A の充電と共に、クロック生成回路 407A からのクロック信号の出力が行われている。

20

#### 【0052】

次に光電変換装置 100 は、容量素子 403A への電荷の充電の後、カウンター回路 406A のカウント値のリセットを行う(ステップ 702)。また、ステップ 702 ではカウンター回路 406A のカウント値のリセットと共に、ラッチ回路 405A に保持されたカウント値の初期化を行う。

#### 【0053】

次に光電変換装置 100 は、第1の増幅回路 102 により、容量素子 403A に充電された電荷の放電をおこなう(ステップ 703)。容量素子 403A からの電荷の放電は、上述したように第1のスイッチ 401A をオフ、第2のスイッチ 402A をオンにすることにより、容量素子 403A と第1の増幅回路 102 との電気的な接続をさせることによって行われる。なお容量素子 403A に充電された電荷の放電は、ステップ 702 で行われるカウンター回路 406A のリセットと共に開始されてもよい。

30

#### 【0054】

次にステップ 703 では、クロック生成回路 407A からのクロック信号の出力に応じて、カウンター回路 406A ではカウント値のカウントアップが行われる(ステップ 704)。

40

#### 【0055】

次にステップ 704 で、カウントアップするカウント値が最大値に達した否かが判断される(ステップ 705)。ステップ 705 のとき、カウント値が最大値に達していなければ、ラッチ回路 405A に出力されるコンパレータ 404A からの出力信号  $V_{comp}$  が L レベルであるか否かの判断がされる(ステップ 706)。ステップ 706 のとき、カウント値が最大値に達しておらず、且つコンパレータ 404A の出力が L レベルではない場合、再度ステップ 704 でのカウント値のカウントアップが行われる。ステップ 705 で、カウントアップするカウント値が最大値に達した場合、及びカウント値が最大値に達しておらず、且つコンパレータ 404A の出力が L レベルのとき、ラッチ回路 405A がカウント値をラッチする(ステップ 707)。以上の動作により、光電変換装置 100 はラッ

50

チ回路 405A でラッチしたカウント値に基づいて光電流  $I_L$  の大きさに応じたデジタル信号  $S_{out} 1$  を出力させることができる。なお、上記説明した第 1 の A/D 変換回路 103 は、カウント値が小さい程、光電流  $I_L$  が大きく、カウント値が大きいほど光電流  $I_L$  が小さいということになる。カウント値が最大の場合には、光の検出がされなかったこととなるため、光の強度も「0」ということになる。

#### 【0056】

また図 5 乃至図 7 での説明では、第 1 の A/D 変換回路 103 を一例として、説明したが、第 2 の A/D 変換回路 106 についても同様にして、光電流  $I_P$  の大きさに応じたデジタル信号  $S_{out} 2$  を出力させることができる。

#### 【0057】

第 2 の A/D 変換回路より得られるデジタル信号  $S_{out} 2$  は、第 1 の光電変換素子 101 とは異なる分光感度特性を得るため、図 17 で示したように赤外光透過フィルタ 109 を透過して第 2 の光電変換素子 104 に照射されて得られる光電流  $I_P$  に応じた信号である。一方、第 1 の A/D 変換回路 103 より得られるデジタル信号  $S_{out} 1$  は、本実施の形態では、単結晶シリコン基板を用いて作られた第 1 の光電変換素子 101 に照射されて得られる光電流  $I_L$  に応じた信号である。そのため、可視光の波長領域とは異なり、赤外領域である 900 nm 付近で高い量子効率を有する。そのため、減算回路 107 で、デジタル信号  $S_{out} 1$  からデジタル信号  $S_{out} 2$  を減算することにより、可視光領域の分光感度に応じたデジタル信号  $S_{out}$  を得ることができる。

#### 【0058】

上述のように本実施の形態の構成では、光電流  $I_L$ 、光電流  $I_P$  の差分をとることにより、照度の出力をデジタル値で得ることができる。

#### 【0059】

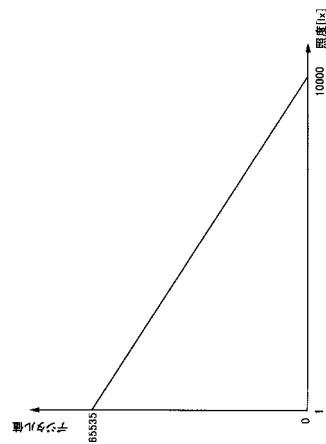

また、光電流  $I_L$ 、光電流  $I_P$  に応じて変化するデジタル信号  $S_{out}$  は、光の強度と光電流  $I_L$  との関係が比較的線形性を有するため、光電流  $I_L$  が小さければ、出力されるデジタル信号  $S_{out}$  の変化が緩やかとなる。そのため、デジタル信号  $S_{out}$  について、光電流  $I_L$  が小さい場合、光電変換素子に照射される光の照度に対応する値の間隔を大きくすることができます。そして特に、低照度領域（例えば、1 ルクス ( $1 \times$ ) 以上 1000 ルクス以下）の光の大きさを検出する上で分解能を向上させることができます。なお照度を横軸、デジタル信号  $S_{out}$  のデジタル値を縦軸とした際の関係について図 8 に示す。図 8 に示すように、照度の増加に伴い、デジタル値が減少する右下がりのグラフとなる。

#### 【0060】

なお、図 8 において、デジタル信号  $S_{out}$  のデジタル値は 16 ビット（0 乃至 65535）のデジタル値を生成するものとし、また、デジタル値に対応する照度としては、一例として、1 ルクス乃至 1000 ルクスとして示している。

#### 【0061】

上記照度とデジタル信号  $S_{out}$  のデジタル値の関係が右下がりのグラフに対して、照度の増加によってデジタル値も増加する、いわゆる右上がりのグラフだと、照度が大きすぎるとデジタル値が飽和してしまう。また、右上がりのグラフで低照度領域の分解能を高くしようとすると、低照度領域で対応するデジタル値の間隔をあけてとる必要があるため、照度のダイナミックレンジは広く取れないといったことになる。これに対し、右下がりのグラフの関係を有する本実施の形態で示す構成では、低照度であるとデジタル値が飽和するため、低照度領域の分解能を高めたとしてもダイナミックレンジを広くできる。そのため、本実施の形態で示す構成においては、特に低照度領域で分解能も高く、確度の高い照度に応じたデジタル値のデジタル信号を出力するとともに、広いダイナミックレンジを実現できる。

#### 【0062】

以上説明したように本実施の形態の光電変換装置の構成では、視感度に近い分光感度特性を得ることができると共に、低照度領域での照度の分解能を向上させた光電変換装置を提供することができる。

10

20

30

40

50

**【 0 0 6 3 】**

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

**【 0 0 6 4 】****( 実施の形態 2 )**

本実施の形態では、上記実施の形態とは別の構成について説明する。

**【 0 0 6 5 】**

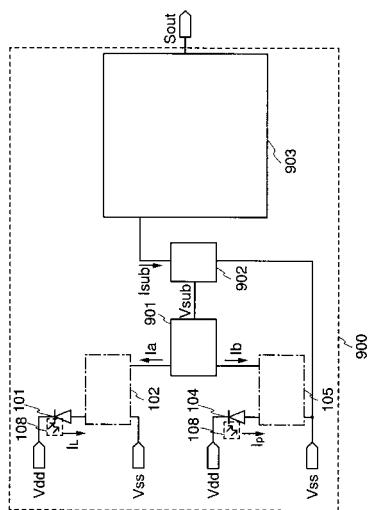

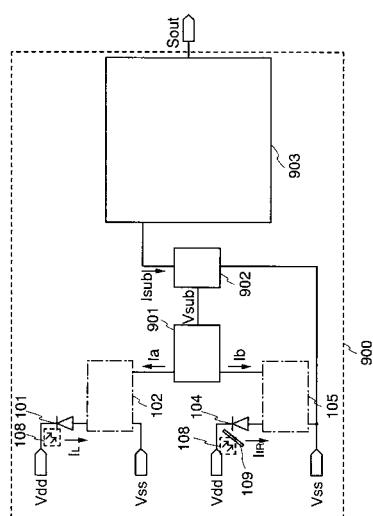

まず本発明の光電変換装置における回路図について説明する。図9に示す光電変換装置900は、第1の光電変換素子101、第1の增幅回路102、第2の光電変換素子104、第2の增幅回路105、減算回路901、電圧電流変換回路902、及びA/D変換回路903を有する。10

第1の光電変換素子101は、一方の端子(陰極側)に高電源電位(Vdd)が供給され、他方の端子(陽極側)が第1の増幅回路102に電気的に接続されている。第1の増幅回路102は、第1の光電変換素子101より出力される光電流ILを増幅した第1の電流Iaを低電源電位(Vss)に向けて流すための回路である。また、第1の増幅回路102は低電源電位Vssが供給されている。第2の光電変換素子104は、一方の端子に高電源電位Vddが供給され、他方の端子が第2の増幅回路105に電気的に接続されている。第2の増幅回路105は、第2の光電変換素子104より出力される光電流Ipを増幅した第2の電流Ibを低電源電位Vssに向けて流すための回路である。20

また、第2の増幅回路105は低電源電位Vssが供給されている。減算回路901は、第1の電流Ia及び第2の電流Ibの差分を演算し、電圧Vsusbとして出力するための回路である。また電圧電流変換回路902は、電圧Vsusbに応じた第3の電流Isusbを電圧電流変換回路902に向けて流すための回路である。また、A/D変換回路903は、電圧電流変換回路902に流れる第3の電流Isusbに応じて、デジタル信号Soutを出力する回路である。また図9中矢印108は、第1の光電変換素子101及び第2の光電変換素子104に入射される外光を表すものである。

**【 0 0 6 6 】**

なお本実施の形態では一例として、図9で示す構成の第2の光電変換素子104で第1の光電変換素子101とは異なる分光感度特性を得るために、図18に示すように、光が入射される側に赤外光透過フィルタ109を設ける構成とする。これは、第1の光電変換素子101及び第2の光電変換素子104より得られるデジタル信号より差分を演算することで、特許文献2にあるように、可視光の強度となるように赤外光を透過するフィルタを選択したことによるものである。30

本実施の形態では、第1の光電変換素子101より得られる分光感度特性に応じた物理量と、第2の光電変換素子104より得られる分光感度特性より得られる物理量の差分を演算することにより所望の分光感度に応じた物理量が得られるものとして説明を行う。なお、差分を演算することによりデジタル信号Soutが可視光の強度である照度を得られる構成であれば、光フィルタの有無は問わない。

**【 0 0 6 7 】**

なお、減算回路901は、第1の増幅回路102及び第2の増幅回路105で得られる第1の電流Ia及び第2の電流Ibの差分をとり、電圧値として出力する回路である。40

図9では、電圧Vsusbが出力される構成としているが、第1の電流Iaと第2の電流Ibとの差分を出力する回路であればよく、出力は電圧値によるものであっても、電流値によるものであってもよい。なお減算回路で差分を取る際にオペアンプによる差分を演算するには、第1の電流Ia及び第2の電流Ibを一旦電圧値に変換した上でオペアンプに入力して、電圧Vsusbを出力する構成とすればよい。減算回路901で第1の電流Iaと第2の電流Ibとの差分が演算されることで、単結晶シリコンの分光感度特性より赤外光の分光感度特性が減算された値である、視感度に近い可視光領域の分光感度に応じた電圧Vsusbが出力されることとなる。そのため、電圧Vsusbは光電変換装置900に照射される光の照度に応じた信号となる。

**【 0 0 6 8 】**

なお、電圧電流変換回路902は電圧Vsusbを第3の電流Isusbに変換し、第3の電50

流  $I_{sub}$  を A/D 変換回路 903 から電圧電流変換回路 902 に向けて流すための回路である。一例としては、トランジスタ等を用いて構成し、電圧  $V_{sub}$  がトランジスタのゲートに印加されるように構成すればよい。なお第 3 の電流  $I_{sub}$  も、電圧  $V_{sub}$  と同様に、光電変換装置 900 の照度に応じた信号となる。

#### 【0069】

なお、A/D 変換回路 903 は、上記実施の形態 1 で説明した第 1 の A/D 変換回路 103 及び第 2 の A/D 変換回路 106 の構成と同様である。また動作についても、上記実施の形態 1 で説明した第 1 の A/D 変換回路 103 及び第 2 の A/D 変換回路 106 について説明した箇所と同様である。そのため、光電変換装置 900 は、照度に応じたデジタル信号  $S_{out}$  を出力することができる。

10

#### 【0070】

以上説明したように本実施の形態の光電変換装置の構成では、視感度に近い分光感度特性を得ることができると共に、低照度領域での照度の分解能を向上させた光電変換装置を提供することができる。

#### 【0071】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0072】

##### (実施の形態 3)

本実施の形態では、上記実施の形態とは別の構成について説明する。

20

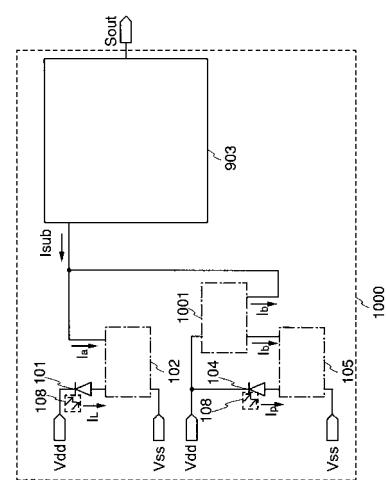

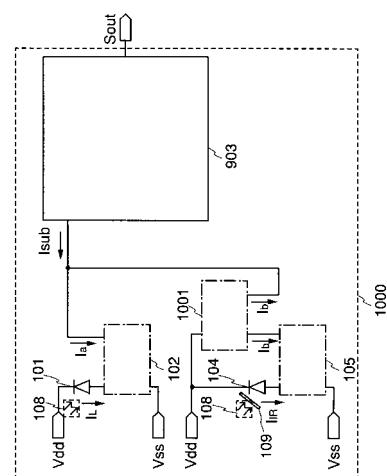

#### 【0073】

まず本発明の光電変換装置における回路図について説明する。図 10 に示す光電変換装置 1000 は、第 1 の光電変換素子 101、第 1 の增幅回路 102、第 2 の光電変換素子 104、第 2 の增幅回路 105、カレントミラー回路 1001、及び A/D 変換回路 903 を有する。第 1 の光電変換素子 101 は、一方の端子（陰極側）に高電源電位（ $V_{dd}$ ）が供給され、他方の端子（陽極側）が第 1 の增幅回路 102 に電気的に接続されている。第 1 の增幅回路 102 は、第 1 の光電変換素子 101 より出力される光電流  $I_L$  を増幅して第 1 の電流  $I_a$  を低電源電位（ $V_{ss}$ ）に向けて流すための回路である。また、第 1 の增幅回路 102 は低電源電位  $V_{ss}$  が供給されている。第 2 の光電変換素子 104 は、一方の端子に高電源電位  $V_{dd}$  が供給され、他方の端子が第 2 の增幅回路 105 に電気的に接続されている。第 2 の增幅回路 105 は、第 2 の光電変換素子 104 より出力される光電流  $I_P$  を増幅して第 2 の電流  $I_b$  を低電源電位  $V_{ss}$  に向けて流すための回路である。また、第 2 の增幅回路 105 は低電源電位  $V_{ss}$  が供給されている。カレントミラー回路 1001 は、第 2 の電流  $I_b$  を、第 1 の電流  $I_a$  が第 1 の增幅回路 102 に向けて流れる配線に、流すための回路である。A/D 変換回路 903 と、第 1 の增幅回路 102 及びカレントミラー回路 1001 とが電気的に接続される配線に、第 1 の電流  $I_a$  及び第 2 の電流  $I_b$  が流れることにより、第 1 の電流  $I_a$  と第 2 の電流  $I_b$  とが相殺されて、第 3 の電流  $I_{sub}$  が生成されることとなる。また、A/D 変換回路 903 は、A/D 変換回路 903 より流れる第 3 の電流  $I_{sub}$  に応じて、デジタル信号  $S_{out}$  を出力する回路である。また図 9 中矢印 108 は、第 1 の光電変換素子 101 及び第 2 の光電変換素子 104 に入射される外光を表すものである。

30

#### 【0074】

なお本実施の形態では一例として、図 10 で示す構成の第 2 の光電変換素子 104 で第 1 の光電変換素子 101 とは異なる分光感度特性を得るために、図 19 に示すように、光が入射される側に赤外光透過フィルタ 109 を設ける構成とする。これは、第 1 の光電変換素子 101 及び第 2 の光電変換素子 104 より得られるデジタル信号より差分を演算することで、特許文献 2 にあるように、可視光の強度となるように赤外光を透過するフィルタを選択したことによるものである。本実施の形態では、第 1 の光電変換素子 101 より得られる分光感度特性に応じた物理量と、第 2 の光電変換素子 104 より得られる分光感度特性より得られる物理量の差分を演算することにより所望の分光感度に応じた物理量が得

40

50

られるものとして説明を行う。なお、差分を演算することによりデジタル信号  $S_{out}$  が可視光の強度である照度を得られる構成であれば、光フィルタの有無は問わない。

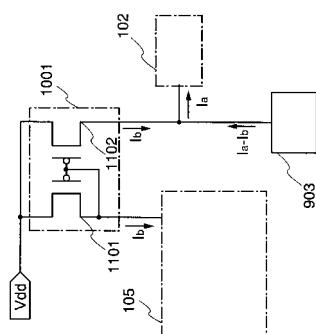

#### 【0075】

なお、カレントミラー回路 1001 は、第 2 の増幅回路 105 で得られる第 2 の電流  $I_b$  と同じ大きさの電流を流すための回路である。図 11 にカレントミラー回路の具体的な回路構成について示す。図 11 でカレントミラー回路 1001 は、第 1 の p チャネル型トランジスタ 1101、第 2 の p チャネル型トランジスタ 1102 を有する。第 1 の p チャネル型トランジスタ 1101 の第 1 端子及び第 2 の p チャネル型トランジスタ 1102 の第 1 端子は、高電源電位  $V_{dd}$  に電気的に接続されている。第 1 の p チャネル型トランジスタ 1101 及び第 2 の p チャネル型トランジスタ 1101 のゲート端子は互いに電気的に接続されており、第 1 の p チャネル型トランジスタ 1101 の第 2 端子に電気的に接続されている。第 1 の p チャネル型トランジスタ 1101 の第 2 端子は第 2 の増幅回路 105 に電気的に接続されており、第 2 の増幅回路 105 に向けて第 2 の電流  $I_b$  が流れている。第 2 の p チャネル型トランジスタ 1102 の第 2 端子は第 1 の増幅回路 102 及び AD 变換回路 903 に電気的に接続されている。10

#### 【0076】

第 1 の増幅回路に向けて流れる第 1 の電流  $I_a$  とカレントミラー回路より流れる第 2 の電流  $I_b$  の大きさは、光電流  $I_L$  及び光電流  $I_p$  の大きさに依る。光電流  $I_L$  は、単結晶シリコンが有する分光感度特性に基づいた光の強度に応じて出力されるものである。一方、光電流  $I_p$  は、単結晶シリコンが有する分光感度特性より、可視光以下の光以外の分光感度特性が分離された赤外光の強度に応じて出力されるものである。そのため、第 1 の電流  $I_a$  は、第 2 の電流  $I_b$  より大きくなり、( $I_a - I_b$ ) の大きさを有する  $I_{sub}$  が AD 变換回路 903 より流れることとなる。AD 变換回路 903 より  $I_a$  と  $I_b$  の差分である  $I_{sub}$  が流れることで、単結晶シリコンの分光感度特性より赤外光の分光感度特性が減算された値であり、そして視感度に近い可視光領域の分光感度に応じたデジタル信号  $S_{out}$  として照度を得ることができる。20

#### 【0077】

なお、AD 变換回路 903 は、図 12 に示すように、上記実施の形態 1 で説明した第 1 の AD 变換回路 103 及び第 2 の AD 变換回路 106 の構成と同様である。また動作についても、上記実施の形態 1 で説明した第 1 の AD 变換回路 103 及び第 2 の AD 变換回路 106 について説明した箇所と同様である。そのため、光電変換装置 900 は、照度に応じたデジタル信号  $S_{out}$  を出力することができる。30

#### 【0078】

以上説明したように本実施の形態の光電変換装置の構成では、視感度に近い分光感度特性を得ることができると共に、低照度領域での照度の分解能を向上させた光電変換装置を提供することができる。

#### 【0079】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0080】

##### (実施の形態 4)

本実施の形態では、上記実施の形態で説明した光電変換装置に加え、デジタル信号が出力される外部の回路を加えたブロック図の構成について図 13、図 14 を用いて説明する。

#### 【0081】

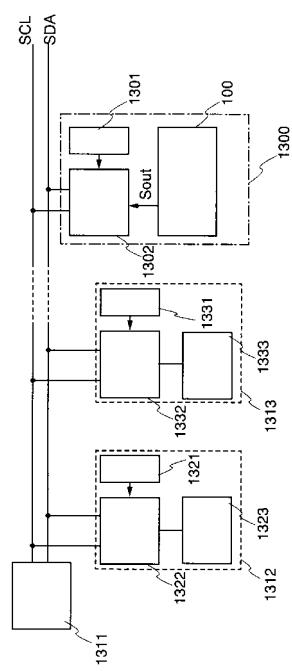

図 13 に示すデジタル出力型のフォト IC 1300 は、図 1 で示した光電変換装置 100、アドレスメモリ 1301、I<sub>2</sub>C (Inter Integrated circuit) インターフェース回路 1302 を有する。また、I<sub>2</sub>C インターフェース回路 1302 は、他の装置とのデータ通信のためのシリアルデータライン (S<sub>DA</sub>) と、他の装置との間のデータ通信を制御及び同期化するためのシリアルクロックライン (S<sub>CL</sub>) と、からなる I<sub>2</sub>C バスによって外部装置と電気的に接続されている。S<sub>DA</sub> と S<sub>CL</sub> からなる4050

I<sub>2</sub>Cバスは、各装置に設けられるアドレスメモリに割り振られた固有のアドレスによって、マイクロコンピュータ1311からの制御を行うためのバス規格である。なお他の装置が液晶表示装置である場合には、一例として、アドレスメモリ1321、I<sub>2</sub>Cインターフェース回路1322、ロジック部1323を有するディスプレイドライバー1312、アドレスメモリ1331、I<sub>2</sub>Cインターフェース回路1332、ロジック部1333を有するLEDドライバー1313がI<sub>2</sub>Cバスに電気的に接続される構成となる。他の装置がEL素子を具備する表示装置の場合には、バックライトであるLEDの制御を行うLEDドライバーは必ずしも必要ない。

#### 【0082】

なお、上記実施の形態での光電変換装置より得られるデジタル信号は、I<sub>2</sub>Cインターフェース回路1302を介して、LEDドライバー1313等の他の外部装置に送られる。LEDドライバー1313は、フォトIC1300で得られた照度に関するデジタル信号に応じて、表示装置のバックライトであるLEDを制御するための信号を生成し、出力するものである。

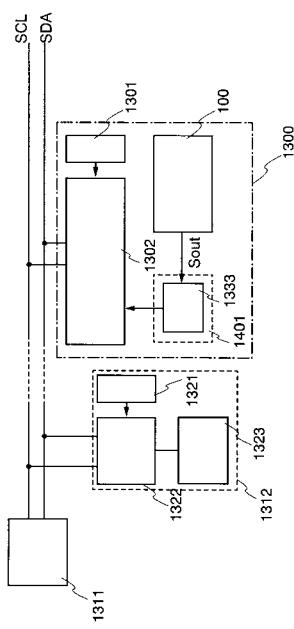

#### 【0083】

また図13に示したデジタル出力型のフォトIC1300について、別の構成を図14に示す。図14で示すフォトIC1300は、光電変換装置100に加え、アドレスメモリ1301、I<sub>2</sub>Cインターフェース回路1302、LEDドライバー1401を有する。また、I<sub>2</sub>Cインターフェース回路1302は、SDAと、SCLと、からなるI<sub>2</sub>Cバスによってディスプレイドライバー1312と電気的に接続されている。図14に示す構成が、図13と異なる点はフォトIC1300の内部にロジック部1333を有するLEDドライバー1401とする点にある。LEDドライバー1401をフォトIC1300の内部に設ける構成とすることにより、光電変換装置100で生成されたデジタル信号を直接LEDドライバー1401で受け取り、I<sub>2</sub>Cインターフェース回路1302より出力することができるため、回路の共通化を図ることができるため、小型化及び高付加価値化を図ることができる。

#### 【0084】

なお図13、図14において、各回路のインターフェースは、一例として、デジタルシリアルインターフェースの一つであるI<sub>2</sub>Cインターフェースを用いる構成について示した。なおI<sub>2</sub>Cバス以外に、ユニバーサルシリアルバス(Universal Serial Serial Bus)、シリアル周辺インターフェース(Serial Peripheral Interface)等のバス規格を用いることが可能である。

#### 【0085】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0086】

(実施の形態5)

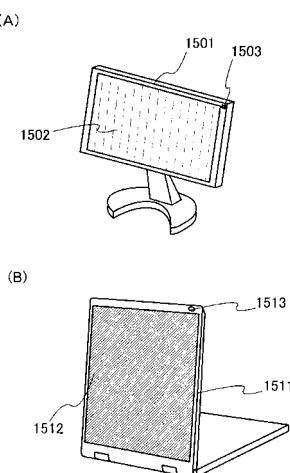

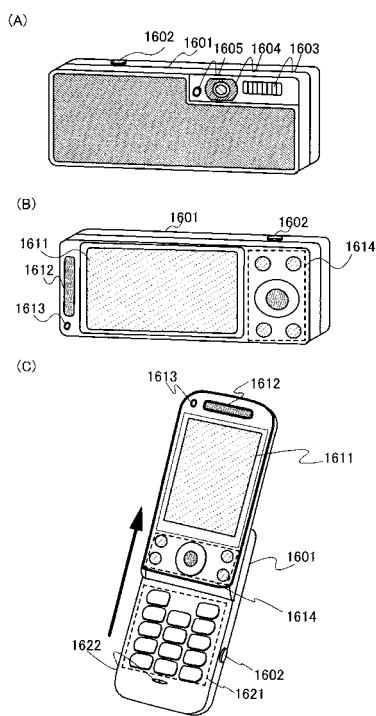

本発明の光電変換装置は、視感度に近い分光感度特性を得ることができると共に、低照度領域での照度の分解能を向上させることができるといった特徴を有している。よって、本発明の光電変換装置を具備する電子機器は、光電変換装置をその構成要素に追加することに伴って、視感度に近い分光感度特性で照度を得ることができ、暗所での光の検出を行うことができる。本発明の光電変換装置は、表示装置、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、本発明の光電変換装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機または電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、などが挙げられる。これら電子機器の具体例を図15、図16に示す。

#### 【0087】

10

20

30

40

50

図15( A )は表示装置であり、筐体1501、表示部1502、センサ部1503等を有する。本発明の光電変換装置は、センサ部1503に用いることができる。センサ部1503は外光の強度を検知する。表示装置は、検知した外光の強度に合わせて、表示部1502の輝度のコントロールを行うことができる。外光の強度に合わせて表示部1502の輝度のコントロールすることで、表示装置の消費電力を抑えることができる。なお、表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

#### 【0088】

図15( B )は、デジタルフォトフレームであり、筐体1511、表示部1512、センサ部1513等を有する。表示部1512は、デジタルカメラ等などで撮影した画像を表示させることで、通常の写真立てと同様に機能させることができる。本発明の光電変換装置は、センサ部1513に用いることができる。センサ部1513は外光の強度を検知する。表示装置は、検知した外光の強度に合わせて、表示部1512の輝度のコントロールを行うことができる。外光の強度に合わせて表示部1512の輝度のコントロールすることで、表示部での視認性の向上を図ることができる。

10

#### 【0089】

図16( A )乃至( C )は撮像機能付き(以下、デジタルカメラ機能ともいう)の携帯電話の例を示す図である。図16( A )はデジタルカメラ機能をさせる場合の前面方向から見た斜視図である。また図16( B )は、デジタルカメラ機能をせる際の背面方向から見た斜視図である。また図16( C )は携帯電話機能をせる場合の斜視図である。図16( A )においてデジタルカメラ機能付き携帯電話には、筐体1601、シャッターボタン1602、フラッシュ1603、レンズ1604、センサ1605が備えられている。また図16( B )には、筐体1601、シャッターボタン1602、表示部1611、音声出力部1612、センサ1613、操作ボタン部1614が備えられている。また図16( C )には、筐体1601、シャッターボタン1602、表示部1611、音声出力部1612、センサ1613、操作ボタン部1614、操作ボタン1621、音声入力部1622が備えられている。

20

#### 【0090】

図16( A )乃至( C )で示すシャッターボタン1602は、押下されるとシャッターが開き、レンズ1604が有する撮像素子により画像を撮ることができる。なおレンズ1604の撮像素子としては、CCD(Charge Coupled Device)、CMOSセンサ等を用いればよい。

30

#### 【0091】

図16( A )で示すフラッシュ1603は、センサ1605で検知する照度の値に応じて、シャッターボタンが押下されてシャッターが開くと同時に補助光を照射する。フラッシュ1603の補助光により、被写体周辺が低照度下にあっても画像を撮ることができる。本発明の光電変換装置は、センサ1605に用いることができる。センサ1605としてデジタル信号を出力する光電変換装置を用いることにより、レンズ1604及びフラッシュ1603とデジタル信号での信号の入出力を行うことができる。なお、フラッシュ1603としては、LEDフラッシュ、またはキセノンフラッシュを用いることができる。キセノンフラッシュを用いることで、補助光の発光スペクトルを太陽光に近づけることができるため、より自然な画像を撮ることができる。

40

#### 【0092】

図16( B )、( C )で示す表示部1611は、レンズ1604の撮像素子に映る画像を見るためのものである。センサ1605及び/またはセンサ1613は検知した照度に合わせて、輝度のコントロールを行うことができる。照度に応じて表示部1611の輝度のコントロールすることで、携帯電話の消費電力を抑え、視認性の向上を図ることができる。また操作ボタン部1614は、デジタルカメラ機能を操作することが可能なボタンであり、各ボタンにより複数の機能を操作することができる。表示部1611はタッチセンサパネルとすることで、複数の機能の操作と画像を見ることとを一体に行うことができ、表

50

示部の大型化を図ることができる。なお図16( B )では、携帯電話機能で用いる音声出力部1612を示している。

#### 【0093】

図16( C )に、携帯電話で通話するときの形態を示す。図16( C )に示すように、図16( A )、( B )で示した形態での筐体1601を伸長させることで、携帯電話機能を使用する。音声出力部1612及び音声入力部1622は、通話機能をさせるためのものである。また操作ボタン部1614及び操作ボタン1621は、電話番号等を入力するためボタンである。

#### 【0094】

なお本実施の形態で示すデジタルカメラ機能付き携帯電話では、携帯電話機能を使用する際、筐体を伸長させる構成としたが、折りたたんで使用するクラムシェル型の携帯電話であっても本発明の適用を行うことができる。10

#### 【0095】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【図面の簡単な説明】

#### 【0096】

【図1】実施の形態1を説明するための図。

【図2】実施の形態1を説明するための図。

【図3】実施の形態1を説明するための図。

20

【図4】実施の形態1を説明するための図。

【図5】実施の形態1を説明するための図。

【図6】実施の形態1を説明するための図。

【図7】実施の形態1を説明するための図。

【図8】実施の形態1を説明するための図。

【図9】実施の形態2を説明するための図。

【図10】実施の形態3を説明するための図。

【図11】実施の形態3を説明するための図。

【図12】実施の形態3を説明するための図。

【図13】実施の形態4を説明するための図。

30

【図14】実施の形態4を説明するための図。

【図15】実施の形態5を説明するための図。

【図16】実施の形態5を説明するための図。

【図17】実施の形態1を説明するための図。

【図18】実施の形態2を説明するための図。

【図19】実施の形態3を説明するための図。

#### 【符号の説明】

#### 【0097】

100 光電変換装置

101 第1の光電変換素子

40

102 第1の增幅回路

103 第1のA/D変換回路

104 第2の光電変換素子

105 第2の増幅回路

106 第2のA/D変換回路

107 減算回路

108 矢印

109 赤外光透過フィルタ

200 増幅回路

201 nチャネル型トランジスタ

50

|         |                  |    |

|---------|------------------|----|

| 2 0 2   | n チャネル型トランジスタ    |    |

| 2 5 0   | 增幅回路             |    |

| 7 0 1   | ステップ             |    |

| 7 0 2   | ステップ             |    |

| 7 0 3   | ステップ             |    |

| 7 0 4   | ステップ             |    |

| 7 0 5   | ステップ             |    |

| 7 0 6   | ステップ             |    |

| 7 0 7   | ステップ             |    |

| 9 0 0   | 光電変換装置           | 10 |

| 9 0 1   | 減算回路             |    |

| 9 0 2   | 電圧電流変換回路         |    |

| 9 0 3   | A D 変換回路         |    |

| 1 0 0 0 | 光電変換装置           |    |

| 1 0 0 1 | カレントミラー回路        |    |

| 1 1 0 1 | p チャネル型トランジスタ    |    |

| 1 1 0 2 | p チャネル型トランジスタ    |    |

| 1 3 0 0 | フォト I C          |    |

| 1 3 0 1 | アドレスメモリ          |    |

| 1 3 0 2 | I 2 C インターフェース回路 | 20 |

| 1 3 1 1 | マイクロコンピュータ       |    |

| 1 3 1 2 | ディスプレイドライバー      |    |

| 1 3 1 3 | L E D ドライバー      |    |

| 1 3 2 1 | アドレスメモリ          |    |

| 1 3 2 2 | I 2 C インターフェース回路 |    |

| 1 3 2 3 | ロジック部            |    |

| 1 3 3 1 | アドレスメモリ          |    |

| 1 3 3 2 | I 2 C インターフェース回路 |    |

| 1 3 3 3 | ロジック部            |    |

| 1 4 0 1 | L E D ドライバー      | 30 |

| 1 5 0 1 | 筐体               |    |

| 1 5 0 2 | 表示部              |    |

| 1 5 0 3 | センサ部             |    |

| 1 5 1 1 | 筐体               |    |

| 1 5 1 2 | 表示部              |    |

| 1 5 1 3 | センサ部             |    |

| 1 6 0 1 | 筐体               |    |

| 1 6 0 2 | シャッター ボタン        |    |

| 1 6 0 3 | フラッシュ            |    |

| 1 6 0 4 | レンズ              | 40 |

| 1 6 0 5 | センサ              |    |

| 1 6 1 1 | 表示部              |    |

| 1 6 1 2 | 音声出力部            |    |

| 1 6 1 3 | センサ              |    |

| 1 6 1 4 | 操作ボタン部           |    |

| 1 6 2 1 | 操作ボタン            |    |

| 1 6 2 2 | 音声入力部            |    |

| 3 0 0 A | 回路               |    |

| 3 0 1 A | スイッチ             |    |

| 3 0 2 A | スイッチ             | 50 |

|         |          |

|---------|----------|

| 4 0 1 A | スイッチ     |

| 4 0 1 B | スイッチ     |

| 4 0 2 A | スイッチ     |

| 4 0 2 B | スイッチ     |

| 4 0 3 A | 容量素子     |

| 4 0 3 B | 容量素子     |

| 4 0 4 A | コンパレータ   |

| 4 0 4 B | コンパレータ   |

| 4 0 5 A | ラッチ回路    |

| 4 0 5 B | ラッチ回路    |

| 4 0 6 A | カウンター回路  |

| 4 0 6 B | カウンター回路  |

| 4 0 7 A | クロック生成回路 |

| 4 0 7 B | クロック生成回路 |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開2006-332226(JP,A)

特開昭63-263428(JP,A)

特開平02-159527(JP,A)

特開平06-273230(JP,A)

特開平11-264761(JP,A)

特開平06-313840(JP,A)

特開2002-286504(JP,A)

特開平04-357423(JP,A)

特開平01-163632(JP,A)

特開2004-325409(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 31/00 - 31/0392, 31/08 - 31/119,

27/14

G01J 1/00 - 11/00