(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4149441号

(P4149441)

(45) 発行日 平成20年9月10日(2008.9.10)

(24) 登録日 平成20年7月4日(2008.7.4)

(51) Int.Cl.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>H02H</b> | <b>9/02</b> | <b>(2006.01)</b> | H02H | 9/02 | E    |

| <b>H02H</b> | <b>7/20</b> | <b>(2006.01)</b> | H02H | 7/20 | A    |

| <b>H02J</b> | <b>1/00</b> | <b>(2006.01)</b> | H02J | 1/00 | 309R |

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2004-551488 (P2004-551488)

(86) (22) 出願日 平成15年10月1日 (2003.10.1)

(65) 公表番号 特表2006-508628 (P2006-508628A)

(43) 公表日 平成18年3月9日 (2006.3.9)

(86) 國際出願番号 PCT/US2003/030918

(87) 國際公開番号 WO2004/045038

(87) 國際公開日 平成16年5月27日 (2004.5.27)

審査請求日 平成18年7月13日 (2006.7.13)

(31) 優先権主張番号 10/291,015

(32) 優先日 平成14年11月12日 (2002.11.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 300057230

セミコンダクター・コンポーネンツ・イン

ダストリーズ・リミテッド・ライアビリテ

ィ・カンパニー

アメリカ合衆国 アリゾナ州 85008

フェニックス イースト・マクドウェル

・ロード5005

(74) 代理人 100091915

弁理士 本城 雅則

(74) 代理人 100099106

弁理士 本城 吉子

(72) 発明者 ボール, アラン, アール

アメリカ合衆国 アリゾナ州 85296

ギルバート イースト・ホースシュー・

アベニュー530

最終頁に続く

(54) 【発明の名称】集積された突入電流リミッタ回路および方法

## (57) 【特許請求の範囲】

## 【請求項1】

センス電流から生成された制御信号に応答して動作するミラー・トランジスタであって、供給電圧に結合された第1ソース、前記供給電圧の負荷電流を出力ノードヘルートするための共通ドレイン、および、前記負荷電流をサンプリングして前記センス電流を生成するための第2ソースを有するミラー・トランジスタと、

第1フォールト条件に応答して前記ミラー・トランジスタを不能にするフォールト保護回路であって、前記フォールト保護回路は、フォールト・スレショルド信号を生成するために形成され、かつ、前記突入電流リミッタ回路の外部のコンポーネントを用いて、前記フォールト・スレショルド信号の値を修正するために前記フォールト・スレショルド信号を突入電流リミッタ回路の第1外部リードに結合するために形成されるフォールト保護回路と、

前記突入電流リミッタ回路の外部で発生するフォールト条件を表わすフォールト信号を受信するために前記第1外部リードに結合され、前記フォールト信号を使用して前記ミラー・トランジスタを不能にするためのフォールト通信回路と、

から構成されることを特徴とする突入電流リミッタ回路。

## 【請求項2】

前記フォールト保護回路を形成するための第1表面、および、前記ミラー・トランジスタの前記共通ドレインを形成するための第2表面、を有する半導体基板と、

検出回路であって、

前記フォールト保護回路、および、

第2フォールト条件を前記ミラー・トランジスタの温度としてモニタするために前記半導体基板上に形成された熱センサ、

を含む検出回路と、をさらに含み、

前記半導体基板の前記温度が予め決められた温度スレショルドよりも高いとき、前記熱センサがシャットダウン信号を生成する、

ことを特徴とする請求項1記載の前記突入電流リミッタ回路。

## 【請求項3】

前記供給電圧をモニタするために前記突入電流リミッタ回路の第2外部リードに結合された不足電圧検出器をさらに含むことを特徴とする請求項1記載の突入電流リミッタ回路。

。

## 【請求項4】

制御信号に応答して動作するための共通ゲートを有し、かつ、供給電圧に結合された電力ソース、負荷電流を供給するための共通ドレイン、および、前記負荷電流をサンプリングしてセンス電流を生成するためのセンシング・ソースを有する第1ミラー・トランジスタと、

第1過電圧スレショルド信号を生成するために形成され、前記供給電圧が第1過電圧スレショルド信号よりも大きいときに前記第1ミラー・トランジスタを不能にするために結合された第1検出回路であって、前記第1検出回路は、前記突入電流リミッタの第1外部リードに結合された入力を有し、かつ、前記第1過電圧スレショルド信号を前記第1外部リードに結合し前記第1過電圧スレショルド信号の値を外部から修正するために形成される、第1検出回路と、

フォールト条件に応答して前記第1ミラー・トランジスタを不能にし、かつ、シャットダウン信号を生成するために前記第1外部リードに結合された第1フォールト保護回路と、

、

から構成されることを特徴とする突入電流リミッタ。

## 【請求項5】

前記第1検出回路および前記第1フォールト保護回路を形成するための第1表面、および、前記第1ミラー・トランジスタの前記共通ドレインを形成するための第2表面を有する第1半導体基板と、

第2半導体基板と、

前記第2半導体基板の第1表面上に形成され、かつ、前記第1ミラー・トランジスタの前記電力ソースおよび前記センシング・ソースにそれぞれ結合された電力ソースおよびセンシング・ソース、および、前記第2半導体基板の第2表面上に形成された共通ドレインを有する第2ミラー・トランジスタと、

前記供給電圧が第2過電圧スレショルド信号よりも大きいときに前記第2ミラー・トランジスタを不能にするために前記第2半導体基板の前記第1表面上に形成され、かつ、前記第2過電圧スレショルド信号の値を外部から修正するために前記突入電流リミッタ回路の第3外部リードに結合された入力を有する第2検出回路と、

前記シャットダウン信号で前記第2ミラー・トランジスタを不能にするために前記第1外部リードに結合された入力を有する第2フォールト保護回路と、

をさらに含むことを特徴とする請求項4記載の突入電流リミッタ。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、一般に半導体デバイスに関し、より詳しくは、電力供給バス上の電流サーチを制限するための高電流半導体デバイスに関する。

## 【背景技術】

## 【0002】

多くのエレクトロニクス・システムは、システム全体をパワーダウンすることなくユー

10

20

30

40

50

ザが回路カードの挿入および取り出しを行えるように設計されており、それは一般に「ホット・スワップ」と称される。電力が、電力供給バス上の多数のカードに分配されるシステムでは、それぞれの回路カードは、バス上のノイズを減少するために典型的には大きなフィルタ・コンデンサを含むので、ホット・スワップによって、もし制限されなければ何百アンペアにも達するような突入電流スパイクが生成される可能性があり、そのためにシステムに挿入される回路カード、そのコネクタ、または他の回路カードが破損されるおそれがある。さらに、突入電流スパイクは、データ損失、あるいはホット・スワップされているカードまたは他のシステム・カード上での他のシステム誤動作を生成することがある。突入電流の有害な影響を制御するために、ホット・スワップ可能なカードは、典型的には供給バスからの負荷電流をルートするためのパワーMOSFETスイッチを含む突入電流制限回路で形成される。

## 【0003】

個別の電流レベルで動作する回路カードは、それらの突入電流制限機能を実行するために、独自の設計がされ、異なるコンポーネントが用いられる。独自の設計によって回路カードの製造原価が増加し、また、異なるコンポーネントを在庫しておく必要性があることから、それらのカードおよびコンポーネントの製作者は、大きな「規模の経済性」を得ることが難しい。

## 【0004】

従って、「規模の経済性」を達成することによって製造原価を減少させるために、異なる電流レベルで動作するカードをサポートすることができる突入電流リミッタに対する要 求がある。

## 【発明の開示】

## 【0005】

図面中、同一の参照番号を有する要素は同様の機能を有する。

## 【0006】

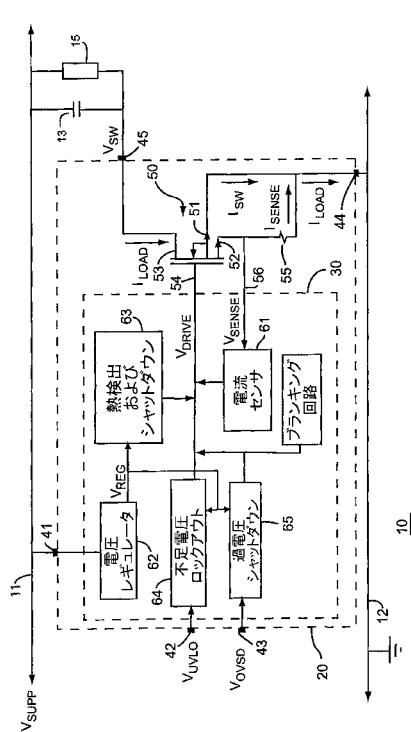

図1は、電力供給電圧( $V_{SUPP} = 48.0$ ボルト)と接地ノード12との間で動作する分配型電源バス11にプラグおよび/またはアンプラグするためのホット・スワップ可能な回路カード10の単純化した概要図である。電源バス11および接地ノード12は、電子システムの他のコンポーネント(図示せず)へ同時に電力を供給していくよい。

## 【0007】

大きなフィルタ・コンデンサ13は、電源バス11上のノイズ・スパイクを平坦化して、安定したバイアスを提供する。回路カード10の機能を実行する回路は、負荷15として示され、電源バス11から突入電流リミッタ回路20を経由して負荷電流 $I_{LOAD}$ を流す。ある実施例において、負荷15は、コンデンサ13および負荷15を経由して、ピーク値として負荷電流=10.0アンペアを流す電圧レギュレータを含む。 $I_{LOAD}$ の典型的な平均値は、約4アンペアである。ある実施例において、コンデンサ13は、約1000マイクロファラドの値を有する。回路カードがホット・スワップされるとき、電流 $I_{LOAD}$ はコンデンサ13内へ流れ、それを $V_{SUPP}$ の値にチャージする。突入電流リミッタ回路20は、さもなければ100アンペア以上に達したであろう $I_{LOAD}$ のピーク値を制限して指定された値にする。ある実施例において、 $I_{LOAD}$ は約10アンペアまで制限される。

## 【0008】

突入電流リミッタ20は検出回路30を含み、それによってミラー・パワー・トランジスタ50が制御され、負荷電流 $I_{LOAD}$ がコンデンサ13および負荷15ヘルートされる。ある実施例において、突入電流リミッタ20は、5個の外部パッケージ・リード41-45を有する集積回路として半導体基板上に形成される。

## 【0009】

ミラー・トランジスタ50は、パワー・ソース51、センシング・ソース52、共通ドレイン53、および共通ゲート54を有する縦型パワーMOSFETトランジスタとして形成される。パワー・ソース51、センシング・ソース52は、 $I_{LOAD}$ の比例成分 $I$

10

20

30

40

50

$V_{SW}$  および  $I_{SENSE}$  をそれぞれ導くために、ミラーされ、あるいは比例する。ある実施例において、トランジスタ 50 は、約 1 ボルトのゲート対ソース導通スレショルドを有する。ある実施例において、パワー・ソース 51 およびセンシング・ソース 52 の有効ササイズは 1000 : 1 の比率で比例するので、電流のピーク値は、 $I_{LOAD} = 10.0$  アンペアのとき、およそ  $I_{SW} = 9.990$  アンペアおよび  $I_{SENSE} = 10.0$  ミリアンペアである。

#### 【0010】

集積センス・レジスタ 55 は、センシング・ソース 52 と直列に結合され、ノード 56 で電流の  $I_{SENSE}$  を検出することによってセンス電圧  $V_{SENSE}$  を生成する。ある実施例において、レジスタ 55 は、約 10 オームの抵抗を有するので、 $I_{SENSE} = 10.0$  ミリアンペアのとき、 $V_{SENSE}$  は約 100 ミリボルトの値および約 1 ミリワットの対応する電力消散を有する。

10

#### 【0011】

検出回路 30 は、電流センサ 61、電圧レギュレータ 62、および、熱フォールト・シャットダウン回路 63、低電圧ロックアウト回路 64、過電圧シャットダウン回路 65、およびブランкиング回路 66 のような複数のフォールト検出および予防回路を含む。

#### 【0012】

電圧レギュレータ 62 は、接地リード 41 と給電リード 44 との間に結合された標準分路レギュレータとして形成され、検出回路 30 にバイアスするための内部供給電圧  $V_{REG}$  を提供する。

20

#### 【0013】

電流センサ 61 は、フィードバック信号として  $V_{SENSE}$  を受信するエラー増幅器によって  $I_{LOAD}$  を間接的に検出し、かつ、代表駆動制御信号  $V_{DRIVE}$  をゲート 54 に生成する。実際には、電流センサ 61 は、センシング・ソース 52 を通る  $I_{LOAD}$  の縮尺部分を  $I_{SENSE}$  としてルートすることにより動作し、負荷電流  $I_{LOAD}$  の大きさを予め決められた最大値、例えば 10 アンペア、に制限するために  $V_{DRIVE}$  を調整する。

#### 【0014】

突入電流リミッタ 20 の動作は以下のように進行する。回路カード 10 のホット・スワップ挿入中に、コンデンサ 13 は実質的にディスチャージされ、ドライン 53 上で出力電圧  $V_{SW}$  がほぼ  $V_{SUPP}$  のレベルに生成される。コンデンサ 13 は、突入電流リミッタ 20 に低インピーダンス負荷を示し、突入電流リミッタ 20 は、これに応答して  $I_{LOAD}$  の予め決められた最大値、例えば 10 アンペア、を供給してコンデンサ 13 をチャージする。実際には、コンデンサ 13 が  $V_{SUPP}$  にチャージされるまでトランジスタ 50 は定電流源として動作し、その時点では、 $V_{DRIVE}$  が  $V_{REG}$  のレベルまで引き上げられ、ミラー・トランジスタ 50 は完全に導通状態である。電流制限機能のために、供給電圧  $V_{SUPP}$  の過度の負荷が回避されるので、出力電圧  $V_{SW}$  は保護信号と称される。

30

#### 【0015】

負荷電流  $I_{LOAD}$  は、直接に検出されるのではなく、低値のセンス電流  $I_{SENSE}$  でサンプリングされるので、センス・レジスタ 55 を通して小量の電力のみが消費され、それによって高性能を提供する。さらに、レジスタ 55 は、突入電流リミッタ 20 の他のコンポーネントと同じダイに容易に集積されるので、外部コンポーネントの数が減少し、それによって回路カード 10 の全費用が低減する。

40

#### 【0016】

供給電圧  $V_{SUPP}$  がその指定された領域未満であるとき、低電圧フォールト条件が生じる。このフォールト条件は、低電圧ロックアウト回路 64 によって検出および保護されるが、それは、スレショルド比較器を含み、これによって供給電圧  $V_{SUPP}$  の大きさが検出され、 $V_{SUPP}$  が低電圧フォールトのスレショルドレベルを越えて上昇するまで、トランジスタ 50 がオフ状態に維持される。低電圧スレショルドレベルは、リード 42 に結合された内部分圧器でセットされ、 $V_{SUPP}$  からの分割電圧  $V_{UVLO}$  を提供するが

50

、もし必要であれば、1またはそれ以上の外部レジスタで調整することができる。デジタル低電圧シャットダウン信号UVLOは、オープン・ドレイン出力ステージを駆動し、低電圧フォールト条件が検出されたときに、ゲート54をほぼ大地電位まで引き下げてトランジスタ50を不能にする。その後、ヒステリシス回路類は、 $V_{SUPP}$ が上位のスレショルドレベルを越えて上昇するまでトランジスタ50をオフ状態に維持し、それによって、急速なサイクリングおよび／または発振を防ぐ。ある実施例において、 $V_{SUPP}$ が48ボルトで動作するところで、低電圧フォールトのスレショルドレベルは約32ボルトの値にセットされる。

#### 【0017】

過電圧フォールト条件は、供給電圧 $V_{SUPP}$ が過電圧フォールトのスレショルドレベルを超過するときに生じる。このフォールト条件は、過電圧シャットダウン回路65によって検出および保護され、低電圧ロックアウト回路64の場合と同様の方法で動作するが、 $V_{SUPP}$ が過電圧フォールトのスレショルドレベルを越えて上昇した場合にスレショルド比較器が検出回路30およびトランジスタ50を不能にする点で異なる。過電圧フォールトのスレショルドレベルは、リード43で $V_{SUPP}$ から分割電圧 $V_{OVS_D}$ を生成する内部分圧器でセットされ、1またはそれ以上の外部レジスタで調整することができる。デジタル・シャットダウン信号OVS\_Dは、オープン・ドレイン出力ステージを駆動し、それが、過電圧フォールト条件が検出されるときに、ゲート54をほぼ大地電位まで引き下げてトランジスタ50を不能にする。ヒステリシス回路類は、 $V_{SUPP}$ が下位のスレショルドレベルを下回るまでトランジスタ50をオフ状態に維持し、急速なサイクリングおよび／または発振を防止する。ある実施例において、 $V_{SUPP}$ が48ボルトで動作するところで、過電圧フォールトのスレショルドレベルは約95ボルトにセットされ、また、下位のスレショルドレベルは約90ボルトの値にセットされる。

#### 【0018】

温度過昇または熱フォールト条件は、検出回路30およびミラー・トランジスタ50と同じ半導体基板上に形成された温度センサを含む熱フォールト・シャットダウン回路63によって検出され保護される。温度センサ回路類は、好ましくは、電源51に隣接して配置されるか、あるいはトランジスタ50のレイアウト内に埋め込まれる、すなわち、突入電流リミッタ20の最も熱い部分の温度を検出するために、最も熱が生成される場所の付近である。熱フォールト条件が検出されたとき、デジタル熱フォールト・シャットダウン信号TEM\_Pが生成されてオープン・ドレイン出力ステージを駆動し、ゲート54をほぼ大地電位まで引き下げてトランジスタ50を不能にする。温度ヒステリシス回路類は、温度が下位のスレショルド温度以下に下がるまでミラー・トランジスタ50の切断状態を確保する。ある実施例において、上位のスレショルド温度は約摂氏180度である。また、下位のスレショルド温度は約摂氏170度である。

#### 【0019】

ブランкиング回路66は、ホット・スワップ・カード挿入後の遅延時間中、突入電流リミッタ20およびトランジスタ50をオフ状態に維持する時定数をセットするためのレジスタ・コンデンサ・ネットワークを含む。このスタートアップ遅延は、回路カード10が突入電流リミッタ20を通って電力を受け取る前に、内部ノードを安定させておくことにより、スタートアップ誤動作を回避する。出力は、オープン・ドレイン配置を有し、スタートアップ遅延中にゲート54を大地電位にスイッチする。ある実施例において、遅延時間は約2マイクロ秒である。

#### 【0020】

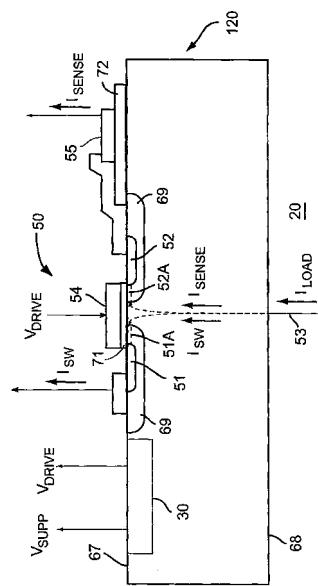

図2は、トランジスタ50、レジスタ55および検出回路30を含む集積回路として半導体基板120上に形成された、突入電流リミッタ20の単純化した断面図である。

#### 【0021】

トランジスタ50は、小さなダイ・エリアを達成するために、縦型装置として実装される。従って、ソース51、52は基板120の上部表面67上のp型ウェル領域内でn型にドープされた領域として形成される。共通ゲート54は、下側に横たわるパワー・チャ

10

20

30

40

50

ネル 5 1 A およびセンス・チャネル 5 1 B の導通を制御するためにゲート酸化層 7 1 上に形成されるが、これらのチャネルは、大地電位で動作し、かつ、図 2 の図外で相互に結合されたウェル領域 6 9 内に、上部表面 6 7 に沿って存在する。ソース 5 1 , 5 2 は、図では同様のサイズを有するように示されるが、ソース 5 2 は、典型的には、ソース 5 1 よりはるかに小さい有効サイズで作られることに注意されたい。ドレイン 5 3 は、基板 1 2 0 の第 2 表面 6 8 上に形成され、その結果、電流  $I_{S_W}$  および  $I_{S_E N S_E}$  は、図示のように、表面 6 7 からチャネル 5 1 A , 5 2 A をそれぞれ通り、基板 1 2 0 を通って、表面 6 8 でドレイン 5 3 へ流れる。縦型構造のトランジスタ 5 0 は、低いオン抵抗および小さなダイサイズを提供し、その結果、高機能性と低製作コストを実現できる。

## 【0022】

10

レジスタ 5 5 は、表面 6 7 上に形成される。ある実施例において、レジスタ 5 5 は、図示のように、誘電層 7 2 上にポリシリコン層を堆積し、パターン化することにより形成される。

## 【0023】

検出回路 3 0 のコンポーネントもまた表面 6 7 上に形成されるが、レジスタ 5 5 の下側に存在してもしなくてもよい。トランジスタは、1つ以上のウェル領域内に形成されるが、ウェル領域 6 9 とは別個のものでもよい。熱フォールト・シャットダウン回路 6 3 内の温度センサは、高精度で基板 1 2 0 の温度を検出するために、最も高温レベルの熱が生成されるトランジスタ 5 0 にきわめて近接した場所に形成される。

## 【0024】

20

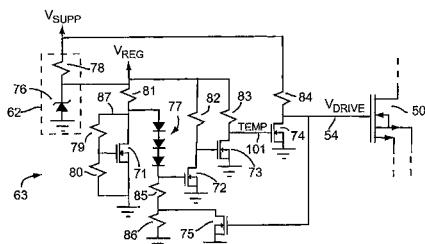

図 3 は電圧レギュレータ 6 2 および熱フォールト・シャットダウン回路 6 3 をさらに詳細に示す概要図であり、トランジスタ 7 1 ~ 7 5 、ツエナダイオード 7 6 、ダイオード列 7 7 、およびレジスタ 7 9 ~ 8 6 を含む。

## 【0025】

電圧レギュレータ 6 2 は、ツエナダイオード 7 6 の両端で内部調整電圧  $V_{R_E G} =$  約 1 2 . 0 ボルトを生成する分路レギュレータとして動作する。ツエナダイオード 7 6 は、電圧の正の温度係数を有する。

## 【0026】

トランジスタ 7 1 およびレジスタ 7 9 , 8 0 は、電圧の負の温度係数を有するノード 8 7 で電圧  $V_{8_7}$  を設定する分路レギュレータとして動作する。ある実施例において、基板 1 2 0 温度が摂氏 2 5 度であるとき、 $V_{8_7} = 2 . 7$  ボルトである。ダイオード列 7 7 の両端で降下した電圧は、温度とともに低下し、その結果、トランジスタ 7 2 のゲート電圧は温度とともに上昇する。

30

## 【0027】

トランジスタ 7 2 , 7 3 は、2段増幅器として機能するためにレジスタ 8 2 , 8 3 と結合し、ノード 1 0 1 上で熱フォールト・シャットダウン信号 T E M P を生成する。レジスタ 8 4 はゲート 5 4 上で高の電位を確定するために使用され、フォールト条件が検出されないときにトランジスタ 5 0 をオンにする。トランジスタ 7 4 は、ゲート 5 4 を駆動するオープン・ドレイン出力ステージとして動作する。基板 1 2 0 の熱フォールト温度スレシヨルドが超過したとき、T E M P は、 $V_{R_E G}$  のレベルとほぼ等しい論理ハイ・レベルで、トランジスタ 7 4 をオンにし、ゲート 5 4 をほぼ大地電位にスイッチしてトランジスタ 5 0 をオフにする。ある実施例において、熱シャットダウン温度は約摂氏 1 8 0 度にセットされる。トランジスタ 7 5 およびレジスタ 8 5 , 8 6 は、約摂氏 1 0 度の温度ヒステリシスを提供して熱発振を防止する。

40

## 【0028】

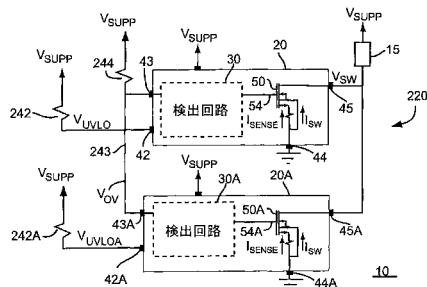

図 4 は、代替の実施例であるホット・スワップ可能な回路カード 1 0 を単純化した概要図であり、突入電流制限ネットワーク 2 2 0 によってより高いレベルの負荷電流  $I_{L_O A_D}$  で保護することを含む。図示のように、突入電流制限ネットワーク 2 2 0 は、突入電流リミッタ 2 0 、および、これに結合され、かつこれと同様に形成された突入電流リミッタ 2 0 A で形成される。ある実施例では、突入電流リミッタ 2 0 , 2 0 A が 1 0 アンペアの

50

負荷電流リミットで形成されている場合、突入電流制限ネットワーク 220 は、負荷電流  $I_{LOAD}$  のリミットを約 20 アンペアに増加させる。記述を単純化するために、突入電流リミッタ 20 A の要素の参照番号は、これらに対応する突入電流リミッタ 20 の同様の要素に「A」を付した番号で示す。

#### 【0029】

図示のように、上位の電流リミットは、共に準並列配列で、ミラー・トランジスタ 50, 50 A に結合されることにより達成され、それぞれの共通ドレインは、リード 45, 45 A を経由して共に結合され、一方で、それぞれのソースは大地電位に結合される。

#### 【0030】

突入電流リミッタ 20 に関し、低電圧フォールト条件は、上述のようにリード 42 上の分割電圧  $V_{UVL0}$  で表わされる低電圧スレショルドレベルによって保護され検出されるが、もし必要であれば、外部レジスタ 242 によって修正される。同様に、突入電流リミッタ 20 A について、低電圧スレショルドレベルは、リード 42 A 上で提供される分割電圧  $V_{UVLA}$  で表わされ、外部レジスタ 242 A によって修正される。分割電圧  $V_{UVL0}$  および  $V_{UVLA}$  は、典型的には、ほぼ同じ電圧レベルにセットされる。10

#### 【0031】

過電圧フォールト条件は、上述の方法と同様の方法で突入電流リミッタ 20, 20 A によって検出され保護されるが、リード 43, 43 A がノード 243 で共に接続されることにより、内部分圧器が並列に結合されて共通の分割電圧  $V_{0v}$  を提供する点において異なる。上記のように、突入電流リミッタ 20, 20 A が同様の集積回路として形成されるところでは、 $V_{0v}$  は突入電流リミッタ 20 の分割電圧、例えば  $V_{0vsd}$  の値とほぼ同一の値を有する。図 4 に示す実施例では、レジスタ 244 を追加することによって、分割電圧  $V_{0v}$  はその内部電圧分割値から修正される。20

#### 【0032】

発明の機能として、リード 43, 43 A は、突入電流リミッタ 20 から突入電流リミッタ 20 A へ、また、それとは逆方向へフォールト情報の通信を可能にする 2 つの機能を有する。このようなフォールト通信を遂行するために、突入電流リミッタ 20 は、リード 43 に結合されたオープン・ドレイン出力トランジスタで形成される出力ステージを有するフォールト通信回路を含む。通常動作中に、上述のように出力トランジスタはオフになり、過電圧検出が進行する。しかしながら、フォールト条件中に、出力トランジスタはオンになり、オープン・ドレインは、ノード 243 およびリード 43 A と同様に、リード 43 をおよそ大地電位にスイッチする。リード 43 A が大地電位であるとき、突入電流リミッタ 20 A 内のフォールト通信回路は、トランジスタ 50 A をオフにすることによって応答し、それによって、同時保護を提供して負荷電流の過負荷条件を回避する。このような電流の過負荷は、残りの動作装置に流されているすべての電流によって、システムのラッチアップという問題を引き起こすおそれがある。30

#### 【0033】

突入電流リミッタ 20 A は、リード 43 A に接続されたオープン・ドレインで同様に形成された出力トランジスタを有し、したがって、検出されたフォールト条件を同様の方法で突入電流リミッタ 20 に伝送することができる。従って、ネットワーク内のいくつかの突入電流リミッタがフォールト条件を検出したとき、そのフォールトは、ネットワーク内の他の突入電流リミッタの全てに伝送され、その後、それら自身をシャットダウンしてシステムのラッチアップを回避する。このスキームによって、高い信頼性がもたらされるが、それは、外部論理回路によって制御される 1 またはそれ以上の予備の突入電流リミッタを追加することにより、さらに増強することができる。温度過昇フォールト条件のようなフォールト条件が 1 つの突入電流リミッタによって検出された場合には、外部回路類は、フォールト情報を使用して、予備の突入電流リミッタのうちの 1 つを不能にし、フォールト条件を有するものの代わりに動作させることができる。40

#### 【0034】

ネットワーク 220 は、2 つの突入電流リミッタ 20, 20 A を有するものとして図示50

および記述したが、これと互換的に、実質上任意の数の個別の突入電流リミッタを準並列的な類似した手法で接続されてもよく、これによって負荷電流リミットが広範囲の値に拡張される。この技術によって、回路カード製作者は、適切な数の集積された突入電流リミッタを選択することが可能になり、特定の設計のための特定の電流リミットを実行することができる。これによって、多数の装置で熱を放散させることができるので、各装置の操作温度が低下し、それゆえ信頼性が改善される。さらに、製作者は、より大きな「規模な経済性」による利益を達成し、それによって、製作コストがより低減する。さらに、突入電流を制限する機能のための設計サイクルが減少し、さらにサイクル時間およびコストが低減する。

## 【0035】

10

突入電流リミッタ20, 20Aは、個別の半導体パッケージに収容された個別の半導体基板上に個々の集積回路として形成されるものとして示されていることに注意されたい。他の実施例では、突入電流リミッタ20, 20Aは、異なる基板上に形成され、同じパッケージに収容されてもよい。さらに他の実施例では、突入電流リミッタ20, 20Aは、同じ半導体基板上に形成され、単一のパッケージに収容されてもよい。

## 【0036】

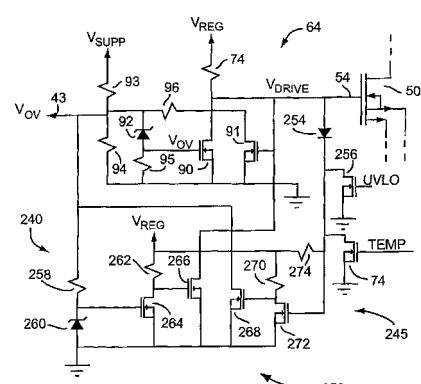

図5は、過電圧シャットダウン回路65およびフォールト通信回路250を含む突入電流リミッタ20の一部を、さらに詳細に示す概要図である。

## 【0037】

20

過電圧シャットダウン回路65は、レジスタ93, 94を含み、それらが、供給電圧 $V_{SUPP}$ を分割してリード43で分割電圧 $V_{OVS_D}$ を提供する分圧器として動作する。ツエナダイオード92のレベルは、 $V_{OVS_D}$ をシフトしてトランジスタ90を制御する。 $V_{SUPP}$ が予め決められた電圧を超過したときに過電圧フォールト条件が生じ、その時点で、トランジスタ90がオンになってゲート54大地電位にスイッチし、トランジスタ50がオフになって突入電流リミッタ20を不能にする。トランジスタ91は、レジスタ94と同時にレジスタ96をスイッチして電圧ヒステリシスを提供し、 $V_{SUPP}$ ノイズによりゲート50上での発振および/または誤ったトリガ回避する。ある実施例において、 $V_{SUPP}$ が約9.5ボルトの過電圧スレショルドに達したときに過電圧フォールト条件が生じ、約5ボルトのヒステリシスを伴う。リード43は、外部レジスタで過電圧スレショルドを調整するための外部接続を提供する。

30

## 【0038】

トランジスタ74は、熱フォールト・シャットダウン回路63のオープン・ドレイン出力トランジスタであり、過昇温度シャットダウン信号TEMPに応答してオンにされる。トランジスタ256は、不足電圧ロックアウト回路64のオープン・ドレイン出力トランジスタであり、不足電圧ロックアウト信号UVLOに応答してトランジスタ50をオンからオフにする。

## 【0039】

上述したように、リード43は過電圧スレショルドを調整し、かつ、フォールト条件に関する情報を通信、すなわち送受信するために使用される。フォールト情報は、受信機240および送信機245を含むフォールト通信回路250によって処理される。

40

## 【0040】

送信機245は、ブロッキング・ダイオード254を通ってゲート54に結合される入力を有し、レジスタ270, 274およびトランジスタ268, 272を含む。 $V_{SUPP} = 4.8 . 0$ ボルトで、かつ、フォールト条件がない場合のアプリケーション内では、分割電圧 $V_{OV}$ は約6ボルトで動作し、また、ゲート54は約 $V_{REG} = 12 . 0$ ボルトの電位で動作する。従って、トランジスタ272はオンであり、トランジスタ268はオフである。トランジスタ268は、リード43上でフォールト情報を提供するオープン・ドレイン出力デバイスとして動作する。内部フォールト条件が検出されると、ゲート54は、例えばトランジスタ74および/またはトランジスタ256によって大地電位に引き上げられ、トランジスタ272がオフになる。トランジスタ268がオンになり、リード4

50

3は大地電位、またはほぼ大地電位にスイッチされる。リード43は、通常、数ボルトの電圧 $V_o.v$ で動作し、また、ほぼ大地電位への移行は、突入電流リミッタ20の動作の通常領域外である。従って、本発明は、例えば大地電位のような領域外電圧レベルを使用して、内部で検出されたフォールト条件に関するフォールト情報を外部へ提供する。

#### 【0041】

受信機240は、他の突入電流リミッタによって外部で生成されたフォールト情報を受信および処理するためにリード43上に入力を有し、レジスタ258, 262、ツエナダイオード260、トランジスタ264, 266を含む。通常動作において、分割電圧 $V_o.v$ は約6ボルトで動作し、したがって、トランジスタ264はオンであり、およびトランジスタ266はオフである。外部のフォールト条件が、他のネットワークされた突入電流リミッタによって検出されるとき、リード43はほぼ大地電位にスイッチされ、それによってトランジスタ264がオフになり、トランジスタ266がオンになる。トランジスタ266は、オープン・ドレイン出力デバイスとして機能するので、ゲート54は大地電位にスイッチされてミラー・トランジスタ50をオフにする。その結果、複数の結合された突入電流リミッタのうちの1つによって検出されたフォールト条件は、ネットワーク内のすべての突入電流リミッタをシャットダウンする。

#### 【0042】

以上を要約すると、本発明は、フォールト・スレショルドを調整し、かつ、フォールト条件に関する情報を転送するためにパッケージ・リードを使用することによって、高い信頼性を有し、しかも低コストの突入電流リミッタ集積回路を提供する。ミラー・トランジスタは、センス電流から生成される制御信号に応答して動作する。ミラー・トランジスタの第1ソースは供給電圧を受け取り、共通ドレインは、供給電圧の負荷電流を出力ノードヘルートし、また、第2ソースは、負荷電流をサンプリングしてセンス電流を生成する。第1フォールト保護回路は、リードに結合されてフォールト・スレショルドを外部から調整し、フォールト条件が生じたときにミラー・トランジスタを不能にする。第2フォールト保護回路は、フォールト条件に応答してミラー・トランジスタを不能にし、第1リードでシャットダウン信号を生成する。

#### 【0043】

この配置によって、マルチプル突入電流リミッタ集積回路は、準パラレル方法でネットワークされ、個々の集積回路のために実質的なものよりもより大きな電流能力の提供を可能にする。フォールト情報は、リードの数を増加させず、個々の突入電流リミッタ集積回路の著しいコスト上昇を防ぎ、ネットワークにつながれた回路内で通信される。従って、低い製作コストおよび高い信頼性が達成される。さらに、システム製作者は、単一タイプの突入電流リミッタの目録を所持することで、上述のように多様な装置を接続することによって広範囲の電流能力をカバーするホット・スワップ・カードまたは他のサブシステムを生成することができる。従って、本発明の技術によって、より大きな規模の経済性が可能となり、それによってさらに製造コストが低減する。

#### 【図面の簡単な説明】

#### 【0044】

- 【図1】ホット・スワップ・カードを含む電子システムの概要図である。

- 【図2】半導体基板上に形成された突入電流リミッタ回路の断面図である。

- 【図3】分路レギュレータ、ならびに、熱検出およびシャットダウン回路を含む、突入電流リミッタの詳細を示す概要図である。

- 【図4】突入電流制限ネットワークによって保護されたホット・スワップ可能な回路カードの概要図である。

- 【図5】過電圧回路およびフォールト通信回路を含む突入電流リミッタ回路の部分概要図である。

【 図 1 】

【 図 2 】

【 図 3 】

【 四 4 】

【 図 5 】

---

フロントページの続き

審査官 廣瀬 文雄

(56)参考文献 特開昭63-318781(JP,A)

特開2000-125463(JP,A)

特開平05-227651(JP,A)

特開平04-100276(JP,A)

特開平03-069159(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02H 9/00-9/08

H02H 7/10-7/20

H02J 1/00-1/16