등록특허 10-2389227

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년04월20일

(11) 등록번호 10-2389227

(24) 등록일자 2022년04월18일

- (51) 국제특허분류(Int. Cl.)

*H01L 23/522* (2006.01) *H01L 23/00* (2006.01)

*H01L 23/488* (2006.01) *H01L 49/02* (2006.01)

- (52) CPC특허분류

*H01L 23/5227* (2013.01)

*H01L 23/488* (2013.01)

- (21) 출원번호 10-2016-7024409

- (22) 출원일자(국제) 2015년02월11일

심사청구일자 2020년01월28일

- (85) 번역문제출일자 2016년09월02일

- (65) 공개번호 10-2016-0120303

- (43) 공개일자 2016년10월17일

- (86) 국제출원번호 PCT/US2015/015450

- (87) 국제공개번호 WO 2015/123321

국제공개일자 2015년08월20일

(30) 우선권주장

14/179,202 2014년02월12일 미국(US)

## (56) 선행기술조사문현

US20130127060 A1\*

JP2011035349 A

KR1020080075790 A

US20070279176 A1

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 13 항

심사관 : 정구원

(54) 발명의 명칭 반도체 디바이스, 반도체 디바이스를 제조하는 방법, 및 컴퓨터 판독가능 저장 매체

**(57) 요 약**

WLP(wafer level package)에 대한 인더터 설계는 다이 상에 솔더 볼들을 디파플레이팅할 필요가 없는데, 왜냐하면 솔더 볼들이 인더터의 부분을 형성하기 때문이다. 인더터 상의 하나의 단자는 다이에 커플링되고, 다른 단자는 다이 상의 단일 솔더 볼에 커플링되고, 인더터를 기계적으로 접촉하는 남아있는 솔더 볼들은 전기적으로 플로팅이 된다. 결과적인 디바이스는 더 양호한 인더턴스, 직류(DC) 저항, BLR(board-level reliability) 및 품질 인자(Q)를 갖는다.

**대 표 도**

(52) CPC특허분류

*H01L 24/02* (2022.01)

*H01L 24/13* (2013.01)

*H01L 24/16* (2013.01)

*H01L 24/81* (2013.01)

*H01L 28/10* (2013.01)

*H01L 2224/0401* (2013.01)

*H01L 2924/30107* (2013.01)

(72) 발명자

**장, 시아오난**

미국 92121-1714 캘리포니아 샌 디에고 모어하우스

드라이브 5775

**레인, 리안, 데이비드**

미국 92121-1714 캘리포니아 샌 디에고 모어하우스

드라이브 5775

---

**하지크리스토스, 아리스토텔레**

미국 92121-1714 캘리포니아 샌 디에고 모어하우스

드라이브 5775

## 명세서

### 청구범위

#### 청구항 1

반도체 패키지로서,

상기 패키지는:

복수의 상호접속부들(104a-104z)로 패플레이팅된(populated) 다이(die)(102); 및

상기 다이에 배치된 인더터(202)를 포함하고,

상기 인더터는 상기 복수의 상호접속부들 중 제 1 상호접속부(104l) 상에, 그리고 상기 복수의 상호접속부들 중 남아있는 상호접속부들(104k, 104p, 104q)의 세트 상에 배치되고, 상기 인더터는:

상기 다이에 전기적으로 그리고 기계적으로 커플링된 제 1 단자;

상기 제 1 상호접속부가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 제 1 상호접속부(104l)를 통해 상기 다이에 전기적으로 그리고 기계적으로 커플링된 제 2 단자; 및

상기 남아있는 상호접속부들의 세트가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 전기적으로 커플링되지는 않지만 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 기계적으로 커플링된 상기 인더터의 남아있는 부분

을 포함하고,

상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트는 전기적으로 플로팅(floating)하는, 반도체 패키지.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 상호접속부(104l)는 UBM(under bump metallization) 층(314)을 통해 상기 다이에 전기적으로 커플링되는, 반도체 패키지.

#### 청구항 3

제 1 항에 있어서,

상기 반도체 패키지는 WLP(wafer level package), FCBGA(flip-chip ball grid array) 패키지, 또는 FCCSP(flip-chip chip-scale package)인, 반도체 패키지.

#### 청구항 4

제 1 항에 있어서,

상기 인더터는 상기 다이 상의 단일 층에 배치되는, 반도체 패키지.

#### 청구항 5

제 1 항에 있어서,

상기 인더터는 2-차원인, 반도체 패키지.

#### 청구항 6

반도체 패키지를 제조하는 방법으로서,

복수의 상호접속부들(104a-104z)로 패플레이팅된 다이(102)를 제공하는 단계; 및

상기 다이에 인더터(202)를 배치하는 단계를 포함하고,

상기 인덕터는 상기 복수의 상호접속부들 중 제 1 상호접속부(104l) 상에, 그리고 상기 복수의 상호접속부들 중 남아있는 상호접속부들(104k, 104p, 104q)의 세트 상에 배치되고, 상기 다이에 상기 인덕터를 배치하는 단계는: 상기 인덕터의 제 1 단자를 형성하고 그리고 상기 다이에 상기 제 1 단자를 전기적으로 그리고 기계적으로 커플링하는 단계;

상기 제 1 상호접속부가 상기 인덕터에 대한 기계적 지지를 제공하도록, 상기 인덕터의 제 2 단자를 형성하고 그리고 상기 제 1 상호접속부(104l)를 통해 상기 다이에 상기 제 2 단자를 전기적으로 그리고 기계적으로 커플링하는 단계; 및

상기 남아있는 상호접속부들의 세트가 상기 인덕터에 대한 기계적 지지를 제공하도록, 상기 인덕터의 남아있는 부분을 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 전기적으로 커플링하지 않지만 상기 인덕터의 남아있는 부분을 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 기계적으로 커플링하여 상기 인덕터의 남아있는 부분을 형성하는 단계

를 포함하고,

상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트는 전기적으로 플로팅하는, 반도체 패키지를 제조하는 방법.

#### 청구항 7

제 6 항에 있어서,

상기 제 1 상호접속부는 UBM(under bump metallization) 층을 통해 상기 다이에 전기적으로 커플링되는, 반도체 패키지를 제조하는 방법.

#### 청구항 8

제 6 항에 있어서,

상기 반도체 패키지는 WLP(wafer level package), FCBGA(flip-chip ball grid array) 패키지, PoP(package-on-package) 패키지, 또는 FCCSP(flip-chip chip-scale package)인, 반도체 패키지를 제조하는 방법.

#### 청구항 9

제 6 항에 있어서,

상기 다이에 배치된 상기 인덕터를 제공하는 단계는 상기 다이 상의 단일 층에 상기 인덕터를 배치하는 단계를 포함하는, 반도체 패키지를 제조하는 방법.

#### 청구항 10

제 6 항에 있어서,

상기 인덕터는 2-차원인, 반도체 패키지를 제조하는 방법.

#### 청구항 11

제 6 항에 있어서,

상기 다이에 금속 층을 제공하는 단계;

상기 금속 층 상에 구리 재분배 층(copper redistribution layer)을 제공하는 단계;

상기 구리 재분배 층 상에 폴리이미드 층(polyimide layer)을 제공하는 단계; 및

상기 폴리이미드 층 상에 부분적으로 배치되고 그리고 상기 구리 재분배 층 상에 부분적으로 배치되는 UBM(under bump metallization) 층을 제공하는 단계를 더 포함하는, 반도체 패키지를 제조하는 방법.

#### 청구항 12

제 1 항에 있어서,

상기 다이 내의 금속 층;

상기 금속 층 상의 구리 재분배 층;

상기 구리 재분배 층 상의 폴리이미드 층; 및

상기 폴리이미드 층 상에 부분적으로 배치되고 그리고 상기 구리 재분배 층 상에 부분적으로 배치되는 UBM(under bump metallization) 층을 더 포함하는, 반도체 패키지.

### 청구항 13

데이터를 포함하는 컴퓨터-판독가능 저장 매체로서,

상기 데이터는, 기계에 의해 액세스될 때, 상기 기계로 하여금, 반도체 패키지를 제조하기 위해 제 6 항 내지 제 11 항 중 어느 한 항의 방법에 따른 동작들을 수행하게 하는, 컴퓨터-판독가능 저장 매체.

### 청구항 14

삭제

### 청구항 15

삭제

### 청구항 16

삭제

### 청구항 17

삭제

### 청구항 18

삭제

### 청구항 19

삭제

### 청구항 20

삭제

### 청구항 21

삭제

### 청구항 22

삭제

### 청구항 23

삭제

## 발명의 설명

### 기술 분야

[0001] 본 개시의 양상들은 일반적으로 반도체 패키징에 관한 것이며, 특히 웨이퍼 레벨 패키징 및 개선된 보드 레벨 신뢰성을 위한 인더터 설계를 구현하는 반도체 패키징에 관한 것이다.

## 배경 기술

- [0002] [0002] 무선 디바이스(예를 들면, 셀룰러 폰 또는 스마트 폰)는 양방향 또는 다중-방향 통신을 지원하기 위해 안테나에 커플링된 수신기 및 송신기를 포함할 수 있다. 송신기는 변조된 신호를 획득하기 위해 음성 및/또는 데이터와 라디오 주파수(RF) 캐리어 신호를 변조하고, 하나 이상의 전력 증폭기들을 사용하여 적절한 출력 전력 레벨을 갖는 출력 RF 신호를 획득하기 위해 변조된 신호를 증폭하고, 출력 RF 신호를 안테나를 통해 기지국으로 송신할 수 있다.

- [0003] [0003] 인더터들은 무선 통신을 위해 사용되는 전력 증폭기들의 필수적인 부분이다. 예를 들면, 인더터들은 초크들 등과 같은 탱크 회로들에서 사용될 수 있다. 인더터들을 디바이스들에 통합할 때, 보드-레벨 신뢰성은 주요 관심사이다. 예를 들면, 보드-레벨 신뢰성에 대한 솔더 보이드들, 온도 사이클링, 기계적 진동, 전기적 이동(electromigration) 등의 가능한 효과들에 관한 관심사들이 상승되고 있다.

- [0004] [0004] 하나의 전통적인 해결책은 SMT(surface mount technology)를 사용하여 칩 상의 하나 이상의 인더터들을 구현하는 것이다. 그러나, 이러한 해결책은 칩 외부에 인더터들이 장착되는 것을 요구한다. 이러한 해결책의 하나의 결과는, 전력 증폭기 내의 초크 인더터가 제거되고 SMT 인더터로 대체되는 것이다. 초크 인더터를 SMT 인더터로 대체하는 것은 전력 증폭기가 감소된 잡음 마진을 갖게 한다.

- [0005] [0005] 다른 전통적인 해결책은 인더터들을 패키지 기판에 임베딩하는 것이다. 이러한 해결책은 물론 도전파제들을 갖는다. 예를 들면, 인더터들을 패키지 기판에 임베딩하는 것은 증가된 패키징 비용들을 발생시킨다. 부가적으로, 인더터들을 패키지 기판에 임베딩하는 것은 인더터들을 위해 필요한 여분의 공간으로 인해 더 큰 패키지를 발생시킨다.

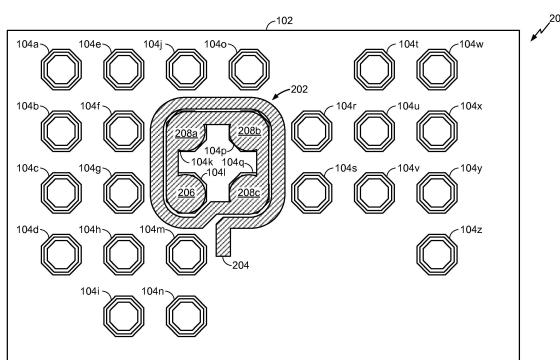

- [0006] [0006] 또 다른 전통적인 해결책은 LGA(land grid array) 기술을 사용하여 적층된 기판 상에서 인더터들을 구현하는 것이다. 이러한 구현은 기판 상의 솔더 볼들(solder balls)을 사용하여 기판에 임베딩된 나선형 인더터를 사용한다. 도 1은 인더터를 구현하기 위한 다이(102)를 형성하는 종래의 기판을 도시한다. 다이(102)는 몇몇의 솔더 볼들(104a-104z)을 포함한다. 인더터가 다이(102) 상에 구현될 때, 솔더 볼들 중 일부는 디파풀레이팅되어야(depopulated) 한다. 예를 들면, 도 1은 솔더 볼들(104k, 104l, 104p 및 104q)이 인더터의 최적의 성능을 위해 디파풀레이팅되어야 한다는 것을 (도트 라인들을 사용하여) 도시한다. 그러나, 솔더 볼들 중 일부가 디파풀레이팅되면, 솔더 볼들에 대한 밀도 요건들이 위반될 수 있다. 예를 들면, 보드 레벨 신뢰성 표준들을 만족시키기 위해, 다이(102)와 인쇄 회로 보드(PCB) 사이에 더 적은 솔더 접속들이 존재할 때, 열적 및/또는 기계적 요건들이 만족되어야 한다.

- [0007] [0007] 대안은 다이(102) 상에 모든 솔더 볼들을 남겨두는 것이다. 솔더 볼들(104k, 104l, 104p 및 104q)이 다이(102)로부터 디파풀레이팅되지 않는다면, 인더터가 다이(102) 상에 통합될 때, 솔더 볼들(104k, 104l, 104p 및 104q)이 다이(102)에 전기적으로 커플링되지 않기 때문에, 그들은 "플로트(float)"된다고 말해진다. 불행하게도, 솔더 볼들을 플로팅하는 것은 높은 와전류들(eddy currents)을 발생시키고, 이것은 인더터의 더 낮은 인더턴스, 인더터에 대한 더 높은 직류(DC) 저항(Rdc), 및 인더터의 낮은 품질 인자(Q)를 발생시킨다.

- [0008] [0008] 또한, L, Rdc 및 Q에 대한 값들은 프로세스 변동들로 인한 변화에 영향을 받는다. 인더턴스에 대한 값들이 변하면, 가령 가변 커패시턴스를 패키지에 포함함으로써 변동들을 보상하기 위한 방식이 필요로 된다. 이러한 부가된 컴포넌트는 물자표(bill of material)가 증가하게 하고, 제조 비용이 증가하게 하고, 패키지의 크기가 증가하게 한다.

- [0009] [0009] 따라서, 예를 들면, 전력 증폭기에서 인더터를 구현하기 위한 개선된 장치들 및 방법들이 필요로 된다.

## 발명의 내용

- [0010] [0010] 본원에 설명된 기술의 예시적인 구현들은 WLP(wafer level package)에 대한 플로팅 솔더 볼들에 대한 인더터 설계에 대한 장치들, 시스템들, 방법들 및 컴퓨터-판독 가능 매체에 관한 것이다. 인더터 설계의 특징들은 인더터 설계가 보드 레벨 신뢰성 표준들과 호환 가능하고 솔더 볼들을 디파풀레이팅하는 것을 수반하지 않고, 인더터의 인더턴스 및 품질 인자(Q)를 여전히 유지하는 것이다.

- [0011] [0011] 하나 이상의 구현들에서, 반도체 디바이스는 제 1 상호접속부 및 복수의 남아있는 상호접속부들로 파풀레이팅된 다이를 포함한다. 반도체 디바이스는 또한 다이에 배치된 인더터를 포함한다. 인더터는 다이에 전기적으로 그리고 기계적으로 커플링된 제 1 단자를 포함한다. 인더터는 또한 제 1 상호접속부를 사용하여 다이에

전기적으로 그리고 기계적으로 커플링된 제 2 단자를 포함한다. 인덕터는 복수의 남아있는 상호접속부들에 기계적으로 커플링되지만 복수의 남아있는 상호접속부들에 전기적으로 커플링되지 않는 남아있는 부분을 포함한다.

[0012] 일부 구현들에서, 제 1 상호접속부는 UBM(under bump metallization) 층을 사용하여 다이에 전기적으로 커플링된 솔더 볼일 수 있고, 반도체 디바이스는 WLP(wafer level package), FCBGA(flip-chip ball grid array) 패키지 및 FCCSP(flip-chip chip-scale package) 중 적어도 하나에 통합되고, 인덕터는 다이 상의 단일 층에 배치되고, 인덕터는 2-차원이다.

[0013] 다른 구현에서, 반도체 디바이스는 제 1 상호접속부 및 복수의 남아있는 상호접속부들로 패플레이팅된 다이를 포함한다. 반도체 디바이스는 또한 PCB(printed circuit board)를 포함한다. 반도체 디바이스는 다이에 배치된 인덕터를 더 포함한다. 인덕터는 다이에 전기적으로 그리고 기계적으로 커플링된 제 1 단자 및 제 1 상호접속부를 사용하여 PCB(printed circuit board)에 전기적으로 그리고 기계적으로 커플링된 제 2 단자를 포함한다. 인덕터의 남아있는 부분은 복수의 남아있는 상호접속부들에 기계적으로 커플링되지만 남아있는 상호접속부들에 전기적으로 커플링되지 않는다.

[0014] 추가의 구현에서, 반도체 디바이스는 제 1 상호접속부 및 복수의 남아있는 상호접속부들로 패플레이팅된 다이를 포함한다. 반도체 디바이스는 또한 PCB(printed circuit board)를 포함한다. 반도체 디바이스는 인쇄 회로 보드에 배치된 인덕터를 더 포함한다. 인덕터는 제 1 상호접속부를 사용하여 인쇄 회로 보드에 전기적으로 그리고 기계적으로 커플링된 제 1 단자를 포함한다. 인덕터는 또한 다이에 전기적으로 그리고 기계적으로 커플링된 제 2 단자를 포함한다. 인덕터는 복수의 남아있는 상호접속부들에 기계적으로 커플링되지만 복수의 남아있는 상호접속부들에 전기적으로 커플링되지 않은 남아있는 부분을 포함한다.

[0015] 또 다른 구현에서, 반도체 디바이스를 제조하는 방법은 제 1 상호접속부 및 복수의 남아있는 상호접속부들로 패플레이팅된 다이를 제공하는 단계를 포함한다. 반도체 디바이스를 제조하는 방법은 또한 인덕터를 다이에 배치하는 단계를 포함한다. 인덕터는 다이에 전기적으로 그리고 기계적으로 커플링된 제 1 단자 및 제 1 상호접속부를 사용하여 다이에 전기적으로 그리고 기계적으로 커플링된 제 2 단자를 포함한다. 인덕터는 또한 복수의 남아있는 상호접속부들에 기계적으로 커플링되지만 복수의 남아있는 상호접속부들에 전기적으로 커플링되지 않은 남아있는 부분을 포함한다.

[0016] 또 다른 구현에서, 반도체 디바이스는 제 1 상호접속부 및 복수의 남아있는 상호접속부들로 패플레이팅된 다이를 제공하기 위한 수단 및 인덕터를 다이에 배치하기 위한 수단을 포함한다. 인덕터를 다이에 배치하기 위한 수단은 제 1 단자를 형성하기 위한 수단, 제 1 단자를 다이에 전기적으로 그리고 기계적으로 커플링하기 위한 수단, 제 2 단자를 형성하기 위한 수단, 제 1 상호접속부를 사용하여 제 2 단자를 다이에 전기적으로 그리고 기계적으로 커플링하기 위한 수단, 인덕터의 남아있는 부분을 형성하기 위한 수단, 및 인덕터의 남아있는 부분을 복수의 남아있는 상호접속부들에 전기적으로 커플링하지만, 인덕터의 남아있는 부분을 복수의 남아있는 상호접속부들에 전기적으로 커플링하지 않기 위한 수단을 포함한다.

[0017] 비일시적인 컴퓨터-판독 가능 매체는 본원에 설명된 방법들 중 하나 이상을 구현할 수 있다. 또한, 반도체 디바이스/조립체는 유선 또는 무선 디바이스에서 구현될 수 있다.

[0018] 위의 것은 본원에 설명된 하나 이상의 구현들에 관한 간략한 요약이다. 이로써, 요약은 모든 고려되는 양상들 및/또는 구현들에 관한 광범위한 개요로 고려되지 않아야 하고 및/또는 모든 고려되는 양상들 구현들에 관한 핵심적인 또는 중요한 엘리먼트들을 식별하거나 임의의 특정 양상 및/또는 구현과 연관된 범위를 기술하기 위한 요약인 것으로 고려되지 않아야 한다. 따라서, 요약은 아래에 제시된 상세한 설명에 선행하여 본원에 개시된 메커니즘들에 관한 하나 이상의 양상들 및/또는 구현들에 관한 특정 개념들을 간략한 형태로 제시할 목적만을 갖는다.

## 도면의 간단한 설명

[0019] 첨부된 도면들은 본원에 설명되는 기술의 설명을 돋기 위해 제시되고, 구현들의 제한이 아닌 구현들의 예시를 위해서만 제공된다.

[0020] 도 1은 인덕터를 구현하기 위한 종래의 기판의 상면도이다.

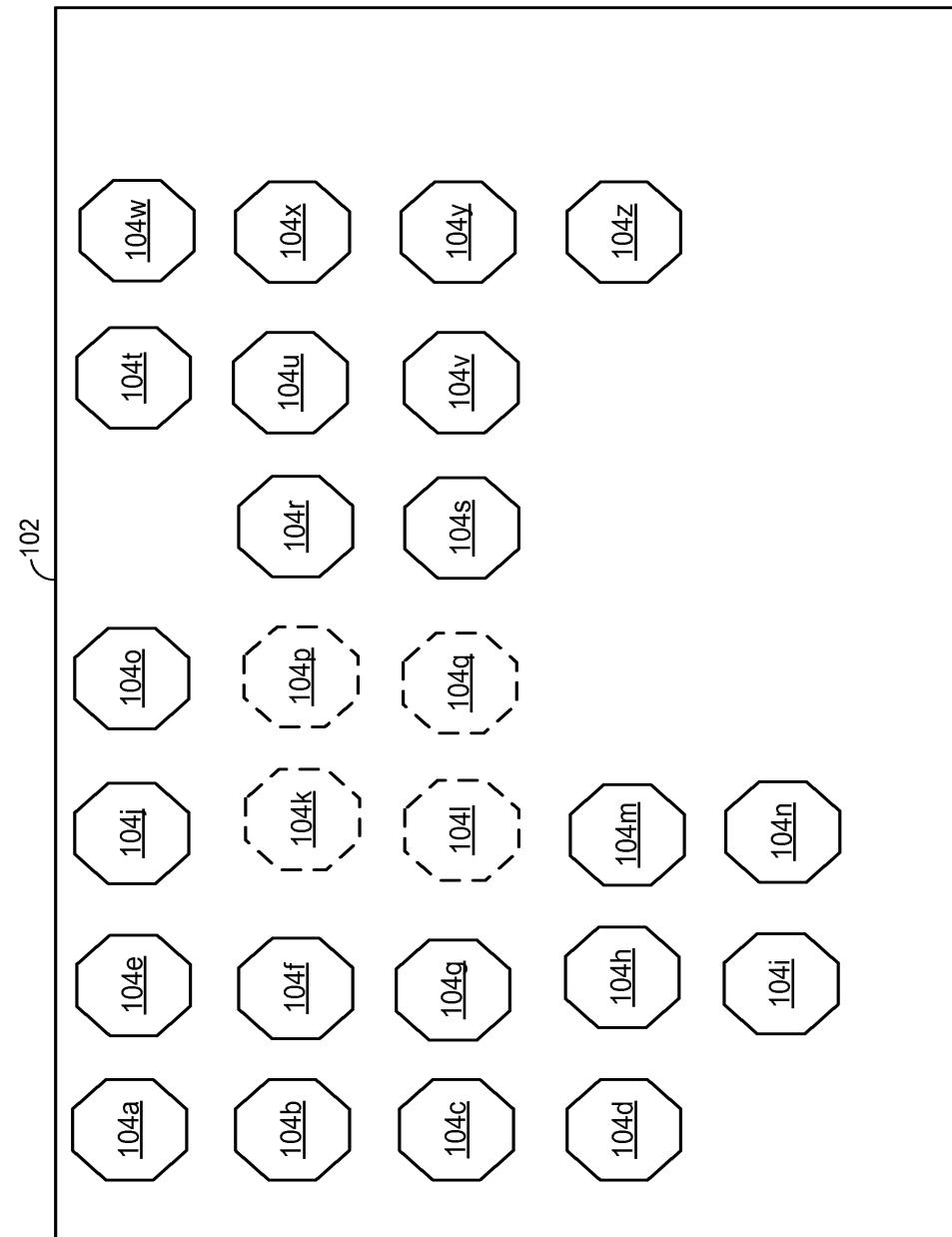

[0021] 도 2는 본원에 설명된 기술의 하나 이상의 구현들에 따른 인덕터가 그 안에 배치된 기판의 상면도이다.

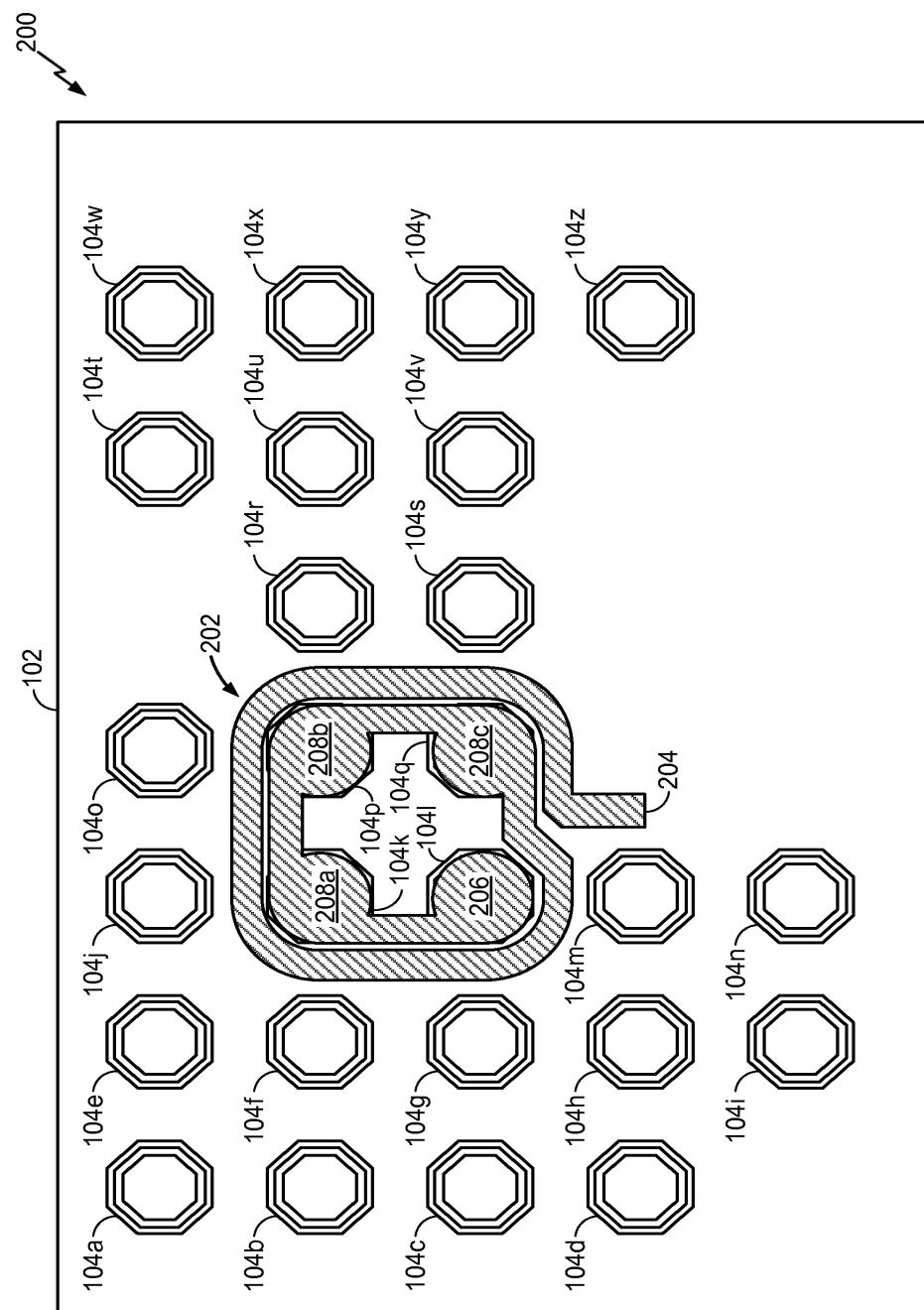

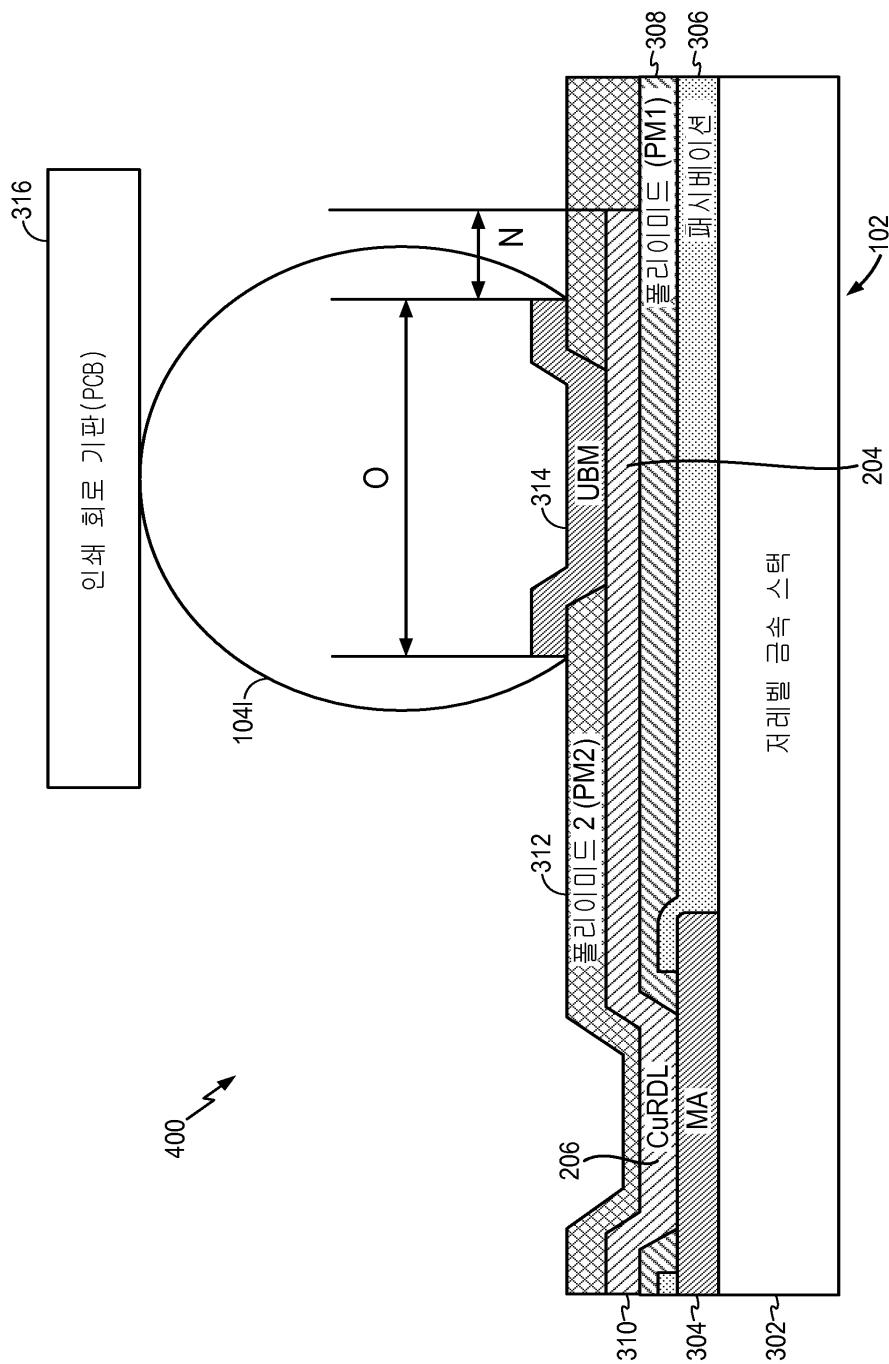

- [0022] 도 3은 본원에 설명된 기술의 하나 이상의 구현들에 따른 반도체 조립체의 단면도이다.

- [0023] 도 4는 본원에 설명된 기술의 하나 이상의 구현들에 따른 반도체 디바이스의 단면도이다.

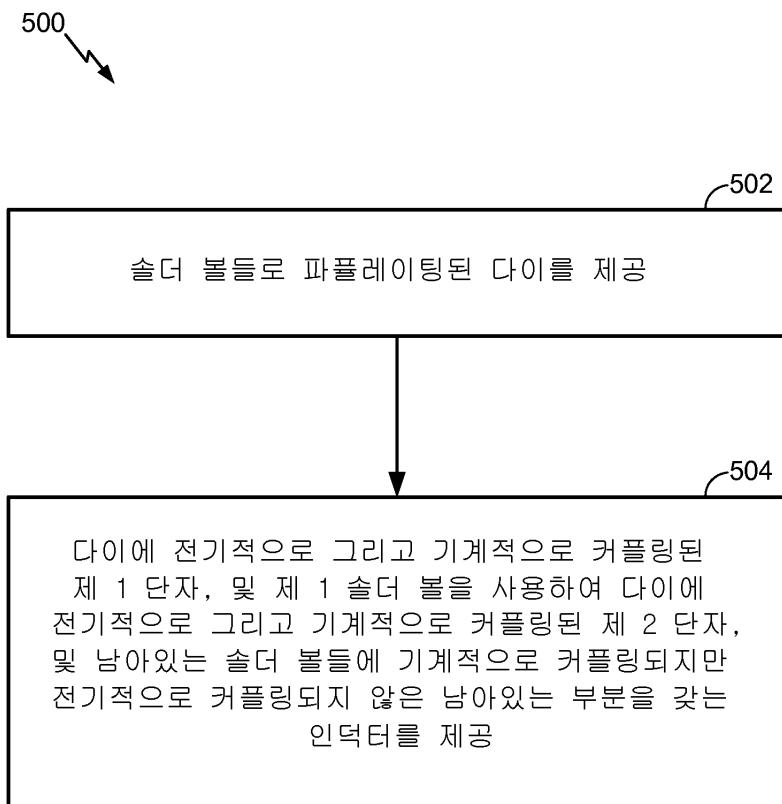

- [0024] 도 5는 본원에 설명된 구현들에 따른 반도체 디바이스를 제조하는 방법의 흐름도이다.

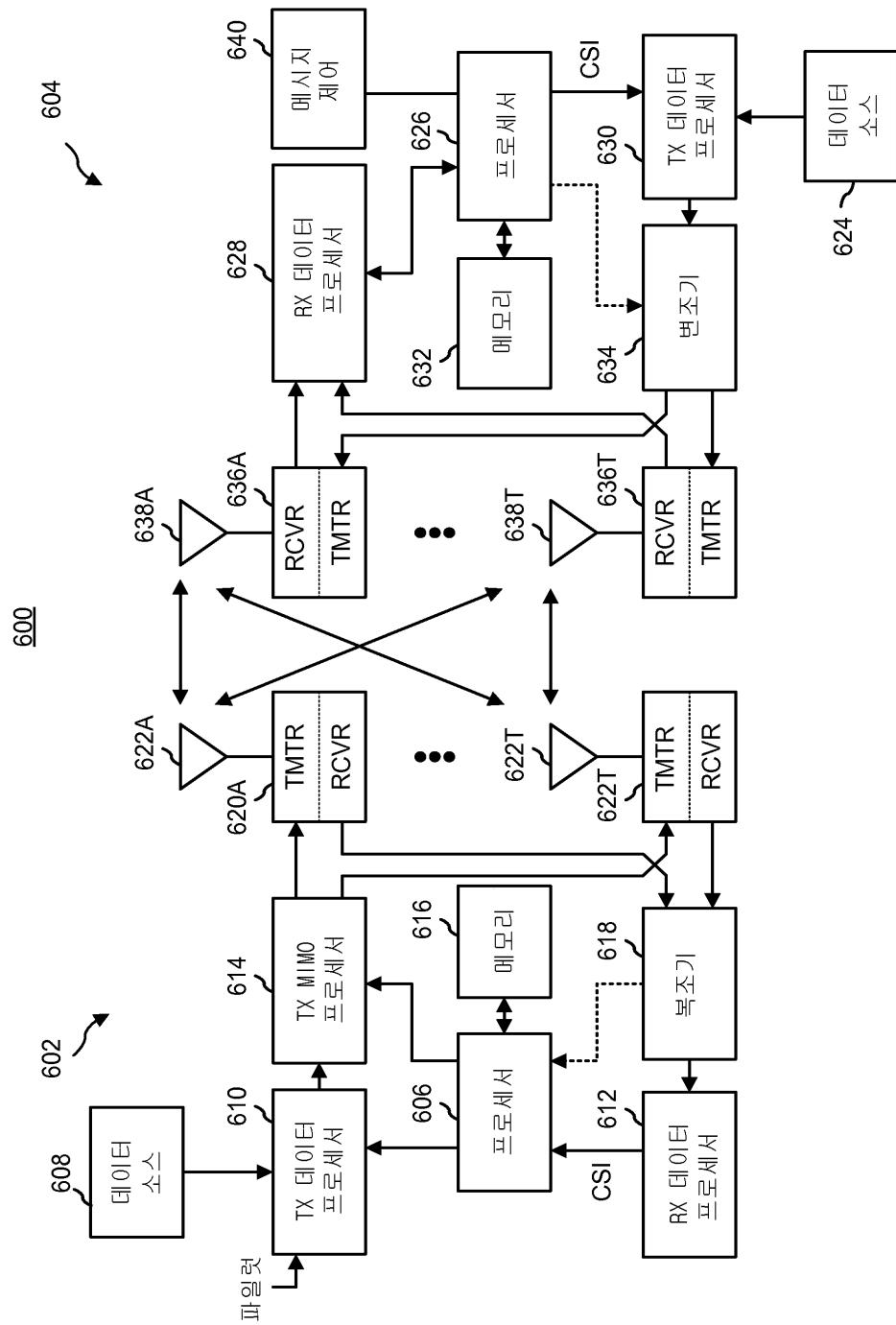

- [0025] 도 6은 본원에 설명된 구현들에 따라 본원에 개시된 기술이 전개될 수 있는 무선 네트워크이다.

### 발명을 실시하기 위한 구체적인 내용

- [0020] [0026] 일반적으로, 본원에 개시된 요지는 WLP(wafer level package)에 대한 플로팅 상호접속부들 및/또는 솔더 볼들에 대한 인덕터 설계를 위한 시스템들, 방법들, 장치들 및 컴퓨터-판독 가능 매체에 관한 것이다. 하나 이상의 구현들에서, 인덕터 설계는 웨이퍼/다이 상에 솔더 볼들을 디파플레이팅하는 것을 수반하지 않는다. 플로팅 솔더 볼들은 인덕터의 부분을 형성한다.

- [0021] [0027] 본원에 설명된 기술의 하나의 특징은 인덕터에서 더 낮은 직류(DC) 저항이 존재한다는 것이다. 이것은 인덕터의 UBM(under bump metallization) 패드들을 사용하여 인덕터를 통과하는 더 큰 전류가 존재하기 때문이다.

- [0022] [0028] 본원에 설명된 기술의 다른 특징은 인덕터에 대한 증가된 인덕턴스가 존재한다는 것이다. 이것은 플로팅 솔더 볼들이 인덕터의 부분이고 나선형 인덕터 내의 하나 이상의 턴을 허용하기 때문이다.

- [0023] [0029] 본원에 설명된 기술의 다른 특징은, 솔더 볼들(104k, 104l, 104p 및 104q)을 디파플레이팅하지 않고서 높은 품질 인자(Q)가 달성된다는 것이다. 예를 들면, 인덕터에 대한 품질 인자(Q)는 다음의 수학식을 통해 발견될 수 있다.

- $$Q = \frac{\omega L}{R}$$

- [0024] [0030] 여기서  $\omega$ 는 라디안 동작 주파수이고,  $L$ 은 인덕터의 인덕턴스이고,  $R$ 은 인덕터의 유효 직렬 저항이고, 프로덕트  $\omega L$ 은 인덕터의 유도 리액턴스(inductive reactance)이다. 따라서, 본원에 설명된 인덕터는, 더 낮은 유효 직렬 저항( $R$ ) 및 더 높은 인덕턴스( $L$ )가 존재하기 때문에, 더 높은 품질 인자( $Q$ )를 달성할 수 있다.

- [0026] [0031] 본원에 설명된 기술의 다른 특징은, 인덕터가 구현되는 전력 증폭기에서 이것이 더 큰 전압 헤드룸을 가능하게 하는 것이다. 예를 들면, 본원에 설명된 기술에 따라 구현된 인덕터를 사용하여, 인덕터에서 더 낮은 기생 저항이 존재한다. 더 낮은 기생 저항을 통해, 옴의 법칙( $V=I*R$ , 여기서  $V$ 는 전압이고,  $I$ 는 전류이고,  $R$ 은 저항임)은 인덕터가 더 많은 전압을 강하시킬 것이라는 지시한다. 따라서, 인덕터에 대한 더 큰 전압 헤드룸이 존재한다.

- [0027] [0032] 본원에 설명된 기술의 다른 특징은, 전력 증폭기가 더 높은 PAE(power-add-efficiency) 및 전력 증폭기 계인을 달성할 수 있다는 것이다. 예를 들면, 인덕터에서 더 낮은 기생 저항은 더 낮은 전력 손실들을 발생시킨다. 더 낮은 전력 손실들은 더 높은 PAE(power-add-efficiency)를 발생시킨다.

- [0028] [0033] 본원에 설명되는 기술의 또 다른 특징은, 패키지에 통합된 인덕터가 3 차원이 아니라 2 차원이기 때문에 와전류들이 감소 또는 제거된다는 것이다. 즉, 인덕터는 패키지 상의 단일 층에 배치된다. 이것은 또한 더 큰 보드 레벨 신뢰성(BLR)을 발생시킨다.

- [0029] [0034] 도 2는 솔더 볼들(104a-104z)로 완전히 파플레이팅된 다이(102)를 갖는 반도체 디바이스(200)의 상면도이다. 솔더 볼들(104a-104z)을 갖는 것으로 예시되지만, 다이(102)는 임의의 적절한 상호접속부로 파플레이팅될 수 있다.

- [0030] [0035] 하나 이상의 구현들에서, 반도체 디바이스(200)는, 적층 패키지 기판과 반대로, WLP(wafer level package), FCBGA(flip-chip ball grid array) 패키지, 또는 FCCSP(flip-chip chip-scale package)이다

- [0031] [0036] 인덕터(202)는 솔더 볼들(104a-104z)의 일부 상에 배치된다. 예시된 구현에서, 인덕터(202)는 솔더 볼들(104k, 104l, 104p 및 104q) 상에 배치된다. 따라서, 솔더 볼들(104a-104z) 중 어느 것도 인덕터(202)를 수용하기 위해 다이(102)로부터 디파플레이팅되지 않았다. 솔더 볼들(104k, 104p 및 104q)은 전기적으로 "플로트"되게 남겨진다. 인덕터(202)가 그 안에 배치되는 경우 솔더 볼들(104k, 104p 및 104q)이 파플레이팅되게 남겨두는 것은 솔더 볼들(104k, 104l, 104p 및 104q)이 적층된 기판들 상의 전통적인 인덕터 구현들에서 제공되지 않는 인덕터(202)에 대한 기계적 지지를 제공하도록 허용한다. 인덕터(202)가 그 안에 배치된 경우에

솔더 볼들(104k, 104l, 104p 및 104q)이 패플레이팅되게 남겨두는 것은 또한 솔더 볼들(104k, 104l, 104p 및 104q)이 인덕터(202)의 부분을 형성하도록 허용한다.

[0032] 예시된 구현에서, 인덕터(202)는 제 1 단자(204), 제 2 단자(206) 및 남아있는 부분(208a-208c)을 포함한다. 제 1 단자(204)는 금속 트레이스(미도시)를 사용하여 다이(102)에 전기적으로 그리고 기계적으로 커플링된다. 제 2 단자(206)는, UBM(under bump metallization) 층(미도시)에 커플링된 솔더 볼(104l)을 사용하여 다이(102)에 전기적으로 그리고 기계적으로 커플링된다. 인덕터(202)의 남아있는 부분(208a-208c)은 솔더 볼들(104k, 104p 및 104q)에 기계적으로 커플링되지만, 다이(102) 또는 솔더 볼들(104k, 104p 및 104q)에 전기적으로 커플링되지 않는다. 솔더 볼들(104k, 104p 및 104q)은 전기적으로 플로팅한다.

[0033] 도 3은 본원에 설명된 기술의 하나 이상의 구현들에 따른 반도체 조립체(300)에서 구현되는 반도체 디바이스(200)의 일부의 단면도이다. 예시된 구현은 저레벨 금속 스택(302) 및 저레벨 금속 스택(302) 상에 배치된 상부 금속 층(MA 층)(304)을 갖는 다이(102)를 도시한다.

[0034] 패시베이션 층(306)은 또한 저레벨 금속 스택(302) 및 MA 층(304) 상에 배치된다. 패시베이션 층은 임의의 적절한 산화물일 수 있다. 제 1 폴리아미드 층(308)은 패시베이션 층(306) 및 MA 층(304) 상에 배치된다.

[0035] CuRDL(copper redistribution layer)(310)은 인덕터(202)를 형성하기 위해 MA 층(304) 및 폴리아미드 층(PM1)(308) 상에 배치된다. CuRDL(copper redistribution layer)(310)은 하나의 인덕터(202) 단자로부터 다른 인덕터(202) 단자로부터 원형 턴(circular turn)을 취하는 나선형 설계에 있을 수 있다. 하나의 인덕터(202) 단자는 PM1(polyimide layer)(308) 상의 패드에 커플링될 수 있고, 반면에 다른 인덕터(202) 단자는 MA 층(304)에 커플링될 수 있다.

[0036] 예시된 구현에서, 단자(206)는 PM1(polyimide layer)(308) 상의 하나 이상의 패드들을 통해 CuRDL(copper redistribution layer)(310)에 커플링된다. 또한, 예시된 구현에서, 단자(204)는 MA 층(304) 상의 하나 이상의 패드들을 통해 CuRDL(copper redistribution layer)(310)에 커플링된다.

[0037] 대안적인 구현에서, 단자(204)는 PM1(polyimide layer)(308) 상의 하나 이상의 패드들을 통해 CuRDL(copper redistribution layer)(310)에 커플링되고, 단자(206)는 MA 층(304) 상의 하나 이상의 패드들을 통해 CuRDL(copper redistribution layer)(310)에 커플링된다. CuRDL(copper redistribution layer)(310)은 임의의 적절한 전기 전도성 테이프일 수 있다.

[0038] 제 2 PM2(polyimide layer)(312)은 PM1(polyimide layer)(308) 및 CuRDL(copper redistribution layer)(310) 상에 배치된다. UBM(under bump metallization) 층(314)은 제 2 PM2(polyimide layer)(312) 및 CuRDL(copper redistribution layer)(310) 상에 배치된다. 솔더 볼(104l)은 UBM(under bump metallization) 층(314) 상에 배치된다. PCB(printed circuit board)(316)는 솔더 볼(104l) 상에 배치된다.

[0039] 예시된 구현에서, CuRDL(copper redistribution layer)(310)은 인덕터(202)의 적어도 일부를 형성한다. 예를 들면, MA 층(304)에 커플링된 CuRDL(copper redistribution layer)(310)의 부분은 인덕터(202)의 제 1 단자(204)일 수 있고, UBM(under bump metallization) 층(314)에 커플링된 CuRDL(copper redistribution layer)(310)의 부분은 인덕터(202)의 제 2 단자(206)일 수 있다. CuRDL(copper redistribution layer)(310)의 남아있는 부분은 패시베이션 층(306) 및 제 2 PM2(polyimide layer)(312)를 사용하여 다이(102)로부터 전기적으로 절연되게 된다.

[0040] 하나 이상의 구현들에서, 인덕터(202)에 대한 더 낮은 직류(DC) 저항(Rdc)은 제 1 PM1(polyimide layer)(308) 상의 큰 CuRDL(copper redistribution layer)(310) 패드에 커플링된 얇은 CuRDL(copper redistribution layer)(310)을 가짐으로써 달성된다. 인덕터(202)에 대한 더 낮은 직류(DC) 저항(Rdc)은 또한 솔더 볼들(104k, 104l, 104p 및 104q)이 디파플레이팅되지 않기 때문에 달성된다. 또한, 솔더 볼들(104k, 104l, 104p 및 104q)이 인덕터(202)의 부분을 형성하게 하는 것은 직류(DC) 저항(Rdc)을 감소시키고, 인덕터(202)에 대한 보드 레벨 신뢰성을 개선한다. 또한, 인덕터(202)가 제 1 PM1(polyimide layer)(308) 패드들로부터 원형 턴을 취하게 하는 것은 조립체의 자속을 개선하고, 이것은 인덕터(202)의 인덕턴스를 개선한다.

[0041] 전형적으로, 솔더 볼들(104k, 104l, 104p 및 104q)이 디파플레이팅되면, 자기장 전파를 방해하는 와전류들이 존재하여, 인덕턴스 저하를 유도한다. 다이(102)로부터 솔더 볼들(104k, 104l, 104p 및 104q)을 디파플레이팅하지 않아야 하는 것은 이러한 소위 "볼 효과"로 인한 저하를 제거한다.

[0042] 도 4는 본원에 설명된 기술의 하나 이상의 대안적인 구현들에 따른 반도체 조립체(400)에서 구현되는 반

도체 디바이스(200)의 부분의 단면도이다. 예시된 구현은, 이것이 저레벨 금속 스택(302), MA 층(304), 패시베이션 층(306), 제 1 PM1(polyimide layer)(308), CuRDL(copper redistribution layer)(310), PM2(polyimide layer)(312), UBM(under bump metallization) 층(314), 솔더 볼(1041), 및 PCB(printed circuit board)(416)를 갖는 다이(102)를 포함한다는 점에서 반도체 조립체(300)와 유사하다.

[0043] [0048] 그러나, 도 4에 예시된 구현에서, MA 층(304)에 커플링된 CuRDL(copper redistribution layer)(310)의 부분은 인더터(202)의 제 2 단자(206)일 수 있고, UBM(under bump metallization) 층(314)에 커플링된 CuRDL(copper redistribution layer)(310)의 부분은 인더터(202)의 제 1 단자(204)일 수 있다. CuRDL(copper redistribution layer)(310)의 남아있는 부분은 패시베이션 층(306) 및 제 2 PM2(polyimide layer)(312)를 사용하여 다이(102)로부터 전기적으로 절연되게 된다.

[0044] [0049] 도 5는 본원에 설명된 기술의 하나 이상의 구현들에 따라 반도체 디바이스(200)를 제조하는 방법(500)을 예시한 흐름도이다.

[0045] [0050] 블록(502)에서, 방법(500)은 솔더 볼들로 파풀레이팅된 다이를 제공한다. 하나 이상의 구현들에서, 방법(500)은 솔더 볼들(104a-104z)로 파풀레이팅된 다이(102)를 제공한다. 다이(102)는 증착, 포토리소그라파, 에칭, CMP(chemical-mechanical planarization) 등과 같은 알려진 기술을 사용하여 제조된다. 다이(102)는 볼 배치 시스템들, 합금 솔더 페이스트를 통한 스텐실 인쇄 등과 같은 알려진 기술들을 사용하여 솔더 볼들로 파풀레이팅될 수 있다.

[0046] [0051] 블록(504)에서, 방법(500)은 다이 내의(또는 상의) 인더터를 제공한다. 하나 이상의 구현들에서, 인더터(202)는 다이(102) 내에(또는 상에) 배치되고, 솔더 볼들(104k, 104l, 104p 및 104q) 둘레에 원형 패턴으로 형성된다. 인더터(202)의 제 1 단자(204)는, CuRDL(copper redistribution layer)(310)이 MA 층(304)과 메이팅(mate)하는 다이(102)에 전기적으로 그리고 기계적으로 커플링될 수 있다. 인더터(202)의 제 2 단자(206)는, CuRDL(copper redistribution layer)(310)가 UBM(under bump metallization) 층(314)과 메이팅하는 다이(102)에 전기적으로 그리고 기계적으로 커플링될 수 있다.

[0047] [0052] 대안적인 구현에서, 단자 접속들이 역전될 수 있다. 결과적인 조립체는 솔더 볼들 중 어느 것도 디파풀레이팅되지 않기 때문에 개선된 기계적 안정성을 갖는다.

[0048] [0053] 도 6은 본원에 설명된 기술의 예시적인 구현에 따른 광대역 무선 네트워크(600)의 블록도이고, 여기서 인더터(202), 반도체 조립체(300) 및/또는 반도체 조립체(400)가 구현될 수 있다. 무선 네트워크(600)는 사용자 디바이스(602) 및 기지국(604)을 포함한다.

[0049] [0054] 예시된 구현에서, 사용자 디바이스(602)는 프로세서(606), 데이터 소스(608), 송신(TX) 데이터 프로세서(610), 수신(RX) 데이터 프로세서(612), 송신(TX) 다중-입력 다중-출력(MIMO) 프로세서(614), 메모리(616), 복조기(DEMOD)(618), 몇몇의 트랜시버들(620A 내지 620T), 및 몇몇의 안테나들(622A 내지 622T)을 포함한다.

[0050] [0055] 예시된 구현에서, 사용자 디바이스(602)는 데이터 소스(624), 프로세서(626), 수신 데이터 프로세서(628), 송신 데이터 프로세서(630), 메모리(632), 복조기(634), 몇몇의 트랜시버들(636A 내지 636T), 몇몇의 안테나들(638A 내지 638T) 및 메시지 제어 모듈(640)을 포함한다.

[0051] [0056] 예시된 사용자 디바이스(602)는 사용자 장비, 가입자국, 가입자 유닛, 이동국, 모바일, 모바일 노드, 원격국, 원격 단말, 사용자 단말, 사용자 에이전트, 사용자 디바이스, 또는 몇몇 다른 용어를 포함하거나, 그로서 구현되거나 또는 공지될 수 있다. 몇몇 구현들에서, 사용자 디바이스(602)는 셀룰러 전화, 코드리스 전화, 세션 개시 프로토콜(SIP) 전화, 무선 로컬 루프(WLL)국, 개인 휴대 정보 단말기(PDA), 무선 접속 성능을 갖는 핸드헬드 디바이스 또는 무선 모뎀에 접속되는 몇몇의 다른 적절한 프로세싱 디바이스일 수 있다. 따라서, 본원에 교시된 하나 이상의 양상들은 전화(예를 들어, 셀룰러 폰 또는 스마트 폰), 컴퓨터(예를 들어, 랩탑), 휴대용 통신 디바이스, 휴대용 컴퓨팅 디바이스(예를 들어, 개인 휴대 정보 단말기), 엔터테인먼트 디바이스(예를 들어, 뮤직 디바이스, 비디오 디바이스 또는 위성 라디오), 글로벌 포지셔닝 시스템 디바이스, 또는 무선 매체를 통해 통신하도록 구성되는 임의의 다른 적절한 디바이스에 통합될 수 있다.

[0052] [0057] 예시된 기지국(604)은 NodeB, eNodeB, 라디오 네트워크 제어기(RNC), 기지국(BS), 라디오 기지국(RBS), 기지국 제어기(BSC), 베이스 트랜시버 스테이션(BTS), 트랜시버 기능부(TF), 라디오 트랜시버, 라디오 라우터, 기본 서비스 세트(BSS), 확장 서비스 세트(ESS), 매크로 셀, 매크로 노드, 홈 eNB(HeNB), 펨토 셀, 펨토 노드, 퍼코 노드, 또는 몇몇 다른 유사한 용어를 포함하거나, 그로서 구현되거나 또는 공지될 수 있다.

- [0053] [0058] 예시된 데이터 소스(608)는 다수의 데이터 스트림들에 대한 트래픽을 송신(TX) 데이터 프로세서(610)에 제공한다.

- [0054] [0059] 송신(TX) 데이터 프로세서(610)는 코딩된 데이터를 제공하기 위해 그 데이터 스트림에 대해 선택된 특정 코딩 방식에 기초하여 각각의 데이터 스트림에 대한 트래픽 데이터를 포맷, 코딩 및 인터리빙한다. 각각의 데이터 스트림에 대한 코딩된 데이터는 OFDM 기술들을 사용하여 파일럿 데이터와 멀티플렉싱될 수 있다.

- [0055] [0060] 파일럿 데이터는 통상적으로 공지된 방식으로 프로세싱되는 공지된 데이터 패턴이고, 수신기 시스템에서 채널 응답을 추정하는데 이용될 수 있다. 이어서, 각각의 데이터 스트림에 대해 멀티플렉싱된 파일럿 및 코딩된 데이터는, 변조 심볼들을 제공하기 위해, 그 데이터 스트림에 대해 선택된 특정한 변조 방식(예를 들어, BPSK, QPSK, M-PSK 또는 M-QAM)에 기초하여 변조(즉, 심볼 맵핑)된다.

- [0056] [0061] 각각의 데이터 스트림에 대한 데이터 레이트, 코딩 및 변조는 프로세서(610)에 의해 수행되는 명령들에 의해 결정될 수 있다. 메모리(616)는 프로그램 코드, 데이터, 및 프로세서(610) 또는 사용자 디바이스(602)의 다른 컴포넌트들에 의해 이용되는 다른 정보를 저장할 수 있다.

- [0057] [0062] 이어서, 모든 데이터 스트림들에 대한 변조 심볼들은 TX MIMO 프로세서(614)에 제공되고, TX MIMO 프로세서(614)는 (예를 들어, OFDM을 위해) 변조 심볼들을 추가적으로 프로세싱할 수 있다. 이어서, TX MIMO 프로세서(614)는,  $N_T$ 개의 트랜시버(XCVR)들(620A 내지 620T)에  $N_T$ 개의 변조 심볼 스트림들을 제공한다. 몇몇 구현들에서, TX MIMO 프로세서(614)는 데이터 스트림들의 심볼들 및 심볼을 송신하고 있는 안테나에 범-형성 가중치들을 적용한다.

- [0058] [0063] 각각의 트랜시버(XCVR)(620A 내지 620T)는 각각의 심볼 스트림을 수신 및 프로세싱하여 하나 이상의 아날로그 신호들을 제공하고, 그 아날로그 신호들을 더 컨디셔닝(예를 들어, 증폭, 필터링 및 상향변환)하여 MIMO 채널을 통한 송신에 적합한 변조된 신호를 제공한다. 이어서, 트랜시버들(XCVR)(620A 내지 620T)로부터의  $N_T$ 개의 변조된 신호들은 각각  $N_T$ 개의 안테나들(622A 내지 622T)로부터 송신된다.

- [0059] [0064] 기지국(604)에서, 송신된 변조 신호들이  $N_R$ 개의 안테나들(638A 내지 638R)에 의해 수신되고, 각각의 안테나(638A 내지 638R)로부터의 수신 신호가 각각의 트랜시버(XCVR)(636A 내지 636R)에 제공된다. 각각의 트랜시버(XCVR)(636A 내지 636R)는 각각의 수신 신호를 컨디셔닝(예를 들어, 필터링, 증폭 및 하향변환)하고, 그 컨디셔닝된 신호를 디지털화하여 샘플들을 제공하고, 그 샘플들을 더 프로세싱하여 대응하는 "수신된" 심볼 스트림을 제공한다.

- [0060] [0065] 이어서, 수신(RX) 데이터 프로세서(628)는 특정 수신기 프로세싱 기술에 기초하여  $N_R$ 개의 트랜시버들(XCVR)(636A 내지 636R)로부터의  $N_R$ 개의 수신된 심볼 스트림들을 수신 및 프로세싱하여  $N_T$ 개의 "검출된" 심볼 스트림들을 제공한다. 이어서, 수신(RX) 데이터 프로세서(628)는 각각의 검출된 심볼 스트림을 복조, 디인터리빙 및 디코딩하여 데이터 스트림에 대한 트래픽 데이터를 복원한다. 수신(RX) 데이터 프로세서(628)에 의한 프로세싱은 사용자 디바이스(602)에서의 송신(TX) MIMO 프로세서(614) 및 송신(TX) 데이터 프로세서(610)에 의해 수행되는 프로세싱에 상보적이다.

- [0061] [0066] 프로세서(626)는 어느 프리-코딩 행렬을 이용할지를 주기적으로 결정한다(아래에 논의됨). 프로세서(626)는 행렬 인덱스 부분 및 랭크(rank) 값 부분을 포함하는 역방향 링크 메시지를 포뮬레이트(formulate)한다.

- [0062] [0067] 데이터 메모리(632)는 프로그램 코드, 데이터 및 프로세서(626) 또는 기지국(604)의 다른 컴포넌트들에 의해 이용되는 다른 정보를 저장할 수 있다.

- [0063] [0068] 역방향 링크 메시지는 통신 링크 및/또는 수신된 데이터 스트림에 관한 다양한 유형들의 정보를 포함할 수 있다. 이어서, 역방향 링크 메시지는, 데이터 소스(624)로부터의 다수의 데이터 스트림들에 대한 트래픽 데이터를 또한 수신하는 TX 데이터 프로세서(630)에 의해 프로세싱되고, 변조기(634)에 의해 변조되고, 트랜시버들(XCVR)(636A 내지 636R)에 의해 컨디셔닝되고, 사용자 디바이스(602)로 다시 송신된다.

- [0064] [0069] 사용자 디바이스(602)에서는, 기지국(604)에 의해 송신된 역방향 링크 메시지를 추출하기 위해, 기지국(604)으로부터의 변조된 신호들이 안테나들(622A 내지 622T)에 의해 수신되고, 트랜시버들(XCVR)(620A 내지 620R)에 의해 컨디셔닝되고, 복조기(DEMOD)(618)에 의해 복조되고, RX 데이터 프로세서(612)에 의해 프로세싱된

다. 이어서, 프로세서(610)는, 추출된 메시지를 프로세싱함으로써, 빔-형성 가중치들을 결정하기 위해 어느 프리코딩 행렬을 이용할지를 결정한다.

[0065] [0070] 사용자 디바이스(602) 및 기지국(604)에 대해, 설명된 컴포넌트들 중 2 개 이상의 기능이 단일 컴포넌트에 의해 제공될 수 있다는 것이 인지되어야 한다. 예를 들면, 단일 프로세싱 컴포넌트는 메시지 제어 컴포넌트(640) 및 프로세서(626)의 기능을 제공할 수 있다.

[0066] [0071] 무선 노드가 비-무선 방식으로(예를 들면, 유선 접속을 통해) 정보를 송신 및/또는 수신하도록 구성될 수 있다는 것이 또한 인지되어야 한다. 따라서, 본원에서 논의된 수신기 및 송신기는 비-무선 매체를 통해 통신하기 위한 적절한 통신 인터페이스 컴포넌트들(예를 들면, 전기 또는 광학 인터페이스 컴포넌트들)을 포함할 수 있다.

[0067] [0072] 네트워크(600)는 하기의 기술들: 코드 분할 다중 액세스(CDMA) 시스템들, 다중-캐리어 CDMA(MC-CDMA), 광대역 CDMA(W-CDMA), 고속 패킷 액세스(HSPA, HSPA+) 시스템들, 시분할 다중 액세스(TDMA) 시스템들, 주파수 분할 다중 액세스(FDMA) 시스템들, 단일-캐리어 FDMA(SC-FDMA) 시스템들, 직교 주파수 분할 다중 액세스(OFDMA) 시스템들 또는 다른 다중 액세스 기술들 중 임의의 하나 또는 그 결합들을 구현할 수 있다. 본 명세서의 교시들을 이용하는 무선 통신 시스템은, IS-97, cdma2000, IS-876, W-CDMA, TD-SCDMA 및 다른 표준들과 같은 하나 이상의 표준들을 구현하도록 설계될 수 있다.

[0068] [0073] CDMA 네트워크는 유니버설 지상 무선 액세스(UTRA), cdma2000 또는 몇몇 다른 기술과 같은 라디오 기술을 구현할 수 있다. UTRA는 W-CDMA 및 로우 칩 레이트(LCR)를 포함한다. cdma2000 기술은 IS-2000, IS-97 및 IS-876 표준들을 커버한다. TDMA 네트워크는 이동 통신용 범용 시스템(GSM)과 같은 무선 기술을 구현할 수 있다. OFDMA 네트워크는 이볼브드 UTRA(E-UTRA), IEEE 802.11, IEEE 802.16, IEEE 802.20, Flash-OFDM® 등과 같은 라디오 기술을 구현할 수 있다. UTRA, E-UTRA 및 GSM은 유니버설 이동 전기통신 시스템(UMTS)의 일부이다.

[0069] [0074] 본원의 교시들은 3GPP 롱 텀 에볼루션(LTE) 시스템, 울트라 모바일 브로드밴드(UMB) 시스템 및 다른 유형들의 시스템들에서 구현될 수 있다. LTE는 E-UTRA를 이용하는 UMTS의 릴리스이다. UTRA, E-UTRA, GSM, UMTS 및 LTE는 "3세대 파트너쉽 프로젝트(3GPP)"로 명명된 기구로부터의 문서들에 제시되는 한편, cdma2000은 "3세대 파트너쉽 프로젝트 2(3GPP2)"로 명명된 기구로부터의 문서들에 제시된다.

[0070] [0075] 본 개시의 특정 양상들이 3GPP 용어를 이용하여 설명될 수 있지만, 본원의 교시들은 3GPP(예를 들어, Rel99, Rel7, Rel6, Rel7) 기술뿐만 아니라, 3GPP2(예를 들어, 1xRTT, 1xEV-DO Rel0, RevA, RevB) 기술 및 다른 기술들에 적용될 수도 있음을 이해해야 한다.

[0071] [0076] 본원에 설명된 기술의 양상들은 본원에 설명된 기술의 특정 구현들에 관련된 다음의 설명 및 관련 도면들에 개시된다. 대안적인 구현들은 본원에 설명된 기술의 범위에서 벗어나지 않고서 고안될 수 있다. 부가적으로, 본원에 설명된 기술의 잘 알려진 엘리먼트들은 상세히 설명되지 않을 것이거나, 본원에 설명된 기술의 관련 세부사항들을 모호하게 하지 않기 위해 생략될 것이다.

[0072] [0077] 단어 "예시적인"은 "예, 경우, 또는 예시로서 작용하는" 것을 의미하도록 본원에서 사용된다. "예시적인" 것으로서 본원에 설명된 임의의 구현예가 다른 구현예들보다 바람직하거나 유리한 것으로서 해석될 필요는 없다. 마찬가지로, 용어 "본원에 설명된 기술의 구현들"은, 본원에 설명된 기술의 모든 구현이 논의된 특징, 이점 또는 동작 모드를 포함한다는 것을 요구하지는 않는다.

[0073] [0078] 본원에 사용된 용어는 단지 특정 구현들을 설명할 목적이며, 본원에 설명된 기술의 구현들을 제한하도록 의도되지 않는다. 본원에 사용된 바와 같이, 단수 형태들("a", "an" 및 "the")은, 문맥이 명백히 달리 표시하지 않는다면, 물론 복수 형태들을 포함하도록 의도된다. 용어들 "포함하다(comprises)", "포함하는(comprising)", "구비하다(includes)" 및/또는 "구비하는(including)"은 본 명세서에 이용될 때, 서술된 특징들, 정수들, 단계들, 동작들, 엘리먼트들 및/또는 컴포넌트들의 존재를 특정하지만, 하나 이상의 다른 특징들, 정수들, 단계들, 동작들, 엘리먼트들, 컴포넌트들 및/또는 그들의 그룹들의 존재 또는 추가를 배제하지는 않음이 더 이해될 것이다.

[0074] [0079] 또한, 많은 구현들은, 예를 들면, 컴퓨팅 디바이스의 엘리먼트들에 의해 수행되도록 동작들의 시퀀스들의 관점에서 설명된다. 본원에 설명된 다양한 동작들이 특정 회로들(예를 들면, ASIC들(application specific IC들)), 하나 이상의 프로세서들에 의해 실행되는 프로그램 명령들 또는 이 둘 모두의 조합에 의해 수행될 수 있다는 것이 인식될 것이다. 부가적으로, 본원에 설명된 이러한 동작들의 시퀀스는, 실행될 때, 연관된 프로세

서로 하여금 본원에 설명된 기능을 수행하게 할 대응하는 컴퓨터 명령들의 세트가 그 안에 저장된 임의의 형태의 컴퓨터-판독 가능 저장 매체 내에서 완전히 구현되는 것으로 고려될 수 있다. 따라서, 본원에 설명된 기술의 다양한 양상들은 다수의 상이한 형태들로 구현될 수 있고, 이를 모두는 청구된 요지의 범위 내에 있는 것으로 고려되었다. 또한, 본원에 설명된 구현들 각각에 대해, 임의의 그러한 구현들의 대응하는 형태는, 예를 들면, 설명된 동작을 수행"하도록 구성된 로직"으로서 설명될 수 있다.

[0075] [0080] 당업자들은, 정보 및 신호들이 다양한 상이한 기술들 및 기법들을 이용하여 표현될 수 있다는 것을 이해할 것이다. 예를 들어, 전술한 설명을 통해 참조될 수 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들 및 칩들은 전압들, 전류들, 전자기파들, 자기장 또는 자기 입자들, 광학장 또는 광학 입자들, 또는 이들의 임의의 조합으로 표현될 수 있다.

[0076] [0081] 더욱이, 당업자들은 본 명세서에 개시된 구현들에 관련하여 설명되는 다양한 예시적인 로직 블록들, 모듈들, 회로들, 및 알고리즘 단계들이 전자 하드웨어, 컴퓨터 소프트웨어, 또는 이 둘의 결합들로서 구현될 수 있음을 이해할 것이다. 하드웨어와 소프트웨어의 상호 교환 가능성을 명확하게 설명하기 위해, 다양한 예시적인 컴퓨터들, 블록들, 모듈들, 회로들, 및 단계들이 이들의 기능성의 관점에서 일반적으로 상술되었다. 이러한 기능이 하드웨어로 구현되는지 또는 소프트웨어로 구현되는지는 전체 시스템에 부과된 설계 제약들 및 특정 애플리케이션에 좌우된다. 당업자들은 설명되는 기능을 각각의 특정 애플리케이션에 대해 다양한 방식들로 구현할 수 있지만, 이러한 구현 결정들이 본원에 설명된 본 기술의 범위를 벗어나게 하는 것으로 해석되어서는 안 된다.

[0077] [0082] 본 명세서에 개시된 구현들과 관련하여 설명된 방법들, 시퀀스들 및/또는 알고리즘들은 직접 하드웨어로, 프로세서에 의해 실행되는 소프트웨어 모듈로, 또는 이 둘의 결합으로 구현될 수 있다. 소프트웨어 모듈은, RAM 메모리, 플래시 메모리, ROM 메모리, EPROM 메모리, EEPROM 메모리, 레지스터들, 하드 디스크, 착탈식 디스크, CD-ROM, 또는 당업계에 공지된 임의의 다른 형태의 저장 매체에 상주할 수 있다. 예시적인 저장 매체는, 프로세서가 저장 매체로부터 정보를 판독하고 저장 매체에 정보를 기록할 수 있도록 프로세서에 커플링된다. 대안적으로, 저장 매체는 프로세서에 통합될 수 있다.

[0078] [0083] 따라서, 본원에 설명된 기술의 구현은 반도체 디바이스를 제조하는 방법을 구현하는 컴퓨터-판독 가능 매체를 포함할 수 있다. 따라서, 본원에 설명된 기술은 예시된 예들로 제한되지 않고, 본원에 설명된 기능을 수행하기 위한 임의의 수단은 본원에 설명된 기술의 구현들에 포함된다.

[0079] [0084] 앞서 말한 개시가 본원에 설명된 기술의 예시적인 구현들을 도시하지만, 첨부된 청구항들에 의해 정의된 바와 같은 본원에 설명된 기술의 범위에서 벗어나지 않고서 다양한 변화들 및 수정들이 본원에서 이루어질 수 있다는 것이 주목되어야 한다. 본원에 설명된 기술의 구현들에 따른 방법 청구항들의 기능들, 단계들 및/또는 동작들은 임의의 특정 순서로 수행될 필요는 없다. 또한, 본원에 설명된 기술의 엘리먼트들이 단수 형태로 설명 또는 청구될 수 있지만, 단수에 대한 제한이 명시적으로 언급되지 않는다면, 복수가 고려된다.

도면

도면1

도면2

도면3

도면4

## 도면5

## 도면6

### 【심사관 직권보정사항】

### 【직권보정 1】

### 【보정항목】 청구범위

### 【보정세부항목】 청구항 1

### 【변경전】

반도체 패키지로서,

### 상기 패키지는:

복수의 상호접속부들(104a-104z)로 패플레이팅된(populated) 다이(die)(102); 및

상기 다이에 배치된 잉髑髑(202)를 포획하고

상기 익더터는 상기 복수의 상호접속부들 중 제 1 상호접속부(1041) 상에, 그리고 상기 복수의 상호접속부들 중 남아있는 상호접속부들(104k, 104p, 104q)의 세트 상에 배치되고, 상기 인더터는:

상기 다이에 전기적으로 그리고 기계적으로 커플링된 제 1 단자;

상기 제 1 상호접속부가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 제 1 상호접속부(1041)를 통해 상기 다이에 전기적으로 그리고 기계적으로 커플링된 제 2 단자; 및

상기 남아있는 상호접속부들의 세트가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 전기적으로 커플링되지는 않지만 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 기계적으로 커플링된 상기 인더터의 남아있는 부분

을 포함하고,

상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트는 전기적으로 플로팅(floating)하는, 반도체 패키지.

#### 【변경후】

반도체 패키지로서,

상기 패키지는:

복수의 상호접속부들(104a-104z)로 패플레이팅된(populated) 다이(die)(102); 및

상기 다이에 배치된 인더터(202)를 포함하고,

상기 인더터는 상기 복수의 상호접속부들 중 제 1 상호접속부(1041) 상에, 그리고 상기 복수의 상호접속부들 중 남아있는 상호접속부들(104k, 104p, 104q)의 세트 상에 배치되고, 상기 인더터는:

상기 다이에 전기적으로 그리고 기계적으로 커플링된 제 1 단자;

상기 제 1 상호접속부가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 제 1 상호접속부(1041)를 통해 상기 다이에 전기적으로 그리고 기계적으로 커플링된 제 2 단자; 및

상기 남아있는 상호접속부들의 세트가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 전기적으로 커플링되지는 않지만 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 기계적으로 커플링된 상기 인더터의 남아있는 부분

을 포함하고,

상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트는 전기적으로 플로팅(floating)하는, 반도체 패키지.

#### 【직권보정 2】

##### 【보정항목】 청구범위

##### 【보정세부항목】 청구항 6

##### 【변경전】

반도체 패키지를 제조하는 방법으로서,

복수의 상호접속부들(104a-104z)로 패플레이팅된 다이(102)를 제공하는 단계; 및

상기 다이에 인더터(202)를 배치하는 단계를 포함하고,

상기 익더터는 상기 복수의 상호접속부들 중 제 1 상호접속부(1041) 상에, 그리고 상기 복수의 상호접속부들 중 남아있는 상호접속부들(104k, 104p, 104q)의 세트 상에 배치되고, 상기 다이에 상기 인더터를 배치하는 단계는:

상기 인더터의 제 1 단자를 형성하고 그리고 상기 다이에 상기 제 1 단자를 전기적으로 그리고 기계적으로 커플링하는 단계;

상기 제 1 상호접속부가 상기 인더터에 대한 기계적 지지를 제공하도록, 상기 인더터의 제 2 단자를 형성하고 그리고 상기 제 1 상호접속부(1041)를 통해 상기 다이에 상기 제 2 단자를 전기적으로 그리고 기계적으로 커플링하는 단계; 및

상기 남아있는 상호접속부들의 세트가 상기 인덕터에 대한 기계적 지지를 제공하도록, 상기 인덕터의 남아있는 부분을 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 전기적으로 커플링하지 않지만 상기 인덕터의 남아있는 부분을 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 기계적으로 커플링하여 상기 인덕터의 남아있는 부분을 형성하는 단계

를 포함하고,

상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트는 전기적으로 플로팅하는, 반도체 패키지를 제조하는 방법.

**【변경후】**

반도체 패키지를 제조하는 방법으로서,

복수의 상호접속부들(104a-104z)로 패플레이팅된 다이(102)를 제공하는 단계; 및

상기 다이에 인덕터(202)를 배치하는 단계를 포함하고,

상기 인덕터는 상기 복수의 상호접속부들 중 제 1 상호접속부(104l) 상에, 그리고 상기 복수의 상호접속부들 중 남아있는 상호접속부들(104k, 104p, 104q)의 세트 상에 배치되고, 상기 다이에 상기 인덕터를 배치하는 단계는:

상기 인덕터의 제 1 단자를 형성하고 그리고 상기 다이에 상기 제 1 단자를 전기적으로 그리고 기계적으로 커플링하는 단계;

상기 제 1 상호접속부가 상기 인덕터에 대한 기계적 지지를 제공하도록, 상기 인덕터의 제 2 단자를 형성하고 그리고 상기 제 1 상호접속부(104l)를 통해 상기 다이에 상기 제 2 단자를 전기적으로 그리고 기계적으로 커플링하는 단계; 및

상기 남아있는 상호접속부들의 세트가 상기 인덕터에 대한 기계적 지지를 제공하도록, 상기 인덕터의 남아있는 부분을 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 전기적으로 커플링하지 않지만 상기 인덕터의 남아있는 부분을 상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트에 기계적으로 커플링하여 상기 인덕터의 남아있는 부분을 형성하는 단계

를 포함하고,

상기 남아있는 상호접속부들(104k, 104p, 104q)의 세트는 전기적으로 플로팅하는, 반도체 패키지를 제조하는 방법.