(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4339000号

(P4339000)

(45) 発行日 平成21年10月7日(2009.10.7)

(24) 登録日 平成21年7月10日(2009.7.10)

(51) Int.Cl.

F 1

|                        |                 |

|------------------------|-----------------|

| GO9F 9/30 (2006.01)    | GO9F 9/30 338   |

| GO2B 5/20 (2006.01)    | GO2B 5/20 101   |

| GO2F 1/1343 (2006.01)  | GO2F 1/1343     |

| HO1L 29/786 (2006.01)  | HO1L 29/78 612C |

| HO1L 21/3205 (2006.01) | HO1L 21/88 J    |

請求項の数 16 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2003-84808 (P2003-84808)

(22) 出願日

平成15年3月26日 (2003.3.26)

(65) 公開番号

特開2004-4663 (P2004-4663A)

(43) 公開日

平成16年1月8日 (2004.1.8)

審査請求日

平成18年3月22日 (2006.3.22)

(31) 優先権主張番号

特願2002-87222 (P2002-87222)

(32) 優先日

平成14年3月26日 (2002.3.26)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 高山 徹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 北川 創

最終頁に続く

(54) 【発明の名称】 半導体装置およびその作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面を有する基板と、

前記基板上の第1の絶縁膜と、

前記第1の絶縁膜に埋め込まれた配線と、

前記第1の絶縁膜及び前記配線上の第2の絶縁膜と、

前記第2の絶縁膜上の薄膜トランジスタとを有し、

前記薄膜トランジスタは半導体層、ゲート絶縁膜、及びゲート電極を有し、

前記配線は、銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金でなり、

前記配線と前記第1の絶縁膜の間及び前記配線と前記第2の絶縁膜の間にはバリア層が設けられ、前記バリア層は前記配線と接しており、

前記薄膜トランジスタの前記ゲート電極は前記配線と電気的に接続していることを特徴とする半導体装置。

## 【請求項 2】

絶縁表面を有する基板と、

前記基板上の第1の絶縁膜と、

前記第1の絶縁膜に埋め込まれた配線と、

前記第1の絶縁膜及び前記配線上の第2の絶縁膜と、

前記第2の絶縁膜上の薄膜トランジスタとを有し、

前記薄膜トランジスタは、ソース領域及びドレイン領域を有する半導体層、ゲート絶縁

膜、並びにゲート電極を有し、

前記配線は、銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金でなり、

前記配線と前記第1の絶縁膜の間及び前記配線と前記第2の絶縁膜の間にはバリア層が設けられ、前記バリア層は前記配線と接しており、

前記薄膜トランジスタの前記ソース領域は前記配線と電気的に接続していることを特徴とする半導体装置。

【請求項3】

絶縁表面を有する基板と、

前記基板上の第1の絶縁膜と、

前記第1の絶縁膜に埋め込まれた配線と、

10

前記第1の絶縁膜及び前記配線上の第2の絶縁膜と、

前記第2の絶縁膜上の薄膜トランジスタとを有し、

前記薄膜トランジスタは、ソース領域及びドレイン領域を有する半導体層、ゲート絶縁膜、並びにゲート電極を有し、

前記配線は、銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金でなり、

前記配線と前記第1の絶縁膜の間及び前記配線と前記第2の絶縁膜の間にはバリア層が設けられ、前記バリア層は前記配線と接しており、

前記薄膜トランジスタの前記ドレイン領域は前記配線と電気的に接続していることを特徴とする半導体装置。

【請求項4】

20

請求項1において、

前記配線はゲート配線であることを特徴とする半導体装置。

【請求項5】

請求項2において、

前記配線は、ソース配線、または電源供給線であることを特徴とする半導体装置。

【請求項6】

絶縁表面を有する基板と、

前記基板上の第1の絶縁膜と、

前記第1の絶縁膜に埋め込まれたゲート配線と、

30

前記第1の絶縁膜及び前記ゲート配線上の第2の絶縁膜と、

前記第2の絶縁膜上の薄膜トランジスタとを有し、

前記薄膜トランジスタは半導体層、ゲート絶縁膜、及びゲート電極を有し、

前記ゲート配線は、銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金でなり、

前記薄膜トランジスタの前記ゲート電極は前記ゲート配線と電気的に接続していることを特徴とする半導体装置。

【請求項7】

40

絶縁表面を有する基板と、

前記基板上の第1の絶縁膜と、

前記第1の絶縁膜に埋め込まれた電源供給線と、

前記第1の絶縁膜及び前記電源供給線上の第2の絶縁膜と、

前記第2の絶縁膜上の薄膜トランジスタとを有し、

前記薄膜トランジスタは、ソース領域及びドレイン領域を有する半導体層、ゲート絶縁膜、並びにゲート電極を有し、

前記電源供給線は、銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金でなり、

前記薄膜トランジスタの前記ソース領域は前記電源供給線と電気的に接続していることを特徴とする半導体装置。

【請求項8】

50

請求項1乃至請求項7のいずれか一において、

前記基板上に形成され、第1の電極、有機化合物を含む層、第2の電極を順に積層してなる発光素子と、前記基板に貼り合わされた、前記発光素子を封止する封止基板とを有することを特徴とする半導体装置。

【請求項9】

請求項8において、前記有機化合物を含む層は白色発光する材料であり、前記封止基板に設けられたカラーフィルタと組み合わせたことを特徴とする半導体装置。

【請求項10】

請求項8において、前記有機化合物を含む層は単色発光する材料であり、前記封止基板に設けられた色変換層または着色層と組み合わせたことを特徴とする半導体装置。

【請求項11】

請求項1乃至請求項10のいずれか一において、前記半導体装置は、ディスプレイ、DVDプレーヤー、電子遊技機器、またはパーソナルコンピュータであることを特徴とする半導体装置。

【請求項12】

請求項1乃至請求項10のいずれか一において、前記半導体装置は発光装置であることを特徴とする半導体装置。

【請求項13】

請求項1乃至請求項7のいずれか一において、前記半導体装置は液晶表示装置であることを特徴とする半導体装置。

【請求項14】

絶縁表面上に導電性を有するエッチングストッパー層を形成し、

前記エッチングストッパー層を覆う第1の絶縁膜を形成し、

前記第1の絶縁膜にエッチングを行い、前記エッチングストッパー層に達する開口を形成し、

前記開口にシードを形成し、

前記シードにメッキを行い、前記開口を覆う埋め込み配線を形成し、

平坦化処理を行い、前記第1の絶縁膜の上面と前記埋め込み配線の上面を平坦にし、

前記第1の絶縁膜及び前記埋め込み配線上にアルミニウムを含む第2の絶縁膜を形成し、

前記第2の絶縁膜上に第3の絶縁膜を形成し、

前記第3の絶縁膜上に、ソース領域及びドレイン領域を有する半導体層、ゲート絶縁膜並びにゲート電極を有する薄膜トランジスタを形成し、

前記ソース領域、前記ドレイン領域、または前記ゲート電極は、前記埋め込み配線と電気的に接続していることを特徴とする半導体装置の作製方法。

【請求項15】

請求項14において、前記埋め込み配線は、ソース配線、ゲート配線または電源供給線であること特徴とする半導体装置の作製方法。

【請求項16】

請求項14または請求項15において、前記埋め込み配線は、銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金であることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示装置に代表される電気光学装置やOLEDを有する発光装置を部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【0003】

10

20

30

40

50

### 【従来の技術】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。

### 【0004】

従来より、画像表示装置として液晶表示装置が知られている。パッシブ型の液晶表示装置に比べ高精細な画像が得られることからアクティブマトリクス型の液晶表示装置が多く用いられるようになっている。アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

10

### 【0005】

また、OLEDを用いた発光装置にとって、TFTはアクティブマトリクス駆動方式を実現する上で、必須の素子となっている。従って、OLEDを用いた発光装置は、少なくとも、スイッチング素子として機能するTFTと、OLEDに電流を供給するTFTとが、各画素に設けられることになる。薄型軽量、高速応答性、直流低電圧駆動などの特徴を有する有機化合物を発光体として用いた発光素子は、次世代のフラットパネルディスプレイへの応用が期待されている。特に、発光素子をマトリクス状に配置した表示装置は、従来の液晶表示装置と比較して、視野角が広く視認性が優れる点に優位性があると考えられている。

20

### 【0006】

発光素子の発光機構は、一対の電極間に有機化合物層を挟んで電圧を印加することにより、陰極から注入された電子および陽極から注入された正孔が有機化合物層中の発光中心で再結合して分子励起子を形成し、その分子励起子が基底状態に戻る際にエネルギーを放出して発光するといわれている。励起状態には一重項励起と三重項励起が知られ、発光はどちらの励起状態を経ても可能であると考えられている。

### 【0007】

このような発光素子をマトリクス状に配置して形成された発光装置には、パッシブマトリクス駆動（単純マトリクス型）とアクティブマトリクス駆動（アクティブマトリクス型）といった駆動方法を用いることが可能である。しかし、画素密度が増えた場合には、画素（又は1ドット）毎にスイッチが設けられているアクティブマトリクス型の方が低電圧駆動できるので有利であると考えられている。

30

### 【0008】

このようなアクティブマトリクス型の表示装置（代表的には液晶表示装置および発光表示装置）の用途は広がっており、画面サイズの大面積化とともに高精細化や高開口率化や高信頼性の要求が高まっている。また、同時に生産性の向上や低コスト化の要求も高まっている。

### 【0009】

40

#### 【発明が解決しようとする課題】

従来、上記TFTのゲート配線材料としてアルミニウムを用いてTFTを作製した場合、熱処理によってヒロックやウィスカー等の突起物の形成や、アルミニウム原子のチャネル形成領域への拡散により、TFTの動作不良やTFT特性の低下を引き起こしていた。そこで、熱処理に耐え得る金属材料、代表的には高い融点を有している金属元素を用いた場合、画面サイズが大面積化すると配線抵抗が高くなる等の問題が発生し、消費電力の増大等を引き起こしていた。

### 【0010】

そこで、本発明は、大画面化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供することを課題としている。

50

## 【0011】

## 【課題を解決するための手段】

上記問題点を解決するため本発明は、絶縁層を形成し、該絶縁層に埋め込み配線 (Cu、Au、Ag、Ni、クロム、パラジウム、ロジウム、錫、鉛またはこれらの合金など) を形成し、さらに該絶縁層の表面を平坦化した後、露出する部分に金属保護膜 (Ti、TiN、Ta、TaNなど) を形成し、この埋め込み配線を発光装置または液晶表示装置の各種配線 (ゲート配線、ソース配線、電源供給線、コモン配線など) の一部に使用することによって配線の低抵抗化を図るものである。本発明により、画面サイズが大面積化しても低消費電力を実現することができる。

## 【0012】

10

本明細書で開示する発明の構成は、図1にその一例を示すように、

絶縁表面を有する第1の基板と透光性を有する第2の基板との間に、第1の電極と、該第1の電極上に接する有機化合物を含む層と、該有機化合物を含む層上に接する第2の電極とを有する発光素子を複数有する画素部と、薄膜トランジスタを有する駆動回路とを有する発光装置であって、

前記画素部に配置されるゲート配線、ソース配線、または電源供給線は、埋め込み配線であることを特徴とする発光装置である。

## 【0013】

20

上記構成において、前記埋め込み配線は、メッキ処理可能な銅、銀、金、またはこれらの合金であることを特徴としている。また、前記埋め込み配線は、前記薄膜トランジスタの下層に設けられる。

## 【0014】

また、上記構成において、前記有機化合物を含む層は白色発光する材料であり、前記第2の基板に設けられたカラーフィルタと組み合わせたことを特徴としている。或いは、前記有機化合物を含む層は単色発光する材料であり、前記第2の基板に設けられた色変換層または着色層と組み合わせたことを特徴としている。

## 【0015】

また、上記構造を実現するための発明の構成は、

絶縁表面上に導電性を有するエッチングストッパー層を形成する第1の工程と、

前記エッチングストッパー層を覆う第1の絶縁膜を形成する第2の工程と、

30

前記第1の絶縁膜にエッチングを行い、前記エッチングストッパー層に達する開口を形成する第3の工程と、

シードを形成してメッキを行い、前記開口を覆う埋め込み配線を形成する第4の工程と、平坦化処理を行う第5の工程と、

アルミニウムを含む第2の絶縁膜を形成する第6の工程と、

前記第2の絶縁膜上に第3の絶縁膜を形成する第7の工程と、

前記第3の絶縁膜上に半導体層を形成する第8の工程と、

前記半導体層上に第4の絶縁膜を形成する第9の工程と、

前記第4の絶縁膜上にゲート電極を形成する第10の工程と、

前記半導体層と接続する配線、および前記埋め込み配線と接続する配線を形成する第11の工程と、

40

第1の電極を形成する第12の工程と、

前記第1の電極上に有機化合物を含む層と、該有機化合物を含む層上に第2の電極を形成する第13の工程と、を有することを特徴とする発光装置の作製方法である。

## 【0016】

また、上記作製方法に関する構成において、前記埋め込み配線は電源供給線であることを特徴としている。

## 【0017】

また、上記作製方法に関する構成において、前記埋め込み配線は、銅、銀、金、またはこれらの合金であることを特徴としている。

50

## 【0018】

また、上記各作製方法に関する構成において、エッチングストッパー層をシードとしてメッキを行ってもよい。

## 【0019】

また、他の発明の構成は、図12に示すように、

絶縁表面を有する第1の基板と透光性を有する第2の基板との間に、第1の電極と、第2の電極と、これらの電極に挟まれた液晶材料とを有する画素部と、薄膜トランジスタを有する駆動回路とを有する液晶表示装置であって、

前記画素部に配置されるゲート配線、またはソース配線は、埋め込み配線であることを特徴とする液晶表示装置である。

10

## 【0020】

また、上記構成において、前記埋め込み配線は、銅、銀、金、またはこれらの合金であることを特徴としている。また、上記構成において、前記埋め込み配線は、前記薄膜トランジスタの下層に設けられる。

## 【0021】

また、上記構造を実現するための発明の構成は、

絶縁表面上に導電性を有するエッチングストッパー層を形成する第1の工程と、

前記エッチングストッパー層を覆う第1の絶縁膜を形成する第2の工程と、

前記第1の絶縁膜にエッチングを行い、前記エッチングストッパー層に達する開口を形成する第3の工程と、

20

シードを形成してメッキを行い、前記開口を覆う埋め込み配線を形成する第4の工程と、平坦化処理を行う第5の工程と、

アルミニウムを含む第2の絶縁膜を形成する第6の工程と、

前記第2の絶縁膜上に第3の絶縁膜を形成する第7の工程と、

前記第3の絶縁膜上に半導体層を形成する第8の工程と、

前記半導体層上に第4の絶縁膜を形成する第9の工程と、

前記第4の絶縁膜上にゲート電極を形成する第10の工程と、

前記半導体層と接続するソース配線、および前記埋め込み配線と前記ゲート電極とを接続する配線を形成する第11の工程と、

を有することを特徴とする液晶表示装置の作製方法である。

30

## 【0022】

また、上記作製方法に関する構成において、前記埋め込み配線はゲート配線であることを特徴としている。また、上記作製方法に関する構成において、前記埋め込み配線は、銅、銀、金、またはこれらの合金であることを特徴としている。

## 【0023】

なお、発光素子（EL素子）は、電場を加えることで発生するルミネッセンス（Electro Luminescence）が得られる有機化合物を含む層（以下、EL層と記す）と、陽極と、陰極とを有する。有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光（蛍光）と三重項励起状態から基底状態に戻る際の発光（リン光）とがあるが、本発明により作製される発光装置は、どちらの発光を用いた場合にも適用可能である。

40

## 【0024】

有機化合物を含む層は積層構造となっている。代表的には、陽極上に正孔輸送層／発光層／電子輸送層という積層構造が挙げられる。この構造は非常に発光効率が高く、現在、研究開発が進められている発光装置は殆どこの構造を採用している。また、他にも陽極上に正孔注入層／正孔輸送層／発光層／電子輸送層、または正孔注入層／正孔輸送層／発光層／電子輸送層／電子注入層の順に積層する構造も良い。発光層に対して蛍光性色素等をドーピングしても良い。また、これらの層は、全て低分子系の材料を用いて形成しても良いし、全て高分子系の材料を用いて形成しても良い。なお、本明細書において、陰極と陽極との間に設けられる全ての層を総称して有機化合物を含む層（EL層）という。したがって、上記正孔注入層、正孔輸送層、発光層、電子輸送層及び電子注入層は、全てEL層に

50

含まれる。また、有機化合物を含む層（E L層）は、シリコンなどの無機材料をも含んでいてよい。

【0025】

また、本発明の発光装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0026】

【発明の実施の形態】

本発明の実施形態について、以下に説明する。

【0027】

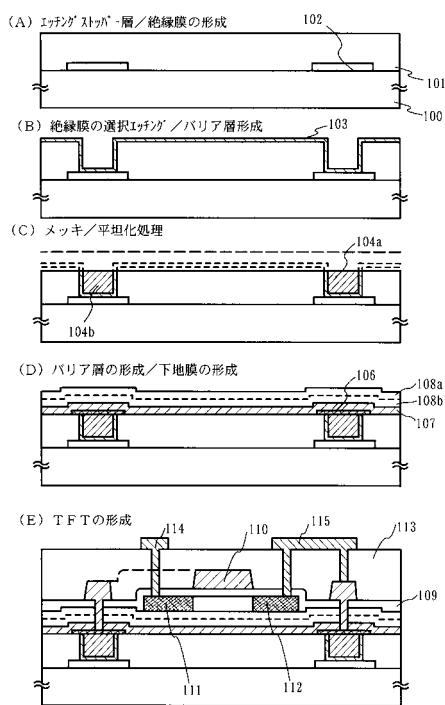

ここでは、埋め込み配線とTFTとを形成する例を図1に示す。

【0028】

まず、絶縁表面を有する基板100上にエッチングストッパー層102を形成する。エッチングストッパー層102としては、Ni、Ti、W、WSi<sub>x</sub>、Al、Mo、Ta、Cr、またはMoから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料を主成分とする膜またはそれらの積層膜を用いればよい。このエッチングストッパー層102は、後に行う電解メッキ処理のシード層（メッキ法での陰極）にもすることができる。次いで、エッチングストッパー層102を覆う珪素を主成分とする絶縁膜101を形成する。（図1（A））

【0029】

次いで、パターニングを行い、絶縁膜101を選択的にエッチングして、エッチングストッパー層102に達する開口（溝）を形成する。次いで、第1のバリア層103を形成した後、電解メッキ処理を行って開口（溝）に十分な厚みの低抵抗金属膜を形成する。電解メッキ処理は、メッキ法により形成しようとする金属イオンを含む水溶液中に直流電流を流し、陰極面に金属膜を形成する方法である。メッキされる金属としては、電気抵抗が低い材料、例えば銅、銀、金、クロム、鉄、ニッケル、白金、またはこれらの合金などを用いることができる。電解メッキ処理において形成される金属膜の膜厚は電流密度と時間を制御することにより実施者が適宜設定することができる。銅の電気抵抗は非常に低いため、ここでは低抵抗金属膜として電解メッキが可能な銅（Cu）を用いる例を示す。なお、メッキを行う前にシードを形成することが望ましい。また、第1のバリア層103は、酸化珪素を主成分とする絶縁膜中の拡散が速い銅の拡散防止層、即ちバリアメタルであり、比抵抗値が300～500μcm程度以下である金属材料（WN<sub>x</sub>、Ta<sub>N<sub>x</sub></sub>、TiSi<sub>x</sub>N<sub>y</sub>、WSi<sub>x</sub>N<sub>y</sub>、TaSi<sub>x</sub>N<sub>y</sub>など）を用いることが好ましい。また、銅は、酸化珪素を主成分とする絶縁膜との密着性が悪いため、密着性の良好な第1のバリア層103を形成することは有用である。

【0030】

次いで、化学機械研磨法（以下、CMP法と呼ぶ）などで代表される平坦化処理を行うことによって、開口（溝）だけに銅と第1のバリア層を残し、不要な部分を除去して埋め込み型の配線（以下、埋め込み配線と呼ぶ）104a、104bを形成する。（図1（B））

【0031】

次いで、露出した銅の耐酸化性を高めるため、第2のバリア層106を形成する。また、第2のバリア層106は、酸化珪素を主成分とする絶縁膜中の拡散が速い銅の拡散防止層としても有用であり、窒化珪素膜、または金属材料（TiN、NbN、WN<sub>x</sub>、Ta<sub>N<sub>x</sub></sub>、TiSi<sub>x</sub>N<sub>y</sub>、WSi<sub>x</sub>N<sub>y</sub>、TaSi<sub>x</sub>N<sub>y</sub>など）を用いることが好ましい。また、銅は、酸化珪素を主成分とする絶縁膜との密着性が悪いため、密着性の良好な第2のバリア層106を形成することは有用である。

【0032】

10

20

30

40

50

次いで、後に形成されるTFTへの不純物拡散を防止する下地絶縁膜として、 $\text{AlN}_x\text{O}_y$ で示される層107を形成する。 $\text{AlN}_x\text{O}_y$ で示される層107は、AlNまたはAlからなるターゲットを用いたRFスパッタ法により、前記ガス導入系から酸素または窒素または希ガスを導入して成膜すればよい。 $\text{AlN}_x\text{O}_y$ で示される層中に窒素を数atm%以上、好ましくは2.5atm%~47.5atm%含む範囲であればよく、酸素を47.5atm%以下、好ましくは、0.01~20atm%未満であればよい。

#### 【0033】

次いで、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜の積層からなる下地絶縁膜108を形成する。ここでは下地絶縁膜108として2層構造を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。下地絶縁膜の一層目108aとしては、プラズマCVD法を用い、 $\text{SiH}_4$ 、 $\text{NH}_3$ 、及び $\text{N}_2\text{O}$ を反応ガスとして成膜される酸化窒化シリコン膜を10~200nm(好ましくは50~100nm)形成する。ここでは、膜厚50nmの酸化窒化シリコン膜(組成比Si=32%、O=27%、N=24%、H=17%)を形成する。次いで、下地絶縁膜の二層目108bとしては、プラズマCVD法を用い、 $\text{SiH}_4$ 及び $\text{N}_2\text{O}$ を反応ガスとして成膜される酸化窒化シリコン膜を50~200nm(好ましくは100~150nm)の厚さに積層形成する。ここでは、膜厚100nmの酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)を形成する。(図1(C))

#### 【0034】

次いで、下地膜上に半導体層を形成する。半導体層は、非晶質構造を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜した後、公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を所望の形状にパターニングして形成する。この半導体層の厚さは25~80nm(好ましくは30~60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム合金などで形成すると良い。

#### 【0035】

また、レーザー結晶化法で結晶質半導体膜を作製する場合には、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、 $\text{YVO}_4$ レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数30Hzとし、レーザーエネルギー密度を100~400mJ/cm<sup>2</sup>(代表的には200~300mJ/cm<sup>2</sup>)とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数1~10kHzとし、レーザーエネルギー密度を300~600mJ/cm<sup>2</sup>(代表的には350~500mJ/cm<sup>2</sup>)とすると良い。そして幅100~1000μm、例えば400μmで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を80~98%として行えばよい。

#### 【0036】

次いで、半導体層の表面をフッ酸を含むエッチャントで洗浄し、半導体層を覆うゲート絶縁膜109を形成する。ゲート絶縁膜109はプラズマCVD法またはスパッタ法を用い、厚さを40~150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、プラズマCVD法により115nmの厚さで酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成する。勿論、ゲート絶縁膜は酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

#### 【0037】

次いで、ゲート絶縁膜109の表面を洗浄した後、ゲート電極110または接続電極を形成する。また、ゲート電極110を形成する前に、埋め込み配線104a、104bに達するコンタクトホールを形成して埋め込み配線104bに接するゲート電極110、また

10

20

30

40

50

は埋め込み配線 104a に接する接続電極を形成して電気的な接続を行う。

【0038】

次いで、半導体に p 型を付与する不純物元素（B など）、ここではボロンを適宜添加して、ソース領域 111 及びドレイン領域 112 を形成する。添加した後、不純物元素を活性化するために加熱処理、強光の照射、またはレーザー光の照射を行う。また、活性化と同時にゲート絶縁膜へのプラズマダメージやゲート絶縁膜と半導体層との界面へのプラズマダメージを回復することができる。特に、室温～300 の雰囲気中において、表面または裏面から YAG レーザーの第 2 高調波を照射して不純物元素を活性化させることは非常に有効である。YAG レーザーはメンテナンスが少ないため好ましい活性化手段である。

【0039】

以降の工程は、有機材料または無機材料からなる層間絶縁膜 113 を形成し、水素化を行った後、ソース領域、ドレイン領域、または接続電極に達するコンタクトホールを形成する。次いで、ソース電極（配線）115、ドレイン電極 114 を形成して埋め込み配線を有する TFT（p チャネル型 TFT）を完成させる。（図 1（E））ここではゲート電極と同時に形成される接続電極を介して埋め込み配線とドレイン電極 114 との接続を行った例を示したが、接続電極を用いずに埋め込み配線に達するコンタクトホールを形成した後、ドレイン電極を形成してもよい。

【0040】

以上の工程により得られる埋め込み配線 104a、104b を有する TFT は、様々な半導体装置、例えば、図 2 に示すような発光装置の TFT（電流制御用 TFT）や図 12 に示すような液晶表示装置の画素 TFT に用いることができる。

【0041】

なお、ここでは、ゲート電極と接続している埋め込み配線 104b と、ドレイン電極に接続している埋め込み配線 104a とを図示したが特に限定されず、様々な配線、例えばソース配線、引き出し配線、電源供給線、容量配線などに用いて配線の低抵抗化を図ることができる。

【0042】

また、本発明は図 1（E）の TFT 構造に限定されず、必要があればチャネル形成領域とドレイン領域（またはソース領域）との間に LDD 領域を有する低濃度ドレイン（LDD：Lightly Doped Drain）構造としてもよい。この構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域を LDD 領域と呼んでいる。さらにゲート絶縁膜を介して LDD 領域をゲート電極と重ねて配置させた、いわゆる GOLD（Gate-drain Overlapped LDD）構造としてもよい。

【0043】

また、ここでは p チャネル型 TFT を用いて説明したが、p 型不純物元素に代えて n 型不純物元素（P、As 等）を用いることによって n チャネル型 TFT を形成することができることは言うまでもない。

【0044】

また、ここではトップゲート型 TFT を例として説明したが、TFT 構造に関係なく本発明を適用することが可能であり、例えばボトムゲート型（逆スタガ型）TFT や順スタガ型 TFT に適用することが可能である。

【0045】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

【0046】

（実施例）

[実施例 1]

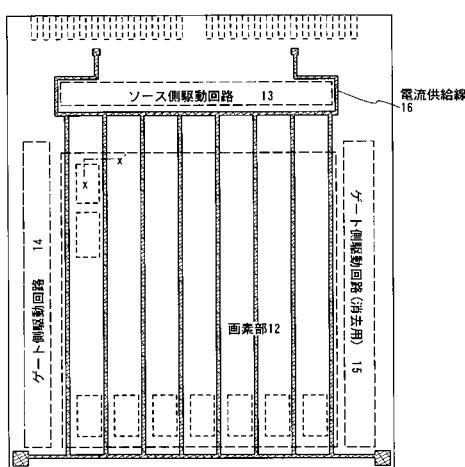

本実施例では、発光装置の電源供給線の主要部を埋め込み配線とする例を図 3～図 6 に示す。

10

20

30

40

50

## 【0047】

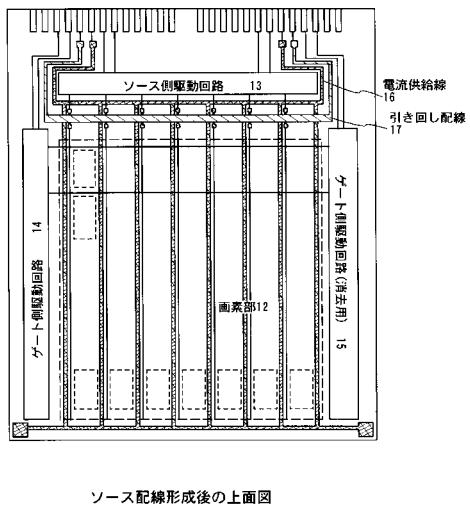

まず、上記実施の形態に従って、絶縁表面を有する基板上にエッチングストッパー層、該エッチングストッパー層を覆う珪素を主成分とする絶縁膜を形成し、該絶縁膜を選択的にエッチングして、エッチングストッパー層に達する開口（溝）を形成し、第1のバリア層を形成した後、電解メッキ処理を行って開口（溝）に十分な厚みの低抵抗金属膜を形成する。次いで、化学機械研磨法（以下、C M P法と呼ぶ）などで代表される平坦化処理を行い、開口（溝）だけに銅と第1のバリア層を残し、不要な部分を除去して埋め込み型の配線を形成する。この段階での上面図が図3に示した図であり、点線x-x'で切断した断面図が図1(C)に相当する。図3において、12は画素部、13はソース側駆動回路、14、15はゲート側駆動回路が配置される領域を示している。図3に示すように、電源供給線16の端部には電解メッキ処理を行う際に外部電源から電流を流すための接続電極パッドが基板の角に設けられている。なお、本実施例では、単色の発光素子をマトリクス状に配置する例とするため、電源供給線16は各画素に共通とし、全て導電位となるようにパターンが繋げられている。10

## 【0048】

なお、簡略化のために電源供給線16は8本しか示していないが、実際は、m×n（m行n列）個の画素数を有している場合、電源供給線は、m本、もしくは電解メッキの均一性を上げるための予備配線を1、2本追加した本数となる。

## 【0049】

次いで、露出した銅の耐酸化性を高めるため、第2のバリア層を形成し、さらに下地絶縁膜として、Al<sub>x</sub>N<sub>y</sub>で示される層を形成した後、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜の積層からなる下地絶縁膜を形成する。次いで、結晶質半導体膜を所望の形状にパターニングして半導体層を形成し、該半導体層を覆うゲート絶縁膜を形成する。20

## 【0050】

次いで、埋め込み配線に達するコンタクトホールを形成した後、ゲート絶縁膜上にゲート配線、端子電極、および引き回し電極を形成する。この引き回し電極は、ソース側駆動回路13と画素部12との間に設け、後に形成するソース配線が引き回し配線（発光素子の陰極または陽極と接続する配線）17と重ならないように配置する電極である。また、端子電極は基板の端部に複数設け、そのうちのいくつかは埋め込み配線である電源供給線と接続させる。この段階での上面図が図4に示した図である。30

## 【0051】

次いで、半導体にp型を付与する不純物元素（Bなど）またはn型を付与する不純物元素（P、As等）を適宜添加して、ソース領域及びドレイン領域を形成する。次いで、添加した不純物元素を活性化するために加熱処理、強光の照射、またはレーザー光の照射を行う。次いで、層間絶縁膜を形成し、水素化を行った後、ソース領域、ドレイン領域、引き回し電極、端子電極、または埋め込み配線に達するコンタクトホールを形成する。

## 【0052】

次いで、ソース電極（配線）、ドレイン電極、または接続電極を形成して各種TFTを完成させる。以上の工程が終了した段階で、画素部12においては、ソース領域と電源供給線とが電気的に接続され、ドレイン領域と接する接続電極（ここでは図示しない）が形成される。また、駆動回路においては、ソース領域に接するソース電極（配線）、ドレイン領域に接するドレイン電極が形成される。また、端子部においては、ある端子電極と接するソース配線、他の端子電極と接する引き回し配線（発光素子の陰極または陽極と接続する配線）17が形成される。また、駆動回路と画素部の間には、引き回し配線（発光素子の陰極または陽極と接続する配線）17が設けられる。この段階での上面図が図5に示した図である。40

## 【0053】

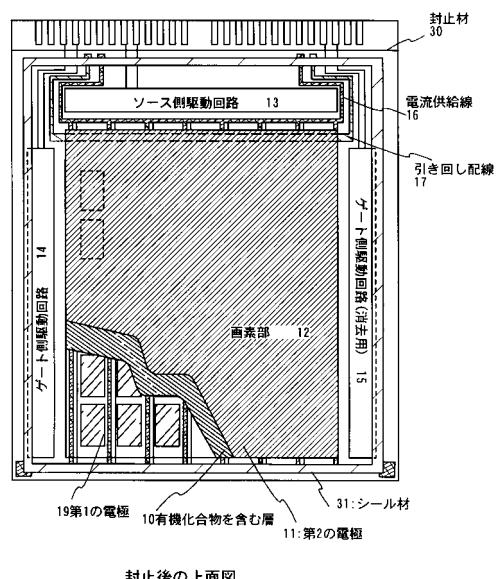

次いで、画素部において、ドレイン領域と接する接続電極に接する第1の電極19をマトリクス状に配置する。この第1の電極19は、発光素子の陽極、或いは陰極となる。次い50

で、第1の電極19の端部を覆う絶縁物（バンク、隔壁、障壁、土手などと呼ばれる）を形成する。次いで、画素部に有機化合物を含む層10を形成し、その上に第2の電極11を形成して発光素子を完成させる。この第2の電極11は、発光素子の陰極、或いは陽極となる。なお、画素部とソース側駆動回路の間の領域で第2の電極11が、引き回し配線17と接して電気的接続させる。

#### 【0054】

次いで、シール材31で基板と封止材（ここでは透光性を有する基板）30とを貼り合せる。この段階での上面図が図6に示した図である。さらに、外気を遮断するため、第2の電極11上に窒化シリコン膜、酸化窒化シリコン膜、またはDLC（ダイヤモンドライカーボン）膜からなる保護膜を形成してもよい。最後に、端子電極に外部回路と接続するためのFPC（フレキシブルプリントサーキット）を貼り付ける。

10

#### 【0055】

以上の工程でアクティブマトリクス型発光装置が完成する。

#### 【0056】

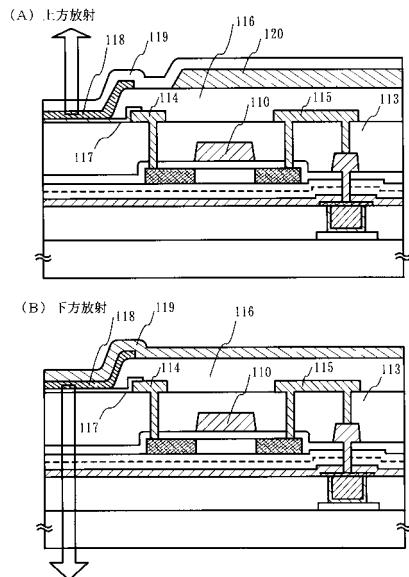

なお、TFTを有するアクティブマトリクス型発光装置は、光の放射方向で2通りの構造が考えられる。一つは、発光素子からの発光が第2の電極を透過して放射されて観測者の目に入る構造である。この場合、観測者は第2の電極側から画像を認識することができる。もう一つは、発光素子からの発光が第1の電極および基板を透過して放射されて観測者の目に入る構造である。

20

#### 【0057】

図2(A)に示すように発光素子からの発光が第2の電極を透過して放射されて観測者の目に入る構造とする場合、第2の電極11（図2(A)における電極119）は透光性を有する材料を用いることが望ましい。

#### 【0058】

例えば、第1の電極19（図2(A)における電極117）を陽極とする場合、第1の電極19の材料として、仕事関数の大きい金属（Pt、Cr、W、Ni、Zn、Sn、In）を用い、端部を絶縁物（バンク、隔壁、障壁、土手などと呼ばれる）116で覆った後、正孔注入層として作用するポリ（エチレンジオキシチオフェン）/ポリ（スチレンスルホン酸）水溶液（PEDOT/PSS）を全面に塗布、焼成した後、発光層として作用する発光中心色素（1,1,4,4-テトラフェニル-1,3-ブタジエン（TPB）、4-ジシアノメチレン-2-メチル-6-（p-ジメチルアミノ-スチリル）-4H-ピラン（DCM1）、ナイルレッド、クマリン6など）ドープしたポリビニルカルバゾール（PVK）溶液を全面に塗布、焼成した後、仕事関数の小さい金属（Li、Mg、Cs）を含む薄膜と、その上に積層した透明導電膜（ITO（酸化インジウム酸化スズ合金）、酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub> ZnO）、酸化亜鉛（ZnO）等）との積層からなる第2の電極11（図2(A)における電極119）を陰極として形成すればよい。なお、図2(A)においては、陰極の低抵抗化を図るために、絶縁物116上に補助電極120を設けている。こうして得られる発光素子は、白色発光を示す。なお、PEDOT/PSSは溶媒に水を用いており、有機溶剤には溶けない。従って、PVKをその上から塗布する場合にも、再溶解する心配はない。また、PEDOT/PSSとPVKは溶媒が異なるため、成膜室は同一のものを使用しないことが好ましい。なお、ここでは塗布により有機化合物を含む層10（図2(A)における118）を形成した例を示したが、特に限定されず、蒸着法により形成してもよい。

30

#### 【0059】

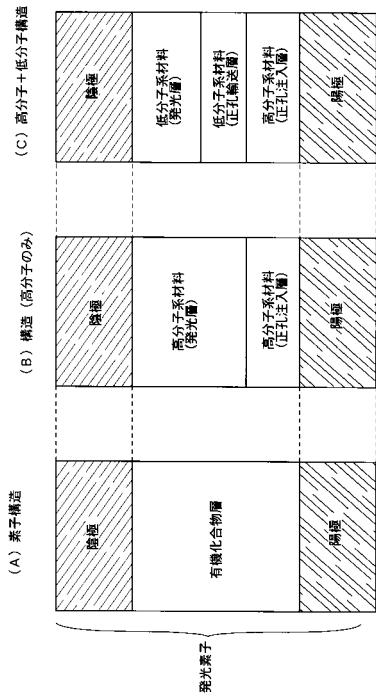

また、上記例では図7(B)に示すように有機化合物層を積層とした例を示したが図7(A)に示すように有機化合物層を単層とすることもできる。例えば、ホール輸送性のポリビニルカルバゾール（PVK）に電子輸送性の1,3,4-オキサジアゾール誘導体（PBD）を分散させてもよい。また、30wt%のPBDを電子輸送剤として分散し、4種類の色素（TPB、クマリン6、DCM1、ナイルレッド）を適量分散することで白色発光が得られる。また、図7(C)に示すように有機化合物層として高分子材料からなる

40

50

層と、低分子材料からなる層とを積層してもよい。

【0060】

なお、有機化合物膜は、陽極と陰極の間に形成されており、陽極から注入された正孔と陰極から注入された電子が有機化合物膜において再結合することにより、有機化合物膜において、白色発光が得られる。

【0061】

また、赤色発光する有機化合物膜や緑色発光する有機化合物膜や青色発光する有機化合物膜を適宜選択し、重ねて混色させることによって全体として白色発光を得ることも可能である。

【0062】

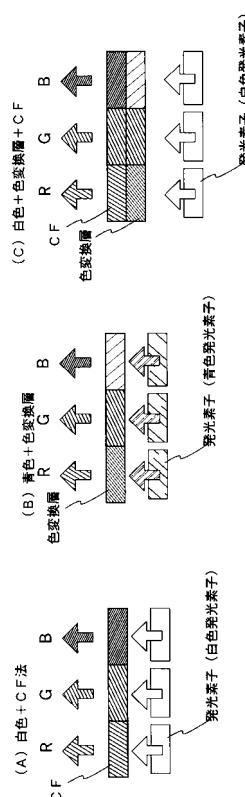

白色発光を示す発光素子を形成し、フルカラー表示とするには様々な方法がある。例えば、図8(A)に示すように、得られた白色発光をカラーフィルターに通すことで赤、緑、青の発光を得るという方式(以下、カラーフィルター法とよぶ)がある。

10

【0063】

上記有機化合物膜が白色発光する方向に赤色発光以外を吸収する着色層(R)、緑色発光以外を吸収する着色層(G)、青色発光以外を吸収する着色層(B)をそれぞれ設けたカラーフィルタを形成することにより、発光素子からの白色発光をそれぞれ分離して、赤色発光、緑色発光、青色発光として得ることができる。また、アクティブマトリクス型の場合には、基板とカラーフィルターの間にTFTが形成される構造となる。また、カラーフィルターにおいて各着色層の間には遮光層が設けられており、大画面化する場合には、この遮光層に乾燥剤を含ませることが好ましい。

20

【0064】

また、着色層(R, G, B)には、最も単純なストライプパターンをはじめとして、斜めモザイク配列、三角モザイク配列、RGBG四画素配列、もしくはRGBW四画素配列などを用いることができる。

【0065】

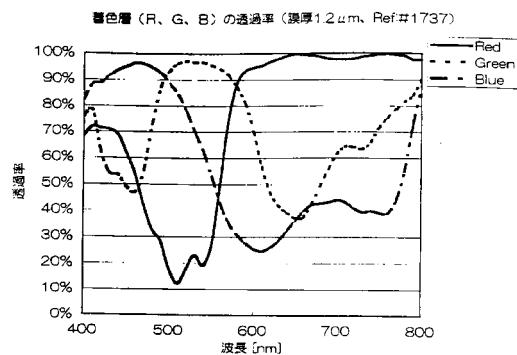

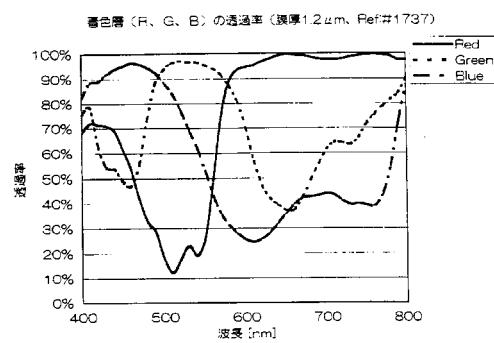

白色光源(D65)を用いて各着色層の透過率と波長との関係の一例を図9に示した。カラーフィルターを構成する着色層は、顔料を分散した有機感光材料からなるカラーレジストを用いて形成される。また、白色発光とカラーフィルタを組み合わせた場合の色再現範囲を色度座標として図10に示す。なお、白色発光の色度座標は(x, y) = (0.34, 0.35)である。図10よりフルカラーとしての色再現性は十分確保されていることが分かる。

30

【0066】

なお、この場合には、得られる発光色が異なっていても、すべて白色発光を示す有機化合物膜で形成されていることから、発光色ごとに有機化合物膜を塗り分けて形成する必要がない。また、鏡面反射を防ぐ円偏光板も特に必要なものとすることができる。

【0067】

次に青色発光性の有機化合物膜を有する青色発光素子と蛍光性の色変換層を組み合わせることにより実現されるCCM法(color changing mediums)について図8(B)により説明する。

40

【0068】

CCM法は、青色発光素子から出射された青色発光で蛍光性の色変換層を励起し、それぞれの色変換層で色変換を行う。具体的には色変換層で青色から赤色への変換(B-R)、色変換層で青色から緑色への変換(B-G)、色変換層で青色から青色への変換(B-B)(なお、青色から青色への変換は行わなくても良い。)を行い、赤色、緑色及び青色の発光を得るというものである。CCM法の場合にも、アクティブマトリクス型の場合には、基板と色変換層の間にTFTが形成される構造となる。

【0069】

なお、この場合にも有機化合物膜を塗り分けて形成する必要がない。また、鏡面反射を防ぐ円偏光板も特に必要なものとすることができる。

50

## 【0070】

また、CCM法を用いる場合には、色変換層が蛍光性であるため外光により励起され、コントラストを低下させる問題があるので、図8(C)に示したようにカラーフィルターを装着するなどしてコントラストを上げるようにすると良い。

## 【0071】

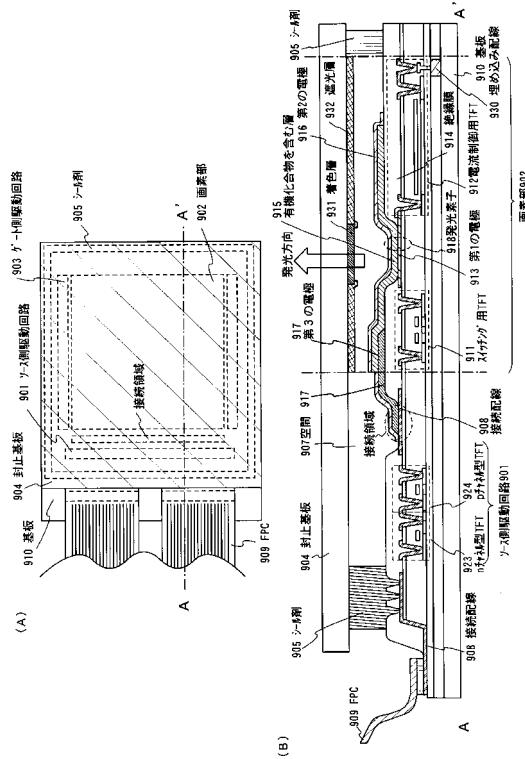

ここで、アクティブマトリクス型発光装置全体の外観図について図11に説明する。なお、図11(A)は、発光装置を示す上面図、図11(B)は図11(A)をA-A'で切断した断面図である。点線で示された901はソース信号線駆動回路、902は画素部、903はゲート信号線駆動回路である。また、904は封止基板、905はシール剤であり、シール剤905で囲まれた内側は、空間907になっている。

10

## 【0072】

なお、908はソース信号線駆動回路901及びゲート信号線駆動回路903に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)909からビデオ信号やクロック信号を受け取る。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基盤(PWB)が取り付けられても良い。本明細書における発光装置には、発光装置本体だけでなく、それにFPCもしくはPWBが取り付けられた状態をも含むものとする。

## 【0073】

次に、断面構造について図11(B)を用いて説明する。基板910上には駆動回路及び画素部が形成されているが、ここでは、駆動回路としてソース信号線駆動回路901と画素部902が示されている。

20

## 【0074】

なお、ソース信号線駆動回路901はnチャネル型TFT923とpチャネル型TFT924とを組み合わせたCMOS回路が形成される。また、駆動回路を形成するTFTは、公知のCMOS回路、PMOS回路もしくはNMOS回路で形成しても良い。また、本実施の形態では、基板上に駆動回路を形成したドライバー一体型を示すが、必ずしもその必要はなく、基板上ではなく外部に形成することもできる。

## 【0075】

また、画素部902はスイッチング用TFT911と、電流制御用TFT912とそのドレインに電気的に接続された第1の電極(陽極)913を含む複数の画素により形成される。電流制御用TFT912のソースには、埋め込み配線930が電気的に接続されている。

30

## 【0076】

また、第1の電極(陽極)913の両端には絶縁層914が形成され、第1の電極(陽極)913上には有機化合物を含む層915が形成される。さらに、有機化合物を含む層915上には第2の電極(陰極)916が形成される。これにより、第1の電極(陽極)912、有機化合物を含む層915、及び第2の電極(陰極)916からなる発光素子918が形成される。ここでは発光素子918は白色発光とする例であるので着色層931とBMM932からなるカラーフィルター(簡略化のため、ここではオーバーコート層は図示しない)が設けている。

40

## 【0077】

第2の電極(陰極)916は全画素に共通の配線としても機能し、接続配線908を経由してFPC909に電気的に接続されている。また、絶縁層914上には第3の電極(補助電極)が形成されており、第2の電極の低抵抗化を実現している。

## 【0078】

また、基板910上に形成された発光素子918を封止するためにシール剤905により封止基板904を貼り合わせる。なお、封止基板904と発光素子918との間隔を確保するために樹脂膜からなるスペーサを設けても良い。そして、シール剤905の内側の空間907には窒素等の不活性気体が充填されている。なお、シール剤905としてはエポキシ系樹脂を用いるのが好ましい。また、シール剤905はできるだけ水分や酸素を透過

50

しない材料であることが望ましい。さらに、空間 907 の内部に酸素や水を吸収する効果をもつ物質を含有させてても良い。

【0079】

また、本実施例では封止基板 904 を構成する材料としてガラス基板や石英基板の他、FRP (Fiberglass-Reinforced Plastics)、PVF (ポリビニルフロライド)、マイラー、ポリエステルまたはアクリル等からなるプラスチック基板を用いることができる。また、シール剤 905 を用いて封止基板 904 を接着した後、さらに側面 (露呈面) を覆うようにシール剤で封止することも可能である。

【0080】

以上のようにして発光素子を空間 907 に封入することにより、発光素子を外部から完全に遮断することができ、外部から水分や酸素といった有機化合物層の劣化を促す物質が侵入することを防ぐことができる。従って、信頼性の高い発光装置を得ることができる。

10

【0081】

一方、図 2 (B) に示すように発光素子からの発光が第 1 の電極および基板を透過して放射されて観測者の目に入る構造とする場合、第 1 の電極 19 (図 2 (A) における電極 117) は透光性を有する材料を用いることが望ましい。

【0082】

例えば、第 1 の電極 19 (図 2 (B) における電極 117) を陽極とする場合、第 1 の電極 19 の材料として、透明導電膜 (ITO (酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金 (In<sub>2</sub>O<sub>3</sub> ZnO)、酸化亜鉛 (ZnO) 等) を用い、端部を絶縁物 (パンク、隔壁、障壁、土手などと呼ばれる) 116 で覆った後、有機化合物を含む層 118 を形成し、その上に金属膜 (MgAg、MgIn、AlLi、CaF<sub>2</sub>、CaN などの合金、または周期表の 1 族もしくは 2 族に属する元素とアルミニウムとを共蒸着法により形成した膜) からなる第 2 の電極 11 (図 2 (B) における電極 119) を陰極として形成すればよい。陰極形成の際には蒸着による抵抗加熱法を用い、蒸着マスクを用いて選択的に形成すればよい。

20

【0083】

また、本実施例は実施の形態と自由に組み合わせることができる。

【0084】

【実施例 2】

30

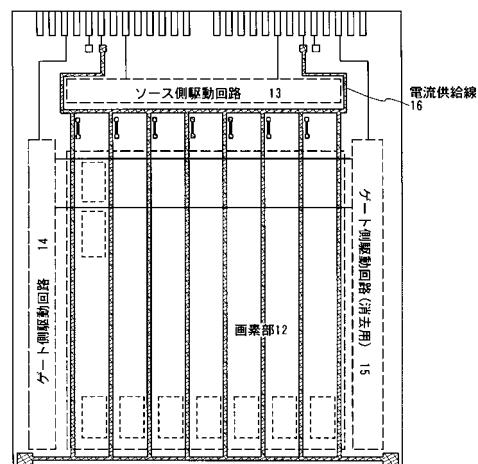

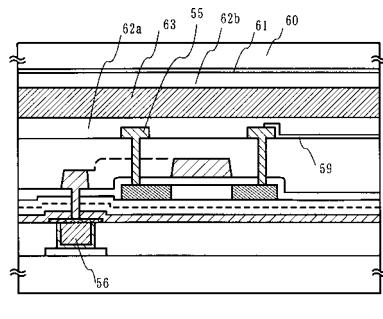

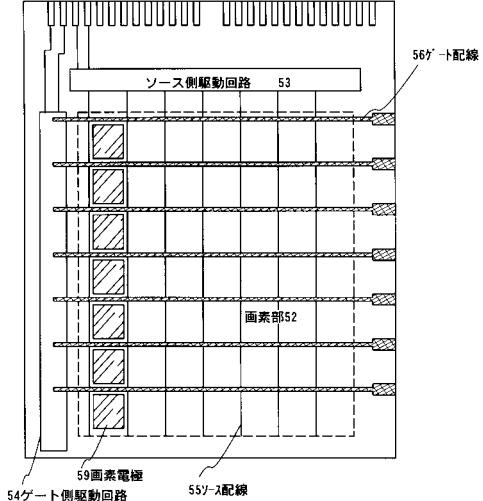

ここでは液晶表示装置のゲート配線の主要部を埋め込み配線とする例を図 12、図 13 に示す。

【0085】

まず、上記実施の形態に従って、絶縁表面を有する基板上にエッティングストッパー層、該エッティングストッパー層を覆う珪素を主成分とする絶縁膜を形成し、該絶縁膜を選択的にエッティングして、エッティングストッパー層に達する開口 (溝) を形成し、第 1 のバリア層を形成した後、電解メッキ処理を行って開口 (溝) に十分な厚みの低抵抗金属膜を形成する。次いで、化学機械研磨法 (以下、CMP 法と呼ぶ) などで代表される平坦化処理を行い、開口 (溝) だけに銅と第 1 のバリア層を残し、不要な部分を除去して埋め込み型の配線を形成する。

40

【0086】

次いで、露出した銅の耐酸化性を高めるため、第 2 のバリア層を形成し、さらに下地絶縁膜として、AlN<sub>x</sub>O<sub>y</sub> で示される層を形成した後、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜の積層からなる下地絶縁膜を形成する。次いで、結晶質半導体膜を所望の形状にパターニングして半導体層を形成し、該半導体層を覆うゲート絶縁膜を形成する。

【0087】

次いで、埋め込み配線に達するコンタクトホールを形成した後、ゲート絶縁膜上にゲート電極、端子電極を形成する。なお、ゲート電極は、埋め込み配線と接続されてゲート配線の低抵抗化が実現する。また、端子電極は基板の端部に複数設ける。

50

## 【0088】

次いで、半導体にp型を付与する不純物元素（Bなど）またはn型を付与する不純物元素（P、As等）を適宜添加して、ソース領域及びドレイン領域を形成する。次いで、添加した不純物元素を活性化するために加熱処理、強光の照射、またはレーザー光の照射を行う。次いで、層間絶縁膜を形成し、水素化を行った後、ソース領域、ドレイン領域、端子電極に達するコンタクトホールを形成する。

## 【0089】

次いで、ソース電極（配線）55、またはドレイン電極を形成して各種TFTを完成させる。以上の工程が終了した段階で、画素部52においては、それぞれドレイン領域とドレイン電極とが電気的に接続され、ソース領域とソース電極（配線）とが電気的に接続される。また、駆動回路においては、ソース領域に接するソース電極（配線）、ドレイン領域に接するドレイン電極が形成される。また、端子部においては、ある端子電極と接するソース配線が形成される。次いで、画素部において、ドレイン領域と接する接続電極に接する画素電極59をマトリクス状に配置する。この段階での上面図が図13に示した図である。図13において、52は画素部、53はソース側駆動回路、54はゲート側駆動回路が配置される領域を示している。図13に示すように、ゲート配線56の端部には電解メッキ処理を行う際に外部電源から電流を流すための接続電極パッドが基板の端面近傍に設けられている。なお、本実施例では、ゲート配線56と同じ本数に対応する接続電極パッドを設けている。また、ゲート配線を全て導電位となるようにパターンを繋げてメッキ処理を行った後、分断して個々のゲート配線を形成してもよい。

10

20

## 【0090】

次いで、配向膜62aを形成した後、ラビング処理を行う。次いで、シール材（図示しない）で基板と対向基板60とを貼り合せ、基板間に液晶材料63を注入した後、封止する。対向基板60には予め、透明導電膜からなる対向電極61と、ラビング処理が行われた配向膜62bとが設けられている。最後に、端子電極に外部回路と接続するためのFPC（フレキシブルプリントサーキット）を貼り付け、さらに偏光板やカラーフィルターを設ける。

## 【0091】

以上の工程でアクティブマトリクス型液晶表示装置が完成する。

30

## 【0092】

なお、TFTを有するアクティブマトリクス型液晶表示装置は、3通りの構造（透過型、反射型、半透過型）が考えられる。画素電極を透明導電膜とし、バックライトを設ける透過型と、画素電極を反射金属膜とし、外光を反射させる反射型と、画素電極の一部を透明導電膜とし、その他の部分を反射金属膜として適宜切り替えを行う半透過型とがあるが、本発明は、いずれの構造に適用することができる。

## 【0093】

また、本実施例は実施の形態と自由に組み合わせることができる。

## 【0094】

## [実施例3]

本発明を実施して形成された駆動回路や画素部は様々なモジュール（アクティブマトリクス型液晶モジュール、アクティブマトリクス型ECモジュール）を完成させることができる。即ち、本発明により、それらを表示部に組み込んだ電子機器全てを完成させることができる。

40

## 【0095】

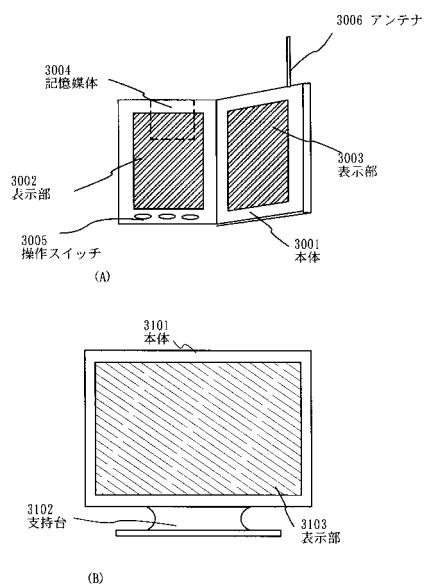

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、プロジェクタ、カーステレオ、パソコン用コンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図14、図15に示す。

## 【0096】

図14（A）はパソコン用コンピュータであり、本体2001、画像入力部2002、表

50

示部 2003、キーボード 2004 等を含む。

【0097】

図 14 (B) はモバイルコンピュータ (モービルコンピュータ) であり、本体 2201、カメラ部 2202、受像部 2203、操作スイッチ 2204、表示部 2205 等を含む。

【0098】

図 14 (C) はプログラムを記録した記録媒体 (以下、記録媒体と呼ぶ) を用いるプレーヤーであり、本体 2401、表示部 2402、スピーカ部 2403、記録媒体 2404、操作スイッチ 2405 等を含む。なお、このプレーヤーは記録媒体として DVD (Digital Versatile Disc)、CD 等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。

10

【0099】

図 15 (A) は携帯書籍 (電子書籍) であり、本体 3001、表示部 3002、3003、記憶媒体 3004、操作スイッチ 3005、アンテナ 3006 等を含む。

【0100】

図 15 (B) はディスプレイであり、本体 3101、支持台 3102、表示部 3103 等を含む。本発明は対角が 10 ~ 50 インチの表示部 3103 を完成させることができる。

【0101】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器を完成させることができが可能である。また、本実施例の電子機器は実施の形態、実施例 1、実施例 2 のどのような組み合わせからなる構成を用いても実現することができる。

20

【0102】

【発明の効果】

本発明により、アクティブマトリクス型の発光表示装置や液晶表示装置に代表される半導体装置において、画素部の面積が大きくなり大画面化しても良好な表示を実現することができる。画素部の配線の抵抗を大幅に低下させることができるために、例えば、対角 40 インチや対角 50 インチの大画面にも本発明は対応しうる。

【図面の簡単な説明】

【図 1】 本発明の工程を示す断面図。(実施の形態)

【図 2】 本発明の発光素子の断面を示す図。(実施例 1)

30

【図 3】 発光装置の作製過程における上面図を示す図。(実施例 1)

【図 4】 発光装置の作製過程における上面図を示す図。(実施例 1)

【図 5】 発光装置の作製過程における上面図を示す図。(実施例 1)

【図 6】 発光装置の作製過程における上面図を示す図。(実施例 1)

【図 7】 発光素子の積層構造を示す図。(実施例 1)

【図 8】 白色発光を用いてフルカラー化する場合の模式図である。(実施例 1)

【図 9】 着色層の透過率を示す図。(実施例 1)

【図 10】 色度座標を示す図。(実施例 1)

【図 11】 アクティブ型表示装置の断面図および上面図。(実施例 1)

【図 12】 液晶表示装置の断面図を示す図。(実施例 2)

【図 13】 液晶表示装置の作製過程における上面図を示す図。(実施例 2)

40

【図 14】 電子機器の一例を示す図。

【図 15】 電子機器の一例を示す図。

【図1】

【図2】

【図3】

埋め込み配線形成後の上面図

【図4】

ゲート配線形成後の上面図

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

液晶素子の断面

【図13】

【図14】

【図15】

---

フロントページの続き

| (51)Int.Cl. |                 | F I     |         |

|-------------|-----------------|---------|---------|

| H 0 1 L     | 23/52 (2006.01) | H 0 5 B | 33/12 E |

| H 0 5 B     | 33/12 (2006.01) | H 0 5 B | 33/14 A |

| H 0 1 L     | 51/50 (2006.01) |         |         |

(56)参考文献 特開平07-020489 (JP, A)

特開平10-209463 (JP, A)

特開平05-061067 (JP, A)

特開2001-249362 (JP, A)

特開平11-026394 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

G09F 9/30

G02B 5/20

G02F 1/1343

H01L 21/3205

H01L 23/52

H01L 29/786

H01L 51/50

H05B 33/12