(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2015-515225

(P2015-515225A)

(43) 公表日 平成27年5月21日(2015.5.21)

(51) Int.Cl.

HO4N 19/82

(2014.01)

F 1

HO4N 19/82

テーマコード(参考)

5C159

審査請求 未請求 予備審査請求 有 (全 51 頁)

(21) 出願番号 特願2015-507184 (P2015-507184)

(86) (22) 出願日 平成25年4月18日 (2013.4.18)

(85) 翻訳文提出日 平成26年10月20日 (2014.10.20)

(86) 國際出願番号 PCT/US2013/037206

(87) 國際公開番号 WO2013/158903

(87) 國際公開日 平成25年10月24日 (2013.10.24)

(31) 優先権主張番号 13/450,734

(32) 優先日 平成24年4月19日 (2012.4.19)

(33) 優先権主張国 米国(US)

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ボ・ジョウ

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】 加速されたビデオ圧縮マルチタップフィルタおよび双線形補間器

## (57) 【要約】

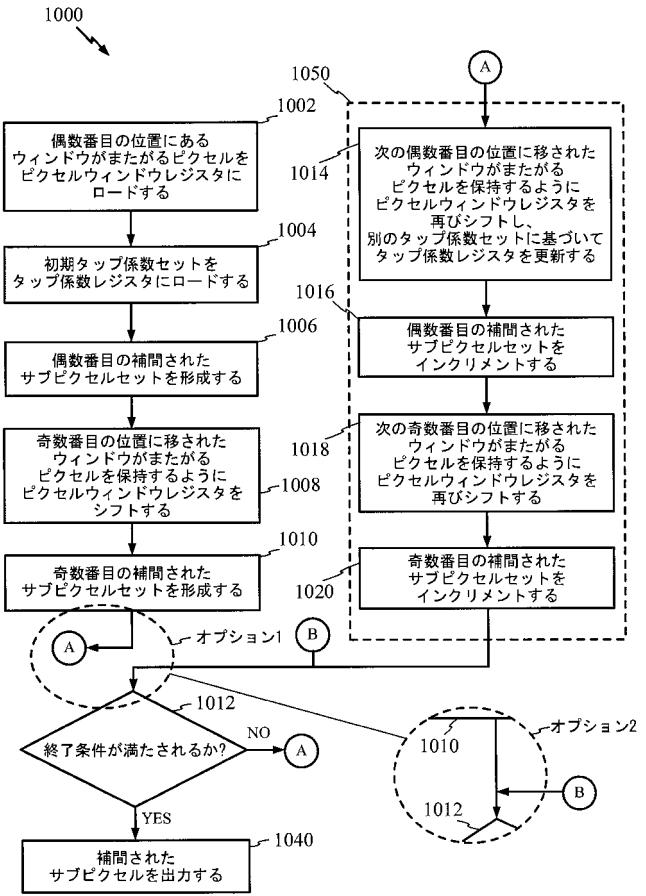

偶数番目の補間されたサブピクセルのセットが、ピクセルウィンドウと、タップ係数セットを有するタップ係数レジスタに基づいて形成され、ピクセルウィンドウがシフトされ、タップ係数レジスタを適用して、奇数番目の補間されたピクセルのセットが形成される。終了条件が満たされるまで、偶数番目の補間されたサブピクセルのセットおよび奇数番目の補間されたサブピクセルのセットが繰り返し累算される。累算するステップにおいて、タップ係数レジスタが、別のタップ係数セットによって更新され、ピクセルウィンドウがシフトされ、偶数番目の補間されたピクセルがインクリメントされ、ピクセルウィンドウが次いで再びシフトされ、奇数番目の補間されたピクセルがインクリメントされる。

FIG. 10

**【特許請求の範囲】**

**【請求項 1】**

ピクセルアレイに対する補間されたピクセルを生成するための方法であって、

前記ピクセルアレイからのピクセルのウィンドウレジスタと、所与のタップ係数セットを有するタップ係数レジスタとに基づいて、偶数番目の補間されたサブピクセルのセットを形成するステップと、

別の前記ピクセルによって前記ウィンドウレジスタを更新するステップと、

前記ウィンドウレジスタと前記タップ係数レジスタとに基づいて、奇数番目の補間されたサブピクセルのセットを形成するステップと、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するステップであって、各累算するステップが、

別のタップ係数セットに基づいて前記タップ係数レジスタを更新し、別の前記ピクセルによって前記ウィンドウレジスタを更新するステップと、

前記ウィンドウレジスタと前記タップ係数レジスタとに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントするステップと、

別の前記ピクセルによって前記ウィンドウレジスタを再び更新するステップと、

前記ウィンドウレジスタと前記タップ係数レジスタとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントするステップと

を含む、累算するステップと、

前記終了条件が満たされると、偶数番目の補間されたサブピクセルの前記セットおよび奇数番目の補間されたサブピクセルの前記セットを出力するステップとを含む、方法。

**【請求項 2】**

前記終了条件が、前記偶数番目の補間されたピクセルの少なくとも1つが6個の積の合計を有することに対応する、請求項1に記載の方法。

**【請求項 3】**

偶数番目の補間されたサブピクセルの前記セットを形成するステップが、単一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットを形成するステップが、単一のマシンサイクルの間に行われる、請求項1に記載の方法。

**【請求項 4】**

偶数番目の補間されたサブピクセルの前記セットを形成するステップが、4個の偶数番目の補間されたサブピクセルを含むように前記セットを形成し、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、奇数番目の補間されたサブピクセルの前記セットを形成するステップが、4個の奇数番目の補間されたサブピクセルを含むように前記セットを形成し、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する、請求項3に記載の方法。

**【請求項 5】**

前記偶数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の偶数番目の補間されたサブピクセルの各々をインクリメントするステップを含み、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含む、請求項4に記載の方法。

**【請求項 6】**

前記タップ係数レジスタを更新し、前記ウィンドウレジスタを更新するステップが、前記偶数番目の補間されたサブピクセルをインクリメントするステップと組み合わされて、単一のマシンサイクルの間に行われ、前記奇数番目の補間されたサブピクセルをインクリメントするステップと組み合わされた、前記ウィンドウレジスタを再び更新する前記ステップが、単一のマシンサイクルの間に行われる、請求項5に記載の方法。

**【請求項 7】**

10

20

30

40

50

前記偶数番目の補間されたサブピクセルを形成するステップが、少なくとも4個の偶数番目の補間されたサブピクセルを形成し、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、

前記奇数番目の補間されたサブピクセルを形成するステップが、少なくとも4個の奇数番目の補間されたサブピクセルを形成し、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有し、

前記偶数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の偶数番目の補間されたサブピクセルの各々をインクリメントするステップを含み、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含む、請求項1に記載の方法。 10

#### 【請求項 8】

前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを2回累算すると、前記終了条件が満たされる、請求項1に記載の方法。

#### 【請求項 9】

前記偶数番目の補間されたサブピクセルを形成するステップが、ウインドウからのピクセルを、前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを合計して積の合計のセットを生成するステップと、積の合計の前記セットを、偶数番目の補間されたサブピクセルの前記セットとして累算器へとロードするステップと、偶数番目の補間されたサブピクセルの前記セットを、累算器レジスタからメモリへとオフロードするステップとを含み、 20

前記奇数番目の補間されたサブピクセルを形成するステップが、前記更新されたウインドウからのピクセルを、前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを合計して積の合計のセットを生成するステップと、積の合計の前記セットを、奇数番目の補間されたサブピクセルの前記セットとして前記累算器へとロードするステップと、奇数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含む、請求項1に記載の方法。

#### 【請求項 10】

偶数番目の補間されたサブピクセルの前記セットを形成するステップが、单一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットを形成するステップが、单一のマシンサイクルの間に行われる、請求項9に記載の方法。 30

#### 【請求項 11】

前記偶数番目の補間されたサブピクセルをインクリメントする各ステップが、偶数番目の補間されたサブピクセルの前記セットを前記メモリから前記累算器レジスタへとロードするステップと、前記更新されたウインドウからのピクセルを、前記更新されたタップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを前記累算器レジスタからの対応する偶数番目の補間されたサブピクセルと合計して、累算された積の合計のセットを生成するステップと、累算された積の合計の前記セットを、偶数番目の補間されたサブピクセルの更新されたセットとして前記累算器レジスタへとロードするステップと、偶数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含み、 40

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、奇数番目の補間されたサブピクセルの前記セットを前記メモリから前記累算器レジスタへとロードするステップと、別の更新されたウインドウからのピクセルを、前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを前記累算器レジスタからの対応する奇数番目の補間されたサブピクセルと合計して、累算された積の合計のセットを生成するステップと、累算された積の合計の前記セットを、奇数番目の補間されたサブピクセルの更新されたセットとして前記累算器レジ 50

スタへとロードするステップと、奇数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含む、請求項9に記載の方法。

#### 【請求項 1 2】

偶数番目の補間されたサブピクセルの前記セットをインクリメントするステップが、单一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットをインクリメントするステップが、单一のマシンサイクルの間に行われる、請求項11に記載の方法。

#### 【請求項 1 3】

ピクセルアレイに対する補間されたピクセルを生成するための装置であって、

前記ピクセルアレイからのピクセルのウィンドウと、所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成するための手段と、

別の前記ピクセルによって前記ウィンドウを更新するための手段と、

ピクセルの前記ウィンドウと、前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成するための手段と、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するための手段であって、

前記タップ係数セットを更新して別の前記ピクセルによって前記ウィンドウを更新し

、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントし、

別の前記ピクセルによってピクセルの前記ウィンドウを更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントする

ように構成される、手段と、

前記所与の終了条件が満たされると、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力するための手段とを含む、装置。

#### 【請求項 1 4】

偶数番目の補間されたサブピクセルの前記セットを形成するための前記手段が、4個の偶数番目の補間されたサブピクセルを含むように前記セットを形成するように構成され、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、

30

奇数番目の補間されたサブピクセルの前記セットを形成するための前記手段が、4個の奇数番目の補間されたサブピクセルを含むように前記セットを形成するように構成され、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

。

#### 【請求項 1 5】

前記偶数番目のサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するための前記手段が、前記4個の偶数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントすることによって、前記偶数番目の補間されたサブピクセルをインクリメントし、前記4個の奇数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントすることによって、前記奇数番目の補間されたサブピクセルをインクリメントするように構成される、請求項14に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

40

#### 【請求項 1 6】

少なくとも1つの半導体ダイにおいて集積される、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 1 7】

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコン

10

20

30

40

50

ピュータからなる群から選択されるデバイスをさらに含み、前記デバイスに前記装置が組み込まれる、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 18】

ワイヤレス通信システム中のプロセッサ装置によって実行されると、プロセッサ装置に、ピクセルアレイに対する補間されたピクセルを生成するための方法を実施する動作を実行させる命令を含む、コンピュータ可読記録媒体であって、前記プロセッサ装置に、

前記ピクセルアレイからのピクセルのウィンドウと、所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成させ、

別の前記ピクセルによって前記ウィンドウを更新させ、

ピクセルの前記ウィンドウと、前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成させ、

所与の終了条件が満たされるまで、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルの前記セットを累算させる命令を含み、前記命令が、前記プロセッサ装置に、

前記タップ係数セットを更新して別の前記ピクセルによってピクセルの前記ウィンドウを更新し、

ピクセルの前記ウィンドウおよび前記タップ係数セットに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントし、

別の前記ピクセルによってピクセルの前記ウィンドウを再び更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントする

ことによって累算させ、

前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力させる、コンピュータ可読記録媒体。

#### 【請求項 19】

前記プロセッサ装置に、偶数番目の補間されたサブピクセルの前記セットを形成させる前記命令が、前記プロセッサ装置に、4個の偶数番目の補間されたサブピクセルを含むように前記セットを形成させ、前記4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、前記プロセッサ装置に、奇数番目の補間されたサブピクセルの前記セットを形成させる前記命令が、前記プロセッサ装置に、4個の奇数番目の補間されたサブピクセルを含むように前記セットを形成させ、前記4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する、請求項18に記載のコンピュータ可読記録媒体。

#### 【請求項 20】

前記プロセッサ装置に、前記偶数番目の補間されたサブピクセルをインクリメントさせる前記命令が、前記プロセッサ装置に、前記4個の偶数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントさせ、

前記プロセッサ装置に、前記奇数番目の補間されたサブピクセルをインクリメントさせる前記命令が、前記プロセッサ装置に、前記4個の奇数番目の補間されたサブピクセルの各々を、別の対応する2個の積の合計によってインクリメントさせ、

前記奇数番目の補間されたサブピクセルをインクリメントする各ステップが、別の対応する2個の積の合計によって、前記4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含む、請求項18に記載のコンピュータ可読記録媒体。

#### 【請求項 21】

ピクセルアレイからのピクセルを受け取るための入力を有する論理回路を含む、ピクセルアレイに対する補間されたピクセルを生成するための装置であって、前記論理回路が、

前記ピクセルアレイからのピクセルのウィンドウと、所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成し、

別の前記ピクセルによって前記ウィンドウを更新し、

10

20

30

40

50

ピクセルの前記ウィンドウと、前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成し、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを累算するように構成され、前記論理回路が、

前記タップ係数セットを更新して前記別のピクセルによって前記ウィンドウを更新し、

ピクセルの前記ウィンドウおよび前記タップ係数セットに基づいて、前記偶数番目の補間されたサブピクセルをインクリメントし、

別の前記ピクセルによってピクセルの前記ウィンドウを更新し、

ピクセルの前記ウィンドウと前記タップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルをインクリメントする

10

ことによって累算し、

前記所与の終了条件が満たされると、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力するように構成される、装置。

#### 【請求項 2 2】

前記論理回路が少なくとも1つの半導体ダイにおいて集積される、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 2 3】

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなる群から選択されるデバイスをさらに含み、前記デバイスに前記論理回路が組み込まれる、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0 0 0 1】

本開示はビデオ圧縮に関し、より詳細には、マルチタップ動き補償フィルタおよび双線形補間器に関する。

#### 【背景技術】

#### 【0 0 0 2】

デジタルビデオカメラからのビデオ出力は、一般にフレームのシーケンスであり、各フレームは、数百万個の光学センサであることが多いカメラの行と列のアレイによって生成されるスナップショットである。各フレームは、衝突画像の時間サンプルであるので、フレームのレートは、ユーザが捉えることを望む最大の動きの速さと関連付けられ得る。たとえば、毎秒15~30フレームというフレームレートは、人の目が支援されずに知覚可能な最速の動きを捉えることができる。より高いフレームレート、たとえば、毎秒100万フレームを超えるフレームレートが、高速な動き、たとえば、ハチドリの羽ばたきまたは砲内弾道学的な事象の捕捉のために使用され得る。

30

#### 【0 0 0 3】

しかし、より低いフレームレートにおいても、不必要的情報と呼ばれ得るようなものを除去するための処理が光学センサによって生成されたデータに対して行われない場合、画像を通信し記憶するために必要とされるデータの量が問題となり得る。不必要的データの例には、必要とされるものよりも詳細な画像、または、実際の情報をほとんど伝えないデータ、たとえば、先行するフレームですでに伝えられていることに対してほとんどまたはまったく付け加えることのないデータがある。後者のタイプの情報は、「フレーム間」冗長性と呼ばれ得る。1つの例は、変化しない背景に向かって走っている人を撮影するビデオカメラであり得る。そのような画像では、実際はフレームとフレームの間の変化は人の位置だけであり得るので、フレームのフィルタリングされないシーケンスは、大量の不必要的情報を伝えるであろう。

40

#### 【0 0 0 4】

50

たとえば、完全なまたは実質的に完全な内容を伴う間欠的なフレームのみを送信し、前のフレームからの変化、すなわちデルタのみとして後続のまたは介在する「フレーム」を送信することによって、上記の冗長性を利用する、様々なアルゴリズムが知られている。送信される変更またはデルタは、1つまたは複数の物体の変位を含んでよく、そのような変位は1つまたは複数の動きベクトルで表され得る。

#### 【0005】

様々なビデオ符号化規格、たとえば、H.263、H.264、MPEG-2、およびMPEG-4による動きベクトルは、1/2ピクセルおよび/または1/4ピクセルの分解能のようなサブピクセルの分解能で生成され得る。サブピクセルの分解能は元の画像よりも大きいので、サブピクセルの分解能を伴う動きベクトルは、元のピクセルの間を補間し、さらに補間されたピクセルの間を補間することによって推定され得る。サブピクセルを推定または補間することと関連付けられる1つのよく知られている問題は、計算的な複雑さである。サブピクセルの分解能を伴う動きベクトルの推定と関連付けられる計算的な複雑さの低減が、望ましいものとして長らく知られている。

10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0006】

1つまたは複数の例示的な実施形態による1つの方法は、ピクセルアレイに対するサブピクセルの補間を行うことができ、ピクセルアレイからのピクセルのウインドウレジスタと所与のタップ係数セットを有するタップ係数レジスタとに基づいて、偶数番目の補間されたサブピクセルのセットを形成するステップと、別のピクセルによってウインドウレジスタを更新するステップと、前記ウインドウレジスタと前記タップ係数レジスタとに基づいて、奇数番目の補間されたサブピクセルのセットを形成するステップと、所与の終了条件が満たされるまで、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルを累算するステップとを含み得る。ある実施形態では、累算する各ステップは、別のタップ係数セットに基づいてタップ係数レジスタを更新し、別のピクセルによってウインドウレジスタを更新するステップと、ウインドウレジスタとタップ係数レジスタとに基づいて、偶数番目の補間されたサブピクセルをインクリメントするステップと、別のピクセルによってウインドウレジスタを再び更新するステップと、ウインドウレジスタとタップ係数レジスタとに基づいて、奇数番目の補間されたサブピクセルをインクリメントするステップとを含み得る。ある態様では、方法は、終了条件が満たされると、偶数番目の補間されたサブピクセルのセットおよび奇数番目の補間されたサブピクセルのセットを出力するステップを含み得る。

20

#### 【0007】

ある態様では、偶数番目の補間されたサブピクセルのセットを形成するステップは、4個の偶数番目の補間されたサブピクセルを含むようにセットを形成し、4個の偶数番目の補間されたサブピクセルの各々が2個の積の合計を有し、さらなる態様では、奇数番目の補間されたサブピクセルのセットを形成するステップは、4個の奇数番目の補間されたサブピクセルを含むようにセットを形成し、4個の奇数番目の補間されたサブピクセルの各々が、対応する2個の積の合計を有する。

30

#### 【0008】

ある態様では、偶数番目の補間されたサブピクセルのセットを形成するステップは、单一のマシンサイクルの間に行われてよく、同様に、奇数番目の補間されたサブピクセルのセットを形成するステップは、单一のマシンサイクルの間に行われてよい。

40

#### 【0009】

ある態様では、偶数番目の補間されたサブピクセルをインクリメントする各ステップは、別の対応する2個の積の合計によって、4個の偶数番目の補間されたサブピクセルの各々をインクリメントするステップを含んでよく、関連する態様では、奇数番目の補間されたサブピクセルをインクリメントする各ステップは、別の対応する2個の積の合計によって、4個の奇数番目の補間されたサブピクセルの各々をインクリメントするステップを含ん

50

でよい。

**【0010】**

ある態様では、タップ係数レジスタを更新し、ウィンドウレジスタを更新するステップは、偶数番目の補間されたサブピクセルをインクリメントするステップと組み合わされて、単一のマシンサイクルの間に行われてよく、さらなる態様では、奇数番目の補間されたサブピクセルをインクリメントするステップと組み合わされた、ウィンドウレジスタを再び更新するステップは、単一のマシンサイクルの間に行われてよい。

**【0011】**

実施形態は、ピクセルアレイに対する補間されたピクセルを生成するための装置を含んでよく、またはそれを提供してよく、態様は、様々な態様によれば、ピクセルアレイからのピクセルのウィンドウと所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成するための手段と、別のピクセルによってウィンドウを更新するための手段と、ピクセルのウィンドウと前記タップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成するための手段と、所与の終了条件が満たされるまで、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルを累算するための手段とを含み得る。ある態様では、累算するための手段は、タップ係数セットを更新して別のピクセルによってウィンドウを更新し、ピクセルのウィンドウとタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルをインクリメントし、別のピクセルによってピクセルのウィンドウを更新し、ピクセルのウィンドウとタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルをインクリメントするように構成され得る。一実施形態では、装置は、所与の終了条件が満たされると、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルを出力するための手段を含み得る。

10

20

30

40

**【0012】**

実施形態は、命令を含むコンピュータ可読媒体を含んでよく、またはそれを提供してよく、命令は、ワイヤレス通信システム中のプロセッサ装置によって実行されると、プロセッサ装置に、ピクセルアレイに対する補間されたピクセルを生成するための方法を実施する動作を実行させ、様々な態様によれば、命令は、プロセッサ装置に、ピクセルアレイからのピクセルのウィンドウと所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成させ、別のピクセルによってウィンドウを更新させ、ピクセルのウィンドウと前記タップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成させ、所与の条件が満たされるまで、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルのセットを累算させることができる。ある実施形態では、命令は、タップ係数セットを更新して別のピクセルによってピクセルのウィンドウを更新し、ピクセルのウィンドウとタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルをインクリメントし、別のピクセルによってピクセルのウィンドウを再び更新し、ピクセルのウィンドウとタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルをインクリメントすることによって、プロセッサ装置に累算させることができる。ある態様では、命令は、プロセッサ装置に、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルを出力させることができる。

**【0013】**

実施形態は、ピクセルアレイに対する補間されたピクセルを生成するための装置を含んでよく、またはそれを提供してよく、装置は、ピクセルアレイからのピクセルを受け取るための入力を有する論理回路を含んでよく、様々な態様によれば、論理回路は、ピクセルアレイからのピクセルのウィンドウと所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットを形成し、別のピクセルによってウィンドウを更新し、ピクセルのウィンドウと前記タップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットを形成し、所与の終了条件が満たされるまで、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルを累算するように構成され得る。様々な態様によれば、論理回路は、タップ係数セットを更新して別のピクセルによってウ

50

ンドウを更新し、ピクセルのウィンドウとタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルをインクリメントし、別のピクセルによってピクセルのウィンドウを更新し、ピクセルのウィンドウとタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルをインクリメントすることによって、累算するように構成され得る。さらなる態様では、論理回路は、所与の終了条件が満たされると、偶数番目の補間されたサブピクセルおよび奇数番目の補間されたサブピクセルを出力するように構成され得る。

#### 【0014】

添付の図面は、本発明の実施形態の説明において助けとなるように提示されており、実施形態の限定ではなく、実施形態の例示のみのために提供されている。

#### 【図面の簡単な説明】

10

#### 【0015】

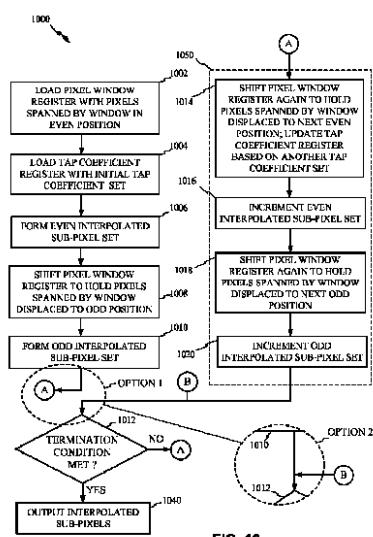

【図1】整数ピクセルおよび補間された分数ピクセルの1つの例示的な構成を示す図である。

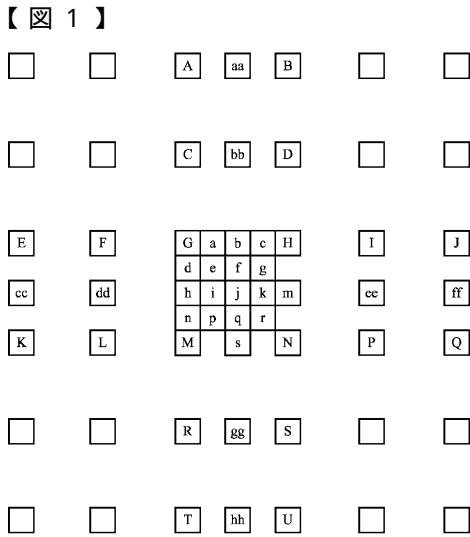

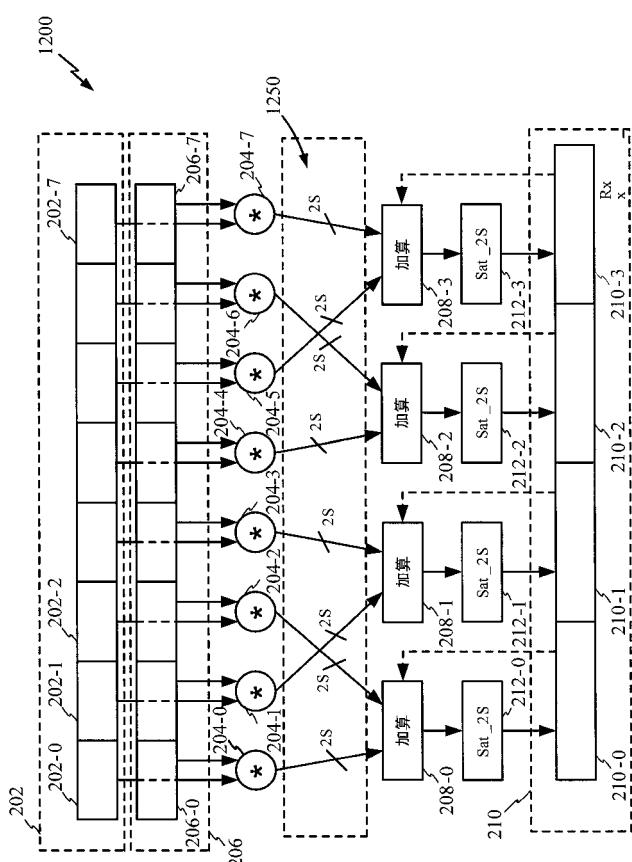

【図2】1つの例示的な実施形態による、1つの例示的な短縮サイクルマルチタップ補間フィルタの機能ブロック図である。

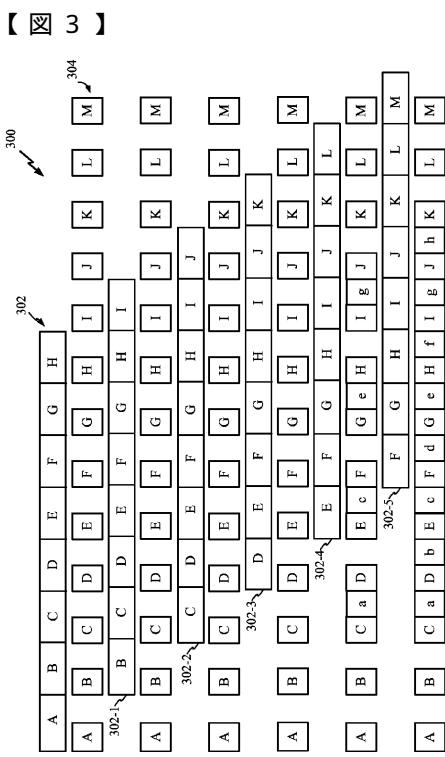

【図3】1つまたは複数の例示的な実施形態による、ピクセルの1つの例示的な入力シーケンスのグラフィカルなモデルを示し、ピクセルウィンドウが画像ピクセルの行に沿って右から左に徐々に移されること、および、短縮サイクルマルチタップ補間フィルタの処理において、対応する補間された1/2ピクセルを生成することを示す図である。

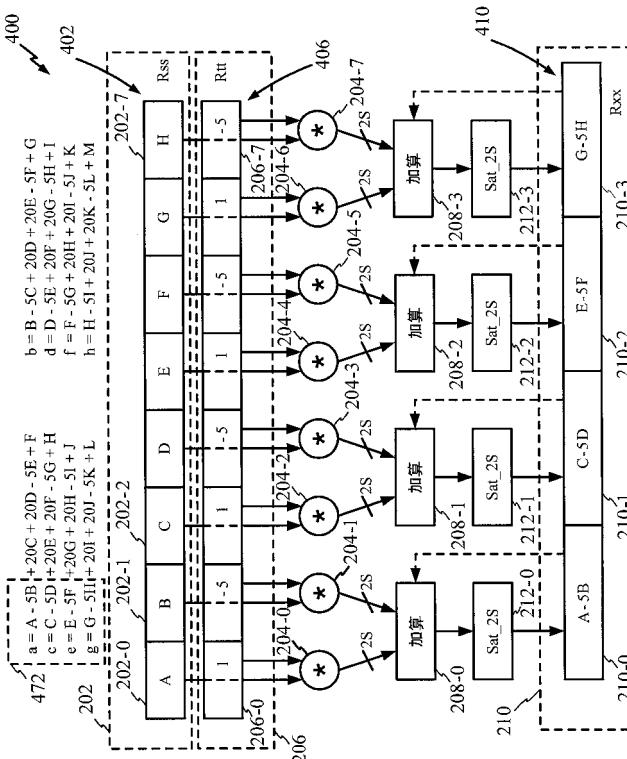

【図4】1つの例示的な実施形態による、図3の第1のピクセルウィンドウ位置に対応するピクセルウィンドウに対して行われる第1の「偶数番目」のマシンサイクルに対する1つの例示的なマシン状態と、1つの短縮サイクルマルチタップ補間フィルタの処理において、第1の複数の補間された1/2ピクセルの開始値を生成することとを、図2の機能ブロック図上で示す図である。

20

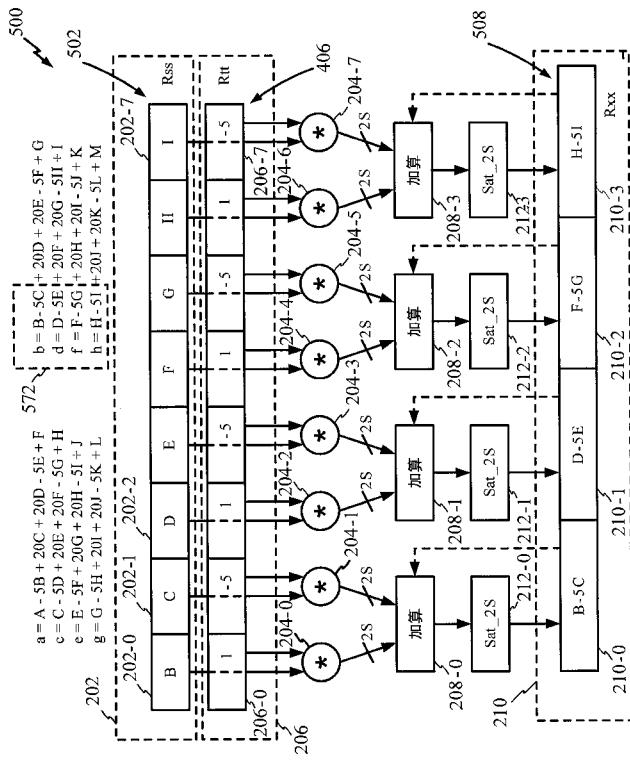

【図5】1つの例示的な実施形態による、図3の第2のピクセルウィンドウ位置に対応するピクセルウィンドウに対して行われる1つの例示的なマシンサイクルと、1つの短縮サイクルマルチタップ補間フィルタの処理において、第2の複数の補間された1/2ピクセルの開始値を生成することとを、図2の機能ブロック図上で示す図である。

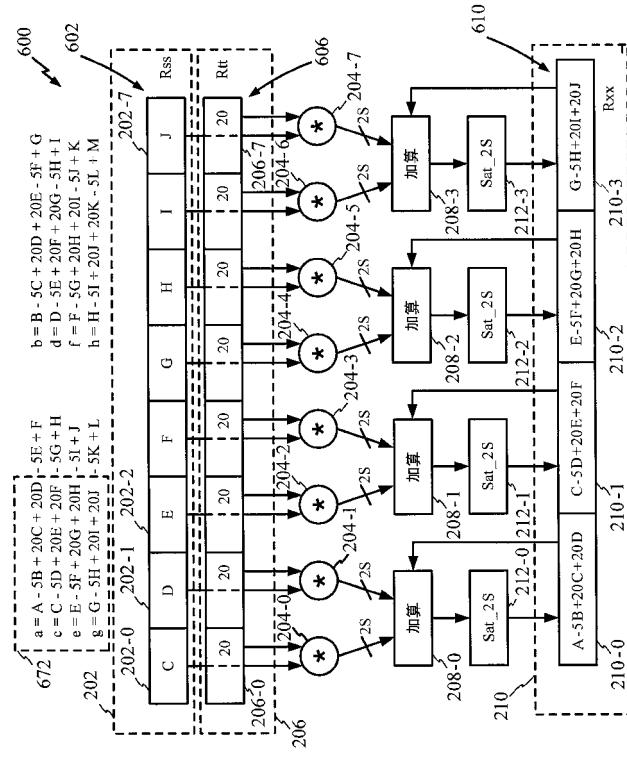

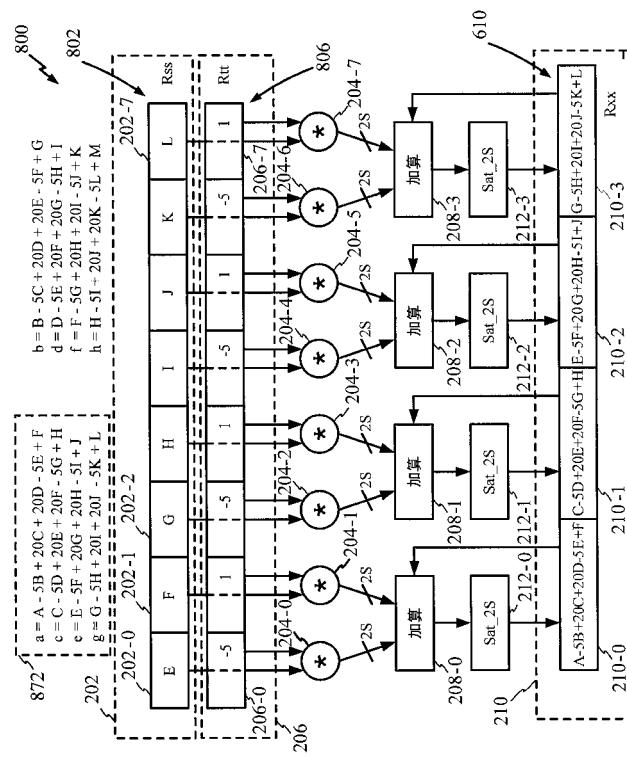

【図6】1つの例示的な実施形態による、図3の第3のピクセルウィンドウ位置に対応するピクセルウィンドウに対して行われる1つの例示的なマシンサイクルと、1つの短縮サイクルマルチタップ補間フィルタの処理において、第1の複数の補間された1/2ピクセルの第1の累算された値または更新された値を生成することとを、図2の機能ブロック図上で示す図である。

30

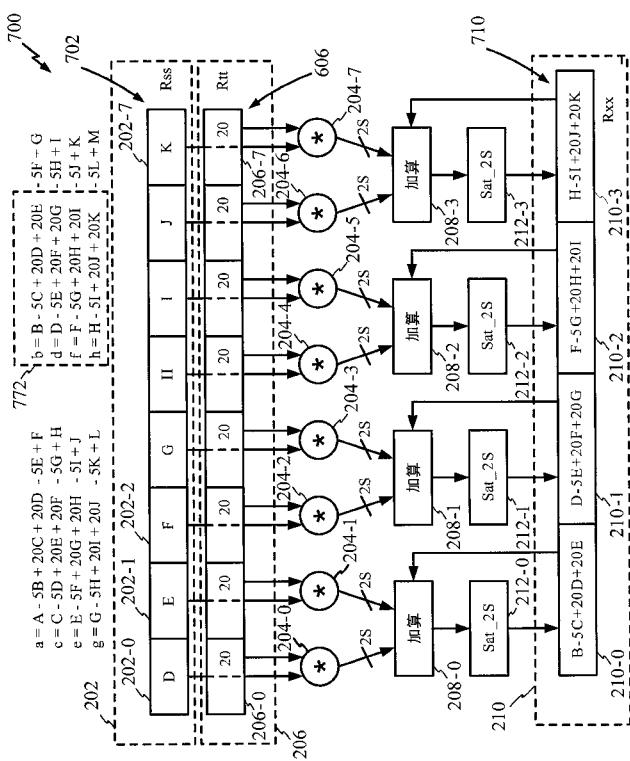

【図7】1つの例示的な実施形態による、図3の第4のピクセルウィンドウ位置に対応するピクセルウィンドウに対して行われる1つの例示的な次のマシンサイクルと、1つの短縮サイクルマルチタップ補間フィルタの処理において、第2の複数の補間された1/2ピクセルの第1の累算された値または更新された値を生成することとを、図2の機能ブロック図上で示す図である。

【図8】1つの例示的な実施形態による、図3の第5のピクセルウィンドウ位置に対応するピクセルウィンドウに対して行われる1つの例示的な最後のマシンサイクルと、1つの短縮サイクルマルチタップ補間フィルタの処理において、第1の複数の補間された1/2ピクセルの最終値を生成することとを、図2の機能ブロック図上で示す図である。

40

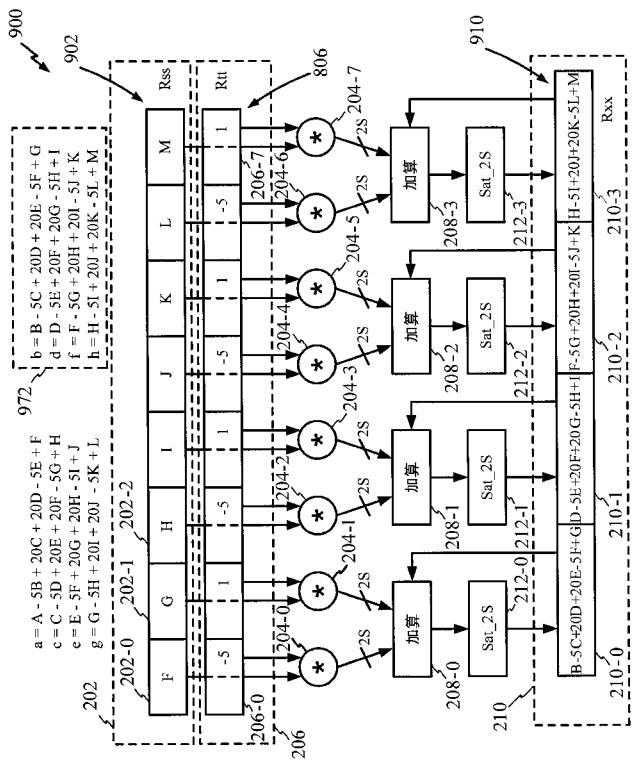

【図9】1つの例示的な実施形態による、図3の第6のピクセルウィンドウ位置に対応するピクセルウィンドウに対して行われる別の例示的な最後のマシンサイクルと、1つの短縮サイクルマルチタップ補間フィルタの処理において、第2の複数の補間された1/2ピクセルの最終値を生成することとを、図2の機能ブロック図上で示す図である。

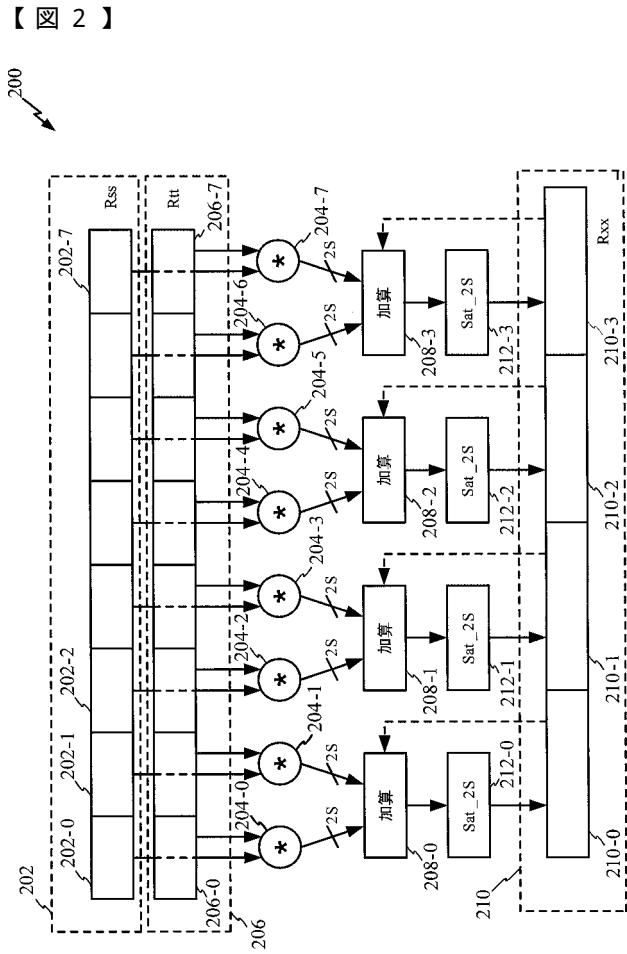

【図10】様々な例示的な実施形態による、1つまたは複数の方法およびシステムにおける、短縮マシンサイクルサブピクセル補間の1つのプロセスの1つの例示的な論理フローを示す図である。

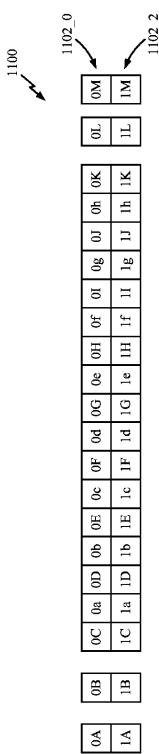

#### 【図11】1つまたは複数の例示的な実施形態による、短縮サイクルマルチタップ補間フ

50

ィルタに対する処理において生成される、2つの例示的なピクセル行セクションおよび対応する例示的な1/2ピクセルを示す図である。

【図12】1つの例示的な実施形態による、図2の短縮サイクルマルチタップ補間フィルタ200の1つの構成を使用する1つの例示的な実装形態における、ある態様ではインターリープされたクロマ成分を提供する、1つの双線形補間フィルタの1つの機能ブロック図である。

【図13】インターリープされたクロマ成分の双線形補間に関与し得る、1つの例示的なピクセルのアレイを示す図である。

【図14】1つの例示的な実施形態によるプロセスにおける、1つの例示的な、生成され双線形補間された、インターリープされたクロマ成分を示す図である。 10

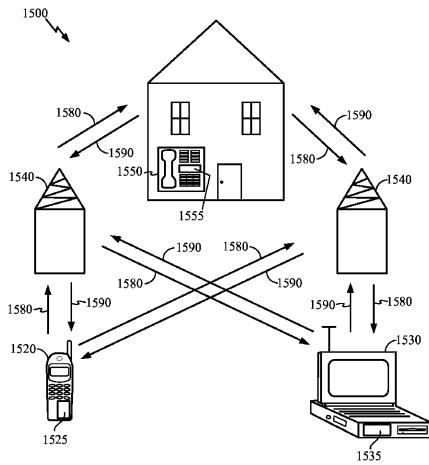

【図15】1つまたは複数の例示的な実施形態による、例示的なパーソナルコンピューティングデバイスの機能ブロック図である。

【発明を実施するための形態】

【0016】

本発明の特定の実施形態を対象とする以下の説明および関連する図面で、本発明の態様が開示される。本発明の範囲から逸脱することなく、代替の実施形態が考案され得る。加えて、本発明の関連する詳細を不明瞭にしないように、本発明のよく知られている要素は詳細に説明されず、または省略される。

【0017】

「例示的な」という言葉は、「例、事例、または例示として機能すること」を意味するように本明細書で使用される。「例示的な」として本明細書で説明される任意の実施形態は、必ずしも他の実施形態よりも好ましいか、または有利であると解釈されるべきではない。同様に、「本発明の実施形態」という用語は、本発明のすべての実施形態が、論じられた特徴、利点または動作モードを含むことを必要としない。 20

【0018】

本明細書で使用される用語は、特定の実施形態の説明のみを目的とするものであり、本発明の実施形態を限定するものではない。本明細書で使用される単数形「a」、「an」、および「the」は、文脈が別段に明確に示すのでなければ、複数形をも含むものとする。さらに、本明細書で使用される「含む(comprises)」、「含んでいる(comprising)」、「含む/includes)」、および/または「含んでいる(including)」という用語は、述べられた特徴、整数、ステップ、動作、要素、および/またはコンポーネントの存在を明示するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、コンポーネント、および/またはそれらのグループの存在または追加を排除しないことを理解されよう。 30

【0019】

さらに、多くの実施形態が、たとえばコンピューティングデバイスの要素によって実行されるべき、一連の動作に関して説明される。本明細書で説明される様々な動作は、特定の回路(たとえば、特定用途向け集積回路(ASIC))によって、1つまたは複数のプロセッサによって実行されるプログラム命令によって、あるいは両方の組合せによって実行され得ることを認識されよう。加えて、本明細書で説明されるこれらの一連の動作は、実行されると、関連するプロセッサに本明細書で説明される機能を実行させるコンピュータ命令の対応するセットを記憶した、任意の形式のコンピュータ可読記憶媒体内で完全に具現化されるものと見なされ得る。したがって、本発明の様々な態様は、特許請求される主題の範囲内にすべて入ることが企図されているいくつかの異なる形式で具現化され得る。加えて、本明細書で説明される実施形態ごとに、任意のそのような実施形態の対応する形式は、本明細書では、たとえば、説明される動作を実行する「ように構成された論理」として説明されることがある。 40

【0020】

H.264のようなビデオ圧縮技法では、動き補償(MC)の精度は、たとえば、ルーマサンプル間の距離の1/4の単位である。動きベクトルが整数サンプル位置を指す例では、予測信号は、参照ピクチャの対応するサンプルからなる。動きベクトルが整数サンプル位置以外

を指す例では、対応するサンプルは、非整数位置を生成するための補間を使用して取得される。1/2サンプル位置における予測値は、1次元の6タップ有限インパルス応答(FIR)フィルタを水平方向および垂直方向に適用することによって取得され得る。1/4サンプル位置における予測値は、整数位置および1/2サンプル位置におけるサンプルを平均することによって生成され得る。

## 【0 0 2 1】

図1は、サンプルa-kおよびn-rに対する分数サンプル補間を示す。bおよびhと標識された1/2サンプル位置におけるサンプルは、それぞれ次のように6タップフィルタを適用することによって、中間値 $b_1$ および $h_1$ をまず計算することによって導出される。

## 【0 0 2 2】

$$b_1 = (E - 5F + 20G + 20H - 5I + J) \quad \text{Eq. (1)}$$

## 【0 0 2 3】

$$h_1 = (A - 5C + 20G + 20M - 5R + T) \quad \text{Eq. (2)}$$

## 【0 0 2 4】

位置bおよびhに対する最終予測値は、次のように得られ、0~255の範囲にとどめられ得る。

## 【0 0 2 5】

$$b = (b_1 + 16) \gg 5 \quad \text{Eq. (3)}$$

## 【0 0 2 6】

$$h = (h_1 + 16) \gg 5 \quad \text{Eq. (4)}$$

## 【0 0 2 7】

jと標識された1/2サンプル位置におけるサンプルは、

$$j_1 = cc - 5dd + 20h_1 + 20m_1 - 5ee + ff \quad \text{Eq. (5)}$$

によって得られてよく、cc、dd、ee、m<sub>1</sub>、およびffによって示される中間値は、h<sub>1</sub>と同様の方式で得られる。そして、最終予測値jは、

$$j = (j_1 + 512) \gg 10 \quad \text{Eq. (6)}$$

として計算され、0~255nの範囲にとどめられ得る。

## 【0 0 2 8】

jの値を得る2つの代替的な方法は、フィルタリング動作が1/2サンプル位置の生成のために分離可能であることを示す。

## 【0 0 2 9】

さらに図1を参照すると、a、c、d、n、f、i、k、およびqと標識された1/4サンプル位置におけるサンプルは、たとえば、

$$a = (G + b + 1) \gg 1 \quad \text{Eq. (7)}$$

として、整数サンプル位置および1/2サンプル位置における2つの最も近いサンプルの上方丸めを伴って平均することによって導出される。

## 【0 0 3 0】

e、g、p、およびrと標識された1/4サンプル位置におけるサンプルは、たとえば、

$$e = (b + h + 1) \gg 1 \quad \text{Eq. (8)}$$

として、対角方向にある1/2サンプル位置における最も近い2つのサンプルを上方丸めを伴って平均することによって導出される。

## 【0 0 3 1】

クロマ成分の予測値は、双線形補間によって得られ得る。クロマのサンプリング格子は、ルーマのサンプリング格子よりも分解能が低いので、クロマのために使用される変位は、1/8サンプル位置の精度を有する。

## 【0 0 3 2】

図2を参照すると、例示的なマルチタップ統合補間フィルタ200は、ピクセルウィンドウレジスタ202、乗算器のアレイ、この例では8個の乗算器204-0、204-1、…、204-7(総称的に「乗算器204」または「乗算器アレイ」と呼ばれ、「204」は図面に明確に現れない)、およびタップ係数セットレジスタ206を含む。ピクセルウィンドウレジスタは、複数の、

10

20

30

40

50

この例では8個のピクセルレジスタ202-0、202-1、…、202-7(総称的に「202-x」と呼ばれ、これは図面には現れない)を有し得る。ある態様では、ピクセルウィンドウレジスタ202を形成する8個のピクセルレジスタ202-xは、パラレルにロード可能なように、パラレルな出力を有するように構成されてよく、たとえば、図2で右から左として示されるような「方向」に、バケツリレー方式で一緒に、選択的にシフトされるように構成され得る。代替的に、ある態様では、ピクセルレジスタ202-xは、ピクセルウィンドウレジスタ202が8ピクセルのパラレルイン/パラレルアウトシフトレジスタ機能を提供するように構成され得る。ピクセルレジスタ202-xは、Sビットの幅であり得る。限定されることなく、「S」の1つの例示的な値は8ビットである。ピクセルウィンドウレジスタ202の1つの例示的な実装形態は、パラレルなロードおよび出力という特徴を有する、ファーストインファーストアウト(FIFO)またはFIFOパイプラインであり得る。ピクセルウィンドウレジスタ202の具体的な構造に関して、自身の保有するノウハウを本開示に適用する当業者は、様々な構造的な実装形態を容易に特定することができるので、そのような構造のさらなる詳細な説明は省略される。

10

#### 【0033】

より後のセクションでより詳細に説明されるように、ピクセルウィンドウレジスタ202を通るSビットのピクセルデータの「右から左への」シフトは、一部、畳み込みタイプの演算をもたらし得る。図3を参照して後のセクションで説明される一例は、ピクセルアレイの例示的な領域(図2には示されない)の行(図2には示されない)にわたる8個のピクセル(図2には示されない)を包含する、ウィンドウのシフトをもたらし得る。

20

#### 【0034】

図2を続けて参照すると、いくつかの態様に対するさらなる動作を説明する際に図面を参照するときに便利なように、乗算器204-0および204-1は、代替的に「第1の乗算器ペア」204-0/1と呼ばれ、乗算器204-2および204-3は「第2の乗算器ペア」204-2/3と呼ばれ、乗算器204-4および204-5は「第3の乗算器ペア」204-4/5と呼ばれ、乗算器204-6および204-7は「第4の乗算器ペア」204-6/7と呼ばれる。「乗算器ペア」という用語は、いくつかの態様に関する例示的な動作を説明するためだけのものであり、ハードウェアアーキテクチャを定義することは意図されないことを理解されたい。逆に、より後のセクションにおけるさらに詳細な説明から理解されるように、一態様では、乗算器204の出力は、図2に示されるものとは異なる構成で、加算デバイス208-yに結合され得る。

30

#### 【0035】

図2をさらに参照すると、ある態様では、乗算器204の各々は、上で説明されたピクセルレジスタ202-xの対応する1つに結合される、または結合されることが可能な第1のオペランドポート(示されているが別々に標識されてはいない)、および、タップ係数セットレジスタ206の対応するタップ係数レジスタ206-xに結合される、または結合されることが可能な第2のオペランドポート(示されているが別々には番号を付けられていない)によって構成され得る。ある態様では、タップ係数セットレジスタ206は、たとえば、第8のタップ係数レジスタ206-7で終わる、第1のタップ係数レジスタ206-0、第2のタップ係数レジスタペア206-1などを含み得る。

40

#### 【0036】

ある態様では、乗算器204は、固定小数点乗算を実行するように構成されてよく、このことは、例示的な演算を説明するために仮定される。しかし、この仮定は、概念とは関係のない複雑さをもたらすことなく例示的な処理の説明を容易にするためのものにすぎず、考慮される実施形態の範囲を限定することは意図されない。逆に、本開示を読めば、実施形態は浮動小数点の計算を使用して実施され得ることが、当業者により容易に理解されるだろう。

#### 【0037】

図2をさらに参照すると、より後のセクションでより詳細に説明されるように、ある態様では、マルチタップ統合補間フィルタ200は、タップ係数の複数のセット(図2には特に示されていない)を記憶装置(図2には特に示されていない)に記憶し、タップ係数のそのよ

50

うなセットを選択的に取り出し、これらをタップ係数セットレジスタ206にロードするよう構成され得る。ピクセルウィンドウレジスタ202およびタップ係数セットレジスタ206は同一の構造を有してよく、たとえば、各々がレジスタアレイ(明確には示されていない)中の論理的に指定されたレジスタであり得ることを理解されたい。

#### 【0038】

図2をさらに参照すると、1つの構成では、第1の乗算器ペア204-0、204-1のそれぞれの出力は、第1の加算デバイス208-0のオペランド入力ポート(示されるが、別々には番号を付けられていない)、第2の加算デバイス208-1のオペランド入力ポート(示されるが、別々には番号を付けられていない)に入力する第2の乗算器ペア204-2、204-3のそれぞれの出力、第3の加算デバイス208-2のオペランド入力ポート(示されるが、別々には番号を付けられていない)に入力する第3の乗算器ペア204-4、204-5のそれぞれの出力、および、第4の加算デバイス208-3のオペランド入力ポート(示されるが、別々には番号を付けられていない)に入力する第4の乗算器ペア204-6、204-7のそれぞれの出力へと、スイッチングされ、ルーティングされ、または別様に結合され得る。例示的な動作の説明を簡潔にするために、第1の加算デバイス208-0、第2の加算デバイス208-1、第3の加算デバイス208-2、および第4の加算デバイス208-3はまた、総称的に、「加算デバイス208-y」として個々に呼ばれ、「加算デバイス208」としてまとめて呼ばれ、「208-y」および「208」という標識は図面には明確には現れないことを理解されたい。

10

#### 【0039】

加算デバイス208への乗算器204の図示され説明される結合を実施するための、スイッチング、ルーティング、または結合の論理(図示されず)に関して、一態様では、当業者は、本開示に基づいて、従来のデジタルシグナルプロセッサの設計技法を適用することによってそのような論理を選択し、または別様に実装できるので、スイッチング、ルーティング、または結合の論理のさらなる詳細な説明は省略される。

20

#### 【0040】

図2の参照を続けると、ある態様では、マルチタップ統合補間フィルタ200は、たとえば、4個の累算器レジスタ210-0、210-1、210-2、210-3(総称的に、「累算器レジスタ210-y」として個々に呼ばれ、「210-y」は図面には明確には現れないことが理解される)を有する累算器210を含み得る。4個という量は一例にすぎず、いかなる実施形態の範囲も限定することは意図されないことが理解されよう。累算器レジスタ210-0、210-1、210-2、および210-3は、別々に制御されるとは限らず、または別々に制御可能なレジスタであるとは限らず、代わりに、累算器210のフィールドであり得ることも理解されたい。さらに、累算器レジスタ210-0、210-1、210-2、および210-3は、4個のフィールドのサブセットとして、または、4個よりも多くのフィールドもしくはその等価物を有する実装された累算器210の等価物のサブセットとして実装され得ることが予想される。

30

#### 【0041】

図2をさらに参照すると、一態様では、各加算デバイス208の出力(示されるが、別々には番号を付けられていない)は、対応する累算器レジスタ210-yに直接入力し得る。さらなる態様では、図2のマルチタップ統合補間フィルタ200は、加算デバイス208の中の、またはそれと関連した、飽和論理、たとえば、図示された2Sビットの符号付き飽和論理212-0、212-1、212-2、212-3(まとめて「2Sビットの符号付き飽和論理212」と呼ばれ、総称的に「飽和論理」212-yとして個々に呼ばれ、「212」「212-y」という標識は図面に明確に現れないことを理解されたい)を含み得る。図2の本態様による例では、飽和論理212-yは、各加算デバイス208-yの出力(示されるが、別々には番号を付けられていない)と対応する累算器レジスタ210-yとの間に論理的に配置され得る。ここでの、および本明細書の他の例における「論理的に配置される」とは、「2Sビットの符号付き飽和論理」212-yが、別個のハードウェアまたは専用のハードウェアであるとは限らないことを意味し得ることを理解されたい。たとえば、一態様では、2Sビットの各符号付き飽和論理212-yは、プログラム可能な機能として、対応する加算デバイス208-yを実装する論理(別々には示されていない)へと組み込まれ得る。2Sビットの符号付き飽和論理212の具体的な構造について、

40

50

当業者は、本開示に鑑みて、当業者に知られている標準的なデジタル設計技法および技術を本開示に適用することによって、そのような論理を実装するための技法および構造を容易に特定することができる。したがって、2Sビットの符号付き飽和論理212の構造のさらなる詳細な説明は省略される。

#### 【0042】

2Sビットの符号付き飽和論理212の動作および機能に関して、これらはさらに、8という以前に説明された例示的なSに関する例によって理解され、(この例では)ウィンドウレジスタ202が8ビットの符号なしのデータを保持し、タップ係数セットレジスタ206に記憶されるタップ係数データは符号付きの8ビットデータであることを意味する。したがって、この例では、2Sビットの符号付き飽和論理212の文脈における値「2S」は16に等しい。Sが8に等しく2Sが16に等しい、2Sビットの符号付き飽和論理212の例示的な特徴は、第1の乗算器ペア204-0、204-1、加算デバイス208-0、および2Sビットの符号付き飽和論理212-0を参照することによって理解され得る。より具体的には、乗算器204-0は、ピクセルレジスタ202-0からの8ビットの符号なしピクセルデータを、タップ係数レジスタ206-0からの対応する符号付きの8ビットのタップ係数と乗算し、1つの符号付きの16ビットの積を生成することができ、同様に、乗算器204-1は、ピクセルレジスタ202-1からの別の8ビットの符号なしピクセルデータを、タップ係数レジスタ206-1からの対応する符号付きの8ビットのタップ係数と乗算し、別の符号付きの16ビットの積を生成することができる。2つのそれぞれの符号付きの16ビットの積は、加算デバイス208-0の2つのオペランド入力ポート(示されるが、別々には番号を付けられていない)に入力される。ある態様では、第1の加算デバイス208-0は、たとえば、入力オペランドポート(示されるが、別々には番号を付けられていない)が累算器の第1のレジスタ210-0に結合されるのを可能にすることによって、または、論理(示されていない)が第1の加算デバイス208-0の内部にあることを可能にすることによって、累算器モードで動作するように選択的に構成され得る。第1の加算デバイス208-0は、累算器モードで動作するとき、符号付きの16ビットの積と、累算器の第1のレジスタ210-0の現在の内容とを加算(または符号によっては減算)することができ、積の合計の結果、または、累算された積の合計の結果を、2Sビットの符号付き飽和論理212-0に与えることができる。16ビットを超えると2Sビットの符号付き飽和論理212-0によって16ビットで飽和させられ得る、この積の合計の結果または累算された積の合計の結果が、次いで第1の累算器レジスタ210-0にロードされ得る。残りの乗算器204-2、204-3、…、204-7、および残りの加算デバイス208-1、208-2、および208-3は、ピクセルウィンドウレジスタ202からの対応するピクセルレジスタ202-xの内容およびタップ係数レジスタ206からのタップ係数レジスタ206-xの内容に対して同様に動作することができ、それぞれの16ビットの積の合計または累算された積の合計の結果を、残りの累算器レジスタ210-1、210-2、および210-3のうちの対応する1つに与えることができる。

#### 【0043】

図3は、A、B、C、…、Mと標識された13個の画像ピクセルの行304に沿った位置の6回のステップシーケンスを通じた、ピクセルウィンドウ302のステップ移行のグラフィカルなモデル300を示す。ピクセルウィンドウ302は、8ビットの幅を有するものとして示されるが、これは単なる例であり、実施形態のいずれかの範囲を限定することは意図されない。開始位置302-0において、ピクセルウィンドウ302は、(8ピクセルという例示的な幅を仮定すると)ピクセルA、B、C、D、E、F、G、およびHにまたがり、終了位置302-5は、ピクセルF、G、H、I、J、K、L、およびMにまたがる。一態様では、6回のステップシーケンスは、3回の「偶数番目」のステップが3回の「奇数番目」のステップと交互に来るものと見なされ得る。「偶数番目」と「奇数番目」という標識は任意であることを理解されたい。関連する態様では、かつより後のセクションにおいてより詳細に説明されるように、図2のマルチタップ統合補間フィルタ200は、6個の状態または構成のシーケンスを通じて構成され操作されてよく、各状態は、シーケンス302-0、…、302-5における、ピクセルウィンドウ302の「偶数番目」または「奇数番目」のステップの1つに対応する。

#### 【0044】

10

20

30

40

50

図2および図3を参照すると、図2のマルチタップ統合補間フィルタ200のピクセルウインドウレジスタ202は、シーケンス302-0、…、302-5における図3のピクセルウインドウ302のこれらの「偶数番目」または「奇数番目」のステップの各々において、その位置における図3のピクセルウインドウ302がまたがるピクセルをロードされる。図2のマルチタップ統合補間フィルタ200は、一態様では、6個の図3のピクセルウインドウ302の位置の各々において、1つまたは複数の例示的な実施形態に従って、補間フィルタプロセスを実行することができる。ある態様では、例示的な動作のより後の説明からさらに理解されるように、6個の図3のピクセルウインドウ302の位置の各々において図2のマルチタップ統合補間フィルタ200によって実行される補間フィルタプロセスは、1つのマシンサイクルにおいて実行され得る。

10

#### 【0045】

「偶数番目」の図3のピクセルウインドウ302の位置302-0、302-2、および302-4に対応する状態において図2のマルチタップ統合補間フィルタ200によって実行される例示的な補間フィルタプロセスを説明する際に便利なように、これらの例示的な補間フィルタプロセスは、代替的に「偶数番目」のマシンサイクルと呼ばれる。したがって、同様に、「奇数番目」の図3のピクセルウインドウ302の位置302-1、302-3、および302-5に対応する状態においてマルチタップ統合補間フィルタ200によって実行される補間フィルタプロセスは、代替的に「奇数番目」のマシンサイクルと呼ばれる。

#### 【0046】

例示的な実施形態による方法およびシステムにおける1つの例示的な6ステップまたは6状態の短縮サイクル補間フィルタプロセスが、図2および図3とともに、図4、図5、図6、図7、図8、および図9を参照して以下により詳細に説明される。概観すると、例は、図4を参照して説明されるような第1の「偶数番目」のマシンサイクルを含んでよく、このマシンサイクルにおいて、ピクセルウインドウレジスタ202は、第1の「偶数番目」の位置302-0においてピクセルウインドウ302がまたがり、第1のタップ係数セットをロードされたタップ係数セットレジスタ206による演算の対象となる、図3のピクセルをロードされ得る。この演算は、累算器210において、図3の4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgの初期値を生成し形成し得る。ある態様では、形成された4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgは、メモリ(図示されない)にオフロードされ得る。理解されるように、このオフロードは、そのいずれもが累算器210の使用について互いに干渉しない、「偶数番目」のマシンサイクルおよび「奇数番目」のマシンサイクルの交互配置を実現し得る。諒解されるように、この交互配置という特徴により、いくつかの利点の中でもとりわけ、様々な例示的な実施形態による実施において、統合補間フィルタが実現し得る。

20

#### 【0047】

ある態様では、図5を参照したより詳細な説明からさらに理解されるように、第1の「奇数番目」のマシンサイクルにおいて、ピクセルウインドウレジスタ202は、第1の「奇数番目」の位置302-1においてピクセルウインドウ302がまたがるピクセルを保持するように更新されてよく、ピクセルウインドウレジスタの内容は、第1の「偶数番目」のマシンサイクルのために使用される同じ第1のタップ係数セットを一態様では有するタップ係数セットレジスタ206による演算の対象となる。この演算は、ある態様では、図3の例示的な4個の「奇数番目」の1/2ピクセルb、d、f、およびhの初期値を形成することができ、これらは次いでメモリにオフロードされ得る。図6を参照してより詳細に説明されるように、第2の「偶数番目」のマシンサイクルは、前に形成された4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgによって累算器210をリロードするステップを含んでよく、ピクセルウインドウレジスタ202は、第2の「偶数番目」の位置302-2においてピクセルウインドウ302がまたがる図3のピクセルを有するように更新され、タップ係数セットレジスタ206は第2のタップ係数セットをロードされる。第2のタップ係数セットを有するタップ係数セットレジスタ206は次いで、図3の「偶数番目」の位置302-2を有するピクセルウインドウレジスタ202の内容に対して演算を行い、増分の値(符号が正または負であり得る)を

30

40

50

生成することができ、これらの増分の値は、累算器210において、前に形成された4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgを調整またはインクリメントすることができる。インクリメントされた4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgは、メモリにオフロードされ得る。

#### 【0048】

次に、図7を参照してより詳細に説明されるように、第2の「奇数番目」のマシンサイクルにおいて、累算器210は、前に形成された4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhをロードされてよく、ピクセルウインドウレジスタ202は、第2の「奇数番目」の位置302-2においてピクセルウインドウ302がまたがる図3のピクセルを有するよう10に更新される。タップ係数セットレジスタセット206は、一態様では、第2のタップ係数セットを保持することができる。次いで、「偶数番目」の補間された1/2ピクセルa、c、e、およびgのインクリメントと同様の方式で、図3の「偶数番目」の位置302-2を有するピクセルウインドウレジスタ202の内容は、タップ係数セットレジスタ206による演算の対象となり、増分の値を生成することができ、この増分の値は、累算器210において、前に形成された4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhを調整またはインクリメントすることができ、インクリメントされたピクセルは次いでメモリにオフロードされ得る。

#### 【0049】

概観を続け、図8を参照してより詳細に説明されるように、第3の「偶数番目」のマシンサイクルは、前にインクリメントされた4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgを累算器210にリロードするステップ、第3の「偶数番目」の位置302-4においてピクセルウインドウ302がまたがる図3のピクセルを有するようピクセルウインドウレジスタ202を更新するステップ、第3のタップ係数セットをタップ係数セットレジスタ206にロードするステップ、および、第2の「偶数番目」のマシンサイクルと実質的に同じ算術演算を使用して、4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgの最終値を累算器210において確立するステップを含み得る。同様に、図9を参照してより詳細に説明されるように、累算器210は、前にインクリメントされた4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhをリロードされてよく、ピクセルウインドウレジスタ202は、第3の「奇数番目」の位置302-5においてピクセルウインドウ302がまたがる図3のピクセルを有するよう30に更新される。ある態様では、タップは、第3のタップ係数セットを保持することができ、増分の値は、4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhの最終値を累算器210において確立するために生成され得る。全体で3回の「偶数番目」のマシンサイクルの間に4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgを形成し累算することを、全体で3回の「奇数番目」のマシンサイクルの間に4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhを形成し累算することと交互に行うことによって、様々な例示的な実施形態による実施における統合補間フィルタは、8個の補間された1/2ピクセルa、b、c、d、e、f、g、およびhという完全なセットを、わずか6回のマシンサイクルで提供できることが、本開示を読めば当業者により諒解されるだろう。

#### 【0050】

例示的な実施形態による方法およびシステムにおける例示的な6状態の短縮サイクル補間フィルタプロセスが、ここで、図2および図3とともに、図4、図5、図6、図7、図8、および図9を参照して以下でより詳細に説明される。一態様では、第1の「偶数番目」のマシンサイクルおよび第1の「奇数番目」のマシンサイクルは、[1, -5, 1, -5, 1, -5, 1, -5]という第1のタップ係数セットを使用することができる。図面において、[1, -5, 1, -5, 1, -5, 1, -5]という第1のタップ係数セットは、図4および図5に現れるタップ係数セットレジスタ206のタップ係数セットレジスタ状態406として標識されている。1つの関連する態様では、タップ係数レジスタ206の図6および図7のタップ係数セットレジスタ状態606に反映されるように、第2のタップ係数セットは[20, 20, 20, 20, 20, 20, 20, 20]であってよく、1つのさらなる態様では、図8および図9のタップ係数セットレジスタ状態806に50

反映されるように、第3のタップ係数セットは[-5, 1, -5, 1, -5, 1, -5, 1]であってよい。これらは、第1、第2、および第3のタップ係数セットのそれぞれの値の例にすぎず、他の値が他の所望のフィルタ動作を得るために使用され得ることを理解されたい。実施形態は、2セットよりも多くのタップ係数を有することが考慮されることも理解されたい。

#### 【0051】

図4から図9のマシン状態において、図2のマルチタップ統合補間フィルタ200により示される例示的な算術演算を説明する前に、この説明は、様々なデータ経路に挿入される、または、様々な説明される論理および算術デバイス内に挿入される、ラッチ(図示されない)がないと仮定していることを理解されたい。言い換えれば、図2を参照すると、1つのマシンサイクルにおいて、ピクセルウインドウレジスタ202からのピクセル値およびタップ係数セットレジスタ206の中のタップ係数値は、乗算器アレイ204に渡され、加算デバイス208および2Sビットの飽和論理212を通過し累算器210にロードされるそれぞれの積を形成するように乗算され得ることが仮定される。ラッチがないというこの仮定は、これらのデータ経路におけるラッチが原因のクロックサイクルの遅延を説明する必要を伴わずに例示的な動作を説明することが目的にすぎないことを理解されたい。しかし、当業者は、説明された概念を、たとえば、説明されたデータ経路におけるラッチを利用する実施に対して容易に適合させることができる。

10

#### 【0052】

さらに、図3のシーケン302-0、…、302-5と、例示的な実施形態による実施におけるピクセルアレイにわたる他のピクセルウインドウの移動とを繰り返す能力を有するピクセルウインドウレジスタ202を実装し、タップ係数セットレジスタ206を実装するための、様々な技法および構造が、本開示から当業者には明らかとなるので、そのような技法および構造のさらなる詳細な説明は省略される。

20

#### 【0053】

例示的な実施形態による方法およびシステムにおける、例示的な6状態の短縮サイクル補間フィルタプロセスの、図4、図5、図6、図7、図8、および図9を参照した説明を簡単にする目的で、2Sビットの飽和論理212により実行される具体的な動作は省略される。本開示を読んだ当業者は、当業者が持つ固定小数点算術演算についての一般的なノウハウを開示される概念に適用して、中間の処理結果および最終的な1/2ピクセルの結果a、b、…、hを、所望の数値範囲内に維持することができる。したがって、主題の演算に付随する例を除いて、説明では、乗算および累算の演算によってもたらされる数値的な増大を無視する。

30

#### 【0054】

図2から図4を参照すると、例示的な第1の「偶数番目」のマシンサイクルがより詳細に説明される。ある態様では、第1の「偶数番目」のマシンサイクルは、図4のピクセルウインドウレジスタ202を状態402へとロードするステップと、図3のウインドウ302の位置302-0がまたがるピクセルA、B、C、D、E、F、G、およびHを反映するステップと、タップ係数セットレジスタ206を、[1, -5, 1, -5, 1, -5, 1, -5]という第1のタップ係数セットである状態406へとロードするステップとを含み得る。乗算器204は、ピクセルウインドウレジスタ202の状態402のピクセルA、B、C、D、E、F、Gを、タップ係数セットレジスタ206の状態406と乗算し、4個の積のペアを生成し、これらを、加算デバイス208の対応する1つのそれぞれのオペランドポート(示されるが標識されていない)に入力することができる。

40

#### 【0055】

一態様では、乗算演算は、乗算器ペア204-0、204-1が、第1のピクセルレジスタ202-0および第2のピクセルレジスタ202-1からピクセルAおよびBを受け取り、これらのピクセルAおよびBをそれぞれ、[1, -5, 1, -5, 1, -5, 1, -5]という第1のタップ係数セットからの「1」および「-5」と乗算し、次いで、「A」および「-5B」であるそれぞれの積を、第1の加算デバイス208-0のオペランドポートに入力することを含み得る。第1の加算デバイス208-0の出力(A-5B)は、こうして、第1の累算器レジスタ210-0における「偶数番目」の補間された1/2ピクセルaを形成する。第2の乗算器ペア204-2、204-3は同様に、第3のピクセル

50

レジスタ202-2および第4のピクセルレジスタ202-3から、それぞれピクセルCおよびDを受け取り、これらを、状態406における第3のタップ係数レジスタ206-2および第4のタップ係数レジスタ206-3から「1」および「-5」と乗算し、結果の出力である「C」および「-5D」を、第2の加算デバイス208-1の入力オペランドポートに送ることができる。第2の加算デバイス208-0の出力(C-5D)は、こうして、第2の累算器レジスタ210-1における「偶数番目」の補間された1/2ピクセルcを形成することができる。同様に、第3の乗算器ペア204-4、204-5は、第5のピクセルレジスタ202-4および第6のピクセルレジスタ202-5からピクセルEおよびFを受け取り、これらを、第5のタップ係数レジスタ206-4および第6のタップ係数レジスタ206-5からの「1」および「-5」と乗算して、第3の加算デバイス208-2を通じて、第3の累算器レジスタ210-2における「偶数番目」の補間された1/2ピクセルeを形成することができる。同様に、第4の乗算器ペア204-6、204-7は、第7のピクセルレジスタ202-6および第8のピクセルレジスタ202-7からピクセルGおよびHを受け取り、これらを、第7のタップ係数レジスタ206-6および第8のタップ係数レジスタ206-7からの「1」および「-5」と乗算して、第4の加算デバイス208-3を通じて、第4の累算器レジスタ210-3における「偶数番目」の補間された1/2ピクセルgを形成することができる。

10

## 【0056】

したがって、累算器210の内容410は、この例では第1の「偶数番目」のマシンサイクルの終わりにおいて、図4の領域470において示される「偶数番目」の補間された1/2ピクセルa、c、e、gの中間値を有し得る。ある態様では、領域470において示される値を伴う説明された補間された1/2ピクセルa、c、e、gを有する内容410は、メモリにオフロードされ得る。

20

## 【0057】

ここで図3および図5を参照すると、第1の「奇数番目」のマシンサイクルの例示的なプロセスが説明される。一態様では、図2のピクセルウィンドウレジスタ202は、B、C、D、E、F、G、H、Iである図3の第2のピクセルウィンドウ位置302-1に対応するピクセルを包含するように、ピクセルの内容を1ピクセル左にシフトする。これは、図5のピクセルウィンドウレジスタの状態502において反映されており、ピクセル「I」をシフトする最後のピクセルレジスタ202-7のファーストインファーストアウト(FIFO)動作によって実行されてよく、 $x=0 \sim 6$ に対して、ピクセルレジスタ202-xの各々は、(右から左の順で)先行するピクセルレジスタ202-x+1の内容を受け取る。タップ係数セットレジスタ206の内容は状態406のまま、すなわち、[1, -5, 1, -5, 1, -5, 1, -5]という第1のタップ係数セットのままである。ある態様では、乗算器204および加算デバイス208は、タップ係数レジスタ206の状態406、すなわち、[1, -5, 1, -5, 1, -5, 1, -5]という第1のタップ係数セットを、第1の「偶数番目」のサイクルについて説明されたのと同じ方式で、ピクセルB、C、D、E、F、G、Hと乗算して、加算デバイス20を通じて、累算器210において、以下の4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびh、すなわち、第1の累算器レジスタ210-0における補間された1/2ピクセルbの初期値として(B-5C)、第2の累算器レジスタ210-1における補間された1/2ピクセルdの初期値として(D-5E)、第3の累算器レジスタ210-2における補間された1/2ピクセルfの初期値として(F-5G)、および第4の累算器レジスタ210-3における補間された1/2ピクセルhの初期値として(H-5I)を形成する。累算器210の内容510、すなわち、「奇数番目」の補間された1/2ピクセルb、d、f、およびhの初期値が、図5の領域572において示され、ある態様では、メモリにオフロードされ得る。

30

## 【0058】

ここで図3および図6を参照すると、例示的な第2の「偶数番目」のマシンサイクルでは、第1の「偶数番目」のマシンサイクルにおいて形成された4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgの初期値は、基本的には、第1の「偶数番目」のマシンサイクルの演算を繰り返すことによって、しかし、図3の第3のピクセルウィンドウ位置302-2におけるピクセルおよび第2のタップ係数セット[20, 20, 20, 20, 20, 20, 20, 20]を使用して、かつ、前の4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgをインクリメントするためにその結果を使用することによって、インクリメントされ得る。

40

50

## 【0059】

図3および図6をさらに参照すると、ある態様では、第2の「偶数番目」のマシンサイクルは、前に形成された4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgを累算器210へとリロードするステップと、ピクセルウインドウレジスタ202を、たとえばFIFO動作によって、ピクセルC、D、E、F、G、H、I、およびJを有するピクセルウインドウレジスタの状態602へとシフトするステップと、状態606に反映されるように、例示的な第2のタップ係数セット[20, 20, 20, 20, 20, 20, 20, 20]をタップ係数セットレジスタ206にロードするステップとを含み得る。乗算器204は、タップ係数セットレジスタ206の内容または状態606[20, 20, 20, 20, 20, 20, 20, 20]を、ピクセルウインドウレジスタ202の中のピクセルC、D、E、F、G、H、I、およびJと乗算し、得られた積を加算デバイス208と結合することができる。これらの乗算器204の出力および前に形成された4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgの図6に示されるフィードバックを受け取ることによって、加算デバイス208は、図6の領域672において示される以下の値を有する、インクリメントされた「偶数番目」の1/2ピクセルa、c、e、およびgを累算器210において形成することができる。それらの値は、第1の累算器レジスタ210-0における、(A - 5B + 20C + 20D)に等しいインクリメントされた「偶数番目」の補間された1/2ピクセルa、第2の累算器レジスタ210-1における、(C - 5D + 20E + 20F)に等しいインクリメントされた「偶数番目」の補間された1/2ピクセルc、第3の累算器レジスタ210-2における、(E - 5F + 20G + 20H)に等しいインクリメントされた「偶数番目」の補間された1/2ピクセルe、および、第4の累算器レジスタ210-3における、(G - 5H + 20I + 20J)に等しいインクリメントされた「偶数番目」の補間された1/2ピクセルgである。ある態様では、これらのインクリメントされた4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgは、メモリにオフロードされ得る。

10

20

30

40

50

## 【0060】

ここで、図3および図7を参照すると、例示的な第2の「奇数番目」のマシンサイクルにおいて、第1の「奇数番目」のマシンサイクルにおいて形成される4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhの初期値は、第2の「偶数番目」のマシンサイクルの演算を繰り返し、しかし、図3の第4のピクセルウインドウ位置302-3におけるピクセルを使用することによって得られる結果により、インクリメントされる。タップ係数レジスタは、第2のタップ係数セット[20, 20, 20, 20, 20, 20, 20, 20]である状態606のままであり得る。ある態様では、ピクセルウインドウレジスタ202は、図7のピクセルウインドウレジスタの状態702によって示されるように、D、E、F、G、H、I、J、およびKである、図3の第4のピクセルウインドウ位置302-3に対応するピクセルを包含するようにシフトされてよく、4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhの初期値をメモリから累算器210へとリロードする。一態様では、第2の「偶数番目」のマシンサイクルについて説明されたのと実質的に同じ演算で、第2の「奇数番目」のマシンサイクルは、累算器210の内容を、図7の領域772にも示される、「奇数番目」の補間された1/2ピクセルb、d、f、およびhの以下の値へと更新することができる。それらの値は、第1の累算器レジスタ210-0における、(B - 5C + 20D + 20E)に等しいインクリメントされた「奇数番目」の補間された1/2ピクセルb、第2の累算器レジスタ210-1における、(D - 5E + 20F + 20G)に等しいインクリメントされた「奇数番目」の補間された1/2ピクセルd、第3の累算器レジスタ210-2における、(F - 5G + 20H + 20I)に等しいインクリメントされた「奇数番目」の補間された1/2ピクセルf、および、第4の累算器レジスタ210-3における、(H - 5I + 20J + 20K)に等しいインクリメントされた「奇数番目」の補間された1/2ピクセルhである。ある態様では、これらのインクリメントされた4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhは、メモリにオフロードされ得る。

## 【0061】

ここで、図3および図8を参照すると、一態様では、第3の「偶数番目」のマシンサイクルは、第2の「偶数番目」のマシンサイクルの演算を繰り返すことによって得られる結果を使用して、ただし、図3の第5のピクセルウインドウ位置302-4のピクセルE、F、G、H、I

、J、K、およびLを包含するようにピクセルウインドウレジスタ202が状態802にシフトされ、第3のタップ係数セット[-5, 1, -5, 1, -5, 1, -5, 1]である状態806へと係数レジスタ206がロードされた状態で、(上で説明された第2の「偶数番目」のマシンサイクルによって)以前にインクリメントされた、4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgの値を、最終値へとインクリメントすることができる。ある態様では、以前にインクリメントされた4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgは、メモリから累算器210にロードされてよく、第2の「偶数番目」のマシンサイクルについて説明されたのと実質的に同じ演算で、第3の「偶数番目」のマシンサイクルは、累算器210の内容を、「偶数番目」の1/2ピクセルa、c、e、およびgの以下の最終値へと更新することができる。それらの最終値は、第1の累算器レジスタ210-0における、(A - 5B + 20C + 20D - 5E + F)に等しい「偶数番目」の補間された1/2ピクセルa、第2の累算器レジスタ210-1における、(C - 5D + 20E + 20F - 5G + H)に等しい「偶数番目」の補間された1/2ピクセルc、第3の累算器レジスタ210-2における、(E - 5F + 20G + 20H - 5I + J)に等しい「偶数番目」の補間された1/2ピクセルe、および、第4の累算器レジスタ210-3における、(G - 5H + 20I + 20J - 5K + L)に等しい「偶数番目」の補間された1/2ピクセルgである。これらの値は、図8の領域872において示される。

10

## 【0062】

ここで、図3および図9を参照すると、一態様では、第3の「奇数番目」のマシンサイクルは、第2の「偶数番目」のマシンサイクルの演算を繰り返すことによって得られる結果を使用して、ただし、図3の第6のピクセルウインドウ位置302-5のピクセルE、F、G、H、I、J、K、およびMを包含するようにピクセルウインドウレジスタ202が状態902にシフトされ、図9の領域972において示される以下の値を有する最終的な「奇数番目」の1/2ピクセルb、d、f、およびhを累算器210において形成する状態で、(上で説明された第2の「奇数番目」のマシンサイクルによって)以前にインクリメントされた、4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhの値を、最終値へとインクリメントすることができる。上記の値は、第1の累算器レジスタ210-0における(B - 5C + 20D + 20E - 5F + G)に等しい「奇数番目」の補間された1/2ピクセルb、第2の累算器レジスタ210-1における、(D - 5E + 20F + 20G - 5H + I)に等しい「奇数番目」の補間された1/2ピクセルd、第3の累算器レジスタ210-2における、(F - 5G + 20H + 20I - 5J + K)に等しい「奇数番目」の補間された1/2ピクセルf、および、第4の累算器レジスタ210-3における、(H - 5I + 20J + 20K - 5L + M)に等しい「奇数番目」の補間された1/2ピクセルhである。

20

## 【0063】

図2のマルチタップ統合補間フィルタ200は、「偶数番目」および「奇数番目」の補間された1/2ピクセルの上で説明された例示的なセットを生成する際に、6タップの補間フィルタプロセスを実行したことを諒解されたい。6タップの補間フィルタは例にすぎず、任意の実施形態より包含される、または任意の実施形態の実施であり得る、実施および構造の範囲を限定することは意図されないことを理解されたい。たとえば、当業者は、6タップの補間フィルタに関して示された概念を容易に適用して、8タップの補間フィルタを実現することができる。

30

## 【0064】

図10は、様々な例示的な実施形態による、1つまたは複数の方法およびシステムにおける、短縮マシンサイクルサブピクセル補間の1つのプロセス1000の1つの例示的な論理フローを示す。1つの例示的な動作では、プロセス1000は、1002を経ることで開始してよく、または1002を経ることを含んでよく、ピクセルに割当てられたインデックス(図示されず)に対する「偶数番目」の位置に対応するピクセルを、ピクセルウインドウレジスタにロードすることができ、または別様にそのピクセルによってピクセルウインドウレジスタを設定することができる。たとえば、図3の位置302-0は、1002による「偶数番目」の位置の例であり得る。1つの例示的な動作において、プロセス1000は、1002に対して任意の時間において、しかし好ましくは1006よりも前に、1004において、タップ係数セットをタップ係数レジスタにロードすることができ、または別様にタップ係数セットによってタップ係数

40

50

レジスタを確立することができる。図4を参照すると、様々な例示的な実施形態による実施について、1004においてタップ係数レジスタにタップ係数セットをロードするステップの一例は、たとえば、第1のタップ係数セット[1, -5, 1, -5, 1, -5, 1]によって、タップ係数セットレジスタ206を状態406へとロードまたは設定するステップであり得る。

#### 【0065】

図10を参照すると、ある態様の1つの例示的な動作において、プロセス1000は、好ましくは、1002および1004に対応する状態が確立された状態で、1006へ進み、様々な例示的な実施形態による補間マルチタップの「偶数番目」のマシンサイクルによって、「偶数番目」のサブピクセルのセットを形成することができる。様々な例示的な実施形態による、補間マルチタップフィルタの「偶数番目」のマシンサイクルによって「偶数番目」のサブピクセルのセットを形成するステップ1006の一例は、「偶数番目」の補間された1/2ピクセルa、c、e、およびgを形成するための、図4に関して説明された第1の「偶数番目」のマシンサイクルであり得る。

10

#### 【0066】

図10の参照を続けると、1つの例示的な動作において、プロセス1000は、様々な例示的な実施形態による補間マルチタップフィルタの「偶数番目」のマシンサイクルによって「偶数番目」のサブピクセルのセットを形成するステップ1006の後で、1008へ進み、たとえば、1002における「偶数番目」の位置と関連付けられるインデックスに対する「奇数番目」の位置に対応するピクセルによって、ピクセルウィンドウレジスタの内容をシフトし、または別様に更新することができる。図3を参照すると、位置302-1は、1008による「奇数番目」の位置の一例を示す。ある態様では、1つの例示的な動作において、プロセス1000は、好ましくは、ピクセルウィンドウレジスタ状態が1008に対応しタップ係数レジスタが状態1004と関連付けられる状態で、1010へと進み、1つまたは複数の例示的な実施形態による補間マルチタップフィルタの「奇数番目」のマシンサイクルによって、「奇数番目」のサブピクセルのセットを形成することができる。補間マルチタップフィルタの「奇数番目」のマシンサイクルによって「奇数番目」のサブピクセルのセットを形成するステップ1010の一例は、「奇数番目」の補間された1/2ピクセルb、d、f、およびhを形成する、図5に関して説明された第1の「奇数番目」のマシンサイクルであり得る。

20

#### 【0067】

図10の参照を続けると、「オプション2」として表される論理フローを有するある態様では、プロセス1000に従った例示的な動作は、「奇数番目」の補間された1/2ピクセルb、d、f、およびhのセットを形成するステップ1010の後で、終了条件脱出ブロック1012へ進み、短縮マシンサイクルのサブピクセル補間にに対する所与の終了条件が満たされているかどうかを判定することができる。言い換えれば、「オプション2」として表される論理フローを有する態様では、4個の「偶数番目」の補間された1/2ピクセルa、c、e、およびgと4個の「奇数番目」の補間された1/2ピクセルb、d、f、およびhとの上で説明された形成は、算術演算の全体を含んでよく、言い換えれば、8個の補間された1/2ピクセルa、b、c、d、e、f、g、およびhの完全なセットの最終値を生成することができる。この「オプション2」の態様は、各々が2個の積の合計である、完全なセットの最終的な補間された1/2ピクセルa、b、c、d、e、f、g、およびhの、2マシンサイクルによる生成を実現することができる。本態様による動作では、終了条件脱出ブロック1012のこの第1の例における答は「YES」であり、プロセス1000はブロック1014へ進み、補間された1/2ピクセルa、b、c、d、e、f、g、およびhの形成されたセットを出力することができる。

30

#### 【0068】

図10についてさらに続けると、「オプション1」として表される論理フローを有する別の態様では、終了条件脱出ブロック1012は、奇数番目の補間された1/2ピクセルを形成するステップ1010の直後に終了条件脱出ブロック1012に入るのではなく、代わりに累算するステップ1050へ進むように構成され得る。以下により詳細に説明されるように、オプション1では、終了条件脱出ブロック1012の終了条件は、1006および1010において形成されたサブピクセルの「偶数番目」のセットおよび「奇数番目」のセットを累算するステップ10

40

50

50を繰り返した回数であり得る。

#### 【0069】

1つの例示的な動作では、「オプション1」の態様により構成されるプロセス1000の累算するステップ1050の第1の例は、1014において、別の「偶数番目」の位置に対応するピクセルによって、ピクセルウインドウレジスタ(たとえば、図2のピクセルウインドウレジスタ202)の内容をシフトし、または別様に更新するステップ、および、タップ係数の別のセットをタップ係数レジスタにロードし、または、そのセットによってタップ係数レジスタを別様に更新するステップであり得る。図3を参照すると、位置302-2は、1014による別の「偶数番目」の位置の一例を示す。図4を参照すると、たとえば、第2のタップ係数セット[20, 20, 20, 20, 20, 20, 20]によって、図4のタップ係数セットレジスタ206を状態606へとロードまたは設定するステップは、1014の、別のタップ係数セットをタップ係数セットレジスタにロードするステップ、または別のタップ係数セットによってタップ係数レジスタを別様に更新するステップの一例を示す。図4のピクセルウインドウレジスタ202の状態402はまた、1014における、「偶数番目」の位置の上で説明された図3の例示的な位置302-2を反映する。

10

#### 【0070】

図10の参照を続けると、ある態様では、「偶数番目」のピクセルウインドウレジスタの状態およびタップ係数レジスタの状態が1014における更新に従う、繰り返し累算する態様による1つの例示的な動作では、プロセス1000は、1016へ進み、1006において形成された、または、以下でより詳細に説明されるように、ループ1014、1016、1018、1020、および1112の先行する繰り返しによって以前にインクリメントされた、「偶数番目」のサブピクセルのセットを、インクリメントまたは別様に更新することができる。ここで説明される例では、これは、1014の第1の例であるので、インクリメントするステップは、1006において形成される「偶数番目」のサブピクセルのセットに対して行われる。補間マルチタップフィルタの「偶数番目」のマシンサイクルによって「偶数番目」のサブピクセルのセットをインクリメントする、または別様に更新するステップ1016の一例は、「偶数番目」の補間された1/2ピクセルa、c、e、およびgをインクリメントするための、図6に関して説明された第2の「偶数番目」のマシンサイクルであり得る。

20

#### 【0071】

図10をさらに参照すると、プロセス1000の1つの例示的な動作において、プロセス1000は、補間マルチタップフィルタの「偶数番目」のマシンサイクルによって「偶数番目」のサブピクセルのセットをインクリメントするステップ1016の後で、1018へ進み、たとえば、1002および1014における「偶数番目」の位置と関連付けられるインデックスに対する別の「奇数番目」の位置に対応するピクセルによって、ピクセルウインドウレジスタの内容をシフトし、または別様に更新することができる。たとえば、図3の位置302-3は、1018による「奇数番目」の位置の例であり得る。一態様によれば、例示的な動作において、プロセス1000は、「奇数番目」のピクセルウインドウレジスタの状態が1018に対応し、同じタップ係数レジスタの状態が1016における「偶数番目」の更新において使用される状態で、1020へと進み、「奇数番目」のサブピクセルのセットをインクリメントし、または別様に更新することができる。これを、1020におけるインクリメントするステップまたは更新するステップの第1の例であると仮定すると、基本的な「奇数番目」のサブピクセルは1010において形成されたセットであり得る。累算するステップ150の次の繰り返しにおいて、基本的な「奇数番目」のサブピクセルは、終了条件脱出ブロック1012によるループとして形成される、累算するステップ、すなわち1014、1016、1018、1020の先行する繰り返しによって以前にインクリメントされたセットであることを理解されたい。補間マルチタップフィルタの「奇数番目」のマシンサイクルによって「奇数番目」の補間されたサブピクセルのセットをインクリメントする、または別様に更新するステップ1020の一例は、「奇数番目」の補間された1/2ピクセルb、d、f、およびhをインクリメントするための、図7に関して説明された第2の「奇数番目」のマシンサイクルであり得る。

40

#### 【0072】

50

図10の参照を続けると、1つの例示的な動作において、プロセス1000は、補間マルチタップフィルタの「奇数番目」のマシンサイクルによって、「奇数番目」のサブピクセルのセットをインクリメントするステップ1020の後で、終了条件脱出ブロック1040へ進み、所与の終了条件、この様態では累算するステップ1050を繰り返した所与の回数が満たされたかどうかを判定することができる。図10とともに図8および図9を参照して以下でさらに詳細に説明される1つのそのような例は、この例では図8の第2の「偶数番目」のマシンサイクルによるものである「偶数番目」の補間された1/2ピクセルa、c、e、およびgの例示的な第2のインクリメントおよび最後のインクリメントを実行するステップ、および、この例では図9の第2の「奇数番目」のマシンサイクルによるものである「奇数番目」の補間された1/2ピクセルb、d、f、およびhの例示的な第2のインクリメントおよび最後のインクリメントを実行するステップである。

10

## 【0073】

図10をさらに参照すると、この例では、所与の終了条件は、累算するステップ1050の2回以上の繰り返しであるので、終了条件脱出ブロック1012における答は「NO」であることが仮定される。したがって、プロセス1000は、累算するステップ1050に戻る。1014、1016、1018、1020、1012のループは、終了条件脱出ブロック1012における終了条件が満たされるまで続く。図8および図9を参照して説明される例を参照すると、これらは、1014、1016、1018、および1020の累算するステップ1050のループの繰り返しの一例を示す。終了条件脱出ブロック1012における終了条件が満たされると、サブピクセルを累算するステップ1050は完了し、プロセス1000は1014へ進み、最終的な補間されたサブピクセルを出力することができる。図8および図9を参照すると、最終的な補間されたサブピクセルを出力する1つの例示的なステップ1014は、サブピクセルa、b、c、d、e、f、g、およびhの最終値の説明された生成である。

20

## 【0074】

図11は、一例として、1つの例示的な実施形態の2つピクセル行セクション1102\_0および1102\_1による、短縮サイクルマルチタップ補間フィルタ装置およびフィルタ方法において処理され得る入力1100を示す。「全体の」ピクセル0A、0B、0C、0D、0E、0F、0G、0H、0I、0J、0K、0L、および0M(まとめて「ピクセル0A～0M」)を有するピクセル行セクション1102\_0が示され、「全体の」ピクセル1A、1B、1C、1D、1E、1F、1G、1H、1I、1J、1K、1L、および1M(まとめて「ピクセル1A～1M」)を有するピクセル行セクション1102\_1が示される。例示的な実施形態による例示的なプロセスを説明する際、ピクセル0A～0Mおよび1A～1Mは、所与の値、たとえば、限定はされないが、光検出器(図示されない)の出力またはフィルタリングされた出力を有することが仮定される。しかし、語句「ピクセル行セクション」の中の「行」という用語は、ピクセルが行対列のビデオアレイの「行」に由来しなければならないことを必ずしも意味しないことを理解されたい。たとえば、ピクセル行セクション1102\_0および1102\_1は、アレイの隣接する、または別様に間隔を空けられた「列」(図示されない)、アレイの隣接する対角方向(図示されない)、またはアレイの他のそれぞれの領域に由来するものであってよい。

30

## 【0075】

図11の参照を続けると、1/2ピクセル位置0a、0b、0c、0d、0e、0f、0g、および0h(まとめて「1/2ピクセル0a～0h」)を有するピクセル行セクション1102\_0も示され、同様に、1/2ピクセル位置1a、1b、1c、1d、1e、1f、1g、および1h(まとめて「1/2ピクセル1a～1h」)を有するピクセル行セクション1102\_1が示される。

40

## 【0076】

付録Aを参照すると、擬似コードセクションA1は、1つの例示的な実施形態による、短縮サイクルマルチタップ補間フィルタ装置およびフィルタ方法のための、かつ、例示的なピクセル行102\_0のピクセル0A～0Mおよびピクセル行102\_1のピクセル1A～1Mを使用して、1つまたは複数の例示的な実施形態による、1/2ピクセル0a～0hおよび1/2ピクセル1a～1hを生成する際の演算のための、例示的なコンピュータ実行可能命令を示す。

## 【0077】

50

図12は、1つの例示的な実施形態による、図2の短縮サイクルマルチタップ補間フィルタ200の、インターリープされたクロマ成分の構成1200の1つの双線形補間を示す。図12を参照すると、ある態様では、インターリープされたクロマ成分の構成1200は、Rssレジスタ202の中の8個の8ビットの符号付きバイトを、Rttレジスタ206の中の対応する8ビットの符号なしのバイトと乗算することができ、乗算器204から加算デバイス208に向けられた矢印により示されるような交差するペアにおける乗算結果を加算する方式で、加算デバイス208-0、208-1、208-2、および208-3を構成する。図2と図12を比較すると、乗算器204から加算デバイス208への乗算結果のそれぞれのルーティングまたは結合は、様々な説明される動作に従つたものであることが諒解されるだろう。図2と図12との間で、加算デバイス208への乗算器204の結合のモードを変更するための、スイッチング、ルーティング、または結合の論理(図示されず)のための技法に関して、一態様では、当業者は、本開示に基づいて、従来のデジタルシグナルプロセッサの設計技法を適用することによってそのような論理を選択し、または別様に実装できるので、さらなる詳細な説明は省略される。

10

## 【0078】

図13は、1つの例示的な実施形態による、平面的なクロマ成分の双線形補間に関与し得る、1つの例示的なピクセルのアレイ1300を示す。

## 【0079】

図14は、図13の例示的なアレイ1300に基づく、平面的なクロマ成分の双線形補間ににおいて生成される1/4ピクセルを有する、1つの例示的なピクセルのアレイ1400を示す。

20

## 【0080】

付録Aを参照すると、擬似コードセクションA2は、図13および図14を参照して、1つまたは複数の例示的な実施形態による装置および方法における、平面的なクロマ成分の双線形補間ににおいて1/4ピクセルを生成するためのコンピュータ実行可能命令の例を示す。

20

## 【0081】

図15は、本開示の1つまたは複数の実施形態が有利に利用され得る例示的なワイヤレス通信システム1500を示す。説明のために、例示的なワイヤレス通信システム1500は、3つの遠隔ユニット1520、1530および1550、ならびに2つの基地局1540を示す。従来のワイヤレス通信システムは、はるかに多くのリモートユニットおよび基地局を有する場合があることを認識されよう。リモートユニット1520、1530、および1550は、半導体デバイス1525、1535、および1555を含んでよく、半導体デバイス1525、1535、および1555の1つまたは複数は、様々な例示的な実施形態による1つまたは複数の短縮マルチタップ補間フィルタ、たとえば、限定されることなく、図3から図10を参照して説明されたようなサブピクセル補間を実行するように構成可能であり、一態様では、図12および図13を参照して説明されたような双線形補間を実行するように、図11を参照して説明されたように構成可能である、図2を参照して説明された短縮サイクルマルチタップ補間フィルタを含み得る。図15は、基地局1540からリモートユニット1520、1530、および1550への順方向リンク信号1580、ならびにリモートユニット1520、1530、および1550から基地局1540への逆方向リンク信号1590を示す。

30

## 【0082】

図15を参照すると、リモートユニット1520は携帯電話として示され、リモートユニット1530はポータブルコンピュータとして示され、リモートユニット1550はワイヤレスローカルループシステム内の固定位置リモートユニットとして示される。これらは、リモートユニット1520、1530、および1550のいずれかを実装し得るデバイスの例にすぎないことを理解されたい。たとえば、リモートユニット1520、1530、および1550は、携帯電話、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、(GPS対応デバイスなどの)ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、メータ読み取り機器などの固定位置データユニット、またはデータもしくはコンピュータ命令の記憶もしくは取出しを行う任意の他のデバイス、またはそれらの任意の組合せのうちの、1つまたは複数であり得る。図15は、本開示の教示による遠隔ユニットを示すが、本開示はこれらの例示的な

40

50

示されたユニットに限定されない。本開示の実施形態は、試験および特性評価のための、メモリおよびオンチップ回路を含む能動的な集積回路を有する少なくとも1つの半導体ダイを含む、任意のデバイスにおいて適切に採用され得る。

#### 【0083】

情報および信号は、多種多様な技術および技法のいずれかを使用して表され得ることを当業者は諒解されよう。たとえば、上記の説明全体にわたって言及され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界または磁性粒子、光場または光学粒子、あるいはそれらの任意の組合せによって表され得る。

#### 【0084】

さらに、本明細書で開示された実施形態に関する説明された様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実装され得ることを、当業者は諒解されよう。ハードウェアとソフトウェアのこの互換性を明確に示すために、様々な例示的なコンポーネント、ブロック、モジュール、回路、およびステップは、上では概してそれらの機能について説明された。そのような機能がハードウェアとして実装されるか、ソフトウェアとして実装されるかは、具体的な適用例および全体的なシステムに課される設計制約に依存する。当業者は、説明された機能を具体的な適用例ごとに様々な方法で実装し得るが、そのような実装の決定は、本発明の範囲からの逸脱を生じるものと解釈されるべきではない。

10

20

#### 【0085】

本明細書で開示された実施形態と関連して説明された方法、シーケンス、および/またはアルゴリズムは、ハードウェアで、プロセッサによって実行されるソフトウェアモジュールで、またはその2つの組合せで直接具現化され得る。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態の記憶媒体中に存在し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体はプロセッサと一体であり得る。

30

#### 【0086】

したがって、本発明の一実施形態は、説明された実施形態の方法に従うものとして、受信されたシリアルビットストリームを位相サンプリングするための方法を具現化する、コンピュータ可読媒体を含み得る。したがって、本発明は図示の例に限定されず、本明細書で説明された機能を実行するためのいかなる手段も、本発明の実施形態中に含まれる。

#### 【0087】

上記の開示は本発明の例示的な実施形態を示すが、添付の特許請求の範囲によって規定される本発明の範囲から逸脱することなく、本明細書において様々な変更および修正が行われ得ることに留意されたい。本明細書で説明された本発明の実施形態による方法クレームの機能、ステップおよび/または動作は、特定の順序で実行されなくてもよい。さらに、本発明の要素は、単数形で説明または特許請求されていることがあるが、単数形に限定することが明示的に述べられていない限り、複数形が企図される。

40

#### 【0088】

【数 1 a】

## APPENDIX A

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0A | 0B | 0C | 0a | 0D | 0b | 0E | 0c | 0F | 0d | 0G | 0e | 0H | 0f | 0I | 0g | 0J | 0h | 0K | 0L | 0M |

| 1A | 1B | 1C | 1a | 1D | 1b | 1E | 1c | 1F | 1d | 1G | 1e | 1H | 1f | 1I | 1g | 1J | 1h | 1K | 1L | 1M |

FIG. 12

**Pseudo-Code Section A1.**

10

Comments:

These computer executable instructions, when executed, generate the above FIG. 11 half-pixels 0a, 0b, 0c, 0c, 0d, 0e, 0f, 0g and 0h, and half-pixels 11a, 1b, 1c, 1d, 1e, 1f, 1g and 1h.

It will be understood that:

R1:0 is a co-efficient set corresponding to FIG. 4 state 406;

R3:2 is a co-efficient set corresponding to FIG. 6 state 602;

R5:4 is a co-efficient set corresponding to FIG. 8 state 802;

R7:6 is an initial state of a pixel window register, corresponding to FIG. 4 state 402, for the 0H – 0A pixels;

R9:8 is an initial state of a pixel window register, corresponding to FIG. 4 state 402, for the 1H – 1A pixels; and

the operation “MEMB\_FIFO()” represents a shifting of the pixel window register, i.e., the operations represented by the state sequence of FIG. 4 state 402, FIG. 5 state 502, FIG. 6 state 602 ... FIG. 9 state 902.

20

Code:

```

//R1:0 = c1|c0|c1|c0|c1|c0|c1|c0=-5|1|-5|1|-5|1|-5|1

//R3:2 = c3|c2|c3|c2|c3|c2|c3|c2=20|20|20|20|20|20|20|20|20|20|20|20

//R5:4 = c5|c4|c5|c4|c5|c4|c5|c4=1|-5|1|-5|1|-5|1|-5

//R7:6 = 0H|0G|0F|0E|0D|0C|0B|0A

//R9:8 = 1H|1G|1F|1E|1D|1C|1B|1A

{

R11:10 = VDMPYBSU(R1:0,R7:6):SAT // [0g|0e|0c|0a]

// [a=A-5B]

// [c=C-5D]

// [e=E-5F]

// [g=G-5H]

R7:6 = MEMB_FIFO() // [0I|0H|0G|0F|0E|0D|0C|0B]

R15:14 = VDMPYBSU(R1:0,R9:8):SAT // [1g|1e|1c|1a]

// [a=A-5B]

// [c=C-5D]

// [e=E-5F]

// [g=G-5H]

R9:8 = MEMB_FIFO()

// [1I|1H|1G|1F|1E|1D|1C|1B]

}

{

R13:12 += VDMPYBSU(R1:0,R7:6):SAT // [0h|0f|0d|0b]

// [b=B-5C]

}

```

30

40

【数1b】

```

// [d=D-5E      ]

// [f=F-5G      ]

// [h=H-5I      ] 10

R7:6 = MEMB_FIFO() // [0J|0I|0H|0G|0F|0E|0D|0C ]

R17:16 += VDMPYBSU(R1:0,R9:8):SAT // [1h|1f|1d|1b ]

// [b=B-5C      ]

// [d=D-5E      ]

// [f=F-5G      ]

// [h=H-5I      ] 20

R9:8 = MEMB_FIFO() // [1J|1I|1H|1G|1F|1E|1D|1C ]

}

{

R11:10 += VDMPYBSU(R1:0,R7:6):SAT // [0g|0e|0c|0a ]

// [a=A-5B+20C+20D ]

// [c=C-5D+20E+20F ]

// [e=E-5F+20G+20H ]

// [g=G-5H+20I+20J ] 30

R7:6 = MEMB_FIFO() // [0K|0J|0I|0H|0G|0F|0E|0D ]

R15:14 += VDMPYBSU(R1:0,R9:8):SAT // [1g|1e|1c|1a ]

// [a=A-5B+20C+20D ]

// [c=C-5D+20E+20F ]

// [e=E-5F+20G+20H ]

// [g=G-5H+20I+20J ] 40

R9:8 = MEMB_FIFO() // [1K|1J|1I|1H|1G|1F|1E|1D ]

}

{

R13:12 += VDMPYBSU(R1:0,R7:6):SAT // [0h|0f|0d|0b ]

// [b=B-5C+20D+20E]

// [d=D-5E+20F+20G]

// [f=F-5G+20H+20I]

// [h=H-5I+20J+20K]

R7:6 = MEMB_FIFO() // [0L|0K|0J|0I|0H|0G|0F|0E ]

R17:16 += VDMPYBSU(R1:0,R9:8):SAT // [1h|1f|1d|1b ]

// [b=B-5C+20D+20E]

// [d=D-5E+20F+20G]

// [f=F-5G+20H+20I]

// [h=H-5I+20J+20K] 50

R9:8 = MEMB_FIFO() // [1L|1K|1J|1I|1H|1G|1F|1E ]

}

{

R11:10 += VDMPYBSU(R1:0,R7:6):SAT // [0g|0e|0c|0a ]

// [a=A-5B+20C+20D-5E+F]

// [c=C-5D+20E+20F-5G+H]

// [e=E-5F+20G+20H-5I+J]

// [g=G-5H+20I+20J-5K+L]

```

【0090】

50

【数1c】

```

R7:6 = MEMB_FIFO() // [0M|0L|0K|0J|0I|0H|0G|0F ] 10

R15:14 += VDMPYBSU(R1:0,R9:8):SAT // [1g|1e|1c|1a ]

// [a=A-5B+20C+20D-5E+F]

// [c=C-5D+20E+20F-5G+H]

// [e=E-5F+20G+20H-5I+J]

// [g=G-5H+20I+20J-5K+L]

R9:8 = MEMB_FIFO() // [1M|1L|1K|1J|1I|1H|1G|1F ] 10

}

{

R13:12 += VDMPYBSU(R1:0,R7:6):SAT // [0h|0f|0d|0b ]

// [b=B-5C+20D+20E-5F+G]

// [d=D-5E+20F+20G-5H+I]

// [f=F-5G+20H+20I-5J+K]

// [h=H-5I+20J+20K-5L+M] 20

R17:16 += VDMPYBSU(R1:0,R9:8):SAT // [1h|1f|1d|1b ]

// [b=B-5C+20D+20E-5F+G]

// [d=D-5E+20F+20G-5H+I]

// [f=F-5G+20H+20I-5J+K]

// [h=H-5I+20J+20K-5L+M] 20

}

{

R11:10 = PACKHL(R12,R10) // [0d|0c|0b|0a ]

R13:12 = PACKHL(R13,R11) // [0h|0g|0f|0e ]

R15:14 = PACKHL(R16,R14) // [1d|1c|1b|1a ]

R17:16 = PACKHL(R17,R15) // [1h|1g|1f|1e ] 30

}

{

R10 = VASRHUB(R11:10,#5):RND:SAT // [0d|0c|0b|0a ]

R11 = VASRHUB(R13:12,#5):RND:SAT // [0h|0g|0f|0e ]

}

{

R14 = VASRHUB(R15:14,#5):RND:SAT // [1d|1c|1b|1a ]

R15 = VASRHUB(R17:16,#5):RND:SAT // [1h|1g|1f|1e ] 30

}

{

MEMD() = R11:10 // [store

// [0h|0g|0f|0e|0d|0c|0b|0a ] 40

MEMD() = R15:14 // [store

// [1h|1g|1f|1e|1d|1c|1b|1a ]

}

```

【0091】

【数1d】

Pseudo-Code Section A2

|    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|

| 0A | 0B | 0C | 0D | 0E | 0F | 0G | 0H | 0I |

| 0a | 0b | 0c | 0d | 0e | 0f | 0g | 0h |    |

| 1A | 1B | 1C | 1D | 1E | 1F | 1G | 1H | 1I |

| 1a | 1b | 1c | 1d | 1e | 1f | 1g | 1h |    |

| 2A | 2B | 2C | 2D | 2E | 2F | 2G | 2H | 2I |

10

FIG. 13

```

//R1:0 = c1|c0|c1|c0|c1|c0|c1|c0

//R3:2 = c3|c2|c3|c2|c3|c2|c3|c2

//R5:4 = 0g|0e|0c|0a

//          0a = c0*0A+c1*0B

//          0c = c0*0C+c1*0D

//          0e = c0*0E+c1*0F

//          0g = c0*0G+c1*0H

//R7:6 = 0h|0f|0d|0b

//          0b = c0*0B+c1*0C

//          0d = c0*0D+c1*0E

//          0f = c0*0F+c1*0G

//          0h = c0*0H+c1*0I

//R9:8 = 1H|1G|1F|1E|1D|1C|1B|1A

{

R5:4 += VDMPYBSU(R3:2,R9:8):SAT      // [0g|0e|0c|0a]

// [0a=c0*0A+c1*0B+c2*1A+c3*1B ]

// [0c=c0*0C+c1*0D+c2*1C+c3*1D ]

// [0e=c0*0E+c1*0F+c2*1E+c3*1F ]

// [0g=c0*0G+c1*0H+c2*1G+c3*1H ]

R11:10 = VDMPYBSU(R1:0,R9:8):SAT // [1g|1e|1c|1a]

// [1a=c0*1A+c1*1B]

// [1c=c0*1C+c1*1D]

// [1e=c0*1E+c1*1F]

// [1g=c0*1G+c1*1H]

R9:8 = MEMB_FIFO()           // [0I|0H|0G|0F|0E|0D|0C|0B]

}

R7:6 += VDMPYBSU(R3:2,R9:8):SAT // [0h|0f|0d|0b]

// [0b=c0*0B+c1*0C+c2*1B+c3*1C ]

// [0d=c0*0D+c1*0E+c2*1D+c3*1E ]

// [0f=c0*0F+c1*0G+c2*1F+c3*1G ]

// [0h=c0*0H+c1*0I+c2*1H+c3*1I ]

```

20

30

40

50

【0092】

【数1e】

```

R13:12 = VDMPYBSU(R1:0, R9:8) : SAT // [1h|1f|1d|1b ]

// [1b=c0*1B+c1*1C]

// [1d=c0*1D+c1*1E]

// [1f=c0*1F+c1*1G]

// [1h=c0*1H+c1*1I]

}

{

R15:14 = VASRH(R5:4, #6) : RND

// [??|0g|??|0e|??|0c|??|0a] ] 10

R17:16 = VASRH(R7:6, #6) : RND

// [??|0h|??|0f|??|0d|??|0b] ]

}

{

R19:18 = SHUFFEB(R17:16, R15:14)

// [0h|0g|0f|0e|0d|0c|0b|0a] ]

}

{

MEMD() = R19:18 // [store ] ] 20

// [0h|0g|0f|0e|0d|0c|0b|0a]

}

```

|       |       |       |       |       |

|-------|-------|-------|-------|-------|

| 0A 0B | 0C 0D | 0E 0F | 0G 0H | 0I 0J |

| 0a 0b | 0c 0d | 0e 0f | 0g 0h |       |

| 1A 1B | 1C 1D | 1E 1F | 1G 1H | 1I 1J |

| 1a 1b | 1c 1d | 1e 1f | 1g 1h |       |

| 2A 2B | 2C 2D | 2E 2F | 2G 2H | 2I 2J |

FIG. 14

```

// R1:0 = c1|c1|c0|c0|c1|c1|c0|c0

// R3:2 = c3|c3|c2|c2|c3|c3|c2|c2 30

// R5:4 = 0f|0e|0b|0a

//      0a = c0*0A+c1*0C

//      0b = c0*0B+c1*0D

//      0e = c0*0E+c1*0G

//      0f = c0*0F+c1*0H

// R7:6 = 0h|0g|0d|0c

//      0c = c0*0C+c1*0E

//      0d = c0*0D+c1*0F

//      0g = c0*0G+c1*0I

//      0h = c0*0H+c1*0J

// R9:8 = 1H|1G|1F|1E|1D|1C|1B|1A 40

{

R5:4 += VXDMPYBSU(R3:2, R9:8) : SAT // [0f|0e|0b|0a ]

// [0a=c0*0A+c1*0C+c2*1A+c3*1C ]

// [0b=c0*0B+c1*0D+c2*1B+c3*1D ]

// [0e=c0*0E+c1*0G+c2*1E+c3*1G ]

// [0f=c0*0F+c1*0H+c2*1F+c3*1H ]

```

【0093】

【数1f】

```

R11:10 = VXDMOPYBSU(R1:0,R9:8):SAT // [1f|1e|1b|1a]

// [1a=c0*1A+c1*1C]

// [1b=c0*1B+c1*1D]

// [1e=c0*1E+c1*1G]

// [1f=c0*1F+c1*1H]

R9:8 = MEMH_FIFO()

// [1J|1I|1H|1G|1F|1E|1D|1C] ] 10

}

{

R7:6 += VXDMOPYBSU(R3:2,R9:8):SAT // [0h|0g|0d|0c

] // [0c=c0*0C+c1*0E+c2*1C+c3*1E]

// [0d=c0*0D+c1*0F+c2*1D+c3*1F]

// [0g=c0*0G+c1*0I+c2*1G+c3*1I]

// [0h=c0*0H+c1*0J+c2*1H+c3*1J] 20

R13:12 = VXDMOPYBSU(R1:0,R9:8):SAT // [1h|1g|1d|1c]

// [1c=c0*1C+c1*1E]

// [1d=c0*1D+c1*1F]

// [1g=c0*1G+c1*1I]

// [1h=c0*1H+c1*1J]

}

{

R14 = VASRHUB(R5:4,#6):RND:SAT // [0f|0e|0b|0a]

R15 = VASRHUB(R7:6,#6):RND:SAT // [0h|0g|0d|0c] 30

}

{

R17:16 = PACKHL(R15,R14)

// [0h|0g|0f|0e|0d|0c|0b|0a] ] 30

}

{

MEMD() = R17:16 // [store

// [0h|0g|0f|0e|0d|0c|0b|0a] ] 30

}

```

【符号の説明】

【0094】

- |     |                   |    |

|-----|-------------------|----|

| 200 | マルチタップ統合補間フィルタ    |    |

| 202 | ピクセルウィンドウレジスタ     |    |

| 204 | 乗算器               | 40 |

| 206 | タップ係数セットレジスタ      |    |

| 208 | 加算デバイス            |    |

| 210 | 累算器               |    |

| 212 | 2Sビットの符号付き飽和論理    |    |

| 300 | ステップ移行のグラフィカルなモデル |    |

| 302 | ピクセルウィンドウ         |    |

| 402 | 状態                |    |

| 406 | 状態                |    |

| 410 | 内容                |    |

| 502 | 状態                |    |

40

50

|        |                    |    |

|--------|--------------------|----|

| 572    | 領域                 |    |

| 602    | 状態                 |    |

| 606    | 状態                 |    |

| 610    | 内容                 |    |

| 672    | 領域                 |    |

| 702    | 状態                 |    |

| 772    | 領域                 |    |

| 802    | 状態                 |    |

| 806    | 状態                 |    |

| 872    | 領域                 | 10 |

| 902    | 状態                 |    |

| 972    | 領域                 |    |

| 1100   | 入力                 |    |

| 1102_0 | ピクセル行セクション         |    |

| 1102_2 | ピクセル行セクション         |    |

| 1200   | インターリープされたクロマ成分の構成 |    |

| 1300   | ピクセルのアレイ           |    |

| 1400   | ピクセルのアレイ           |    |

| 1500   | ワイヤレス通信システム        |    |

| 1520   | リモートユニット           | 20 |

| 1525   | 半導体デバイス            |    |

| 1530   | リモートユニット           |    |

| 1535   | 半導体デバイス            |    |

| 1540   | 基地局                |    |

| 1550   | リモートユニット           |    |

| 1555   | 半導体デバイス            |    |

| 1580   | 順方向リンク信号           |    |

| 1590   | 逆方向リンク信号           |    |

FIG. 1

FIG. 3

FIG. 2

FIG. 4

【 図 5 】

【 図 6 】

【 四 7 】

【 四 8 】

【図 9】

【図 10】

【図 11】

FIG. 11

【図 12】

【図 13】

|    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|

| 0A | 0B | 0C | 0D | 0E | 0F | 0G | 0H | 0I |

| 0a | 0b | 0c | 0d | 0e | 0f | 0g | 0h | 0i |

| 1A | 1B | 1C | 1D | 1E | 1F | 1G | 1H | 1I |

| 1a | 1b | 1c | 1d | 1e | 1f | 1g | 1h | 1i |

| 2A | 2B | 2C | 2D | 2E | 2F | 2G | 2H | 2I |

FIG. 13

【図 15】

FIG. 15

【図 14】

|    |    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|

| 0A | 0B | 0C | 0D | 0E | 0F | 0G | 0H | 0I | 0J |

| 0a | 0b | 0c | 0d | 0e | 0f | 0g | 0h | 0i | 0j |

| 1A | 1B | 1C | 1D | 1E | 1F | 1G | 1H | 1I | 1J |

| 1a | 1b | 1c | 1d | 1e | 1f | 1g | 1h | 1i | 1j |

| 2A | 2B | 2C | 2D | 2E | 2F | 2G | 2H | 2I | 2J |

FIG. 14

## 【手続補正書】

【提出日】平成26年2月19日(2014.2.19)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

ピクセルアレイに対する補間されたピクセルを生成するための方法であって、

前記ピクセルアレイのピクセルウィンドウをウィンドウレジスタにロードするステップと、

所与のタップ係数セットをタップ係数レジスタにロードするステップと、

前記ウィンドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットに対する初期値を生成するステップと、前記ピクセルアレイの別の前記ピクセルによって前記ウィンドウレジスタを更新することによって、アレイの方向に沿って前記ピクセルウィンドウをシフトするステップと、前記ウィンドウレジスタ中の前記シフトされたピクセルウィンドウと、前記タップ係数レジスタ中の前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットに対する初期値を生成するステップと、所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルの値および前記奇数番目の補間されたサブピクセルの値をインクリメントするステップであって、インクリメントする各ステップが、前記タップ係数レジスタ中の前記タップ係数セットを別のタップ係数セットへと更新

するステップと、

前記ピクセルアレイの別の前記ピクセルによって前記ウインドウレジスタを更新することによって、前記方向に沿って前記ピクセルウインドウをシフトするステップと、

前記ウインドウレジスタ中の前記ピクセルウインドウと、前記タップ係数レジスタ中の前記別のタップ係数セットとに基づいて、前記偶数番目の補間されたサブピクセルの前記それぞれの値をインクリメントするステップと、

前記ピクセルアレイの別の前記ピクセルによって前記ウインドウレジスタを再び更新することによって、前記方向に沿って前記ピクセルウインドウを再びシフトするステップと、

前記ウインドウレジスタ中の前記ピクセルウインドウと、前記タップ係数レジスタ中の前記別のタップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルの前記それぞれの値をインクリメントするステップと

を含む、インクリメントするステップと、

前記終了条件が満たされると、偶数番目の補間されたサブピクセルの前記セットおよび奇数番目の補間されたサブピクセルの前記セットを出力するステップとを含む、方法。

#### 【請求項 2】

偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、前記偶数番目の補間されたサブピクセルの少なくとも1つの前記初期値を積の合計として生成し、少なくとも1つの偶数番目の補間されたピクセルの前記値をインクリメントする各ステップが、積の合計によって前記値をインクリメントし、前記終了条件が、前記偶数番目の補間されたピクセルの少なくとも1つが6個の積の合計を有することに対応する、請求項1に記載の方法。

#### 【請求項 3】

偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、単一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、単一のマシンサイクルの間に行われる、請求項1に記載の方法。

#### 【請求項 4】

偶数番目の補間されたサブピクセルの前記セットが、4個の偶数番目の補間されたサブピクセルを含み、前記4個の偶数番目の補間されたサブピクセルの各々の前記初期値が、対応する2個の積の合計として生成され、前記2個の積の各々が、前記ウインドウレジスタ中の前記ピクセルウインドウからのピクセルと、係数レジスタ中の係数の前記所与のセットからの係数との積であり、奇数番目の補間されたサブピクセルの前記セットが、4個の奇数番目の補間されたサブピクセルを含み、前記4個の奇数番目の補間されたサブピクセルの各々の前記初期値が、対応する2個の積の合計として生成され、前記2個の積の各々が、前記ウインドウレジスタ中の前記ピクセルウインドウからのピクセルと、係数レジスタ中にロードされた係数の前記所与のセットからの係数との積である、請求項3に記載の方法。

#### 【請求項 5】

前記4個の偶数番目の補間されたサブピクセルの前記それぞれの値をインクリメントする各ステップが、別の対応する2個の積の合計によって前記値の各々をインクリメントするステップを含み、前記2個の積の各々が、前記シフトするステップによってシフトされ前記ウインドウレジスタに記憶された前記ピクセルウインドウからのピクセルと、前記タップ係数レジスタ中の係数の別のセットからの係数との積であり、

前記4個の奇数番目の補間されたサブピクセルの前記それぞれの値をインクリメントする各ステップが、別の対応する2個の積の合計によって前記値の各々をインクリメントするステップを含み、前記別の対応する2個の積の各々が、前記再びシフトするステップによってシフトされ前記ウインドウレジスタに記憶された前記ピクセルウインドウからのピクセルと、前記係数レジスタ中の係数の前記別のセットからの係数との積である、請求項4に記載の方法。

**【請求項 6】**

前記タップ係数レジスタ中の係数の前記セットを更新し、前記ウインドウレジスタ中の前記ピクセルウインドウをシフトするステップが、前記偶数番目の補間されたサブピクセルの前記それぞれの値をインクリメントするステップと組み合わされて、单一のマシンサイクルの間に行われ、前記奇数番目の補間されたサブピクセルの前記それぞれの値をインクリメントするステップと組み合わされた、前記ウインドウレジスタ中の前記ピクセルウインドウを再びシフトする前記ステップが、单一のマシンサイクルの間に行われる、請求項5に記載の方法。

**【請求項 7】**

偶数番目の補間されたサブピクセルの前記セットが少なくとも4個の偶数番目の補間されたサブピクセルを含み、前記4個の偶数番目の補間されたサブピクセルの各々の前記初期値が、対応する2個の積の合計として生成され、

奇数番目の補間されたサブピクセルの前記セットが少なくとも4個の奇数番目の補間されたサブピクセルを含み、前記4個の奇数番目の補間されたサブピクセルの各々の前記初期値が、対応する2個の積の合計として生成され、

前記4個の偶数番目の補間されたサブピクセルの前記それぞれの値をインクリメントする各ステップが、別の対応する2個の積の合計によって前記値の各々をインクリメントするステップを含み、前記2個の積の各々が、前記シフトするステップによってシフトされ前記ウインドウレジスタに記憶された前記ピクセルウインドウからのピクセルと、前記タップ係数レジスタ中の係数の別のセットからの係数との積であり、

前記4個の奇数番目の補間されたサブピクセルの前記それぞれの値をインクリメントする各ステップが、別の対応する2個の積の合計によって前記値の各々をインクリメントするステップを含み、前記2個の積の各々が、前記再びシフトするステップによってシフトされ前記ウインドウレジスタに記憶された前記ピクセルウインドウからのピクセルと、前記タップ係数レジスタ中の係数の前記別のセットからの係数との積である、請求項1に記載の方法。

**【請求項 8】**

前記偶数番目の補間されたサブピクセルの前記値および前記奇数番目の補間されたサブピクセルの前記値を2回累算すると、前記終了条件が満たされる、請求項1に記載の方法。

**【請求項 9】**

前記偶数番目の補間されたサブピクセルの前記初期値を生成するステップが、前記ウインドウレジスタ中の前記ピクセルウインドウからのピクセルを、前記タップ係数レジスタ中の前記タップ係数セットからの対応するタップ係数と乗算して、対応する積を生成するステップと、前記積のペアを合計して積の合計のセットを生成するステップと、積の合計の前記セットを、偶数番目の補間されたサブピクセルの前記セットの前記初期値として累算器へとロードするステップと、偶数番目の補間されたサブピクセルの前記セットの前記初期値を、累算器レジスタからメモリへとオフロードするステップとを含み、

前記奇数番目の補間されたサブピクセルの前記初期値を生成するステップが、前記ウインドウレジスタ中の前記ピクセルウインドウからのピクセルを、前記タップ係数レジスタ中の前記タップ係数セットからの対応するタップ係数と乗算して、対応する積を生成するステップと、前記積のペアを合計して積の合計のセットを生成するステップと、積の合計の前記セットの前記初期値を、奇数番目の補間されたサブピクセルの前記セットとして前記累算器へとロードするステップと、奇数番目の補間されたサブピクセルの前記セットの前記初期値を、前記累算器レジスタから前記メモリへとオフロードするステップとを含む、請求項1に記載の方法。

**【請求項 10】**

偶数番目の補間されたサブピクセルの前記セットの前記初期値を生成するステップが、单一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットの前記初期値を生成するステップが、单一のマシンサイクルの間に行われる、請求項9に記載の方法。

**【請求項 1 1】**

前記偶数番目の補間されたサブピクセルの前記値をインクリメントする各ステップが、偶数番目の補間されたサブピクセルの前記セットを前記メモリから前記累算器レジスタへとロードするステップと、前記シフトするステップによってシフトされ前記ウインドウレジスタに記憶された前記ピクセルウィンドウからのピクセルを、前記タップ係数レジスタ中の前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを前記累算器レジスタからの対応する偶数番目の補間されたサブピクセルの値と合計して、累算された積の合計のセットを生成するステップと、累算された積の合計の前記セットを、偶数番目の補間されたサブピクセルの前記セットの更新された値として前記累算器レジスタへとロードするステップと、偶数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含み、

前記奇数番目の補間されたサブピクセルの前記値をインクリメントする各ステップが、奇数番目の補間されたサブピクセルの前記セットを前記メモリから前記累算器レジスタへとロードするステップと、前記再びシフトするステップによってシフトされ前記ウインドウレジスタに記憶された前記ピクセルウィンドウからのピクセルを、前記タップ係数レジスタ中の前記タップ係数セットからの対応するタップ係数と乗算して、対応する積の合計を生成するステップと、積の前記合計のペアを前記累算器レジスタからの対応する奇数番目の補間されたサブピクセルの値と合計して、累算された積の合計のセットを生成するステップと、累算された積の合計の前記セットを、奇数番目の補間されたサブピクセルの前記セットの更新された値として前記累算器レジスタへとロードするステップと、奇数番目の補間されたサブピクセルの前記セットを、前記累算器レジスタから前記メモリへとオフロードするステップとを含む、請求項9に記載の方法。

**【請求項 1 2】**

偶数番目の補間されたサブピクセルの前記セットの前記値をインクリメントするステップが、単一のマシンサイクルの間に行われ、奇数番目の補間されたサブピクセルの前記セットの前記値をインクリメントするステップが、単一のマシンサイクルの間に行われる、請求項11に記載の方法。

**【請求項 1 3】**

ピクセルアレイに対する補間されたピクセルを生成するための装置であって、

前記ピクセルアレイのピクセルウィンドウを記憶するための手段と、

タップ係数セットを記憶するための手段と、

前記ピクセルアレイからの前記ピクセルウィンドウ中のピクセルと、タップ係数セットを記憶するための前記手段によって記憶された所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットに対する初期値を生成するための手段と、

ピクセルウィンドウを記憶するための前記手段によって記憶された前記ピクセルウィンドウを別の前記ピクセルによって更新することによって、アレイの方向に沿って前記ピクセルウィンドウをシフトするための手段と、

ピクセルウィンドウを記憶するための手段に記憶された前記シフトされたピクセルウィンドウと、タップ係数セットを記憶するための前記手段によって記憶された前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットに対する初期値を生成するための手段と、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルの値および前記奇数番目の補間されたサブピクセルの値をインクリメントするための手段であって、

タップ係数セットを記憶するための前記手段によって記憶された前記タップ係数セットを別のタップ係数セットへと更新し、

ピクセルウィンドウに記憶するための前記手段によって記憶された前記ピクセルウィンドウを、前記ピクセルアレイの別の前記ピクセルによって更新することによって、前記ピクセルアレイの方向に沿って前記ピクセルウィンドウをシフトし、

ピクセルウィンドウを記憶するための前記手段によって記憶された前記シフトされた

ピクセルウィンドウと、タップ係数セットを記憶するための前記手段によって記憶された前記別のタップ係数セットとに基づいて、前記偶数番目の補間されたサブピクセルのそれぞれの値をインクリメントし、

ピクセルウィンドウに記憶するための前記手段によって記憶された前記ピクセルウィンドウを、前記ピクセルアレイの別の前記ピクセルによって更新することによって、前記ピクセルアレイの方向に沿って前記ピクセルウィンドウを再びシフトし、

ピクセルウィンドウを記憶するための前記手段によって記憶された前記再びシフトされたピクセルウィンドウと、タップ係数セットを記憶するための前記手段によって記憶された前記別のタップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルのそれぞれの値をインクリメントする

ように構成される、手段と、

前記所与の終了条件が満たされると、前記偶数番目の補間されたサブピクセルおよび前記奇数番目の補間されたサブピクセルを出力するための手段とを含む、装置。

#### 【請求項 1 4】

偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するための前記手段が、4個の偶数番目の補間されたサブピクセルを有する前記セットに対する前記初期値を生成するように構成され、前記4個の偶数番目の補間されたサブピクセルの各々に対する前記初期値が、対応する2個の積の合計を有し、

奇数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するための前記手段が、4個の奇数番目の補間されたサブピクセルを有する前記セットに対する前記初期値を生成するように構成され、前記4個の奇数番目の補間されたサブピクセルの各々に対する前記初期値が、対応する2個の積の合計を有する、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 1 5】

前記偶数番目のサブピクセルおよび前記奇数番目の補間されたサブピクセルの前記値をインクリメントするための前記手段が、前記4個の偶数番目の補間されたサブピクセルの前記値を、別の対応する2個の積の合計によってインクリメントすることによって、前記偶数番目の補間されたサブピクセルの前記値をインクリメントすることであって、前記2個の積の各々が、ピクセルウィンドウを記憶するための前記手段によって記憶された前記シフトされたピクセルウィンドウからのピクセルと、タップ係数セットを記憶するための前記手段によって記憶された係数の別のセットからの係数との積である、インクリメントすることと、前記4個の奇数番目の補間されたサブピクセルの各々の前記値を別の対応する2個の積の合計によってインクリメントすることによって、前記奇数番目の補間されたサブピクセルの前記値をインクリメントすることであって、前記2個の積の各々が、ピクセルウィンドウを記憶するための前記手段によって記憶された前記再びシフトされたピクセルウィンドウからのピクセルと、タップ係数セットを記憶するための前記手段によって記憶された係数の前記別のセットからの係数との積である、インクリメントすることとを行いうように構成される、請求項14に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 1 6】

少なくとも1つの半導体ダイにおいて集積される、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 1 7】

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなる群から選択されるデバイスをさらに含み、前記デバイスに前記装置が組み込まれる、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 1 8】

ワイヤレス通信システム中のプロセッサ装置によって実行されると、プロセッサ装置に

、ピクセルアレイに対する補間されたピクセルを生成するための方法を実施する動作を実行させる命令を含む、コンピュータ可読記録媒体であって、前記プロセッサ装置に、

前記ピクセルアレイのピクセルウィンドウをウィンドウレジスタへロードさせ、

所与のタップ係数セットをタップ係数レジスタへロードさせ、

前記ウィンドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットに対する初期値を生成させ、

前記ピクセルアレイの別の前記ピクセルによって前記ウィンドウレジスタを更新することによって、アレイの方向に沿って前記ピクセルウィンドウをシフトさせ、

前記ウィンドウレジスタ中の前記シフトされたピクセルウィンドウと、前記タップ係数レジスタ中の前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットに対する初期値を生成させ、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルの値および前記奇数番目の補間されたサブピクセルの値をインクリメントさせる命令であって、前記プロセッサ装置に、

前記タップ係数レジスタ中の前記タップ係数セットを別のタップ係数セットへと更新し、

前記ピクセルアレイの別の前記ピクセルによって前記ウィンドウレジスタを更新することによって、前記方向に沿って前記ピクセルウィンドウをシフトし、

前記ウィンドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記別のタップ係数セットとに基づいて、前記偶数番目の補間されたサブピクセルのそれぞれの値をインクリメントし、

前記ピクセルアレイの別の前記ピクセルによって前記ウィンドウレジスタを更新することによって、前記方向に沿って前記ピクセルウィンドウを再びシフトし、

前記ウィンドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記別のタップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルのそれぞれの値をインクリメントする

ことによって、前記値をインクリメントさせる、命令と、

前記終了条件が満たされると、前記プロセッサ装置に、偶数番目の補間されたサブピクセルの前記セットおよび奇数番目の補間されたサブピクセルの前記セットを出力させる、命令とを含む、コンピュータ可読記録媒体。

#### 【請求項 19】

前記プロセッサ装置に、偶数番目の補間されたサブピクセルの前記セットの前記初期値を生成させる前記命令が、前記プロセッサ装置に、4個の偶数番目の補間されたサブピクセルを有する前記セットに対する前記初期値を生成することと、前記4個の偶数番目の補間されたサブピクセルの各々の前記初期値を、対応する2個の積の合計として生成することであって、前記2個の積の各々が、前記ウィンドウレジスタ中の前記ピクセルウィンドウからのピクセルと、係数レジスタ中の係数の前記所与のセットからの係数との積である、生成することを行わせ、前記プロセッサ装置に、奇数番目の補間されたサブピクセルの前記セットの前記初期値を生成させる前記命令が、前記プロセッサ装置に、4個の奇数番目の補間されたサブピクセルを有する前記セットに対する前記初期値を生成することと、前記4個の奇数番目の補間されたサブピクセルの各々の前記初期値を、対応する2個の積の合計として生成することであって、前記2個の積の各々が、前記ウィンドウレジスタ中の前記シフトされたピクセルウィンドウからのピクセルと、前記係数レジスタ中の係数の前記所与のセットからの係数との積である、生成することを行わせる、請求項18に記載のコンピュータ可読記録媒体。

#### 【請求項 20】

前記プロセッサ装置に、前記4個の偶数番目の補間されたサブピクセルの前記それぞれの値をインクリメントさせる前記命令が、前記プロセッサ装置に、別の対応する2個の積の合計によって前記値の各々をインクリメントさせ、前記2個の積の各々が、前記ウィン

ドウレジスタ中の前記シフトされたピクセルウィンドウからのピクセルと、前記タップ係数レジスタ中の係数の別のセットからの係数との積であり、

前記プロセッサ装置に、前記4個の奇数番目の補間されたサブピクセルの前記それぞれの値をインクリメントさせる前記命令が、前記プロセッサ装置に、別の対応する2個の積の合計によって前記値の各々をインクリメントさせ、前記2個の積の各々が、前記ウインドウレジスタ中の前記再びシフトされたピクセルウィンドウからのピクセルと、前記タップ係数レジスタ中の係数の前記別のセットからの係数との積である、請求項18に記載のコンピュータ可読記録媒体。

**【請求項 2 1】**

ウインドウレジスタおよびタップ係数レジスタを有し、ピクセルアレイからのピクセルを受け取るための入力を有する論理回路を含む、ピクセルアレイに対する補間されたピクセルを生成するための装置であって、前記論理回路が、

前記ピクセルアレイのピクセルウィンドウを前記ウインドウレジスタにロードし、

所与のタップ係数セットを前記タップ係数レジスタにロードし、

前記ウインドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記所与のタップ係数セットとに基づいて、偶数番目の補間されたサブピクセルのセットに対する初期値を生成し、

前記ピクセルアレイの別の前記ピクセルによって前記ウインドウレジスタを更新することによって、アレイの方向に沿って前記ピクセルウィンドウをシフトし、

前記ウインドウレジスタ中の前記シフトされたピクセルウィンドウと、前記タップ係数レジスタ中の前記所与のタップ係数セットとに基づいて、奇数番目の補間されたサブピクセルのセットに対する初期値を生成し、

所与の終了条件が満たされるまで、前記偶数番目の補間されたサブピクセルの値および前記奇数番目の補間されたサブピクセルの値をインクリメントするように構成され、前記論理回路が、

前記タップ係数レジスタ中の前記タップ係数セットを別のタップ係数セットへと更新し、

前記ピクセルアレイの別の前記ピクセルによって前記ウインドウレジスタを更新することによって、前記方向に沿って前記ピクセルウィンドウをシフトし、

前記ウインドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記別のタップ係数セットとに基づいて、前記偶数番目の補間されたサブピクセルのそれぞれの値をインクリメントし、

前記ピクセルアレイの別の前記ピクセルによって前記ウインドウレジスタを更新することによって、前記方向に沿って前記ピクセルウィンドウを再びシフトし、

前記ウインドウレジスタ中の前記ピクセルウィンドウと、前記タップ係数レジスタ中の前記別のタップ係数セットとに基づいて、前記奇数番目の補間されたサブピクセルのそれぞれの値をインクリメントする

ことによって、前記値をインクリメントし、

前記所与の終了条件が満たされると、偶数番目の補間されたサブピクセルの前記セットおよび奇数番目の補間されたサブピクセルの前記セットを出力するように構成される、装置。

**【請求項 2 2】**

前記論理回路が少なくとも1つの半導体ダイにおいて集積される、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

**【請求項 2 3】**

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなる群から選択されるデバイスをさらに含み、前記デバイスに前記論理回路が組み込まれる、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

**【請求項 2 4】**

偶数番目の補間されたサブピクセルの前記セットが、整数個の偶数番目の補間されたサブピクセルを含み、奇数番目の補間されたサブピクセルの前記セットが、前記整数に等しい数の奇数番目の補間されたサブピクセルを含み、

偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、各初期値に対応する乗算のペアを同時に実行するステップと、各初期値に対する積の対応するペアを生成するステップと、積の各ペアの加算を同時に実行して、前記整数個の偶数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成するステップとを含み、

奇数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、各初期値に対応する乗算のペアを同時に実行するステップと、各初期値に対する積の対応するペアを生成するステップと、積の各ペアの加算を同時に実行して、前記整数個の奇数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成するステップとを含む、請求項1に記載の方法。

**【請求項 2 5】**

前記偶数番目の補間されたサブピクセルの前記初期値を、補間された偶数番目のサブピクセルの前記セットに対する記憶された現在値としてメモリにオフロードするステップと、

前記奇数番目の補間されたサブピクセルの前記初期値を、補間された奇数番目のサブピクセルの前記セットの記憶された現在値としてメモリにオフロードするステップとをさらに含み、

補間された偶数番目のサブピクセルの前記セットの前記値をインクリメントするステップが、前記メモリから、インクリメントされるべき補間された偶数番目のサブピクセルの前記セットの前記値として、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値を取り出すステップと、補間された偶数番目のサブピクセルの前記セットの前記値を、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントする前記ステップの後で記憶するステップとを含み、

補間された奇数番目のサブピクセルの前記セットの前記値をインクリメントするステップが、前記メモリから、インクリメントされるべき補間された奇数番目のサブピクセルの前記セットの前記値として、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値を取り出すステップと、補間された奇数番目のサブピクセルの前記セットの前記値を、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントする前記ステップの後で記憶するステップとを含む、請求項1に記載の方法。

**【請求項 2 6】**

タップ係数の前記所与のセットが、整数に等しい数のタップ係数のペアを含み、タップ係数の各ペアが、前記偶数番目の補間されたサブピクセルの1つおよび前記奇数番目の補間されたサブピクセルの1つに対応する、マルチタップ補間フィルタの2個のタップに対応し、

偶数番目の補間されたサブピクセルの前記セットの前記初期値を生成するステップが、各初期値に対して、タップ係数の対応する1つのペアの1つのタップ係数を前記ピクセルウィンドウ中の1つのピクセルと乗算して積を生成するステップと、タップ係数の前記対応する1つのペアの他方のタップ係数を前記ピクセルウィンドウ中の別のピクセルと乗算して別の積を生成するステップと、前記積を前記別の積に加算して、2個の積の合計を、前記偶数番目の補間されたサブピクセルの前記初期値として生成するステップとを含み、2個の積の前記合計が、前記偶数番目の補間されたサブピクセルの最終値に対する前記2個のタップの寄与を含み、

奇数番目の補間されたサブピクセルの前記セットの前記初期値を生成するステップが、各初期値に対して、前記タップ係数の対応する1つのペアの1つのタップ係数を前記シフトされたピクセルウィンドウ中の1つのピクセルと乗算して積を生成するステップと、タッ

プ係数の前記対応する1つのペアの他方のタップ係数を前記シフトされたピクセルワインドウ中の別のピクセルと乗算して別の積を生成するステップと、前記積を前記別の積に加算して、2個の積の合計を、前記奇数番目の補間されたサブピクセルの前記初期値として生成するステップとを含み、2個の積の前記合計が、前記奇数番目の補間されたサブピクセルの最終値に対する前記2個のタップの寄与を含む、請求項25に記載の方法。

#### 【請求項 27】

偶数番目の補間されたサブピクセルの前記セットの前記値をインクリメントする各ステップが、前記偶数番目の補間されたサブピクセルの各々に、2個の積の合計を加算し、2個の積の前記合計が、偶数番目の補間されたサブピクセルの最終値に対する、前記偶数番目の補間されたサブピクセルに対応するマルチタップ補間フィルタの別の2個のタップの寄与を含み、

奇数番目の補間されたサブピクセルの前記セットの前記値をインクリメントする各ステップが、前記奇数番目の補間されたサブピクセルの各々に、2個の積の合計を加算し、2個の積の前記合計が、奇数番目の補間されたサブピクセルの最終値に対する、前記奇数番目の補間されたサブピクセルに対応するマルチタップ補間フィルタの別の2個のタップの寄与を含む、請求項26に記載の方法。

#### 【請求項 28】

偶数番目の補間されたサブピクセルの前記セットが、整数個の偶数番目の補間されたサブピクセルを含み、奇数番目の補間されたサブピクセルの前記セットが、前記整数に等しい数の奇数番目の補間されたサブピクセルを含み、

偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するための前記手段が、各初期値に対応する乗算のペアを同時に実行し、各初期値に対する積の対応するペアを生成し、積の各ペアの加算を同時に実行して、前記整数個の偶数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成するように構成され、

奇数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するための手段が、各初期値に対応する乗算のペアを同時に実行して、各初期値に対する積の対応するペアを生成し、積の各ペアの加算を同時に実行して、前記整数個の奇数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成するように構成される、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 29】

前記偶数番目の補間されたサブピクセルの前記初期値を、補間された偶数番目のサブピクセルの前記セットに対する記憶された現在値としてオフロードし記憶するための手段と、

前記奇数番目の補間されたサブピクセルの前記初期値を、補間された奇数番目のサブピクセルの前記セットの記憶された現在値としてオフロードし記憶するための手段とをさらに含み、

補間された偶数番目のサブピクセルの前記セットの前記値をインクリメントするための手段が、インクリメントされるべき補間された偶数番目のサブピクセルの前記セットの前記値として、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値を取り出し、補間された偶数番目のサブピクセルの前記セットの前記値を、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントするステップの後で記憶するように構成され、

補間された奇数番目のサブピクセルの前記セットの前記値をインクリメントするための手段が、インクリメントされるべき補間された奇数番目のサブピクセルの前記セットの前記値として、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値を取り出し、補間された奇数番目のサブピクセルの前記セットの前記値を、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントするステップの後で記憶するように構成される、請求項13に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

#### 【請求項 30】

タップ係数の前記所与のセットが、整数に等しい数のタップ係数のペアを含み、タップ係数の各ペアが、前記偶数番目の補間されたサブピクセルの1つおよび前記奇数番目の補間されたサブピクセルの1つに対応する、マルチタップ補間フィルタの2個のタップに対応し、

偶数番目の補間されたサブピクセルの前記セットの前記初期値を生成するための前記手段が、各初期値に対して、タップ係数の対応する1つのペアの1つのタップ係数を前記ピクセルウィンドウ中の1つのピクセルと乗算して積を生成することを実行し、タップ係数の前記対応する1つのペアの他方のタップ係数を前記ピクセルウィンドウ中の別のピクセルと乗算して別の積を生成し、前記積を前記別の積に加算して、2個の積の合計を、前記偶数番目の補間されたサブピクセルの前記初期値として生成するように構成され、2個の積の前記合計が、前記偶数番目の補間されたサブピクセルの最終値に対する前記2個のタップの寄与を含み、

奇数番目の補間されたサブピクセルの前記セットの前記初期値を生成するための前記手段が、各初期値に対して、前記タップ係数の対応する1つのペアの1つのタップ係数を前記シフトされたピクセルウィンドウ中の1つのピクセルと乗算して積を生成することを実行し、タップ係数の前記対応する1つのペアの他方のタップ係数を前記シフトされたピクセルウィンドウ中の別のピクセルと乗算して別の積を生成し、前記積を前記別の積に加算して、2個の積の合計を、前記奇数番目の補間されたサブピクセルの前記初期値として生成するように構成され、2個の積の前記合計が、前記奇数番目の補間されたサブピクセルの最終値に対する前記2個のタップの寄与を含む、請求項29に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

### 【請求項 3 1】

偶数番目の補間されたサブピクセルの前記セットの前記値をインクリメントするための前記手段が、前記偶数番目の補間されたサブピクセルの各々に、2個の積の合計を加算するように構成され、2個の積の前記合計が、偶数番目の補間されたサブピクセルの最終値に対する、前記偶数番目の補間されたサブピクセルに対するマルチタップ補間フィルタの別の2つのタップの寄与を含み、

奇数番目の補間されたサブピクセルの前記セットの前記値をインクリメントするための前記手段が、前記奇数番目の補間されたサブピクセルの各々に、2個の積の合計を加算するように構成され、2個の積の前記合計が、奇数番目の補間されたサブピクセルの最終値に対する、前記奇数番目の補間されたサブピクセルに対するマルチタップ補間フィルタの別の2つのタップの寄与を含む、請求項30に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

### 【請求項 3 2】

偶数番目の補間されたサブピクセルの前記セットが、整数個の偶数番目の補間されたサブピクセルを含み、奇数番目の補間されたサブピクセルの前記セットが、前記整数に等しい数の奇数番目の補間されたサブピクセルを含み、

プロセッサに、偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成させるための前記命令が、前記プロセッサに、各初期値に対応する乗算のペアを同時に実行させて、各初期値に対する積の対応するペアを生成させ、積の各ペアの加算を同時に実行させて、前記整数個の偶数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成させるための命令を含み、

前記プロセッサに、奇数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成させるための前記命令が、前記プロセッサに、各初期値に対応する乗算のペアを同時に実行させて、各初期値に対する積の対応するペアを生成させ、積の各ペアの加算を同時に実行させて、前記整数個の奇数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成させる命令を含む、請求項18に記載のコンピュータ可読記録媒体。

### 【請求項 3 3】

プロセッサに、前記偶数番目の補間されたサブピクセルの前記初期値を、補間された偶数番目のサブピクセルの前記セットに対する記憶された現在値としてメモリヘオフロード

させるための命令と、

前記プロセッサに、前記奇数番目の補間されたサブピクセルの前記初期値を、補間された奇数番目のサブピクセルの前記セットの記憶された現在値としてメモリへオフロードさせるための命令とを含み、

補間された偶数番目のサブピクセルの前記セットの前記値をインクリメントするステップが、前記メモリから、インクリメントされるべき補間された偶数番目のサブピクセルの前記セットの前記値として、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値を取り出すステップと、補間された偶数番目のサブピクセルの前記セットの前記値を、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントする前記ステップの後で記憶するステップとを含み、

補間された奇数番目のサブピクセルの前記セットの前記値をインクリメントするステップが、前記メモリから、インクリメントされるべき補間された奇数番目のサブピクセルの前記セットの前記値として、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値を取り出すステップと、補間された奇数番目のサブピクセルの前記セットの前記値を、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントする前記ステップの後で記憶するステップとを含む、請求項18に記載のコンピュータ可読記録媒体。

**【請求項34】**

偶数番目の補間されたサブピクセルの前記セットが、整数個の偶数番目の補間されたサブピクセルを含み、奇数番目の補間されたサブピクセルの前記セットが、前記整数に等しい数の奇数番目の補間されたサブピクセルを含み、

偶数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、各初期値に対応する乗算のペアを同時に実行するステップと、各初期値に対する積の対応するペアを生成するステップと、積の各ペアの加算を同時に実行して、前記整数個の偶数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成するステップとを含み、

奇数番目の補間されたサブピクセルの前記セットに対する前記初期値を生成するステップが、各初期値に対応する乗算のペアを同時に実行するステップと、各初期値に対する積の対応するペアを生成するステップと、積の各ペアの加算を同時に実行して、前記整数個の奇数番目の補間されたサブピクセルの各々に対する前記初期値を同時に生成するステップとを含む、請求項21に記載の、ピクセルアレイに対する補間されたピクセルを生成するための装置。

**【請求項35】**

前記論理回路がさらに、

前記偶数番目の補間されたサブピクセルの前記初期値を、補間された偶数番目のサブピクセルの前記セットに対する記憶された現在値としてメモリにオフロードし、

前記奇数番目の補間されたサブピクセルの前記初期値を、補間された奇数番目のサブピクセルの前記セットの記憶された現在値としてメモリにオフロードするように構成され、

補間された偶数番目のサブピクセルの前記セットの前記値をインクリメントするステップが、前記メモリから、インクリメントされるべき補間された偶数番目のサブピクセルの前記セットの前記値として、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値を取り出すステップと、補間された偶数番目のサブピクセルの前記セットの前記値を、補間された偶数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントする前記ステップの後で記憶するステップとを含み、

補間された奇数番目のサブピクセルの前記セットの前記値をインクリメントするステップが、前記メモリから、インクリメントされるべき補間された奇数番目のサブピクセルの前記セットの前記値として、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値を取り出すステップと、補間された奇数番目のサブピクセルの前記セットの前記値を、補間された奇数番目のサブピクセルの前記セットの前記記憶された現在値として、インクリメントする前記ステップの後で記憶するステップとを含む、請求項21に記載

のピクセルアレイに対する補間されたピクセルを生成するための装置。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2013/037206 |

|---------------------------------------------------|