(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3927953号

(P3927953)

(45) 発行日 平成19年6月13日(2007.6.13)

(24) 登録日 平成19年3月9日(2007.3.9)

(51) Int.C1.

F 1

|             |                |                  |      |        |      |

|-------------|----------------|------------------|------|--------|------|

| <b>HO3K</b> | <b>19/0185</b> | <b>(2006.01)</b> | HO3K | 19/00  | 101C |

| <b>G09G</b> | <b>3/20</b>    | <b>(2006.01)</b> | G09G | 3/20   | 621L |

| <b>G09G</b> | <b>3/36</b>    | <b>(2006.01)</b> | G09G | 3/36   |      |

| <b>HO3K</b> | <b>17/687</b>  | <b>(2006.01)</b> | HO3K | 17/687 | A    |

| <b>HO4N</b> | <b>5/66</b>    | <b>(2006.01)</b> | HO4N | 5/66   | 102B |

請求項の数 17 (全 22 頁)

(21) 出願番号 特願2003-572178 (P2003-572178)

(86) (22) 出願日 平成14年2月26日 (2002.2.26)

(86) 国際出願番号 PCT/JP2002/001760

(87) 国際公開番号 WO2003/073617

(87) 国際公開日 平成15年9月4日 (2003.9.4)

審査請求日 平成17年1月25日 (2005.1.25)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】振幅変換回路

## (57) 【特許請求の範囲】

## 【請求項 1】

その振幅が第1の電圧である第1の信号を、その振幅が前記第1の電圧よりも高い第2の電圧である第2の信号に変換する振幅変換回路であって、

それらの第1の電極がともに前記第2の電圧を受け、それらの第2の電極が前記第2の信号およびその相補信号を出力するための第1および第2の出力ノードにそれぞれ接続され、それらの入力電極がそれぞれ前記第2および第1の出力ノードに接続された第1の導電形式の第1および第2のトランジスタ、

それらの第1の電極がそれぞれ前記第1および第2の出力ノードに接続された第2の導電形式の第3および第4のトランジスタ、および

前記第1の信号およびその相補信号によって駆動され、前記第1の信号の前縁に応答して前記第1の電圧よりも高い第3の電圧を前記第3のトランジスタの入力電極および第2の電極間に与えて前記第3のトランジスタを導通させ、前記第1の信号の後縁に応答して前記第3の電圧を前記第4のトランジスタの入力電極および第2の電極間に与えて前記第4のトランジスタを導通させる駆動回路を備え、

前記駆動回路は、

前記第3のトランジスタの入力電極および第2の電極間に接続された第1の抵抗素子、

その一方電極が前記第1の信号の相補信号を受け、その他方電極が前記第3のトランジスタの入力電極に接続された第1のキャパシタ、

前記第4のトランジスタの入力電極および第2の電極間に接続された第2の抵抗素子、

および

その一方電極が前記第1の信号を受け、その他方電極が前記第4のトランジスタの入力電極に接続された第2のキャパシタを含み、

前記第1の信号およびその相補信号をそれぞれ前記第3および第4のトランジスタの第2の電極に与える、振幅変換回路。

**【請求項2】**

前記第1の抵抗素子は、前記第3のトランジスタの入力電極および第2の電極間に接続され、その入力電極が第4の電圧を受ける第5のトランジスタを含み、

前記第2の抵抗素子は、前記第4のトランジスタの入力電極および第2の電極間に接続され、その入力電極が前記第4の電圧を受ける第6のトランジスタを含む、請求項1に記載の振幅変換回路。 10

**【請求項3】**

前記第5および第6のトランジスタは第2の導電形式であり、

前記第4の電圧は前記第2の電圧に等しい、請求項2に記載の振幅変換回路。

**【請求項4】**

前記第1の抵抗素子は、前記第3のトランジスタの入力電極および第2の電極間に接続された第5のトランジスタを含み、

前記第2の抵抗素子は、前記第4のトランジスタの入力電極および第2の電極間に接続された第6のトランジスタを含み、

前記駆動回路は、さらに、前記第1の信号の前縁に応答して前記第5のトランジスタの抵抗値をパルス的に高くし、前記第1の信号の後縁に応答して前記第6のトランジスタの抵抗値をパルス的に高くするためのパルス発生回路を含む、請求項1に記載の振幅変換回路。 20

**【請求項5】**

前記第5および第6のトランジスタは第2の導電形式であり、

前記パルス発生回路は、

前記第2の電圧と同極性の第4の電圧のノードと前記第5のトランジスタの入力電極との間に接続された第3の抵抗素子、

その一方電極が前記第1の信号を受け、その他方電極が前記第5のトランジスタの入力電極に接続された第3のキャパシタ、

前記第4の電圧のノードと前記第6のトランジスタの入力電極との間に接続された第4の抵抗素子、および

その一方電極が前記第1の信号の相補信号を受け、その他方電極が前記第6のトランジスタの入力電極に接続された第4のキャパシタを含む、請求項4に記載の振幅変換回路。 30

**【請求項6】**

前記第4の電圧は前記第2の電圧に等しい、請求項5に記載の振幅変換回路。

**【請求項7】**

前記第5および第6のトランジスタは第1の導電形式であり、

前記パルス発生回路は、

前記第2の電圧と逆極性の第4の電圧のノードと前記第5のトランジスタの入力電極との間に接続された第3の抵抗素子、

その一方電極が前記第1の信号の相補信号を受け、その他方電極が前記第5のトランジスタの入力電極に接続された第3のキャパシタ、

前記第4の電圧のノードと前記第6のトランジスタの入力電極との間に接続された第4の抵抗素子、および

その一方電極が前記第1の信号を受け、その他方電極が前記第6のトランジスタの入力電極に接続された第4のキャパシタを含む、請求項4に記載の振幅変換回路。 40

**【請求項8】**

前記駆動回路は、

さらに、前記第3のトランジスタの第2の電極および入力電極間に接続された第1のダ

50

イオード素子、および

前記第4のトランジスタの第2の電極および入力電極間に接続された第2のダイオード素子を含む、請求項1に記載の振幅変換回路。

**【請求項9】**

その振幅が第1の電圧である第1の信号を、その振幅が前記第1の電圧よりも高い第2の電圧である第2の信号に変換する振幅変換回路であって、

それらの第1の電極がともに前記第2の電圧を受け、それらの第2の電極が前記第2の信号およびその相補信号を出力するための第1および第2の出力ノードにそれぞれ接続され、それらの入力電極がそれぞれ前記第2および第1の出力ノードに接続された第1の導電形式の第1および第2のトランジスタ、

それらの第1の電極がそれぞれ前記第1および第2の出力ノードに接続された第2の導電形式の第3および第4のトランジスタ、および

前記第1の信号およびその相補信号によって駆動され、前記第1の信号の前縁に応答して前記第1の電圧よりも高い第3の電圧を前記第3のトランジスタの入力電極および第2の電極間に与えて前記第3のトランジスタを導通させ、前記第1の信号の後縁に応答して前記第3の電圧を前記第4のトランジスタの入力電極および第2の電極間に与えて前記第4のトランジスタを導通させる駆動回路を備え、

前記駆動回路は、

前記第3のトランジスタの第2の電極と基準電圧のノードとの間に接続された第1の抵抗素子、

その一方電極が前記第1の信号を受け、その他方電極が前記第3のトランジスタの第2の電極に接続された第1のキャパシタ、

前記第4のトランジスタの第2の電極と前記基準電圧のノードとの間に接続された第2の抵抗素子、および

その一方電極が前記第1の信号の相補信号を受け、その他方電極が前記第4のトランジスタの第2の電極に接続された第2のキャパシタを含み、

前記第1の信号およびその相補信号をそれぞれ前記第4および第3のトランジスタの入力電極に与える、振幅変換回路。

**【請求項10】**

前記第1の抵抗素子は、前記第3のトランジスタの第2の電極と前記基準電圧のノードとの間に接続された第5のトランジスタを含み、

前記第2の抵抗素子は、前記第4のトランジスタの第2の電極と前記基準電圧のノードとの間に接続された第6のトランジスタを含み、

前記駆動回路は、さらに、前記第1の信号の前縁に応答して前記第5のトランジスタの抵抗値をパルス的に高くし、前記第1の信号の後縁に応答して前記第6のトランジスタの抵抗値をパルス的に高くするためのパルス発生回路を含む、請求項9に記載の振幅変換回路。

**【請求項11】**

前記第5および第6のトランジスタは第2の導電形式であり、

前記パルス発生回路は、

前記第2の電圧と同極性の第4の電圧のノードと前記第5のトランジスタの入力電極との間に接続された第3の抵抗素子、

その一方電極が前記第1の信号を受け、その他方電極が前記第5のトランジスタの入力電極に接続された第3のキャパシタ、

前記第4の電圧のノードと前記第6のトランジスタの入力電極との間に接続された第4の抵抗素子、および

その一方電極が前記第1の信号の相補信号を受け、その他方電極が前記第6のトランジスタの入力電極に接続された第4のキャパシタを含む、請求項1\_0に記載の振幅変換回路。

**【請求項12】**

10

20

30

40

50

前記第4の電圧は前記第2の電圧に等しい、請求項1\_1に記載の振幅変換回路。

**【請求項13】**

さらに、前記第1および第2の出力ノードの電位をラッチするためのラッチ回路を備える、請求項1または請求項9に記載の振幅変換回路。

**【請求項14】**

前記ラッチ回路は、それらの第1の電極がそれぞれ前記第1および第2の出力ノードに接続され、それらの第2の電極がそれぞれ前記第1の信号およびその相補信号を受け、それらの入力電極がそれぞれ前記第2および第1の出力ノードに接続された第2の導電形式の第5および第6のトランジスタを含む、請求項1\_3に記載の振幅変換回路。

**【請求項15】**

前記ラッチ回路は、それぞれ前記第1および第2の出力ノードと基準電圧のノードとの間に接続され、それらの入力電極がそれぞれ前記第2および第1の出力ノードに接続された第2の導電形式の第5および第6のトランジスタを含む、請求項1\_3に記載の振幅変換回路。

**【請求項16】**

さらに、前記第1のトランジスタの第2の電極と前記第1の出力ノードとの間に介挿され、その入力電極が前記第3のトランジスタの入力電極に接続された第1の導電形式の第5のトランジスタ、および

前記第2のトランジスタの第2の電極と前記第2の出力ノードとの間に介挿され、その入力電極が前記第4のトランジスタの入力電極に接続された第1の導電形式の第6のトランジスタを備える、請求項1または請求項9に記載の振幅変換回路。

**【請求項17】**

前記第1～第4のトランジスタは薄膜トランジスタである、請求項1または請求項9に記載の振幅変換回路。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

この発明は振幅変換回路に関し、特に、信号の振幅を変換するための振幅変換回路に関する。

**【0002】**

**【従来の技術】**

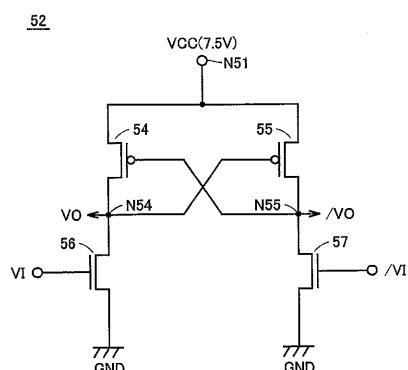

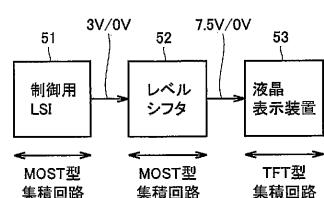

図17は、従来の携帯電話機の画像表示に関連する部分の構成を示すブロック図である。

**【0003】**

図17において、この携帯電話機は、MOS（MOSトランジスタ）型集積回路である制御用LSI51と、MOS型集積回路であるレベルシフタ52と、TFT（薄膜トランジスタ）型集積回路である液晶表示装置53とを備える。

**【0004】**

制御用LSI51は、液晶表示装置53用の制御信号を生成する。この制御信号の「H」レベルは3Vであり、その「L」レベルは0Vである。制御信号は実際には多数生成されるが、ここでは説明の簡単化のため制御信号は1つとする。レベルシフタ52は、制御用LSI51からの制御信号の論理レベルを変換して内部制御信号を生成する。この内部制御信号の「H」レベルは7.5Vであり、その「L」レベルは0Vである。液晶表示装置53は、レベルシフタ52からの内部制御信号に従って画像を表示する。

**【0005】**

図18は、レベルシフタ52の構成を示す回路図である。図18において、このレベルシフタ52は、PチャネルMOSトランジスタ54, 55およびNチャネルMOSトランジスタ56, 57を含む。PチャネルMOSトランジスタ54, 55は、それぞれ電源電位VCC(7.5V)のノードN51と出力ノードN54, N55との間に接続され、それらのゲートはそれぞれ出力ノードN55, N54に接続される。NチャネルMOSト

10

20

30

40

50

ンジスタ 56, 57 は、それぞれ出力ノード N54, N55 と接地電位 GND のノードとの間に接続され、それらのゲートはそれぞれ入力信号 VI, /VI を受ける。

#### 【0006】

今、入力信号 VI, /VI がそれぞれ「L」レベル(0V)および「H」レベル(3V)にされ、出力信号 VO, /VO がそれぞれ「H」レベル(7.5V)および「L」レベル(0V)にされているものとする。このとき、MOSトランジスタ 54, 57 が導通し、MOSトランジスタ 55, 56 が非導通になっている。

#### 【0007】

この状態で、入力信号 VI が「L」レベル(0V)から「H」レベル(3V)に立上げられるとともに入力信号 /VI が「H」レベル(3V)から「L」レベル(0V)に立下げられると、まずNチャネルMOSトランジスタ 56 が導通して出力ノード N54 の電位が低下する。出力ノード N54 の電位が、電源電位 VCC から PチャネルMOSトランジスタ 55 のしきい値電圧の絶対値を減算した電位よりも低くなると、PチャネルMOSトランジスタ 55 が導通し始め、出力ノード N55 の電位が上昇し始める。出力ノード N55 の電位が上昇し始めると、PチャネルMOSトランジスタ 54 のソース - ゲート間の電圧が小さくなつて PチャネルMOSトランジスタ 54 の導通抵抗値が高くなり、出力ノード N54 の電位がさらに低下する。したがつて、回路は正帰還的に動作し、出力ノード VO, /VO がそれぞれ「L」レベル(0V)および「H」レベル(7.5V)になってレベル変換動作が完了する。

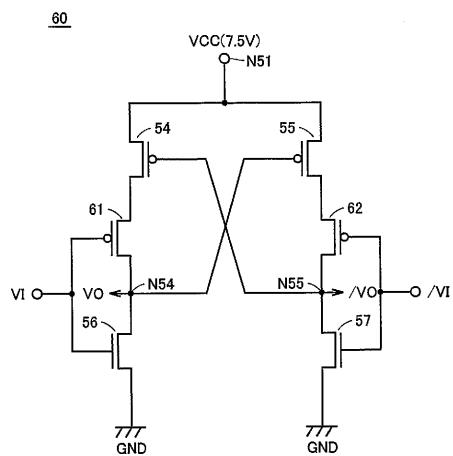

#### 【0008】

図 19 は、従来の他のレベルシフタ 60 の構成を示す回路図である。図 19 を参照して、このレベルシフタ 60 が図 18 のレベルシフタ 52 と異なる点は、PチャネルMOSトランジスタ 61, 62 が追加されている点である。PチャネルMOSトランジスタ 61 は、PチャネルMOSトランジスタ 54 のドレインと出力ノード N54 との間に介挿され、そのゲートは入力信号 VI を受ける。PチャネルMOSトランジスタ 62 は、PチャネルMOSトランジスタ 55 のドレインと出力ノード N55 との間に介挿され、そのゲートは入力信号 /VI を受ける。

#### 【0009】

このレベルシフタ 60 では、入力信号 VI が「L」レベル(0V)から「H」レベル(3V)に立上げられると、PチャネルMOSトランジスタ 61 が導通状態から非導通状態になり、電源電位 VCC のノード N51 から出力ノード N54 に流れる電流が低減されるので、出力ノード N54 の電位が低下しやすくなる。この結果、PチャネルMOSトランジスタ 55 が導通して出力ノード N55 の電位が上昇しやすくなるので、図 18 のレベルシフタ 52 よりも動作マージンが大きくなる。

#### 【0010】

このように、従来のレベルシフタ 52, 60 では、入力信号 VI が「L」レベル(0V)から「H」レベル(3V)に立上げられたことに応じて NチャネルMOSトランジスタ 56 が導通することが動作の前提となる。NチャネルMOSトランジスタ 56 が導通するためには、NチャネルMOSトランジスタ 56 のしきい値電位が入力信号 VI の「H」レベル(3V)以下である必要がある。

#### 【0011】

一般的な半導体 LSI ではトランジスタのしきい値電圧を 3V 以下にすることは容易であるが、液晶表示装置に含まれている低温ポリシリコン TFT はしきい値電圧のばらつきが大きく、TFT のしきい値電圧を 3V 以下にすることは困難である。このため、図 17 で示したように、高耐圧のMOSトランジスタで構成されたレベルシフタ 52 または 60 を制御用 LSI 51 と液晶表示装置 53 との間に設けて信号の論理レベルの変換を行なっている。

#### 【0012】

##### 【発明が解決しようとする課題】

しかし、このようなレベルシフタ 52, 60 を設けると、レベルシフタ 52, 60 のコ

10

20

30

40

50

ストがシステムコストに加算されることになり、システムコストの上昇を招く。

**【0013】**

それゆえに、この発明の主たる目的は、入力トランジスタのしきい値電圧よりも入力信号の振幅電圧が低い場合でも正常に動作する振幅変換回路を提供することである。

**【0014】**

**【課題を解決するための手段および効果】**

この発明に係る振幅変換回路は、その振幅が第1の電圧である第1の信号を、その振幅が第1の電圧よりも高い第2の電圧である第2の信号に変換するものである。この振幅変換回路では、それらの第1の電極とともに第2の電圧を受け、それらの第2の電極が第2の信号およびその相補信号を出力するための第1および第2の出力ノードにそれぞれ接続され、それらの入力電極がそれぞれ第2および第1の出力ノードに接続された第1の導電形式の第1および第2のトランジスタと、それらの第1の電極がそれぞれ第1および第2の出力ノードに接続された第2の導電形式の第3および第4のトランジスタと、第1の信号およびその相補信号によって駆動され、第1の信号の前縁に応答して第1の電圧よりも高い第3の電圧を第3のトランジスタの入力電極および第2の電極間に与えて第3のトランジスタを導通させ、第1の信号の後縁に応答して第3の電圧を第4のトランジスタの入力電極および第2の電極間に与えて第4のトランジスタを導通させる駆動回路とが設けられる。10

**【0015】**

この駆動回路は、第3のトランジスタの入力電極および第2の電極間に接続された第1の抵抗素子と、その一方電極が第1の信号の相補信号を受け、その他方電極が第3のトランジスタの入力電極に接続された第1のキャパシタと、第4のトランジスタの入力電極および第2の電極間に接続された第2の抵抗素子と、その一方電極が第1の信号を受け、その他方電極が第4のトランジスタの入力電極に接続された第2のキャパシタとを含み、第1の信号およびその相補信号をそれぞれ第3および第4のトランジスタの第2の電極に与える。したがって、第1の信号の前縁または後縁に応答して第1の信号の振幅電圧である第1の電圧よりも高い第3の電圧を第3または第4のトランジスタの入力電極および第2の電極間に与えるので、第1の信号の振幅電圧が第3および第4のトランジスタのしきい値電圧よりも低い場合でも動作する。20

**【0016】**

また好ましくは、第1の抵抗素子は、第3のトランジスタの入力電極および第2の電極間に接続され、その入力電極が第4の電圧を受ける第5のトランジスタを含む。第2の抵抗素子は、第4のトランジスタの入力電極および第2の電極間に接続され、その入力電極が第4の電圧を受ける第6のトランジスタを含む。この場合は、第1および第2の抵抗素子の占有面積が小さくて済む。30

**【0017】**

また好ましくは、第5および第6のトランジスタは第2の導電形式であり、第4の電圧は第2の電圧に等しい。この場合は、電圧源の数が少なくて済む。

**【0018】**

また好ましくは、第1の抵抗素子は、第3のトランジスタの入力電極および第2の電極間に接続された第5のトランジスタを含む。第2の抵抗素子は、第4のトランジスタの入力電極および第2の電極間に接続された第6のトランジスタを含む。駆動回路は、さらに、第1の信号の前縁に応答して第5のトランジスタの抵抗値をパルス的に高くし、第1の信号の後縁に応答して第6のトランジスタの抵抗値をパルス的に高くするためのパルス発生回路を含む。この場合は、第3および第4のトランジスタの入力電極の電位低下を緩やかにすることができます。40

**【0019】**

また好ましくは、第5および第6のトランジスタは第2の導電形式である。パルス発生回路は、第2の電圧と同極性の第4の電圧のノードと第5のトランジスタの入力電極との間に接続された第3の抵抗素子と、その一方電極が第1の信号を受け、その他方電極が第

5のトランジスタの入力電極に接続された第3のキャパシタと、第4の電圧のノードと第6のトランジスタの入力電極との間に接続された第4の抵抗素子と、その一方電極が第1の信号の相補信号を受け、その他方電極が第6のトランジスタの入力電極に接続された第4のキャパシタとを含む。この場合は、第3または第4の抵抗素子を介して第4の電圧に充電された第5または第6のトランジスタの入力電極が第3または第4のキャパシタを介して第1の電圧分だけ降圧される。

#### 【0020】

また好ましくは、第4の電圧は第2の電圧に等しい。この場合は、電圧源の数が少なくて済む。

#### 【0021】

また好ましくは、第5および第6のトランジスタは第1の導電形式である。パルス発生回路は、第2の電圧と逆極性の第4の電圧のノードと第5のトランジスタの入力電極との間に接続された第3の抵抗素子と、その一方電極が第1の信号の相補信号を受け、その他方電極が第5のトランジスタの入力電極に接続された第3のキャパシタと、第4の電圧のノードと第6のトランジスタの入力電極との間に接続された第4の抵抗素子と、その一方電極が第1の信号を受け、その他方電極が第6のトランジスタの入力電極に接続された第4のキャパシタとを含む。この場合は、第3または第4の抵抗素子を介して第4の電圧に充電された第5または第6のトランジスタの入力電極が第3または第4のキャパシタを介して第1の電圧分だけ昇圧される。

#### 【0022】

また好ましくは、駆動回路は、さらに、第3のトランジスタの第2の電極および入力電極間に接続された第1のダイオード素子と、第4のトランジスタの第2の電極および入力電極間に接続された第2のダイオード素子とを含む。この場合は、第3または第4のトランジスタの入力電極を第1の電圧に迅速に充電することができる。

#### 【0023】

また、この発明に係る他の振幅変換回路は、その振幅が第1の電圧である第1の信号を、その振幅が第1の電圧よりも高い第2の電圧である第2の信号に変換するものである。この振幅変換回路では、それらの第1の電極がともに第2の電圧を受け、それらの第2の電極が第2の信号およびその相補信号を出力するための第1および第2の出力ノードにそれぞれ接続され、それらの入力電極がそれぞれ第2および第1の出力ノードに接続された第1の導電形式の第1および第2のトランジスタと、それらの第1の電極がそれぞれ第1および第2の出力ノードに接続された第2の導電形式の第3および第4のトランジスタと、第1の信号およびその相補信号によって駆動され、第1の信号の前縁に応答して第1の電圧よりも高い第3の電圧を第3のトランジスタの入力電極および第2の電極間に与えて第3のトランジスタを導通させ、第1の信号の後縁に応答して第3の電圧を第4のトランジスタの入力電極および第2の電極間に与えて第4のトランジスタを導通させる駆動回路とが設けられる。この駆動回路は、第3のトランジスタの第2の電極と基準電圧のノードとの間に接続された第1の抵抗素子と、その一方電極が第1の信号を受け、その他方電極が第3のトランジスタの第2の電極に接続された第1のキャパシタと、第4のトランジスタの第2の電極と基準電圧のノードとの間に接続された第2の抵抗素子と、その一方電極が第1の信号の相補信号を受け、その他方電極が第4のトランジスタの第2の電極に接続された第2のキャパシタとを含み、第1の信号およびその相補信号をそれぞれ第4および第3のトランジスタの入力電極に与える。したがって、第1の信号の前縁または後縁に応答して第1の信号の振幅電圧である第1の電圧よりも高い第3の電圧を第3または第4のトランジスタの入力電極および第2の電極間に与えるので、第1の信号の振幅電圧が第3および第4のトランジスタのしきい値電圧よりも低い場合でも動作する。

#### 【0024】

また好ましくは、第1の抵抗素子は、第3のトランジスタの第2の電極と基準電圧のノードとの間に接続された第5のトランジスタを含む。第2の抵抗素子は、第2のトランジスタの第2の電極と基準電圧のノードとの間に接続された第6のトランジスタを含む。駆

10

20

30

40

50

動回路は、さらに、第1の信号の前縁に応答して第5のトランジスタの抵抗値をパルス的に高くし、第1の信号の後縁に応答して第6のトランジスタの抵抗値をパルス的に高くするためのパルス発生回路を含む。この場合は、第3および第4のトランジスタの入力電極の電圧上昇を緩やかにすることができる。

#### 【0025】

また好ましくは、第5および第6のトランジスタは第2の導電形式である。パルス発生回路は、第2の電圧と同極性の第4の電圧のノードと第5のトランジスタの入力電極との間に接続された第3の抵抗素子と、その一方電極が第1の信号を受け、その他方電極が第5のトランジスタの入力電極に接続された第3のキャパシタと、第4の電圧のノードと第6のトランジスタの入力電極との間に接続された第4の抵抗素子と、その一方電極が第1の信号の相補信号を受け、その他方電極が第6のトランジスタの入力電極に接続された第4のキャパシタとを含む。この場合は、第3または第4の抵抗素子を介して第4の電圧に充電された第5または第6のトランジスタの入力電極が第3または第4のキャパシタを介して第1の電圧分だけ降圧される。10

#### 【0026】

また好ましくは、第4の電圧は第2の電圧に等しい。この場合は、電圧源の数が少なくて済む。

#### 【0027】

また好ましくは、さらに、第1および第2の出力ノードの電位をラッチするためのラッチ回路が設けられる。この場合は、第1および第2の出力ノードの電位を安定に保持することができる。20

#### 【0028】

また好ましくは、ラッチ回路は、それらの第1の電極がそれぞれ第1および第2の出力ノードに接続され、それらの第2の電極がそれぞれ第1の信号およびその相補信号を受け、それらの入力電極がそれぞれ第2および第1の出力ノードに接続された第2の導電形式の第5および第6のトランジスタを含む。この場合は、ラッチ回路を容易に構成することができる。

#### 【0029】

また好ましくは、ラッチ回路は、それぞれ第1および第2の出力ノードと基準電圧のノードとの間に接続され、それらの入力電極がそれぞれ第2および第1の出力ノードに接続された第2の導電形式の第5および第6のトランジスタを含む。この場合は、第1の信号およびその相補信号の駆動力が小さくて済む。30

#### 【0030】

また好ましくは、さらに、第1のトランジスタの第2の電極と第1の出力ノードとの間に介挿され、その入力電極が第3のトランジスタの入力電極に接続された第1の導電形式の第5のトランジスタと、第2のトランジスタの第2の電極と第2の出力ノードとの間に介挿され、その入力電極が第4のトランジスタの入力電極に接続された第1の導電形式の第6のトランジスタとが設けられる。この場合は、第2の電圧のノードから第1および第2の出力ノードに流れる電流を小さくすることができ、消費電流の低減化を図ることができる。40

#### 【0031】

また好ましくは、第1～第4のトランジスタは薄膜トランジスタである。この発明は、この場合に特に有効である。

#### 【0032】

#### 【発明の実施の形態】

##### [実施の形態1]

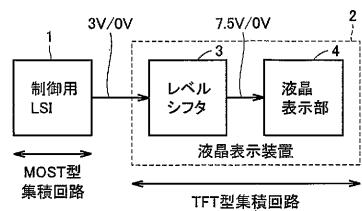

図1は、この発明の実施の形態1による携帯電話機の画像表示に関連する部分の構成を示すブロック図である。

#### 【0033】

図1において、この携帯電話機は、MOS T型集積回路である制御用LSI1と、TF50

T型集積回路である液晶表示装置2とを備え、液晶表示装置2はレベルシフタ3および液晶表示部4を含む。

#### 【0034】

制御用LSI1は、液晶表示装置2用の制御信号を出力する。この制御信号の「H」レベルは3Vであり、その「L」レベルは0Vである。制御信号は実際には多数生成されるが、ここでは説明の簡単化のため制御信号は1つとする。レベルシフタ3は、制御用LSI1からの制御信号の論理レベルを変換して内部制御信号を生成する。この内部制御信号の「H」レベルは7.5Vであり、その「L」レベルは0Vである。液晶表示部4は、レベルシフタ3からの内部制御信号に従って画像を表示する。

#### 【0035】

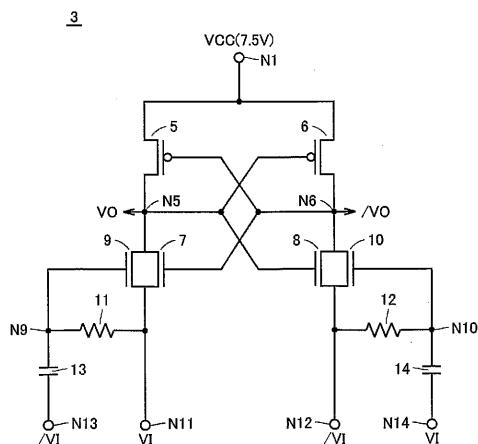

図2は、レベルシフタ3の構成を示す回路図である。図2において、このレベルシフタ3は、P型TFT5, 6、N型TFT7～10、抵抗素子11, 12およびキャパシタ13, 14を含む。P型TFT5, 6は、それぞれ電源電位VCC(7.5V)のノードN1と出力ノードN5, N6との間に接続され、それらのゲートはそれぞれ出力ノードN6, N5に接続される。出力ノードN5, N6に現われる信号は、それぞれ、このレベルシフタ3の出力信号VO, /VOとなる。N型TFT7は、出力ノードN5と入力ノードN11との間に接続され、そのゲートは出力ノードN6に接続される。N型TFT8は、出力ノードN6と入力ノードN12との間に接続され、そのゲートは出力ノードN5に接続される。入力ノードN11, N12は、それぞれ入力信号VI, /VIを受ける。P型TFT5, 6およびN型TFT7, 8は、出力ノードN5, N6のレベルをラッチするためのラッチ回路を構成する。

#### 【0036】

N型TFT9は、入力ノードN11と出力ノードN5との間に接続され、そのゲートはノードN9に接続される。N型TFT10は、入力ノードN11と出力ノードN6との間に接続され、そのゲートはノードN10に接続される。抵抗素子11はノードN9とN11の間に接続され、抵抗素子12はノードN10とN12の間に接続される。キャパシタ13は入力ノードN13とノードN9との間に接続され、キャパシタ14は入力ノードN14とノードN10との間に接続される。入力ノードN13, N14は、それぞれ入力信号VI, /VIを受ける。抵抗素子11およびキャパシタ13は昇圧回路を構成し、抵抗素子12およびキャパシタ14は昇圧回路を構成する。

#### 【0037】

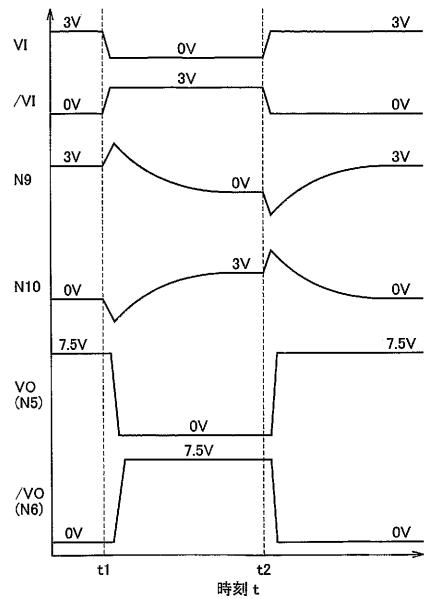

図3は、図2に示したレベルシフタ3の動作を示すタイムチャートである。図3を参照して、初期状態では、入力信号VI, /VIがそれぞれ「H」レベル(3V)および「L」レベル(0V)にされ、出力信号VO, /VOがそれぞれ「H」レベル(7.5V)および「L」レベル(0V)にされている。このとき、ノードN9は抵抗素子11によって入力信号VIと同電位の3Vにされ、ノードN10は抵抗素子12によって入力信号VIと同電位の0Vにされている。これらの電位関係により、P型TFT5およびN型TFT8が導通し、他のTFT6, 7, 9, 10は非導通になっている。つまり、出力ノードN5はP型TFT5を介して電源電位VCC(7.5V)を受け、出力ノードN6はN型TFT8を介して入力信号VIの電位(0V)を受けている。

#### 【0038】

次に、ある時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられるとともに入力信号VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、入力信号VIの電位変化がキャパシタ13を介してノードN9に伝達され、ノードN9の電位は3V以上の電位に上昇する。このときの電位上昇分は、キャパシタ13の容量値とノードN9の寄生容量(図示せず)の容量値との比でほぼ決まる。キャパシタ13が容量値をノードN9の寄生容量の容量値よりも十分大きな値に設定すると、ノードN9は入力信号VI, /VIの振幅電圧(3V)の2倍の6V近くまで上昇する。

#### 【0039】

10

20

30

40

50

一方、入力信号V<sub>I</sub>は/V<sub>I</sub>と同時に「H」レベル(3V)から「L」レベル(0V)に立下げられるので、ノードN9の電荷が抵抗素子11を介してノードN11に放電される。したがって、ノードN9の電位は、3Vから上昇してピーク値に達した後、0Vまで徐々に低下する。ここで、抵抗素子11の抵抗値を適切に設定することにより、ノードN9の電位を所定時間だけ3V以上の所定電位に保持させることができる。ノードN9の電位が所定電位になるとN型TFT9が導通し、出力ノードN5の電位が低下する。出力ノードN5の電位が低下すると、P型TFT6が導通して出力ノードN6の電位が上昇する。これにより、P型TFT5が非導通になるとともに、N型TFT7が導通し、出力ノードN5の電位が急速に「L」レベル(0V)に低下する。

## 【0040】

10

一方、入力信号V<sub>I</sub>が「H」レベル(3V)から「L」レベル(0V)への電位変化がキャパシタ14を介してノードN10に伝達され、ノードN10の電位は0Vから-3V近くまで低下する。しかし、N型TFT10は既に非導通になっているので、回路動作への影響はない。

## 【0041】

以上の結果、出力信号V<sub>O</sub>が「H」レベル(7.5V)から「L」レベル(0V)に立下げられるとともに出力信号/V<sub>O</sub>が「L」レベル(0V)から「H」レベル(7.5V)に立上げられ、3Vから7.5Vへの論理レベルの変換が行なわれたことになる。

## 【0042】

20

ノードN9,N10の電位は、それぞれ抵抗素子11,12によって時間の経過とともにそれぞれ入力信号V<sub>I</sub>,/V<sub>I</sub>のレベルにシフトされる。時刻t2では、ノードN9,N10の電位は、それぞれ入力信号V<sub>I</sub>,/V<sub>I</sub>のレベルになっている。時刻t2において、入力信号/V<sub>I</sub>が「L」レベル(0V)から「H」レベル(3V)に立上げられるとともに入力信号V<sub>I</sub>が「H」レベル(3V)から「L」レベル(0V)に立下げられると、上記と逆の電位関係で回路が動作する。

## 【0043】

この実施の形態1では、入力信号V<sub>I</sub>の立下がりエッジに応答して入力信号V<sub>I</sub>の振幅電圧(3V)よりも高い電圧(約6V)を生成してN型TFT9のゲート-ソース間に与えるので、入力信号V<sub>I</sub>の振幅電圧(3V)がN型TFT9のしきい値電圧よりも低い場合でもレベルシフタ3が動作する。したがって、図1に示したように、レベルシフタ3と液晶表示部4を1つの液晶表示装置2(TFT型集積回路)にすることができる。よって、レベルシフタ52と液晶表示装置53とを別個に設ける必要があった従来に比べ、部品数が少なくて済み、システムコストが低くなる。

30

## 【0044】

また、動作の途中で過渡的に電源電流が流れるが、出力ノードN5,N6のレベルが決まった後はTFT5,8,10またはTFT6,7,9が非導通になるので、電源電位V<sub>CC</sub>のノードN1から入力ノードN11~N14への直流電流は流れない。したがって、回路の消費電力も極めて小さくなる。

## 【0045】

40

なお、この実施の形態1では、TFT5~10を用いたが、TFTの代わりにMOSトランジスタを用いてもよい。この場合は、入力信号V<sub>I</sub>,/V<sub>I</sub>の振幅がMOSトランジスタのしきい値電圧よりも小さい場合でも動作する。

## 【0046】

また、この実施の形態1では、絶縁ゲート型電界効果トランジスタであるTFTを用いたが、他の形式の電界効果トランジスタを用いてもよいことは言うまでもない。

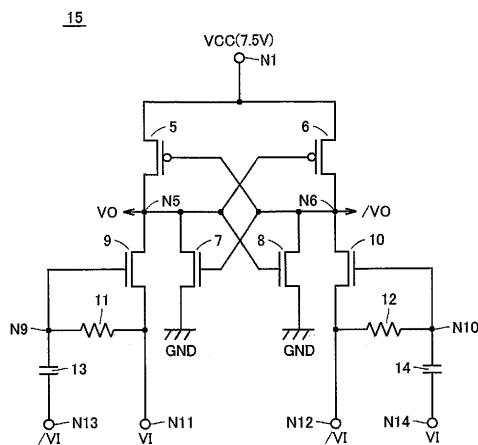

## 【0047】

以下、この実施の形態1の種々の変更例について説明する。図4のレベルシフタ15では、N型TFT7,8のソースが接地される。この変更例では、N型TFT7,8の電流を入力ノードN11,N12に流さずに接地電位GNDのラインに流すので、入力信号V<sub>I</sub>,/V<sub>I</sub>の駆動力が小さくて済む。

50

## 【0048】

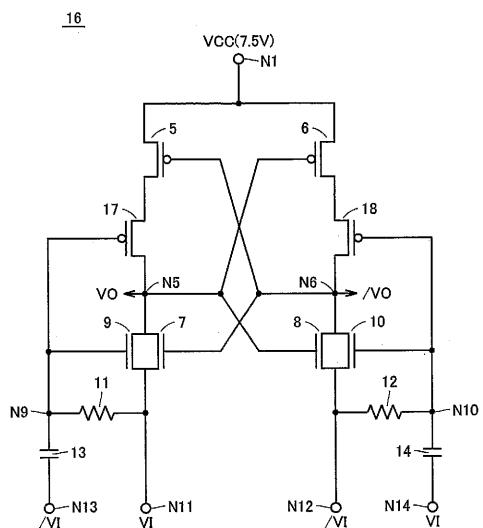

図5のレベルシフタ16が図2のレベルシフタ3と異なる点は、P型TFT17, 18が追加されている点である。P型TFT17は、P型TFT5のドレインとノードN5との間に介挿され、そのゲートはノードN9に接続される。P型TFT18は、P型TFT6のドレインとノードN6との間に介挿され、そのゲートはノードN10に接続される。この変更例では、たとえば、入力信号VIが「L」レベル(0V)から「H」レベル(3V)に立上げられたときに(図3の時刻t1参照)、P型TFT17が導通状態から非導通状態に変化し、電源電位VCCのノードN1から出力ノードN5に流入する電流を抑制するので、出力ノードN5の電位が低下しやすくなる。この結果、P型TFT6が迅速に導通してノードN6の電位が上昇しやすくなる。また、上述のように、P型TFT17, 18が非導通になることによって電源電位VCCのノードN1から出力ノードN5, N6に流入する電流が抑制されるので、消費電力が小さくて済む。

## 【0049】

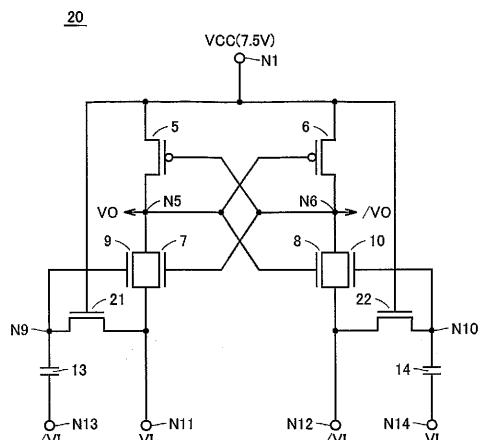

図6のレベルシフタ20が図2のレベルシフタ3と異なる点は、抵抗素子11, 12がそれぞれN型TFT21, 22で置換されている点である。N型TFT21は、ノードN9とN11の間に接続され、そのゲートは電源電位VCCを受ける。N型TFT22は、ノードN10とN12の間に接続され、そのゲートは電源電位VCCを受ける。N型TFT21, 22の各々は、等価的に抵抗素子の働きをする。図2の抵抗素子11, 12に比べて単位寸法当たりの抵抗値が高いので、抵抗素子としての占有面積が小さくなる。なお、N型TFT21, 22の各々をP型TFTで置換してもよい。ただし、この場合はP型TFTのゲートに負電圧(-7.5V)を与える必要がある。

## 【0050】

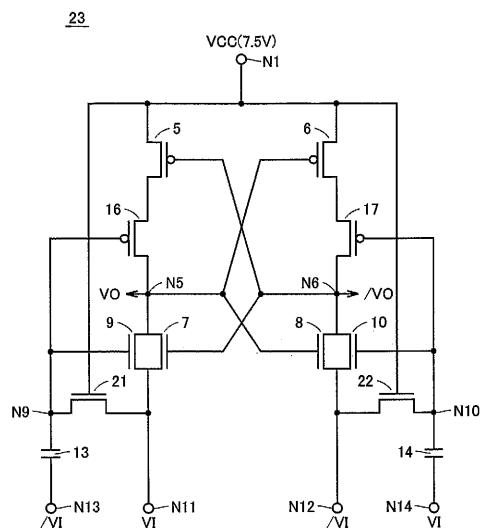

図7のレベルシフタ23が図5のレベルシフタ16と異なる点は、抵抗素子11, 12がそれぞれN型TFT21, 22で置換されている点である。したがって、この変更例では、図5の変更例と図6の変更例の両方の効果を有する。

## 【0051】

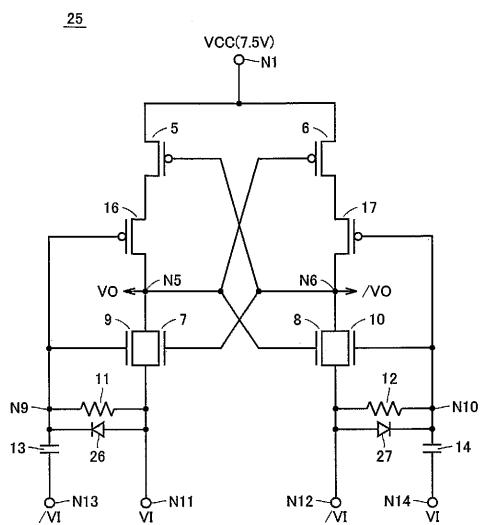

図8のレベルシフタ25は、図5のレベルシフタ16にダイオード素子26, 27を追加したものである。ダイオード素子26はノードN11とN9の間に接続され、ダイオード素子27はノードN12とN14の間に接続される。ダイオード素子26は、入力信号VIが「L」レベル(0V)から「H」レベル(3V)に立上げられたとき、ノードN9の「H」レベル(3V)への上昇を速くする(図3参照)。これにより、次に入力信号VIが「L」レベル(0V)から「H」レベル(3V)に立上げられたときにノードN9の「H」レベル(3V)への立上がりが速くなり、N型TFT9は迅速に導通する。ダイオード素子27は、N型TFT10に対してダイオード素子26と同じ働きをする。したがって、この変更例では、入力信号VI, /VIのレベル変化に対する出力信号VO, /VOのレベル変化が速くなる。

## 【0052】

## [実施の形態2]

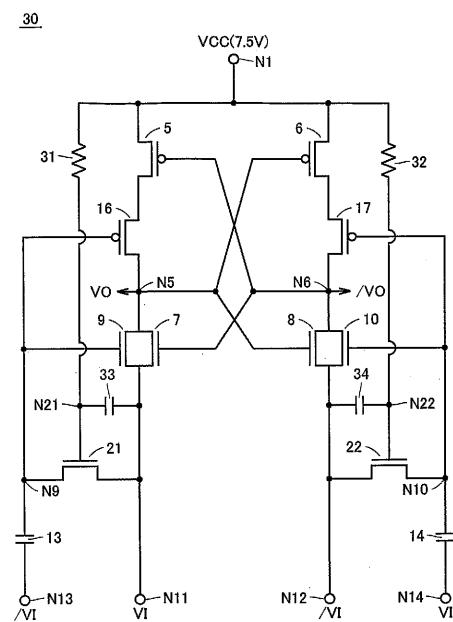

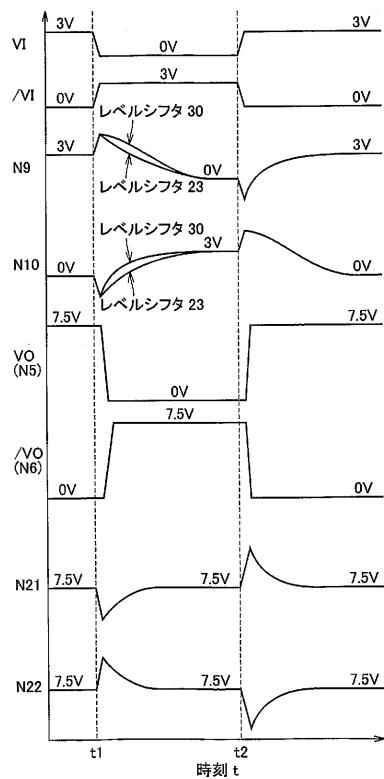

図9は、この発明の実施の形態2によるレベルシフタ30の構成を示す回路図であって、図7と対比される図である。図9を参照して、このレベルシフタ30が図7のレベルシフタ23と異なる点は、抵抗素子31, 32およびキャパシタ33, 34が追加されている点である。抵抗素子31は電源電位VCCのノードN1とN型TFT21のゲート(ノードN21)との間に介挿され、抵抗素子32はノードN1とN型TFT22のゲート(ノードN22)との間に介挿される。キャパシタ33はノードN11とN21の間に接続され、キャパシタ34はノードN12とN22の間に接続される。

## 【0053】

図10は、レベルシフタ30の動作を示すタイムチャートである。図10において、初期状態では、入力信号VI, /VIがそれぞれ「H」レベル(3V)および「L」レベル(0V)にされ、出力信号VO, /VOがそれぞれ「H」レベル(7.5V)および「L」レベル(0V)にされている。ノードN21, N22はそれぞれ抵抗素子31, 32を

介して電源電位VCC(7.5V)を受けてるので、N型TFT21, 22は導通している。したがって、ノードN9は入力信号VIと同電位の3Vにされ、ノードN10は入力信号/VIと同電位の0Vにされている。これらの電位関係により、P型TFT5, 16およびN型TFT8が導通し、他のTFT6, 7, 9, 10, 17は非導通になっている。つまり、出力ノードN5はP型TFT5, 16を介して電源電位VCC(7.5V)を受け、出力ノードN6はN型TFT8を介して入力信号/VIの電位(0V)を受けている。

#### 【0054】

次に、ある時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられるとともに入力信号/VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、入力信号/VIの電位変化がキャパシタ13を介してノードN9に伝達され、ノードN9の電位は3V以上の電位に上昇する。同時に、入力信号VIの電位変化がキャパシタ33を介してノードN29に伝達され、ノードN21の電位は3V程度低下する。ノードN21の電位が低下するとノードN1から抵抗素子31を介してノードN21に電力が流入し、ノードN21が電源電位VCC(7.5V)に戻る。ノードN21が7.5Vよりも低下している期間はN型TFT21の抵抗値は高くなる。

#### 【0055】

また、時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられると、ノードN9の電荷がN型TFT21を介してノードN11に放電される。したがって、ノードN9の電位は、3Vから上昇してピーク値に達した後、0Vまで徐々に低下する。

#### 【0056】

このとき、N型TFT21の抵抗値は所定時間だけ比較的高くなるので、ノードN1のレベル低下が図7のレベルシフタ23に比べて緩やかになる。これにより、N型TFT9の導通時間が長くなりノードN5の電位低下が容易になる。

#### 【0057】

他方、ノードN10側では、時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられるとともに入力信号/VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、入力信号/VIの電位変化がキャパシタ14を介してノードN10に伝達され、ノードN10の電位は0V以下の電位に低下する。同時に、入力信号/VIの電位変化がキャパシタ34を介してノードN22に伝達され、ノードN22の電位は3V程度上昇する。ノードN22の電位が上昇するとノードN22から抵抗素子32を介してノードN21に電流が流出し、ノードN22が電源電位VCC(7.5V)に戻る。ノードN22の電位が7.5Vよりも高い期間はN型TFT22の抵抗値は低くなる。

#### 【0058】

また、時刻t1において、入力信号/VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、ノードN12からN型TFT22を介してノードN10に電流が流入する。したがって、ノードN10の電位は、0Vから低下してピーク値に達した後、3Vまで徐々に上昇する。

#### 【0059】

このとき、N型TFT22の抵抗値が所定時間だけ比較的低くなるので、ノードN10のレベル上昇が図7のレベルシフタ23に比べて速くなる。これにより、次の時刻t2におけるノードN10の昇圧を容易に行なうことができる。

#### 【0060】

以上より、このレベルシフタ30の動作マージンはレベルシフタ23の動作マージンよりも大きくなる。

#### 【0061】

なお、この実施の形態2では、抵抗素子31, 32の一方電極を電源電位VCC(7.5V)のノードN1に接続したが、電源電位VCCとは異なる正の電源電位のノードに接

10

20

30

40

50

続してもよい。

#### 【0062】

また、抵抗素子31, 32の各々をN型TFTまたはP型TFTで構成してもよい。N型TFTのゲートには電源電位VCCよりも高い正電位を与え、P型TFTのゲートには電源電位VCCよりも低い電位を与えるとよい。また、P型TFT16, 17を削除してもよい。

#### 【0063】

##### [実施の形態3]

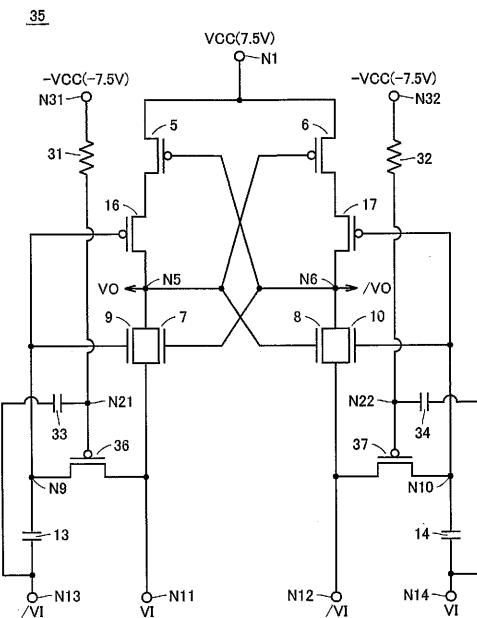

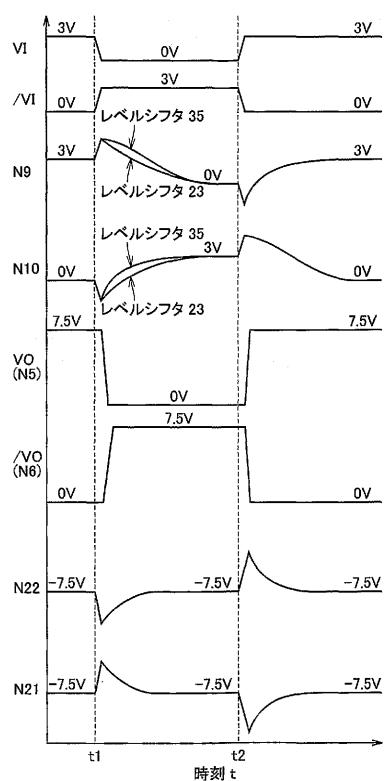

図11は、この発明の実施の形態3によるレベルシフタ35の構成を示す回路図であつて、図9と対比される図である。図11を参照して、このレベルシフタ35が図9のレベルシフタ30と異なる点は、N型TFT21, 22がP型TFT36, 37で置換されている点である。P型TFT36は、ノードN9とN11の間に接続され、そのゲートはノードN21に接続される。P型TFT37は、ノードN10とN12の間に接続され、そのゲートはノードN22に接続される。

#### 【0064】

また、抵抗素子31は、ノードN21と負の電源電位-VCC(-7.5V)のノードN31との間に接続される。抵抗素子32は、ノードN22と負の電源電位-VCC(-7.5V)のノードN32との間に接続される。キャパシタ33はノードN13とN21の間に接続され、キャパシタ34はノードN14とN22の間に接続される。

#### 【0065】

図12は、レベルシフタ35の動作を示すタイムチャートである。図12において、初期状態では、入力信号VI, /VIがそれぞれ「H」レベル(3V)および「L」レベル(0V)にされ、出力信号VO, /VOがそれぞれ「H」レベル(7.5V)および「L」レベル(0V)にされている。ノードN21, N22はそれぞれ抵抗素子31, 32を介して負の電源電位-VCC(-7.5V)を受けており、P型TFT36, 37は導通している。したがって、ノードN9は入力信号VIと同電位の3Vにされ、ノードN10は入力信号/VIと同電位の0Vにされている。これらの電位関係により、P型TFT5, 16およびN型TFT8が導通し、他のTFT6, 7, 9, 10, 17は非導通になっている。つまり、出力ノードN5はP型TFT5, 16を介して電源電位VCC(7.5V)を受け、出力ノードN6はN型TFT8を介して入力信号/VIの電位(0V)を受けている。

#### 【0066】

次に、ある時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられるとともに入力信号/VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、入力信号/VIの電位変化がキャパシタ13を介してノードN9に伝達され、ノードN9の電位は3V以上の電位に上昇する。同時に、入力信号/VIの電位変化がキャパシタ33を介してノードN21に伝達され、ノードN21の電位は3V程度上昇する。ノードN21の電位が上昇するとノードN21から抵抗素子31を介してノードN31に電流が流出し、ノードN21は負の電源電位-VCC(-7.5V)に戻る。ノードN21の電位が-7.5Vよりも高い期間はP型TFT36の抵抗値は高くなる。

#### 【0067】

また、時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられると、ノードN9の電荷がP型TFT36を介してノードN11に放電される。したがって、ノードN9の電位は、3Vから上昇してピーク値に達した後、0Vまで徐々に低下する。

#### 【0068】

このとき、P型TFT36の抵抗値が所定時間だけ比較的高くなるので、ノードN9のレベル低下が図7のレベルシフタ23に比べて緩やかになる。これにより、N型TFT9の導通時間が長くなりノードN5の電位低下が容易になる。

10

20

30

40

50

## 【0069】

他方、ノードN10側では、時刻t1において、入力信号VIが「H」レベル(3V)から「L」レベル(0V)に立下げられるとともに入力信号/VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、入力信号VIの電位変化がキャパシタ14を介してノードN10に伝達され、ノードN10の電位は0V以下の電位に低下する。同時に入力信号VIの電位変化がキャパシタ34を介してノードN22に伝達され、ノードN22の電位は3V程度低下する。ノードN22の電位が低下するとノードN32から抵抗素子32を介してノードN20に電流が流入し、ノードN22が負の電源電位-VCC(-7.5V)に戻る。ノードN22の電位が-7.5Vよりも低い期間はP型TFT37の抵抗値は低くなる。

10

## 【0070】

また、時刻t1において、入力信号/VIが「L」レベル(0V)から「H」レベル(3V)に立上げられると、ノードN12からP型TFT37を介してノードN10に電流が流入する。したがって、ノードN10の電位は、0Vから低下してピーク値に達した後、3Vまで徐々に上昇する。

## 【0071】

このとき、P型TFT37の抵抗値が所定時間だけ比較的低くなるので、ノードN10のレベル上昇は図7のレベルシフタ23に比べて早くなる。これにより、次の時刻t2におけるノードN10の昇圧を容易に行なうことができる。

## 【0072】

以上より、このレベルシフタ35の動作マージンはレベルシフタ23の動作マージンよりも大きくなる。

20

## 【0073】

なお、抵抗素子31,32の各々をN型TFTまたはP型TFTで構成してもよい。N型TFTのゲートには正の電源電位VCCよりも高い電位を与え、P型TFTのゲートには負の電源電位-VCCよりも低い負電位を与えるとよい。また、P型TFT16,17を削除してもよい。

## 【0074】

## [実施の形態4]

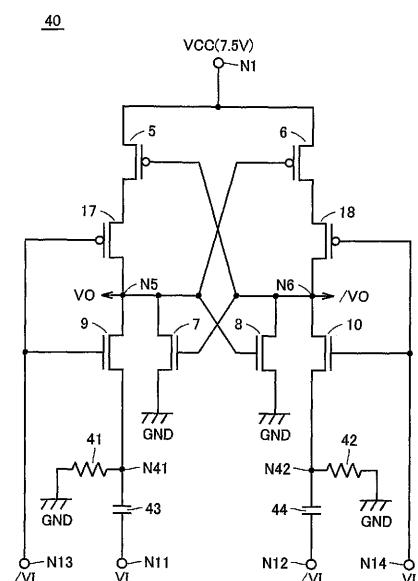

図13は、この発明の実施の形態4によるレベルシフタ40の構成を示す回路図であつて、図5と対比される図である。

30

## 【0075】

図13において、このレベルシフタ40が図5のレベルシフタ16と異なる点は、N型TFT7,8のソースがともに接地され、抵抗素子11,12およびキャパシタ13,14が抵抗素子41,42およびキャパシタ43,44で置換されている点である。

## 【0076】

キャパシタ43は入力ノードN11とN型TFT9のソース(ノードN41)との間に接続され、キャパシタ44は入力ノードN12とN型TFT10のソース(ノードN42)との間に接続される。抵抗素子41,42は、それぞれノードN41,N42と接地電位GNDのラインとの間に接続される。入力信号VIはTFT9,17のゲートに直接与えられ、入力信号VIはTFT10,18のゲートに直接与えられる。

40

## 【0077】

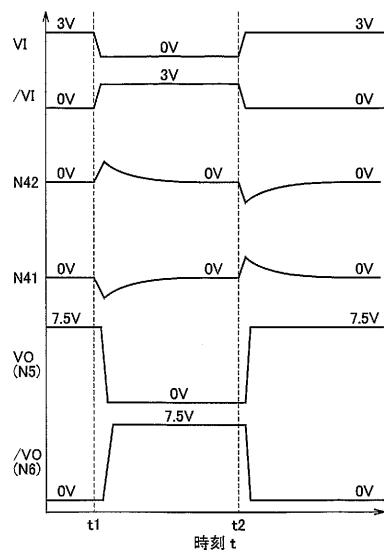

図14は、レベルシフタ40の動作を示すタイムチャートである。図14を参照して、初期状態では、入力信号VI,VIがそれぞれ「H」レベル(3V)および「L」レベル(0V)にされ、出力信号VO,VOがそれぞれ「H」レベル(7.5V)および「L」レベル(0V)にされている。ノードN41,N42は、抵抗素子41,42によって接地電位GNDにされている。これらの電位関係により、P型TFT5,17およびN型TFT8,10が導通し、他のTFT6,7,9,18は非導通になっている。つまり、出力ノードN5はP型TFT5,7を介して電源電位VCC(7.5V)を受け、出力ノードN6はN型TFT8を介して接地電位GND(0V)を受けている。

50

## 【0078】

次に、ある時刻  $t_1$ において、入力信号  $V_I$  が「H」レベル(3V)から「L」レベル(0V)に立下げられるとともに入力信号  $/V_I$  が「L」レベル(0V)から「H」レベル(3V)に立上げられると、入力信号  $V_I$  の電位変化がキャパシタ43を介してノードN41に伝達され、ノードN41は接地電位GND(0V)以下の電位に低下する。電位の低下分は、キャパシタ43の容量値とノードN41の寄生容量(図示せず)の容量値との比で決まる。キャパシタ43の容量値を寄生容量の容量値よりも十分大きな値に設定すると、ノードN41の電位は入力信号  $V_I$  の振幅電圧分だけ低下し、-3Vまで低下する。

## 【0079】

ノードN41の電位が約-3Vまで低下すると、接地電位GNDのラインから抵抗素子41を介してノードN41に電流が流入する。したがって、ノードN41の電位は、0Vから低下してピーク値に達した後、0Vまで徐々に上昇する。ここで、抵抗素子41の抵抗値を適切に設定することにより、ノードN41の電位を所定時間だけ0V以下の所定電位に保持させることができる。

## 【0080】

ノードN41が所定電位になると、N型TFT9のゲート-ソース間の電圧が3V~6Vになり、N型TFT9が導通してノードN5の電位が低下する。ノードN5の電位が低下すると、P型TFT6が導通してノードN6の電位が上昇する。このように、P型TFT5が非導通になるとともにN型TFT7が導通し、出力ノードN5の電位が急速に「L」レベル(0V)に低下する。

## 【0081】

一方、入力信号  $/V_I$  の「L」レベル(0V)から「H」レベル(3V)への電位変化がキャパシタ44を介してノードN42に伝達され、ノードN42の電位は0Vから3V近くまで上昇する。しかし、N型TFT10は既に非導通になっているので、回路動作への影響はない。

## 【0082】

以上の結果、出力信号  $V_O$  が「H」レベル(7.5V)から「L」レベル(0V)に立下げられるとともに出力信号  $/V_O$  が「L」レベル(0V)から「H」レベル(7.5V)に立上げられ、3Vから7.5Vへの論理レベルの変換が行なわれたことになる。

## 【0083】

ノードN41, N42の電位は、それぞれ、抵抗素子41, 42によって時間の経過とともにそれぞれ接地電位GNDに近づき、時刻  $t_2$  ではノードN41, N42の電位はほぼ接地電位GNDになっている。時刻  $t_2$  において、入力信号  $V_I$  が「L」レベル(0V)から「H」レベル(3V)に立上げられるとともに入力信号  $/V_I$  が「H」レベル(3V)から「L」レベル(0V)に立下げられると、上記と逆の電位関係で回路が動作する。

## 【0084】

この実施の形態4でも、実施の形態1と同じ効果が得られる。

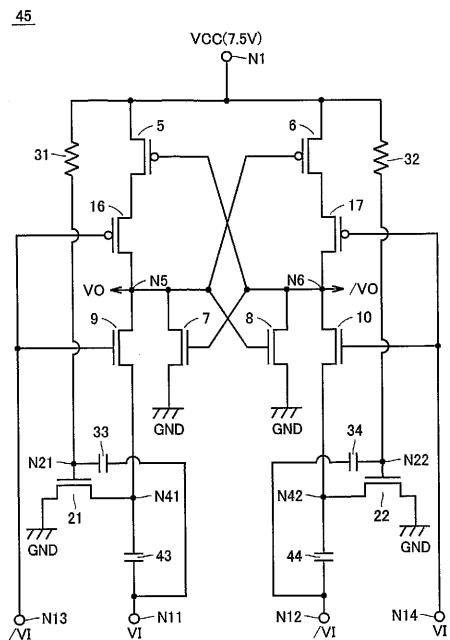

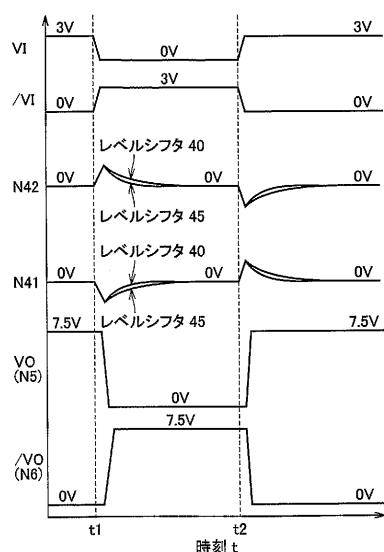

なお図15に示すように、実施の形態2に従って、抵抗素子41, 42をそれぞれN型TFT21, 22で置換し、N型TFT21, 22のゲート(ノードN21, N22)とノードN1との間にそれぞれ抵抗素子31, 32を接続し、ノードN11, N12とノードN21, N22との間にそれぞれキャパシタ33, 34を接続してもよい。図16に示すように、時刻  $t_1$  において入力信号  $V_I$  が「H」レベル(3V)から「L」レベル(0V)に立下げられると、ノードN21の電位が約3V低下し、所定時間だけ電源電位  $V_{CC}$ (7.5V)よりも低くなる。ノードN21の電位が7.5Vよりも低くなると、N型TFT21の抵抗値は高くなる。したがって、ノードN41のレベル上昇が図13のレベルシフタ40よりも緩やかになり、出力ノードN5を「L」レベルに引下げやすくなる。また、時刻  $t_1$  において入力信号  $/V_I$  が「L」レベル(0V)から「H」レベル(3V)に立上げられると、ノードN22の電位が約3V上昇し、所定時間だけ電源電位  $V_{CCC}$  50

(7.5V)よりも高くなる。ノードN21の電位が7.5Vよりも高くなると、N型TFT22の抵抗値が低くなる。したがって、ノードN42のレベル低下が図13のレベルシフタ40よりも早くなり、次の時刻t2におけるノードN42の降圧動作を容易に行なうことができる。

【0085】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【図1】この発明の実施の形態1による携帯電話機の画像表示に関連する部分を示すブロック図である。

【図2】図1に示したレベルシフタの構成を示す回路図である。

【図3】図2に示したレベルシフタの動作を示すタイムチャートである。

【図4】実施の形態1の変更例を示す回路図である。

【図5】実施の形態1の他の変更例を示す回路図である。

【図6】実施の形態1のさらに他の変更例を示す回路図である。

【図7】実施の形態1のさらに他の変更例を示す回路図である。

【図8】実施の形態1のさらに他の変更例を示す回路図である。

【図9】この発明の実施の形態2によるレベルシフタの構成を示す回路図である。

【図10】図9に示したレベルシフタの動作を示すタイムチャートである。

【図11】この発明の実施の形態3によるレベルシフタの構成を示す回路図である。

【図12】図11に示したレベルシフタの動作を示すタイムチャートである。

【図13】この発明の実施の形態4によるレベルシフタの構成を示す回路図である。

【図14】図13に示したレベルシフタの動作を示すタイムチャートである。

【図15】実施の形態4の変更例を示す回路図である。

【図16】図15に示したレベルシフタの動作を示すタイムチャートである。

【図17】従来の携帯電話機の画像表示に関連する部分を示すブロック図である。

【図18】図17に示したレベルシフタの構成を示す回路図である。

【図19】従来の他のレベルシフタの構成を示す回路図である。

10

20

30

【図1】

FIG.1【図3】

FIG.3【図2】

FIG.2【図4】

FIG.4【図5】

FIG.5

【図6】

FIG.6【図7】

FIG.7【図8】

FIG.8【図9】

FIG.9

【図 1 0】

FIG.10【図 1 1】

FIG.11【図 1 2】

FIG.12【図 1 3】

FIG.13

【図 1 4】

FIG.14【図 1 5】

FIG.15【図 1 6】

FIG.16【図 1 8】

FIG.18【図 1 7】

FIG.17

【図 19】

FIG.19

---

フロントページの続き

(72)発明者 飛田 洋一

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 清水 稔

(56)参考文献 特開平09-130231(JP,A)

特開平04-268818(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/0185

G09G 3/20

G09G 3/36

H03K 17/687

H04N 5/66