(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년02월23일

(11) 등록번호 10-1831710

(24) 등록일자 2018년02월19일

- (51) 국제특허분류(Int. Cl.)

*G01P 3/487* (2006.01) *G01P 3/488* (2006.01)

*G01P 3/489* (2006.01)

- (21) 출원번호 10-2012-7033397

- (22) 출원일자(국제) 2011년05월04일

심사청구일자 2016년03월29일

- (85) 번역문제출일자 2012년12월21일

- (65) 공개번호 10-2013-0086298

- (43) 공개일자 2013년08월01일

- (86) 국제출원번호 PCT/US2011/035142

- (87) 국제공개번호 WO 2011/152947

국제공개일자 2011년12월08일

- (30) 우선권주장

12/793,159 2010년06월03일 미국(US)

- (56) 선행기술조사문현

JP58193213 U

KR1020080000882 A

- (73) 특허권자

알레그로 마이크로시스템즈, 엘엘씨

미합중국 01615-0036 메사츄세츠 워스터 115

노스이스트 컷오프

- (72) 발명자

폴레토, 안드레아

프랑스 에프-74000 안시 1 르 데 빠빌롱

페르난데스, 데번

미국 03053 뉴햄프셔주 런던더리 29 오크리지 드

라이브

버네트, 에릭

미국 03857 뉴햄프셔주 뉴마켓 3 앤리스 드라이브

- (74) 대리인

박영우

전체 청구항 수 : 총 24 항

심사관 : 김창주

(54) 발명의 명칭 동작 센서, 그 방법 및 상태 채터가 감소된 상태 프로세서를 구비한 동작 센서에 제공되는 컴퓨터 판독용 저장매체

**(57) 요약**

동작센서는 상태 프로세서를 포함하여 자기장 필드 센싱 소자에 의해 제공되는 자기장 필드 신호와 연동된 상태들을 감지한다. 상태 프로세서는 감소된 상태 채터(state chatter)를 갖는 상태들을 생성하는 상태 피크 로직 모듈(state peak logic module)을 포함한다.

**대 표 도** - 도1

## 명세서

### 청구범위

#### 청구항 1

물체와 연동된 자기장필드를 나타내는 복수개의 자기장 필드 신호를 생성하는 복수개의 자기장 필드 센싱 소자들; 및

복수개의 상태 프로세서들을 포함하되, 상기 상태 프로세서들의 각각은 상기 자기장 필드 신호들의 각각에 응답하는 신호를 인가받아 상기 각 상태 프로세서는 상기 복수개의 자기장 필드 신호들의 각각과 연동된 복수개의 상태들을 나타내는 각각의 STATE\_SM 신호를 생성하고, 상기 각 상태는 신호 값들(signal value)의 각 영역을 나타내며, 상기 STATE\_SM 신호는 복수개의 제1 방향 상태 변환들(first direction state transition) 및 복수개의 제2 방향 상태 변환들을 포함하고, 상기 STATE\_SM 신호의 상기 제1 방향 상태 변환들 및 상기 제2 방향 상태 변환들은 상태 변환 채터(state transition chatter)할 수 있으며, 상기 상태 프로세서들의 각각은:

상기 각 STATE\_SM 신호를 인가받아 각 STATE\_PEAK 신호를 생성하는 각 상태 피크 로직 모듈(state peak logic module)을 포함하고, 상기 STATE\_PEAK 신호는 복수개의 제1 방향 상태 피크 변환들 및 복수개의 제2 방향 상태 피크 변환들을 포함하며, 상기 STATE\_PEAK 신호의 상기 제1 방향 상태 피크 변환들 및 상기 제2 방향 상태 피크 변환들은 감소된 상태 변환 채터를 갖는 동작 센서.

#### 청구항 2

제 1 항에 있어서, 상기 STATE\_SM 신호의 상태 값들(state values)은 STATE\_SM 레지스터 내에서 훌딩되고, 상기 STATE\_PEAK 신호의 상태 값들은 STATE\_PEAK 레지스터 내에서 훌딩되는 것을 특징으로 하는 동작센서.

#### 청구항 3

제 2 항에 있어서, 상기 동작센서는 상기 복수개의 상태 프로세서들과 연동된 진동 프로세서를 더 포함하고, 상기 진동 프로세서는 STATE\_PEAK 신호에 의한 상태가 STATE\_SM 신호에 의한 상태와 기설정된 숫자의 상태들만큼 차이나는 경우 상태 변환들이 발생하는 2-상태 POSCOMP\_PK 신호(two-state POSCOMP\_PK 신호)를 생성하는 굴절 프로세서(inflexion processor)를 포함하는 것을 특징으로 하는 동작센서.

#### 청구항 4

제 3 항에 있어서, 상기 상태 피크 로직 모듈은 상기 POSCOMP\_PK 신호가 제1 상태와 동일하고 상기 STATE\_SM 신호의 상태 값이 상기 STATE\_PEAK 신호의 상태 값보다 상기 기설정된 숫자의 상태들만큼 큰 경우에, 상기 STATE\_PEAK 레지스터 내에서 훌딩된 상태 값이 상기 STATE\_SM 레지스터 내에서 훌딩된 값과 동일하게 되도록 셋팅하는 상태 피크 로직 프로세서(state peak logic processor)를 포함하고,

상기 상태 피크 로직 프로세서는 상기 POSCOMP\_PK 신호가 제2 차등 상태(second different state)와 동일하고 상기 STATE\_SM 신호의 상태 값이 상기 STATE\_PEAK 신호의 상태 값보다 상기 기설정된 숫자의 상태들만큼 작은 경우에, 상기 STATE\_PEAK 레지스터 내에서 훌딩된 상태 값이 상기 STATE\_SM 레지스터 내에서 훌딩된 값과 동일하게 되도록 셋팅하는 것을 특징으로 하는 동작센서.

#### 청구항 5

제 3 항에 있어서, 상기 진동 프로세서는 상기 STATE\_PEAK 신호, 상기 STATE\_SM 신호 또는 상기 POSCOMP\_PK 신호 중 적어도 하나에 응답하여 상기 복수개의 자기장 필드 센싱 소자들 또는 상기 물체 중 적어도 하나의 진동을 나타내는 진동신호를 생성하는 것을 특징으로 하는 동작센서.

#### 청구항 6

제 3 항에 있어서, 상기 상태 프로세서는 상기 STATE\_SM 신호 또는 상기 STATE\_PEAK 신호 중 적어도 하나가 제1 및 제2 상태들에 응답하는 경우 제1 및 제2 차등 상태 변환(different state transition)을 갖는 2-상태 POSCOMP 신호를 생성하는 것을 특징으로 하는 동작 센서.

**청구항 7**

제 6 항에 있어서, 상기 제1 및 제2 상태들은 다른 상태들인 것을 특징으로 하는 동작센서.

**청구항 8**

제 6 항에 있어서, 상기 진동 프로세서는 상기 STATE\_PEAK 신호, 상기 STATE\_SM 신호, 상기 POSCOMP 신호 또는 상기 POSCOMP\_PK 신호 중 적어도 하나에 응답하여 상기 복수개의 자기장 필드 센싱 소자들 또는 상기 물체 중 적어도 하나의 진동을 나타내는 진동 신호를 생성하는 것을 특징으로 하는 동작센서.

**청구항 9**

물체와 연동된 자기장 필드를 나타내는 복수의 자기장 필드 신호들을 생성하는 단계;

복수개의 상태들의 각각은 신호 값들(signal value)의 각 영역을 나타내고, STATE\_SM 신호는 복수개의 제1 방향 상태 변환들 및 복수개의 제2 방향 상태 변환들을 포함하고, 상기 STATE\_SM 신호의 상기 제1 방향 상태 변환들 및 상기 제2 방향 상태 변환들은 상태 변환 채터(state transition chatter)할 수 있으며, 상기 자기장 필드 신호들의 각각에 연동되는 상기 복수개의 상태들을 나타내는 상기 STATE\_SM 신호를 생성하는 단계; 및

STATE\_PEAK 신호는 복수개의 제1 방향 상태 피크 변환들 및 복수개의 제2 방향 상태 피크 변환들을 포함하고, 상기 STATE\_PEAK 신호의 상기 제1 방향 상태 피크 변환들 및 상기 제2 방향 상태 피크 변환들은 감소된 상태 변환 채터를 가지며, 상기 STATE\_SM 신호에 연동된 상기 STATE\_PEAK 신호를 생성하는 단계를 포함하는 물체의 동작을 감지하는 방법.

**청구항 10**

제 9 항에 있어서, STATE\_SM 레지스터 내에서 상기 STATE\_SM 신호의 상태 값을 훌딩하는 단계; 및

STATE\_PEAK 레지스터 내에서 상기 STATE\_PEAK 신호의 값을 훌딩하는 단계를 더 포함하는 것을 특징으로 하는 물체의 동작을 감지하는 방법.

**청구항 11**

제 10 항에 있어서, 상기 STATE\_PEAK 신호에 의한 상태가 상기 STATE\_SM 신호에 의한 상태와 기 설정된 숫자의 상태들만큼 다른 경우에 상태 변환들이 발생하는 2-상태 POSCOMP\_PK 신호(two-state POSCOMP\_PK signal)를 생성하는 단계를 더 포함하는 것을 특징으로 하는 물체의 동작을 감지하는 방법.

**청구항 12**

제 11 항에 있어서,

상기 POSCOMP\_PK 신호가 제1 상태와 동일하고 상기 STATE\_SM 신호의 상태 값이 상기 STATE\_PEAK 신호의 상태 값보다 기 설정된 숫자의 상태들만큼 큰 경우에, 상기 STATE\_PEAK 레지스터 내에서 훌딩된 상태 값을 상기 STATE\_SM 레지스터 내에서 훌딩된 상태 값과 동일하게 설정하는 단계; 및

상기 POSCOMP\_PK 신호가 제2 차등 상태(second different state)와 동일하고 상기 STATE\_SM 신호의 상태 값이 상기 STATE\_PEAK 신호의 상태 값보다 상기 기 설정된 숫자의 상태들만큼 작은 경우에, 상기 STATE\_PEAK 레지스터 내에서 훌딩된 상태 값을 상기 STATE\_SM 레지스터 내에서 훌딩된 상태 값과 동일하게 설정하는 단계를 더 포함하는 것을 특징으로 하는 물체의 동작을 감지하는 방법.

**청구항 13**

제 11 항에 있어서, 상기 STATE\_PEAK 신호, 상기 STATE\_SM 신호 또는 상기 POSCOMP\_PK 신호 중 적어도 하나에 응답하여 복수개의 자기장 필드 센싱 소자들 또는 상기 물체 중 적어도 하나의 진동을 나타내는 진동신호를 생성하는 단계를 더 포함하는 것을 특징으로 하는 물체의 동작을 감지하는 방법.

**청구항 14**

제 11 항에 있어서, 상기 STATE\_SM 신호 또는 상기 STATE\_PEAK 신호 중 적어도 하나가 제1 및 제2 상태들의 각각에 대응되는 경우 제1 및 제2 차등 상태 변환(different state transition)이 발생하는 2-상태 POSCOMP 신호

를 생성하는 단계를 더 포함하는 것을 특징으로 하는 물체의 동작을 감지하는 방법.

### 청구항 15

제 14 항에 있어서, 상기 제1 및 제2 상태들은 다른 상태들인 것을 특징으로 하는 물체의 동작을 감지하는 방법.

### 청구항 16

제 14 항에 있어서, 상기 STATE\_PEAK 신호, 상기 STATE\_SM 신호, 상기 POSCOMP 신호 또는 상기 POSCOMP\_PK 신호 중 적어도 하나에 응답하여 복수개의 자기장 필드 센싱 소자들 또는 상기 물체 중 적어도 하나의 진동을 나타내는 진동신호(vibration signal)를 생성하는 단계를 더 포함하는 것을 특징으로 하는 물체의 동작을 감지하는 방법.

### 청구항 17

물체와 연동된 자기장 필드를 나타내는 복수의 자기장 필드 신호들을 인가받는 명령;

복수개의 상태들의 각각은 신호 값들(signal value)의 각 영역을 나타내고, STATE\_SM 신호는 복수개의 제1 방향 상태 변환들 및 복수개의 제2 방향 상태 변환들을 포함하고, 상기 STATE\_SM 신호의 상기 제1 방향 상태 변환들 및 상기 제2 방향 상태 변환들은 상태 변환 채터(state transition chatter)할 수 있으며, 상기 자기장 필드 신호들의 각각에 연동되는 상기 복수개의 상태들을 나타내는 상기 STATE\_SM 신호를 생성하는 명령; 및

STATE\_PEAK 신호는 복수개의 제1 방향 상태 피크 변환들 및 복수개의 제2 방향 상태 피크 변환들을 포함하고, 상기 STATE\_PEAK 신호의 상기 제1 방향 상태 피크 변환들 및 상기 제2 방향 상태 피크 변환들은 감소된 상태 변환 채터를 가지며, 상기 STATE\_SM 신호에 연동된 상기 STATE\_PEAK 신호를 생성하는 명령을 포함하고, 상기 물체의 동작을 감지하는 컴퓨터 관독가능한 코드를 포함하는 컴퓨터 관독가능한 저장매체(computer-readable storage medium).

### 청구항 18

제 17 항에 있어서, STATE\_SM 레지스터 내에서 상기 STATE\_SM 신호의 상태 값을 홀딩하는 명령; 및

STATE\_PEAK 레지스터 내에서 상기 STATE\_PEAK 신호의 값을 홀딩하는 명령을 더 포함하는 것을 특징으로 하는 컴퓨터 관독가능한 저장매체.

### 청구항 19

제 18 항에 있어서, 상기 STATE\_PEAK 신호에 의한 상태가 상기 STATE\_SM 신호에 의한 상태와 기설정된 숫자의 상태들만큼 다른 경우에 상태 변환들이 발생하는 2-상태 POSCOMP\_PK 신호(two-staet POSCOMP\_PK signal)를 생성하는 명령을 더 포함하는 것을 특징으로 하는 컴퓨터 관독가능한 저장매체.

### 청구항 20

제 19 항에 있어서,

상기 POSCOMP\_PK 신호가 제1 상태와 동일하고 상기 STATE\_SM 신호의 상태 값이 상기 STATE\_PEAK 신호의 상태 값보다 기설정된 숫자의 상태들만큼 큰 경우에, 상기 STATE\_PEAK 레지스터 내에서 홀딩된 상태 값을 상기 STATE\_SM 레지스터 내에서 홀딩된 상태 값과 동일하게 셋팅하는 명령; 및

상기 POSCOMP\_PK 신호가 제2 차등 상태(second different state)와 동일하고 상기 STATE\_SM 신호의 상태 값이 상기 STATE\_PEAK 신호의 상태 값보다 상기 기설정된 숫자의 상태들만큼 작은 경우에, 상기 STATE\_PEAK 레지스터 내에서 홀딩된 상태 값을 상기 STATE\_SM 레지스터 내에서 홀딩된 상태 값과 동일하게 셋팅하는 명령을 더 포함하는 컴퓨터 관독가능한 저장매체.

### 청구항 21

제 19 항에 있어서, 상기 STATE\_PEAK 신호, 상기 STATE\_SM 신호 또는 상기 POSCOMP\_PK 신호 중 적어도 하나에 응답하여 복수개의 자기장 필드 센싱 소자들 또는 상기 물체 중 적어도 하나의 진동을 나타내는 진동신호를 생성하는 명령을 더 포함하는 것을 특징으로 하는 컴퓨터 관독가능한 저장매체.

## 청구항 22

제 19 항에 있어서, 상기 STATE\_SM 신호 또는 상기 STATE\_PEAK 신호 중 적어도 하나가 제1 및 제2 상태들의 각각에 대응되는 경우 제1 및 제2 차등 상태 변환(different state transition)이 발생하는 2-상태 POSCOMP 신호를 생성하는 명령을 더 포함하는 것을 특징으로 하는 컴퓨터 관독가능한 저장매체.

## 청구항 23

제 22 항에 있어서, 상기 제1 및 제2 상태들은 다른 상태들인 것을 특징으로 하는 컴퓨터 관독가능한 저장매체.

## 청구항 24

제 22 항에 있어서, 상기 STATE\_PEAK 신호, 상기 STATE\_SM 신호, 상기 POSCOMP 신호 또는 상기 POSCOMP\_PK 신호 중 적어도 하나에 응답하여 복수개의 자기장 필드 센싱 소자들 또는 상기 물체 중 적어도 하나의 진동을 나타내는 진동신호(vibration signal)를 생성하는 명령을 더 포함하는 것을 특징으로 하는 컴퓨터 관독가능한 저장매체.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 동작센서에 관한 것으로, 보다 상세하게는 상태 프로세서(state processor)를 포함하는 동작 센서에 관한 것이다.

### 배경 기술

[0002]

강자성 물체들(ferromagnetic articles) 및/또는 자성 물체들(magnetic articles)을 검출하기 위한 자기장 센서들(예를 들어, 회전 감지기들)이 알려져 있다. 상기 강자성 물체 또는 상기 자성 물체와 관련되는 자기장은 홀 요소(Hall element) 또는 자기 저항 요소와 같은 검출된 자기장에 비례하는 신호(즉, 자기장 신호)를 제공하는 자기장 센싱 요소(magnetic field sensing element)에 의해 검출된다. 일부 배열들에 있어서, 상기 자기장 신호는 전기적 신호이다.

[0003]

상기 자기장 센서는, 일부 배열들에 있어서, 상기 자기장 신호가 피크들(양의 및/또는 음의 피크들)에 인접하거나 일부 다른 레벨에 인접하는, 예를 들면 상기 자기장의 0점을 가로지르는 바와 같이 스레시홀드들(thresholds)을 가로지르는 매 시간 상태를 변화시키는 출력 신호를 발생시키도록 상기 자기장 신호를 처리한다. 따라서 상기 출력 신호는 상기 강자성의(예를 들어, 철을 함유하는) 또는 자성의 물체, 예를 들면 기어나 링 자석(둘 중의 하나는 철을 함유할 수 있거나 그렇지 않은)의 회전 속도를 나타내는 에지 레이트(edge rate) 혹은 주기를 가진다.

[0004]

자기장 센서를 위한 하나의 응용은 회전하는 강자성 기어나 경자성(hard magnetic) 기어 혹은 연강자성(soft ferromagnetic) 기어의 각 톱니의 접근 및 후퇴를 감지하는 것이다. 일부 특정 배열들에 있어서, 교변되는 극성을 갖는 자기 영역들(영구적이거나 경자성 물질)을 포함하는 링 자석은 상기 강자성 기어에 연결되거나 그 자체로 사용되며, 상기 자기장 센서가 상기 링 자석의 상기 자기 영역들의 접근 및 후퇴에 빠르게 반응하게 된다. 다른 배열들에 있어서, 정지된 자석에 인접하게 배치되고 상기 자기장 센서는 상기 기어의 회전에 따른 자기장의 요동에도 빠르게 반응하게 된다. 이러한 배열들은 또한 근접 센서들 또는 모션 센서들로 언급된다. 감지된 회전의 경우, 상기 배열들은 회전 센서들로 언급될 수 있다. 여기서 사용되는 바에 있어서, "검출기(detector)" 및 "센서(sensor)"라는 용어들은 실질적으로 동일한 것을 의미하도록 사용된다.

[0005]

때때로 피크-투-피크(peak-to-peak) 퍼센티지 검출기(또는 스레시홀드 검출기)로 언급되는 자기장 센서의 하나의 종류에 있어서, 하나 또는 그 이상의 스레시홀드 레벨들은 피크-투-피크 자기장 신호의 해당 퍼센트들과 동일하다. 이와 같은 피크-투-피크 퍼센티지 검출기의 하나는 미국 특허 제5,917,320호(발명의 명칭: "주기적으로 스레시홀드 검출을 조절하는 동안 통과하는 자석 물체들의 검출(Detection of Passing Magnetic Articles While Periodically Adapting Detection Threshold)")에 기재되어 있으며, 이는 본 출원의 양수인과 양수인이 동일하다.

[0006]

때때로 슬로프 활성화된(slope-activated) 검출기(또는 피크-참조된 검출기 혹은 생략하여 피크 검출기)로 언급되는 자기장 센서의 또 다른 종류는 본 출원의 양수인과 양수인이 동일한 미국 특허 제6,091,239호(발명의

명칭: "피크 참조된 슬레이드 검출기를 구비한 통과하는 자석 물체들의 검출(Detection Of Passing Magnetic Articles With a Peak Referenced Threshold Detection)"에 기재되어 있다. 상기 피크-참조된 자기장 센서에 있어서, 슬레이드 신호는 상기 자기장 신호의 양의 및 음의 피크들(즉, 피크들 및 골들)과 소정의 양만큼 다르다. 따라서, 이러한 형태의 자기장 센서에 있어서, 출력 신호는 상기 자기장 신호가 상기 조장의 양으로 상기 자기장 신호의 피크 또는 골로부터 멀어질 때에 상태를 변화시킨다.

[0007] 전술한 슬레이드 검출기와 전술한 피크 검출기가 모두 자기장 신호의 양의 및 음의 피크들을 확인할 수 있는 회로망을 가지기 때문이라는 점을 이해할 수 있을 것이다. 그러나, 상기 슬레이드 검출기와 상기 피크 검출기는 각기 다른 방식들로 검출된 피크들을 사용한다.

[0008] 자기장 신호의 양의 및 음의 피크들을 정확하게 검출하기 위하여, 상기 자기장 센서는 상기 자기장 신호의 적어도 일부를 추적할 수 있다. 이를 위하여, 통상적으로 하나 또는 그 이상의 디지털-아날로그 컨버터(digital-to-analogue converter; DAC)들이 상기 자기장 신호를 추적하는 추적 신호를 생성하도록 사용될 수 있다. 예를 들면, 전술한 미국 특허 제5,917,320호 및 미국 특허 제6,091,239호에 있어서, 두 개의 디지털-아날로그 컨버터(DAC)들이 사용되고, 하나(PDAC)는 상기 자기장 신호의 양의 피크들을 검출하며, 다른 하나(NDAC)는 상기 자기장 신호의 음의 피크들을 검출한다.

[0009] 상기 강자성 물체와 및 결과적인 자기장 신호에 관련된 자기장은, 예를 들면 상기 회전하는 강자성 기어인 강자성 물체와, 예를 들면 상기 홀 요소인 상기 근접 검출기에 사용되는 자기장 센싱 요소(들) 사이의 거리에 비례한다. 이러한 거리는 여기서 "에어 갭(air gap)"으로 언급된다. 상기 에어 갭이 증가함에 따라, 상기 자기장 센싱 요소들은 상기 회전하는 강자성 기어로부터의 보다 작은 작은 자기장을 겪는 경향이 있으며, 이에 따라 상기 회전하는 강자성 기어의 통과하는 톱니에 의해 생성되는 상기 자기장에서 보다 작게 변화된다.

[0010] 근접 검출기는 상기 강자성 물체(예를 들면, 상기 회전하는 강자성 기어)가 회전할 뿐만 아니라 진동하기도 하는 시스템들 내에 사용되어 왔다. 정상 작동에서 회전축에 대해 회전할 수 있는 상기 강자성 기어를 위하여, 상기 진동은 적어도 두 진동 성분들을 가질 수 있다. 제1 진동 성분은 그 회전축에 대해 전후방으로 진동하는 상기 강자성 기어를 위한 "회전 진동(rotational vibration)"에 대응된다. 제2 진동 성분은 전술한 에어 갭 치수의 진동을 위한 "병진 진동(translational vibration)"에 대응된다. 상기 회전 진동 및 상기 병진 진동은 상기 강자성 기어가 정상 작동으로 회전하지 않는 때에도 발생될 수 있다. 분리되거나 결합되는 상기 제1 및 제2 진동 성분들은 모두 상기 강자성 기어가 정상 작동으로 회전하지 않는 때에도 상기 강자성 기어의 회전을 나타내는 상기 근접 검출기로부터의 출력 신호를 발생시킬 수 있다.

[0011] 회전 진동과 병진 진동을 검출하고 반응하도록 적용된 근접 검출기들은, 예를 들면 2008년 4월 29일 자로 등록된 미국 특허 제7,365,530호, 2009년 9월 22일 자로 등록된 미국 특허 제7,592,801호, 2009년 11월 24일 자로 등록된 미국 특허 제7,622,914호, 2007년 8월 7일 자로 등록된 미국 특허 제7,253,614호, 그리고 2008년 12월 18일 자로 출원된 미국 특허 출원 제12/338,048호에 개시되어 있으며, 이들은 각기 본 출원의 양수인과 양수인이 동일하다.

[0012] 근접 검출기들은 자동차 휠들의 회적 속도를 결정하도록 자동차의 브레이크 잠김 방지 시스템(antilock brake system: ABS)에 적용되어 왔다. 근접 검출기은 또한 소정의 이동 지점들에서 변속기를 이동시키고 다른 자동차 시스템 기능들을 수행하기 위하여 변속기 기어들의 회전 속도를 결정하도록 자동차 변속기들에 적용되어 왔다.

[0013] 진동 동안 상기 자기장 센싱 요소에 의해 생성되는 자기장 신호들은 상기 진동의 속성에 따른 특징들을 가질 수 있다. 예를 들면, 자동차 변속기에 사용될 때, 자동차 엔진의 시동 동안, 상기 근접 검출기는 주로 제1 과형을 갖는 자기장 신호들을 발생시키기 용이한 회전 진동을 겪는 경향이 있다. 대조적으로, 엔진 공회전 동안, 상기 근접 검출기는 주로 제2 과형을 갖는 자기장 신호들을 발생시키기 쉬운 병진 진동을 경험하려는 경향이 있다. 진동 동안 발생되는 상기 자기장 신호들은 또한 시간들 마다 또는 응용들마다, 예를 들면 자동차 모델들 마다 변화될 수 있다.

[0014] 많은 기계적인 어셈블리들의 사이즈 및 위치 제조 공차(manufacturing tolerance)들을 갖는 점을 이해할 수 있을 것이다. 예를 들면, 상기 근접 검출기가 조립에 사용될 때, 상기 에어 갭은, 상기 강자성 물체가 정상 작동 및 상기 자기장 신호에서 대응되는 진동으로 회전할 때에 상기 근접 검출기에 사용되는 상기 자기장 센싱 요소들에 의해 감지되는 자기장 내의 진동을 야기하는 제조 공차를 가질 수 있다. 상기 기계적인 어셈블리 내에 마모(wear)가 발생됨에 따라 상기 에어 갭이 시간에 따라 변화될 수 있는 점도 이해할 수 있을 것이다.

[0015] 자기장 센서들의 일부 유형들은, 예를 들면 상기 센서의 시동이나 전원의 인가에 근접한 시간에서 혹은 그렇지

않으면 원하는 시간마다 하나 또는 그 이상의 초기화(initialization) 또는 보정(calibration)의 형태들을 수행한다. 보정의 하나의 형태 동안, 전술한 스레시홀드 레벨이 결정된다. 보정의 일부 형태들에 있어서, 보정이 일어나는 동안의 시간 간격이 상기 자기장 신호의 사이클들의 미리 정해진 횟수에 따라 결정된다. 따라서, 빠른 자기장 신호들을 위해서(예를 들면, 빠른 회전하는 기어들을 위해서), 보정을 위해 이용될 수 있는 시간은 작다. 동작 또는 회전이 빠르고 보정을 위해 사용될 수 있는 시간은 적은 이러한 응용들에 있어서, 상기 회전 검출기가 적절하게 보정하지 않을 수 있다. 즉, 상기 스레시홀드가 적절하게 결정되지 않을 수 있다.

[0016] 진동에 반응하여 발생되는 자기장 신호의 많은 특징들은 정상 작동에서의 상기 강자성 물체의 회전 동안에 발생되는 자기장 신호의 특징들과 동일하거나 유사할 수 있다. 예를 들면, 진동 동안 발생되는 자기장 신호의 주파수는 정상 작동에서의 회전 동안 발생되는 자기장 신호의 주파수와 동일하거나 유사할 수 있다. 다른 예로서, 진동에 반응하여 발생되는 자기장 신호의 진폭은 정상 작동에서의 회전 동안 발생되는 자기장 신호의 진폭과 동일하거나 유사할 수 있다. 이에 따라, 종래의 근접 검출기는 정상 작동에서의 진동에 반응하고 회전에 모두 반응하는 출력 신호를 발생시킨다. 따라서 상기 근접 검출기로부터의 출력 신호는 정상 작동에서의 진동에 반응하여 발생되는지 아니면 회전에 반응하여 발생되는지와 동일하게 나타난다.

[0017] 오직 진동만 존재할 때에 정상 작동에서의 회전과 관련되는 근접 검출기로부터의 출력 신호를 해석하는 시스템을 위하여, 예를 들면 상기 근접 검출기가 사용되는 자동차 시스템인 시스템의 동작에는 불리할 수 있다. 예를 들면, 훨씬 회전을 검출하도록 근접 검출기를 이용하는 브레이크 잠김 방지 시스템(ABS)은 상기 출력 신호가 오직 진동으로 인하여 발생될 수 있을 때에 훨씬의 회전을 나타내도록 상기 근접 검출기로부터의 출력 신호를 해석할 수 있다. 따라서 상기 브레이크 잠김 방지 시스템이 의도한 바에 따라 사용되지 않을 수 있다.

[0018] 정상 작동에서의 회전에 반응하는 것보다 진동에 반응하여 근접 탐지 보정을 수행함도 바람직하지 않을 수 있다. 보정에 대해서는 다음에 보다 상세하게 기술한다. 종래의 근접 검출기가 정상 작동에서의 회전에 반응하여 발생되는 자기장 신호와 정상 작동에서의 진동에 반응하여 발생되는 자기장 신호를 구분할 수 없기 때문에, 상기 근접 검출기는 진동을 겪을 때에 원하지 않는 시간에서 보정들을 수행할 수 있으며, 이에 따라 부정확한 보정이 야기된다.

[0019] 모션 센서가 출력 신호의 에지들에 정확하게 위치하지 않은 노이즈(전기적이거나 진동적인)로 인하여, 그 에지의 배치는 감지되는 물체의 회전의 정도의 무명수(absolute number)를 나타낸다. 또한 이러한 노이즈로 인하여, 상기 모션 센서는, 특히 에지들이 정확하지 않게 위치하여 진동이 가장 높을 때에 전원의 인가 시간에 부근에서 정확하지 않은 출력 신호를 발생시킬 수 있다.

[0020] 이에 따라, 그로부터의 출력 신호에 향상된 에지 배치(또는 회전 각도의 다른 표현)를 가지는 모션 센서의 제공이 요구된다.

## 발명의 내용

### 해결하려는 과제

[0021] 본 발명의 동작 센서, 그 방법 및 컴퓨터 판독용 저장매체의 목적은, 에지 위치(edge placement, 또는 회전각을 나타내는 다른 대푯값)가 향상된 동작 센서를 제공하는데 있다. 동작센서는 정확성을 의해 출력신호에 방향정보(direction information)를 제공하게 된다. 동작센서는 빠르고 정확하게 보정된다.

### 과제의 해결 수단

[0022] 본 발명의 일견지에 따른 동작 센서는 물체와 연동된 자기장필드를 나타내는 복수개의 자기장 필드 신호를 생성하는 복수개의 자기장 필드 센싱 소자들을 포함한다. 상기 동작 센서는 또한 복수개의 상태 프로세서들을 포함하여, 상기 상태 프로세서들의 각각은 상기 자기장 필드 신호들의 각각에 응답하는 신호를 인가받아 상기 각 상태 프로세서는 상기 복수개의 자기장 필드 신호들의 각각과 연동된 복수개의 상태들을 나타내는 각각의 STATE\_SM 신호를 생성하고, 상기 각 상태는 신호 값들(signal value)의 각 영역을 나타내며, 상기 STATE\_SM 신호는 복수개의 제1 방향 상태 변환들(first direction state transition) 및 복수개의 제2 방향 상태 변환들을 포함하고, 상기 제1 방향 상태 변환들 및 상기 제2 방향 상태 변환들은 변환 채터(transition chatter)의 상태에 대응된다. 상기 상태 프로세서들의 각각은 상기 각 STATE\_SM 신호를 인가받아 각 STATE\_PEAK 신호를 생성하는 각 상태 피크 로직 모듈(state peak logic module)을 포함한다. 상기 STATE\_PEAK 신호는 복수개의 제1 방향 상태 피크 변환들 및 복수개의 제2 방향 상태 피크 변환들을 포함하며, 상기 제1 방향 상태 피크 변환들 및 상

기 제2 방향 상태 피크 변환들은 감소된 상태 변환 채터(state transition chatter)를 포함한다.

[0023] 본 발명의 다른 견지에 따른 물체의 동작을 감지하는 방법은 물체와 연동된 자기장 필드를 나타내는 복수의 자기장 필드 신호들을 생성하는 단계 및 상기 자기장 필드 신호들의 각각에 연동되는 상기 복수개의 상태들을 나타내는 STATE\_SM 신호를 생성하는 단계를 포함한다. 상기 STATE\_SM 신호를 생성하는 단계는 복수개의 상태들의 각각은 신호 값들(signal value)의 각 영역을 나타내고, 상기 STATE\_SM 신호는 복수개의 제1 방향 상태 변환들 및 복수개의 제2 방향 상태 변환들을 포함하고, 상기 제1 방향 상태 변환들 및 상기 제2 방향 상태 변환들은 변환 채터(transition chatter)를 상태변환(state)할 수 있다. 상기 방법은 또한 상기 STATE\_SM 신호에 연동된 상기 STATE\_PEAK 신호를 생성하는 단계를 더 포함한다. 상기 STATE\_SM 신호에 연동된 상기 STATE\_PEAK 신호를 생성하는 단계는 STATE\_PEAK 신호는 복수개의 제1 방향 상태 피크 변환들 및 복수개의 제2 방향 상태 피크 변환들을 포함하고, 상기 제1 방향 상태 피크 변환들 및 상기 제2 방향 상태 피크 변환들은 감소된 상태 변환 채터를 가진다.

[0024] 본 발명의 다른 견지에 따른 물체의 동작을 감지하는 컴퓨터 판독가능한 코드를 포함하는 컴퓨터 판독가능한 저장매체는 물체와 연동된 자기장 필드를 나타내는 복수의 자기장 필드 신호들을 인가받는 명령 및 상기 자기장 필드 신호들의 각각에 연동되는 상기 복수개의 상태들을 나타내는 STATE\_SM 신호를 생성하는 명령을 포함한다. 상기 복수개의 상태들을 나타내는 STATE\_SM 신호를 생성하는 명령은 복수개의 상태들의 각각은 신호 값들(signal value)의 각 영역을 나타내고, 상기 STATE\_SM 신호는 복수개의 제1 방향 상태 변환들 및 복수개의 제2 방향 상태 변환들을 포함하고, 상기 제1 방향 상태 변환들 및 상기 제2 방향 상태 변환들은 변환 채터(transition chatter)를 상태변환(state)할 수 있다. 상기 컴퓨터 판독가능한 저장매체는 또한 상기 STATE\_SM 신호에 연동된 상기 STATE\_PEAK 신호를 생성하는 명령을 더 포함한다. 상기 STATE\_SM 신호에 연동된 상기 STATE\_PEAK 신호를 생성하는 명령은 STATE\_PEAK 신호는 복수개의 제1 방향 상태 피크 변환들 및 복수개의 제2 방향 상태 피크 변환들을 포함하고, 상기 제1 방향 상태 피크 변환들 및 상기 제2 방향 상태 피크 변환들은 감소된 상태 변환 채터를 가진다.

### 발명의 효과

[0025] 본 발명에 따르면, 동작센서는 상태 채터(state chatter)의 양이 감소된다. 따라서 상태들(state)이 다른 가능한 경우들보다 가깝게 배치될 수 있다. 동작센서는 이동하는 물체(예를 들어, 회전하는 물체의 회전각)의 위치에 대한 정보를 보다 정확하게 제공할 수 있다.

### 도면의 간단한 설명

[0026] 도 1은 두 상태 프로세서들, 진동 프로세서, 자동 오프셋 조절(AOA) 및 자동 이득 제어(AGC) 프로세서, 두 오프셋 및 이득 조절 회로들 그리고 출력 프로토콜 프로세서들을 구비하는 모션 센서를 나타내는 블록도이고,

도 2는 상태 로직 모듈 및 상태 피크 로직 모듈들을 포함하는 도 1의 두 상태 프로세서들 중에서 하나를 보다 상세하게 나타내는 블록도이며,

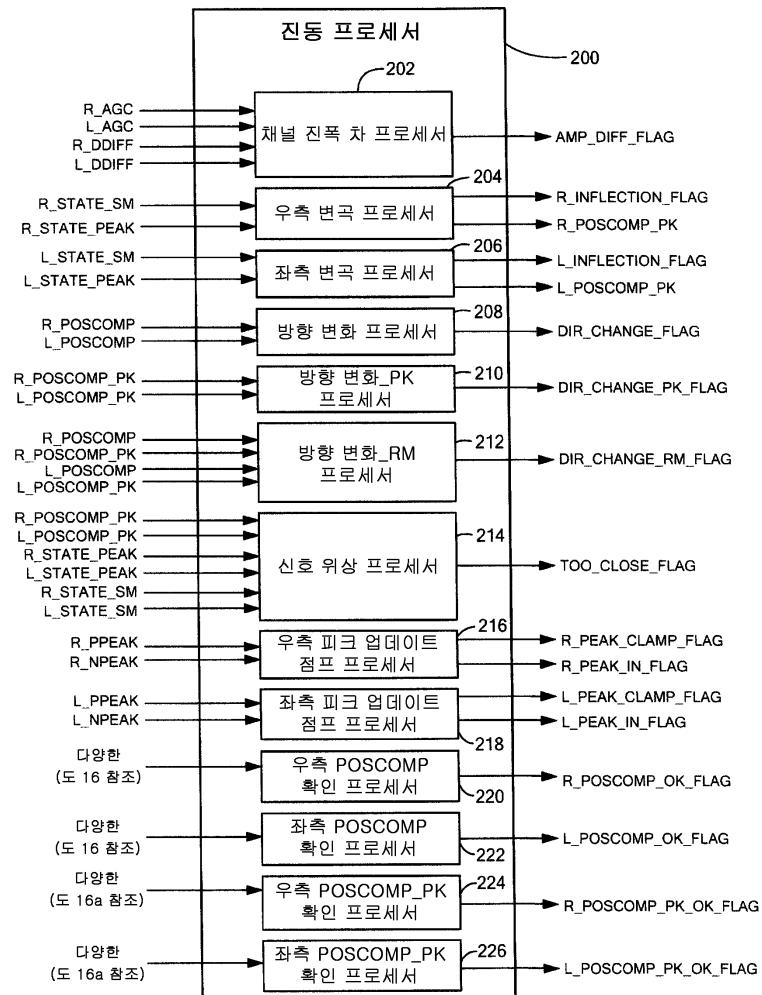

도 3은 채널 진폭 차 프로세서, 우측 및 좌측 채널 변곡 프로세서들, 방향 변화 프로세서, 방향 변화\_PK 프로세서, 방향 변화\_RM 프로세서, 신호 위상 프로세서, 우측 및 좌측 채널 업데이트 점프 프로세서들, 우측 및 좌측 채널 POSCOMP 확인 프로세서들 그리고 우측 및 좌측 채널 POSCOMP\_PK 확인 프로세서들을 포함하는 도 1의 진동 프로세서의 부분들을 나타내는 블록도이고,

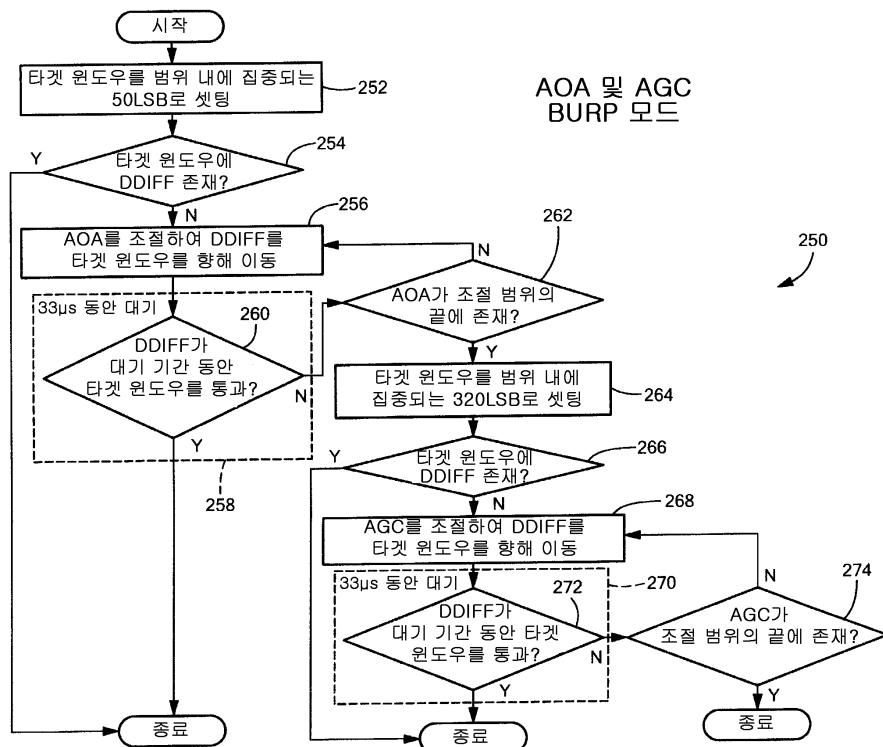

도 4는 동작의 BURP 모드에서 도 1의 AOA/AGC 프로세서의 동작의 프로세스를 나타내는 흐름도이며,

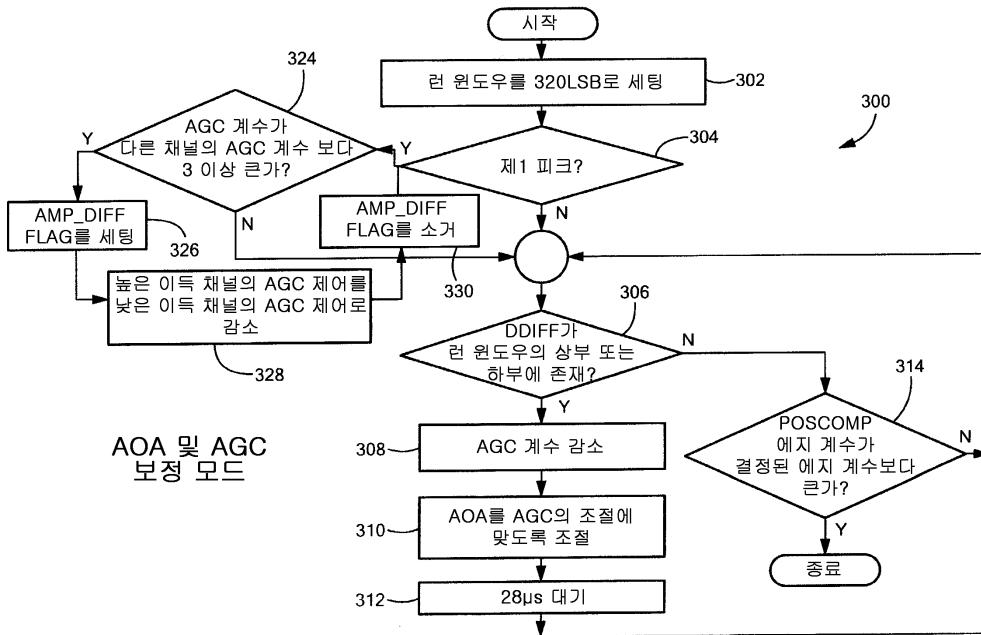

도 5는 도 3의 채널 진폭 차 프로세서의 동작을 포함하는 동작의 보정 모드에서 도 1의 AOA/AGC 프로세서의 동작의 프로세스를 나타내는 흐름도이고,

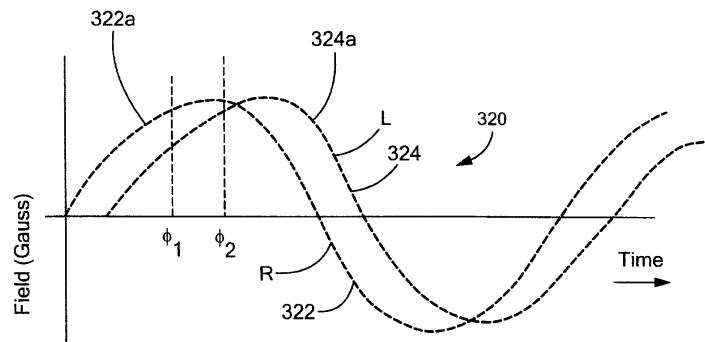

도 5a 및 도 5b는 진동과 관련되고 도 3의 채널 진폭 차 프로세서 및 도 5의 프로세스와 관련된 도 1의 모션 센서의 신호 파형들을 나타내는 그래프들이며,

도 6은 동작의 실행 모드에서 도 1의 AOA/AGC 프로세서의 동작의 프로세스를 나타내는 흐름도이고,

도 7은 DIFF 신호(또한 디지털 DDIFF 신호 또는 디지털 IDDIFF 신호를 나타내는) 및 도 1의 모션 센서의 관련된 상태들을 나타내는 그래프이며,

도 7a는 도 1의 모션 센서에 의해 도 7의 DIFF 신호로부터 파생되는 POSCOMP 및 POSCOMP\_PK 신호들을 나타내는

그래프이고,

도 8은 도 1의 모션 센서와 관련된, 특히 도 2의 상태 로직 모듈과 관련된 상태들의 시퀀스를 나타내는 상태 도표이며,

도 9는 DIFF 신호 및 변곡(방향의 변화)이 발생할 때에 도 1의 모션 센서의 관련된 상태들을 나타내는 그래프이고,

도 9a는 POSCOMP 및 POSCOMP\_PK 신호들 및 도 1의 모션 센서에 의해 도 10의 DIFF 신호로부터 유도되는 상태들을 나타내는 그래프이며,

도 10은 도 3의 변곡 프로세서에 사용될 수 있는 변곡 프로세싱을 나타내는 흐름도이고,

도 11은 도 3의 방향 변화 프로세서에 사용될 수 있는 방향 변화 프로세싱을 나타내는 흐름도이며,

도 12는 도 3의 방향 변화\_PK 프로세서에 사용될 수 있는 방향 변화\_PK 프로세싱을 나타내는 흐름도이고,

도 13은 도 3의 방향 변화\_RM 프로세서에 사용될 수 있는 방향 변화\_RM 프로세싱을 나타내는 흐름도이며,

도 14는 도 3의 신호 위상 프로세서에 사용될 수 있는 신호 위상 프로세싱을 나타내는 흐름도이고,

도 15는 도 3의 피크 업데이트 점프 프로세서들에서 사용될 수 있는 신호 피크 점프 프로세싱을 나타내는 흐름도이며,

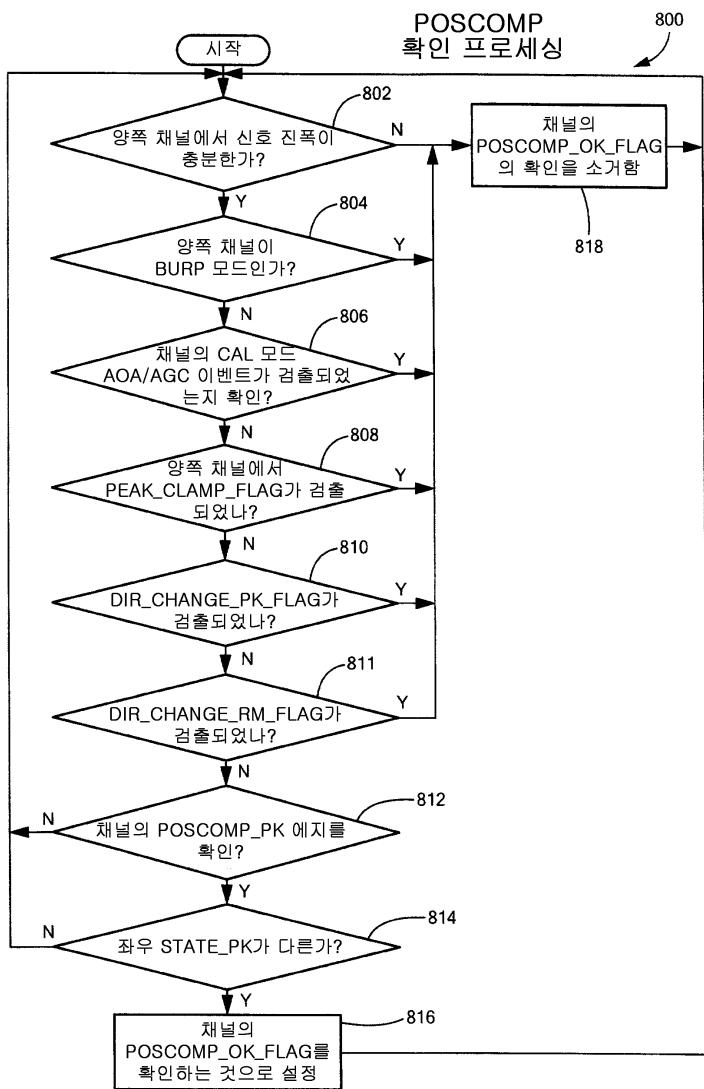

도 16은 도 3의 POSCOMP 확인 프로세서들에 사용될 수 있는 POSCOMP 확인 프로세싱을 나타내는 흐름도이고,

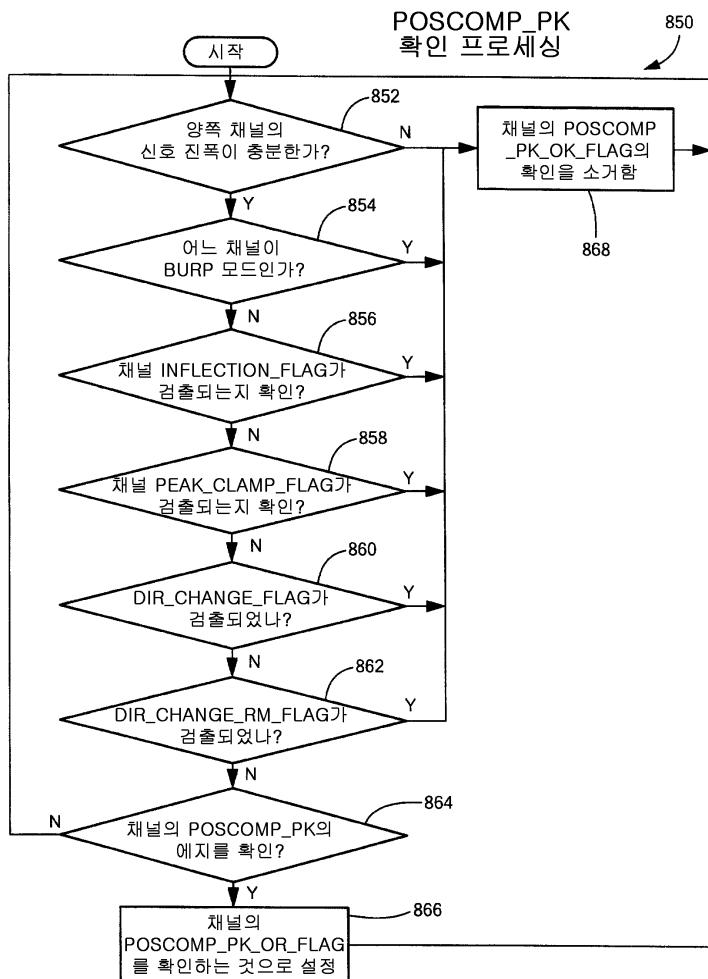

도 16a는 도 3의 POSCOMP\_PK 확인 프로세서들에 사용될 수 있는 POSCOMP\_PK 확인 프로세싱을 나타내는 흐름도이며,

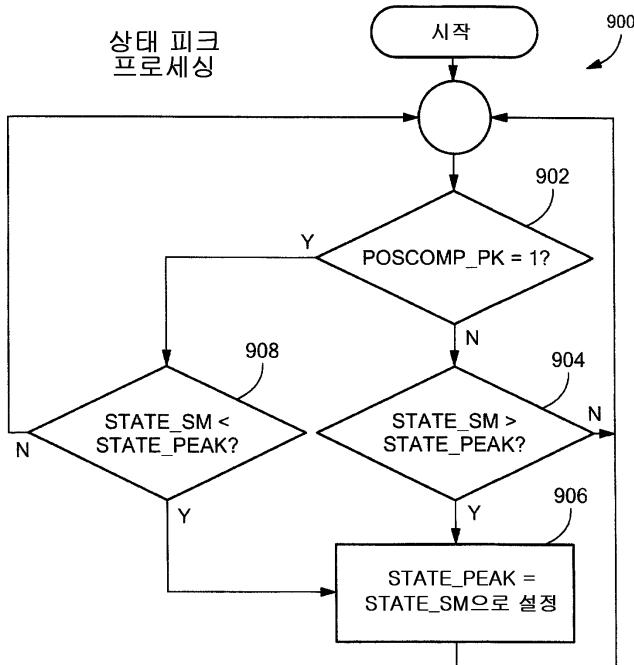

도 17은 도 2의 상태 피크 로직 모듈에 사용될 수 있는 상태 피크 프로세싱을 나타내는 흐름도이고,

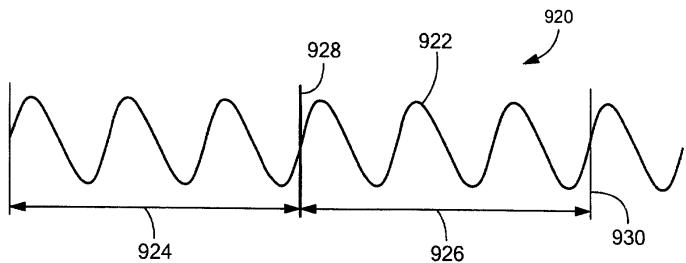

도 18은 DIFF 신호 및 방향 확인 윈도우를 나타내는 그래프이며,

도 18a는 DIFF 신호 및 변경된 방향 확인 윈도우를 나타내는 그래프이고,

도 19 내지 도 19b는 함께 도 18a의 변경된 방향 확인 윈도우를 발생시키기 위한 프로세스를 나타내는 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0027]

본 발명을 설명하기 전에, 일부 도입부 개념들과 용어들을 설명한다. 여기서 사용되는 바와 같이, "자기장 센싱 요소(magnetic field sensing element)"라는 용어는 자기장을 감지할 수 있는 다양한 형태들의 전자 요소들을 기술하는 데 사용된다. 상기 자기장 센싱 요소들은, 이에 제한되는 것은 아니지만, 홀 효과(Hall effect) 요소들, 자기 저항(magnetoresistance) 요소들 또는 자기 트랜지스터(magnetotransistor)들에 해당될 수 있다. 알려진 바와 같이, 예를 들면 평면형 홀 요소들, 수직형 홀 요소들, 원형 홀 요소들과 같이 홀 효과 요소들의 다른 유형들이 존재한다. 또한 알려진 바와 같이, 자기 저항 요소들의 다른 형태들, 예를 들면 이방성 자기 저항(anisotropic magnetoresistance: AMR) 요소들, 거대 자기 저항(giant magnetoresistance: GMR) 요소들, 터널링 자기 저항(tunneling magnetoresistance: TMR) 요소들, 인듐 안티몬(InSb) 요소들, 그리고 자기 터널 접합(magnetic tunnel junction: MTJ) 요소들이 존재한다.

[0028]

알려진 바와 같이, 전술한 자기장 센싱 요소들의 일부들은 자기장 센싱 요소를 지지하는 기판에 대해 평행한 최대 감도(maximum sensitivity)의 축을 가지려는 경향이 있으며, 전술한 자기장 센싱 요소들의 다른 것들은 상기 자기장 센싱 요소를 지지하는 기판에 대해 수직한 최대 감도의 축을 가지려는 경향이 있다. 특히, 모두는 아니지만, 자기 저항 요소들의 많은 형태들은 기판에 대해 평행한 최대 감도의 축을 가지려는 경향이 있으며, 모두는 아니지만, 홀 요소들의 많은 유형들은 기판에 대해 수직한 감도의 축을 가지려는 경향이 있다.

[0029]

여기서 사용되는 바와 같이, "자기장 센서(magnetic field sensor)"라는 용어는 자기장 센싱 요소를 포함하는 회로를 기술하는 데 사용된다. 자기장 센서들은, 이에 한정되는 것은 아니지만, 전류가 흐르는 도체에 의해 운반되는 전류에 의해 발생되는 자기장을 감지하는 전류 센서, 강자성 혹은 자성 물체의 근접을 감지하는 자기 스위치나 근접 검출기, 예를 들면 강자성 기어의 일 자석이나 톱니의 자기 도메인들이 통과하는 강자성 물체들을 감지하는 회전 검출기(회전 센서 또는 모션 센서), 그리고 자기장의 자기장 밀도를 감지하는 자기장 센서를 포

함하는 다양한 형태들의 응용들에 사용된다. 회전 검출기들은 여기서는 예들로서 사용된다. 그러나 여기서 설명하는 회로들과 기술들은 또한 물체의 동작을 감지할 수 있는 임의의 자기장 센서, 즉 임의의 모션 센서에 적용된다.

- [0030] 여기서 사용되는 바와 같이, "회전 진동(rotational vibration)"이라는 용어는 정상 작동에서의 회전축에 대해 단일 방향의 방식으로 물체가 회전하도록 적용되는 회전축에 대해 물체의 후방 및 전방으로의 회전을 언급한다. 여기서 사용되는 바와 같이, "병진 진동(translation vibration)"이라는 용어는 물체 및/또는 대체로 회전축에 대해 수직한 방향으로 상기 물체에 의해 발생되는 자기장들을 검출하는 자기장 센서들의 병진을 언급한다. 회전 진동과 병진 진동이 모두 자기장 센서들에 의해 생성되는 신호들을 발생시킬 수 있는 점을 인지할 수 있을 것이다.

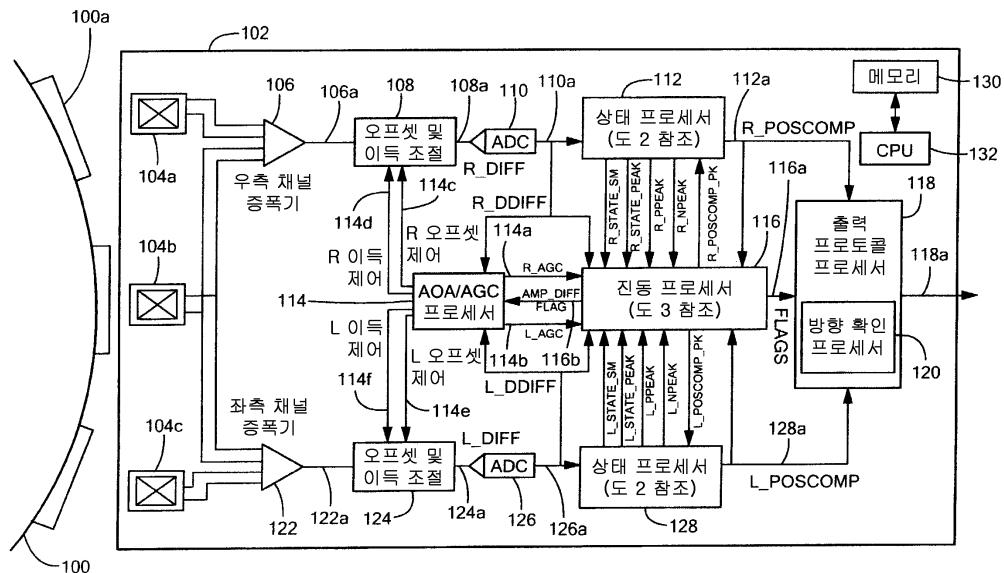

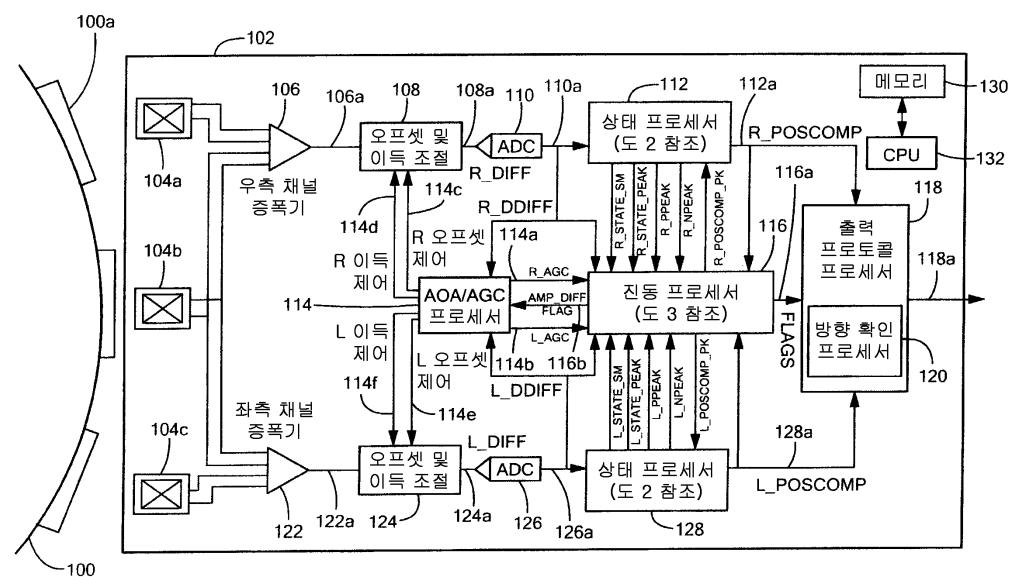

- [0031] 도 1을 참조하면, 예시적인 모션 센서(102)는 회전하는 기어(100)의 통과하는 톱니들, 특히 톱니(100a)가 하나의 예시인 회전하는 기어(100)의 톱니들에 반응하여 해당 자기장 센싱 요소 신호를 발생시키도록 각기 구성된 세 개의 자기장 센싱 요소들(104a 내지 104c)을 포함한다. 상기 모션 센서(102)는 또한 우측 채널 증폭기(right channel amplifier)(106) 및 좌측 채널 증폭기(left channel amplifier)(122)를 포함한다. "우측(right)" 및 "좌측(left)"이라는 용어들은 우측 채널과 좌측 채널에 기여하는 상기 자기장 센싱 요소들의 서로 다른 물리적인 위치들을 나타내는 임의의 식별자들이다.

- [0032] 상기 모션 센서(102)는 원치 않는 직류(DC) 오프셋(offset)들을 제거하는 오프셋 및 이득 조절 회로들(offset and gain adjustment circuits)(108, 124)을 포함할 수 있으며, 상기 증폭기들(106, 122)에 의해 각기 제공되는 신호들(106a, 122a)에 대해 조절 가능한 이득들을 제공할 수 있다. 상기 오프셋 및 이득 조절 회로들(108, 124)은 각기 R\_DIFF 신호(108a) 및 L\_DIFF 신호(124a)를 발생시킨다. 일부 선택적인 실시예들에 있어서, 상기 모션 센서(102)는 오프셋 조절 회로만을 또는 이득 조절 회로만을 포함한다.

- [0033] 상기 오프셋 및 이득 조절 회로들(108, 124)은 여기서 상세하게 기술되지는 않는다. 그러나 상기 오프셋 및 이득 조절 회로들(108, 124)은 본 출원의 양수인과 양수인이 동일한 2006년 11월 21일자로 등록된 미국 특허 제 7,138,793호에 기재된 형태가 될 수 있다.

- [0034] 상기 R\_DIFF 신호(108a)와 상기 L\_DIFF 신호(124a)는 여기서 상기 자기장 센싱 요소들(104a 내지 104c)에 의해 감지되는 자기장들에 반응하는 자기장 신호들로 언급된다. 상기 R\_DIFF 신호(108a)는 상기 자기장 센싱 요소들(104a, 104b)에 의해 겪는 자기장을 나타내고, 상기 L\_DIFF 신호(124a)는 상기 자기장 센싱 요소들(104b, 104c)에 의해 경험되는 자기장을 나타낸다.

- [0035] 상기 모션 센서(102)는 상기 R\_DIFF 신호(108a)를 수신하도록 연결되고 우측 채널 디지털 DIFF 신호인 R\_DDIFF(110a)를 발생시키도록 구성되는 아날로그-디지털 컨버터(ADC)(110)를 포함할 수 있다. 다른 아날로그-디지털 컨버터(ADC)(126)가 상기 L\_DIFF 신호(124a)를 수신하도록 연결되고 좌측 채널 디지털 DIFF 신호인 L\_DDIFF(126a)를 발생시키도록 구성된다. 상기 R\_DDIFF 신호(110a) 및 상기 L\_DDIFF 신호(126a)도 여기서 자기장 신호들로 언급될 수 있다.

- [0036] 상기 모션 센서(102)는 상기 R\_DDIFF 신호(110a)를 수신하도록 연결되고 우측 채널 상태 신호인 R\_STATE\_SM을 포함하는 상기 R\_DDIFF 신호(110a)와 관련된 복수의 상태들을 나타내는 복수의 신호들을 발생시키도록 구성되는 제1 상태 프로세서(state processor)(112)를 포함할 수 있으며, 각 상태는 해당 시한 동안 상기 R\_DDIFF 신호(110a)가 나뉘는 신호 값들의 범위를 나타낸다.

- [0037] 상기 제1 상태 프로세서(112)는 또한 다음에 설명하는 바와 같이 상기 R\_STATE\_SM 신호의 소정의 상태들에 따른 상태 변환들을 갖는 두 가지 상태 신호들로 이해될 수 있는 R\_POSCOMP 신호(112a)를 발생시키도록 구성된다.

- [0038] 이와 유사하게, 상기 모션 센서(102)는 상기 L\_DDIFF 신호(126a)를 수신하도록 연결되고 좌측 채널 상태 신호인 L\_STATE\_SM을 포함하는 상기 L\_DDIFF 신호(126a)와 관련된 복수의 상태들을 나타내는 복수의 신호들을 발생시키도록 구성되는 제2 상태 프로세서(128)를 포함할 수 있으며, 각각의 상태는 해당 시한 동안 상기 L\_DDIFF 신호(126a)가 나뉘는 신호 값들의 범위를 나타낸다.

- [0039] 상기 제2 상태 프로세서(128)는 또한 다음에서 논의하는 바와 같이 상기 L\_STATE\_SM 신호의 소정의 상태들에 따른 상태 변환들을 갖는 두 가지 상태 신호로 이해될 수 있는 L\_POSCOMP 신호(128a)를 발생시키도록 구성된다.

- [0040] 신호 상태들은 다음에서 도 2, 도 3, 도 7 및 도 8과 관련하여 보다 상세하게 설명된다.

- [0041] 상기 상태 프로세서들(112, 128)은 또한 R\_STATE\_PEAK 신호와 L\_STATE\_PEAK 신호를 각기 발생시키도록

구성되며, 이는 도 17과 관련하여 다음에서 보다 상세하게 설명되며, 이들은 상기 R\_STATE\_SM 및 L\_STATE\_SM 신호들과 유사한 신호들이지만, 상태들 사이의 원하지 않는 채터(chatter)의 양이 감소된다.

[0042] 상기 상태 프로세서들(112, 128)은 또한 각기 R\_PPEAK 신호와 L\_PPEAK 신호를 발생시키도록 구성되고, 이는 도 2와 관련하여 다음에 보다 상세하게 설명되며, 이들은 각기 상기 R\_DDIFF 신호 및 상기 L\_DDIFF 신호의 양의 피크들의 크기들을 나타내는 신호들이다.

[0043] 상기 상태 프로세서들(112, 128)은 각기 R\_NPEAK 신호와 L\_NPEAK 신호를 발생시키도록 구성되며, 이는 도 2와 관련하여 다음에 보다 상세하게 설명되고, 이들은 각기 상기 R\_DDIFF 신호 및 상기 L\_DDIFF 신호의 음의 피크들의 크기들을 나타내는 신호들이다.

[0044] 상기 프로세서들(112, 128)은 또한 R\_POSCOMP\_PK 신호 및 L\_POSCOMP\_PK 신호를 발생시키도록 구성되고, 이는 도 7a, 도 9a 및 도 10과 관련하여 다음에 보다 상세하게 설명되며, 이들은 상기 R\_POSCOMP 및 L\_POSCOMP 신호들(112a, 128a)과 유사한 신호들이지만 다른 타이밍(timing)을 가진다.

[0045] 상기 모션 센서(102)는 상기 R\_POSCOMP 신호(112a), 상기 L\_POSCOMP 신호(128a), 상기 R\_STATE\_SM 신호, 상기 L\_STATE\_SM 신호, 상기 R\_STATE\_PEAK 신호, 상기 L\_STATE\_PEAK 신호, 상기 R\_PPEAK 신호, 상기 L\_PPEAK 신호, 상기 R\_NPEAK 신호, 상기 L\_NPEAK 신호, 상기 R\_POSCOMP\_PK 신호, 그리고 상기 L\_POSCOMP\_PK 신호를 수신하도록 연결되는 진동 프로세서(vibration processor)(116)를 포함할 수 있다.

[0046] 상기 진동 프로세서(116)는 또한 우측 및 좌측 채널 자동 이득 제어 신호들(114d, 114f)의 값들을 각기 나타내는 R\_AGC 신호(114a)와 L\_AGC 신호(114b)를 수신하도록 연결된다. 상기 진동 프로세서(116)는 하나 또는 그 이상의 FLAG 신호들(이진수 표시기들(binary indicators))(116a)과 진폭 차 플래그 신호(AMP\_DIFF\_FLAG 신호)(116b)를 발생시키도록 구성되며, 이들은 각기 물체(100)의 진동이나 상기 물체(100)의 진동이 없는 것을 나타낼 수 있다.

[0047] 일부 실시예들에 있어서, 상기 진동 프로세서(116)는 도 3과 관련하여 다음에 서술되는 진동 서브-프로세서들(vibration sub-processors)을 포함할 수 있으며, 이들은 각기 진동을 검출할 수 있고, 각기 상기 FLAG 신호들(116a, 116b)에 기인할 수 있다. 예를 들면, 각각의 하나는 각기 진동을 나타내는 하나 또는 그 이상의 진동 비트들에 기여할 수 있고. 상기 진동 프로세서(116)는 도 3, 도 5 내지 도 5b 및 도 9 내지 도 16a와 관련하여 다음에 보다 상세하게 설명된다.

[0048] 상기 모션 센서(102)는 또한 여기서 함께 AOA/AGC 프로세서(114)로 언급되는 자동 이득 제어(automatic gain control: AGC) 프로세서(114)와 함께 자동 오프셋 조절(automatic offset adjusting: AOA) 프로세서(114)를 포함할 수 있다. 상기 AOA/AGC 프로세서(114)는 상기 R\_DDIFF 신호(110a), 상기 L\_DDIFF 신호(126a), 상기 진폭 차 플래그 신호인 AMP\_DIFF\_FLAG 신호(116b)를 수신하도록 연결된다. 상기 AOA/AGC 프로세서(114)는, 상기 오프셋 및 이득 조절 모듈들(108, 124)의 이득과 오프셋을 제어하기 위해 우측 및 좌측 채널 이득 제어 신호들(114d, 114f)을 각기 발생시키고, 또한 우측 및 좌측 채널 오프셋 제어 신호들(114c, 114e)을 각기 발생시키도록 구성된다. 상기 AOA/AGC 프로세서(114)는 또한 R\_AGC 신호(114a) 및 L\_AGC 신호(114b)를 각기 발생시키도록 구성되며, 이들은 상기 이득 제어 신호들(114d, 114f)을 나타내는 신호들이다. 일부 선택적인 실시예들에 있어서, 상기 AOA/AGC 프로세서(114a)는 AOA 프로세서만으로 또는 AGC 프로세서만으로 대체된다.

[0049] 상기 모션 센서(102)는 상기 R\_POSCOMP 신호(112a), 상기 L\_POSCOMP 신호(128a) 및 상기 FLAG 신호들(116a)을 수신하도록 연결되는 출력 프로토콜 프로세서(output protocol processor)(118)를 포함할 수 있다. 상기 출력 프로토콜 프로세서(118)는 상기 기어(100)의 동작(회전)을 나타내며, 또한 하나 또는 그 이상의 상기 자기장 센싱 요소들(114a 내지 114c) 및/또는 상기 기어(102)의 진동을 나타내는 모션 신호(motion signal)(118a)를 발생시키도록 구성된다.

[0050] 상기 출력 프로토콜 프로세서(118)는 상기 모션 신호(118a)를 발생시키기 위하여 상기 R\_POSCOMP 신호(112a), 상기 L\_POSCOMP 신호(128A) 및 상기 FLAG 신호(116a)를 처리하도록 구성되는 방향 확인 프로세서(direction validation processor)(120)를 포함할 수 있다.

[0051] 일부 실시예들에 있어서, 상기 모션 신호(118a)는 상기 기어(100)의 회전 속도와 관계되는 주파수와 상기 기어(100)의 회전의 방향을 나타내는 두 개의 펄스 폭(pulse width)들 중에서 선택되는 하나를 갖는 싱글 비트(single bit) 디지털 신호이다. 일부 실시예들에 있어서, 상기 모션 신호(118a)는 상기 FLAG 신호(116a)가 진동을 나타낼 때에 블랭크(즉, 비활성화)된다. 일부 실시예들에 있어서, 상기 모션 센서(102)의 첫 번째 전원 인가에 따라, 상기 모션 신호(118a)는 활성화된 후에 유효 시간(valid time)까지 블랭크된다(또는 그렇지 않으면 회

전들의 방향을 나타내지 않는다). 상기 유효 시간의 식별은 도 18, 도 18a 및 도 19 내지 도 19b와 관련하여 다음에 설명된다. 그러나, 다른 실시예들에 있어서, 상기 모션 신호(118a)는 다른 방식들로 상기 기어(100)의 회전의 측면들을 나타낼 수 있으며, 전술한 진동이 다른 방식들로 표시될 수 있다.

[0052] 상이한 프로토콜들을 갖는 예시적인 출력 신호들이 2008년 7월 31일자로 출원된 미국 특허 출원 제12/183,367호, 2004년 11월 9일자로 등록된 미국 특허 제6,815,944호, 그리고 2006년 4월 11일자로 등록된 미국 특허 제7,026,808호에 기재되어 있다.

[0053] 일부 실시예들에 있어서, 상기 모션 센서(102)는, 예를 들면 게이트들(gates)인 전자 성분들을 갖는 다양한 프로세서들과 전술한 모듈들 및 후술하는 다양한 프로세스들을 구현하도록 구성되는 품질 향상 전자 장치(custom electronic device)로 이루어진다. 다른 실시예들에 있어서, 상기 모션 센서(102)는 전술한 다양한 프로세서들과 모듈들 및 후술하는 다양한 프로세스들을 구현하도록 구성되는, 중앙 처리 유닛(CPU)(132)과, 예를 들면 프로그램 메모리인 메모리(130)(컴퓨터 판독 가능 기억 매체)로 이루어진다.

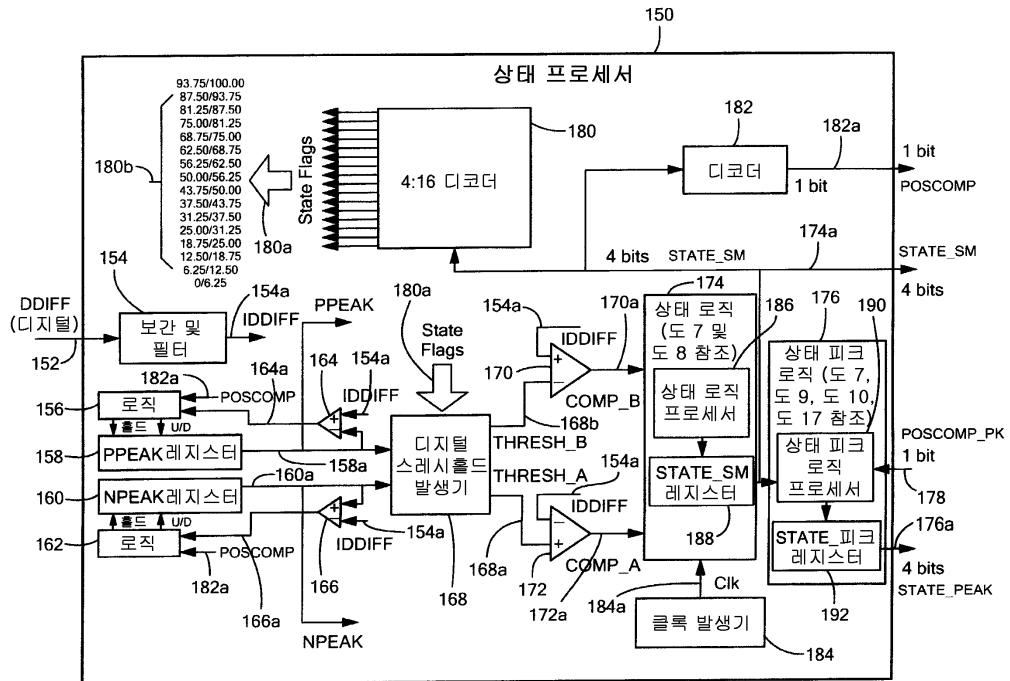

[0054] 다시 도 2를 참조하면, 상태 프로세서(150)는 도 1의 상태 프로세서들(112, 128) 중에서 각기 하나와 동일하거나 유사할 수 있으나, 여기서는 도 1의 좌측 또는 우측 채널들 중에서 하나만을 위해 도시된다. 상기 상태 프로세서(150)는 도 1의 상기 R\_DDIFF 신호(110a) 또는 상기 L\_DDIFF 신호(126a)와 동일하거나 유사할 수 있는 DDIFF 신호(152)를 수신하도록 연결된다. 도 2에 있어서, 상기 우측 및 좌측 채널 유형들(designations)(R 및 L)은 상기 상태 프로세서(150)가 상기 우측 및 좌측 채널들 중에서 하나가 될 수 있으므로 생략된다.

[0055] 일부 실시예들에 있어서, 상기 상태 프로세서(150)는 상기 DDIFF 신호(152)를 수신하도록 연결되고, 보간된 (interpolated) 디지털 DIFF 신호(IDDIFF)(154a)를 발생시키도록 구성된 보간(interpolation) 및 필터링 모듈(154)을 포함할 수 있다. 상기 보간 및 필터링은 상기 DDIFF 신호(152) 보다 높은 해상도와 샘플링 레이트(sampling rate)를 갖는 상기 IDDIFF 신호(154a)를 생성하는 다양한 방식들로 수행될 수 있다. 일부 실시예들에 있어서, 상기 DDIFF 신호(152)는 초당 약 삼십만 샘플들의 샘플링 레이트를 가지며, 각 샘플은 9-비트 워드이다. 일부 실시예들에 있어서, 상기 IDDIFF 신호(154a)는 초당 약 2백 7십만 샘플들의 샘플링 레이트(상기 DDIFF 레이트 9배)를 가지며, 각 샘플은 9-비트 워드이다.

[0056] 일부 실시예들에 있어서 상기 보간 및 필터 모듈(154)은 아래와 같은 전달 함수를 위하여,  $1-z^{-9}$ ,  $1-z^{-9}$ ,  $x_9$ ,  $1/(1-z^{-1})$ ,  $1/(1-z^{-1})$  및  $1/81$ 의 단계들을 구비하는, 6단계 CIC(cascaded integrator comb)(2차원 CIC) 인터폴레이팅 필터(interpolating filter)를 수행한다.

$$[1-2z^{-9} + z^{-18}] / [81(1-2z^{-1} + z^{-2})]$$

[0058] 예를 들면, 선형 보간 필터(linear interpolation filter), 이차 보간 필터(quadratic interpolation filter) 또는 지수 보간 필터(exponential interpolation filter)와 같은 다른 유형들의 보간 및 필터 모듈들도 사용될 수 있다.

[0059] 상기 상태 프로세서(150)는 제1 로직 회로(156)의 제어 하에서 유지되거나 합산(count up) 혹은 감산(count down) 할 수 있는 PPEAK 레지스터(158)(일부 실시예들에서 계수기(counter)가 될 수 있는)를 포함한다. 상기 제1 로직 회로(156)는 POSCOMP 신호(182a)(도 1의 R\_POSCOMP 신호(112a) 또는 L\_POSCOMP 신호(128a)와 동일하거나 유사할 수 있는)에 반응하고, 비교기(comparator)(164)에 의해 생성되는 비교기 출력 신호(164a)에 반응한다. 상기 PPEAK 레지스터(158)는 상기 IDDIFF 신호(154a)의 양의 피크들을 추적하는 PPEAK 신호(158a)에 기여하는 값들을 유지한다.

[0060] 이와 유사하게, 상기 상태 프로세서(150)는 제2 로직 회로(162)의 제어 하에서 유지되거나 합산 혹은 감산할 수 있는 NPEAK 레지스터(160)(일부 실시예들에서 계수기가 될 수 있는)를 포함한다. 상기 제2 로직 회로(162)는 POSCOMP 신호(182a)에 반응하고, 비교기(166)에 의해 생성되는 비교기 출력 신호(166a)에 반응한다. 상기 NPEAK 레지스터(160)는 상기 IDDIFF 신호(154a)의 음의 피크들을 추적하는 NPEAK 신호(160a)에 기여하는 값들을 유지한다. 상기 비교기들(164, 166)은 디지털 신호들을 수신하기 위해 연결되고 디지털 출력 신호들을 발생시키도록 구성되는 디지털 비교기들이다.

[0061] 상기 PPEAK 신호(158a)와 상기 NPEAK 신호(160a)의 발생은 도 7과 관련하여 다음에 보다 상세하게 설명한다. 하지만, 여기서는 상기 PPEAK 신호(158a)와 상기 NPEAK 신호(160a)가 일반적으로 직류(DC) 디지털 신호들이고, 상기 PPEAK 신호(158a)와 상기 NPEAK 신호(160a) 사이의 차이가 상기 IDDIFF 신호(154a)의 피크-투-피크(peak-

to-peak) 진폭을 나타내는 것으로 충분하다.

[0062] 상기 상태 프로세서(150)는 또한 상기 PPEAK 신호(158a)와 상기 NPEAK 신호(160a)를 수신하도록 연결되는 디지털 스레시홀드 발생기(threshold generator)(168)를 포함할 수 있다. STATE FLAGS 신호(180a)의 제어 하에서, 상기 디지털 스레시홀드 발생기(168)는 상기 IDDIFF 신호(154a)의 피크-투-피크 진폭의 결정된 퍼센티지인 선택된 스레시홀드 신호들(168a, 168b)을 발생시키도록 구성된다. 예를 들면, 하나의 기간 동안, 상기 스레시홀드 신호들(168a, 168b)은 각기 상기 IDDIFF 신호(154a)의 피크-투-피크 진폭의 31.25% 및 37.50%에 근접할 수 있다.

[0063] 두 개의 스레시홀드 신호들(168a, 168b)(또한 THRESH\_A 및 THRESH\_B로 언급되는)은 디지털 비교기들(172, 170)에 의해 각기 수신된다. 상기 비교기들(170, 172)은 또한 상기 IDDIFF 신호(154a)를 수신하도록 연결된다. 상기 비교기(170)는 COMP\_B 비교 신호(170a)를 발생시키도록 구성되고, 상기 비교기(172)는 COMP\_A 비교 신호(172a)를 발생시키도록 구성된다. 상기 비교기들(170, 172)이 윈도우(window) 비교기로서 동작하는 점을 인지할 수 있을 것이며, 상기 신호들(170a, 172a)로부터 상기 IDDIFF 신호(154a)가 상기 스레시홀드들인 THRESH\_A(168a)와 THRESH\_B(168b) 사이일 경우에는 유추될 수 있다.

[0064] 상기 THRESH\_A 및 THRESH\_B 신호들(168a, 168b)은 16쌍의 값들(180b) 중에서 하나로 선택되는 한 쌍의 디지털 값들을 나타낸다. 따라서, 어느 순간 이던지 시간 내에 상기 비교기들(170, 172)은 상기 IDDIFF 신호(154a)에 관계하는 값들의 16개의 범위들을 확인할 수 있다. 상기 범위들(180b)은 여기서 상기 IDDIFF 신호(154a)의 상태들(또는 상기 대응되는 DIFF 또는 DDIFF 신호들의 상태들)로서 언급된다.

[0065] 상기 상태 프로세서(150)는 또한 각기 상기 COMP\_A 및 COMP\_B 신호들(172a, 170a)을 각기 수신하도록 연결되는 상태 로직 모듈(state logic module)(174)을 포함한다. 상기 상태 로직 모듈(174)은 도 7 및 도 8과 관련하여 다음에 보다 상세하게 설명된다. 그러나, 여기서는 상기 상태 로직 모듈(174)이 전술한 COMP\_A 및 COMP\_B 신호들(172a, 170a)과 관련된 상태 정보를 디코딩하고, 4-비트 STATE\_SM 신호(174a)를 발생시키는 것으로 말할 수 있으면 충분하다. 상기 STATE\_SM 신호(174a)는 상태들, 즉 상기 IDDIFF 신호(154a)가 진행하는 범위들을 나타낸다.

[0066] 상기 상태 로직 모듈(174)은 상기 STATE\_SM 신호(174a)의 값들(예를 들면, 계속하여 한 번에 하나의 값)을 유지하도록 구성되는 STATE\_SM 레지스터(188)에 연결되는 상태 로직 프로세서(state logic processor)(186)를 포함할 수 있다.

[0067] 상기 상태 프로세서(150)는 또한 도 7, 도 7a, 도 9 및 도 9a와 관련하여 다음에 보다 상세하게 기술하는 상기 STATE\_SM 신호(174a)와 POSCOMP\_PK 신호(178)를 수신하도록 연결된 상태 피크 로직 모듈(state peak logic module)(176)을 포함할 수 있다. 상기 상태 피크 로직 모듈(176)은 상기 STATE\_SM 신호(174a)와 유사하지만, 보다 작은 변환 에러들(캐터)을 갖는 변환들을 구비하는 STATE\_PEAK 신호(176a)를 발생시키도록 구성된다. 상기 변환 에러들은 도 7 및 도 7a와 관련하여 다음에 보다 상세하게 기재된다.

[0068] 상기 상태 피크 로직 모듈(176)은 상기 STATE\_PEAK 신호(176a)의 값들을 유지하도록 구성된 STATE\_PEAK 레지스터(192)에 연결되는 상태 피크 로직 프로세서(state peak logic processor)(190)를 포함할 수 있다.

[0069] 상기 상태 프로세서(150)는 또한 상기 STATE\_SM 신호(174a)를 수신하도록 연결되는 4 : 16 디코더(decoder)(180)를 포함할 수 있다. 상기 4 : 16 디코더(180)는 16개의 제어 신호들, 즉 도시된 바와 같이 STATE FLAGS(180a) 중에서 하나를 제공하도록 구성된다. 상기 플래그들 각각은 복수의 진폭 범위(180b) 중에서 특정한 진폭 범위를 나타낸다. 상기 진폭 범위들(180b)은 상기 IDDIFF 신호(154a)의 피크-투-피크 범위의 퍼센티지들로서 표현된다.

[0070] 특정한 진폭 범위들(180b)이 도시되어 있지만, 상기 진폭 범위들이 도시된 것들과 다를 수 있으며, 선형적으로 구성될 필요는 없는 점을 이해할 수 있을 것이다.

[0071] 상기 상태 프로세서(150)는 또한 상기 STATE\_SM 신호(174a)를 수신하도록 연결되고 상기 STATE\_SM 신호(174a) 내에서 상기 상태 변환들의 특정한 하나들의 시간들에서 변환들을 갖는 상기 POSCOMP 신호(182a)를 발생시키도록 구성되는 디코더(decoder)(182)를 포함할 수 있다.

[0072] 상기 상태 프로세서(150)는 상기 상태 로직 모듈을 클록하는 클록 신호(CLK)(184a)를 제공하는 클록 발생기 회로(clock generator circuit)(184)와 상기 상태 프로세서(150) 내의 다른 프로세서들 및 모듈들을 포함할 수 있다.

- [0073] 도 3을 참조하면, 진동 프로세서(vibration processor)(200)는 도 1의 진동 프로세서(116)와 동일하거나 유사할 수 있다. 상기 진동 프로세서(200)는 도 1을 참조하여 상술한 바와 같이, 도 1의 모션 센서(102)의 우측 및 좌측 채널들로부터 많은 신호들을 수신하도록 연결된다. 상기 진동 프로세서(200)는 다양한 입력 신호들을 처리하고, 싱글 비트의 두 가지 상태 신호들이 될 수 있는 복수의 플래그 신호들(flag signals)을 발생시키도록 구성된다.

- [0074] 특히, 상기 진동 프로세서(200)는 도 1의 우측 및 좌측 이득 제어 신호들(114d, 114f)을 나타내는 상기 R\_AGC 및 L\_AGC 신호들을 수신하도록 구성되며, 또한 도 1의 R\_DDIFF 신호(110a)와 L\_DDIFF 신호(126a)를 수신하도록 연결되는 채널 진폭 차 프로세서(channel amplitude difference processor)(202)를 포함할 수 있다. 상기 채널 진폭 차 프로세서(202)는, 도 1의 물체(100)의 진동을 나타내는 경향이 있는, 소정의 양 이상에 의해 달라지는 상기 우측 및 좌측 이득 제어 신호들(114d, 114f)을 나타내는 AMP\_DIFF\_FLAG 신호를 발생시키도록 구성된다. 상기 채널 진폭 차 프로세서(202)의 동작은 도 5 내지 도 5b와 관련하여 다음에 보다 상세하게 서술된다.

- [0075] 상기 진동 프로세서(200)는 또한 우측 및 좌측 변곡 프로세서(inflexion processor)들(204, 206)을 각기 포함할 수 있다. 상기 우측 변곡 프로세서(204)는 도 1의 R\_STATE\_SM 신호(또한 도 2의 상기 STATE\_SM 신호(174a) 참조)와 도 1의 R\_STATE\_PEAK 신호(또한 도 2의 상기 STATE\_PEAK 신호(176a) 참조)를 수신하도록 연결된다. 상기 우측 변곡 프로세서(204)는 도 1의 물체(100)의 방향의 변화를 나타내는 R\_INFLECTION\_FLAG 신호를 발생시키고, 또한 도 1의 R\_POSCOMP\_PK 신호(또한 도 2의 POSCOMP\_PK 신호(178) 참조)를 발생시키도록 구성된다.

- [0076] 상기 좌측 변곡 프로세서(206)는 도 1의 L\_STATE\_SM 신호(또한 도 2의 STATE\_SM 신호(174a) 참조)와 도 1의 L\_STATE\_PEAK 신호(또한 도 2의 STATE\_PEAK 신호(176a) 참조)를 수신하도록 연결된다. 상기 좌측 변곡 프로세서(206)는 도 1의 물체(100)의 방향의 변화를 나타내는 L\_INFLECTION\_FLAG 신호를 발생시키고, 도 1의 L\_POSCOMP\_PK 신호(또한 도 2의 POSCOMP\_PK 신호(178) 참조)를 발생시키도록 구성된다.

- [0077] 상기 R\_POCOMP\_PK 신호 및 상기 L\_POSCOMP\_PK 신호의 발생은 도 7, 도 7a 및 도 10과 관련하여 다음에 보다 상세하게 설명된다. 상기 변곡 프로세서들(204, 206)의 동작은 도 9, 도 9a 및 도 10과 관련하여 다음에 보다 상세하게 설명된다.

- [0078] 상기 진동 프로세서(200)는 도 1의 R\_POSCOMP 신호(112a)와 L\_POSCOMP 신호(128a)를 수신하도록 연결되는 방향 변화 프로세서(direction change processor)(208)를 포함할 수 있다(또한 도 2의 POSCOMP 신호(182a) 참조). 상기 방향 변화 프로세서(208)는 도 1의 물체(100)의 방향의 변화를 나타내는 DIR\_CHANGE\_FLAG 신호를 발생시키도록 구성된다. 상기 방향 변화 프로세서(208)의 동작은 도 11과 관련하여 다음에 보다 상세하게 기재된다.

- [0079] 상기 진동 프로세서(200)는 또한 도 1의 R\_POSCOMP\_PK 신호와 L\_POSCOMP\_PK 신호를 수신하도록 연결되는 방향 변화\_PK 프로세서(210)를 포함할 수 있다(또한 도 2의 POSCOMP\_PK 신호(178)와 도 3의 우측 변곡 프로세서(204)에 의해 생성되는 R\_POSCOMP\_PK 신호 및 좌측 변곡 프로세서(206)에 의해 생성되는 L\_POSCOMP\_PK 신호 참조). 상기 방향 변화\_PK 프로세서(210)는 도 1의 물체(100)의 방향의 변화를 나타내는 DIR\_CHANGE\_PK\_FLAG 신호를 발생시키도록 구성된다. 상기 방향 변화\_PK 프로세서(210)의 동작은 도 12와 관련하여 다음에 상세하게 기재한다.

- [0080] 상기 진동 프로세서(200)는 또한 상기 R\_POSCOMP\_PK 신호, 상기 L\_POSCOMP\_PK 신호, 상기 R\_POSCOMP\_PK 신호 및 상기 L\_POSCOMP\_PK 신호를 수신하도록 연결되는 방향 변화\_RM(실행 모드(running mode)) 프로세서(212)를 포함할 수 있다. 상기 방향 변화\_RM 프로세서(212)는 도 1의 물체(100)의 방향의 변화를 나타내는 DIR\_CHANGE\_RM\_FLAG 신호를 발생시키도록 구성된다. 상기 방향 변화\_RM 프로세서(212)의 동작은 도 13과 관련하여 다음에 상세하게 기술한다.

- [0081] 상기 진동 프로세서(200)는 또한 도 1의 상기 R\_POSCOMP\_PK 신호, 상기 L\_POSCOMP\_PK 신호, 상기 R\_STATE\_PK 신호, 상기 L\_STATE\_PK 신호, 상기 R\_STATE\_SM 신호 및 상기 L\_STATE\_SM 신호(또한 도 2의 STATE\_PEAK 신호(176a) 및 STATE\_SM 신호(174a) 참조)를 수신하도록 연결되는 신호 위상 프로세서(signal phase processor)(214)를 포함할 수 있다. 상기 신호 위상 프로세서(214)는 위상이 너무 근접하는 상기 우측 및 좌측 채널들에서 신호들과 이에 따른 도 1의 물체(100)의 진동을 나타내는 TOO\_CLOSE\_FLAG 신호를 발생시키도록 구성된다. 상기 신호 위상 프로세서(214)의 동작은 도 14와 관련하여 다음에 상세하게 설명된다.

- [0082] 상기 진동 프로세서(200)는 또한 우측 및 좌측 피크 업데이트 점프 프로세서(peak update jump processor)들(216, 218)을 각기 포함할 수 있다. 상기 우측 피크 업데이트 점프 프로세서(216)는 도 1의 R\_PPEAK 신호 및 R\_NPEAK 신호(또한 도 2의 PPEAK 및 NPEAK 신호들(158a, 160a)을 각기 참조)를 수신하도록 연결된다. 상기 좌

측 피크 업데이트 점프 프로세서(216)는 도 1의 L\_PPEAK 신호 및 L\_NPEAK 신호(또한 도 2의 PPEAK 및 NPEAK 신호들(158a, 160a)을 각기 참조)를 수신하도록 연결된다. 상기 우측 피크 업데이트 점프 프로세서(216)는, 진폭이 너무 많이 증가하는 우측 채널 자기장 신호를 나타내는 R\_PEAK\_CLAMP\_FLAG 신호와 진폭이 너무 작은 우측 채널 자기장 신호를 나타내는 R\_PEAK\_IN\_FLAG 신호를 발생시키도록 구성된다. 상기 좌측 피크 업데이트 점프 프로세서(218)는, 진폭이 너무 큰 좌측 채널 자기장 신호를 나타내는 L\_PEAK\_CLAMP\_FLAG 신호와 진폭이 너무 작은 좌측 채널 자기장 신호를 나타내는 L\_PEAK\_IN\_FLAG 신호를 발생시키도록 구성된다. 상기 피크 업데이트 점프 프로세서들(216, 218)의 동작은 도 15와 관련하여 다음에 상세하게 기술된다.

[0083] 상기 진동 프로세서(200)는 또한 우측 및 좌측 POSCOMP 진동 프로세서들(220, 222)을 각기 포함할 수 있다. 상기 우측 및 좌측 POCOMP 진동 프로세서들(220, 222)은 도 16과 관련하여 다음에 보다 명백하게 논의하는 바와 같이 다양한 입력 신호들을 수신하도록 연결된다. 상기 우측 POSCOMP 진동 프로세서(220)는 적절한 R\_POSCOMP 신호를 나타내는 R\_POSCOMP\_OK\_FLAG 신호를 발생시키도록 구성된다. 상기 좌측 POSCOMP 진동 프로세서(222)는 적절한 L\_POSCOMP 신호를 나타내는 L\_POSCOMP\_OK\_FLAG 신호를 발생시키도록 구성된다. 상기 POSCOMP 진동 프로세서들(220, 222)의 동작은 도 16과 관련하여 다음에 상세하게 설명된다.

[0084] 상기 진동 프로세서(200)는 또한 우측 및 좌측 POSCOMP\_PK 진동 프로세서들(224, 226)을 각기 포함할 수 있다. 상기 우측 및 좌측 POSCOMP\_PK 진동 프로세서들(224, 226)들은 도 16a와 관련된 다음의 논의로부터 명확해지는 바와 같이 다양한 입력 신호를 수신하도록 연결된다. 상기 우측 POSCOMP\_PK 진동 프로세서(224)는 적절한 R\_POSCOMP\_PK 신호를 나타내는 R\_POSCOMP\_PK\_OK\_FLAG 신호를 발생시키도록 구성된다. 상기 좌측 POSCOMP\_PK 진동 프로세서(226)는 적절한 L\_POSCOMP\_PK 신호를 나타내는 L\_POSCOMP\_PK\_OK\_FLAG 신호를 발생시키도록 구성된다. 상기 POSCOMP\_PK 진동 프로세서들(224, 226)의 동작은 도 16a와 관련하여 다음에 상세하게 기술된다.

[0085] 도 4, 도 5, 도 6, 도 10 내지 도 17 및 도 19가 도 1의 모션 센서(102)에서 구현될 수 있는 다음의 고려된 기술에 대응되는 흐름도(flow chart)들을 나타내는 것을 이해할 수 있을 것이다. 여기서 "프로세싱 블록들(processing blocks)"로 나타낸 사각형 요소들(도 4의 요소(256)에 의해 정형화된)은 컴퓨터 소프트웨어 명령들 또는 명령들의 그룹들을 나타낸다. 여기서 "판단 블록들(decision blocks)"로 나타낸 다이아몬드 형상의 요소들(도 4의 요소(26)에 의해 정형화된)은 상기 프로세싱 블록들에 의해 나타나는 상기 컴퓨터 소프트웨어 명령들의 실행에 영향을 미치는 컴퓨터 소프트웨어 명령들 또는 명령들의 그룹들을 나타낸다.

[0086] 선택적으로, 상기 프로세싱 또는 판단 블록들은 디지털 신호 프로세서 회로 또는 주문형 반도체(application specific integrated circuit: ASIC)와 같은 기능적으로 동등한 회로들에 의해 수행되는 단계들을 나타낸다. 상기 흐름 도표(flow diagram)들은 특정한 프로그래밍 언어의 문법(syntax)을 묘사하지 않는다. 오히려, 상기 흐름 도표들은 회로들을 제조하거나 특정한 장비에 요구되는 프로세싱을 수행하기 위한 컴퓨터 소프트웨어를 생성할 것을 요구하는 해당 기술 분야에서 통상의 지식을 가진 자에게 기능적인 정보를 예시한다. 루프들(loops) 및 변수들의 초기화와 임시적인 변수들의 사용과 같은 많은 루틴 프로그램(routine program)들은 도시되지 않음에 유의하도록 한다. 해당 기술 분야에서 통상의 지식을 가진 자라면 여기서 별도로 표시되지 않는 한 기재된 블록들의 특정한 배열은 단지 예시적인 것이며, 본 발명의 범주로부터 벗어나지 않고도 변화될 수 있음을 이해할 수 있을 것이다. 따라서 가능할 경우에 기재된 블록들에 대해 다른 순서로 다르게 언급하지 않는 한, 단계들은 편의에 따라 또는 원하는 순서로 수행될 수 있다.

[0087] 도 4, 도 5 및 도 6은 도 1의 상기 AOA/AGC 프로세서(114), 상기 진동 프로세서(116), 그리고 상기 오프셋 및 이득 조절 모듈들(108, 124)과 관련된 프로세스들을 나타낸다.

[0088] 도 4를 참조하면, 프로세스(250)는 전원이 먼저 도 1의 모션 센서(102)에 인가된 후에 짧게 시작될 수 있으며, 여기서 동작의 BURP 모드로 언급된다. 그렇지만 상기 프로세스(250)는 상기 우측 또는 좌측 채널들 중에서 하나를 언급한다. 상기 프로세스(250)가 상기 우측 및 좌측 채널들 모두에 직렬로 또는 병렬로 적용될 수 있음을 이해할 수 있을 것이다.

[0089] 상기 프로세스(250)는 타겟 윈도우(target window)가 설정되는 블록(252)에서 시작된다. 특정한 일 실시예에 있어서, 약 50의 최하위 비트(least significant bit: LSB)들의 타겟 윈도우가 선택되며, 이는 상기 DDIFF 신호가 채용할 수 있는 값들(도 1의 R\_DDIFF 신호(110a) 및/또는 L\_DDIFF 신호(126a))의 동작 범위의 중간에 근접하여 집중된다. 특정한 일 실시예에 있어서, 상기 DDIFF 신호는 9 비트들을 가지며, 이에 따라 상기 DDIFF 신호의 전체 범위는 511의 최하위 비트(LSB)들이 된다. 상기 동작의 BURP 모드 동안, 해당 DDIFF 신호가 상기 AOA/AGC 프로세서(114)(도 1)와 상기 오프셋 및 이득 조절 모듈들(108, 124)(도 1)의 동작에 의해 이동되어 상기 동작 범위의 중심에 근접하는 상기 타겟 윈도우 내에 있는 것이 바람직하다.

- [0090] 상기 DDIFF 신호가 상기 타겟 원도우 내에 있지 않을 경우, 이후에 블록(256)에서, 상기 AOA(즉, 상기 DIFF 신호의 오프셋)은 도 1의 AOA 프로세서(114)의 동작에 의해 조절된다. 일부 실시예들에 있어서, 블록(256)에서, 도 1의 오프셋 제어 신호들(114c, 114e) 중에서 하나 또는 모두는, 예를 들면 하나의 계산인 상기 DDIFF 신호가 상기 타겟 원도우로부터 얼마나 멀리 있는가에 의존할 수 있는 수치에 따라 상기 타겟 원도우를 향해 상기 DDIFF 신호를 강제할 수 있도록 조절된다.

- [0091] 대략 33 마이크로초(microsecond)의 대기 기간(waiting period)(258) 동안에 일어나는 블록(260)에서, 상기 DDIFF 신호는 상기 DDIFF 신호가 상기 대기 기간 동안의 어느 때에도 상기 타겟 원도우를 가로지를 경우에 이를 확인하도록 검사된다. 상기 DDIFF 신호가 상기 대기 기간(258) 동안의 어느 때에서 상기 타겟 원도우를 가로지른 경우, 상기 프로세스(250)는 종료된다.

- [0092] 블록(260)에서 상기 DDIFF 신호가 상기 대기 기간(258) 동안에 상기 타겟 원도우를 가로지르지 않을 경우, 그러면 상기 프로세스는 만약 상기 AOA(자동 오프셋 조절)가 그 조절 범위의 끝부분에 있는지를 확인하는 곳인 블록(262)으로 진행한다. 상기 AOA가 그 조절 범위의 끝부분에 있지 않을 경우, 상기 프로세스는 블록(256)으로 복귀한다.

- [0093] 블록(262)에서 상기 AOA가 그 조절 범위의 끝부분에 있을 경우, 그러면 상기 프로세스는 대신에 블록(264)으로 진행한다.

- [0094] 블록(264)에서, 상기 타겟 원도우가 상기 DDIFF 신호인 값들의 동작 범위의 중간에 근접하여 집중된 약 320의 최하위 비트 LSB들로 확장된다.

- [0095] 블록(266)에서, 상기 DDIFF 신호가 새로운 타겟 원도우 내에 있는지가 결정된다. 상기 DDIFF 신호가 상기 새로운 타겟 원도우 내에 있을 경우, 상기 프로세스는 종료된다. 상기 DDIFF 신호가 상기 새로운 타겟 원도우 내에 있지 않을 경우, 상기 프로세스는 상기 AOA 보다는 상기 AGC가 상기 새로운 타겟 원도우를 향해 상기 DDIFF 신호를 이동시키도록 조절되는 블록(268)으로 진행한다. 일부 실시예들에 있어서, 블록(268)에서, 도 1의 상기 이득 제어 신호들(114d, 114f) 중에서 하나 또는 모두는, 예를 들면 하나의 계산인 상기 타겟 원도우로부터 상기 DDIFF 신호가 얼마나 멀어졌는지에 의존하는 수치에 의해 상기 DDIFF 신호가 상기 새로운 타겟 원도우를 향해 강제되도록 조절된다.

- [0096] 약 33 마이크로초의 대기 기간(270) 동안에 발생되는 블록(272)에서, 상기 DDIFF 신호는 상기 DDIFF 신호가 상기 대기 기간(270) 동안 어느 때라도 상기 새로운 타겟 원도우를 가로지르는지를 확인하도록 검사된다. 상기 DDIFF 신호가 상기 대기 기간(270) 동안에 어느 때라도 상기 새로운 타겟 원도우를 가로지른 경우, 상기 프로세스(250)는 종료된다.

- [0097] 블록(272)에서, 상기 DDIFF 신호가 상기 대기 기간(270) 동안에 상기 타겟 원도우를 가로지르지 않을 경우, 상기 프로세스는 상기 AGC가 그 조절 범위의 끝부분에 있는지를 확인하는 곳인 블록(274)으로 진행한다. 상기 AGC가 그 조절 범위의 끝부분에 있지 않을 경우, 상기 프로세스(250)는 블록(268)으로 복귀한다. 블록(274)에서, 상기 AGC가 그 조절 범위의 끝부분에 있을 경우, 상기 프로세스(250)는 종료된다.

- [0098] 다시 도 5를 참조하면, 도 4를 참조하여 상술한 상기 동작의 BURP 모드 후에, 상기 AGC 및 AOA는 보정 모드 및 대응되는 프로세스(300)로 진입한다. 상기 프로세스(300)는 약 320의 최하위 비트들의 런 원도우(learn window)가 선택되는 블록(302)에서 시작된다. 상기 런 원도우는, 일부 실시예들에 있어서, 511의 최하위 비트 범위를 위한 9 비트들을 갖는 DDIFF 신호의 전체 범위로 집중된다.

- [0099] 상기 프로세스(300)는 상기 DDIFF 신호가 도 4의 상기 BURP 모드를 뒤따르는 첫 번째 신호 피크를 이미 구현하였는지를 결정하는 블록(304)으로 진행한다. 상기 첫 번째 피크는 다양한 방식들로 확인될 수 있다. 특정한 일 실시예에 있어서, 상기 첫 번째 피크는 상기 DDIFF 신호가 상기 런 원도우의 상한(upper limit)과 상기 런 원도우의 하한(lower limit)을 가로지르기 전에 한 번에 인된다.

- [0100] 기본적으로, 블록(304)에서, 상기 DDIFF 신호가 상기 양의 및 음의 한계들을 모두 가로질렀기만 하면, 상기 DDIFF 신호는 범위 내에 상기 DDIFF 신호를 가져오도록 이득 조절을 요구하는 상기 런 원도우를 넘어서 양의 및 음의 과도함을 모두 가진다. 이러한 표준들을 사용하여, 이득 조절이 상기 첫 번째 신호 피크 상에서 일어나지 않는다.

- [0101] 상기 DDIFF 신호가 도 4의 상기 BURP 모드를 따르는 상기 첫 번째 피크 내에 존재할 경우, 그러면 상기 프로세스는 도 1의 우측 및 좌측 채널들의 이득 제어 신호들(114d, 114f)의 상기 AGC 계산들이 3 이상 다른 가를 결정

하는 블록(324)으로 진행한다. 상기 AGC 계산들이 3 이상으로 다를 경우, 상기 프로세스는 도 1 및 도 3의 상기 AMP\_DIFF\_FLAG 신호가 설정되는 블록(326)으로 진행한다.

[0102] 블록(328)에서, 보다 높은 이득 채널의 AGC 계산이 보다 낮은 이득 채널의 AGC 계산을 향하여 감소된다. 이러한 조절의 이유들은 도 5a 및 도 5b와 관련된 다음의 논의로부터 보다 명확해진다. 일부 실시예들에 있어서, 블록(328)에서, 상기 보다 높은 이득 채널의 AGC 계산이 상기 보다 낮은 이득 채널의 AGC 계산과 동일하도록 감소된다. 다른 실시예들에 있어서, 상기 보다 높은 이득 채널의 AGC 계산이, 예를 들면 3인 상기 보다 낮은 이득 채널의 소정의 계산 내로 감소된다.

[0103] 블록(330)에서, 상기 AMP\_DIFF\_FLAG 신호는 소거된다.

[0104] 블록(324)에서, 상기 두 채널들의 상기 AGC 계산들이 3 이상으로 다르지 않을 경우, 상기 프로세스는 블록(306)으로 진행한다. 블록(304)에서, 상기 DIFF 신호가 그 첫 번째 피크 후에 존재할 경우, 그러면 상기 프로세스(300)는 블록(306)으로 진행한다.

[0105] 남는 블록들은 상기 우측 또는 좌측 채널만을 논의하지만, 상술한 바와 같이, 상기 로직이 병렬이나 직렬로 두 채널들 모두에 적용될 수 있다.

[0106] 블록(306)에서, 상기 DIFF 신호가 상기 런 윈도우의 상한 보다 위에 또는 상기 런 윈도우의 하한 보다 아래에 있을 경우, 그러면 상기 DDIFF 신호는 지나치게 크고(이득이 너무 높고) 상기 프로세스는 상기 AGC 계산(예를 들면, 도 1의 해당 이득 제어 신호(114d 또는 114f))이 감소되는 블록(308)으로 진행한다.

[0107] 블록(310)에서, 상기 AOA, 즉 상기 오프셋 제어 신호(예를 들면, 도 1의 해당 오프셋 제어 신호(114c 또는 114e))는 블록(308)의 상기 AGC 조절에 따른 양에 의해 조절될 수 있다.

[0108] 상기 DDIFF 신호의 볼트로서 상기 AOA 단계 사이즈는 상기 AGC 이득의 함수이다. 신호 정규화(signal normalization)는 AGC 조절이 일어남에 따라 상기 AGC 조절에 의해 야기되는 바와 유사한 전압에 의해 상기 DIFF 신호를 이동시키도록 상기 AOA를 사용하여 지속적으로 이루어질 수 있다. 주어진 AGC 이득에서 AOA 사이즈의 예상되는 전압 단계 사이즈와 주어진 AGC 조절로 기인하는 예상되는 전압 이동 모두를 이용하여, 표로서 각각의 가능한 AGC 조절을 위한 상기 AOA 계산을 조절하는 양에 관하여 미리 계산할 수 있다. 상기 수행은 루업 테이블(lookup table)이 될 수 있다.

[0109] 블록(312)에서, 상기 프로세스(300)는 약 28 밀리초(millisecond) 동안 대기하고, 이후에 블록(306)으로 돌아간다.

[0110] 블록(306)에서, 상기 DDIFF 신호가 상기 런 윈도우의 상한 보다 위에 또는 상기 런 윈도우의 하한 보다 아래에 있지 않을 경우, 상기 프로세스는 도 2의 POSCOMP 신호(182a)의 에지들(edges)의 결정된 숫자가 검출되었는지를 결정하는 블록(314)으로 진행한다. 상기 결정된 숫자는 임의의 진동이 검출되었는지에 따라 동적으로 결정된 숫자이다. 상기 결정된 숫자는 도 19 내지 도 19b와 관련된 다음의 논의로부터 보다 잘 이해될 것이다. 일부 실시예에 있어서, 여기서는 상기 결정된 숫자가 상기 POSCOMP 신호의 3 또는 그 이상의 에지들인 것으로 말하면 충분하다.

[0111] 상기 POSCOMP 에지들의 결정된 숫자가 생성되는 경우, 그러면 상기 프로세스가 종료된다. 상기 에지들의 결정된 숫자가 발생되지 않을 경우, 상기 프로세스는 블록(306)으로 돌아가고, AGC 및 AOA 조절들이 더 수행될 수 있다.

[0112] 적어도 블록들(324 내지 330)이 도 3의 채널 진폭 차 프로세서(202)에 의해 수행될 수 있는 점은 명백하다. 그러나, 함수들의 다른 분할(partitioning)도 가능하다.

[0113] 도 5a를 참조하면, 그래프(320)는 가우스(Gauss)의 자기장 강도의 단위들로 나타낸 수직 축들과 시간의 임의의 단위들 나타낸 수평 스케일을 가진다. 상기 그래프(320)는 2개의 신호들을 포함한다. 제1 신호(322)는, 예를 들면 도 1의 모션 센서(102)의 우측 채널에 기여하는 상기 자기장 센싱 요소들(104a, 104b)에 의해 겪는 제1 자기장을 나타낸다. 제2 자기장 신호(324)는, 예를 들면 도 1의 모션 센서(102)의 좌측 채널에 기여하는 자기장 센싱 요소들(104b, 104c)에 의해 겪는 제2 자기장을 나타낸다.

[0114] 상기 제1 신호(322)는  $\Phi_1$  및  $\Phi_2$ 의 각도들 사이의 도 1의 기어(100)의 회전의 각도들의 사이에 존재하는 부분(322a)을 포함한다. 상기 제2 신호(324)는 상기  $\Phi_1$  및  $\Phi_2$ 의 각도들 사이의 도 1의 기어(100)의 회전의 각도들의 사이에 존재하는 부분(324a)을 포함한다. 도 1의 상기 기어(100)가 회전 진동을 경험하는 경우, 상기 회전

진동은 상기  $\Phi_1$  및  $\Phi_2$ 의 각도들 사이의 전방 및 후방 회전에 대응될 수 있다. 따라서 상기 신호들(322, 324)의 다른 부분들은 실제로 발생되지 않지만, 이에 상관없이 명확성을 위해 마치 상기 기어(100)가 완전히 회전하는 것처럼 가상의 선들로 도시된다.

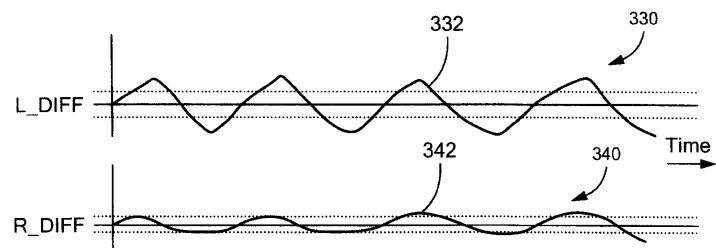

[0115] 도 5b를 참조하면, 그레프(330)는 볼트의 임의의 단위들로 나타낸 수직 축들과 시간의 임의의 단위들로 나타낸 수평 축들을 가진다. 상기 그레프(330)는 상기 기어(100)의 존재 시에 상기 기어가 도 5a의  $\Phi_1$  및  $\Phi_2$ 의 각도들 사이의 회전 진동을 경험할 때에 도 1의 모션 센서(102)에 의해 생성될 수 있는 신호(332)를 포함한다. 특히, 상기 신호(332)는 도 1의 L\_DIFF 신호(124a)에 대응될 수 있다. 도 1의 기어(100)가 완전히 회전하지 않음을 통해 상기 기어(100)의 이동이 여전히 도 1의 변화하는 L\_DIFF 신호(124a)를 발생시키고, L\_DIFF 신호(332)가 결과로 야기되는 점을 이해할 수 있을 것이다.

[0116] 상기 그레프(336)는 또한 볼트의 임의의 단위들로 나타낸 수직 축들과 시간의 임의의 단위들로 나타낸 수평 스케일을 가진다. 상기 그레프(336)는 상기 기어(100)의 존재 시에 상기 기어가 도 5a의  $\Phi_1$  및  $\Phi_2$ 의 각도들 사이에서 회전 진동을 겪을 때에 도 1의 모션 센서(102)에 의해 생성될 수 있는 신호(338)를 포함한다. 특히, 상기 신호(338)는 도 1의 R\_DIFF 신호(108a)에 대응될 수 있다. 도 1의 기어(100)가 완전히 회전하지 않음을 통해 상기 기어(100)의 이동이 여전히 도 1의 변화하는 R\_DIFF 신호(108a)를 발생시키고, R\_DIFF 신호(338)를 야기하는 점을 이해할 수 있을 것이다.

[0117] 상기 R\_DIFF 신호(338)가 상기 L\_DIFF 신호(332)보다 작은 진폭을 가지는 점은 명확할 것이다. 다른 진폭들은 도 5a의 신호 범위들(322a, 324a)의 다른 기울기들에 기인한다. 상기 회전 진동이 도 5a의  $\Phi_1$  및  $\Phi_2$ 의 각도들 사이에서 아니라 기어 각도들에서 일어났을 경우, 그러면 상기 신호들(332, 338)의 다른 상대적인 진폭들이 발생될 수 있다.

[0118] 상기 다른 진폭의 L\_DIFF 및 R\_DIFF 신호(332, 338)들은 각기 도 1의 기어(100)의 진동을 나타내며, 이에 따라, 충분히 다를 경우, 진동의 검출에 다른 진폭들이 이용될 수 있는 점을 이해할 수 있을 것이다.

[0119] 따라서, 도 5의 박스들(324 내지 330)이 상기 동작의 보정 모드 동안 상기 두 채널들 사이의 진폭 오정합(mismatch)을 야기하는 진동에 따라 도 1의 모션 센서(102)의 두 채널들의 AGC 설정을 수정하는 데 사용되는 점은 명백하다.

[0120] 도 5의 박스들(324 내지 330)은 또한 진동의 부재 시에도 도 1의 모션 센서(102)의 신속한 보정을 야기할 수 있다. 더욱이, 상기 AGC 계산 차이가 블록(328)에서 감소되지 않을 경우라 하여도, 상기 프로세스는 여전히 진동을 검출하고 블록(328)에서 상기 AMP\_DIFF\_FLAG 신호를 설정하는데 사용될 수 있다.

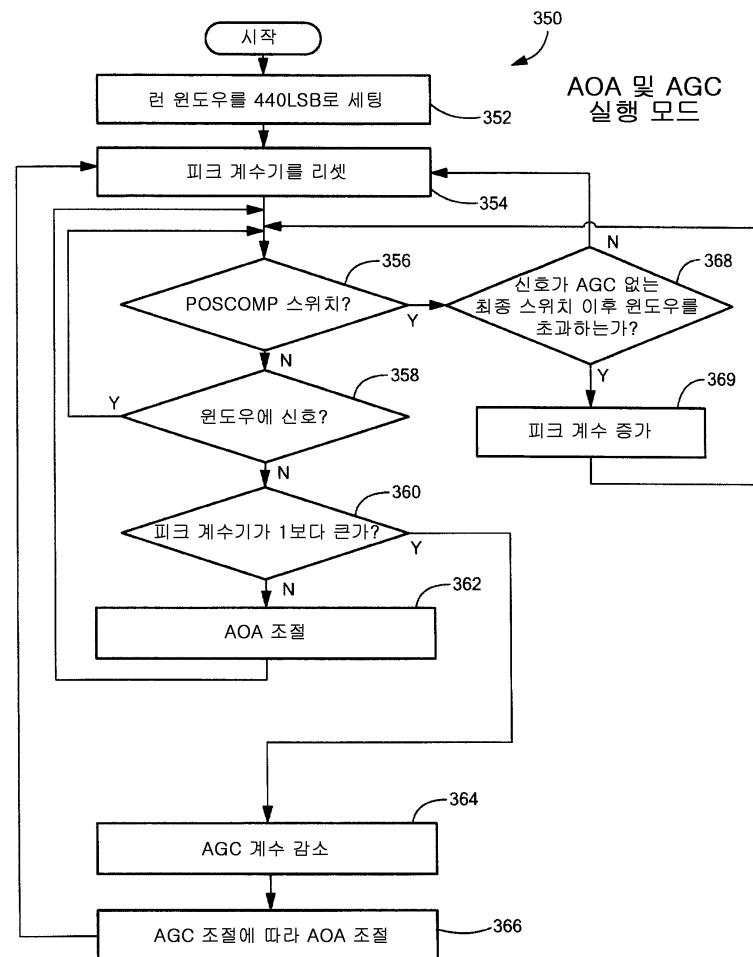

[0121] 도 6을 참조하면, 프로세스(350)는, 도 4의 동작의 BURP 모드 후에 및 도 5의 동작의 보정 모드 후에, 도 1의 모션 센서(102)의 두 채널들의 AGC 및 AOA를 제어하는 데 사용된다. 상기 프로세스(350)는 동작의 실행 모드(running mode) 동안에 일어나며, 상기 좌측 또는 우측 채널 중에서 하나를 위해 다음에서 설명한다.

[0122] 블록(352)에서, 약 440의 최하위 비트의 렌 윈도우가 선택된다. 상기 렌 윈도우는, 일부 실시예들에서, 511의 최하위 비트 범위를 위해 9 비트들을 갖는 상기 DIFF 신호의 전체 범위 내로 집중된다.

[0123] 블록(354)에서, 피크 계수기(peak counter)는 0으로 리셋된다. 상기 피크 계수기는 상기 렌 윈도우의 외측에서 검출되는 상기 DDIFF 신호의 사례들을 세는 데 사용된다.

[0124] 블록(356)에서, 상기 프로세스(350)는 도 2의 POSCOMP 신호(182a)의 상태가 상기 프로세스(350)가 블록(356)으로 진입하였던 최후의 시간 아래로 변화하였는지를 확인한다.

[0125] 상기 POSCOMP 신호의 상태의 변화가 없었을 경우, 그러면 상기 프로세스는 상기 렌 윈도우 내에 상기 DIFF 신호가 존재하는지를 결정하는 블록(358)으로 진행한다. 블록(358)에서, 상기 DDIFF 신호가 상기 렌 윈도우의 위나 아래의 외측에 있을 경우, 상기 프로세스는 블록(360)으로 진행한다.

[0126] 블록(360)에서, 상기 피크 계수기에 의해 유지된 값들이 0 또는 1일 경우, 예를 들면 도 1의 오프셋 조절 신호들(114c, 114e)의 하나 또는 모두가 관련된 DDIFF 신호를 상기 렌 윈도우를 향해 이동시키기 위해 조절되는 바와 같이 상기 프로세스는 상기 AOA 제어 신호가 조절되는 블록(362)으로 진행하고, 상기 프로세스는 블록들(356)로 돌아간다.

[0127] 블록(356)에서, 상기 POSCOMP 신호의 상태의 변화가 있었을 경우, 그러면 상기 프로세스는 상기 DDIFF 신호가

상기 POSCOMP 신호의 상태의 최후의 스위치로 인하여 상기 런 윈도우를 초과하는지와 AGC 조절이 없었던지 확인하는 블록(368)으로 진행한다. 상술한 바가 참일 경우, 상기 프로세스는 피크 계수기가 1 증가하는 블록(369)으로 진행한다. 상기 프로세스는 이후에 블록(356)으로 돌아간다.

- [0128] 블록(360)에서, 상기 피크 계수기가 1보다 더 큰 값을 유지할 경우, 상기 프로세스는, 예를 들면 도 1의 이득 제어 신호들(114d, 114f)의 하나 또는 모두가 상기 런 윈도우를 향해 관련된 DDIFF 신호를 이동시키기 위해 감소되는 바와 같이 AGC 제어 신호가 증가하는(보다 낮은 이득) 블록(364)으로 진행된다. 블록(366)에서 상기 AOA는 또한 블록(364)에서 수행된 상기 AGC 조절에 따라 조절된다. 상기 프로세스는 이후에 블록(354)으로 돌아간다.

- [0129] 블록(368)에서, 블록(368)의 상술한 조건이 참이 아닐 경우, 그러면 상기 프로세스는 블록(354)으로 돌아간다.

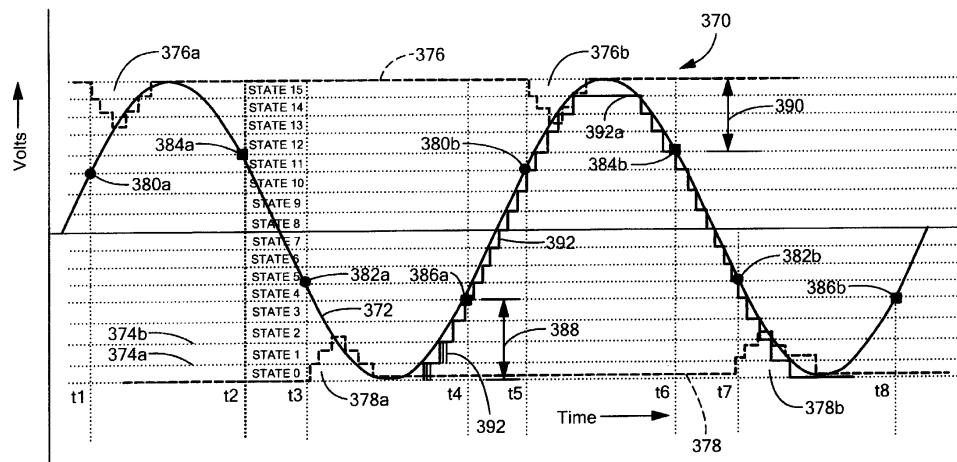

- [0130] 도 7을 참조하면, 그레프는 볼트의 전압 단위들을 갖는 수직 축과 시간의 임의의 단위들을 갖는 수평 축을 가진다. 신호(372)는 DIFF 신호를 나타내며, 예를 들면 도 1의 R\_DIFF 신호(108a) 또는 L\_DIFF 신호(124a) 중에서 하나를 나타낸다. 상기 신호(372)는 또한 DDIFF 신호를 나타내고, 예를 들면 도 1의 R\_DDIFF 신호(110a) 또는 L\_DDIFF 신호(126a) 중에서 하나를 나타내지만, 아날로그 형식이다. 보다 구체적으로는, 상기 신호(372)는 도 2의 IDDIFF 신호(154a)를 나타낼 수 있다.

- [0131] 상기 신호(372)는 그 상태들(374a, 374b)을 나타내는 도 7의 상태(STATE) 0으로부터 상태(STATE) 15까지로 확인되는 복수의 상태들을 통과한다. 각각의 상태는 DIFF 신호(아날로그 신호)에 관련된 값들의 아날로그 범위를 나타내는 값들의 범위를 나타내며, DDIFF 신호(디지털 신호)에 관련된 값들의 디지털 범위도 나타내는 값들의 디지털 범위를 나타낸다. 상기 값들의 디지털 범위들은, 순서대로, 상기 DDIFF 신호의 값들의 아날로그 범위들을 가리킨다.

- [0132] 상태 0으로부터 상태 15까지 관련된 값들(상기 DIFF 신호, 상기 DDIFF 신호 또는 상기 IDDIFF 신호의 피크-투-피크 범위의 퍼센티지에서)의 예시적인 범위들은 도 2의 요소(180b)로서 확인된다.

- [0133] 상태 신호(392)는 상기 DIFF 신호가 시간에 따라 나뉘어져 도 2의 상태 신호(174a)와 동일하거나 유사하게 되는 상태들을 나타낸다. 따라서 도시된 바와 같이 상기 DIFF 신호(372)는 일부 시간들에서 상태 0 내에, 다른 시간들에서 상태 1 내에 있는 등과 같이 있게 된다. 상기 DIFF 신호(372)에서 상태 15가 구현되고 요소(392a)로서 확인되는 점을 이해할 수 있을 것이다. 상기 DIFF 신호(372)는 상태 15(374a)에서 라인 상부에 계속될 수 있고, 상기 DIFF 신호(372)는 상기 DIFF 신호가 상태 15(372a) 아래로 떨어질 때까지 상태 15(392a) 내에 여전히 있게 된다.

- [0134] 범위들(376a, 376b)을 갖는 신호(376)는 도 2의 PPEAK 신호(158a)를 나타낸다. 범위들(378a, 378b)을 포함하는 신호(378)는 도 2의 NPEAK 신호(160a)를 타나낸다. 상기 PPEAK 신호(376)는 일반적으로 상기 DIFF 신호(372)의 양의 피크의 진폭을 나타내는 값을 유지한다. 상기 NPEAK 신호(378)는 일반적으로 상기 DIFF 신호(372)의 음의 피크의 진폭을 나타내는 값을 유지한다.

- [0135] 상기 범위들(376a, 376b)은 도 2의 로직(156)과 비교기(166)의 동작 방식에 의해 상기 PPEAK 신호(376)가 상기 DIFF 신호(372)를 다시 얻도록 계산하거나 그렇지 않으면 하방으로 전환하고, 이후에 상기 DIFF 신호(372)의 양의 피크를 얻도록 계산하거나 다시 상방으로 전환되는 시간들을 나타낸다.

- [0136] 지점들(points)(380a, 380b)은 10번째 상태인 상태 10으로부터 11번째 상태인 상태 11까지 전환하는 상기 DIFF 신호를 나타낸다. 지점들(382a, 382b)은 5번째 상태인 상태 5로부터 4번째 상태인 상태 4까지 전환하는 상기 DIFF 신호를 나타낸다.

- [0137] 상기 범위들(376a, 376b)의 시작이 각기 상기 지점들(380a, 380b)과 일치하는 점은 명백해질 것이다. 또한 상기 범위들(376a, 376b)의 시작이 각기 상기 지점들(382a, 382b)과 일치하게 되는 점이 분명해질 것이다. 도 7a와 관련된 다음의 논의로부터 상기 지점들(380a, 380b, 382a, 382b)이 상기 POCOMP 신호의 전환들과 일치하는 점도 명백해질 것이다.

- [0138] 지점들(384a, 384b)은 상기 DIFF 신호가 상태 15로부터 상태 15 아래의 4 상태들까지 변화하는, 즉 상태 차이(390)로 나타낸 상태 11까지의 변화를 나타낸다. 지점들(386a, 386b)은 상기 DIFF 신호가 상태 0으로부터 상태 0 위의 4 상태들까지 변화하는, 즉 상태 차이(388)에 의해 나타낸 상태 4로의 변화를 나타낸다. 도 7a와 관련된 다음의 논의로부터 상기 지점들(384a, 384b, 386a, 386b)도 상기 POSCOMP\_PK 신호의 전환들과 일치하는 점이 분명해 질 것이다.

- [0139] 상태 채터(392)에 의해 정형화된 일부 상태 채터(부적절한 상태 전환들)는 상태 전환들 동안에 나타날 수 있다. 상태 전환 채터는 도 2의 STATE\_SM 신호(174a)와 관련된다. 상기 상태 전환 채터는 후술하는 프로세스에 의한 도 2의 상태 피크 로직 모듈(176)에 의해 본질적으로 감소되거나 소거되어, 감소된 상태 채터를 갖거나 상태 채터를 갖지 않는 도 2의 STATE\_PEAK 신호(176a)를 야기한다.

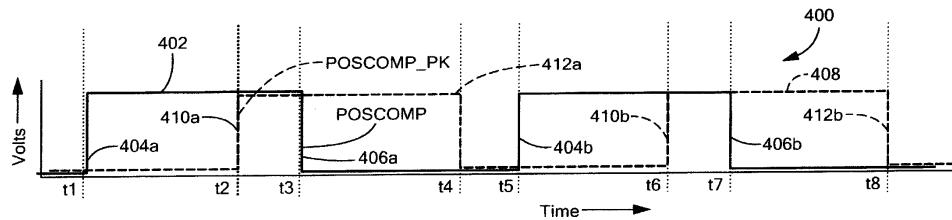

- [0140] 다시 도 7a를 참조하면, 그래프(400)는 볼트의 전압의 단위들을 갖는 수직 축과 도 7의 수평 축에 대해 시간으로 정렬되는 임의의 시간의 단위들을 갖는 수평 축을 포함한다.

- [0141] 신호(402)는 도 2의 POSCOMP 신호(182a)를 나타낸다. 상술한 바와 같이, 상기 POSCOMP 신호(402)의 전환들(404a, 404b 및 406a, 406b)은 상기 상태 전환들 및 도 7의 관련된 지점들(380a, 380b 및 382a, 382b)과 일치하고, 상기 상태 전환들 및 도 7의 관련된 지점들(380a, 380b 및 382a, 382b)에 기인한다(도 2의 디코더(182)를 통해).

- [0142] 가상의 라인들로 나타낸 신호(408)는 도 10과 관련하여 다음에 기재되는 프로세스 동안에 발생되는 도 2의 POSCOMP\_PK 신호(178)를 나타낸다. 전술한 바와 같이, POSCOMP\_PK 신호(408)의 전환들(410a, 410b 및 412a, 412b)은 상기 상태 전환들 및 도 7의 관련된 지점들(384a, 384b 및 386a, 386b)과 일치하고, 상기 상태 전환들 및 도 7의 관련된 지점들(384a, 384b 및 386a, 386b)에 기인한다(도 10의 프로세스를 통해).

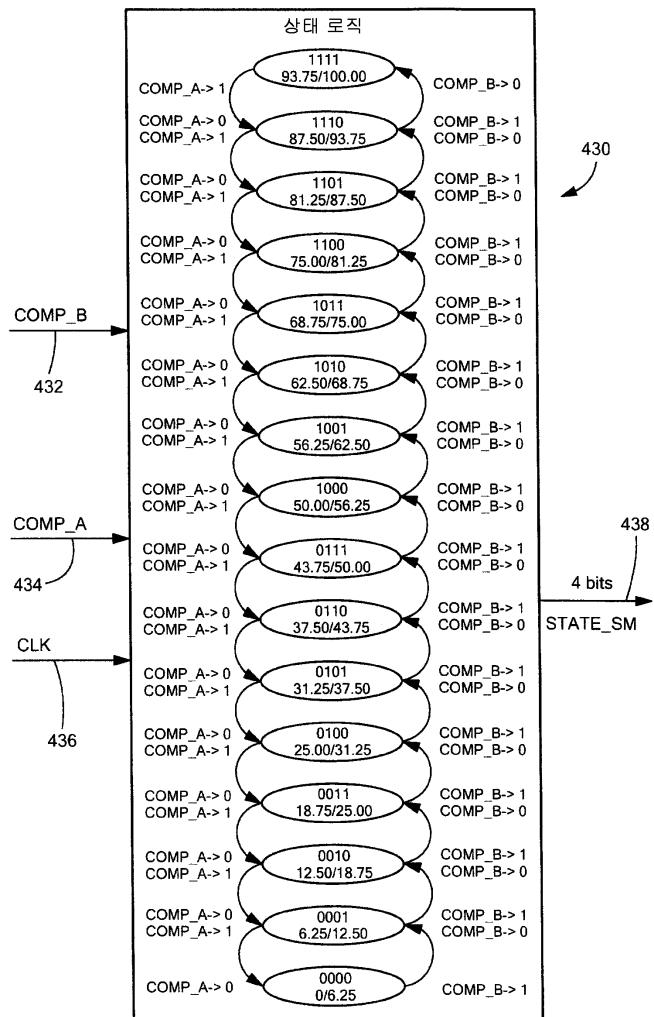

- [0143] 도 8을 참조하면, 도 7의 상태 전환은 상태 로직 모듈(430) 내에 상태 도표 형식(state diagram format)으로 도시되며, 이는 도 2의 상태 로직 모듈(174)과 동일하거나 유사할 수 있다. 상기 상태 로직 모듈(430)은 COMP\_A 신호(434), COMP\_B 신호(432) 및 클록 신호(436)를 수신하며, 이들은 도 2의 COMP\_A 신호(172a), COMP\_B 신호(170a) 및 클록 신호(184a)와 동일하거나 유사할 수 있다.

- [0144] 각 버블들(bubbles) 내에 0 내지 15의 상태 숫자들이 각기 도시되어 있지만, 도 2의 예시적인 값의 범위들(180b)에 따라 각각의 상태의 관련되는 값의 한계들을 따른 이진수 형태이다. COMP\_A 및 COMP\_B 신호 상태들은 상태 로직 모듈(430) 내에 도시된다.

- [0145] 상기 COMP\_B 신호(432)의 상태의 전환들에 의해 상기 로직 전환들은 0에서부터 1까지 상향된다. 상기 로직 전환들 상기 COMP\_A 신호의 상태의 전환들에 의해 0으로부터 1까지 하향된다.

- [0146] 상기 상태 로직 프로세서(430)는 도 2의 STATE\_SM 신호(174a)와 동일하거나 유사할 수 있는 STATE\_SM 신호(438)를 발생시키도록 구성된다.

- [0147] 상기 상태 전환들은 상술한 채터를 포함할 수 있으며, 이는 적절한 상태가 구현될 때까지 전후로 첫 번째로 한 방향(상방 또는 하방)을 따르고 이후에 다른 방향을 따르는 전환으로 나타내어 질 수 있다. 상기 상태 채터는, 예를 들면 상기 COMP\_A 신호(434) 및/또는 상기 COMP\_B 신호(432) 상의 노이즈로부터 일어날 수 있으며, 이는, 예를 들면 도 2의 IDDIFF 신호(126a) 상의 노이즈로부터 일어날 수 있다.

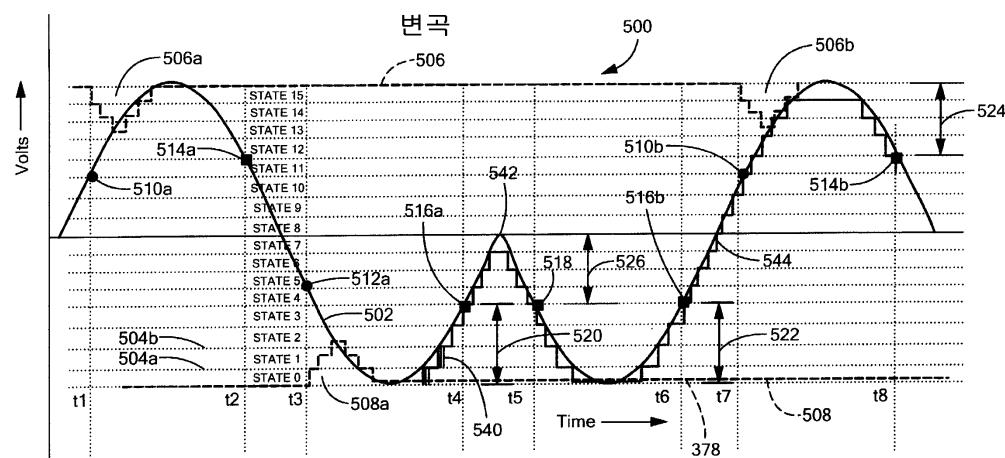

- [0148] 도 9를 참조하면, 그래프(500)는 볼트의 전압 단위들로 나타낸 수직축과 시간의 임의의 단위들로 나타낸 수평축을 가진다. 신호(502)는 DIFF 신호, 예를 들면 도 1의 R\_DIFF 신호(108a) 또는 L\_DIFF 신호(124a) 중에서 하나를 나타낸다. 상기 신호(502)는 또한 DDIFF 신호, 예를 들면 도 1의 R\_DDIFF 신호(110a) 또는 L\_DDIFF 신호(126a) 중에서 하나를 나타낸다.

- [0149] 도 7에서와 같이, 상기 신호(502)는 도 7의 상태 0에서 상태 15까지로 확인되는 상태들(504a, 504b)이 대표적인 복수의 상태들을 통과한다. 각 상태는 값들의 범위를 나타내고, 이는 DIFF 신호(아날로그 신호)와 관련하여 값들의 아날로그 범위를 나타내며, DDIFF 신호(디지털 신호)와 관련하여 값들의 디지털 범위를 나타내고, IDDIFF 신호(디지털 신호)와 관련하여 값들의 디지털 범위도 나타낸다. 상기 값들의 디지털 범위들은 차례로 상기 DIFF 신호의 값들의 아날로그 범위들을 나타낸다.

- [0150] 전술한 바와 같이, 상태 0에서 상태 15와 관련된 값들의 예시적인 범위들(상기 DIFF 신호, 상기 DDIFF 신호 또는 상기 IDDIFF 신호의 피크-투-피크 범위의 퍼센티지들)은 도 2의 요소(180b)로 확인된다.

- [0151] 상태 신호(544)는 상기 DIFF 신호가 시간에 따라 하락하고, 도 2의 STATE\_SM 신호(174a)와 동일하거나 유사해지는 상태들을 나타낸다. 따라서 상기 DIFF 신호(502)는 상태 0의 일부 시간들에서, 상태 1의 다른 시간들에서 등과 같이 도시된다. 상기 DIFF 신호(502)는 DIFF 신호(502)의 중간-사이클 변화(mid-cycle change)를 나타내는 변곡(inflexion)(542)을 가지는 점에서 도 7의 DIFF 신호(372)와 다르며, 변곡(542)은, 예를 들면 도 1의 물체(100)의 회전 방향 변화와 같은 방향 변화로부터 일어날 수 있거나, 물체(100)의 회전 진동으로부터 일어날

수 있다.

- [0152] 범위들(506a, 506b)을 갖는 신호(506)는 도 2의 PPEAK 신호(158a)를 나타낸다. 범위(508a)를 포함하는 신호(508)는 도 2의 NPEAK 신호(160a)를 나타낸다. 상기 PPEAK 신호(506)는 일반적으로 상기 DIFF 신호(502)의 양의 피크의 진폭을 나타내는 값을 유지한다. 상기 NPEAK 신호(508)는 일반적으로 상기 DIFF 신호(502)의 음의 피크의 진폭을 나타내는 값을 유지한다.

- [0153] 상기 범위들(506a, 506b)은, 도 2의 로직(156) 및 비교기(164)의 작동에 의하여 상기 DIFF 신호(502)를 다시 수득하도록 상기 PPEAK 신호(506)가 계산하거나 그렇지 않으면 전환들이 하향되고, 이후에 상기 DIFF 신호(502)를 얻도록 계산하거나 그렇지 않으면 전환들이 상향되는 시간들을 나타낸다. 이와 유사하게, 상기 범위(508a)는, 도 2의 로직(162) 및 비교기(166)의 작동에 의하여 상기 DIFF 신호(502)를 다시 얻도록 상기 NPEAK 신호(508)가 계산하거나 그렇지 않으면 전환들이 상향되고, 이후에 상기 DIFF 신호(502)의 음의 피크를 수득하도록 계산하거나 그렇지 않으면 전환들이 하향된다.

- [0154] 지점들(510a, 510b)은 상기 열 번째 상태인 상태 10으로부터 상기 열한 번째 상태인 상태 11까지 전환되는 상기 DIFF 신호(502)를 나타낸다. 지점(512a)은 상기 다섯 번째 상태인 상태 5로부터 상기 네 번째 상태인 상태 4까지 전환되는 DIFF 신호(502)를 나타내지만, 상기 포인트(510a) 후에서만이다.

- [0155] 상기 범위들(506a, 506b)의 시작들이 각기 상기 지점들(510a, 510b)과 일치하는 점은 명확해질 것이다. 상기 범위(508a)의 시작이 상기 지점(512a)과 일치하는 점 또한 분명해질 것이다. 도 9a와 관련하여 다음에 논의하는 바로부터 상기 지점들(510a, 512a, 510b)이 상기 POSCOMP 신호의 전환들과 일치하는 점이 분명해질 것이다.

- [0156] 지점들(514a, 514b)은, 상태 15로부터 4개의 상태들 아래인 상태 11까지 상태들을 변화시키는, 즉 상태 차이(524)로 나타나는 상태 11까지 변화시키는 상기 DIFF 신호(502)를 나타낸다. 지점들(516a, 516b)은, 상태 0으로부터 상태 0 위의 2개의 상태들인 상태를 갖도록, 즉 상태 차이들(520, 522)로 나타나는 상태 4까지 변화시키는 상기 DIFF 신호(502)를 나타낸다. 상기 지점들(514a, 514b, 516a, 516b)이 또한 상기 POSCOMP\_PK 신호의 전환들과 일치하는 점은 도 9a와 관련된 다음의 논의로부터 명확해질 것이다.

- [0157] 추가적인 지점(518)은, 상태 8로부터 상태 8의 4개의 상태들 아래까지 변화, 즉 상태 차이(526)로 나타나는 상태 4까지 변화하는 상기 DIFF 신호(502)를 나타낸다. 상기 지점들(514a, 514b, 518)이 각기 상기 상태 신호(544)가 4개의 상태들에 의해 감소할 때의 시간을 나타내는 점을 이해할 수 있을 것이다. 상기 지점들(516a, 516b)은 각기 상기 상태 신호(544)가 4개의 상태들에 의해 증가되는 때의 시간을 나타낸다.

- [0158] 상기 지점(518)이 또한 상기 POSCOMP\_PK 신호의 전환과 일치하는 점은 도 9a와 관련된 다음의 논의로부터 명확해질 것이다.

- [0159] 상태 채터(540)로 정형화된 일부 상태 채터들(부적절한 상태 전환들)은 상태 전환들 동안에 존재할 수 있다. 상태 전환 채터는 도 2의 STATE\_SM 신호(174a)와 연관된다. 상기 상태 전환 채터는 다음에 설명하는 프로세스에 의해 도 2의 상태 피크 로직 모듈(176)에 의하여 본질적으로 감소되거나 소거되어, 도 2의 STATE\_PEAK 신호(176a) 내에 감소된 상태 채터를 갖거나 상태 채터가 없게 된다.

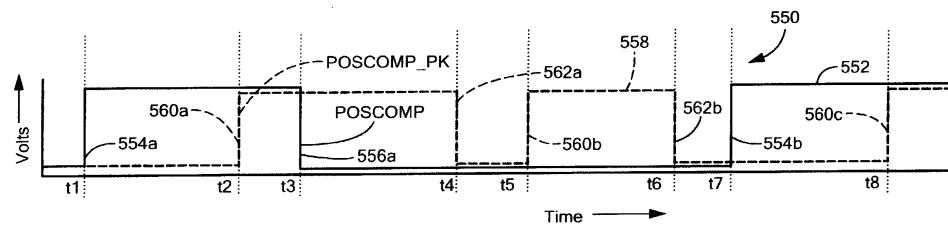

- [0160] 도 9a를 참조하면, 그래프(550)는 볼트로 전압의 단위들로 나타낸 수직축과 도 9의 수평축에 대해 시간으로 정렬된 시간의 임의의 단위들로 나타낸 수평축을 가진다.

- [0161] 신호(552)는 도 2의 POSCOMP 신호(182a)를 나타낸다. 전술한 바와 같이, 상기 POSCOMP 신호(502)의 전환들(554a, 554b, 555a)은 상기 상태 전환들 및 도 9의 관련된 지점들(510a, 510b, 512a)과 일치하고, 상기 상태 전환들 및 도 9의 관련된 지점들(510a, 510b, 512a)에 기인한다(도 2의 디코더(182)를 통해).

- [0162] 가상의 라인들로 도시한 신호(558)는 도 2의 POSCOMP\_PK 신호(178)를 나타내고, 도 10과 관련하여 후술하는 프로세스 동안 발생된다. 전술한 바와 같이, POSCOMP\_PK 신호(558)의 전환들(560a, 560b, 560c, 562a, 562b)은 상태 전환들 및 도 9의 관련된 지점들(514a, 518, 514b, 516a, 516b)과 일치하고, 상태 전환들 및 도 9의 관련된 지점들(514a, 518, 514b, 516a, 516b)에 기인한다(도 10의 프로세스를 통해).

- [0163] 도 10 내지 도 17은 진동을 확인하는데 사용되는 프로세스들을 나타낸다. 여기서 기술되는 분할(partitioning)에 있어서, 이러한 프로세스들은 도 1의 진동 프로세스(116)와 동일하거나 유사할 수 있는 도 3의 진동 프로세서(200) 내에 도시된 다양한 진동 서브-프로세서들(204 내지 226)에 의해 수행된다. 그러나 여기서 나타낸 상기 분할은 도시의 명확성을 위하여 단지 하나의 예시적인 기능들의 분할임을 이해할 수 있을 것이다. 도 3의 진동 서브-프로세서들(202-226) 중에서 임의의 하나는 도 1의 다른 블록 내에, 예를 들면 도 1의 AOA/AGC 프로세서

(114) 내에 또는 도 1의 상태 프로세서들(112, 128) 내에 구현될 수 있다.

[0164] 도 10 내지 도 17의 프로세스들 중에서 각각의 하나는 "시작" 블록에서 시작된다. 상기 시작 블록은 도 1의 모션 센서(102)가 처음으로 전원이 인가되는 때의 시간, 또는 그 후의 임의의 시간, 예를 들면 도 5의 프로세스에 의해 정형화되는 상기 보정 모드의 끝부분에서의 시간을 나타낼 수 있다.

[0165] 상술한 바와 같이, 도 3의 채널 진폭 차 프로세서(202)에 의해 수행되는 프로세스들은 도 5의 프로세스(300)에 의해 정형화되고, 특히 도 5의 블록들(324 내지 330)에 의해 정형화된다.

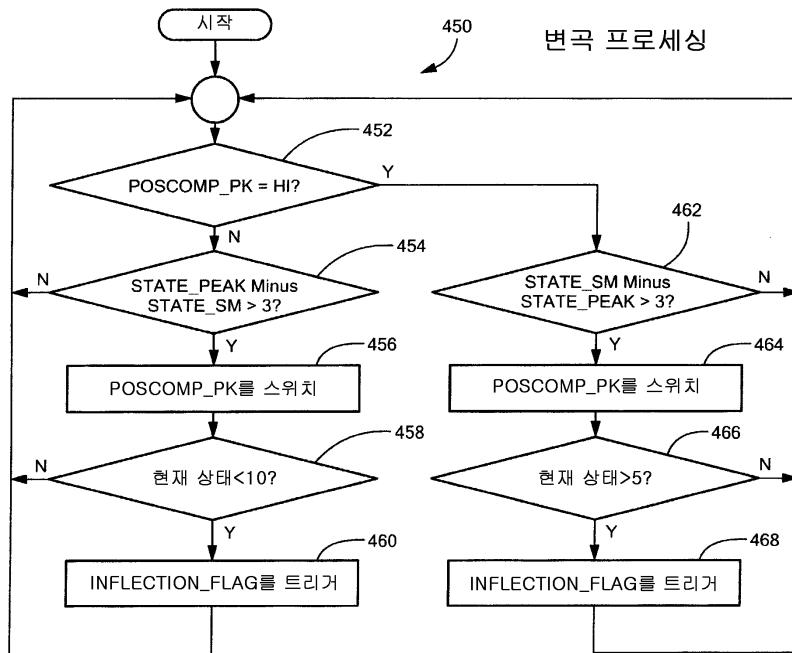

[0166] 도 10을 참조하면, 예시적인 프로세스(450)는 도 3의 우측 변곡 프로세서(204)에 의하여 우측 채널(예를 들면, 도 1 참조)을 위해 수행될 수 있다. 상기 예시적인 프로세스(450)는 또한 도 3의 좌측 변곡 프로세서(206)에 의해 좌측 채널(예를 들면, 도 1 참조)을 위해 수행될 수 있다. 상기 두 채널들의 동작은 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(450)는 좌측 또는 우측 채널 중에서 하나에 대하여 다음에 설명된다. 상기 프로세스(450)는 오류 상태(fault condition) 또는 진동을 나타내는 변곡과 이에 따른 도 1의 물체(100)의 방향 변화를 확인하는 데 사용된다. 상기 프로세스(450)는 또한 상기 POSCOMP\_PK 신호의 전환들을 야기한다.

[0167] 상기 프로세스(450)는 변곡들, 예를 들면 도 9의 변곡(542)을 확인에 관련되며, 상기 변곡들은, 예를 들면 도 1의 물체(100)의 회전 방향의 명확한 변화와 같은 방향의 명확하거나 실제 변화에 의해 야기되는 상기 DIFF 신호, 상기 DDIFF 신호 및/또는 상기 IDDIFF 신호들의 변화들이다. 상기 방향의 분명한 변화는 물체(100)의 진동에 기인할 수 있다. 상기 방향의 명백한 변화는 도 9 및 도 9a와 관련하여 앞에서 도시한 바와 같이, 상기 DIFF 신호, 상기 DDIFF 신호 및 상기 IDDIFF 신호들의 위상의 급작스러운 변화에 의해서 정형화되는 경향이 있다.

[0168] 상기 프로세스(450)는 상기 POSCOMP\_PK 신호(예를 들면, 도 1의 POSCOMP\_PK 신호, 도 2의 POSCOMP\_PK 신호(178), 도 3의 POSCOMP\_PK 신호들 또는 도 9a의 POSCOMP\_PK 신호(558))가 높은지를 확인할 수 있는 블록(452)에서 시작된다. 상기 POSCOMP\_PK 신호가 높지 않을 경우(즉, 낮을 경우), 그러면 상기 프로세스는 블록(454)으로 진행한다.

[0169] 블록(454)에서, 예를 들면 도 2의 STATE\_PEAK 신호(176a)와 같은 STATE\_PEAK 신호로부터, 예를 들면 도 2의 STATE\_SM 신호(174a)와 같은 도 9의 상태 신호(544)에 의해 나타나는 STATE\_SM 신호를 감한 것이 3보다 큰지를 확인한다. 달리 말하면, 이들의 상태들이 4 또는 그 이상으로 다르게 된다. 상기 STATE\_PEAK 신호의 발생은 도 17과 관련하여 다음에 보다 상세하게 설명된다. 여기서는 적어도 4 상태들의 차이가 도 9의 상태 차이들(524, 526)에 의해 나타나는 것으로 말하면 충분하다.

[0170] 상기 상태 차이가 3 보다 클 경우, 상기 프로세스는 상기 POSCOMP\_PK 신호가 대향되는 상태(opposite state), 즉 높은 상태로 스위치되는 블록(456)으로 진행한다(예를 들면, 도 9a의 에지(560b)와 관련된 도 9의 지점(518) 참조).

[0171] 블록(458)에서, 상기 STATE\_SM 신호에서 확인된 현재의 상태가 10보다 작거나 같은 경우, 그러면 상기 프로세스는, 도 3의 변곡 플래그 신호들(inflection flag signals) 중에서 하나와 동일하거나 유사할 수 있는 INFLECTION\_FLAG 신호가 트리거(trigger)되는 블록(452)으로 진행한다. 이후에 상기 프로세스(450)는 블록(452)으로 돌아간다.

[0172] 여기서 사용되는 바에 있어서, "트리거된다(triggered)"라는 용어는 플래그 신호가 그 최초 상태로 되돌아간 후에 플래그 신호의 상태의 순간적인 변화를 언급한다. 트리거된 상태는, 예를 들면 도 2의 클록 신호(184a)의 하나의 사이클 동안 존재할 수 있다.

[0173] 블록(452)에서, 상기 POSCOMP\_PK 신호가 높을 경우, 그러면 상기 프로세스는 STATE\_SM 신호에서 상기 STATE\_PEAK 신호를 감한 것이 3보다 큰지를 확인하는 블록(462)으로 진행한다. 달리 말하면, 이들의 상태들이 4 또는 그 이상으로 다르다.

[0174] 상기 상태 차이가 3보다 클 경우, 상기 프로세스는 상기 POSCOMP\_PK 신호가 대향되는 상태, 즉 낮은 상태로 스위치되는 블록(464)으로 진행한다(예를 들면, 도 9a의 에지(562b)와 관련된 도 9의 지점(516b) 참조).

[0175] 블록(466)에서, 상기 STATE\_SM 신호에서 확인되는 현재 상태가 5보다 클 경우, 그러면 상기 프로세스는 상기 INFLECTION\_FLAG 신호가 트리거되는 블록(468)으로 진행하며, 상기 프로세스(450)는 블록(452)으로 돌아간다.

[0176] 블록들(454, 458, 462, 466)에서, 나타난 조건들이 잘못된(false) 경우, 그러면 상기 프로세스는 블록(452)으로

돌아간다.

[0177] 상기 POSCOMP\_PK 신호의 에지들이 상기 프로세스(450)의 결과임을 인지할 수 있을 것이다.

[0178] 상기 프로세스(450)는 계속하여 변곡들을 위해 상기 DDIFF 또는 상기 IDDIFF 신호들을 스캔할 수 있으며, 변곡이 검출될 경우에 상기 우측 또는 좌측 채널의 상기 INFLECITON\_FLAG를 트리거한다. 상기 프로세스(450)는 계속적으로 상기 POSCOMP\_PK 신호를 발생시킬 수 있다.

[0179] 도 11을 참조하면, 예시적인 프로세스(570)는 도 3의 방향 변화 프로세서(208)에 의해 수행될 수 있다. 상기 프로세스(570)는 상기 두 채널들인 우측 및 좌측 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(570)는 양쪽 채널 모두에 대하여 다음에서 설명된다. 일반적으로, 도 1의 R\_POSCOMP 신호(112a)와 도 1의 L\_POSCOMP 신호(128a) 사이의 상대적 위상(플러스 또는 마이너스)이 도 1의 물체(100)의 회전 방향을 나타내고, 상기 상대적 위상의 변화, 특히 상대적 위상의 사인(sign)의 변화는 물체(100)의 회전 방향의 변화를 나타내는 점을 인식할 수 있을 것이다. 상기 프로세스(570)는 오류 상태 또는 진동을 나타내는 도 1의 물체(100)의 방향 변화를 확인하는 데 이용된다.

[0180] 상기 프로세스(570)는 블록(572)에서 시작되며, 여기서 에지가 L\_POSCOMP 신호에 검출되는 경우에는 상기 프로세스(570)는 블록(574)으로 진행한다.

[0181] 블록(574)에서, 이동의 검출된 방향(R\_POSCOMP 신호와 L\_POSCOMP 사이의 위상 사인)이 상기 L\_POSCOMP 신호의 최후의 에지 아래로 변했을 경우, 그러면 상기 프로세스는 블록(576)으로 진행한다.

[0182] 블록(576)에서, 상기 우측 및 좌측 채널들 모두를 위한 "방향 확인 에지 계수기(direction validation edge counter)"가 0 보다 큰지가 결정된다. 상기 방향 확인 에지 계수기는 도 19 내지 도 19b의 블록(1022)과 관련하여 설명된다. 기본적으로, 상기 방향 확인 에지 계수기는 도 19 내지 도 19b의 프로세스에 의해 상기 우측 또는 좌측 채널 중에서 하나에서 검출되는 진동이 있을 때에 0으로 리셋된다.

[0183] 블록(576)에서, 상기 L\_POSCOMP 에지가 첫 번째 에지일 경우, 그러면 상기 프로세스는 블록(578)으로 진행한다.

[0184] 블록(578)에서, 상기 L\_POSCOMP 신호 및 상기 R\_POSCOMP 신호가, 예를 들면 도 16의 프로세스로 모두 확인되었는지가 결정된다. 모두 확인되었을 경우, 도 3의 POSCOMP\_OK\_FLAGS가 모두 설정될 것이다. 모두가 확인되었을 경우, 상기 프로세스는 블록(580)으로 진행한다.

[0185] 블록(580)에서, 상기 우측 및 좌측 채널들 모두에 충분한 진폭이 있는지가 결정된다. 이러한 결정은 다양한 방식들로 이루질 수 있다. 특정한 일 실시예에 있어서, 상기 PPEAK 신호(도 2의 158a)와 상기 NPEAK 신호(도 2의 160a) 사이의 차이들은 소정의 슬레이蚀와 비교될 수 있다.

[0186] 블록(580)에서 양 채널의 상기 진폭이 충분히 높은지가 결정되는 경우, 상기 프로세스는 도 3의 DIR\_CHANGE\_FLAG 신호가 트리거되고 상기 프로세스가 블록(572)으로 돌아가는 블록(582)으로 진행한다.

[0187] 블록(572)에서, L\_POSCOMP 에지가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(584)으로 진행하고, 여기서 상기 R\_POSCOMP 신호 내에 에지가 검출되는 경우에 상기 프로세스(570)는 블록(586)으로 진행한다.

[0188] 블록(586)에서, 이동의 검출된 방향(R\_POSCOMP 신호와 L\_POSCOMP 신호 사이의 위상의 사인)이 상기 R\_POSCOMP 신호의 최후의 에지 아래로 변화되었을 경우, 그러면 상기 프로세스는 블록(576)으로 진행한다.

[0189] 블록(584)에서 R\_POSCOMP 에지가 존재하지 않을 경우(그리고 L\_POSCOMP 에지가 존재하지 않을 경우), 그러면 상기 프로세스(570)는 블록(588)으로 진행한다.

[0190] 블록(588)에서, 상기 다른 채널 상에 POSCOMP 또는 POSCOMP\_PK 에지가 없이 하나의 채널 상에 세 POSCOMP 및 POSCOMP\_PK 에지들의 결합된 총합이 존재하였는지가 결정된다. 이러한 조건이 사실일 경우, 그러면 상기 프로세스는 상기 DIR\_CHANGE\_FLAG 신호가 트리거되는 블록(582)으로 진행한다. 이러한 조건이 오류인 경우, 그러면 상기 프로세스(570)는 블록(572)으로 돌아간다.

[0191] 상기 블록들(574 내지 580, 586 또는 588) 중에서 임의의 하나의 조건들이 오류일 경우, 그러면 상기 프로세스는 블록(572)으로 돌아간다.

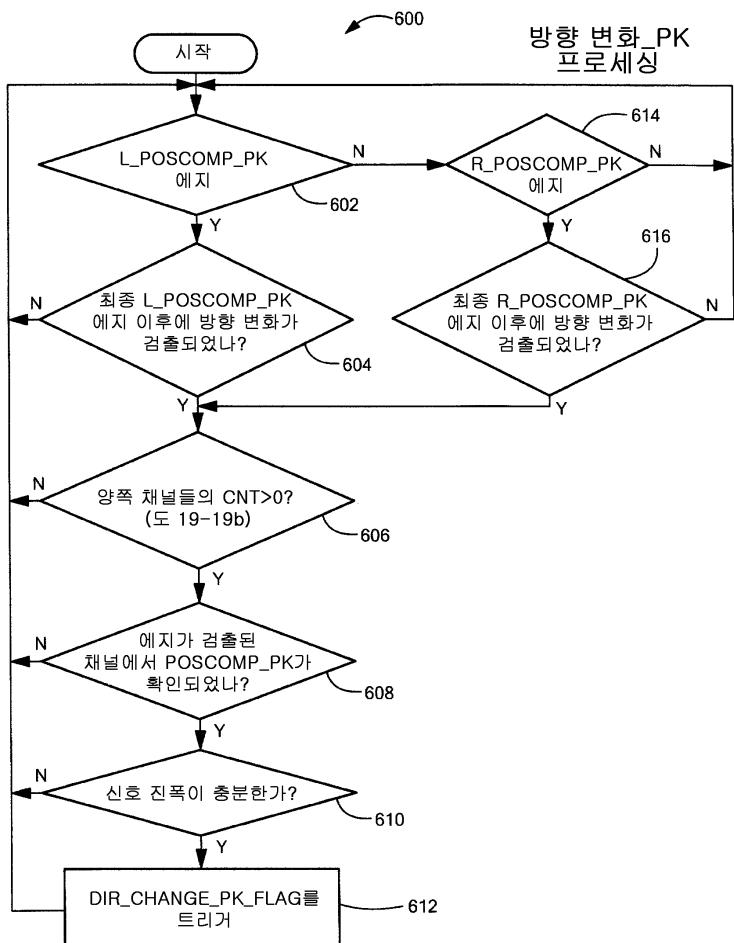

[0192] 도 12를 참조하면, 예시적인 프로세스(600)는 도 3의 방향 변화\_PK 프로세서(210)에 의해 수행될 수 있다. 상기 프로세스(600)는 우측 및 좌측인 상기 두 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(600)는 모든 채널들에 대하여 다음에 설명된다. 상기 프로세스(600)는 오류 상태나 진동을 나타는 도 1의 물체

(100)의 방향의 변화를 확인하는 데 사용된다.

- [0193] 상기 프로세스는 블록(602)에서 시작하고, 여기서 상기 L\_POSCOMP\_PK 신호에 에지가 검출되는 경우, 상기 프로세스(600)는 블록(604)으로 진행한다.

- [0194] 블록(604)에서, 이동의 검출된 방향(R\_POSCOMP 신호와 L\_POSCOMP 신호 사이의 위상의 사인)이 상기 L\_POSCOMP\_PK 신호의 최후의 에지 아래로 변화되었을 경우, 그러면 상기 프로세스(600)는 블록(606)으로 진행한다.

- [0195] 블록(604)에서, "상기 방향 확인 에지 계수기"가 상기 에지가 검출되었던 상기 채널을 위해 0 보다 큰지가 결정된다. 상기 방향 진동 에지 계수기는 도 19 내지 도 19b의 블록(1022)과 관련하여 설명된다.

- [0196] 블록(606)에서, 도 19 내지 도 19b의 방향 확인 계수기(CNT)가 상기 에지가 검출되었던 상기 채널을 위하여 0보다 큰 경우, 그러면 상기 프로세스(600)는 블록(608)으로 진행한다.

- [0197] 블록(608)에서, 상기 POSCOMP\_PK 신호가, 상기 에지가 블록들(602 또는 604)에서 검출되었던 우측 또는 좌측인 상기 채널을 위해 확인되었는지(POSCOMP\_PK\_OK\_FLAG 세트, 도 3 참조)가 결정된다.

- [0198] 블록(610)에서, 상기 우측 및 좌측 채널들 모두에 충분한 진폭이 있는지가 결정된다. 이러한 결정은 다양한 방식으로 이루어질 수 있다. 특정한 일 실시예에 있어서, 상기 PPEAK 신호(도 2의 158a)와 상기 NPEAK 신호(도 2의 160a) 사이의 차이들이 소정의 스퍼레이드와 비교될 수 있다.

- [0199] 블록(610)에서 모든 채널들의 진폭이 충분히 높은지가 결정될 경우, 상기 프로세스는 블록(612)으로 진행하고, 여기서 도 3의 DIR\_CHAGE\_PK\_FLAG 신호가 트리거되고, 상기 프로세스가 블록(602)으로 돌아간다.

- [0200] 블록(602)에서, L\_POSCOMP\_PK 에지가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(614)으로 진행하고, 여기서 상기 R\_POSCOMP\_PK 신호에 에지가 검출되는 경우, 상기 프로세스(600)는 블록(616)으로 진행한다.

- [0201] 블록(616)에서, 이동의 검출된 방향(R\_POSCOMP 신호와 L\_POSCOMP 사이 위상의 사인)이 상기 R\_POSCOMP\_PK 신호의 최후의 에지 아래로 변화되었는지가 결정될 경우, 그러면 상기 프로세스는 블록(608)으로 진행한다.

- [0202] 블록(614)에서 R\_POSCOMP\_PK 에지가 없을 경우(그리고 L\_POSCOMP\_PK 에지가 없을 경우), 그러면 상기 프로세스(600)는 블록(602)으로 돌아간다.

- [0203] 상기 블록들(604 내지 610, 614, 616) 중에서 어느 하나의 조건들이 오류일 경우, 그러면 상기 프로세스는 블록(602)으로 돌아간다.

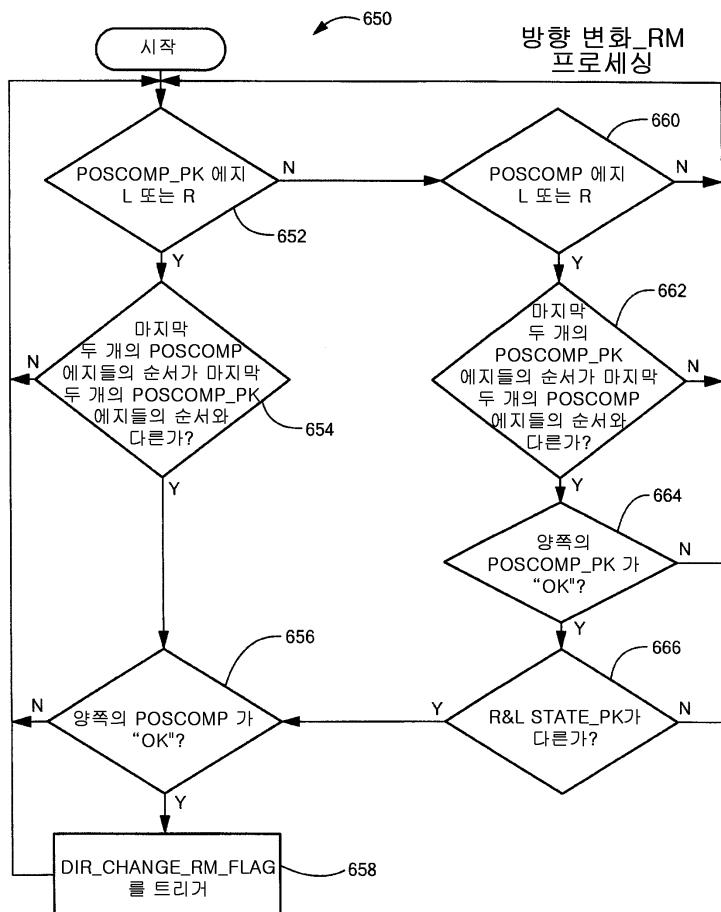

- [0204] 도 13을 참조하면, 예시적인 프로세스(650)는 도 3의 방향 변화\_RM(실행 모드) 프로세서(212)에 의해 수행될 수 있다. 상기 프로세스(650)는 우측 및 좌측인 상기 두 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(650)는 모든 채널들에 대하여 다음에 설명된다. 상기 프로세스(650)는 오류 상태 또는 진동을 나타내는 도 1의 물체(100)의 방향의 변화를 확인하는 데 이용된다.

- [0205] 상기 프로세스(650)는 상기 우측 및 좌측 채널들 모두의 POSCOMP\_PK 신호가 검사되는 블록(652)에서 시작한다. 에지(전환)가 상기 우측 또는 좌측 채널 중에서 하나의 POSCOMP\_PK에서 검출될 경우, 상기 프로세스(650)는 블록(654)으로 진행한다.

- [0206] 블록(654)에서, 상기 우측 및 좌측 채널들에서 POSCOMP 신호들의 최후의 두 에지들(즉, 위상 사인)의 순서(우측, 좌측)가 상기 우측 및 좌측 채널들에서 상기 POSCOMP\_PK 신호들의 최후의 두 에지들의 순서와 비교된다. 상기 최후의 두 POSCOMP\_PK 에지들은 블록(652)만에서 검출되는 하나를 포함한다. 상기 순서가 상기 POSCOMP\_PK 신호들을 위해서보다는 상기 POSCOMP 신호들을 위해 다를 경우, 그러면 상기 프로세스는 블록(656)으로 진행한다.

- [0207] 블록(656)에서, 상기 POSCOMP 신호들이, 예를 들면 도 16의 프로세스(800)에 의해 상기 우측 및 좌측 채널들 모두에서 확인될 경우, 그러면 상기 프로세스는 블록(658)으로 계속되고, 여기서 상기 DIR\_CHAGE\_RM\_FLAG 신호(도 3 참조)가, 예를 들면 도 2의 클록 신호(182a)의 하나의 사이클을 위해 순간적으로 트리거되고, 상기 프로세스는 블록(652)으로 돌아간다.

- [0208] 블록(652)에서, 상기 우측 또는 좌측 채널들 중에서 하나의 POSCOMP\_PK 신호에서 에지가 검출되지 않을 경우, 그러면 상기 프로세스는 상기 POSCOMP 신호들이 검사되는 블록(660)으로 진행한다. 블록(660)에서 전환은 상기 우측 또는 좌측 채널들 중에서 하나의 상기 POSCOMP 신호에서 전환이 검출될 경우, 그러면 상기 프로세스는 블

록(662)으로 진행한다.

- [0209] 블록(662)에서, 상기 우측 및 좌측 채널들에서 상기 POSCOMP\_PK 신호들의 최후의 두 에지들(즉, 위상 사인)의 순서(우측, 좌측)가 상기 우측 및 좌측 채널들의 POSCOMP 신호들의 최후의 두 에지들의 순서와 비교된다. 상기 최후의 두 POSCOMP 에지들은 블록(660)에서만 검출되는 하나를 포함한다. 상기 순서가 상기 POSCOMP 신호들을 위해서 그리고 상기 POSCOMP\_PK 신호들을 위해서 다를 경우, 그러면 상기 프로세스는 블록(664)으로 진행한다.

- [0210] 블록(664)에서, 상기 POSCOMP\_PK 신호들이, 예를 들면 도 16a의 프로세스(850)에 의해 상기 우측 및 좌측 채널들 모두에서 확인될 경우, 그러면 상기 프로세스는 블록(666)으로 계속된다.

- [0211] 블록(666)에서, 상기 우측 및 좌측 채널들의 STATE\_PK 상태 신호들에 표시되는 상기 상태들이 다른지가 결정된다. 상기 상태들이 다를 경우, 그러면 상기 프로세스는 블록(656)으로 진행한다. 상기 상태들이 상기 두 채널들에서 다르지 않을 경우, 그러면 상기 프로세스(650)는 블록(652)으로 돌아간다.

- [0212] 블록(660)에서, 상기 우측 또는 좌측 채널들 중에서 하나의 상기 POSCOMP 신호에서 에지가 검출되지 않을 경우, 상기 프로세스(650)는 블록(652)으로 돌아간다. 블록들(652, 660)은 기본적으로 POSCOMP\_PK 신호 또는 상기 좌측 또는 우측 채널들 중에서 하나의 POSCOMP 신호에서 전환이 검출될 때까지 루프(loop)된다.

- [0213] 블록(662)에서, 상기 POSCOMP\_PK 신호에서 전환들의 순서가 블록(660)에서 검출되는 전환을 갖는 상기 POSCOMP 신호에서 전환들의 순서와 다르지 않을 경우, 그러면 상기 프로세스는 블록(652)으로 돌아간다.

- [0214] 블록(664)에서, 상기 POSCOMP\_PK 신호들이 양호한(OK) 것으로 확인되지 않을 경우, 그러면 상기 프로세스(650)는 블록(652)으로 돌아간다.

- [0215] 블록들(654 또는 656)의 조건들이 참이 아닐 경우, 그러면 상기 프로세스는 블록(652)으로 돌아간다.

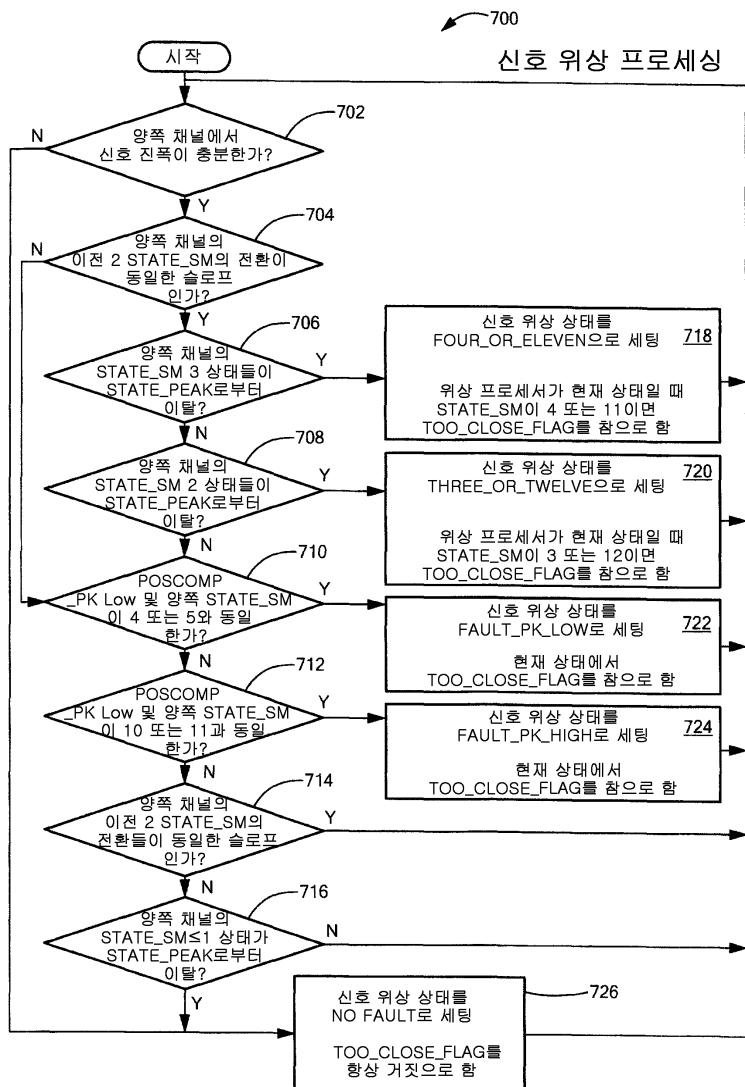

- [0216] 도 14를 참조하면, 예시적인 프로세스(700)는 도 3의 신호 단계 프로세서(214)에 의해 수행될 수 있다. 상기 프로세스(700)는 우측 및 좌측의 상기 두 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(700)는 모든 채널들에 대하여 다음에 설명된다. 상기 프로세스(700)는 오류 조건 또는 진동을 나타내기 위해 충분한 규모의 상기 우측 및 좌측 채널들 사이의 위상 미스매치(phase mismatch)를 확인하는 데 이용된다.

- [0217] 상기 프로세스(700)는 블록(702)에서 시작하며, 여기서 상기 우측 및 좌측 모든 채널들의 상기 신호 진폭(도 1 및 도 2의 DIFF 신호, DDIFF 신호 또는 IDIFF 신호)이 충분한 진폭을 가지는지가 결정된다. 그러한 결정은 도 11의 블록(580)과 관련하여 전술한 바와 같다. 상기 우측 및 좌측 양 채널들의 진폭이 충분할 경우, 상기 프로세스(700)는 블록(704)으로 진행한다.

- [0218] 블록(704)에서, 상기 우측 및 좌측 모든 채널들의 상기 STATE\_SM 신호가 상기 우측 및 좌측 채널 STATE\_SM 신호들의 상태의 적어도 최후의 두 변화들을 위해 동일한 기울기(상향 또는 하향 상태 전환들)를 나타내었는지가 결정된다. 이러한 조건이 참인 경우, 상기 프로세스는 블록(706)으로 진행한다.

- [0219] 블록(706)에서, 상기 우측 및 좌측 채널들 모두의 상기 STATE\_SM 신호들이 상기 우측 및 좌측 채널들의 관련된 STATE\_PEAK 신호들로부터 3개의 상태들로 떨어져있는지가 결정된다. 이러한 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(708)으로 진행한다.

- [0220] 블록(708)에서, 상기 우측 및 좌측 채널들 모두의 상기 STATE\_SM 신호들이 상기 우측 및 좌측 채널들의 관련된 STATE\_PEAK 신호로부터 2개의 상태들로 떨어져있는지가 결정된다. 이러한 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(710)으로 진행한다.

- [0221] 블록(710)에서, 상기 우측 및 좌측 채널 POSCOMP\_PK 신호들이 낮은지 및 상기 우측 및 좌측 채널 STATE\_SM 신호들이 상태 4 또는 5를 나타내는지가 결정된다. 이러한 조건이 거짓인 경우, 그러면 상기 프로세스는 블록(712)으로 진행한다.

- [0222] 블록(712)에서, 상기 우측 및 좌측 채널 POSCOMP\_PK 신호들이 높은지 및 상기 우측 및 좌측 채널 STATE\_SM 신호들이 상태 10 또는 11을 나타내는지가 결정된다. 이러한 조건이 오류일 경우, 그러면 상기 프로세스는 블록(714)으로 진행한다.

- [0223] 블록(714)에서, 블록(704)에서와 같이, 상기 우측 및 좌측 채널들 모두의 모든 STATE\_SM 신호들이 상기 우측 및 좌측 채널 STATE\_SM 신호들의 상태의 적어도 최후의 두 변화들을 위해 동일한 기울기(상향 또는 하향 상태 전환들)를 나타내었는지가 결정된다. 이러한 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(716)으로 진행한다.

- [0224] 블록(716)에서, 상기 우측 및 좌측 채널 STATE\_SM 신호들이 모두가 상기 관련된 STATE\_PEAK 신호로부터 하나의 상태 보다 작거나 동일하게 떨어져 있는지가 결정된다. 이러한 조건이 참일 경우, 그러면 상기 프로세스는 블록(726)으로 진행하고, 여기서 3의 상기 TOO\_CLOSE\_FLAG 신호가 소거, 즉 거짓으로 설정된다.

- [0225] 블록(706)에서 블록(706)과 관련하여 상술한 조건이 참일 경우, 그러면 상기 프로세스는 블록(718)으로 진행한다. 블록(718)에서, 상기 우측 또는 좌측 채널 STATE\_SM 신호가 상태 4 또는 11을 나타낼 경우, 도 3의 TOO\_CLOSE\_FLAG 신호는 참으로 설정된다. 이후에 상기 프로세스는 블록(702)으로 돌아간다.

- [0226] 블록(708)에서, 블록(708)과 관련하여 상술한 조건이 참일 경우, 그러면 상기 프로세스는 블록(720)으로 진행한다. 블록(720)에서, 상기 우측 및 좌측 채널 STATE\_SM 신호가 상태 3 또는 12를 나타낼 경우, 상기 TOO\_CLOSE\_FLAG 신호는 참으로 설정된다. 이후에 상기 프로세스는 블록(702)으로 돌아간다.

- [0227] 블록(710)에서, 블록(710)과 관련하여 상술한 조건이 참일 경우, 그러면 상기 프로세스는 블록(722)으로 진행한다. 블록(722)에서, 상기 TOO\_CLOSE\_FLAG 신호가 참으로 설정된다. 이후에 상기 프로세스는 블록(702)으로 돌아간다.

- [0228] 블록(712)에서, 블록(712)과 관련하여 상술한 조건이 참일 경우, 그러면 상기 프로세스는 블록(724)으로 진행한다. 블록(724)에서, 상기 TOO\_CLOSE\_FLAG 신호가 참으로 설정된다. 그러면 상기 프로세스는 블록(702)으로 돌아간다.

- [0229] 블록(702)에서, 블록(702)과 관련하여 상술한 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(726)으로 진행한다.

- [0230] 블록(704)에서, 블록(704)과 관련하여 상술한 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(710)으로 진행한다.

- [0231] 블록들(714 또는 716)과 관련하여 상술한 조건들이 각기 참 및 거짓일 경우, 그러면 상기 프로세스는 블록(702)으로 돌아간다.

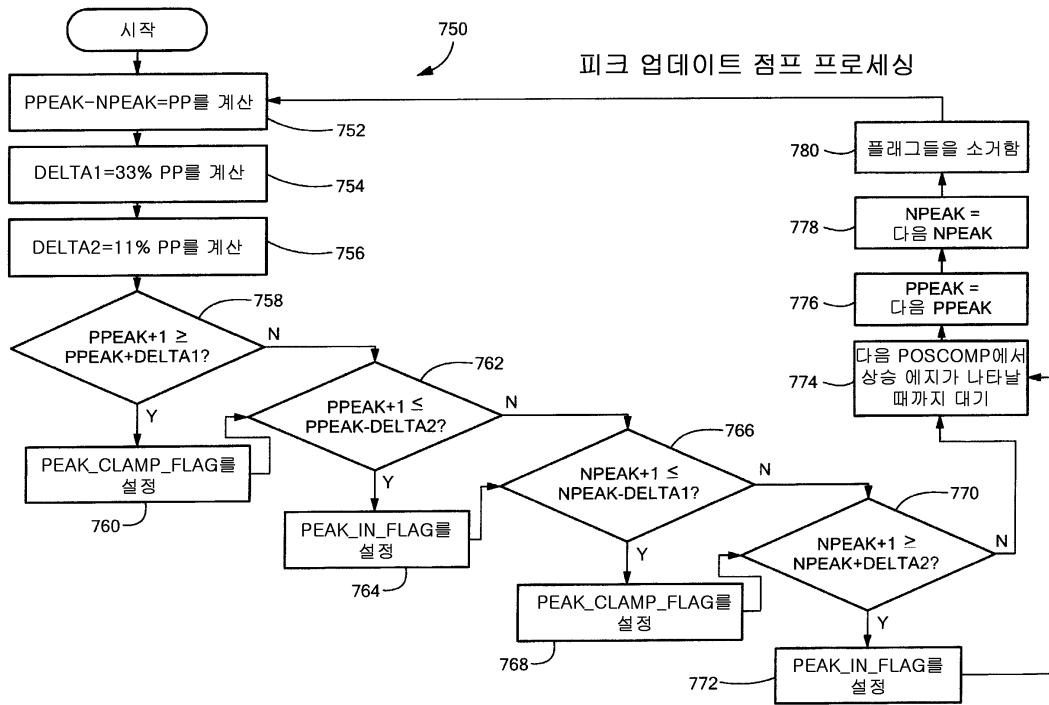

- [0232] 도 15를 참조하면, 예시적인 프로세스(750)는 도 3의 피크 업데이트 점프 프로세서들(216, 218)에 의해 수행될 수 있다. 상기 프로세스(750)는 우측 및 좌측의 두 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(750)가 오직 하나의 채널에 대하여 다음에 설명된다. 상기 프로세스(750)는 오류 조건 또는 진동을 나타내도록 충분한 규모의 상기 우측 또는 좌측 채널들에서(DIFF 신호, DDIFF 신호, 또는 IDDIFF 신호) 진폭 점프를 확인하는 데 사용된다.

- [0233] 상기 프로세스는 블록(752)에서 시작되고, 여기서 신호 크기(DIFF 신호, DDIFF 신호 또는 IDDIFF 신호)가 상기 PPEAK 신호(158a)(도 2)와 상기 NPEAK 신호(160a)(도 2) 사이의 차이를 산정하여 계산되며, 피크-튜-피크(PP) 크기 값이 야기된다. 블록(754)에서, 첫 번째 차이 값(DELTA1)은 상기 PP 값의 33%로 계산된다. 블록(756)에서, 두 번째 차이 값(DELTA2)은 상기 PP 값의 11%로 계산된다.

- [0234] 블록(758)에서 다음 양의 피크 값(PPEAK+1)이 이전의 양의 피크 값(PPEAK)에 상기 첫 번째 차이 값(DELTA1)을 더한 것 보다 크거나 동일한지가 결정된다. 상기 조건이 참일 경우, 그러면 상기 프로세스는 블록(760)으로 진행하고, 여기서 도 3의 PEAK\_CLAMP\_FLAG 신호가 설정되면 상기 프로세스는 블록(762)으로 진행한다. 상기 조건이 거짓일 경우, 그러면 상기 프로세스도 블록(762)으로 진행한다.

- [0235] 블록(762)에서, 상기 다음 양의 피크 값(PPEAK+1)이 이전의 양의 피크 값(PPEAK)에서 상기 두 번째 차이 값(DELTA2)을 뺀 것보다 작거나 동일한지가 결정된다. 상기 조건이 참일 경우, 그러면 상기 프로세스는 블록(764)으로 진행하고, 여기서 도 3의 PEAK\_IN\_FLAG 신호가 설정되면 상기 프로세스는 블록(766)으로 진행한다. 상기 조건이 거짓일 경우, 그러면 상기 프로세스도 블록(766)으로 진행한다.

- [0236] 블록(766)에서, 다음 음의 피크 값(NPEAK+1)이 이전의 음의 피크 값(NPEAK)에서 상기 첫 번째 차이 값(DELTA1)을 뺀 것보다 작거나 같은지가 결정된다. 상기 조건이 참일 경우, 그러면 상기 프로세스는 블록(768)으로 진행하고, 여기서 도 3의 PEAK\_CLAMP\_FLAG 신호가 설정되면 상기 프로세스가 블록(770)으로 진행한다. 상기 조건이 거짓일 경우, 그러면 상기 프로세스도 블록(770)으로 진행한다.

- [0237] 블록(770)에서, 상기 다음 음의 피크 값(NPEAK+1)이 이전의 음의 피크 값(NPEAK)에 상기 두 번째 차이 값(DELTA2)을 더한 것보다 크거나 같은지가 결정된다. 상기 조건이 참일 경우, 그러면 상기 프로세스는 블록(772)으로 진행하고, 여기서 도 3의 PEAK\_IN\_FLAG가 설정되고 상기 프로세스가 블록(774)으로 진행한다. 상기 조건

이 거짓일 경우, 그러면 상기 프로세스도 블록(774)으로 진행한다.

[0238] 블록(774)에서, 상기 프로세스(750)는 상기 채널에서 처리되는 다음의 POSCOMP 상승되는 에지(rising edge)를 기다린다.

[0239] 블록(776)에서, 상기 PPEAK 값은 상기 다음의 PPEAK 값을 적용하고, 블록(778)에서 상기 NPEAK 값은 상기 다음의 NPEAK 값을 채용한다. 블록(780)에서, 블록들(760, 764, 768 또는 772) 내에 설정된 임의의 플래그들이 분명해진다. 상기 프로세스는 이후에 블록(752)으로 돌아간다.

[0240] 도 16을 참조하면, 예시적인 프로세스(800)는 도 3의 POSCOMP 확인 프로세서들(220, 222)에 의해 수행될 수 있다. 상기 프로세스(800)는 우측 및 좌측인 두 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스(800)는 오직 하나의 채널에 대하여 다음에 설명되지만, 상기 블록들 중에서 일부에서 상기 다른 채널을 이용한다. 상기 프로세스(800)는 적절한 POSCOMP 신호를 확인하는 데 사용된다. 부적절한 POSCOMP 신호는 오류 또는 진동 조건을 나타낼 수 있다.

[0241] 상기 프로세스(800)는 블록(802)에서 시작하고, 여기서 상기 우측 및 좌측 모든 채널들의 신호 진폭(도 1 및 도 2의 DIFF 신호, DDIFF 신호 또는 IDDIFF 신호)이 충분한 진폭을 가지는지가 결정된다. 그러한 결정은 도 11의 블록(580)과 관련하여 상술하였다. 상기 우측 및 좌측 모든 채널들의 진폭이 충분할 경우, 상기 프로세스(800)는 블록(804)으로 진행한다.

[0242] 블록(804)에서, 도 1의 모션 센서(102)가 도 4를 참조하여 상술한 동작의 상기 BURP 모드에 현재 존재하는지가 결정된다. 상기 동작의 BURP 모드는 상기 모션 센서(102)가 처음으로 전원을 인가받은 후에 짧게 일어난다. 상기 모션 센서(102)가 현재 상기 동작의 BURP 모드에 있지 않을 경우, 그러면 상기 프로세스(800)는 블록(806)으로 진행한다.

[0243] 블록(806)에서, 상기 모션 센서(102)가 도 5를 참조하여 상술한 상기 동작의 보정 모드에 현재 존재하는지와 AOA/AGC 사건(event)이 발생되는지가 결정된다. 상기 동작의 보정 모드는 상기 모션 센서(102)가 상기 동작의 BURP 모드에 존재하는 후 또는 다른 시간들에서 짧게 일어날 수 있다. 상기 모션 센서(102)가 현재 상기 동작의 보정 작동에 있지 않을 경우, 그러면 상기 프로세스(800)는 블록(808)으로 진행한다.

[0244] 블록(808)에서, 도 3 및 도 15의 PEAK\_CLAMP\_FLAG 신호가 확인되는 상기 우측 또는 좌측인 채널에서 검출되는지가 결정된다. 상기 PEAK\_CLAMP\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(810)으로 진행한다.

[0245] 블록(810)에서, 도 3 및 도 12의 DIR\_CHAGE\_PK\_FLAG 신호가 검출(설정)되는지가 결정된다. 상기 DIR\_CHAGE\_PK\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(811)으로 진행한다.

[0246] 블록(811)에서, 도 3 및 도 13의 DIR\_CHAGE\_RM\_FLAG 신호가 검출(설정)되는지가 결정된다. 상기 DIR\_CHAGE\_RM\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(812)으로 진행한다.

[0247] 블록(812)에서, 상기 POSCOMP 신호의 에지(전환)가 확인되는 상기 우측 또는 좌측인 채널에서 검출되는지가 결정된다. 상기 POSCOMP 에지가 검출되는 경우, 그러면 상기 프로세스는 블록(814)으로 진행한다.

[0248] 블록(814)에서, 상기 우측 및 좌측 채널 STATE\_PK 신호들에 의해 나타나는 상기 상태들이 다른지가 결정된다. 상기 나타난 상태들이 다를 경우, 그러면 상기 프로세스는 블록(816)으로 진행하고, 여기서 상기 POSCOMP\_OK\_FLAG 신호가 확인되는 우측 또는 좌측인 채널에 설정된다. 상기 POSCOMP\_OK\_FLAG 신호의 설정은 확인된 POSCOMP 신호를 나타낸다. 상기 프로세스(800)는 이후에 블록(802)으로 돌아간다.

[0249] 상기 조건이 블록(802)에서 거짓이거나 상기 블록들(804 내지 811) 중에서 어떤 것의 조건들이 참일 경우, 상기 프로세스(800)는 블록(818)으로 진행하고, 여기서 확인되지 않은 POSCOMP 신호를 나타내는 상기 POSCOMP\_OK\_FLAG 신호가 확인되는 우측 또는 좌측인 채널에서 소거되며, 이후에 상기 프로세스(800)는 블록(802)으로 돌아간다.

[0250] 블록들(812 또는 814)의 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(802)으로 돌아간다.

[0251] 도 16a를 참조하면, 예시적인 프로세스(850)는 도 3의 POSCOMP\_PK 확인 프로세서들(224, 226)에 의해 수행될 수 있다. 상기 프로세스(850)는 상기 우측 및 좌측인 두 채널들을 위해 직렬로 또는 병렬로 수행될 수 있다. 상기 프로세스는(850)은 오직 하나의 채널에 대하여 후술되지만, 상기 블록들의 일부에서는 상기 다른 채널을 이용한다. 상기 프로세스(850)는 적절한 POSCOMP\_PK 신호를 확인하는 데 사용된다. 부적절한 POSCOMP\_PK 신호는 오류

또는 진동 조건을 나타낼 수 있다.

- [0252] 상기 프로세스(850)는 블록(852)에서 시작하고, 여기서 상기 우측 및 좌측 모든 채널들의 신호 진폭(도 1 및 도 2의 DIFF 신호, DDIFF 신호, IDDIFF 신호)이 충분한 진폭을 가지는지가 결정된다. 그러한 결정은 도 11의 블록(580)과 관련하여 상술하였다. 상기 우측 및 좌측 모든 채널들의 진폭이 충분할 경우, 상기 프로세스(850)는 블록(854)으로 진행한다.

- [0253] 블록(854)에서, 도 1의 모션 센서(102)가 도 4를 참조하여 상술한 상기 동작의 BURP 모드에 현재에 있는지가 결정된다. 상기 동작의 BURP 모드는 상기 모션 센서(102)가 처음으로 전원을 받은 후에 짧게 발생할 수 있다. 상기 모션 센서(102)가 상기 동작의 BURP 모드에 현재 있지 않을 경우, 그러면 상기 프로세스(850)는 블록(856)으로 진행한다.

- [0254] 블록(856)에서, 도 3 및 도 10의 INFLECTION\_FLAG 신호가 확인되는 상기 우측 또는 좌측인 채널에서 검출되는지가 결정된다. 상기 INFLECTION\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스(850)는 블록(858)으로 진행한다.

- [0255] 블록(858)에서, 도 3 및 도 15의 PEAK\_CLAMP\_FLAG 신호가 확인되는 상기 우측 또는 좌측인 채널에서 검출되는지가 결정된다. 상기 PEAK\_CLAMP\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(860)으로 진행한다.

- [0256] 블록(860)에서, 도 3 및 도 11의 DIR\_CHAGE\_FLAG 신호가 검출(설정)되는지가 결정된다. 상기 DIR\_CHAGE\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(864)으로 진행한다.

- [0257] 블록(862)에서, 도 3 및 도 13의 DIR\_CHAGE\_RM\_FLAG 신호가 검출(설정)되는지가 결정된다. 상기 DIR\_CHAGE\_RM\_FLAG 신호가 검출되지 않을 경우, 그러면 상기 프로세스는 블록(864)으로 진행한다.

- [0258] 블록(864)에서, 상기 POSCOMP\_PK 신호의 에지(전환)가 확인되는 상기 우측 또는 좌측인 채널에서 검출(설정)되는지가 결정된다. 상기 POSCOMP\_PK 에지가 검출되는 경우, 그러면 상기 프로세스(850)는 블록(866)으로 진행한다.

- [0259] 블록(866)에서, 상기 POSCOMP\_PK\_OK\_FLAG 신호가 확인되는 우측 또는 좌측인 채널에 설정되는지가 결정된다. 상기 POSCOMP\_PK\_OK\_FLAG 신호의 설정은 확인되는 POSCOMP\_PK 신호를 나타낸다. 상기 프로세스(850)는 이후에 블록(852)으로 돌아간다.

- [0260] 블록(852)에서 상기 조건이 거짓이거나 상기 블록들(854 내지 862) 중의 어떤 것의 조건들이 참일 경우, 그러면 상기 프로세스(850)는 블록(868)으로 진행하고, 여기서 확인되지 않은 POSCOMP\_PK 신호를 나타내는 상기 POSCOMP\_PK\_OK\_FLAG 신호가 분명해지며, 이후에 상기 프로세스(850)는 블록(852)으로 돌아간다.

- [0261] 블록(864)의 조건이 거짓일 경우, 그러면 상기 프로세스는 블록(852)으로 돌아간다.

- [0262] 도 17을 참조하면, 프로세스(900)는 도 2의 STATE\_SM 신호(174a)로부터 상기 STATE\_PEAK 신호(176a)를 발생시키데 사용될 수 있다. 상술한 바와 같이, 상기 STATE\_PEAK 신호(176a)는 상기 STATE\_SM 신호(174a)에 존재할 수 있는 것으로부터 감소된 상태 채터를 가진다.

- [0263] 상기 프로세스(900)는 단계(902)에서 시작하고, 여기서 도 2, 도 7a, 도 9a 및 도 10의 POSCOMP\_PK 신호가 높은 상태(하나)에 있는지가 결정된다. 상기 POSCOMP\_PK 신호가 높은 상태에 있지 않을 경우, 상기 프로세스(900)는 블록(904)으로 진행한다.

- [0264] 블록(904)에서, 상기 STATE\_SM 신호에 의해 나타나는 상태가 상기 STATE\_PEAK 신호에 의해 나타나는 상태보다 큰지가 결정된다. 상기 조건이 참일 경우, 상기 프로세스(900)는 블록(906)으로 진행한다.

- [0265] 블록(906)에서, 상기 STATE\_PEAK 신호가 상기 STATE\_SM 신호와 동일하게 설정되며 상기 프로세스는 블록(902)으로 돌아간다. 따라서 상기 STATE\_PEAK 신호의 전환들은 블록(906)에서 발생된다.

- [0266] 블록(904)에서, 상기 조건이 거짓일 경우, 그러면 상기 프로세스(900)는 블록(902)으로 돌아간다.

- [0267] 블록(902)에서 상기 조건이 참일 경우, 그러면 상기 프로세스는 블록(908)으로 진행한다.

- [0268] 블록(908)에서, 상기 STATE\_SM 신호에 의해 나타나는 상태가 상기 STATE\_PEAK 신호에 의해 표시되는 상태보다 적은지가 결정된다. 상기 조건이 참일 경우, 상기 프로세스(900)는 블록(906)으로 진행한다. 상기 조건이 거짓

일 경우, 상기 프로세스(900)는 블록(902)으로 돌아간다.

[0269] 상기 STATE\_SM 신호 내의 채터와 비교되는 상기 STATE\_PEAK 신호 내의 감소된 채터가

[0270] 상태 경계들(예를 들면, 도 2의 180b 참조) 또는 보다 근접하게 이격되거나 그렇지 않으면 가능한 상태들을 사용하는 능력을 가져올 수 있는 점을 이해할 수 있을 것이다. 도 2를 간단하게 참조하면, 상기 STATE\_SM 신호(174a) 내의 채터는, 특히 적용되는 스레시홀드들, THRESH\_A(168a) 및 THRESH\_B(168b)가 근접하게 이격될 때에 상기 COMP\_A 신호(172a) 내 및 상기 COMP\_B신호(170a) 내의 전환들과 같이 나타나는 상기 IDDIFF 신호(154a) 내의 노이즈에 의해 영향을 받는다. 도 17은

[0271] 보다 근접하게 이격되는 두 스레시홀드들, THRESH\_A(168a) 및 THRESH\_B(168b)를 허용하는 도 2의 2개의 비교기들(170, 172)에 대한 히스테리시스(hysteresis)와 유사한 함수를 제공한다.

[0272] 보다 근접하게 이격되는 상태들의 제공은 결과적으로 보다 정확한(시간 내의) 도 1의 POSCOMP 신호들(112a, 128a)의 에지 배치를 허용한다(예를 들면, 도 7 및 도 7a 참조). 상기 POSCOMP 신호들의 에지들(전환들)이 직접적으로 도 1의 물체(100)의 절대 회전 각도와 관련되기 때문에, 상기 STATE\_PEAK 신호를 야기하는 도 17의 프로세스(900)는 상기 물체(100)의 절대 회전 각도의 보다 정확한 지식을 제공한다.

[0273] 도 18을 참조하면, 그래프(920)는 진폭의 임의의 단위들로 스케일을 나타낸 수직 축과 시간의 임의의 단위들로 스케일을 나타낸 수평 축을 가진다. 신호(922)는 도 1의 DIFF 신호들(108a, 124a) 중에서 하나를 나타내거나, 도 1의 DDIFF 신호들(110a, 126a) 중에서 하나를 나타내지만 아날로그 형태이며, 혹은 도 2의 IDDIFF 신호(154a)를 나타내지만 아날로그 형태이다.

[0274] 첫 번째 시간(928)은 사이클들(924)의 첫 번째 소정의 숫자, 예를 들면 도 1의 모션 센서(102)에 전원이 인가된 후의 세 사이클들을 나타낸다. 진동이 도 1의 진동 프로세서(116)에 의해 검출되지 않을 경우, 그러면, 일부 실시예들에 있어서, 도 1의 출력 프로토콜 프로세서(118)가 상기 시간(928)(시간(928)이 유효 시간이 될 수 있는)에서 활성 출력 신호(118a)를 발생시킬 수 있다. 그러나 진동이 상기 진동 프로세서(116)에 의해 검출될 경우, 그러면 사이클들(926)의 다른 소정의 숫자가 사이클들(924)의 상기 첫 번째 소정의 숫자에 추가될 수 있어, 시간(930)(새로운 유효 시간)까지 연기되는 상기 활성 출력 신호(118a)를 야기한다. 상기 사이클들의 첫 번째 소정의 숫자의 곱들은 상기 진동이 더 이상 검출되지 않는 이러한 시간까지 상기 사이클들(924)의 첫 번째의 소정의 숫자에 추가될 수 있으며, 이에 따라 상기 활성 출력 신호(118a)가 연기될 수 있다.

[0275] 이런 배열은 불필요하게 길어질 수 있는 양으로 상기 활성 출력 신호(118a)가 연기되는 것으로 이해될 수 있다.

[0276] 가능한 신속하게 활성 출력 신호(118a)를 제공하는 것이 바람직함을 인지할 수 있을 것이다.

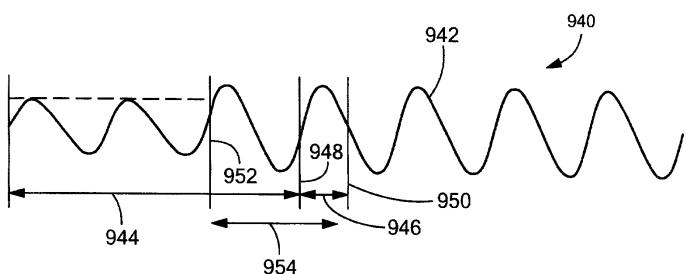

[0277] 도 18a를 참조하면, 그래프(940)는 진폭의 임의의 단위들로 스케일을 나타낸 수직 축과 시간의 임의의 단위들로 스케일을 나타낸 수평 축을 가진다. 신호(942)는, 도 1의 DIFF 신호들(108a, 124a) 중에서 하나를 나타내거나, 또는 도 1의 DDIFF 신호들(106a, 126a) 중에서 하나를 나타내지만 아날로그 형식이며, 혹은 도 2의 IDDIFF 신호(154a)를 나타내지만 아날로그 형식이다.

[0278] 첫 번째 시간(948)은 사이클들의 소정의 숫자, 예를 들면 도 1의 모션 센서(102)에 전력이 인가된 후의 세 사이클들을 나타낸다. 시간(0)으로부터 시간(948)까지, 도 1의 진동 프로세서(116)에 의해 진동이 검출되지 않을 경우, 상기 시간(948)이 유효 시간이 되며, 일부 실시예들에 있어서, 도 1의 출력 프로토콜 프로세서(118)는, 시간(948) 이전의 비활성 출력 신호가 될 수 있는 유효하지 않은 출력 신호에 의해 앞서는, 시간(948)에서 활성 출력 신호(118a)가 될 수 있는 유효 출력 신호를 발생시킬 수 있다.

[0279] 그러나, 진동이 상기 진동 프로세서(116)에 의해 검출될 경우, 상기 유효 시간은 상기 시간(948)보다 더 늦게 발생할 수 있다. 진동 검출은 상기 DIFF 신호(942)의 진폭 변화가 발생되는 시간(952)에서 일어나도록 도시된다.

[0280] 상기 사이클들(944)의 소정의 숫자를 나타내는 시간(948) 전에 진동이 도 1의 진동 프로세서(116)에 의해 검출되는 경우, 그러면 "결정된(determined)" 시한(954)이 검출(950)의 시간으로부터 추가될 수 있어, 시간(950)까지 연장되고, 상기 시간(950) 전에 상기 유효하지 않은 출력 신호에 의해 앞서는 상기 유효한 출력 신호(118a)가 야기된다. 달리 말하면, 시간(950)에서 새로운 유효 시간이 발생된다. 상기 결정된 시한(954)(또는 사이클들의 숫자)은 도 19 내지 도 19b와 관련하여 다음에 설명하는 바와 같은 검출된 진동의 특정한 성질들(예를 들면, 상기 진동의 유형, 상기 진동의 기간)에 따라 결정될 수 있다.

- [0281] 일부 실시예들에 있어서, 상기 결정된 시한(954)은 상기 검출된 진동의 특정한 성질들에 따라 결정된 상기 DIFF 신호(942)(또는 도시하지는 않았지만 POSCOMP 신호)의 사이클들의 숫자를 포함할 수 있다. 다른 실시예들에 있어서, 상기 결정된 시한(954)은 상기 DIFF 신호의 사이클들과는 관련이 없는 상기 검출된 진동의 특정한 성질들과 연관되는 시한이 될 수 있다.

- [0282] 이러한 배열은 원하는 바와 같이 도 18의 배열보다 적은 양으로 상기 유효한 출력 신호(118a)를 연기하는 점으로 이해될 수 있을 것이다. 달리 말하면, 상기 유효 시간(950)은 도 18의 유효 시간(930) 전에 발생한다.

- [0283] 상술한 배열이 상기 시간(950)(또는 948) 전의 상기 유효하지 않은 출력 신호가 "비활성화(inactive)"되고, 상기 시간(950)(또는 948) 후에 상기 유효한 출력 신호가 "활성화(active)"되는 것으로 설명하였지만, 도 1의 출력 프로토콜 프로세서(118)가 보다 일반적으로 상기 시간(950)(또는 948)(여기서 "유효 시간"이라고 언급된) 전에 첫 번째 특성들을 갖는 상기 출력 신호(118a)를 제공할 수 있으며, 상기 시간(950)(또는 948) 후에 두 번째의 상이한 특성들을 갖는 상기 출력 신호(118a)를 제공할 수 있는 점을 이해할 수 있을 것이다.

- [0284] 일부 선택적인 실시예들에 있어서, 상기 유효 시간(950)(즉, 상기 유효하지 않은 신호) 전의 상기 첫 번째 특징들은 방향 정보를 포함하지 않을 수 있고(그러나 일부 실시예들에 있어서, 동작 속도 정보를 포함할 수도 있고), 상기 시간(950)(즉, 상기 유효한 신호) 후의 상기 두 번째 다른 특징들은 유효한 방향 정보와 상기 동작 속도 정보를 포함할 수 있다. 일부 다른 실시예들에 있어서, 상기 유효 시간(950)(즉, 상기 유효하지 않은 신호) 전의 상기 첫 번째 특징들은 추정된(유효하지 않은) 방향 정보와 동작 속도 정보를 포함할 수 있으며, 상기 시간(950)(즉, 상기 유효한 신호) 후의 상기 두 번째의 다른 특징들은 상기 유효한 방향 정보와 상기 동작 속도 정보를 포함할 수 있다.

- [0285] 도 1과 관련하여 상술한 바와 같이, 다른 프로토콜들을 갖는 예시적인 출력 신호들은 2008년 7월 31일자로 출원된 미국 특허 출원 제12/183,367호, 2004년 11월 9일자로 등록된 미국 특허 제6,815,944호, 그리고 2006년 4월 11일자로 등록된 미국 특허 제7,026,808호에 기재되어 있다.

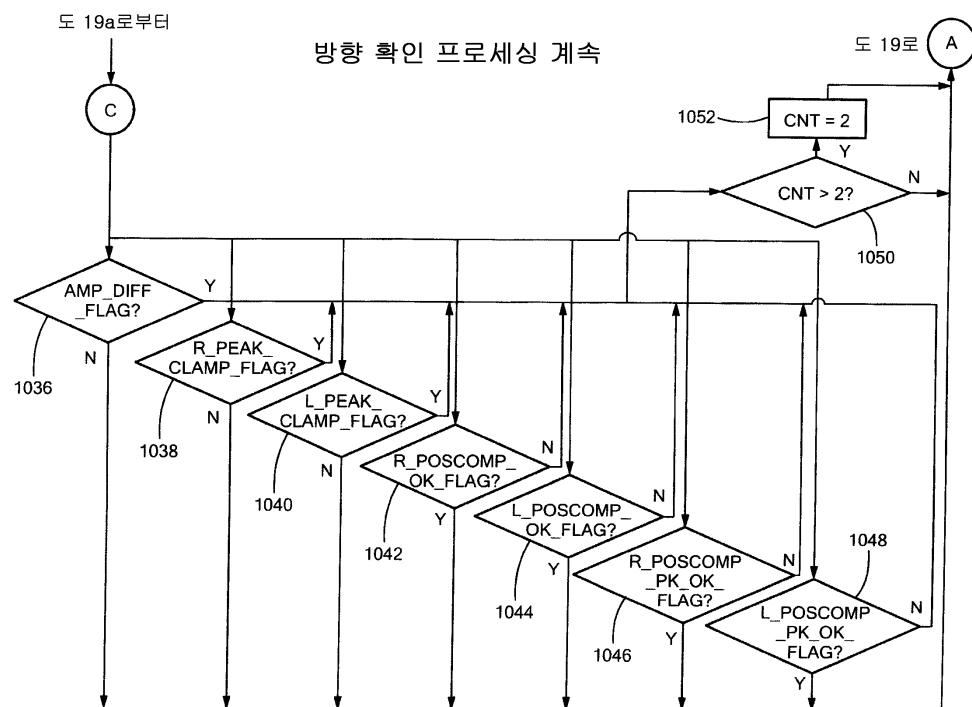

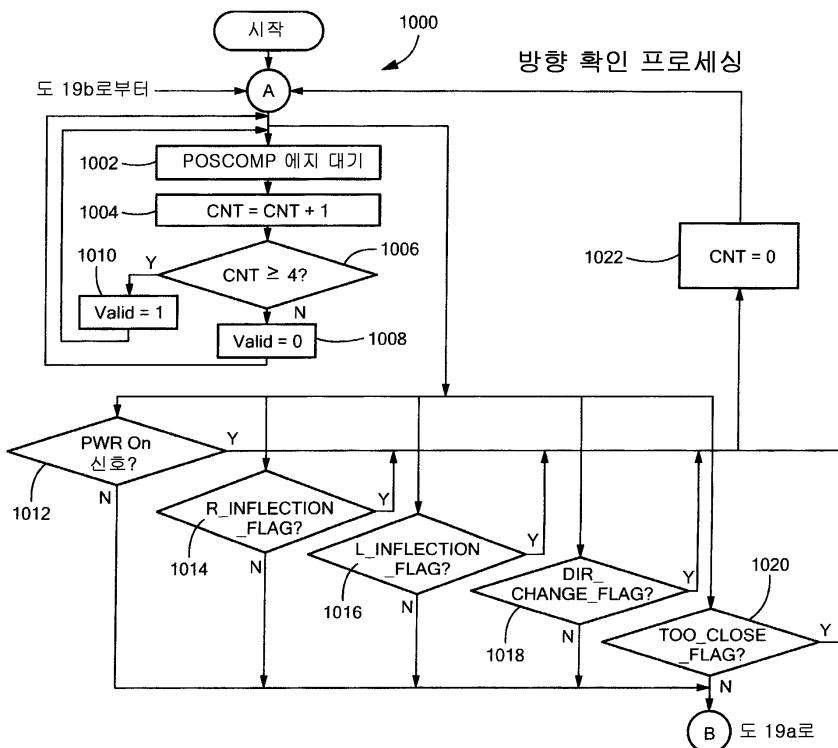

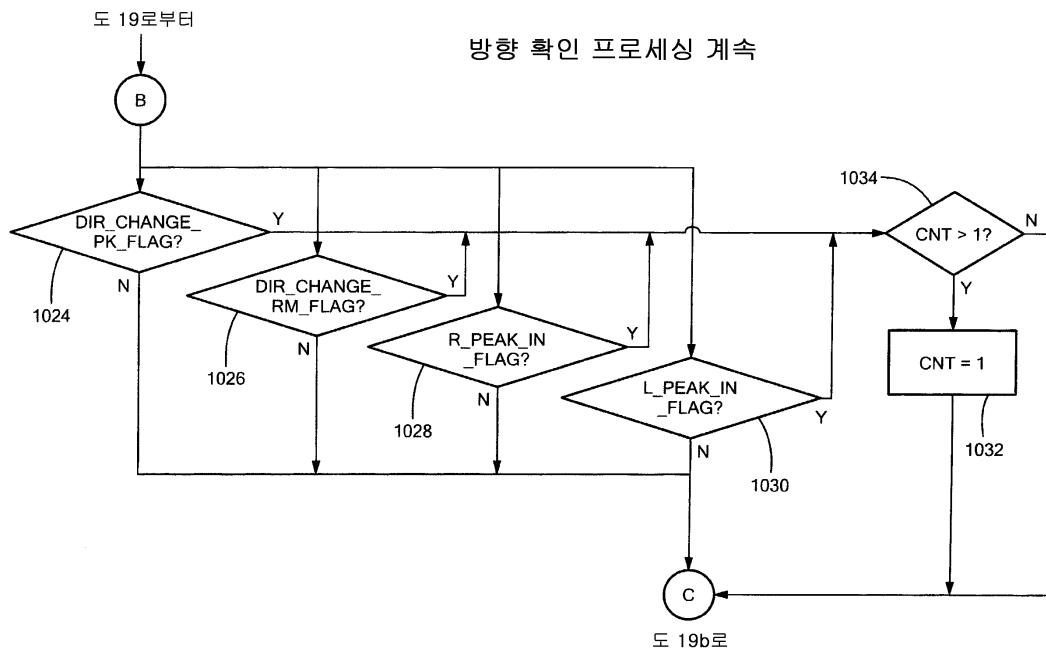

- [0286] 도 19 내지 도 19b를 참조하면, 함께 프로세스(1000)를 설명한다. 상기 프로세스(1000)는 병렬로 실행되는 프로세스들을 포함한다. 첫 번째 프로세스는 블록들(1002 내지 1010)들을 포함한다. 두 번째 프로세스는 블록들(1012 내지 1052)(도 19 내지 도 19b)들을 포함한다. 상기 프로세스(1000)는, 도 1의 출력 신호(118a)가 활성화되거나 그렇지 아니면 도 1의 물체(100)의 동작 방향을 나타내는 시간에서 도 18a의 시간(950)(상기 결정된 시간(946) 또는 상기 사이클들(944)의 소정의 숫자에 추가된 사이클들(946)들의 결정된 숫자를 포함하여)을 확인하는 데 사용될 수 있다.

- [0287] 블록(1002)에서, 상기 프로세스(1000)는 우측 또는 좌측 채널에서 POSCOMP 신호의 에지를 대기한다. 에지가 POSCOMP 신호에서 일단 검출되면, 그러면 상기 프로세스는 계수(CNT)(POSCOMP 에지들의)가 하나씩 증가하는 블록(1004)으로 진행한다.

- [0288] 블록(1006)에서, 상기 계수(CNT)가 4보다 더 크거나 같은지가 결정된다. 상기 계수가 4보다 크지 않거나 같을 경우, 그러면 상기 프로세스(1000)는 블록(1008)으로 진행하고, 여기서 VALID 신호가 0으로 설정되며, 아직 유효하지 않은 도 1의 상기 출력 신호(118a)를 나타내고, 이 경우, 일부 실시예들에 있어서, 활성 출력 신호(118a)(도 1)가 억제될 수 있다. 상기 프로세스는 블록(1002)으로 돌아간다.

- [0289] 블록(1006)에서, 상기 계수(CNT)가 4보다 크거나 같을 경우, 상기 VALID 신호는 0으로 설정되고, 유효하게 되는 도 1의 출력 신호(118a)를 나타내며, 이 경우, 상기 활성 출력 신호(118a)가 발생될 수 있다. 블록(1010)의 VALID=1은 도 18a의 유효 시간(950)이 발생되는 시간을 나타낸다.