(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6206339号

(P6206339)

(45) 発行日 平成29年10月4日(2017.10.4)

(24) 登録日 平成29年9月15日(2017.9.15)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 29/06  | (2006.01)    |

| HO 1 L 29/78  | (2006.01)    |

| HO 1 L 29/12  | (2006.01)    |

| HO 1 L 21/336 | (2006.01)    |

|               | HO 1 L 29/78 |

請求項の数 8 (全 20 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2014-128213 (P2014-128213) |

| (22) 出願日  | 平成26年6月23日 (2014.6.23)       |

| (65) 公開番号 | 特開2016-9714 (P2016-9714A)    |

| (43) 公開日  | 平成28年1月18日 (2016.1.18)       |

| 審査請求日     | 平成29年2月23日 (2017.2.23)       |

|           |                                                 |

|-----------|-------------------------------------------------|

| (73) 特許権者 | 000002130<br>住友電気工業株式会社<br>大阪府大阪市中央区北浜四丁目5番33号  |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                      |

| (72) 発明者  | 和田 圭司<br>大阪市此花区島屋一丁目1番3号 住友電<br>気工業株式会社 大阪製作所内  |

| (72) 発明者  | 久保田 良輔<br>大阪市此花区島屋一丁目1番3号 住友電<br>気工業株式会社 大阪製作所内 |

| (72) 発明者  | 日吉 透<br>大阪市此花区島屋一丁目1番3号 住友電<br>気工業株式会社 大阪製作所内   |

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の主面と、前記第1の主面の反対側に位置する第2の主面とを有し、かつ、第1の導電型を有する炭化珪素層を準備する工程と、

半導体素子部を配置するための素子領域を囲む、前記炭化珪素層の領域に、前記第1の導電型と異なる第2の導電型を有する不純物をイオン注入して、前記炭化珪素層の内部に、前記不純物を含む不純物領域を形成する工程と、

前記炭化珪素層を加熱することにより、前記不純物を活性化させる工程と、

前記炭化珪素層を熱酸化させて、前記炭化珪素層の前記第1の主面を覆う二酸化珪素膜を形成する工程とを備え、

前記二酸化珪素膜を形成する工程は、前記炭化珪素層の前記第1の主面から前記炭化珪素層の内部へと前記不純物を移動させて、前記第1の主面近傍における前記不純物の濃度を低下させることを含み、

前記不純物領域を形成する工程は、

前記炭化珪素層の前記第1の主面からの深さが大きくなるほど前記不純物の濃度が低下するように、前記不純物イオンを注入する工程を含み、

前記二酸化珪素膜を形成する工程は、

前記炭化珪素層の前記第1の主面からの深さ方向に対して前記不純物の濃度が平坦となる部分を含む、前記不純物の濃度プロファイルを形成する工程を含む、炭化珪素半導体装置の製造方法。

**【請求項 2】**

前記二酸化珪素膜を形成する工程により、前記不純物領域は、前記第1の主面から離れた前記炭化珪素層の内部の位置において、前記不純物のピーク濃度を有し、

前記ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下である、請求項1に記載の炭化珪素半導体装置の製造方法。

**【請求項 3】**

前記ピーク濃度の前記位置は、前記炭化珪素層の前記第1の主面から、 $0.3 \mu\text{m}$ 以上かつ $0.5 \mu\text{m}$ 以下の位置である、請求項2に記載の炭化珪素半導体装置の製造方法。

**【請求項 4】**

前記不純物領域は、前記炭化珪素層の前記第1の主面に接するように、前記炭化珪素層の内部に配置される、請求項1～請求項3のいずれか1項に記載の炭化珪素半導体装置の製造方法。 10

**【請求項 5】**

前記不純物領域は、JTE ( Junction Termination Extension ) 領域を含む、請求項1～請求項4のいずれか1項に記載の炭化珪素半導体装置の製造方法。

**【請求項 6】**

前記不純物領域は、ガードリング領域を含む、請求項1～請求項5のいずれか1項に記載の炭化珪素半導体装置の製造方法。

**【請求項 7】**

前記炭化珪素層の前記第1の主面は、(0001)面に対するオフ角が $-8^\circ$ 以上かつ $8^\circ$ 以下の面である、請求項1～請求項6のいずれか1項に記載の炭化珪素半導体装置の製造方法。 20

**【請求項 8】**

前記第1の導電型は、n型であり、

前記第2の導電型は、p型である、請求項1～請求項7のいずれか1項に記載の炭化珪素半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、炭化珪素半導体装置およびその製造方法に関する。より特定的には、本発明は、耐圧特性が向上された炭化珪素半導体装置、およびその製造方法に関する。 30

**【背景技術】****【0002】**

従来、半導体装置を構成する材料として珪素が広く使用されてきた。近年、半導体装置を構成する材料として、炭化珪素の採用が進められつつある。

**【0003】**

炭化珪素は、珪素のバンドギャップよりも大きいバンドギャップを有するワイドバンドギャップ半導体である。半導体装置を構成する材料に炭化珪素を採用することによって、半導体装置の高耐圧化および低損失化を図ることができるとともに、高温環境下で半導体装置を使用できる。 40

**【0004】**

半導体装置の高耐圧化を達成するために、半導体装置の材料に加えて、半導体装置の構造について検討が進められている。一例として、炭化珪素半導体装置において、素子領域の外周を囲む外周構造（終端構造とも呼ばれる）が検討されている。炭化珪素半導体装置に高電圧が印加されたときに、外周構造は電界集中を緩和する機能を果たす。電界集中を緩和することによって、炭化珪素半導体装置の耐圧を高くすることができる。

**【0005】**

これまでに、炭化珪素半導体装置の有する外周構造に関するさまざまな提案が、文献によって説明されている。たとえば特許文献1は、リサーフ ( RESURF ; Reduced Sur 50

face Field) 層と、2つのガードリング層とを備えた高耐圧半導体装置を開示する。2つのガードリング層のうちの一方は、リサーフ層の内部に形成されて、高い不純物濃度を有する。他方のガードリング層は、リサーフ層よりも外側に配置されて、リサーフ層の不純物濃度と同程度の不純物濃度を有する。

#### 【0006】

たとえば特許文献2は、リサーフ層と、電界緩和層とを備えた炭化珪素半導体装置を開示する。電界緩和層は、リサーフ層から離間して、リサーフ層の内周側に配置される。

#### 【0007】

たとえば非特許文献1は、炭化珪素半導体装置の1つとしてショットキーバリアダイオードを開示する。このショットキーバリアダイオードは、終端構造を有する。たとえば終端構造は、JTE ( Junction Termination Extension ) およびリサーフ領域を有する。さらに、非特許文献1は、JTE領域の不純物濃度とショットキーバリアダイオードの耐圧との間の関係を開示する。10

#### 【0008】

たとえば非特許文献2および非特許文献3は、上記のJTE領域の構造および濃度を提案する。

#### 【先行技術文献】

##### 【特許文献】

##### 【0009】

【特許文献1】特開2003-101039号公報20

【特許文献2】特開2008-270412号公報

##### 【非特許文献】

##### 【0010】

【非特許文献1】松波弘之、大谷昇、木本恒暢、中村孝著、「半導体SiC技術と応用」、第2版、日刊工業新聞社、2011年9月30日、p.341およびp.353

【非特許文献2】Hiroki Niwa, Gan Feng, Jun Suda, and Tsunenobu Kimoto "Breakdown Characteristics of 12-20kV-class 4H-SiC PiN Diodes with Improved Junction Termination Structures", Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs, 3-7 June 2012, Bruges, Belgium, p381-384

【非特許文献3】Hiroki Niwa, Jun Suda, and Tsunenobu Kimoto "21.7 kV 4H-SiC PiN Diode with a Space-Modulated Junction Termination Extension", The Japan Society of Applied Physics, Applied Physics Express 5 (2012) 64001, 64001-1-64001-330

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0011】

上記のように挙げられた文献は、JTE領域あるいはリサーフ領域といった終端構造に関して、具体的な構成あるいは不純物濃度が炭化珪素半導体装置の耐圧に対して与える影響を説明する。しかし上記の文献は、これらの領域について、深さ方向に沿った不純物の濃度プロファイルを詳細には説明していない。

##### 【0012】

たとえばアバランシェブレークダウンが発生した際には、逆方向電流が終端構造 ( JTE領域あるいはリサーフ領域 ) を通る。不純物領域の深さ方向における不純物の濃度プロファイルを適切に設定することにより、炭化珪素半導体装置の破壊耐量を高めることができる可能性がある。40

##### 【0013】

本発明の目的は、破壊耐量を高めることが可能な炭化珪素半導体装置、およびその製造方法を提供することである。

#### 【課題を解決するための手段】

##### 【0014】

本発明の一態様に係る炭化珪素半導体装置は、第1の主面と、第1の主面の反対側に位50

置する第2の主面とを有し、かつ、第1の導電型を有する炭化珪素層と、炭化珪素層に形成された半導体素子部を含む素子領域と、第1の導電型と異なる第2の導電型を有し、かつ、平面視において素子領域を囲むように、炭化珪素層の内部に配置された不純物領域とを備える。不純物領域は、炭化珪素層の第1の主面から離れた炭化珪素層の内部の位置において、第2の導電型の不純物のピーク濃度を有する。ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下である。

#### 【0015】

本発明の一態様に係る炭化珪素半導体装置の製造方法は、第1の主面と、第1の主面の反対側に位置する第2の主面とを有し、かつ、第1の導電型を有する炭化珪素層を準備する工程と、半導体素子部を配置するための素子領域を囲む、炭化珪素層の領域に、第1の導電型と異なる第2の導電型を有する不純物をイオン注入して、炭化珪素層の内部に、不純物を含む不純物領域を形成する工程と、炭化珪素層を加熱することにより、不純物を活性化させる工程と、炭化珪素層を熱酸化させて、炭化珪素層の第1の主面を覆う二酸化珪素膜を形成する工程とを備える。二酸化珪素膜を形成する工程は、炭化珪素層の第1の主面から炭化珪素層の内部へと不純物を移動させて、第1の主面近傍における不純物の濃度を低下させることを含む。

#### 【発明の効果】

#### 【0016】

上記によれば、破壊耐量を高めることができることが可能な炭化珪素半導体装置、およびその製造方法を提供することができる。

#### 【図面の簡単な説明】

#### 【0017】

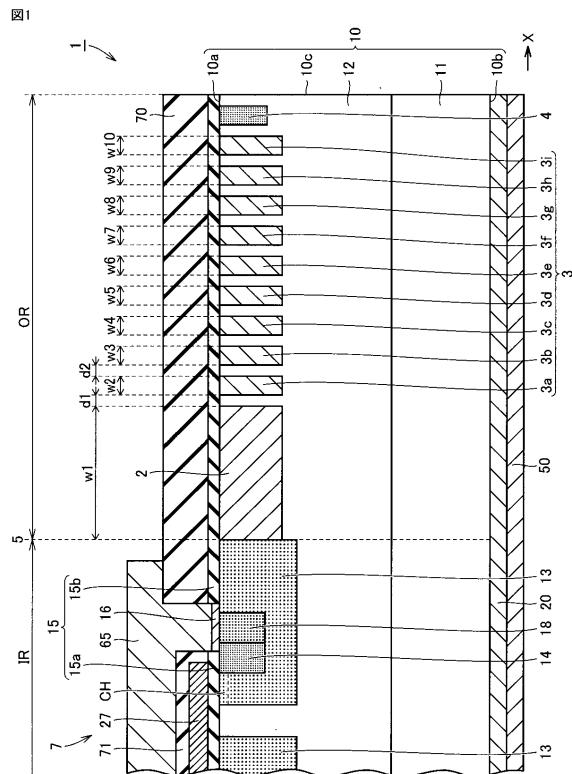

【図1】本発明の第1の実施の形態に係る炭化珪素半導体装置の構造を概略的に示す断面模式図である。

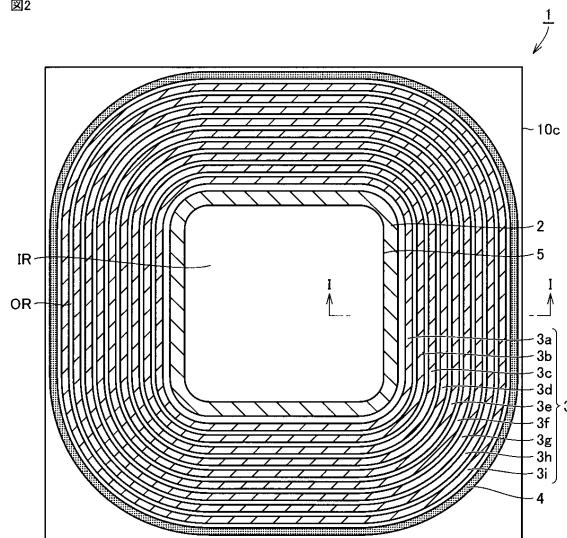

【図2】本発明の一実施の形態に係る炭化珪素半導体装置のJTE ( Junction Termination Extension ) 領域およびガードリング領域の構造を概略的に示す平面模式図である。

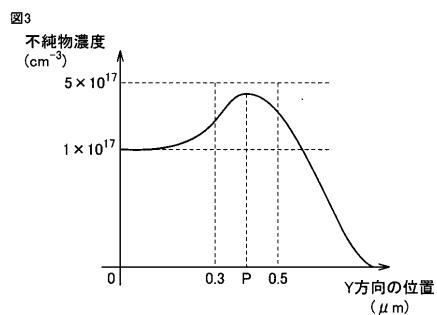

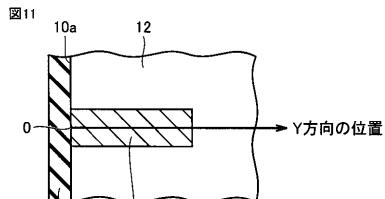

【図3】JTE領域のY方向の位置と不純物濃度との関係を示す模式図である。

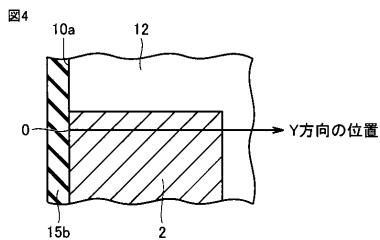

【図4】図3におけるY方向の位置を説明するための図である。

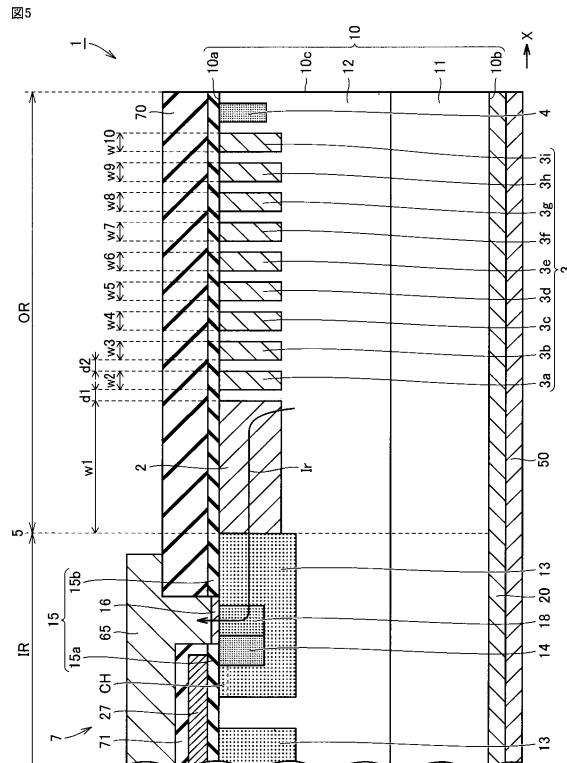

【図5】本発明の実施の形態に係る炭化珪素半導体装置に、アバランシェブレークダウンが発生した状態を示す模式図である。

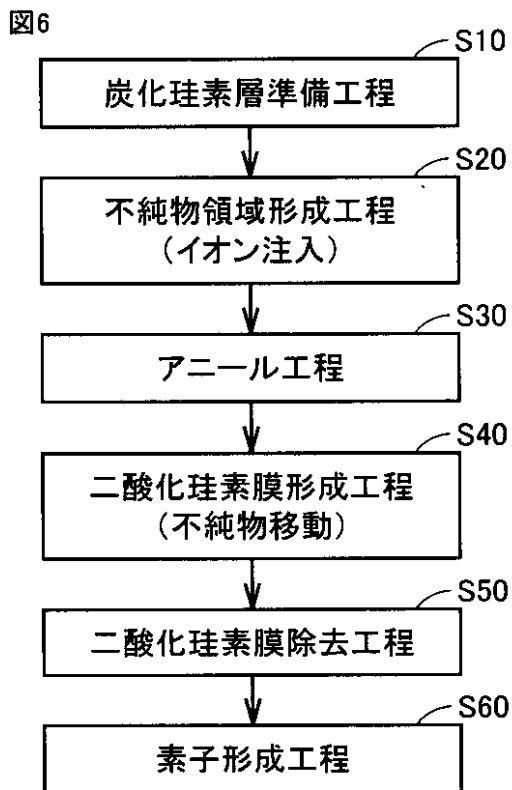

【図6】本発明の一実施の形態に係る炭化珪素半導体装置の製造方法を概略的に示したフローチャートである。

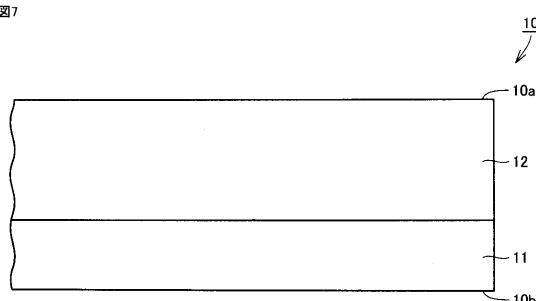

【図7】本発明の一実施の形態に係る炭化珪素半導体装置の製造方法に含まれる工程(S10)を概略的に示す断面模式図である。

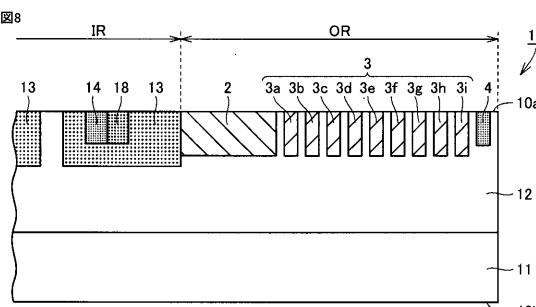

【図8】本発明の一実施の形態に係る炭化珪素半導体装置の製造方法に含まれる工程(S20)を概略的に示す断面模式図である。

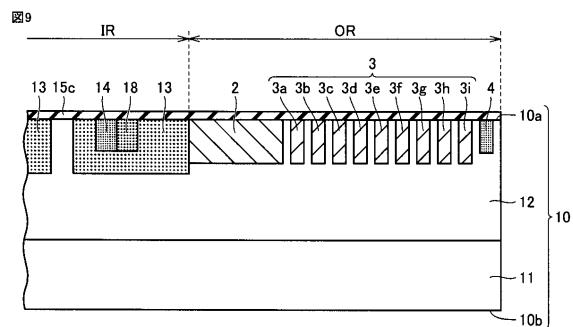

【図9】本発明の一実施の形態に係る炭化珪素半導体装置の製造方法に含まれる工程(S40)を概略的に示す断面模式図である。

【図10】JTE領域における不純物濃度プロファイルの変化を示す模式図である。

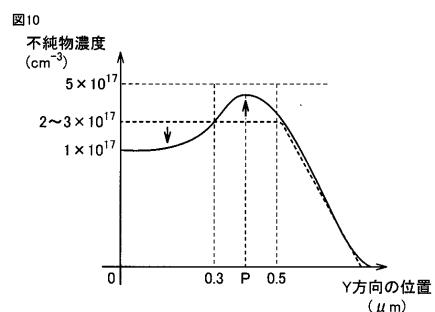

【図11】ガードリング領域のY方向の位置を示す模式図である。

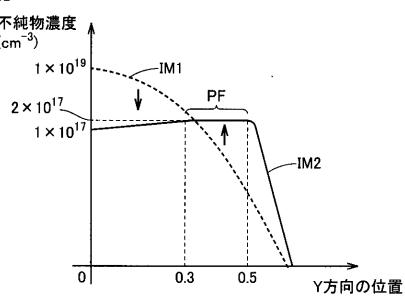

【図12】本発明の第2の実施の形態における、p型不純物濃度領域の濃度プロファイルの模式図である。

#### 【発明を実施するための形態】

#### 【0018】

##### [本発明の実施形態の説明]

最初に本発明の実施態様を列記して説明する。本明細書中においては、個別方位を[]、集合方位を<>、個別面を()、集合面を{}でそれぞれ示す。また、負の指数については、結晶学上、" - " (バー) を数字の上に付けることになっているが、本明細書中では、数字の前に負の符号を付けている。また、「酸化膜」とは二酸化珪素(SiO<sub>2</sub>)の膜

10

20

30

40

50

を意味する。

**【0019】**

(1) 本発明の一態様に係る炭化珪素半導体装置は、第1の主面(10a)と、第1の主面(10a)の反対側に位置する第2の主面(10b)とを有し、かつ、第1の導電型を有する炭化珪素層(10)と、炭化珪素層(10)に形成された半導体素子部(7)を含む素子領域(IR)と、第1の導電型と異なる第2の導電型を有し、かつ、平面視において素子領域(IR)を囲むように、炭化珪素層(10)の内部に配置された不純物領域とを備える。不純物領域は、炭化珪素層(10)の第1の主面(10a)から離れた炭化珪素層(10)の内部の位置(P)において、第2の導電型の不純物のピーク濃度を有する。ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下である。10

**【0020】**

上記構成によれば、破壊耐量を高めることができが可能な炭化珪素半導体装置を提供することができる。たとえばアバランシェブレークダウンが生じた場合に、逆方向電流が不純物領域を流れる。逆方向電流は、不純物領域において、不純物濃度のピークに近い部分を流れやすいと考えられる。したがって逆方向電流は、炭化珪素層の第1の主面から離れた部分を流れやすい。これにより、炭化珪素半導体装置の破壊耐量を高めることができる。

**【0021】**

(2) 好ましくは、ピーク濃度の位置(P)は、炭化珪素層(10)の第1の主面(10a)から、 $0.3 \mu\text{m}$ 以上かつ $0.5 \mu\text{m}$ 以下の位置である。

**【0022】**

上記構成によれば、逆方向電流が第1の主面から離れた経路(不純物領域の内部)を流れれる可能性を高めることができる。20

**【0023】**

(3) 好ましくは、不純物領域は、炭化珪素層(10)の第1の主面(10a)に接するように、炭化珪素層(10a)の内部に配置される。

**【0024】**

上記構成によれば、不純物領域が第1の主面に接する場合においても、逆方向電流が第1の主面から離れた経路(不純物領域の内部)を流れれる可能性を高めることができる。

**【0025】**

(4) 好ましくは、不純物領域は、JTE(Junction Termination Extension)領域(2)を含む。30

**【0026】**

上記構成によれば、逆方向電流を、JTE領域の内部(第1の主面から離れた場所)に流すことができる。

**【0027】**

(5) 好ましくは、不純物領域は、ガードリング領域(3)を含む。

上記構成によれば、逆方向電流を、ガードリング領域の内部(第1の主面から離れた場所)に流すことができる。

**【0028】**

(6) 好ましくは、炭化珪素層(10)の第1の主面(10a)は、(0001)面に対するオフ角が $-8^\circ$ 以上かつ $8^\circ$ 以下の面である。40

**【0029】**

上記構成によれば、第1の主面から離れた炭化珪素層の内部の位置に、第2の導電型の不純物のピーク濃度を有しやすくなる。

**【0030】**

(7) 好ましくは、第1の導電型は、n型であり、第2の導電型は、p型である。

上記構成によれば、炭化珪素半導体装置の製造のしやすさを向上することができる。

**【0031】**

(8) 本発明の他の態様に係る炭化珪素半導体装置の製造方法は、第1の主面(10a)と、第1の主面(10a)の反対側に位置する第2の主面(10b)とを有し、かつ、50

第1の導電型を有する炭化珪素層(10)を準備する工程(S10)と、半導体素子部(7)を配置するための素子領域(IR)を囲む、炭化珪素層(10)の領域に、第1の導電型と異なる第2の導電型を有する不純物をイオン注入して、炭化珪素層(10)の内部に、不純物を含む不純物領域を形成する工程(S20)と、炭化珪素層(10)を加熱することにより、不純物を活性化させる工程(S30)と、炭化珪素層(10)を熱酸化させて、炭化珪素層(10)の第1の主面(10a)を覆う二酸化珪素膜(15c)を形成する工程(S40)とを備える。二酸化珪素膜を形成する工程(S40)は、炭化珪素層(10)の第1の主面(10a)から炭化珪素層(10)の内部へと不純物を移動させて、第1の主面(10a)近傍における不純物の濃度を低下させることを含む。

## 【0032】

10

上記構成によれば、破壊耐量を高めることができが可能な炭化珪素半導体装置を製造することができる。二酸化珪素膜を形成する工程において、炭化珪素層に熱処理が施される。これにより第1の主面から炭化珪素層の内部へと不純物を移動させることができる。たとえばアバランシェブレークダウンが生じた場合に、逆方向電流は、炭化珪素層の第1の主面から離れた部分を流れやすくなる。したがって炭化珪素半導体装置の破壊耐量を高めることができる。

## 【0033】

(9) 好ましくは、二酸化珪素膜を形成する工程(S40)により、不純物領域は、第1の主面(10a)から離れた炭化珪素層(10)の内部の位置(P)において、不純物のピーク濃度を有する。ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下である。

20

## 【0034】

上記構成によれば、逆方向電流が第1の主面から離れた経路(不純物領域の内部)を流れる可能性を高めることができる。

## 【0035】

(10) 好ましくは、ピーク濃度の位置(P)は、炭化珪素層(10)の第1の主面(10a)から、 $0.3 \mu\text{m}$ 以上かつ $0.5 \mu\text{m}$ 以下の位置である。

30

## 【0036】

上記構成によれば、逆方向電流が第1の主面から離れた経路(不純物領域の内部)を流れる可能性を高めることができる。

## 【0037】

(11) 好ましくは、不純物領域は、炭化珪素層(10)の第1の主面(10a)に接するように、炭化珪素層(10)の内部に配置される。

## 【0038】

上記構成によれば、不純物領域が第1の主面に接する場合においても、逆方向電流が第1の主面から離れた経路(不純物領域の内部)を流れる可能性を高めることができる。

## 【0039】

(12) 好ましくは、不純物領域は、JTE(Junction Termination Extension)領域(2)を含む。

40

## 【0040】

上記構成によれば、逆方向電流を、JTE領域の内部(第1の主面から離れた場所)に流すことができる。

## 【0041】

(13) 好ましくは、不純物領域は、ガードリング領域(3)を含む。

上記構成によれば、逆方向電流を、ガードリング領域の内部(第1の主面から離れた場所)に流すことができる。

## 【0042】

(14) 好ましくは、炭化珪素層(10)の第1の主面(10a)は、(0001)面に対するオフ角が $-8^\circ$ 以上かつ $8^\circ$ 以下の面である。

## 【0043】

50

上記構成によれば、二酸化珪素膜を形成する工程において炭化珪素層に熱処理が施されることにより、第1の主面から離れた炭化珪素層の内部の位置に、第2の導電型の不純物のピーク濃度を有しやすくなる。

#### 【0044】

(15) 好ましくは、不純物領域を形成する工程は、炭化珪素層(10)の第1の主面(10a)からの深さが大きくなるほど不純物の濃度が低下するように、不純物イオンを注入する工程を含む。二酸化珪素膜を形成する工程(S40)は、炭化珪素層(10)の第1の主面(10a)からの深さ方向に対して不純物の濃度が平坦となる部分(PF)を含む、不純物の濃度プロファイルを形成する工程を含む。

#### 【0045】

上記構成によれば、不純物領域において、逆方向電流が流れる部分(電流経路)の深さ方向の幅が大きくなる。これにより、その不純物領域における電流密度を低下させることができる。したがって、炭化珪素半導体装置の破壊耐量をより高めることが可能となる。

#### 【0046】

(16) 好ましくは、第1の導電型は、n型であり、第2の導電型は、p型である。

上記構成によれば、炭化珪素半導体装置の製造のしやすさを向上することができる。

#### 【0047】

##### [本発明の実施形態の詳細]

以下、図面に基づいて本発明の実施の形態を説明する。なお、以下の図面において同一または相当する部分には同一の参照番号を付し、その説明は繰返さない。

#### 【0048】

##### <第1の実施の形態>

図1は、本発明の第1の実施の形態に係る炭化珪素半導体装置の構造を概略的に示す断面模式図である。図2は、本発明の一実施の形態に係る炭化珪素半導体装置のJTE(Junction Termination Extension)領域およびガードリング領域の構造を概略的に示す平面模式図である。

#### 【0049】

図1および図2を参照して、まず本発明の一実施の形態に係る炭化珪素半導体装置としてのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)の構成について説明する。

#### 【0050】

図1および図2を参照して、炭化珪素半導体装置1は、素子領域IRと、終端領域ORとを有する。終端領域ORは、素子領域IRの外側に配置されて、素子領域IRを囲む。終端領域ORは、炭化珪素半導体装置1における電界集中を緩和するための領域である。

#### 【0051】

炭化珪素半導体装置1の詳細な構成を以下に説明する。炭化珪素半導体装置1は、炭化珪素層10と、絶縁膜15と、ゲート電極27と、ソース電極16と、ドレイン電極20と、絶縁膜70と、層間絶縁膜71と、パッド電極65と、裏面保護電極50とを含む。

#### 【0052】

炭化珪素層10は、たとえばポリタイプ4Hの六方晶炭化珪素からなり、第1の主面10aと、第2の主面10bとを有している。第2の主面10bは、第1の主面10aとは反対側に位置する。炭化珪素層10の導電型(第1の導電型)は、n型である。

#### 【0053】

主面10aは、(0001)に対するオフ角が-8°以上かつ8°以下の面である。したがって、主面10aは、(0001)面であってもよい。

#### 【0054】

炭化珪素層10は、n<sup>+</sup>基板11と、ドリフト層12とを有する。n<sup>+</sup>基板11は、たとえばポリタイプ4Hの六方晶炭化珪素からなる。n<sup>+</sup>基板11は、たとえばN(窒素)などの不純物(ドナー)を高濃度で含む。n<sup>+</sup>基板11の不純物濃度は、たとえば1.0×10<sup>18</sup> cm<sup>-3</sup>程度である。

10

20

30

40

50

## 【0055】

ドリフト層12は、たとえばポリタイプ4Hの六方晶炭化珪素からなるエピタキシャル層である。たとえばドリフト層12の厚みは5μm程度以上35μm程度以下である。なお、「厚み」あるいは「深さ」との用語は、炭化珪素層10の第1の主面10aに垂直な方向の長さを意味する。

## 【0056】

ドリフト層12の不純物濃度は、n<sup>+</sup>基板11の不純物濃度よりも低い。ドリフト層12の不純物濃度はたとえば1.0×10<sup>15</sup>c m<sup>-3</sup>程度以上1.0×10<sup>16</sup>c m<sup>-3</sup>程度以下である。ドリフト層12に含まれる不純物は、たとえば窒素である。

## 【0057】

この実施の形態では、炭化珪素層10は、2つの層によって構成される。ただし、炭化珪素層10は、単一の層により実現されていてもよい。あるいは、炭化珪素層10は、3つ以上の層によって構成されていてもよい。

## 【0058】

素子領域IRは、炭化珪素層10に形成された半導体素子部7を含む。より詳細には、素子領域IRは、ボディ領域13と、ソース領域14と、p<sup>+</sup>領域18とを含む。終端領域ORは、JTE領域2と、ガードリング領域3と、フィールドストップ領域4とを含む。ボディ領域13、ソース領域14、p<sup>+</sup>領域18、JTE領域2、ガードリング領域3、およびフィールドストップ領域4は、炭化珪素層10の内部に配置される。

## 【0059】

JTE領域2は、炭化珪素半導体装置1における電界集中を緩和するための第1の電界緩和領域である。図1に示されるように、平面視において、JTE領域2は、ボディ領域13の外側に配置されて、ボディ領域13を囲むように炭化珪素層10の内部に配置される。「平面視」との用語は、炭化珪素層10の第1の主面10aから見た視野を意味する。

## 【0060】

JTE領域2は、ボディ領域13と接する。JTE領域2とボディ領域13との境界5が、素子領域IRと終端領域ORとの境界に相当する。さらに、JTE領域2は、炭化珪素層10の第1の主面10aに接している。

## 【0061】

JTE領域2は、第1の導電型と異なる第2の導電型を有する。この実施の形態では、JTE領域2は、p型を有する。JTE領域2に含まれる不純物(アクセプタ)は、たとえばA1(アルミニウム)、B(ホウ素)などである。JTE領域2に含まれる不純物のドーズ量は、1×10<sup>13</sup>c m<sup>-2</sup>以上である。好ましくは、JTE領域2に含まれる不純物のドーズ量は、1×10<sup>13</sup>c m<sup>-2</sup>以上かつ2×10<sup>13</sup>c m<sup>-2</sup>以下の範囲にある。ドーズ量は、たとえば、JTE領域2の深さ方向に沿ってJTE領域2のp型不純物濃度を積分することにより求めることができる。

## 【0062】

図2に示された方向Xは、炭化珪素層10第1の主面10aにおける中央部(素子領域IR)から、第1の主面10aにおける周縁部(終端領域OR)へと向かう方向を表す。この明細書において、方向Xは「周縁方向」とも呼ばれる。

## 【0063】

この明細書では、周縁方向に沿う長さ、すなわち方向Xに沿う長さを「幅」と呼ぶ。JTE領域2の幅w1は、15μm以上かつ50μm以下である。第1の主面10aを基準としたJTE領域2の厚みは、たとえば0.3μm程度以上0.8μm程度以下である。

## 【0064】

ガードリング領域3は、炭化珪素半導体装置1における電界集中を緩和するための第2の電界緩和領域である。具体的には、ガードリング領域3は、アルミニウムあるいはホウ素などの不純物を含むp型の領域である。ガードリング領域3に含まれる不純物のドーズ量は、たとえば1×10<sup>13</sup>c m<sup>-2</sup>以上である。ガードリング領域3に含まれる不純物のド

10

20

30

40

50

一ズ量を、JTE領域2に含まれる不純物のドーズ量と同じ程度（たとえばJTE領域2に含まれる不純物のドーズ量を基準にして±5%の範囲内）としてもよい。

#### 【0065】

JTE領域2に加えてガードリング領域3によって、炭化珪素半導体装置1の電界集中を緩和することができる。したがって炭化珪素半導体装置1の耐圧を、より高めることができる。このような理由により、ガードリング領域3を炭化珪素半導体装置1に設けることが好ましい。しかしながら、たとえば炭化珪素半導体装置1にとって必要な耐圧をJTE領域2によって達成できる場合には、ガードリング領域3が、本発明の実施の形態に係る炭化珪素半導体装置1に設けられていなくてもよい。

#### 【0066】

ガードリング領域3は、複数のガードリング部3a～3iを有していてもよい。図2に示されるように、平面視において、複数のガードリング部3a～3iの各々は、環形状を有し、互いに隙間を隔てて配置される。一実施形態では、ガードリング部の数は9である。しかし、ガードリング部の数は特に限定されるものではない。さらに、図1に示された構成では、各ガードリング部は、炭化珪素層10の第1の主面10aに接している。しかし各ガードリング部は、炭化珪素層10の第1の主面10aから離されるように炭化珪素層10（ドリフト層12）の内部に配置されていてもよい。

#### 【0067】

フィールドストップ領域4は、平面視においてガードリング領域3よりも外側に配置され、かつガードリング領域3を囲む。「外側」とは、炭化珪素層10の端部10cの側に対応する。フィールドストップ領域4は、ガードリング領域3と離間して設けられている。フィールドストップ領域4は、n型の導電型を有する。フィールドストップ領域4の不純物濃度は、ドリフト層12の不純物濃度よりも高い。フィールドストップ領域4は、たとえばP（リン）などの不純物を含む。

#### 【0068】

ボディ領域13は、p型を有する領域である。ボディ領域13に含まれる不純物（アクセプタ）は、たとえばアルミニウム、ホウ素などである。一実施形態では、ボディ領域13は、炭化珪素層10の第1の主面10aに接するように炭化珪素層10の内部に配置される。

#### 【0069】

ボディ領域13の不純物濃度は、JTE領域2の不純物濃度よりも高い。言い換えると、JTE領域2の不純物濃度は、ボディ領域13の不純物濃度よりも低い。たとえば、第1の主面10a近傍のボディ領域13の不純物濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 程度以上 $5 \times 10^{17} \text{ cm}^{-3}$ 程度以下である。ボディ領域13の深部における不純物濃度は、たとえば $1 \times 10^{18} \text{ cm}^{-3}$ 程度である。炭化珪素層10の第1の主面10aを基準としたボディ領域13の厚みは、たとえば $0.5 \mu\text{m}$ 程度以上 $1.0 \mu\text{m}$ 程度以下である。

#### 【0070】

ソース領域14は、n型を有する領域である。ソース領域14は、ボディ領域13の内部に配置されて、炭化珪素層10の第1の主面10aに接する。ソース領域14は、ボディ領域13によって、ドリフト層12から隔てられる。

#### 【0071】

ソース領域14は、たとえばP（リン）などの不純物を含む。ソース領域14の不純物濃度は、ドリフト層12の不純物濃度よりも高い。たとえばソース領域14の不純物濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 程度以上 $1 \times 10^{20} \text{ cm}^{-3}$ 程度以下である。

#### 【0072】

p<sup>+</sup>領域18（コンタクト領域）は、p型の領域であり、たとえばアルミニウムあるいはホウ素などの不純物を含む。p<sup>+</sup>領域18は、ボディ領域13の内部に配置されるとともに、炭化珪素層10の第1の主面10aに接する。図1に示すように、p<sup>+</sup>領域18は、ソース領域14と接してもよい。p<sup>+</sup>領域18の不純物濃度は、ボディ領域13の不純物濃度よりも高い。たとえばp<sup>+</sup>領域18の不純物濃度は、 $2 \times 10^{19} \text{ cm}^{-3}$ 程度以上 $5$

10

20

30

40

50

$\times 10^{20} \text{ cm}^{-3}$  程度以下である。

#### 【0073】

絶縁膜 15 は、ゲート絶縁膜 15a と、絶縁膜 15b とを含む。この実施形態において、絶縁膜 15 (ゲート絶縁膜 15a および絶縁膜 15b) は、二酸化珪素膜であり、たとえば熱酸化膜である。第 1 の主面 10a を基準としたゲート絶縁膜 15a および絶縁膜 15b の厚みは、たとえば 50 nm 程度である。

#### 【0074】

ゲート絶縁膜 15a は、炭化珪素層 10 の第 1 の主面 10a において、ボディ領域 13 に形成されたチャネル領域 CH と対向する位置に設けられる。ゲート絶縁膜 15a は、一方のソース領域 14 の上部表面から他方のソース領域 14 の上部表面にまで延在するよう 10 に、ボディ領域 13、ソース領域 14 およびドリフト層 12 に接する。絶縁膜 15b は、JTE 領域 2 に接するように、炭化珪素層 10 の第 1 の主面 10a 上に配置される。

#### 【0075】

ゲート電極 27 は、ゲート絶縁膜 15a 上に配置される。ゲート電極 27 は、一方のソース領域 14 上から他方のソース領域 14 上にまで延在して、それら 2 つのソース領域の間に位置するドリフト層 12 の部分、および、2 つのチャネル領域 CH に対向する。ゲート電極 27 は、たとえば不純物の添加されたポリシリコン、あるいはアルミニウムなどの導電体からなる。

#### 【0076】

ソース電極 16 は、ソース領域 14 および p<sup>+</sup>領域 18 と接して、ソース領域 14 および p<sup>+</sup>領域 18 に電気的に接続される。好ましくは、ソース電極 16 はソース領域 14 および p<sup>+</sup>領域 18 とオーミック接合している。一実施形態では、ソース電極 16 は、ニッケルおよびシリコンを有する材料からなる。ソース電極 16 は、チタン、アルミニウムおよびシリコンを有する材料からなっていてもよい。

#### 【0077】

絶縁膜 70 は、絶縁膜 15b に接するように配置される。層間絶縁膜 71 は、ゲート絶縁膜 15a 上に配置されて、ゲート電極 27 を覆う。絶縁膜 70 および層間絶縁膜 71 の各々は、たとえば二酸化珪素膜である。たとえば堆積酸化膜が絶縁膜 70 および層間絶縁膜 71 の各々に適用される。

#### 【0078】

絶縁膜 70 の厚みおよび絶縁膜 15b の厚みの合計は、たとえば 0.05 μm 程度以上かつ 2.0 μm 程度以下であってもよい。したがって、図 1 に示した構成から、絶縁膜 70 が省略されてもよい。あるいは、絶縁膜 70 上に、追加の絶縁膜 (たとえば窒化珪素膜) が設けられてもよい。

#### 【0079】

ドレイン電極 20 は、炭化珪素層 10 の第 2 の主面 10b に接して、n<sup>+</sup>基板 11 と電気的に接続される。ドレイン電極 20 は、たとえば上記ソース電極 16 と同様の構成を有していてもよい。あるいは、ドレイン電極 20 は、ニッケルなど、n<sup>+</sup>基板 11 とオーミック接合可能な他の材料からなっていてもよい。

#### 【0080】

裏面保護電極 50 は、ドレイン電極 20 に接する。したがって裏面保護電極 50 は、ドレイン電極 20 に電気的に接続される。裏面保護電極 50 は、たとえばチタン、ニッケル、銀あるいはそれらの合金からなる。

#### 【0081】

パッド電極 65 は、絶縁膜 70 および層間絶縁膜 71 に被せられるとともにソース電極 16 に接する。したがって、パッド電極 65 は、ソース電極 16 を介して、ソース領域 14 および p<sup>+</sup>領域 18 に電気的に接続される。パッド電極 65 はたとえばアルミニウムからなってもよい。また、パッド電極 65 の一部は、JTE 領域 2 とボディ領域 13 との境界を跨ぐように、絶縁膜 (絶縁膜 70 および絶縁膜 15b) 上に配置されていてもよい。

#### 【0082】

10

20

30

40

50

この実施の形態では、JTE領域2の幅w1は、15μm以上かつ50μm以下である。幅w1が15μm未満である場合には、炭化珪素半導体装置1のサイズを小さくすることが可能である。しかしJTE領域2において、電界集中を緩和する効果が弱くなりやすい。一方で、JTE領域2の幅w1が50μmを超えた場合、JTE領域2において電界集中を緩和する効果を十分に発揮させることが可能である。しかしながら炭化珪素半導体装置1のサイズが大きくなる。したがって、炭化珪素半導体装置1のサイズの増大をできるだけ抑えながら、炭化珪素半導体装置1の耐圧を十分に高くする観点から、JTE領域2の幅w1は、15μm以上かつ50μm以下とされることが好ましい。

#### 【0083】

JTE領域2に含まれる不純物のドーズ量は、 $1 \times 10^{13} \text{ cm}^{-2}$ 以上かつ $2 \times 10^{13} \text{ cm}^{-2}$ 以下の範囲にあることが好ましい。<sup>10</sup> JTE領域2に対する不純物のドーズ量が $1 \times 10^{13} \text{ cm}^{-2}$ 未満であると、たとえば炭化珪素半導体装置1の耐圧が十分に高くならないことが考えられる。一方、JTE領域2に対する不純物のドーズ量が $2 \times 10^{13} \text{ cm}^{-2}$ を超えた場合、JTE領域2による電界集中の緩和が弱くなりやすい。したがって、JTE領域2に対する不純物のドーズ量は、 $1 \times 10^{13} \text{ cm}^{-2}$ 以上かつ $2 \times 10^{13} \text{ cm}^{-2}$ 以下の範囲にあることが好ましい。

#### 【0084】

ガードリング領域3において、9本のガードリング部3a～3iの各々の幅w2～w10はたとえば5μmである。JTE領域2とガードリング領域3との間隔d1はたとえば2μm程度以上5μm程度以下である。隣り合う2つのガードリング部の間隔d2は、たとえば2μm程度以上5μm程度以下である。たとえば、JTE領域2の端部（JTE領域2とボディ領域13との境界）から、最も外側に位置するガードリング部（図2に示す構成では、ガードリング部3i）の端部までの幅は、20μm程度以上かつ200μm程度以下である。<sup>20</sup>

#### 【0085】

図3および図4を参照して、JTE領域2の不純物濃度とY方向の位置との関係について説明する。図4に示すように、Y方向は、炭化珪素層10の第1の主面10aの法線方向、言い換えると、深さ方向である。第1の主面10aを位置0とし、第1の主面10aから第2の主面10bに向かう方向を正としている。

#### 【0086】

図3に示される不純物濃度とは、JTE領域2に含まれる第2導電型不純物の濃度であり、具体的にはアクセプタ濃度である。なお、ドーズ量とは、上記の不純物濃度をY方向の位置で積分した量に対応する。<sup>30</sup>

#### 【0087】

図3では、p型不純物のピーク濃度のY方向における位置がピーク位置Pとして表される。ピーク位置Pは、位置0よりも、JTE領域2の内部の位置である。すなわち、本発明の実施の形態によれば、JTE領域2は、炭化珪素層10の第1の主面10aから離れた炭化珪素層10の内部の位置において、p型不純物のピーク濃度を有する。この実施形態では、ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下とされる。好ましくは、ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $2 \times 10^{17} \text{ cm}^{-3}$ 以下である。たとえば、JTE領域2では、第1の主面10a近傍におけるp型不純物の濃度が、 $1 \times 10^{17} \text{ cm}^{-3}$ 程度であり、ピーク位置Pにおけるp型不純物の濃度が、 $2 \times 10^{17} \text{ cm}^{-3}$ 程度である。ピーク位置Pは、位置0（第1の主面10a）から0.3μm以上かつ0.5μm以下の範囲内の位置である。<sup>40</sup>

#### 【0088】

図5は、本発明の実施の形態に係る炭化珪素半導体装置に、アバランシェブレークダウンが発生した状態を示す模式図である。図5を参照して、ボディ領域13とJTE領域2とは電気的に接続される。

#### 【0089】

この実施の形態では、炭化珪素半導体装置1はnチャネル型MOSFETである。炭化

10

20

30

40

50

珪素半導体装置 1 を使用する場合には、ドレイン電圧が、ソース電圧に対して高くなる。すなわち、高電圧下での炭化珪素半導体装置 1 の使用において、ソース電圧に対してドレイン電圧が高くなる。

#### 【 0 0 9 0 】

ドレイン電圧は、裏面保護電極 5 0 およびドレイン電極 2 0 を通じて炭化珪素層 1 0 (n<sup>+</sup>基板 1 1 およびドリフト層 1 2 ) に印加される。ソース電圧は、パッド電極 6 5 およびソース電極 1 6 を通じて、ソース領域 1 4 および p<sup>+</sup>領域 1 8 に印加される。さらに、ソース電圧は、p<sup>+</sup>領域 1 8 を通じてボディ領域 1 3 に印加される。J T E 領域 2 は、ボディ領域 1 3 に電気的に接続される。このため、ドリフト層 1 2 とボディ領域 1 3 との接合面、ドリフト層 1 2 およびドリフト層 1 2 と J T E 領域 2 との接合面から、空乏層(図示せず)が広がる。10

#### 【 0 0 9 1 】

さらに、ガードリング領域 3 (ガードリング部 3 a ~ 3 i の各々) とドリフト層 1 2 との接合面から空乏層が広がる。しかし、説明を単純にするために、ドリフト層 1 2 と J T E 領域 2 との接合面から広がる空乏層について説明する。

#### 【 0 0 9 2 】

J T E 領域 2 1 は、ボディ領域 1 3 よりも最も高い不純物濃度を有する。したがって、J T E 領域 2 において電界集中が発生する可能性がある。たとえば、J T E 領域 2 1 の端部 2 1 a では、接合面の曲率が大きいために電界が集中しやすい。このため、J T E 領域 2 の端部において、アバランシェブレークダウンが発生する可能性がある。20

#### 【 0 0 9 3 】

J T E 領域 2 においてアバランシェブレークダウンが発生すると、ドリフト層 1 2 から J T E 領域 2 に向けて逆方向電流 I<sub>r</sub> が流れる。逆方向電流 I<sub>r</sub> は、J T E 領域 2 からボディ領域 1 3 へと流れ、p<sup>+</sup>領域 1 8 およびソース電極 1 6 を介してパッド電極 6 5 へと流出される。

#### 【 0 0 9 4 】

逆方向電流 I<sub>r</sub> は、J T E 領域 2 の内部において、抵抗値のより低い部分を流れやすいと考えられる。抵抗値の低い部分とは、p 型不純物濃度の高い部分に対応する。図 3 に示される通り、J T E 領域 2 の深さ方向 (Y 方向) の不純物濃度のプロファイルは、炭化珪素層 1 0 の第 1 の主面 1 0 a から離れた位置においてピークを有する。したがって、逆方向電流 I<sub>r</sub> は、J T E 領域 2 の内部、より具体的には、不純物濃度のピークに近い部分を流れやすいと考えられる。30

#### 【 0 0 9 5 】

J T E 領域 2 およびガードリング領域 3 は、炭化珪素層 1 0 の第 1 の主面 1 0 a に接している。第 1 の主面 1 0 a は、炭化珪素層 1 0 と絶縁膜 1 5 b との界面に相当する。この実施の形態によれば、J T E 領域 2 あるいはガードリング領域 3 において、逆方向電流 I<sub>r</sub> は、炭化珪素層 1 0 と絶縁膜 1 5 b との界面から離れた部分を流れやすい。したがって、絶縁膜 1 5 b (酸化膜) の劣化を抑制することが可能になる。これにより、炭化珪素半導体装置 1 の寿命を長くすることができる。さらに、炭化珪素半導体装置 1 のアバランシエ耐量を高めることができる。40

#### 【 0 0 9 6 】

図 6 は、本発明の一実施の形態に係る炭化珪素半導体装置の製造方法を概略的に示したフロー・チャートである。図 6 を参照して、まず、炭化珪素層準備工程 (S 1 0) により、炭化珪素層 1 0 が準備される。図 7 を参照して、ポリタイプ 4 H を有する六方晶炭化珪素からなる n<sup>+</sup>基板 1 1 の一方の主面上に、エピタキシャル成長によりドリフト層 1 2 が形成される。

#### 【 0 0 9 7 】

たとえば原料ガスに、SiH<sub>4</sub> (シラン) と C<sub>3</sub>H<sub>8</sub> (プロパン) との混合ガスを採用して、エピタキシャル成長を実施することができる。エピタキシャル成長の際に、たとえば N (窒素) が n 型不純物として導入される。これにより、n<sup>+</sup>基板 1 1 に含まれる不純物50

よりも低い濃度の不純物を含むドリフト層 12 が形成される。炭化珪素層準備工程 (S 10) により、第 1 の主面 10a および第 2 の主面 10b を有し、かつ第 1 の導電型 (n 型) を有する炭化珪素層 10 が形成される。

#### 【0098】

この実施形態では、n<sup>+</sup>基板 11 の c 面にドリフト層 12 が形成される。本明細書では、c 面を、(0001) に対するオフ角が -8° 以上 8° 以下となる面と定義する。c 面にドリフト層 12 が形成されることにより、炭化珪素層 10 の第 1 の主面 10a は、c 面、すなわち (0001) に対するオフ角が -8° 以上 8° 以下となる面になる。

#### 【0099】

次に、図 6 に示す不純物領域形成工程 (S 20) が実施される。図 7 には示されないが、たとえば CVD により、二酸化珪素からなる酸化膜が、炭化珪素層 10 の第 1 の主面 10a 上に形成される。その酸化膜の上に、レジストが塗布された後、露光および現像が行なわれる。これにより、所望のボディ領域 13 の形状に応じた領域に開口を有するレジスト膜が形成される。そして、当該レジスト膜をマスクとして用いて、たとえば RIE (R e a c t i v e I o n E t c h i n g ; 反応性イオンエッチング) により酸化膜が部分的に除去されることによって、第 1 の主面 10a 上に、開口パターンを有する酸化膜からなるマスク層が形成される。

#### 【0100】

図 8 を参照して、炭化珪素層 10 の第 1 の主面 10a に対して不純物がイオン注入される。これにより、炭化珪素層 10 の素子領域 IR にボディ領域 13、ソース領域 14 および p<sup>+</sup>領域 18 が形成されるとともに、炭化珪素層 10 の終端領域 OR に、電界緩和領域としての JTE 領域 2 およびガードリング領域 3 が形成される。なお、ガードリング領域 3 は、複数のガードリング部 3a ~ 3i を有する。

#### 【0101】

具体的には、上記レジスト膜を除去した上で、マスク層をマスクとして用いて、A1 などの p 型不純物を、ドリフト層 12 に対してイオン注入することにより、ボディ領域 13 が形成される。P (リン) などの n 型不純物が、ドリフト層 12 のうちのボディ領域 13 に、イオン注入により導入されることにより、ソース領域 14 が形成される。次に、A1、B などの p 型不純物がドリフト層 12 のうちのボディ領域 13 に、イオン注入により導入されることにより、p<sup>+</sup>領域 18 が形成される。なお、300 から 500 程度の温度に炭化珪素層 10 を加熱しながらイオン注入が行なわれてもよい。

#### 【0102】

さらに、A1 などの p 型不純物をドリフト層 12 に対してイオン注入することにより、JTE 領域 2 およびガードリング領域 3 が形成される。JTE 領域 2 はボディ領域 13 と接するように形成される。さらに、JTE 領域 2 およびガードリング領域 3 の各々は、炭化珪素層 10 の第 1 の主面 10a に接するように形成される。

#### 【0103】

好ましくは、JTE 領域 2 への p 型不純物のドーズ量は、 $1 \times 10^{13} \text{ cm}^{-2}$  以上である。好ましくは、JTE 領域 2 への p 型不純物のドーズ量は、 $1 \times 10^{13} \text{ cm}^{-2}$  以上かつ  $2 \times 10^{13} \text{ cm}^{-2}$  以下の範囲 (一例としては、 $1.65 \times 10^{13} \text{ cm}^{-2}$ ) ある。ガードリング領域 3 の注入ドーズ量は、 $1 \times 10^{13} \text{ cm}^{-2}$  以上である。上記のとおり、ガードリング領域 3 に含まれる不純物のドーズ量を、JTE 領域 2 に含まれる不純物のドーズ量と同じ程度 (たとえば JTE 領域 2 に含まれる不純物のドーズ量を基準にして ± 5 % の範囲内) としてもよい。

#### 【0104】

次に、活性化アニール工程 (S 30) が実施される。工程 (S 30) では、イオン注入によって導入された不純物を活性化させる熱処理が実施される。具体的には、イオン注入が実施された炭化珪素層 10 が、たとえば Ar (アルゴン) 雰囲気中において 1700 程度に加熱され、30 分間程度保持される。

#### 【0105】

10

20

30

40

50

図6および図9を参照して、二酸化珪素膜形成工程(S40)が実施される。不純物領域が形成された炭化珪素層10の第1の主面10aが熱酸化される。熱酸化は、たとえば酸素含有ガス雰囲気中で、1100程度～1300程度に炭化珪素層10を加熱した状態を、40分間程度、保持することにより実施することができる。これにより、二酸化珪素膜15cが、炭化珪素層10の第1の主面10aに接して形成される。

#### 【0106】

熱酸化によって炭化珪素層10の第1の主面10aの珪素が酸素と結合して、二酸化珪素膜15c(熱酸化膜)が形成される。一方、第1の主面10a(c面)近傍に配置された炭素原子は、この熱酸化に伴って、炭化珪素層10の内部に移動(拡散)する。これにより、炭化珪素層10の内部における欠陥の密度を低減することができる。さらに、図10に示すように、第1の主面10aから炭化珪素層10の内部への炭素原子の移動(再配置)に伴って、主面10a近傍に配置されたp型不純物(アルミニウム(A1))を炭化珪素層10の内部へ移動させることができる。これにより、第1の主面10a近傍におけるp型不純物の濃度が低下する。第1の主面10aの近傍におけるp型不純物が炭化珪素層10の内部へと移動することにより、p型不純物の濃度は、JTE領域2の内部においてピークとなる。したがって、JTE領域2は、位置0(第1の主面10a)から0.3μm以上かつ0.5μm以下の範囲内の位置(ピーク位置P)において不純物濃度がピークとなる濃度プロファイルを有することができる。

#### 【0107】

ピーク濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下である。たとえば二酸化珪素膜形成工程(S40)前において、主面10a近傍における不純物濃度が $10^{17} \text{ cm}^{-3}$ オーダー(たとえば $2 \times 10^{17} \text{ cm}^{-3}$ ～ $3 \times 10^{17} \text{ cm}^{-3}$ )とされる。工程(S40)を実施することにより、図10に示される濃度プロファイルを形成することができる。

#### 【0108】

次に、図6に示す酸化膜除去工程(S50)が実施される。具体的には、フッ酸によるウェットエッチング処理により、図10に示された二酸化珪素膜15c(熱酸化膜)が除去される。したがって、工程(S40)は、犠牲酸化工程とみなすことができる。

#### 【0109】

次に、図6に示す素子形成工程(S60)が実施される。図1および図6を参照して、たとえば導電体であるポリシリコン、アルミニウムなどからなるゲート電極27が、一方のソース領域14上から他方のソース領域14上にまで延在するとともに、絶縁膜15に接触するように形成される。ゲート電極27の材料としてポリシリコンを採用する場合、当該ポリシリコンは、リンが $1 \times 10^{20} \text{ cm}^{-3}$ を超える高い濃度で含まれていてもよい。その後、ゲート電極27を覆うように、たとえば二酸化珪素からなる層間絶縁膜71が形成される。

#### 【0110】

次に、電極形成工程が実施される。たとえばニッケルおよびシリコンを含む材料からなるソース電極16がソース領域14およびp<sup>+</sup>領域18に接して形成される。ソース電極16は、チタン、アルミニウムおよびシリコンを含む材料であってもよい。ソース電極16が形成された炭化珪素層10が1000程度に加熱されることにより、ソース電極16がシリサイド化し、炭化珪素層10のソース領域14およびp<sup>+</sup>領域18とオーミック接合するソース電極16が形成される。同様に、炭化珪素層10の第2の主面10bにオーミック接合するドレイン電極20が形成される。ドレイン電極20を形成する材料は、ニッケルおよびシリコンを含む材料であってもよいし、チタン、アルミニウムおよびシリコンを含む材料であってもよい。ソース電極16と接し、たとえばアルミニウムからなるパッド電極65が形成される。また、たとえばチタン、ニッケルおよび銀を含む裏面保護電極50が形成される。以上の工程により、図1に示す炭化珪素半導体装置1(MOSFET)が完成する。

#### 【0111】

さらに、ガードリング領域3(ガードリング部3a～3iの各々)も、図3あるいは図

10

20

30

40

50

10に示される濃度プロファイルを有することができる。図11に示すY方向は、炭化珪素層10の第1の主面10aの法線方向であり、図4に示すY方向と一致する。すなわち、図3および図10に示す濃度プロファイルを有する不純物領域は、JTE領域2およびガードリング領域3の一方または両方を含むことができる。

#### 【0112】

以上のように、第1の実施の形態によれば、炭化珪素半導体装置1は、炭化珪素層10の第1の主面10aから離れた炭化珪素層10の内部においてp型不純物のピーク濃度を有する不純物領域を有する。この不純物領域は、JTE領域2およびガードリング領域3の一方または両方を含むことができる。これにより、炭化珪素半導体装置1のアバランシェ耐量を高めることができる。加えて、炭化珪素半導体装置1の寿命を長くすることができます。10

#### 【0113】

<第2の実施の形態>

第2の実施の形態に係る炭化珪素半導体装置の構成は、図1および図2に示された構成と同様である。さらに、第2の実施の形態に係る炭化珪素半導体装置の製造方法は、図3～図9により説明される製造方法と同様である。第2の実施の形態は、JTE領域2およびガードリング領域3の一方または両方におけるp型不純物の濃度プロファイルの点で、第1の実施の形態と異なる。

#### 【0114】

図12は、本発明の第2の実施形態における、p型不純物濃度領域の濃度プロファイルの模式図である。図6および図12を参照して、第2の実施形態では、不純物領域形成工程(S20)において、炭化珪素層10の第1の主面10aからの深さが大きくなるほどp型不純物の濃度が低下するように、p型不純物イオン(たとえばアルミニウム(A1))を注入する工程を含む。「炭化珪素層10の第1の主面10aからの深さが大きくなる」とは、Y方向の位置を示す値が大きくなることを意味する。たとえば、濃度プロファイルIM1(破線の曲線)によって示されるように、第1の主面10aの位置(位置0)におけるp型不純物濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 程度とされる。20

#### 【0115】

その後、活性化アニール工程(S30)を経て、二酸化珪素膜形成工程(S40)が実施される。第1の実施の形態と同様に、工程(S40)において、主面10a近傍に配置されたp型不純物(アルミニウム(A1))を炭化珪素層10の内部へ移動させて、第1の主面10a近傍におけるp型不純物の濃度を低下させる。この結果、JTE領域2は、位置0(第1の主面10a)から $0.3 \mu\text{m}$ 以上かつ $0.5 \mu\text{m}$ 以下の範囲内の位置において不純物濃度がピークとなる。30

#### 【0116】

第1の実施の形態と異なり、第2の実施の形態では、工程(S40)により、炭化珪素層10の第1の主面10aからの深さ方向に対してp型不純物の濃度が平坦となる部分PFを含む、濃度プロファイルIM2が形成される。平坦部分PFは、Y方向の位置が $0.3 \mu\text{m}$ から $0.5 \mu\text{m}$ までの範囲内に存在する、不純物濃度のフラットなピークの部分である。したがって、部分PFの不純物濃度は、 $1 \times 10^{16} \text{ cm}^{-3}$ 以上かつ $5 \times 10^{17} \text{ cm}^{-3}$ 以下の範囲内になる。40

#### 【0117】

「平坦」とは、Y方向の位置の変化に対して、不純物濃度がほぼ変化しないとみなすことができるることを意味する。たとえば、Y方向の位置が $0 \mu\text{m}$ から $0.3 \mu\text{m}$ まで変化するときにp型不純物の濃度が $1 \times 10^{17} \text{ cm}^{-3}$ 程度から $2 \times 10^{17} \text{ cm}^{-3}$ 程度へと変化する。これに対して、Y方向の位置が $0.3 \mu\text{m}$ から $0.5 \mu\text{m}$ まで変化するときには、p型不純物の濃度 $2 \times 10^{17} \text{ cm}^{-3}$ 程度から $1 \times 10^{16} \text{ cm}^{-3}$ 程度変化する。この例のように、Y方向の位置が $0 \mu\text{m}$ から $0.3 \mu\text{m}$ まで変化するときのp型不純物の濃度の変化量に対して、Y方向の位置が $0.3 \mu\text{m}$ から $0.5 \mu\text{m}$ まで変化するときのp型不純物の濃度の変化量が1桁小さい場合、不純物領域(たとえばJTE領域2)は、p型不純物濃度50

が平坦となる濃度プロファイルを有するとみなすことができる。

**【0118】**

第2の実施の形態によれば、第1の実施の形態と同様に、JTE領域2およびガードリング領域3の一方または両方を、炭化珪素層10の第1の主面10aから離れた炭化珪素層10の内部においてp型不純物のピーク濃度を有する不純物領域とすることができます。これにより、炭化珪素半導体装置1のアバランシェ耐量を高めることができます。さらに、炭化珪素半導体装置1の寿命を長くすることができます。

**【0119】**

特に、第2の実施の形態においては、炭化珪素層10の第1の主面10aから離れた炭化珪素層10の内部において、不純物領域（JTE領域2およびガードリング領域3の一方または両方）の不純物濃度プロファイルは、平坦な部分を有する。したがって、アバランシェブレークダウンが発生した場合に、逆方向電流Ir（図5を参照）が流れる部分（電流経路）の深さ方向の幅が大きくなる。すなわち、JTE領域2および/またはガードリング領域3に逆方向電流Irが流れる場合に、その領域における電流密度を低下させることができます。これにより、炭化珪素半導体装置1の破壊耐量をより高めることができます。さらに、炭化珪素半導体装置1の寿命をより長くすることができます。

10

**【0120】**

なお、図1に示されたMOSFETは、プレナー型MOSFETである。ただし、本発明の実施の形態として実現されるMOSFETは、トレンチ型MOSFETであってもよい。さらに、上記実施の形態では、炭化珪素半導体装置の一例としてMOSFETを例に挙げて説明したが、炭化珪素半導体装置は、ショットキーバリアダイオードなどのダイオードであってもよいし、IGBT（Insulated Gate Bipolar Transistor）などであってもよい。

20

**【0121】**

上記実施の形態では、第1の導電型がn型であり、かつ第2の導電型がp型である。これにより、炭化珪素半導体装置の製造のしやすさを向上させることができます。しかしながら第1の導電型がp型であり、かつ第2の導電型がn型であってもよい。

**【0122】**

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は上記した実施の形態ではなく特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

30

**【符号の説明】**

**【0123】**

- 1 炭化珪素半導体装置

- 2 JTE領域

- 3 ガードリング領域

- 3a～3i ガードリング部

- 4 フィールドストップ領域

- 5 境界

- 7 半導体素子部

- 10 炭化珪素層

- 10a 第1の主面

- 10b 第2の主面

- 10c 端部（炭化珪素層）

- 11 n<sup>+</sup>基板

- 12 ドリフト層

- 13 ボディ領域

- 14 ソース領域

- 15, 15b, 70 絶縁膜

40

50

### 1.5.a ゲート絶縁膜

15c 二酸化珪素膜

16 ソース電極

1 8 p + 領 域

20 ドレイン電極

27 ゲート電極

50 裏面保護電池

65 パッド電極

7.1 層間絶縁膜

C H チャネル領

TM1 濃度プロフ

T B 素子領域

王業領域

送力向電流

終端領域

## 終端領域 E—位置

P-E位置

卷一百一十五

八 方向

$d_1, d_2$  間

$$w_1 \sim w$$

【 四 1 】

【 図 2 】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

---

フロントページの続き

審査官 棚田 一也

(56)参考文献 国際公開第2012 / 137659 (WO, A1)

特開2012 - 129492 (JP, A)

特開2010 - 267783 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 06

H 01 L 21 / 336

H 01 L 29 / 12

H 01 L 29 / 78