(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5904240号

(P5904240)

(45) 発行日 平成28年4月13日(2016.4.13)

(24) 登録日 平成28年3月25日(2016.3.25)

(51) Int.Cl.

F 1

H03M 1/38 (2006.01)

H03M 1/46 (2006.01)H03M 1/38

H03M 1/46

請求項の数 15 (全 31 頁)

(21) 出願番号 特願2014-155183 (P2014-155183)

(22) 出願日 平成26年7月30日 (2014.7.30)

(62) 分割の表示 特願2010-249949 (P2010-249949)

の分割

原出願日 平成22年11月8日 (2010.11.8)

(65) 公開番号 特開2014-200116 (P2014-200116A)

(43) 公開日 平成26年10月23日 (2014.10.23)

審査請求日 平成26年8月29日 (2014.8.29)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 羽田 秀生

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】 A／D変換回路、電子機器及びA／D変換方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号に基づいてA／D変換を行い、A／D変換データを出力するA／D変換回路であって、

比較回路と、

前記比較回路からの比較結果信号により逐次比較結果データが設定される逐次比較レジスターを有し、逐次比較用データを出力する制御回路と、

前記制御回路からの前記逐次比較用データをD／A変換して、D／A出力信号を出力する第1のD／A変換回路と、

時間的に変化するコードデータを生成するコードデータ生成部と、

前記コードデータをD／A変換して、コード信号を出力する第2のD／A変換回路と、補正処理を行う補正部と、

を含み、

前記比較回路は、

前記入力信号のサンプリング信号と前記コード信号との加算信号を、前記D／A出力信号と比較する処理、又は前記D／A出力信号と前記コード信号との加算信号を、前記サンプリング信号と比較する処理を行い、

前記制御回路は、

前記逐次比較結果データと前記コードデータとに基づき求められる出力データを、前記A／D変換データとして出力し、

10

20

前記補正部は、

前記コードデータを用いたコードシフトによって前記比較回路による逐次比較結果がオーバーフローしないように補正する補正処理を、前記コードデータの符号と前記逐次比較結果データとに基づいて行うことを特徴とするA/D変換回路。

**【請求項2】**

請求項1において、

前記補正部は、

前記コードデータの符号を反転することで、前記コードシフトにより前記逐次比較結果がオーバーフローしないように補正する前記補正処理を行うことを特徴とするA/D変換回路。

10

**【請求項3】**

請求項1又は2において、

前記補正部は、

A/D入力電圧範囲の高電位側に前記逐次比較結果がオーバーフローする場合に、前記コードシフトの方向が低電位側になるように前記コードデータの符号を反転し、前記A/D入力電圧範囲の低電位側に前記逐次比較結果がオーバーフローする場合に、前記コードシフトの方向が高電位側になるように前記コードデータの符号を反転する前記補正処理を行うことを特徴とするA/D変換回路。

**【請求項4】**

請求項1乃至3のいずれか一項において、

20

前記補正部は、

前回の前記A/D変換での前記逐次比較結果データである前回逐次比較結果データが、A/D入力電圧範囲の高電位側の第1の範囲に対応するデータであり、且つ、前記コードシフトの方向が高電位側方向である場合に、今回の前記A/D変換での前記逐次比較結果データが低電位側にシフトするように、前記コードデータの符号を反転する前記補正処理を行い、

前記前回逐次比較結果データが、前記A/D入力電圧範囲の低電位側の第2の範囲に対応するデータであり、且つ、前記コードシフトの方向が低電位側方向である場合に、今回の前記A/D変換での前記逐次比較結果データが高電位側にシフトするように、前記コードデータの符号を反転する前記補正処理を行うことを特徴とするA/D変換回路。

30

**【請求項5】**

請求項4において、

前記コードデータ生成部は、

前記前回逐次比較結果データが、前記第1の範囲と前記第2の範囲の間の第3の範囲に対応するデータである場合には、交互に正、負となる前記コードデータを生成して前記第2のD/A変換回路に出力することを特徴とするA/D変換回路。

**【請求項6】**

請求項4又は5において、

前記補正部は、

前記前回逐次比較結果データが、前記第1の範囲又は前記第2の範囲に対応するデータであったか否かについての情報を記憶する情報レジスターを含むことを特徴とするA/D変換回路。

40

**【請求項7】**

請求項6において、

前記情報レジスターは、

複数のチャンネルの信号を時分割で前記A/D変換する場合に、前記複数のチャンネルの各チャンネルについて、前記前回逐次比較結果データが前記第1の範囲又は前記第2の範囲に対応するデータであったか否かについての前記情報を記憶することを特徴とするA/D変換回路。

**【請求項8】**

50

請求項 1 乃至 7 のいずれか一項において、

前記コードデータ生成部は、

所定のデータ範囲内において、1 又は複数回の A / D 変換タイミング毎に異なった値になるデータを、前記コードデータとして出力することを特徴とする A / D 変換回路。

## 【請求項 9】

請求項 8 において、

前記コードデータ生成部は、

2 のべき乗倍のオーバーサンプリングの前記 A / D 変換が行われる場合に、素数個のコードデータを生成して出力することを特徴とする A / D 変換回路。

## 【請求項 10】

請求項 1 乃至 9 のいずれか一項において、

前記第 1 の D / A 変換回路及び前記第 2 の D / A 変換回路は、電荷再分配型の D / A 変換回路であることを特徴とする A / D 変換回路。

## 【請求項 11】

請求項 10 において、

前記第 1 の D / A 変換回路は、

前記比較回路の比較ノードに一端が接続される複数のキャパシタを有する第 1 のキャパシタアレイ部と、

前記第 1 のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記逐次比較用データの上位ビットデータに基づきスイッチ制御される複数のスイッチ素子を有する第 1 のスイッチアレイ部と、

前記比較ノードと第 1 のノードとの間に設けられる第 1 の直列キャパシタと、

前記第 1 のノードに一端が接続される複数のキャパシタを有する第 2 のキャパシタアレイ部と、

前記第 2 のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記逐次比較用データの下位ビットデータに基づきスイッチ制御される複数のスイッチ素子を有する第 2 のスイッチアレイ部を含み、

前記第 2 の D / A 変換回路は、

前記比較ノードと第 2 のノードとの間に設けられる第 2 の直列キャパシタと、

前記第 2 のノードに一端が接続される複数のキャパシタを有する第 3 のキャパシタアレイ部と、

前記第 3 のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記コードデータに基づきスイッチ制御される複数のスイッチ素子を有する第 3 のスイッチアレイ部を含むことを特徴とする A / D 変換回路。

## 【請求項 12】

請求項 1 乃至 11 のいずれか一項において、

前記制御回路は、

前記サンプリング信号と前記コード信号との前記加算信号を、前記 D / A 出力信号と比較する前記処理が行われる場合に、前記逐次比較レジスターの前記逐次比較結果データから前記コードデータを減算する処理を行うことを特徴とする A / D 変換回路。

## 【請求項 13】

請求項 1 乃至 11 のいずれか一項において、

前記制御回路は、

前記 D / A 出力信号と前記コード信号との加算信号を、前記サンプリング信号と比較する前記処理が行われる場合に、前記逐次比較レジスターの前記逐次比較結果データに前記コードデータを加算する処理を行うことを特徴とする A / D 変換回路。

## 【請求項 14】

請求項 1 乃至 13 のいずれか一項に記載の A / D 変換回路を含むことを特徴とする電子機器。

## 【請求項 15】

10

20

30

40

50

比較回路と逐次比較レジスターとD/A変換回路とを有し、入力信号に基づいてA/D変換を行い、A/D変換データを出力する逐次比較型のA/D変換回路におけるA/D変換方法であって、

時間的に変化するコードデータに対応するコード信号を生成し、

前記入力信号のサンプリング信号と前記コード信号との加算信号を、前記D/A変換回路からのD/A出力信号と比較する処理、又は前記D/A出力信号と前記コード信号との加算信号を、前記サンプリング信号と比較する処理を、前記比較回路により行い、

前記逐次比較レジスターからの逐次比較結果データと前記コードデータとに基づき求められる出力データを、前記A/D変換データとして出力し、

前記コードデータを用いたコードシフトによって前記比較回路による逐次比較結果がオーバーフローしないように補正する補正処理を、前記コードデータの符号と前記逐次比較結果データとに基づいて行うことを特徴とするA/D変換方法。 10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、A/D変換回路、電子機器及びA/D変換方法等に関する。

##### 【背景技術】

##### 【0002】

従来より、アナログ信号をデジタルデータに変換するA/D変換回路として、逐次比較型のA/D変換回路が知られている。この逐次比較型のA/D変換回路は、比較回路と、逐次比較レジスターと、D/A変換回路を備え、入力信号をサンプリング（サンプル・ホールド）した信号を逐次比較動作によりA/D変換することでデジタルデータを出力する。このような逐次比較型のA/D変換回路の従来技術としては特許文献1等に開示される技術が知られている。 20

##### 【0003】

このようなA/D変換回路では、その変換精度の大部分はD/A変換回路の精度に依存する。そして、D/A変換回路の精度を高めようとすると、キャパシタの面積（電荷再分配型の場合）が抵抗の面積（ラダー抵抗型の場合）が要因となって、回路が大規模化してしまう。一方、回路の大規模化を抑制するために、D/A変換回路の回路に工夫を加えると、今度は、微分非直線性であるDNL（Differential Non Linearity）や積分非直線性であるINL（Integral Non Linearity）の誤差が原因で、いわゆるミッシングコードが発生するなどの問題が生じる。 30

##### 【0004】

また、このようなDNLやINLなどのA/D変換特性が改善したとしても、A/D変換のダイナミックレンジが減少してしまうと、A/D変換に求められる性能としては望ましくない。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

##### 【特許文献1】特開平8-321779号公報

40

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0006】

本発明の幾つかの態様によれば、A/D変換特性を改善しながらダイナミックレンジの減少も抑止できるA/D変換回路、電子機器、A/D変換方法等を提供できる。

##### 【課題を解決するための手段】

##### 【0007】

本発明の一態様は、比較回路と、前記比較回路からの比較結果信号によりレジスター値が設定される逐次比較レジスターを有し、逐次比較用データを出力する制御回路と、前記制御回路からの前記逐次比較用データをD/A変換して、前記逐次比較用データに対応す 50

る D / A 出力信号を出力する第 1 の D / A 変換回路と、時間的に変化するコードデータを D / A 変換して、前記コードデータに対応するコード信号を出力する第 2 の D / A 変換回路と、補正処理を行う補正部とを含み、前記比較回路は、入力信号のサンプリング信号と前記コード信号の加算信号と、前記 D / A 出力信号とを比較する処理、或いは前記サンプリング信号と、前記 D / A 出力信号と前記コード信号の加算信号とを比較する処理を行い、前記制御回路は、前記逐次比較レジスターの逐次比較結果データと前記コードデータとに基づき求められる出力データを、前記入力信号の A / D 変換データとして出力し、前記補正部は、前記コードデータを用いたコードシフトにより前記逐次比較結果データがオーバーフローするのを補正する補正処理を行う A / D 変換回路に関係する。

## 【0008】

10

本発明の一態様によれば、逐次比較レジスターを有する制御回路からの逐次比較用データが第 1 の D / A 変換回路に入力されて、逐次比較用データに対応する D / A 出力信号が出力される。また時間的に変化するコードデータが第 2 の D / A 変換回路に入力されて、コードデータに対応するコード信号が出力される。そして入力信号のサンプリング信号とコード信号の加算信号と、D / A 出力信号とを比較する処理、或いはサンプリング信号と、D / A 出力信号とコード信号の加算信号とを比較する処理が行われる。そして逐次比較結果データとコードデータとに基づき求められる出力データが、入力信号の A / D 変換データとして出力される。このようにすれば、時間的に変化するコードデータによりコードシフトが行われるようになり、A / D 変換特性を改善できる。

## 【0009】

20

更に本発明の一態様によれば、このようなコードデータを用いたコードシフトにより逐次比較結果データがオーバーフローしてしまうのを、補正処理により抑止できる。従って、コードシフトにより A / D 変換特性を改善しながら、コードシフトによるダイナミックレンジの減少も抑止することが可能になる。

## 【0010】

また本発明の一態様では、前記第 1 の D / A 変換回路の最小分解能を RS1、前記第 2 の D / A 変換回路の最小分解能を RS2 とした場合に、RS2 > RS1 であってもよい。

## 【0011】

このようにすれば、第 1 の D / A 変換回路の最小分解能 RS1 以上の大きさのコード信号の加算処理を行って、コードシフトを実現できるようになる。

30

## 【0012】

また本発明の一態様では、前記補正部は、前記コードデータを補正することで前記補正処理を行ってもよい。

## 【0013】

このようにすれば、コードシフトによるダイナミックレンジの減少を抑止する補正処理を、コードデータを補正するという簡素な処理で実現することが可能になる。

## 【0014】

また本発明の一態様では、前記補正部は、前回の A / D 変換での逐次比較結果データである前回逐次比較結果データに基づき前記コードデータを補正することで、前記補正処理を行ってもよい。

40

## 【0015】

このようにすれば、前回の A / D 変換での逐次比較結果データを利用し、今回の A / D 変換での逐次比較結果データがオーバーフローするかどうかを予測することで、コードシフトによるダイナミックレンジの減少を抑止する補正処理を実現できるようになる。

## 【0016】

また本発明の一態様では、前記補正部は、前記前回逐次比較結果データが、A / D 入力電圧範囲の高電位側の第 1 の範囲に対応するデータである場合には、今回の A / D 変換での前記逐次比較結果データが低電位側にシフトするように、前記コードデータの補正処理を行い、前記前回逐次比較結果データが、前記 A / D 入力電圧範囲の低電位側の第 2 の範囲に対応するデータである場合には、今回の A / D 変換での前記逐次比較結果データが高

50

電位側にシフトするように、前記コードデータの補正処理を行ってもよい。

【0017】

このようにすれば、前回逐次比較結果データが高電位側の第1の範囲のデータである場合には、逐次比較結果データが低電位側にシフトするようにコードデータを補正することで、コードシフトによりダイナミックレンジが減少するを抑止できる。また前回逐次比較結果データが低電位側の第2の範囲のデータである場合には、逐次比較結果データが高電位側にシフトするようにコードデータを補正することで、コードシフトによりダイナミックレンジが減少するのを抑止できる。

【0018】

また本発明の一態様では、前記コードデータを生成して前記第2のD/A変換回路に出力するコードデータ生成部を含み、前記コードデータ生成部は、前記前回逐次比較結果データが、前記第1の範囲と前記第2の範囲の間の第3の範囲に対応するデータである場合には、交互に正、負となる前記コードデータを生成して前記第2のD/A変換回路に出力してもよい。10

【0019】

このようにコードデータが交互に正、負になることで、コードデータの変化による周波数成分の影響を低減することができ、A/D変換特性への悪影響を抑止できる。

【0020】

また本発明の一態様では、前記補正部は、前記前回逐次比較結果データが、前記第1の範囲又は前記第2の範囲に対応するデータであったか否かについての情報を記憶する情報レジスターを含んでもよい。20

【0021】

このようにすれば、情報レジスターに記憶された情報に基づいて、前回逐次比較結果データが第1の範囲又は第2の範囲に対応するデータであったか否かを判断して、今回のA/D変換でのコードデータを補正することが可能になる。

【0022】

また本発明の一態様では、前記情報レジスターは、複数のチャンネルの信号が時分割でA/D変換される場合に、前記複数のチャンネルの各チャンネルについて、前記前回逐次比較結果データが前記第1の範囲又は前記第2の範囲に対応するデータであったか否かについての前記情報を記憶してもよい。30

【0023】

このようにすれば、複数のチャンネルの信号が時分割でA/D変換される場合にも、各チャンネルの前回逐次比較結果データが第1の範囲又は第2の範囲に対応するデータであったか否かを、情報レジスターに記憶された情報に基づき判断して、各チャンネルについてのコードデータを補正することが可能になる。

【0024】

また本発明の一態様では、前記コードデータを生成して、前記第2のD/A変換回路に対して出力するコードデータ生成部を含み、前記コードデータ生成部は、所定のデータ範囲内において、1又は複数回のA/D変換タイミング毎に異なった値になるデータを、前記コードデータとして出力してもよい。40

【0025】

このようにすれば、1又は複数回のA/D変換タイミング毎に異なった値になるコードデータに対応するコード信号の加算処理が行われて、コードシフトが実現される。これにより、例えばDNL特性の悪化を周囲のコードに時間的に拡散させて、A/D変換特性を改善できる。

【0026】

また本発明の一態様では、前記コードデータ生成部は、2のべき乗倍のオーバーサンプリングのA/D変換が行われる場合に、素数個のコードデータを生成して出力してもよい。50

【0027】

このようにすれば、オーバーサンプリングとコードシフトの相乗効果による A / D 変換特性の向上を実現できるようになる。

【0028】

また本発明の一態様では、前記第1のD / A 変換回路及び前記第2のD / A 変換回路は、電荷再分配型のD / A 変換回路であってもよい。

【0029】

なお第1、第2のD / A 変換回路の一部又は全部をラダー抵抗型で実現してもよい。

【0030】

また本発明の一態様では、前記第1のD / A 変換回路は、前記比較回路の比較ノードに一端が接続される複数のキャパシタを有する第1のキャパシタアレイ部と、前記第1のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記逐次比較用データの上位ビットデータに基づきスイッチ制御される複数のスイッチ素子を有する第1のスイッチアレイ部と、前記比較ノードと第1のノードとの間に設けられる第1の直列キャパシタと、前記第1のノードに一端が接続される複数のキャパシタを有する第2のキャパシタアレイ部と、前記第2のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記逐次比較用データの下位ビットデータに基づきスイッチ制御される複数のスイッチ素子を有する第2のスイッチアレイ部を含み、前記第2のD / A 変換回路は、前記比較ノードと第2のノードとの間に設けられる第2の直列キャパシタと、前記第2のノードに一端が接続される複数のキャパシタを有する第3のキャパシタアレイ部と、前記第3のキャパシタアレイ部の前記複数のキャパシタの他端に接続され前記コードデータに基づきスイッチ制御される複数のスイッチ素子を有する第3のスイッチアレイ部を含んでもよい。10

【0031】

このような構成の第1のD / A 変換回路を用いれば、回路面積の増加を最小限に抑えながら、A / D 変換の高ビット化を図れる。またこのような構成の第2のD / A 変換回路を用いれば、サンプリング信号と、D / A 出力信号とコード信号の加算信号とを比較する処理を実現できる。

【0032】

また本発明の一態様では、前記制御回路は、前記サンプリング信号と前記コード信号の加算信号と、前記D / A 出力信号との比較処理が行われる場合に、前記逐次比較レジスターの前記逐次比較結果データから前記コードデータを減算する処理を行ってもよい。30

【0033】

このようにすれば、サンプリング信号とコード信号の加算信号と、D / A 出力信号との比較処理が行われる場合に、コードデータの減算処理を行うことで、適正なA / D 変換データを出力できるようになる。

【0034】

また本発明の一態様では、前記制御回路は、前記サンプリング信号と、前記D / A 出力信号と前記コード信号の加算信号との比較処理が行われる場合に、前記逐次比較レジスターの前記逐次比較結果データに前記コードデータを加算する処理を行ってもよい。

【0035】

このようにすれば、サンプリング信号と、D / A 出力信号とコード信号の加算信号との比較処理が行われる場合に、コードデータの加算処理を行うことで、適正なA / D 変換データを出力できるようになる。40

【0036】

また本発明の他の態様は、上記のいずれかに記載のA / D 変換回路を含む電子機器に関係する。

【0037】

また本発明の他の態様は、比較回路と逐次比較レジスターとD / A 変換回路を有する逐次比較型のA / D 変換回路におけるA / D 変換方法であって、時間的に変化するコードデータに対応するコード信号を生成し、入力信号のサンプリング信号と前記コード信号の加算信号と、前記D / A 変換回路からのD / A 出力信号とを比較する処理、或いは前記サン50

プリング信号と、前記D/A出力信号と前記コード信号の加算信号とを比較する処理を行い、前記逐次比較レジスターからの逐次比較結果データと前記コードデータとに基づき求められる出力データを、前記入力信号のA/D変換データとして出力すると共に、前記コードデータを用いたコードシフトにより前記逐次比較結果データがオーバーフローするのを補正する補正処理を行うA/D変換方法に関する。

#### 【0038】

本発明の他の態様によれば、コードデータに対応するコード信号が生成され、入力信号のサンプリング信号とコード信号の加算信号と、D/A出力信号とを比較する処理、或いはサンプリング信号と、D/A出力信号とコード信号の加算信号とを比較する処理が行われる。そして逐次比較結果データとコードデータとに基づき求められる出力データが、入力信号のA/D変換データとして出力される。このようにすれば、時間的に変化するコードデータによりコードシフトが行われるようになり、A/D変換特性を改善できる。10

#### 【0039】

更に本発明の他の態様によれば、このようなコードデータを用いたコードシフトにより逐次比較結果データがオーバーフローしてしまうのを、補正処理により抑止できる。従つて、コードシフトによりA/D変換特性を改善しながら、コードシフトによるダイナミックレンジの減少も抑止することが可能になる。

#### 【図面の簡単な説明】

#### 【0040】

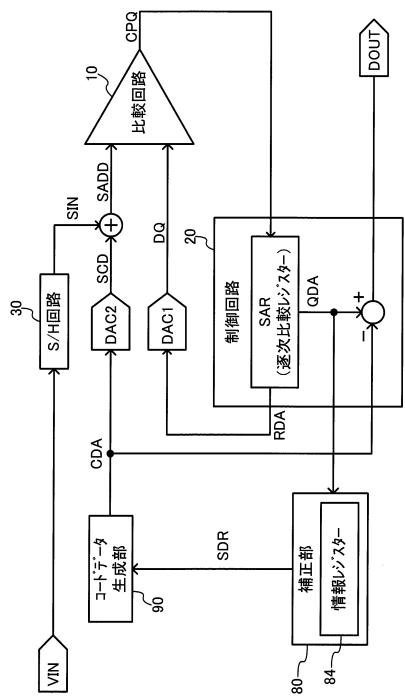

【図1】本実施形態のA/D変換回路の構成例。20

【図2】A/D変換回路の第1の比較例。

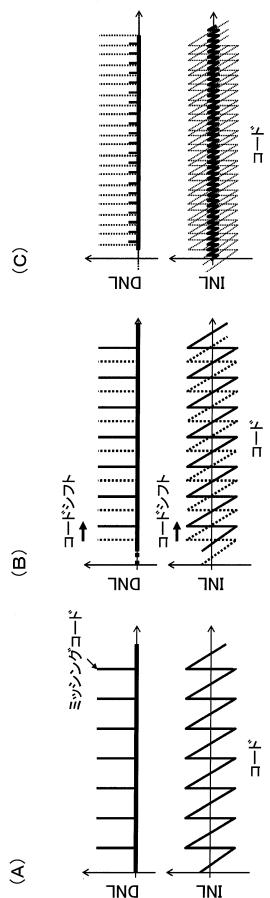

【図3】図3(A)～図3(C)は本実施形態のコードシフト手法の説明図。

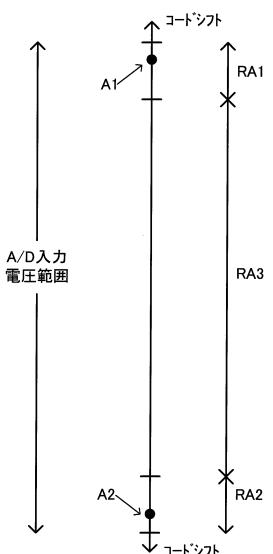

【図4】コードシフトによるダイナミックレンジの減少の問題点の説明図。

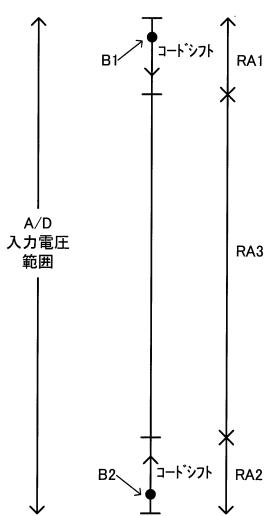

【図5】本実施形態の補正手法の説明図。

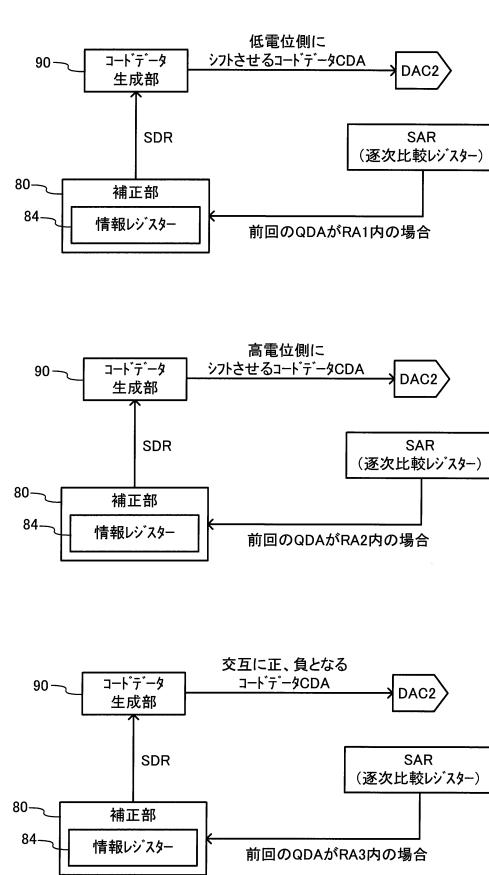

【図6】図6(A)～図6(C)は本実施形態によるコードデータの補正処理の説明図。

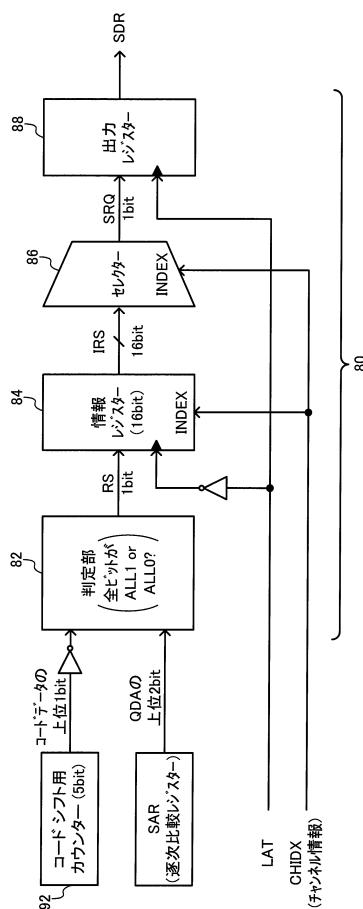

【図7】補正部の構成例。

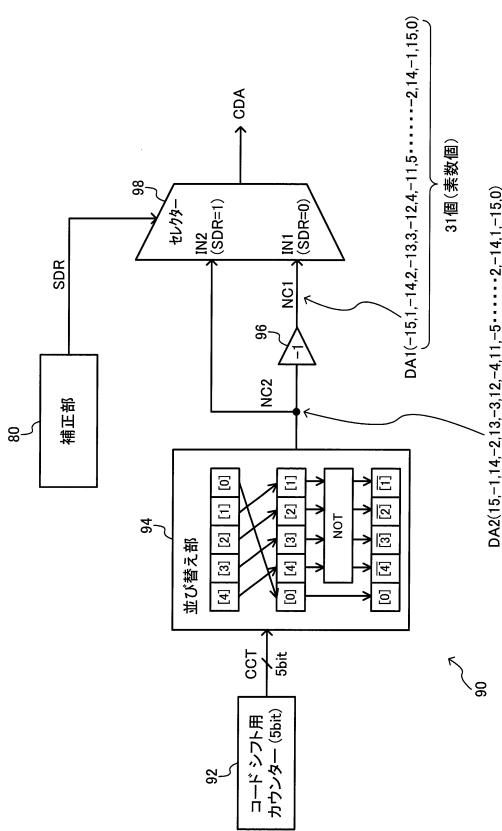

【図8】コードデータ生成部の構成例。

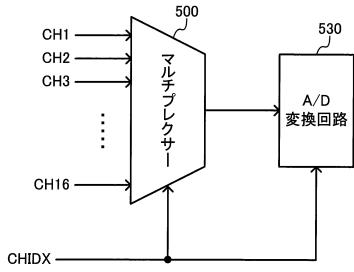

【図9】複数チャンネルの信号を時分割でA/D変換する手法の説明図。

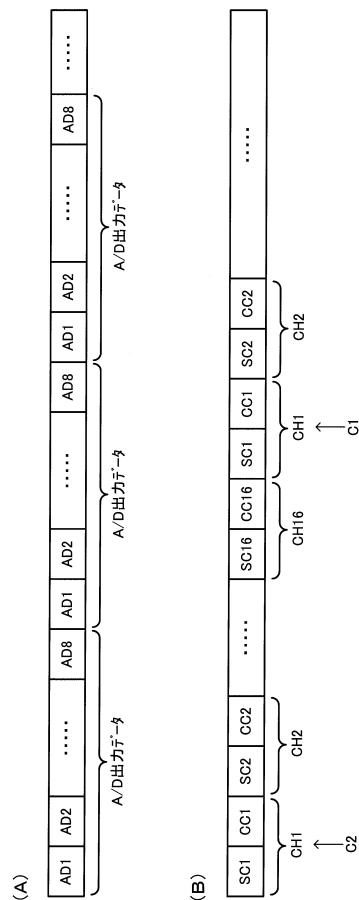

【図10】図10(A)、図10(B)はオーバーサンプリングのA/D変換手法や複数チャンネルの信号を時分割でA/D変換する手法の説明図。30

【図11】本実施形態のA/D変換回路の詳細な構成例。

【図12】A/D変換回路の動作を説明するための図。

【図13】A/D変換回路の第2の比較例。

【図14】A/D変換回路の第3の比較例。

【図15】寄生容量が及ぼす悪影響についての説明図。

【図16】図16(A)、図16(B)はDNL、INLの説明図。

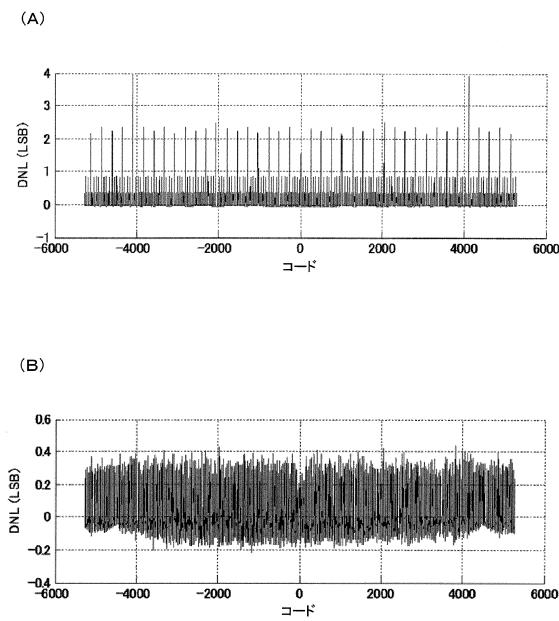

【図17】図17(A)、図17(B)はDNLのシミュレーション結果の例。

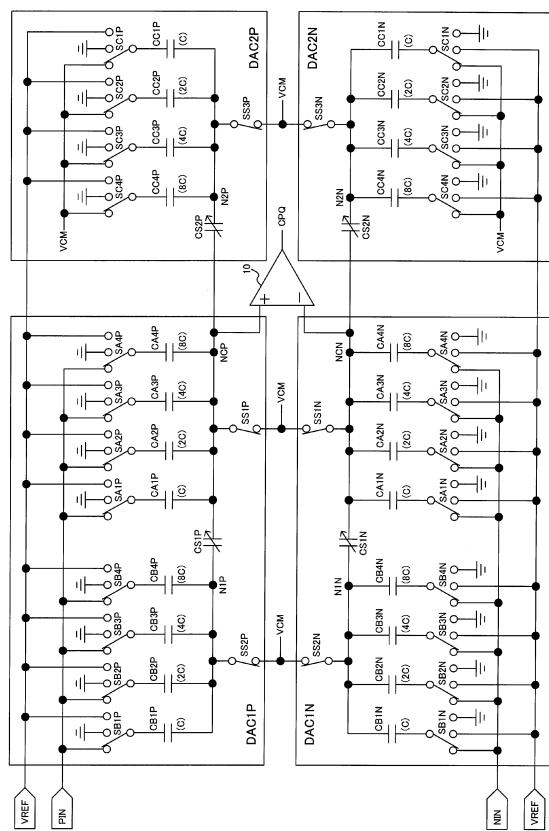

【図18】本実施形態の全差動型のA/D変換回路の構成例。

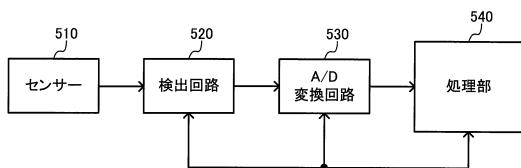

【図19】本実施形態の電子機器の構成例。

#### 【発明を実施するための形態】

#### 【0041】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

#### 【0042】

##### 1. 構成

図1に本実施形態のA/D変換回路の構成例を示す。このA/D変換回路は、比較回路10、制御回路20、第1のD/A変換回路DAC1、第2のD/A変換回路DAC2、補正部80を含む。また、S/H(サンプル・ホールド)回路30やコードデータ生成部90を含むことができる。50

**【 0 0 4 3 】**

なお、本実施形態の A / D 変換回路は図 1 の構成に限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えば S / H 回路 3 0 の構成要素を省略し、D / A 変換回路に入力信号 V I N のサンプル・ホールド機能を持たせてもよい。まだコードデータ生成部 9 0 の構成要素を省略し、コードデータ C D A を外部から直接に入力してもよい。

**【 0 0 4 4 】**

比較回路 1 0 は、コンパレーター（例えばラッチ型コンパレーター）により実現され、例えば信号 S A D D と信号 D Q の比較処理を行う。

**【 0 0 4 5 】**

制御回路 2 0 は、逐次比較レジスター S A R (Successive Approximation Register) を有し、逐次比較用データ R D A (D / A 入力データ) を出力する。逐次比較レジスター S A R は、比較回路 1 0 からの比較結果信号 C P Q によりそのレジスター値が設定されるレジスターである。例えば比較回路 1 0 が、M S B のビットから L S B のビットに至るまでの逐次比較処理を行った場合に、各ビットにおける比較処理結果（「1」、「0」）が、逐次比較レジスター S A R の各レジスター値として記憶される。

**【 0 0 4 6 】**

なお制御回路 2 0 は、A / D 変換回路の各回路ブロックの制御処理も行うこともできる。例えば D / A 変換回路 D A C 1、D A C 2 に含まれるスイッチ素子（スイッチアレイ）のオン・オフ制御を行う。

**【 0 0 4 7 】**

D / A 変換回路 D A C 1 は、制御回路 2 0 からの逐次比較用データ R D A の D / A 変換を行う。そして逐次比較用データ R D A に対応する D / A 出力信号 D Q (R D A を D / A 変換したアナログ信号) を出力する。この D / A 変換回路 D A C 1 は、キャパシタアレイを用いた電荷再分配型であってもよいし、その一部又は全部がラダー抵抗型であってもよい。

**【 0 0 4 8 】**

D / A 変換回路 D A C 2 は、コードデータ C D A を D / A 変換する。そしてコードデータ C D A に対応するコード信号 S C D (C D A を D / A 変換した信号) を出力する。ここでコードデータ C D A は時間的に変化するデータ（所定タイミング毎に変化するデジタルデータ）である。具体的には所定のデータ範囲内において、1 又は複数回の A / D 変換タイミング毎に異なった値になるデータである。

**【 0 0 4 9 】**

なおこの場合のデータ範囲は、第 1 のデジタルデータを上限値とし、第 2 のデジタルデータを下限値とする範囲である。A / D 変換タイミングは例えばデジタルデータをアナログ信号に変換する各 A / D 変換期間に対応するタイミングである。

**【 0 0 5 0 】**

S / H (サンプル・ホールド) 回路 3 0 は、A / D 変換の対象となる入力信号 V I N をサンプル・ホールドする回路である。なお電荷再分配型の場合には S / H 回路 3 0 の機能は D / A 変換回路により実現できる。

**【 0 0 5 1 】**

コードデータ生成部 9 0 は、コードデータ C D A を生成して D / A 変換回路 D A C 2 に出力する。例えば所定データ範囲内において、1 又は複数回の A / D 変換タイミング毎に異なった値になるコードデータ C D A を出力する。具体的には逐次比較用データの下位ビットデータのデータ範囲内において、1 又は複数回の A / D 変換タイミング毎に異なった値になるコードデータ C D A を出力する。

**【 0 0 5 2 】**

補正部 8 0 は補正処理を行う。具体的には、コードデータ C D A を用いたコードシフトによりダイナミックレンジが減少するのを防止するための補正処理を行う。この補正部 8 0 は情報レジスター 8 4 を有する。

10

20

30

40

50

## 【0053】

そして本実施形態では比較回路10は、入力信号VINのサンプリング信号SIN(VINをサンプル・ホールドした信号)とコード信号SCDの加算信号SADDと、D/A出力信号DQとを比較する処理を行う。具体的には比較回路10は、第1の入力端子に入力される加算信号SADD(加算電圧)と第2の入力端子に入力されるD/A出力信号DQ(D/A変換電圧)を比較する。なお、電荷再分配型の場合等では、比較回路10は、サンプリング信号SINと、D/A出力信号DQとコード信号SCDの加算信号とを比較する処理を行う。例えば信号SINのサンプリング電圧と、信号DQとSCDの加算電圧を比較する。

## 【0054】

そして制御回路20は、逐次比較レジスターSARからの逐次比較結果データQDA(最終的なデータ)とコードデータCDAとに基づき求められる出力データDOUTを、入力信号VINのA/D変換データとして出力する。例えば制御回路20は、図1のようにサンプリング信号SINとコード信号SCDの加算信号SADDと、D/A出力信号DQとの比較処理が行われる場合には、逐次比較レジスターSARの逐次比較結果データQDAからコードデータCDAを減算する処理を行う。一方、後述する電荷再分配型のように、サンプリング信号SINと、D/A出力信号DQとコード信号SCDの加算信号との比較処理が行われる場合には、逐次比較結果データQDAにコードデータCDAを加算する処理を行う。

## 【0055】

また補正部80は、コードデータCDAを用いたコードシフトにより逐次比較結果データQDAがオーバーフローするのを補正(防止)する補正処理を行う。ここでコードデータによるコードシフトとは、入力信号のサンプリング信号とコード信号の加算処理を行うこと或いはD/A出力信号とコード信号の加算処理を行うことで、逐次比較結果データが、入力信号に対応するデータから高電位側又は低電位側にシフトすることである。

## 【0056】

例えば補正部80は、コードデータCDAを補正することで当該補正処理を行う。そして補正指示信号SDRをコードデータ生成部90に出力する。具体的には、前回のA/D変換での逐次比較結果データである前回逐次比較結果データに基づきコードデータCDA(今回のコードデータ)を補正することで補正処理を行う。なお本実施形態の補正処理は、コードデータCDAを補正する処理には限定されず、逐次比較結果データQDAがオーバーフローするのを補正できるものであれば種々の変形実施が可能である。また前回逐次比較結果データに加えて、コードデータCDAの符号等を判定して、補正処理を行ってもよい。

## 【0057】

次に本実施形態のコードシフト手法について、A/D変換のビット数が8ビットである場合を例にとり説明する。

## 【0058】

まずS/H回路30が入力信号VINをサンプル・ホールドしてサンプリング信号SINを出力する。またコードデータ生成部90は、所定のデータ範囲内(例えば0000~1111)の任意のコードデータCDAを出力し、D/A変換回路DAC2がCDAに対応するコード信号SCDを出力する。

## 【0059】

制御回路20は、例えばMSBのビットが「1」に設定された逐次比較用データRDA=10000000を出力し、D/A変換回路DAC1がRDAに対応するD/A出力信号DQを出力する。

## 【0060】

そして比較回路10は、サンプリング信号SINにコード信号SCDを加算した信号SADDの電圧と、D/A出力信号DQの電圧を比較し、「1」又は「0」の比較結果信号CPQを出力する。例えば信号DQの電圧の方が信号SADDの電圧よりも大きければ「

10

20

30

40

50

「1」を出力し、小さければ「0」を出力する。これにより逐次比較レジスターSARのレジスター値のMSBのビットには「1」又は「0」が設定される。

#### 【0061】

次に制御回路20は、MSBの次のビットが「1」に設定された逐次比較用データRD A = 11000000又は01000000を出力する。例えばMSBの比較結果が「1」である場合にはRDA = 11000000を出力し、「0」である場合にはRDA = 01000000を出力する。するとD/A変換回路DAC1はRDAに対応するD/A出力信号DQを出力する。

#### 【0062】

そして比較回路10は、サンプリング信号SINにコード信号SCDを加算した信号S ADDの電圧と、D/A出力信号DQの電圧を比較し、「1」又は「0」の比較結果信号CPQを出力する。これにより逐次比較レジスターSARのレジスター値のMSBの次のビットには「1」又は「0」が設定される。10

#### 【0063】

以上のような逐次比較動作を、MSBのビットからLSBのビットに至るまで実行することで、最終的な逐次比較結果データQDAが取得される。即ち入力信号VINの電圧とD/A出力信号DQの電圧が等しくなるように逐次比較動作を行うことで、最終的な逐次比較結果データQDAが取得される。そして、取得された逐次比較結果データQDAからコードデータCDAを減算したデータが、入力信号VINをA/D変換したデータDOTとして出力される。20

#### 【0064】

図2に、本実施形態の第1の比較例のA/D変換回路を示す。この第1の比較例ではコードデータ生成部90や第2のD/A変換回路DAC2は設けられていない。そしてこの第1の比較例では、図3(A)に示すように、例えばDNLの誤差等が原因で特定のコードでミッシングコードが発生する。例えばDNLが1 LSBを超えると、出力コードが存在しないコードが発生するというミッシングコードの現象が生じる。

#### 【0065】

この点、本実施形態によれば、このようなミッシングコードが発生したとしても、時間的に変化するコードデータCDAの信号SCDを、サンプリング信号SINに加算することで、図3(B)に示すようなコードシフトが行われる。なお図3(B)の実線はコードシフト後の特性を表すものであり、破線はコードシフト前の特性を表すものである。30

#### 【0066】

即ち本実施形態では1又は複数回のA/D変換タイミング毎にコードデータCDAを異なった値にすることで、図3(B)に示すように、ミッシングコードが発生するコードの場所が1又は複数回のA/D変換タイミング毎に変化する。例えば00010000のコードでミッシングコードが発生したとしても、その場所が、00010001や00010010や00001111の場所にシフトする。この結果、長い時間範囲で見ると、図3(C)に示すようにDNLやINLが改善され、ミッシングコードの現象が生じない良好な特性を得ることができる。即ち、ある特定のコードで発生していたDNL特性の悪化(ミッシングコード)を、時間的に変化するコードデータCDAにより周囲のコードに拡散させることで、特性の改善を図っている。40

#### 【0067】

つまり図3(A)に示すようにミッシングコードが発生している状態で、入力電圧に意図的にオフセット電圧を加えた場合を考える。その時のDNL、INL特性は、図3(B)に示すように、あたかも加えたオフセット電圧に相当するコードだけシフトしたようになる。この場合に、A/D変換回路で変換されたデジタルデータは、オフセット電圧に相当するコードが加えられているので、オフセット電圧に相当するコードを減算することで最終結果が得られる。本実施形態のコードシフト手法は、この特性を利用し、入力電圧に毎回異なるオフセット電圧を加える。これを行うことで、図3(C)に示す特性のA/D変換回路で、見かけ上、変換を行っていることになる。50

**【 0 0 6 8 】**

例えば、ミッシングコードが発生しているコードに対応する電圧をA / D変換する場合を考える。コードシフトを行わない場合、この入力電圧周辺では非線形な変換が行われてしまう。これに対して、ある値だけコードシフトを行った場合、上記の入力電圧周辺では、線形性が良い変換が行われる。つまり、さまざまな値でコードシフトさせることで、あるコードシフト値では非線形であるが、大半のコードシフト値では線形な変換が行われる。最終的に、コードシフトを行うことで、本来ミッシングコードが発生している入力電圧においても比較的線形な変換が行われるようになる。

**【 0 0 6 9 】**

以上のように、本実施形態によれば、コードデータCDAを発生して加算するという簡単な処理により、ミッシングコードの発生を防止し、A / D変換回路のDNLやINLの特性を改善することに成功している。10

**【 0 0 7 0 】****2 . 補正処理**

さて、以上のように説明したコードシフト手法には、ダイナミックレンジが減少してしまう問題があることが判明した。即ち、ダイナミックレンジの限界付近の入力電圧の時に、コードシフトによるオフセット電圧を加えてしまうと、実際にA / D変換するデータはダイナミックレンジをオーバーしてしまうので、実効的にダイナミックレンジが減少してしまう。

**【 0 0 7 1 】**

このような問題を回避するため、本実施形態では例えば前回の変換値を記憶しておく、コードシフトによってダイナミックレンジをオーバーしそうな場合は、記憶しておいた変換値に基づいて、ダイナミックレンジをオーバーしないコードデータを生成する。そして生成されたコードデータをコードシフト用のD / A変換回路DAC2に入力することで、ダイナミックレンジの劣化を回避する。20

**【 0 0 7 2 】**

例えば図4において、A / D入力電圧範囲はA / D変換回路のダイナミックレンジを表すものであり、A / D変換回路は、このA / D入力電圧範囲の入力電圧については適正にA / D変換を行うことが可能になっている。

**【 0 0 7 3 】**

そして、入力電圧がA / D入力電圧範囲の高電位側の第1の範囲RA1である場合に、A1に示すように高電位側方向（正方向）へのコードシフトが行われてしまうと、ダイナミックレンジをオーバーしてしまい、実効的にダイナミックレンジが減少してしまう。同様に、入力電圧がA / D入力電圧範囲の低電位側の第2の範囲RA2である場合に、A2に示すように低電位側方向（負方向）へのコードシフトが行われてしまうと、ダイナミックレンジをオーバーしてしまい、実効的にダイナミックレンジが減少してしまう。30

**【 0 0 7 4 】**

このような問題を解決するために、本実施形態では、入力電圧が高電位側の第1の範囲RA1である場合には、図5のB1に示すようにA / D変換結果が低電位側にシフトするようにコードデータを補正する。また入力電圧が低電位側の第2の範囲RA2である場合には、B2に示すようにA / D変換結果が高電位側にシフトするようにコードデータを補正する。なお、第1の範囲RA1は、例えばA / D入力電圧範囲の最大電圧（例えば電源電圧）を含む高電位側の電圧範囲であり、第2の範囲RA2は、例えばA / D入力電圧範囲の最少電圧（例えば0V）を含む低電位側の電圧範囲である。また第3の電圧範囲RA3は第1の範囲RA1と第2の範囲RA2の間の電圧範囲（中間電圧範囲）である。40

**【 0 0 7 5 】**

例えば本実施形態では補正部80は、前回のA / D変換での逐次比較結果データである前回逐次比較結果データに基づきコードデータを補正する。

**【 0 0 7 6 】**

具体的には図6(A)に示すように補正部80は、前回の逐次比較結果データQDAが50

、 A / D 入力電圧範囲の高電位側の第 1 の範囲 R A 1 に対応するデータである場合には、今回の A / D 変換での逐次比較結果データ Q D A が低電位側にシフトするように、コードデータ C D A の補正処理を行う。例えば前回の逐次比較結果データ Q D A が第 1 の範囲 R A 1 内のデータであり、コードシフトの方向が図 4 の A 1 に示すように高電位側方向（正方向）であったとする。この場合には、コードデータ生成部 9 0 は、補正部 8 0 からの補正指示信号 S D R により、図 5 の B 1 に示すように逐次比較結果データ Q D A が低電位側方向にシフトするように、コードデータ C D A を補正して、コードシフト用の第 2 の D / A 変換回路 D A C 2 に出力する。

#### 【 0 0 7 7 】

また図 6 ( B ) に示すように補正部 8 0 は、前回の逐次比較結果データ Q D A が、A / D 入力電圧範囲の低電位側の第 2 の範囲 R A 2 に対応するデータである場合には、今回の A / D 変換での逐次比較結果データ Q D A が高電位側にシフトするように、コードデータ C D A の補正処理を行う。例えば前回の逐次比較結果データ Q D A が第 2 の範囲 R A 2 内のデータであり、コードシフトの方向が図 4 の A 2 に示すように低電位側方向（負方向）であったとする。この場合には、コードデータ生成部 9 0 は、補正部 8 0 からの補正指示信号 S D R により、図 5 の B 2 に示すように逐次比較結果データ Q D A が高電位側方向にシフトするように、コードデータ C D A を補正して、第 2 の D / A 変換回路 D A C 2 に出力する。

#### 【 0 0 7 8 】

また前回の逐次比較結果データ Q D A が、図 5 の第 1 の範囲 R A 1 と第 2 の範囲 R A 2 の間の第 3 の範囲 R A 3 に対応するデータであったとする。この場合には図 6 ( C ) に示すように、コードデータ生成部 9 0 は、交互に正、負となるコードデータを生成して、第 2 の D / A 変換回路 D A C 2 に出力する。

#### 【 0 0 7 9 】

補正部 8 0 が含む情報レジスター 8 4 は、前回の逐次比較結果データ Q D A が、第 1 の範囲 R A 1 又は第 2 の範囲 R A 2 に対応するデータであったか否かについての情報を記憶する。なお、後述するように複数のチャンネルの信号が時分割で A / D 変換される場合には、情報レジスター 8 4 は、複数のチャンネルの各チャンネルについて、前回の逐次比較結果データが第 1 の範囲 R A 1 又は第 2 の範囲 R A 2 に対応するデータであったか否かについての情報を記憶する。

#### 【 0 0 8 0 】

具体的には補正部 8 0 は、例えば前回の A / D 変換での逐次比較結果データ Q D A が第 1 の範囲 R A 1 のデータであり且つコードシフトの方向が高電位側方向であるか否か、或いは、前回の逐次比較結果データ Q D A が第 2 の範囲 R A 2 のデータであり且つコードシフトの方向が低電位側方向であるか否かを判定する。この判定結果情報が情報レジスター 8 4 に記憶される。そして補正部 8 0 は、記憶された判定結果情報に基づいて補正指示信号 S D R を生成して、コードデータ生成部 9 0 に出力し、コードデータ C D A の補正を指示する。これによりコードデータ生成部 9 0 が、今回の A / D 変換でのコードデータ C D A を補正して、第 2 の D / A 変換回路 D A C 2 に出力する。

#### 【 0 0 8 1 】

##### 3 . 補正部、コードデータ生成部

図 7、図 8 に補正部 8 0 、コードデータ生成部 9 0 の構成例を示す。なお、補正部 8 0 、コードデータ生成部 9 0 は図 7、図 8 の構成に限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【 0 0 8 2 】

補正部 8 0 は、判定部 8 2 、情報レジスター 8 4 、セレクター 8 6 、出力レジスター 8 8 を含む。

#### 【 0 0 8 3 】

判定部 8 2 は、コードシフト用カウンター 9 2 から、コードデータの符号ビットである上位の 1 ビットを反転した反転符号ビットを受ける。また逐次比較レジスター S A R から

10

20

30

40

50

、逐次比較結果データQ D Aの上位の2ビットを受ける。コードシフト用カウンター92は、5ビットのカウンターであり、2の補数表現の5ビットのコードデータを出力する。従って、コードデータの上位の1ビットは符号ビットになる。また逐次比較レジスターS A Rからの逐次比較結果データQ D Aの上位の2ビットは、M S BビットとM S Bの次のビットである。

#### 【0084】

判定部82は、コードデータの反転符号ビットと逐次比較結果データQ D Aの上位の2ビットからなる3ビットの全てが、「1」或いは「0」かを判断し、全てが「1」或いは「0」である場合には、判定結果信号R S = 1を出力する。

#### 【0085】

ここで、コードデータの上位の1ビットが「1」であることはコードデータの符号が正であることを意味し、「0」であることは符号が負であることを意味する。そして後述するようにコードデータはA / D変換毎に交互に正、負になる。従って、判定部82に入力される反転符号ビットが「1」であることは、前回のA / D変換でのコードデータの符号が負であり、今回のA / D変換のコードデータの符号が正になることを意味する。また反転符号ビットが「0」であることは、前回のA / D変換でのコードデータの符号が正であり、今回のA / D変換のコードデータの符号が負になることを意味する。

#### 【0086】

また逐次比較結果データQ D Aの上位の2ビットが「11」であることは、Q D Aが図5の第1の範囲R A 1に対応するデータであることを意味し、上位の2ビットが「00」であることは、Q D Aが第2の範囲R A 2に対応するデータであることを意味する。

#### 【0087】

そして、コードデータの反転符号ビットと逐次比較結果データQ D Aの上位の2ビットからなる3ビットが「111」又は「000」である場合に、判定結果信号がR S = 1になる。従って、判定結果信号R S = 1は、前回のA / D変換の逐次比較結果データQ D Aが第1の範囲R A 1内であり且つ今回のコードデータの符号が正（シフト方向が高電位側方向）であること、或いは、Q D Aが第2の範囲R A 2内であり且つ今回のコードデータの符号が負（シフト方向が低電位側方向）であることを意味する。

#### 【0088】

情報レジスター84は、判定部82から判定結果信号R Sを受けて記憶する。ここで図9に示すように、本実施形態ではA / D変換回路530が複数チャンネルC H 1 ~ C H 16の信号を時分割でA / D変換している。即ちA / D変換回路530の前段側にマルチブレクサー500が設けられ、このマルチブレクサー500が、チャンネル選択用のインデックス信号C H I D Xに基づいて複数チャンネルC H 1 ~ C H 16のうちの1つのチャンネルの信号を選択する。そしてA / D変換回路530は、選択されたチャンネルの信号（電圧）をA / D変換する。この時、インデックス信号C H I D XはC H 1、C H 2、C H 3 … C H 16の順でチャンネルの選択を指示するため、A / D変換回路530は、C H 1、C H 2、C H 3 … C H 16の順で各チャンネルの信号をA / D変換することになる。

#### 【0089】

情報レジスター84は、C H 1 ~ C H 16の16チャンネル（広義にはNチャンネル）に対応する16ビット（広義にはNビット）のレジスターになっている。情報レジスター84は、上述したチャンネル選択用のインデックス信号C H I D Xと判定部82からの1ビットの判定結果信号R Sを受ける。そして、判定結果情報I R Sの16ビットのうち、現在A / D変換中のチャンネルに対応するビットを、判定結果信号R Sの値に設定する。例えば判定結果信号R Sが「1」である場合には、判定結果情報I R Sの対応するビットは「1」に設定され、R Sが「0」である場合にはI R Sの対応するビットは「0」に設定される。例えばチャンネルC H 1では、逐次比較結果データQ D Aが第1の範囲R A 1内であり且つコードデータの符号が正（或いはR A 2内であり且つ符号が負）であり、他のチャンネルC H 2 ~ C H 16では、Q D Aが第3の範囲R A 3内であったとする。この

10

20

30

40

50

場合には、判定結果情報IRSは「1000000000000000」に設定される。

#### 【0090】

セレクター86は情報レジスター84から判定結果情報IRSを受ける。そして、16ビットの判定結果情報IRSのビットのうち、チャンネル選択用のインデックス信号CHIDXで指定されるチャンネルに対応するビットの値を、1ビットの信号SRQとして出力する。例えば判定結果情報IRSが前述のように「1000000000000000」であり、インデックス信号CHIDXがチャンネルCH1を指定していた場合には、セレクター86は信号SRQ=1を出力する。一方、インデックス信号CHIDXがチャンネルCH2～CH16を指定していた場合には、セレクター86は信号SRQ=0を出力する。

10

#### 【0091】

出力レジスター88は、セレクター86からの信号SRQをラッチし、ラッチした信号を次のA/D変換のタイミングで補正指示信号SDRとしてコードデータ生成部90に出力する。

#### 【0092】

以上のようにすることで、前回のA/D変換における逐次比較結果データが第1の範囲RA1であり且つ今回のA/D変換でのコードシフトの方向が高電位側方向（コードデータの符号が正）である場合には、今回のA/D変換における補正指示信号はSDR=1になる。同様に、前回のA/D変換における逐次比較結果データが第2の範囲RA2であり且つ今回のA/D変換でのコードシフトの方向が低電位側方向（コードデータの符号が負）である場合にも、今回のA/D変換における補正指示信号はSDR=1になる。一方、前回の逐次比較結果データが第3の範囲RA3である場合には、今回のA/D変換における補正指示信号はSDR=0になる。従って、コードデータ生成部90が、補正指示信号がSDR=1になった場合にコードデータの符号を反転させることで、コードシフトによるオーバーフローを防止できるようになる。

20

#### 【0093】

図8に示すように、コードデータ生成部90は、コードシフト用カウンター92、並び替え部94、反転部96、セレクター98を含む。

#### 【0094】

コードシフト用カウンター92は、前述のように5ビットのカウンターであり、5ビットのカウント値CCTを生成して、並び替え部94に出力する。並び替え部94は、5ビットのカウント値CCTをバイナリで並び替えて、15、-1、14、-2、13、-3、12、-4、11、-5……2、-14、1、-15、0というような-15～+15の範囲の31個（広義には素数個）のデータDA2を、ノードNC2に順次出力する。反転部96はノードNC2のデータDA2の符号を反転して、-15、1、-14、2、-13、3、-12、4、-11、5……-2、14、-1、15、0というような-15～+15の範囲の31個のデータDA1を順次出力する。

30

#### 【0095】

セレクター98は、補正部80からの補正指示信号SDRに基づいてデータDA1、DA2のいずれかを選択して、コードデータCDAとして出力する。例えばSDR=0である場合には、端子IN1に入力されるデータDA1を選択してコードデータCDAとして出力する。SDR=1である場合には、端子IN2に入力されるデータDA2を選択してコードデータCDAとして出力する。データDA2はデータDA1の符号を反転したデータになる。従って、補正指示信号がSDR=1になると、DA1を反転した信号がコードデータCDAとして出力されるようになる。

40

#### 【0096】

例えば前回の逐次比較結果データQDAが図5の第1の範囲RA1内であり、データDA1が14であったとする。この場合に、このデータDA1=14が今回のコードデータとしてセレクター98により選択されてしまうと、図4のA1に示すようにダイナミックレンジの正側へのオーバーフローが生じてしまう。従って、この場合には補正指示信号が

50

$S\ D\ R = 1$  になり、セレクター 98 がデータ  $D\ A\ 1 = 1\ 4$  の符号を反転したデータ  $D\ A\ 2 = -1\ 4$  を選択する。従って、コードデータ  $C\ D\ A$  として  $D\ A\ 2 = -1\ 4$  が出力されるようになり、図 5 の B 1 に示すようにダイナミックレンジの正側へのオーバーフローが抑止される。

#### 【0097】

一方、前回の逐次比較結果データ  $Q\ D\ A$  が第 2 の範囲  $R\ A\ 2$  内であり、データ  $D\ A\ 1$  が  $-1\ 5$  であったとする。この場合に、このデータ  $D\ A\ 1 = -1\ 5$  が今回のコードデータとして選択されてしまうと、図 4 の A 2 に示すようにダイナミックレンジの負側へのオーバーフローが生じてしまう。従って、この場合にも補正指示信号が  $S\ D\ R = 1$  になり、セレクター 98 がデータ  $D\ A\ 1 = -1\ 5$  の符号を反転したデータ  $D\ A\ 2 = 1\ 5$  を選択する。従って、コードデータ  $C\ D\ A$  として  $D\ A\ 2 = 1\ 5$  が出力されるようになり、図 5 の B 2 に示すようにダイナミックレンジの負側へのオーバーフローが抑止される。10

#### 【0098】

以上のように本実施形態によれば、コードデータを用いたコードシフトにより逐次比較結果データがオーバーフローするのが補正されるため、コードシフトによるダイナミックレンジの減少を抑止できる。従って、コードシフトにより A / D 変換回路の  $D\ N\ L$  や  $I\ N\ L$  の特性を改善しながら、コードシフトを要因とするダイナミックレンジの減少も抑止できるようになる。

#### 【0099】

なお、前回の逐次比較結果データ  $Q\ D\ A$  が第 3 の範囲  $R\ A\ 3$  内である場合には、補正指示信号が  $S\ D\ R = 0$  になるため、セレクター 98 によりデータ  $D\ A\ 1$  が選択されて、交互に正、負となるコードデータ  $C\ D\ A$  が出力されるようになる。このようにコードデータ  $C\ D\ A$  が交互に正、負になることで、コードデータ  $C\ D\ A$  の変化の周波成分（低周波成分）が、A / D 変換特性に悪影響を及ぼす事態を抑止できる。即ち、コードデータ  $C\ D\ A$  が交互に正、負になることで、コードデータ  $C\ D\ A$  の変化の周波数成分が高周波数側がシフトする。そして、このような高周波数成分については、例えば A / D 変換回路の後段のデジタルフィルター（ローパスフィルター）によりカットできるため、コードデータ  $C\ D\ A$  の変化の周波数成分の影響を低減することができ、A / D 変換特性への悪影響を抑止できるようになる。20

#### 【0100】

また図 1 のように入力信号のサンプリング信号  $S\ I\ N$  とコード信号  $S\ C\ D$  の加算信号と、D / A 出力信号  $S\ C\ D$  とを比較する方式を採用した場合には、正の符号のコードデータは  $Q\ D\ A$  を高電位側方向にシフトさせるデータになり、負の符号のコードデータは  $Q\ D\ A$  を低電位側方向にシフトさせるデータになる。しかしながら、サンプリング信号  $S\ I\ N$  と、D / A 出力信号  $D\ Q$  とコード信号  $S\ C\ D$  の加算信号とを比較する方式を採用した場合には、正の符号のコードデータは  $Q\ D\ A$  を低電位側方向にシフトさせるデータになり、負の符号のコードデータは  $Q\ D\ A$  を高電位側方向にシフトさせるデータになる。30

#### 【0101】

##### 4. オーバーサンプリング

本実施形態では、2 のべき乗倍のオーバーサンプリングの A / D 変換を行っている。例えば 8 倍のオーバーサンプリングを例にとれば、図 10 (A) に示すように、8 回の A / D 変換  $A\ D\ 1 \sim A\ D\ 8$  が行われる毎に、最終的な 1 個の A / D 出力データが出力される。即ち、本来必要な帯域よりも広い帯域（速い周波数）で A / D 変換回路を動作させ、A / D 変換回路の後段のデジタルフィルターを用いて必要な帯域にフィルターを掛けて信号を取り出す。この時に、必要な帯域外の量子化ノイズがデジタルフィルターにより除去され、その結果、S N R (Signal to Noise Ratio) が向上する。例えば O S R (Over-Sampling-Ratio) を 2 倍にすると、理論上は、S N R は 3 d B (0.5 ビット) だけ改善する効果が得られる。またオーバーサンプリングを行うことで、A / D 変換回路の前段の前置きフィルターの次数を減少させることができるというメリットもある。40

#### 【0102】

しかしながら、このようなオーバーサンプリングのA / D変換を行った時に、コードデータの変化の周期と、オーバーサンプリングの周期の間に相関性があると、オーバーサンプリングによるS N Rの向上が抑制されてしまうおそれがある。例えば図10(A)のように2のべき乗倍のオーバーサンプリングが行われる場合に、コードデータの個数も2のべき乗個であると、2のべき乗回の各A / D変換と各コードデータとの対応づけが一定になってしまう。従って、オーバーサンプリングとコードシフトの相乗効果によるS N R等の向上が抑制されてしまう。

#### 【0103】

そこで本実施形態ではコードデータ生成部90は、2のべき乗倍(2倍、4倍、8倍、16倍、32倍等)のオーバーサンプリングのA / D変換が行われる場合に、素数個のコードデータを生成するようにしている。図8を例にとれば、コードデータ生成部90は、素数個である31個のコードデータを生成して順次出力する。このようにすれば、2のべき乗回の各A / D変換と各コードデータとの対応づけが一定にならないようになる。従って、オーバーサンプリングとコードシフトの相乗効果によるS N R等の向上を実現できる。

#### 【0104】

なおオーバーサンプリングのA / D変換は図10(A)の手法に限定されず、種々の変形実施が可能である。またコードデータの個数や生成パターンも図8に示した例には限定されない。

#### 【0105】

また図9に示すように複数チャンネルの信号を時分割でA / D変換する場合には、図10(B)に示すようにA / D変換回路は動作することになる。例えばチャンネルC H 1の信号についてのサンプリングS C 1及び変換C C 1を実行した後に、チャンネルC H 2の信号についてのサンプリングS C 2及び変換C C 2を実行する。その後、同様にしてC H 3 ~ C H 16の各チャンネルのサンプリング及び変換を順次実行する。この場合に図10(B)のC 1が今回のA / D変換である場合には、C 2が前回のA / D変換になる。従って、図7の情報レジスター84には、C 2に示す前回のA / D変換の判定結果情報が記憶され、このC 2での判定結果情報に基づいて、C 1に示す今回のA / D変換におけるコードデータが補正されるようになる。

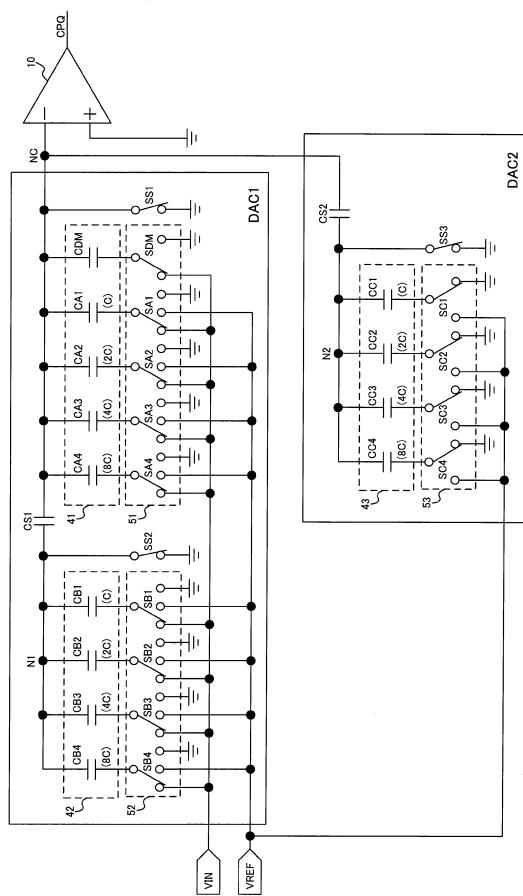

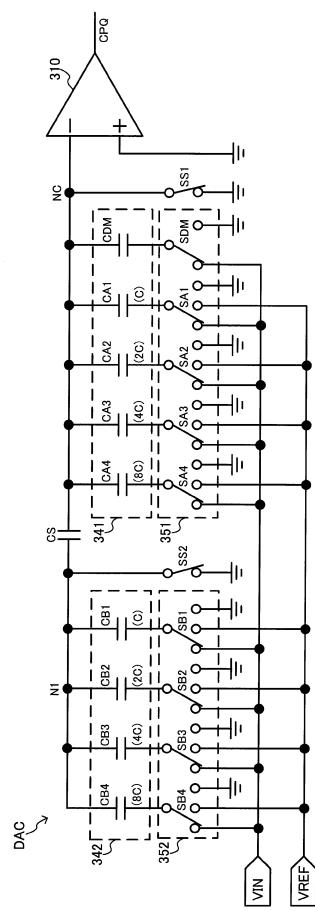

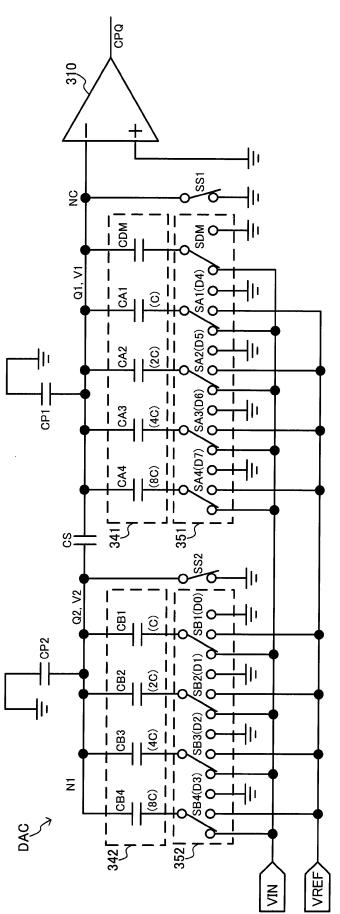

#### 【0106】

##### 5. 詳細な構成例

図11に本実施形態のA / D変換回路の詳細な構成例を示す。図11は、図1のD A C 1、D A C 2、比較回路10の詳細な構成例を示すものであり、D A C 1、D A C 2は電荷再分配型のD / A変換回路により構成される。

#### 【0107】

具体的には第1のD / A変換回路D A C 1は、第1のキャパシタアレイ部41と第1のスイッチアレイ部51を含む。また比較ノードN Cと第1のノードN 1との間に設けられる第1の直列キャパシタC S 1を含む。またD A C 1は、第2のキャパシタアレイ部42と第2のスイッチアレイ部52を含む。またサンプリング期間において、ノードN C、N 1をG N D(A G N D)に設定するためのスイッチ素子S S 1、S S 2を含む。

#### 【0108】

なお、ノードN 1に対して第3の直列キャパシタの一端を接続し、この第3の直列キャパシタの他端側に、キャパシタアレイ部42、スイッチアレイ部52と同様の構成のキャパシタアレイ部、スイッチアレイ部を設けてよい。

#### 【0109】

D A C 1の第1のキャパシタアレイ部41は、複数のキャパシタC A 1 ~ C A 4を含む。これらのキャパシタC A 1 ~ C A 4は、その一端が比較回路10の比較ノードN Cに接続される。ここで比較ノードN C(サンプリングノード)は、比較回路10の第1の入力端子(反転入力端子)に接続されるノードであり、比較回路10の第2の入力端子(非反転入力端子)はG N Dに設定される。またキャパシタC A 1 ~ C A 4はバイナリで重み付

10

20

30

40

50

けされており、例えば C A 1、C A 2、C A 3、C A 4 の容量値は、4 ビットの場合には C、2 C、4 C、8 C になっている。また第 1 のキャパシタアレイ部 4 1 は、ダミーキャパシタ C D M も含む。

#### 【 0 1 1 0 】

D A C 1 の第 1 のスイッチアレイ部 5 1 は、複数のスイッチ素子 S A 1 ~ S A 4 を含む。これらのスイッチ素子 S A 1 ~ S A 4 は、第 1 のキャパシタアレイ部 4 1 のキャパシタ C A 1 ~ C A 4 の他端に接続される。そしてスイッチ素子 S A 1 ~ S A 4 は、逐次比較用データ R D A の上位ビットのデータ（例えば R D A が 8 ビットの場合には上位の 4 ビットのデータ）に基づきスイッチ制御される。

#### 【 0 1 1 1 】

D A C 1 の第 2 のキャパシタアレイ部 4 2 は、複数のキャパシタ C B 1 ~ C B 4 を含む。これらのキャパシタ C B 1 ~ C B 4 は、その一端が第 1 のノード N 1 に接続される。ここで第 1 のノード N 1 は、一端が比較ノード N C に接続される直列キャパシタ C S 1 の他端側のノードである。またキャパシタ C B 1 ~ C B 4 はバイナリで重み付けされており、例えば C B 1、C B 2、C B 3、C B 4 の容量値は、4 ビットの場合には C、2 C、4 C、8 C になっている。

10

#### 【 0 1 1 2 】

D A C 1 の第 2 のスイッチアレイ部 5 2 は、複数のスイッチ素子 S B 1 ~ S B 4 を含む。これらのスイッチ素子 S B 1 ~ S B 4 は、第 2 のキャパシタアレイ部 4 2 のキャパシタ C B 1 ~ C B 4 の他端に接続される。そしてスイッチ素子 S B 1 ~ S B 4 は、逐次比較用データ R D A の下位ビットのデータ（例えば R D A が 8 ビットの場合には下位の 4 ビットのデータ）に基づきスイッチ制御される。

20

#### 【 0 1 1 3 】

第 2 の D / A 変換回路 D A C 2 は、比較ノード N C と第 2 のノード N 2 との間に設けられる第 2 の直列キャパシタ C S 2 を含む。また第 3 のキャパシタアレイ部 4 3 と第 3 のスイッチアレイ部 5 3 を含む。またサンプリング期間において、第 2 のノード N 2 を G N D に設定するためのスイッチ素子 S S 3 を含む。

#### 【 0 1 1 4 】

D A C 2 の第 3 のキャパシタアレイ部 4 3 は、複数のキャパシタ C C 1 ~ C C 4 を含む。これらのキャパシタ C C 1 ~ C C 4 は、その一端が第 2 のノード N 2 に接続される。ここで第 2 のノード N 2 は、一端が比較ノード N C に接続される直列キャパシタ C S 2 の他端側のノードである。またキャパシタ C C 1 ~ C C 4 はバイナリで重み付けされており、例えば C C 1、C C 2、C C 3、C C 4 の容量値は、4 ビットの場合には C、2 C、4 C、8 C になっている。

30

#### 【 0 1 1 5 】

D A C 2 の第 3 のスイッチアレイ部 5 3 は、複数のスイッチ素子 S C 1 ~ S C 4 を含む。これらのスイッチ素子 S C 1 ~ S C 4 は、第 3 のキャパシタアレイ部 4 3 のキャパシタ C C 1 ~ C C 4 の他端に接続される。そしてスイッチ素子 S C 1 ~ S C 4 は、コードデータ C D A に基づきスイッチ制御される。

#### 【 0 1 1 6 】

40

即ち図 1 のコードデータ生成部 9 0 は、D / A 変換回路 D A C 2 に対してコードデータ C D A を出力し、このコードデータ C D A に基づいてスイッチ素子 S C 1 ~ S C 4 はスイッチ制御される。例えばコードデータ生成部 9 0 は、逐次比較用データ R D A の下位ビットデータのデータ範囲内において、1 又は複数回の A / D 変換タイミング毎に異なった値になるデータを、コードデータ C D A として出力する。

#### 【 0 1 1 7 】

具体的には図 11 の 8 ビットの A / D 変換の場合には、逐次比較用データ R D A の下位の 4 ビットのデータ範囲内において、コードデータ C D A を変化させる。例えば 0 0 0 0 ~ 1 1 1 1 のデータ範囲内（或いは 0 0 0 0 ~ 1 1 1 1 よりも狭いデータ範囲内）においてコードデータ C D A をランダムに変化させて、D / A 変換回路 D A C 2 のスイッチアレ

50

イ部 5 3 のスイッチ素子 S C 1 ~ S C 4 をスイッチ制御する。このとき D / A 変換回路 D A C 1 のスイッチアレイ部 5 2 のスイッチ素子 S B 1 ~ S B 4 も、逐次比較用データ R D A の下位の 4 ビットのデータによりスイッチ制御される。このように、コードデータ C D A を変化させる範囲を、D A C 1 のスイッチ素子 S B 1 ~ S B 4 をスイッチ制御する逐次比較用データ R D A のデータ範囲内に設定することで、ミッシングコードの発生を効果的に防止できる。

#### 【 0 1 1 8 】

なお、D / A 変換回路 D A C 1 の最小分解能 ( L S B に相当する電圧、量子化電圧 ) を R S 1 とし、D / A 変換回路 D A C 2 の最小分解能を R S 2 としたとする。この場合に図 11 では R S 2 = R S 1 になっている。具体的には例えば直列キャパシタ C S 1 と C S 2 の容量値は同一（ほぼ同一）になっており、D A C 1 の L S B に相当するキャパシタ C B 1 の容量値と、D A C 2 の L S B に相当するキャパシタ C C 1 の容量値も同一（ほぼ同一）になっている。即ち D A C 2 は、D A C 1 の最小分解能 R S 1 ( L S B ) 未満のノイズ電圧ではなく、ノイズ電圧よりも大きなコード電圧を出力している。このようにすることで図 3 ( B ) に示すようなコードシフトを実現できる。なお R S 2 = R S 1 には限定されず、R S 2 ≠ R S 1 であってもよい。

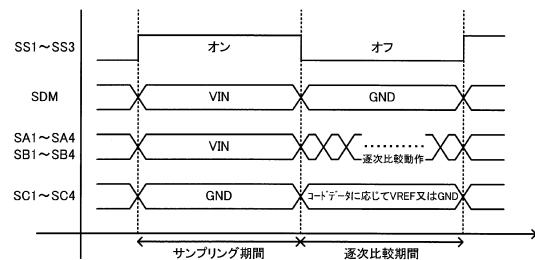

#### 【 0 1 1 9 】

次に、図 12 を用いて本実施形態の動作について詳細に説明する。図 12 に示すように、入力信号 V I N のサンプリング期間では、メインの D / A 変換回路 D A C 1 のスイッチ素子 S S 1、S S 2 がオンになり、ノード N C、N 1 が G N D に設定される。また D / A 変換回路 D A C 1 のスイッチ素子 S A 1 ~ S A 4、S B 1 ~ S B 4 を介して、キャパシタ C A 1 ~ C A 4、C B 1 ~ C B 4 の他端が V I N の電圧レベルに設定される。

#### 【 0 1 2 0 】

これにより入力信号 V I N のサンプリングが行われる。そしてスイッチ素子 S A 1 ~ S A 4、S B 1 ~ S B 4 がオフすると、そのタイミングでの入力信号 V I N の電圧がホールドされる。なおサンプリング期間では、ダミーキャパシタ用のスイッチ素子 S D M を介して、ダミーキャパシタ C D M の他端が V I N の電圧レベルに設定される。

#### 【 0 1 2 1 】

またサンプリング期間では、コードシフト用の D / A 変換回路 D A C 2 のスイッチ素子 S S 3 がオンになり、ノード N 2 が G N D に設定される。またスイッチ素子 S C 1 ~ S C 4 を介して、キャパシタ C C 1 ~ C C 4 の他端が G N D に設定される。これによりキャパシタ C C 1 ~ C C 4 の両端が G N D に設定され、電荷が蓄積されない状態になる。

#### 【 0 1 2 2 】

次に、A / D 変換の逐次比較期間になると、メインの D / A 変換回路 D A C 1 のスイッチ素子 S S 1、S S 2 がオフになる。またダミーキャパシタ用のスイッチ素子 S D M の他端は G N D に設定される。

#### 【 0 1 2 3 】

そして、逐次比較用データ R D A の各ビットに基づいて、D A C 1 のスイッチ素子 S A 1 ~ S A 4、S B 1 ~ S B 4 がスイッチ制御され、キャパシタ C A 1 ~ C A 4、C B 1 ~ C B 4 の他端は V R E F 又は G N D に設定される。

#### 【 0 1 2 4 】

例えれば逐次比較用データが R D A = 1 0 0 0 0 0 0 0 である場合には、R D A の M S B に対応するキャパシタ C A 4 の他端は基準電圧 V R E F に設定される。また、他のキャパシタ C A 3 ~ C A 1、C B 4 ~ C B 1 の他端は G N D に設定される。

#### 【 0 1 2 5 】

また逐次比較用データが R D A = 1 0 0 0 1 0 0 0 である場合には、キャパシタ C A 4 と C B 4 の他端は V R E F に設定される。また、他のキャパシタ C A 3 ~ C A 1、C B 3 ~ C B 1 の他端は G N D に設定される。

#### 【 0 1 2 6 】

また A / D 変換の逐次比較期間になると、コードシフト用の D / A 変換回路 D A C 2 の

10

20

30

40

50

スイッチ素子 S S 3 がオフになる。そして、コードデータ C D A の各ビットに基づいて、D A C 2 のスイッチ素子 S C 1 ~ S C 4 がスイッチ制御され、キャパシタ C C 1 ~ C C 4 の他端は V R E F 又は G N D に設定される。

#### 【 0 1 2 7 】

例えればコードデータが C D A = 1 0 0 0 である場合には、キャパシタ C C 4 の他端は V R E F に設定され、他のキャパシタ C C 3 ~ C C 1 の他端は G N D に設定される。またコードデータが C D A = 1 1 0 0 である場合には、キャパシタ C C 4 、 C C 3 の他端は V R E F に設定され、他のキャパシタ C C 2 、 C C 1 の他端は G N D に設定される。

#### 【 0 1 2 8 】

この場合にコードデータ C D A は、図 1 2 に示す 1 回の A / D 変換タイミング毎に変化する。即ちサンプリング期間及び逐次比較期間により構成される 1 回の A / D 変換期間毎にコードデータ C D A は変化する。なお複数回の A / D 変換タイミング毎にコードデータ C D A を変化させてもよい。

#### 【 0 1 2 9 】

図 1 1 の電荷再分配型の A / D 変換回路においては、V I N のサンプリング信号（サンプリング電圧）と、D / A 出力信号とコード信号（コード電圧）の加算信号（加算電圧）との比較処理が行われる。この場合には図 1 の制御回路 2 0 は、逐次比較レジスター S A R の逐次比較結果データ Q D A にコードデータ C D A を加算する処理を行うことになる。

#### 【 0 1 3 0 】

具体的にはサンプリング期間においては、入力信号 V I N に応じた電荷がキャパシタ C A 1 ~ C A 4 、 C B 1 ~ C B 4 に蓄積される。そして、この V I N に応じて蓄積された電荷と、逐次比較期間において逐次比較用データ R D A 及びコードデータ C D A に応じてキャパシタ C A 1 ~ C A 4 、 C B 1 ~ C B 4 、 C C 1 ~ C C 4 に蓄積された電荷とが比較される。そして、両者の電荷が一致した時の逐次比較用データ R D A が、逐次比較結果データ Q D A として逐次比較レジスター S A R から出力される。そして、この逐次比較結果データ Q D A にコードデータ C D A を加算したデータが、入力信号 V I N を A / D 変換したデータ D O U T として出力されることになる。このようにすることで、図 3 ( B ) に示すようなコードデータ C D A によるコードシフトを実現しながら、適正な A / D 変換データを出力できるようになる。

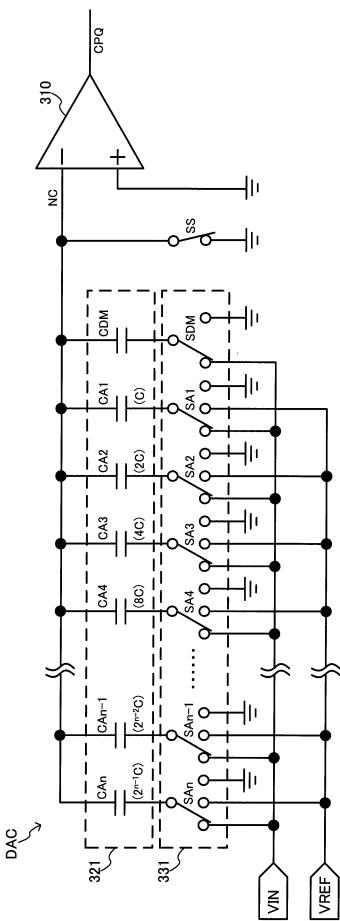

#### 【 0 1 3 1 】

図 1 3 に本実施形態の第 2 の比較例の A / D 変換回路を示す。この第 2 の比較例は、図 2 の第 1 の比較例を電荷再分配型で実現した例であり、D / A 変換回路 D A C ( 及び S / H 回路 3 3 0 ) は、キャパシタアレイ部 3 2 1 、スイッチアレイ部 3 3 1 、スイッチ素子 S S により実現される。

#### 【 0 1 3 2 】

A / D 変換回路の変換精度を決める大きな要因となるのは、D A C の変換精度である。図 1 3 の第 2 の比較例において、D A C の分解能を n ビットとすると、キャパシタアレイ部 3 2 1 は、バイナリに重み付けされた n 個のキャパシタ C A 1 ~ C A n と、1 個のダミーキャパシタ C D M により構成される。そしてサンプリング期間では、キャパシタ C A 1 ~ C A n の他端は入力信号 V I N に接続され、比較ノード N C は G N D に設定される。

#### 【 0 1 3 3 】

そして逐次比較期間において、最上位ビットである M S B から順次、逐次比較処理が行われる。具体的には、キャパシタ C A 1 ~ C A n の他端を、スイッチアレイ部 3 3 1 のスイッチ素子 S A 1 ~ S A n を用いて、D / A 変換回路の入力値に応じて、基準電圧 V R E F もしくは G N D に接続されるかを切り替える。これより比較回路 3 1 0 の反転入力端子の比較ノード N C の電圧は、D A C の出力値から V I N のサンプリング電圧を引いた電圧になる。

#### 【 0 1 3 4 】

しかしながら、図 1 3 の第 2 の比較例では、A / D 変換回路の分解能を例えば 1 2 ビットにするために、D A C の分解能を 1 2 ビットにすると、合計で  $2^{12} \times C$  の容量値が必

10

20

30

40

50

要になってしまふ。このため、回路が大規模化すると共に、キャパシタを充電するために大きな電流が必要になてしまふ。A / D 変換回路の分解能を高くするほど、この傾向は強くなるため、図 13 の第 2 の比較例には高ビット化に限界があるという問題がある。

#### 【0135】

図 14 に A / D 変換の第 3 の比較例を示す。この第 3 の比較例は、上述の第 2 の比較例の問題を解決するために、直列キャパシタ CS を設け、バイナリに重み付けされたキャパシタを複数段にする構成にしている。即ち、一端が比較ノード NC に接続され、他端がノード N1 に接続される直列キャパシタ CS を設ける。また比較ノード NC に接続されるキャパシタアレイ部 341 及びそのスイッチ制御を行うスイッチアレイ部 351 と、ノード N1 に接続されるキャパシタアレイ部 342 及びそのスイッチ制御を行うスイッチアレイ部 352 を設ける。10

#### 【0136】

図 14 の第 3 の比較例の構成によれば、例えばキャパシタアレイ部 341 のキャパシタ CA1 の容量値と、キャパシタアレイ部 342 のキャパシタ CB1 の容量値と同じにできる。従って 8 ビットの場合を例にとると、図 13 の第 2 の比較例では  $2^8 \times C$  の容量値が必要になるが、図 14 の第 3 の比較例では  $2^5 \times C$  の容量値で済む。このため、回路の小面積化を図れると共にキャパシタの充電電流も小さくできる。

#### 【0137】

ところが、図 14 の第 3 の比較例では、ノード N1 に寄生する容量が DAC の DNL ( Differential Non Linearity ) や INL ( Integral Non Linearity ) を劣化させるという問題が生じる。これは、バイナリごとに重み付けされた容量比が、寄生容量によって狂うことが原因である。この悪影響は、図 14 の 8 ビットの場合を例にとると、 LSB から 5 ビット目が変化するコード付近で顕著に生じる。具体的には 00001111 と 00010000 ( MSB が先頭 ) の変わり目で生じ、図 3 ( A ) に示すようなミッシングコードの問題が発生する。20

#### 【0138】

このような問題を解決する手法として、直列キャパシタ CS の容量値をトリミングして、特性を微調整する手法も考えられる。しかしながら、トリミングだけでは、トリミングできる容量単位や範囲に限界がある。また製造工程にトリミング工程が必要になり、高コスト化等を招く。また A / D 変換データをデジタル補正するデジタル補償処理などを行つて、高精度化を図る手法も考えられるが、処理が繁雑化すると共に余分な処理が必要になつてしまふという問題がある。30

#### 【0139】

次に、図 15 を用いて、ノード NC 、 N1 に寄生容量 CP1 、 CP2 が付加された場合の SAR 型 ADC の理論式について説明する。寄生容量 CP1 、 CP2 を含まない理論式は、 CP1 、 CP2 を 0 にすれば導出できる。なお、キャパシタ CA1 及び CB1 、 CA2 及び CB2 、 CA3 及び CB3 、 CA4 及び CB4 の容量値を、各々、 C 、 2C 、 4C 、 8C とする。また直列キャパシタ CS の容量値を C とする。またダミーキャパシタ CD M は、サンプリング時に充電される電荷量を調整する目的 ( フルスケール調整 ) で用いられるものであるが、ここでは説明の簡素化のためにダミーキャパシタ CD M の容量値は無視する。40

#### 【0140】

図 15 はサンプリング期間でのスイッチ素子の状態を示している。このサンプリング期間においてノード NC に充電される電荷量 Q1 は下式 (1) のように表される。

#### 【0141】

##### 【数 1】

$$\begin{aligned} Q1 &= (C + 2C + 4C + 8C)(0 - VIN) \\ &= -15C \cdot VIN \end{aligned} \quad (1)$$

#### 【0142】

10

20

30

40

50

またサンプリング期間においてノードN1に充電される電荷量Q2は下式(2)のよう

に表される。

【0143】

【数2】

$$\begin{aligned} Q2 &= (C + 2C + 4C + 8C)(0 - VIN) \\ &= -15C \cdot VIN \end{aligned} \quad (2)$$

【0144】

なお直列キャパシタCS及び寄生容量CP1、CP2は、両端の電圧がGND(接地電位)であるため、電荷は充電されない。 10

【0145】

次に、逐次比較期間でのノードNCの電圧V1とノードN1の電圧V2を求める。例えば図15において、スイッチ素子SB1～SB4は、逐次比較用データRDAの下位の4ビットD0～D3によりスイッチ制御され、スイッチ素子SA1～SA4は、RDAの上位の4ビットD4～D7によりスイッチ制御される。具体的には、ビットDi = 1 (0 ≤ i ≤ 7)の場合にはVINに接続され、ビットDi = 0の場合にはGNDに接続される。この場合に、逐次比較期間においてノードNC、N1に蓄積される電荷量Q1、Q2は下式(3)、(4)のように表される。

【0146】

【数3】

$$\begin{aligned} Q1 &= CP1(V1 - 0) + CS(V1 - V2) \\ &\quad + C(V1 - VREF \cdot D0) + 2C(V1 - VREF \cdot D1) + 4C(V1 - VREF \cdot D2) + 8C(V1 - VREF \cdot D3) \end{aligned} \quad (3)$$

【0147】

【数4】

$$\begin{aligned} Q2 &= CP2(V2 - 0) + CS(V2 - V1) \\ &\quad + C(V2 - VREF \cdot D4) + 2C(V2 - VREF \cdot D5) + 4C(V2 - VREF \cdot D6) + 8C(V2 - VREF \cdot D7) \end{aligned} \quad (4)$$

【0148】

そして電荷保存の法則により、式(1)と式(3)の電荷量Q1は等しく、式(2)と式(4)の電荷量Q2は等しい。また、逐次比較用データRDAの全てのビットD0～D7についての比較動作が完了したときには、比較回路310の反転入力端子のノードNCの電圧は、非反転入力端子のGNDと等しくなるため、下式(5)が成立する。 30

【0149】

【数5】

$$V1 = 0 \quad (5)$$

【0150】

従って、式(1)～(5)の連立方程式をVINについて解くと、下式(6)が導かれる。 40

【0151】

【数6】

$$VIN = \frac{VREF}{255C + 15CP2} \left[ \frac{(D0 + 2D1 + 4D2 + 8D3 + 16D4 + 32D5 + 64D6 + 128D7)C}{(D4 + 2D5 + 4D6 + 8D7)CP2} \right] \quad (6)$$

【0152】

式(6)から明らかなように、VINのA/D変換結果には、ノードNCの寄生容量CP1の影響はなく、ノードN2の寄生容量CP2だけが特性に悪影響を与える。従って、寄生容量CP2の悪影響を低減するために直列キャパシタCSのトリミングが必要になる。また式(6)から、寄生容量CP2の悪影響はD4以上のビットに対応するスイッチ素 50

子の接続が変化するときに現れ、これにより図3(A)に示すようなミッシングコードが発生することが理解される。

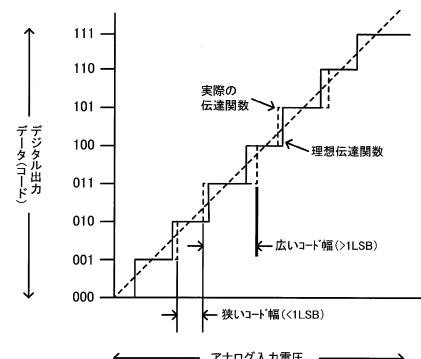

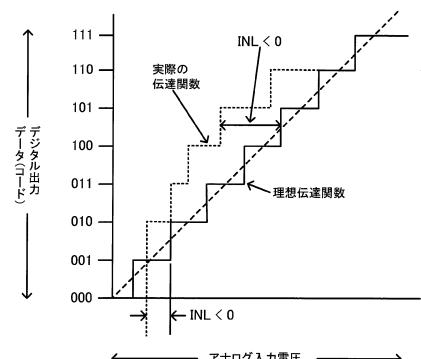

#### 【0153】

なお、図16(A)、図16(B)はDNL、INLの説明図である。図16(A)に示すDNLは、理想的なコード幅と測定されたコード幅の差分である。例えば図16(A)では、DNLの特性の悪化により、010のコードの幅が狭くなり、011のコードの幅が広くなっている。そして010のコードの幅が更に狭くなつて消失すると、010のコードは図3(A)のようなミッシングコードになる。

#### 【0154】

また図16(B)のINLは、ゲイン誤差とオフセット誤差を除去した後の、実際のコード遷移点(破線)と、それに対応する理想的な遷移点(実線)の最大偏差である。正のINLは、遷移が理想よりも遅れていることを示し、負のINLは、遷移が理想よりも早いことを示している。

#### 【0155】

図17(A)、図17(B)にDNLのシミュレーション結果例を示す。ここでは、後述する全差動型のA/D変換回路を用い、メインのDAC1が14ビットであり、コードシフト用のDAC2が4ビットの場合を例にとり説明する。図11では、メインのDAC1は、4ビット+4ビットの2段の直列構成になっているが、14ビットのメインのDAC1の場合には、6ビット+4ビット+4ビットの3段構成になる。

#### 【0156】

図17(A)は本実施形態のコードシフト手法を採用しなかつた場合のDNLのシミュレーション結果例である。図17(A)では、DNLが1 LSB以上になるミッシングコードが発生している。

#### 【0157】

図17(B)は本実施形態のコードシフト手法を採用した場合のDNLのシミュレーション結果例である。図17(B)では、DNLが1 LSB未満になっており、ミッシングコードの発生が防止されている。

#### 【0158】

以上のように本実施形態によれば、図14の第3の比較例に対して、図11に示すようにコードシフト用のDAC2を追加し、DAC2によりコードデータの信号を加算することで、コードシフトを実現している。

#### 【0159】

即ち図14の第3の比較例では、ノードN1の寄生容量CP2が原因で、図3(A)や図17(A)に示すようなミッシングコードが発生している。これに対して本実施形態では、時間的に変化するコードデータの信号をDAC2により加算することで、特定のコードで発生していたDNLの悪化(ミッシングコード)を周囲のコードに時間的に拡散させる。例えばミッシングコードが00010000というようにMLS Bから4ビット目で発生する場合に、0000~1111のデータ範囲で変化するランダムなコードデータの信号を加算する。こうすることで、図3(B)や図17(B)に示すように、DNLを1 LSB未満に抑えて、ミッシングコードの発生を防止できる。従って、回路規模を小さくするために直列キャパシタCS1を設けた場合にも、ノードN1の寄生容量を原因とするミッシングコードの発生を防止できる。この結果、回路規模の縮小化と、A/D変換特性の劣化防止とを両立することが可能になる。

#### 【0160】

##### 6. 全差動型

図18に本実施形態のコードシフト手法を適用した全差動型のA/D変換回路の構成例を示す。図18のA/D変換回路は、比較回路10と、比較回路10の非反転入力端子に接続されるメインのD/A変換回路DAC1Pと、反転入力端子に接続されるメインのD/A変換回路DAC1Nを含む。また、比較回路10の非反転入力端子に接続されるコードシフト用のD/A変換回路DAC2Pと、反転入力端子に接続されるコードシフト用の

10

20

30

40

50

D / A 変換回路 D A C 2 N を含む。

**【 0 1 6 1 】**

非反転側（正側）のメインの D A C 1 P 及び反転側（負側）のメインの D A C 1 N の構成は、図 1 1 のメインの D A C 1 と同様に、キャパシタアレイ部とスイッチアレイ部を含む。そして D A C 1 P には、差動信号を構成する非反転側（正側）の入力信号 P I N が入力され、D A C 1 N には、差動信号を構成する反転側（負側）の入力信号 N I N が入力される。

**【 0 1 6 2 】**

そしてサンプリング期間では、D A C 1 P のノード N C P 、 N 1 P は、スイッチ素子 S S 1 P 、 S S 2 P によりコモン電圧（中間電圧） V C M に設定される。また D A C 1 N のノード N C N 、 N 1 N は、スイッチ素子 S S 1 N 、 S S 2 N によりコモン電圧 V C M に設定される。

10

**【 0 1 6 3 】**

またサンプリング期間では、D A C 1 P のスイッチ素子 S A 1 P ~ S A 4 P 、 S B 1 P ~ S B 4 P の一端は、差動信号の非反転側の信号 P I N に接続され、D A C 1 N のスイッチ素子 S A 1 N ~ S A 4 N 、 S B 1 N ~ S B 4 N の一端は、差動信号の反転側の信号 N I N に接続される。

**【 0 1 6 4 】**

一方、逐次比較期間では、D A C 1 P のスイッチ素子 S A 1 P ~ S A 4 P 、 S B 1 P ~ S B 4 P の一端は、逐次比較用データの対応するビットが「 1 」である場合には V R E F に接続され、「 0 」である場合には G N D に接続される。

20

**【 0 1 6 5 】**

これに対して、D A C 1 N のスイッチ素子 S A 1 N ~ S A 4 N 、 S B 1 N ~ S B 4 N の一端は、逐次比較用データの対応するビットが「 1 」である場合には G N D に接続され、「 0 」である場合には V R E F に接続される。

**【 0 1 6 6 】**

非反転側のコードシフト用の D A C 2 P 及び反転側のコードシフト用の D A C 2 N は、図 1 1 のコードシフト用の D A C 2 と同様に、キャパシタアレイ部とスイッチアレイ部を含む。

**【 0 1 6 7 】**

そしてサンプリング期間では、D A C 2 P のノード N 2 P は、スイッチ素子 S S 3 P により V C M に設定される。また D A C 2 N のノード N 2 N は、スイッチ素子 S S 3 N により V C M に設定される。また D A C 2 P のスイッチ素子 S C 1 P ~ S C 4 P 及び D A C 2 N のスイッチ素子 S C 1 N ~ S C 4 N の一端は V C M に接続される。

30

**【 0 1 6 8 】**

一方、逐次比較期間では、D A C 2 P のスイッチ素子 S C 1 P ~ S C 4 P の一端は、コードデータの対応するビットが「 1 」である場合には V R E F に接続され、「 0 」である場合には G N D に接続される。これに対して、D A C 2 N のスイッチ素子 S C 1 N ~ S C 4 N の一端は、コードデータの対応するビットが「 1 」である場合には G N D に接続され、「 0 」である場合には V R E F に接続される。

40

**【 0 1 6 9 】**

図 1 8 の構成によっても、コードシフト手法により、A / D 変換回路の D N L や I N L を改善し、ミッキングコード等の発生を防止できる。また全差動型で A / D 変換回路を構成することで、振幅を大きく取ることができ、S / N 比を向上できると共に、コモンモードノイズの影響を低減できる。

**【 0 1 7 0 】**

7 . 電子機器

図 1 9 に本実施形態の A / D 変換回路を含む電子機器の構成例を示す。この電子機器は、センサー 5 1 0 、検出回路 5 2 0 、 A / D 変換回路 5 3 0 、処理部 5 4 0 を含む。なおこれらの一の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が

50

可能である。例えば検出回路 520、A/D 変換回路 530、処理部 540 は集積回路装置により実現できる。

#### 【0171】

図19の電子機器としては、例えば生体計測機器（脈拍計、歩数計等）、携帯型情報端末、映像機器（デジタルカメラ、ビデオカメラ）、時計などの種々の機器を想定できる。

#### 【0172】

センサー 510 は、ジャイロセンサー、加速度センサー、フォトセンサー、圧力センサー等であって、電子機器の用途に応じた様々なセンサーが用いられる。検出回路 520 はセンサー 510 から出力されるセンサー信号を增幅して、所望信号を抽出する。また A/D 変換回路 530 は検出回路 520 からの検出信号（所望信号）をデジタルデータに変換して、処理部 540 へ出力する。

10

#### 【0173】

処理部 540 は、A/D 変換回路 530 からのデジタルデータに対して必要なデジタル信号処理を実行する。また処理部 540 は、検出回路 520 のゲイン制御等を行ってもよい。ここで処理部 540 で行われるデジタル信号処理としては、センサー信号から適正な所望信号を抽出するための高速フーリエ変換等の種々の処理を想定できる。

#### 【0174】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また A/D 変換回路、電子機器の構成・動作や、A/D 変換手法、コード生成手法、コードシフト手法等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。例えば図11ではメインの D/A/C 1 が 2 段構成である場合の例を示したが、3 段以上の構成であってもよい。

20

#### 【符号の説明】

#### 【0175】

D/A/C 1 第1のD/A 変換回路、D/A/C 2 第2のD/A 変換回路、

30

SAR 逐次比較レジスター、SDR 補正指示信号、

CA1～CA4、CB1～CB4、CC1～CC4 キャパシタ、

SA1～SA4、SB1～SB4、SC1～SC4、SS1～SS3 スイッチ素子、

CS1 第1の直列キャパシタ、CS2 第2の直列キャパシタ、

10 比較回路、20 制御回路、30 S/H 回路、

41 第1のキャパシタアレイ部、42 第2のキャパシタアレイ部、

43 第3のキャパシタアレイ部、

51 第1のスイッチアレイ部、52 第2のスイッチアレイ部、

53 第3のスイッチアレイ部、

80 補正部、82 判定部、84 情報レジスター、86 セレクター、

40

88 出力レジスター、90 コードデータ生成部、92 コードシフト用カウンター、

94 並び替え部、96 反転部、98 セレクター、

310 比較回路、320 制御回路、330 S/H 回路、

510 センサー、520 検出回路、530 A/D 変換回路、540 処理部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

(A)

(B)

【図17】

【 図 1 8 】

【図19】

---

フロントページの続き

(56)参考文献 特表2009-516433(JP,A)

特表2010-506535(JP,A)

実開昭62-112221(JP,U)

特開平08-321779(JP,A)

特開平06-045933(JP,A)

特開2012-104938(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 03 M 1 / 00 - 1 / 88