## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2003/0018880 A1

#### Jan. 23, 2003 (43) **Pub. Date:**

## Litaize et al.

#### (54) MULTIPLE-MODE MEMORY SYSTEM

Inventors: Daniel Litaize, Saint Orens de Gameville (FR); Jean-Clauke Salinier, Ramonville Saint-Agne (FR); Abdelaziz

Mzoughi, Toulouse (FR);

Fatima-Zahra Elkhlifi, Toulouse (FR); Mustapha Lalama, Toulouse (FR); Pascal Sainrat, Toulouse (FR)

Correspondence Address: WALSTEIN BENNETT SMITH III P. O. BOX 1668 GEORGETOWN, TX 78628 (US)

(21) Appl. No.: 10/212,682

(22) Filed: Aug. 7, 2002

#### Related U.S. Application Data

Continuation of application No. 10/022,421, filed on Dec. 20, 2001, which is a continuation of application No. 09/577,447, filed on May 24, 2000, now Pat. No. 6,345,321, which is a continuation of application No. 08/024,803, filed on Mar. 1, 1993, now Pat. No. 6,112,287, which is a continuation of application No. 07/400,113, filed on Aug. 14, 1989, now abandoned.

#### (30)Foreign Application Priority Data

Dec. 14, 1987 (FR)...... 87.18103 Dec. 9, 1988 (]...... PCT/FR88/00608

### **Publication Classification**

- (52)

- ABSTRACT (57)

A system includes a first and second integrated circuit and associated interconnect. The first integrated circuit is a memory component and includes a RAM, one or more configuration registers, and associated control logic. The second integrated circuit is a memory controller that is a master to the memory component. The behavior of the memory component, including selection from a number of different operating modes, is controllable via configuration register mode bits. The various modes include several transfer-length modes, where each mode corresponds to data transfers of a predetermined length. Based on the mode selection specified by the mode bits, the controller determines the length of the data transfers.

Fig. 5

Fig. 11

Fig. 12a

a31 a30 ......a14 a13 a12 .....a6 a5 a4 .....a0

tag cadre mot

Fig. 12b

adr\_RG

w\_RG

DESCRIPTEUR

l

data\_RG

Fig. 12c

255

Fig. 16

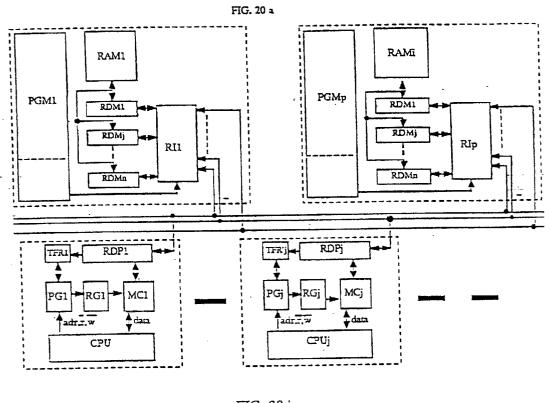

FIG. 20 b RDM! □ RDM1 = PGMp PGM1 RDMn I RDMn = RIp RIi RAM1 LS11 LS21 ĹSjp ĽSqp C C p Il Io c c p II Ip c | c | 1 | p [p CPUp,MCp CPU2,MC2 CPU1,MC1 UCn / UC1-UC2

Fig.22

#### MULTIPLE-MODE MEMORY SYSTEM

[0001] The invention relates to a multiprocessor system of the type comprising a central memory, treatment processors and cache memories associated with treatment processors. It also relates to a process for the exchange of information between central memory and treatment processors via the cache memory associated with each of these processors. It also provides a new integrated circuit component, capable of equipping the multiprocessor system.

[0002] It is known that, in the most common known multiprocessor systems, all the information (data, address) is relayed by a common parallel communication bus between the central memory and the various treatment processors, which constitutes a bottleneck: its transfer rate is in effect insufficient to feed all the processors for full efficiency, from a common central memory.

[0003] For increasing the information transfer rate, a first solution consists in associating with each treatment processor a cache memory which, by the location of the information, permits reducing the demands on the central memory. However, in the case in which the volume of data shared between processors is substantial, the maintenance of coherence of the data between memories generates complementary information traffic on the communication bus which resists a significant reduction of the overall flow on this bus, and therefor removes a large part of the interest in this solution.

[0004] Another solution consists in providing the communication bus in the form of a grid network designed as a "crossbar", which permits a direct communication between each treatment processor and each subassembly of the central memory (memory bank). However, this solution is very heavy and very costly to achieve because of the very great number of interconnections, and it becomes completely unrealistic beyond about ten treatment processors. Moreover, in the case of multiple demands of several processors on the same memory bank, such a solution implies access conflicts, a source of slowing up the exchanges.

[0005] Another more current solution by reason it its architectural simplicity consists in associating a local memory with each treatment processor for storing specific data therein, and storing the transferred data in the common central memory. However, the great deficiency of this architecture is its non-transparency, that is, the need for the programmer to organize the detail of the allocation of data in the various memories, such that this solution is of a very constrained usefulness. Moreover, in the case of high volume of transferred data, it may lead as before to a saturation of the access bus in the central memory.

[0006] A solution which has been called "aquarius architecture" has been proposed by the University of Berkeley and consists in improving the aforementioned crossbar solution by combining with the crossbar network, for the shared data, cache memories which are connected to the crossbar network, and for the shared data, distinct cache memories which are connected to a common synchronization bus. This solution contributes a gain in speed of exchange but remains very heavy and very costly to achieve.

[0007] The present invention seeks to provide a new solution, permitting considerably increasing the flow rate of

information exchange, while retaining an architecture which is transparent for the user, much simpler than the crossbar architecture.

[0008] An object of the invention is thus to permit notably increasing the number of treatment processors of the system, while benefitting from a high efficiency for each processor.

[0009] Another object is to provide a structure of an integrated circuit component, permitting a very simple realization of the architecture of this new multiprocessor system.

[0010] To this end, the multiprocessor system provided by the invention is of the type comprising a central memory (RAM) organized in blocks of information (bi), treatment processors (CPU $_1$  . . . CPU $_j$  . . . CPU $_n$ ), a cache memory (MC $_i$ ) connected to each treatment processor (CPU $_j$  . . . CPU $_j$  a cache memory (MC $_j$ ) connected to each treatment processor (CPU $_j$ ) and organized in blocks of information (b $_i$ ) of the same size as those of the central memory, a directory (RG $_j$ ) and its management processor (PG $_j$ ) associated with each cache memory (MC $_j$ ), means for communication of addresses of blocks between processors (CPU $_j$ ) and a central memory (RAM). According to the present invention, the multiprocessor system is provided with:

[0011] an assembly of shift registers, termed memory shift registers (RDM1 . . . RDM<sub>j</sub> . . . RDMn), each register (RDM<sub>j</sub>) of this assembly being connected to the central memory (RAM) in such a manner as to permit, in one cycle of this memory, a parallel transfer in read or write of a block of information (b<sub>i</sub>) between said register and said central memory;

[0012] shift registers, termed processor shift registers (RDP1 . . . RDP<sub>j</sub> . . . RDPn), each processor shift register (RDP<sub>j</sub>) being connected to the cache memory (MC<sub>j</sub>) of a processor (CPU<sub>j</sub>) in such a manner as to permit a parallel transfer in reading or writing of a block of information (b<sub>i</sub>) between said shift register (RDP<sub>j</sub>) and said cache memory (MC<sub>i</sub>);

[0013] an assembly of series links (LS<sub>1</sub>...LS<sub>j</sub>...LS<sub>n</sub>), each connecting a memory shift register (RDM<sub>j</sub>) and a processor shift register (RDP<sub>j</sub>) and adapted to permit the transfer of blocks of information (b<sub>i</sub>) between the two registers considered (RDM<sub>i</sub>, RDP<sub>j</sub>).

[0014] Thus, in the multiprocessor system according to the invention, the exchanges between the cache memories and the associated processors are carried out as in the conventional systems provided with cache memories. By contrast, the exchanges between the central memory and the cache memories is carried out in an entirely original manner.

**[0015]** Each transfer of an information block  $(b_i)$  from the central memory (RAM) to the cache memory  $(MC_j)$  of a given processor  $(CPU_j)$  consists of:

[0016] transferring, in a cycle of the central memory, the block (b<sub>i</sub>) of said central memory (RAM) to the memory shift register (RDM<sub>j</sub>) (of the size of one block) which is directly connected to the central memory and which corresponds to the processor (CPU<sub>j</sub>) considered,

[0017] transferring on the corresponding series link (LS<sub>i</sub>) the contents of this memory shift register (RDM<sub>i</sub>)

to the processor shift register (RDP<sub>j</sub>) (of the same capacity) which is associated with the cache memory (MC<sub>i</sub>) of the processor considered (CPU<sub>j</sub>),

[0018] transferring the contents of said processor shift register (RDP<sub>i</sub>) to the cashe memory (MC<sub>i</sub>)

[0019] In the opposite direction, each transfer of information blocks (b<sub>i</sub>) from the cache memory (MC<sub>j</sub>) of a given processor (CPU<sub>i</sub>) to the central memory (RAM) consists of:

[0020] transferring the block (b<sub>i</sub>) of said cache memory considered (MC<sub>j</sub>) to the processor shift register (RDP<sub>j</sub>) which is associated with said cache memory (MC<sub>i</sub>),

[0021] transferring on the corresponding series link (LS<sub>j</sub>) the contents of the processor shift register (RDP<sub>j</sub>) to the memory shift register (RDM<sub>j</sub>), allocated to the processor considered (among the assembly of shift registers (RDM1 . . . RDM<sub>j</sub> . . . RDMn) connected to the central memory (RAM),

[0022] transferring in a cycle of the central memory, the contents of the memory shift register (RDM<sub>j</sub>) to said central memory (RAM).

[0023] In these conditions, the transfer of each block of information  $(b_i)$  is carried out, no longer through a parallel bus as is the case in the known systems, but by the series links of high flow rate. These series links permit obtaining comparable times of transfer for each block  $(b_i)$  and even lower than the transfer times in known parallel bus systems. The comparative example given hereinbelow with the current values of the parameter for current technology, illustrates clearly this fact which seems paradoxical.

[0024] It is assumed that each block of information (b<sub>i</sub>) is of a size equal to 64 octets.

[0025] In the system of the invention, the transfer time between the central memory and a cache memory breaks down into:

[0026] a central memory transfer time (RAM)/memory shift register (RDM<sub>j</sub>): 100 nanoseconds (performance of a central random access memory of known type),

[0027] a series transfer time on the corresponding series link: 64×8×1/500.10<sup>6</sup>, either 1024 nanoseconds, assuming a transfer frequency of 500 megahertz (not exceptional with current technology which permits attaining frequencies of 3000 megahertz),

[0028] a processor shift register transfer time (RDP<sub>j</sub>)/cache memory (Mc<sub>j</sub>): 50 nanoseconds (cache memory of the very current type).

[0029] The total time of transfer of a block is therefor on the order of 1200 nanoseconds (while integrating the chaining delays of the second order).

[0030] In known systems with cache memories in which the exchanges of information is carried out directly in parallel by words of 4 octets (the most current systems leading to busses of the conventional type of 32 data lines), the transfer time for one block is equal to the transfer time of 16 words of 4 octets which comprise this block, that is: 16×100=1600 nanoseconds.

[0031] Thus, it is seen that, with the average hypotheses in the two solutions, these times are comparable. But, if one

compares the architecture of the system according to the invention with that of a parallel bus common with cache memories (first solution mentioned previously), it will be realized that:

[0032] in the conventional solution (common parallel bus), the central memory and the common bus are occupied at 100% during the transfer, since the information circulates between the two for the entire transfer time,

[0033] in the system according to the invention, the series link is occupied 100% during the, transfer, but the central memory is occupied less that 10% of the transfer time (time of memory reading and loading of the memory shift register (RDM<sub>j</sub>)), such that the central memory may serve 10 times more processors than in the preceding case (the use of the series link being without significance since it is private and directed to the processor).

[0034] It is important to emphasize that in this system of the invention, each series connection which connects each processor in an individual manner to the central memory is a simple connection (of one or two data leads), such that the series network thus constituted is not comparable in the overall plan to the complexity with, for example, a crossbar network of which each connection is a parallel connection with multiplicity of leads (32 leads of data in the comparative example above), with all of the necessary switches.

[0035] Further, as will be seen below on the comparative curves, the system according to the invention has greatly improved performance with respect to the traditional common bus systems and permits in practice operating a much higher number of processors (of several tens to a hundred processors). This performance is compatible with that of a crossbar system, but the system, according to the invention is of a much greater architectural simplicity.

[0036] In the system of the invention, each series link may in practice be achieved either by means of two unidirectional series links for bit by bit transfer, or by means of a single bidirectional series link.

[0037] In the first case, each memory shift register;  $(RDM_j)$  and each processor shift register  $(RDP_j)$  are divided into two registers, one specialized for the transfer in one direction, the other for the transfer in the other direction. The two unidirectional series links are then connected to the divided memory shift register  $(RDM_j)$  and to the corresponding divided processor shift register  $(RDP_j)$ , in such a manner as to permit, for one, a transfer in one direction, and for the other, a transfer in the other direction.

[0038] This embodiment with two unidirectional links presents the advantage of not requiring any transfer management on the link, but the inconvenience of doubling the necessary resources (link, registers).

[0039] In the second case, a validation logic of the transfer direction is associated with the bidirectional link such as to permit an alternate transfer in the two directions on said link. This logic may be integrated in the management processor  $(PG_j)$  associated with the cache memory  $(MC_j)$  to which said bidirectional link is connected.

[0040] It will be understood that each series link may ultimately be provided with a higher number of series links.

[0041] In the multiprocessor system according to the invention, the address communication means may cover essentially two forms embodiments: in the first case, it may consist of a parallel address communication bus for blocks (BUSA), common to all of the processors (CPU<sub>i</sub>) and connecting the latter and the central memory (RAM) in a conventional manner with an arbitrator bus (AB) adapted to manage access conflicts on said bus. It is necessary to note that this address bus is only utilized for communication of addresses of blocks: in the plan of the structure, this bus is identical to the parallel address communication bus of known systems, for which no problems of saturation are interposed, since it will be freed right after transfer of the address block.

[0042] However, another embodiment of this address communication means may be considered in the multiprocessor system of the invention, consisting in operating the series links for transfer of blocks of information (b<sub>i</sub>) to transfer the addresses of these blocks.

[0043] In this case, a complementary shift register (RDC<sub>j</sub>) is connected to each series link (LS<sub>j</sub>) in parallel with the corresponding memory shift register (RDC<sub>j</sub>). The addresses transmitted by said series link are thus loaded into each of these complementary registers (RDC<sub>j</sub>). An access management arbitrator connected to said registers (RDC<sub>j</sub>) and to the central memory (RAM) is thus provided for selecting the addresses contained in said registers and for managing the conflicts of access to the central memory (RAM). Such an arbitrator is conceivably known it itself, this type of access conflicts being now resolved for a number of years. In this embodiment, the presence of a parallel communication address bus is avoided, but the management resources are made more heavy.

[0044] Further, the multiprocessor system according to the invention is particularly well suited for managing in an efficient manner the problems of coherence of the data shared between treatment processors. In effect, the conventional solutions for managing these shared data find their limits in the known systems from the fact of the bottleneck at the level of the communication of information, but become, on the contrary, perfectly satisfactory and efficient in the system of the invention where such a bottleneck no longer exists, such that this system may be equipped with shared data management means of an analogous concept to that of known systems.

[0045] For example, one traditional solution of shared data management consists in avoiding the relay of shared data by the cache memories: in a conventional manner, a partition logic (LP<sub>j</sub>) is associated with each treatment processor (CPU<sub>j</sub>) in order to differentiate the addresses of the shared data and those of the non-shared data so as to direct the first directly toward the central memory (RAM) and the second toward the corresponding cache memory (MC<sub>1</sub>).

[0046] In a first version of the architecture according to the invention, the system comprises:

[0047] a special bus for parallel communication of words (BUSD) connecting the processors (CPU<sub>j</sub>) and the central memory (RAM),

[0048] a partition logic (LP<sub>j</sub>) associated with each processor (CPU<sub>j</sub>) and adapted to differentiate the addresses of the shared data and those of the non-shared data in

such a manner as to transmit the non-shared data on the address communication means with their identification,

[0049] a decoding logic (DEC) associated with the central memory (RAM) and adapted to receive the addresses with their identification and to direct the data into the memory output either to the corresponding memory shift register (RDM<sub>j</sub>) for the non-shared data, or to the special word communication bus (BUSD) for the shared data.

[0050] This solution presents the advantage of being very simple in the architectural plan. The presence of the special parallel communication bus (BUSD) leads to better performances with respect to a solution which consists in utilizing the series connections for transferring not only the blocks of non-shared data but also the words of shared data. It should be noted that this latter solution may, in some cases, be provided in case of low flow of shared data.

[0051] In another version, the system is provided with a special bus for parallel communication of words and a special common bus for communication of addresses of words (BUSAM) in order to transfer the data by the special word bus (BUSD), and direct the non-shared data to the address communication means (which may comprise a parallel communication bus where the communication is carried out by the series links).

[0052] The presence of a special bus for communication of addresses of words permits, in this version, to move back the saturation limit of the address communication means, in case of high demand for shared data.

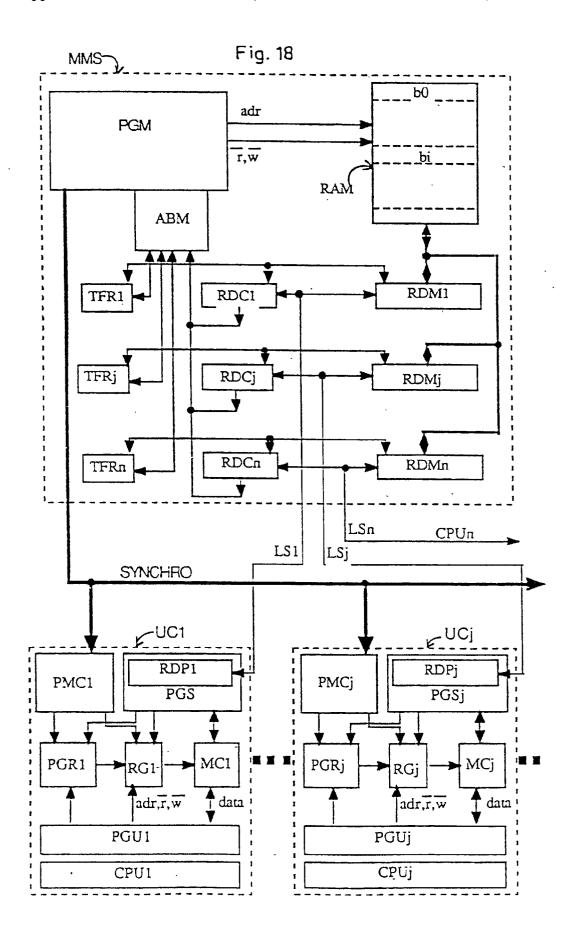

[0053] Another version which will be preferred in practice in the case in which the address communication means comprises a parallel address communication bus (BUSA) consists in providing the system with a memory management processor (PGM) associated with the memory (RAM) and a snooper processor with a bus (PE) associated with each treatment processor (CPU;) and to the corresponding management directory (RG<sub>i</sub>). The memory management processor (PGM) and each (espion) processor, of structures known in themselves, are connected to the address communication bus (BUSA) in order respectively to oversee and to treat the addresses of blocks transmitted on said bus in such a manner as to permit an updating of the central memory (RAM) and of the associated cache memory (MC<sub>i</sub>) in case of detection of an address of a block present in the associated directory (RG<sub>i</sub>).

[0054] The memory management processor (PGM) and each snooper processor (PE<sub>j</sub>) associate status bits of each block of information, holding them open as a function of the nature (read or write) of the requirements of the block which transitions on the bus (BUSA) and assures the coherence of the shared data while using these status bits which permit them to force or not write a block into the central memory at the moment of the requests on the bus (BUSA).

[0055] In the case referred to previously where the communications of addresses are made by the series connections, the management of shared data may also be assured in a centralized manner, by a memory management processor (PGM) associated with the central memory (RAM) and a processor for maintaining the coherence of the shared data (PMC<sub>j</sub>) associated with each treatment processor (CPU<sub>j</sub>) and with the corresponding management directory (RG<sub>j</sub>), each

coherence maintenance processor being connected to a synchronization bus (SYNCHRO) controlled by the memory management processor (PGM), in such a manner as to permit an updating of the central memory (RAM) and of the associated cache memories ( $MC_i$ ) in case of detection of an address block, an updating of the central memory (RAM) and the cache memories ( $MC_i$ ) at each address selection in the complementary shift registers (RDC<sub>i</sub>).

[0056] As before this operation is assured due to the status bits associated with each block of information by the processor (PGM).

[0057] It should be noted that a synchronization bus of the type hereinafter defined may, in some cases, be provided in the preceding architecture where the address of blocks move on a common address bus BUSA. In this case, the snooper processors (PE<sub>j</sub>) are urged by the memory management processor (PGM) via the synchronization bus, and this only when they are concerned by the transfer. Thus, non-useful access to the cache memories is avoided. The snooper processors become then passive (since driven by the processor PGM) and they are designated more by the more appropriate expression "coherence maintenance processor" according to the terminology hereinabove utilized.

[0058] Another solution consists in reserving the parallel address communication bus (BUSA) for the transfer of addresses of blocks of shared data and using the series links for the transfer of blocks of non-shared data.

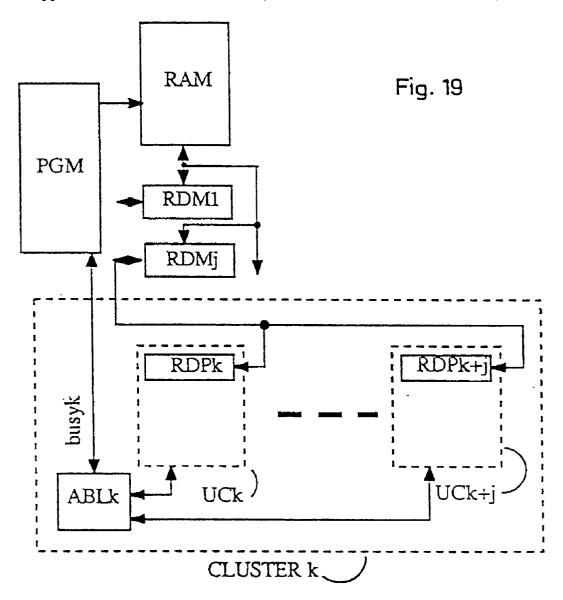

[0059] Further, the multiprocessor system according to the invention lends itself to the regroupings of treatment processors on a same series link, in such a manner as to limit the series links and the corresponding memory shift registers (RDM<sub>1</sub>) necessary.

**[0060]** The number of memory shift registers (RDM<sub>j</sub>) may correspond to the number of series links (LS<sub>j</sub>), to which case each memory shift register (RDM<sub>j</sub>) is connected in a static manner to a series link (LS<sub>j</sub>) specifically appropriated to said register.

[0061] The number of memory shift registers  $(RDM_j)$  may also be different from that of the series connections  $(LS_j)$  and in particular less, in which case these registers are connected in a dynamic manner to the series links  $(LS_j)$  through an interconnection network.

[0062] As in conventional systems, the central memory (RAM) may be divided into 'm' memory banks (RAM $_1$ ... RAM $_p$ ... RAM $_m$ ) arranged in parallel. Each memory shift register (RDM $_j$ ) is then comprised of m elementary registers (RDM $_j$ 1... RDM $_j$ p... RDM $_j$ m) connected in parallel to the corresponding series link (LS $_j$ ). However, a level of supplementary parallelism and a better electrical or optical adaptation of the connection is obtained in a variation in which each memory bank RAM $_p$  is connected to each processor CPU $_i$  by a series link from point to point LS $_i$ p.

[0063] In order to provide transfer performance at least equal to those of conventional systems with a parallel bus, the system according to the invention is preferably synchronized by a clock of a frequency F at least equal to 100 megahertz. The memory shift registers (RDM<sub>j</sub>) and processor shift registers (RDP<sub>j</sub>) may very simply be of a type adapted to present a shift frequency at least equal to F.

[0064] In the case of very high frequencies (particularly greater than 500 megahertz with current technology), the registers may be divided into sub-registers of a lower shift frequency, and then multiplexed.

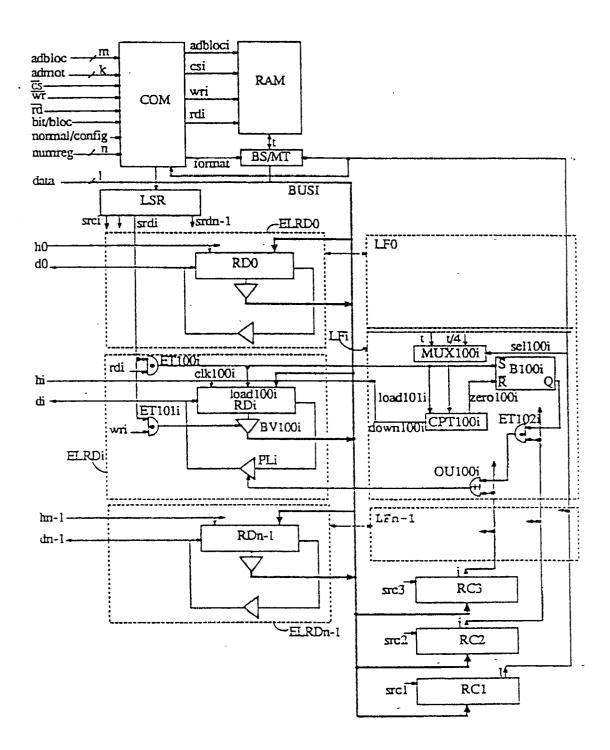

[0065] The invention also relates to a multiport series memory component, susceptible of equipping the multiprocessor system previously described, in order to simplify the fabrication. This component, which may have different applications, is constituted by an integrated circuit comprising a random access memory (RAM) of a pre-determined width corresponding to a block of information (bi), an assembly of shift registers  $(RDM_1 \dots RDM_i \dots RDM_n)$ , each of a capacity corresponding to the size of the memory, an internal parallel bus (BUSI) connecting the access of the memory and the shift registers, a selection logic of a shift register (LSR) adapted to validate the connection on the internal bus between the memory and a predetermined shift register, and an assembly of external input/output pins for the input of addresses to the memory (RAM), for the input of addresses to the selection program (LSR), for the input and the validation of transfer commands in read or write of a block of information (bi) between the memory (RAM) and the shift registers (RDM<sub>i</sub>), for the input of a clock signal to each shift register (RDM<sub>i</sub>), for the input bit by bit of a block of information (bi) to each shift register (RDM,) and for the output bit by bit of a block of information from each shift register (RDM<sub>i</sub>).

[0066] This component may be made parametrable by the adjunction of configuration registers ( $RC_1$ ,  $RC_2$ , . . . ) permitting particularly a choice of sizes of blocks of information (bi) and of diverse modes of operation of the shift registers.

[0067] The invention having been described in its general form, is illustrated by the description which follows in reference to the accompanying drawings which show without limitation several embodiments. In these drawings, which form an integral part of the present description:

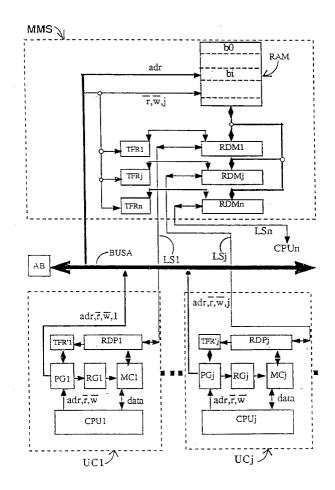

[0068] FIG. 1 is a block diagram of a first embodiment of the multiprocessor system according to the invention;

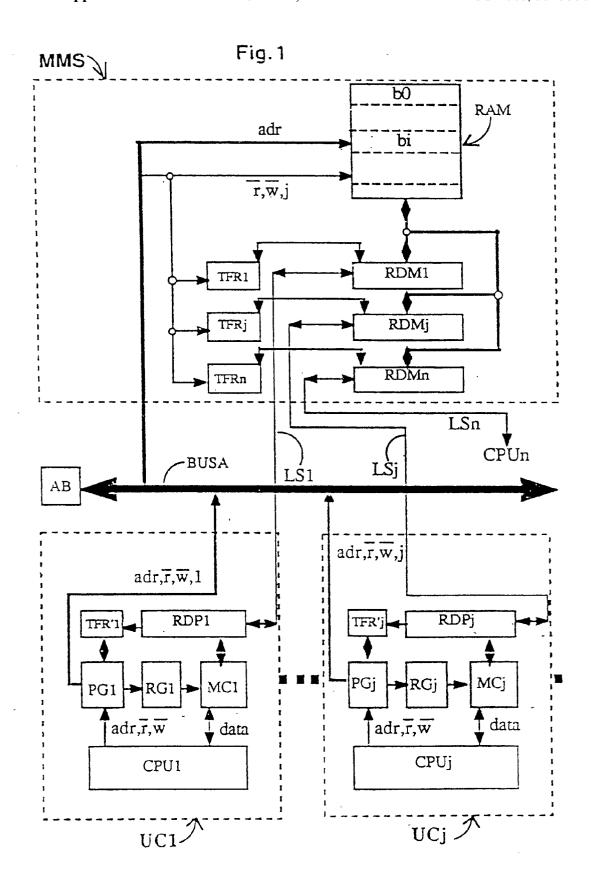

[0069] FIG. 2 is a diagram giving the calculated performance curve of this system (A) and, by way of comparison, the corresponding curve (B) for a conventional multiprocessor architecture with a common bus;

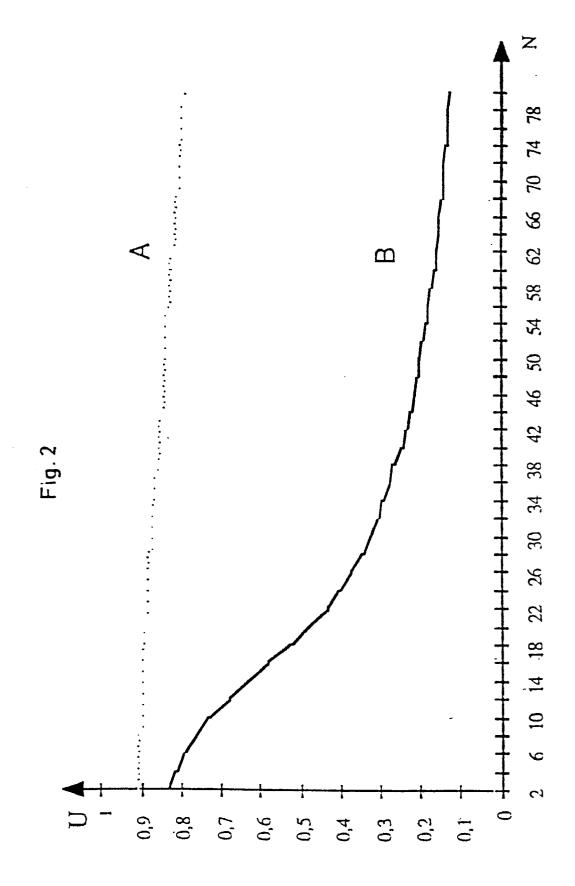

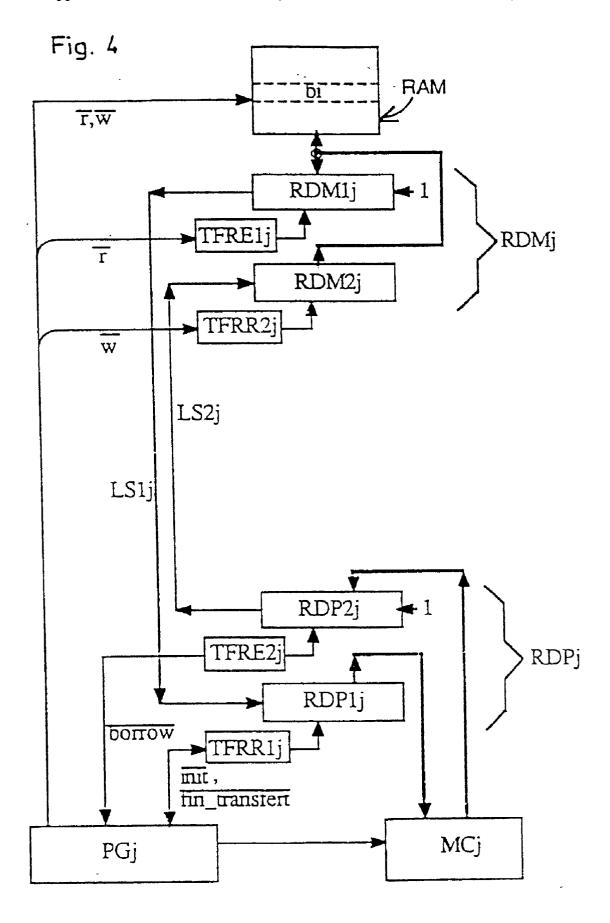

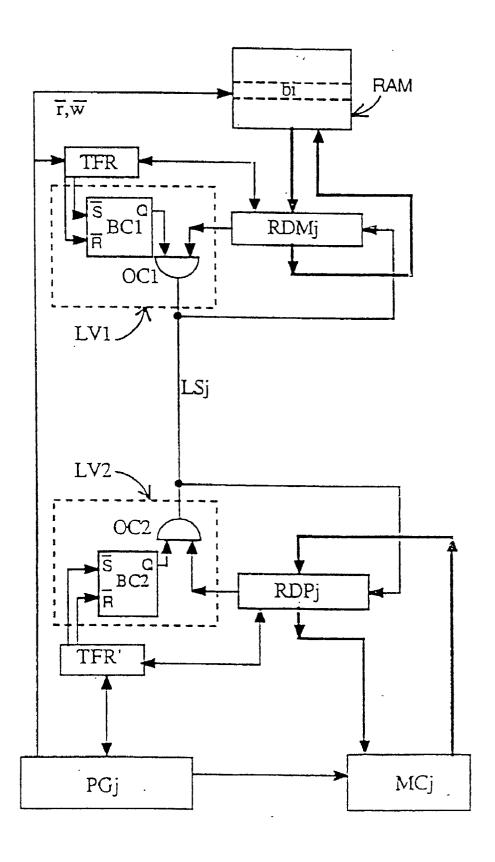

[0070] FIGS. 3, 4 and 5 are detailed logic schematics of functional units of the system of FIG. 1;

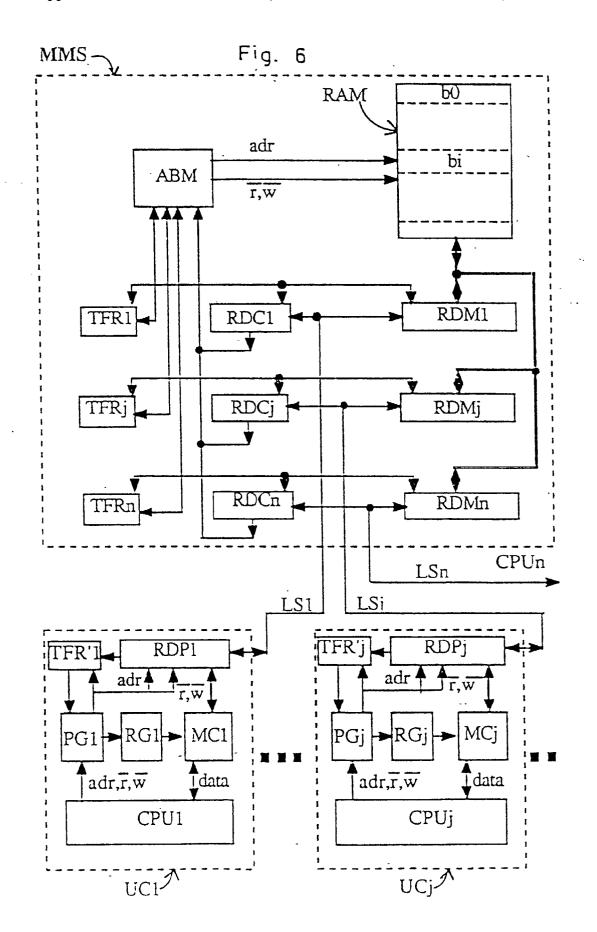

[0071] FIG. 6 is a block diagram of another embodiment of the system;

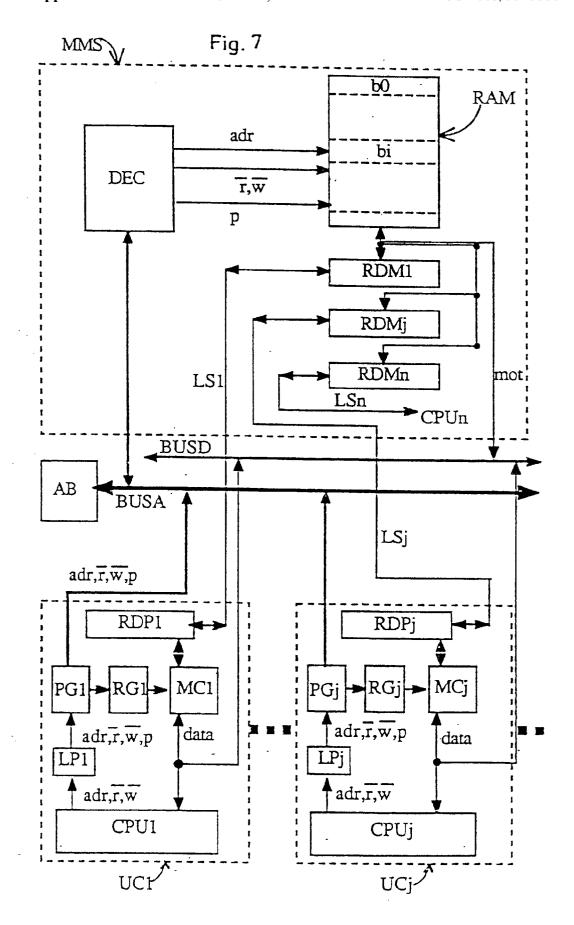

[0072] FIG. 7 is a block diagram of a system of the type as that of FIG. 1, provided with shared data management means;

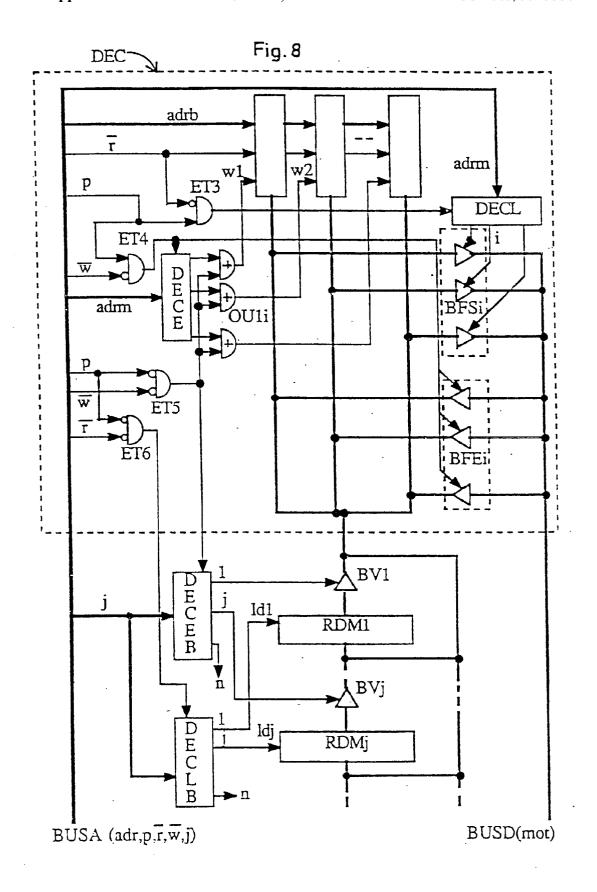

[0073] FIG. 8 is a detailed logic diagram of a sub-assembly of the system of FIG. 7;

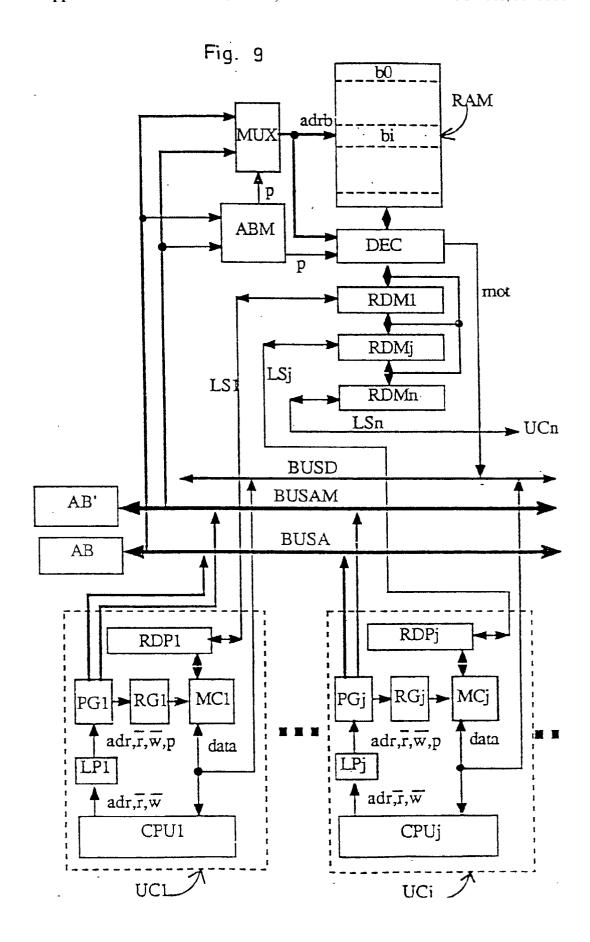

[0074] FIG. 9 is a block diagram of a system analogous to that of FIG. 7 with a variation in the shared data management means;

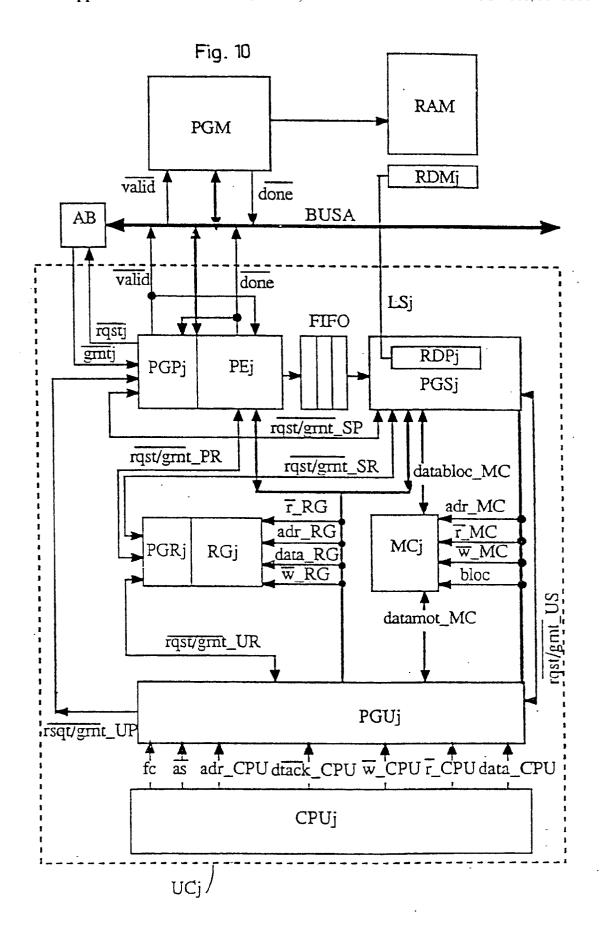

[0075] FIG. 10 is a block diagram of an analogous system, provided with a different shared data management means;

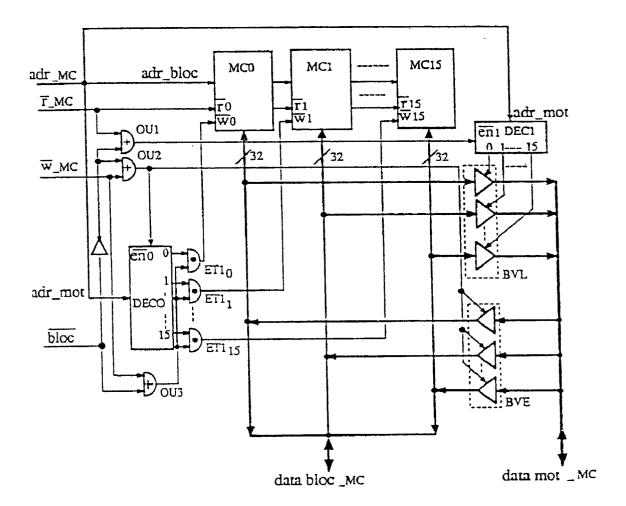

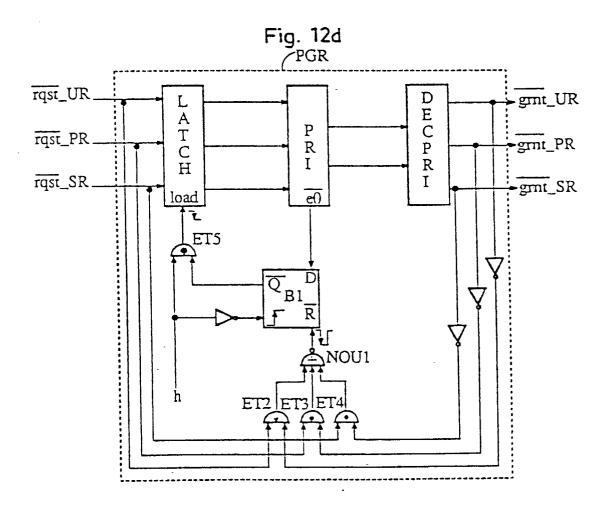

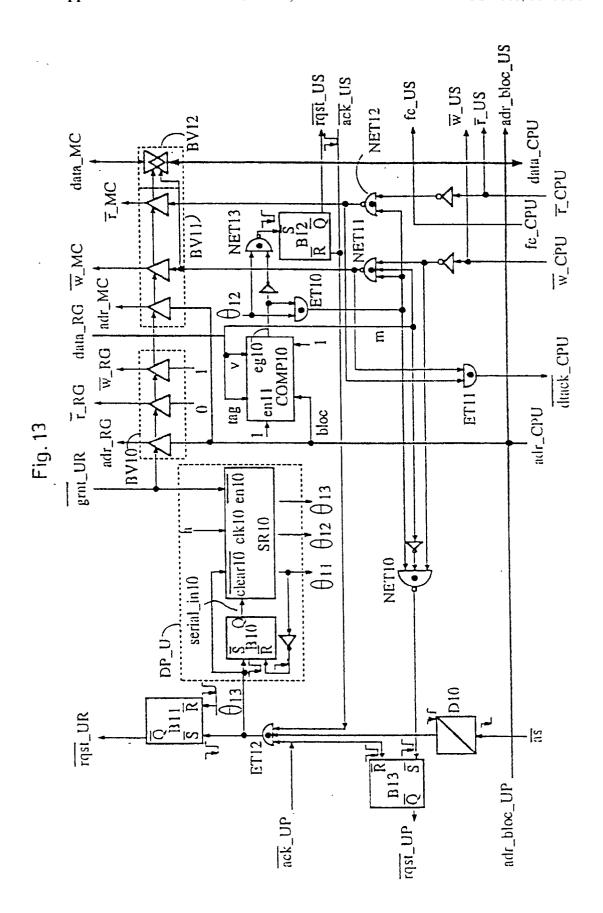

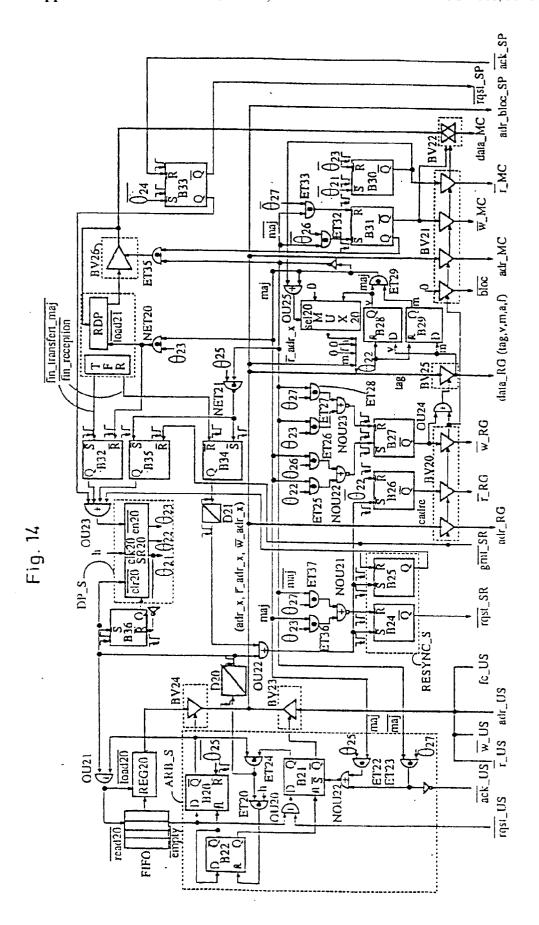

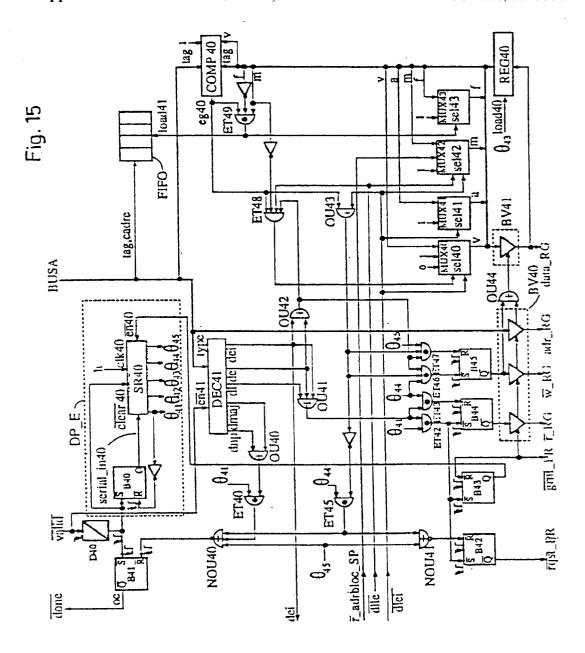

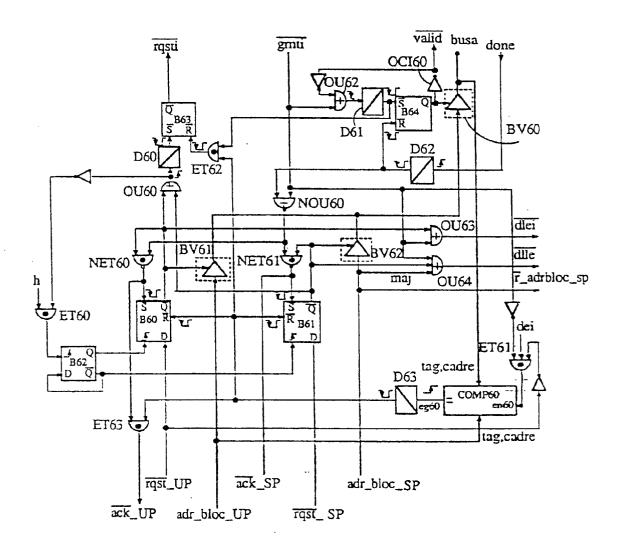

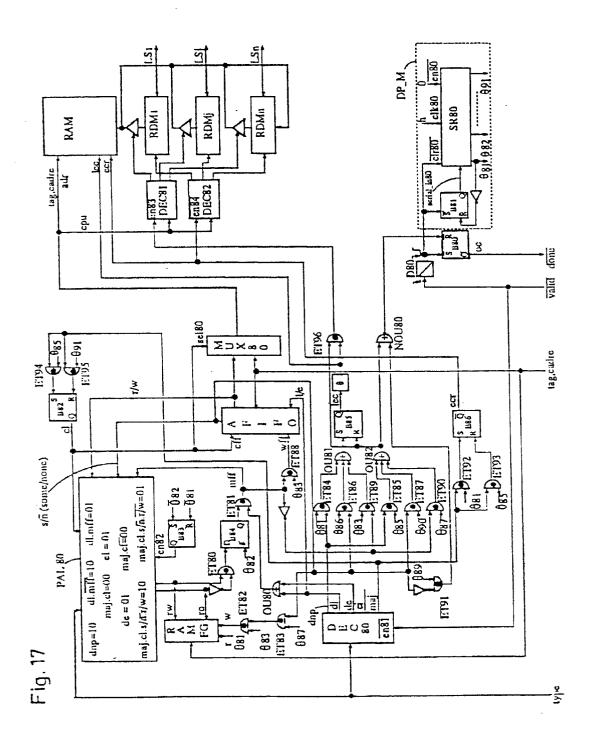

[0076] FIGS. 11, 12*a*, 12*b*, 12*c*, 12*d*, 13, 14, 15, 1617 are detailed logic schematics of the functional units of the processor system of FIG. 10;

[0077] FIG. 18 is a block diagram of a system of the type as that of FIG. 6, provided with means for shared data management:

[0078] FIG. 19 is a simplified block diagram of a variation of the system, in which several central units share the same series link;

[0079] FIG. 20a is a block diagram of a preferred embodiment, in which the central memory is organized into several memory banks,

[0080] FIG. 20b is a variation of the architecture shown in FIG. 20A;

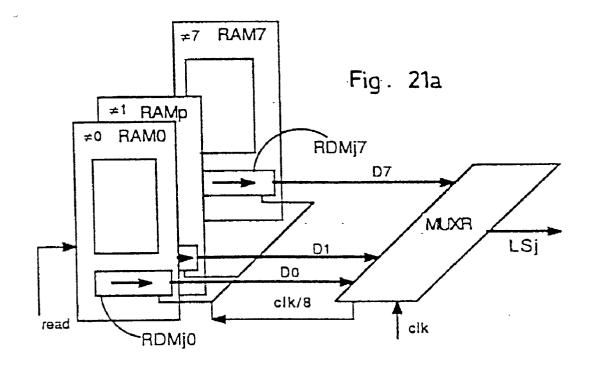

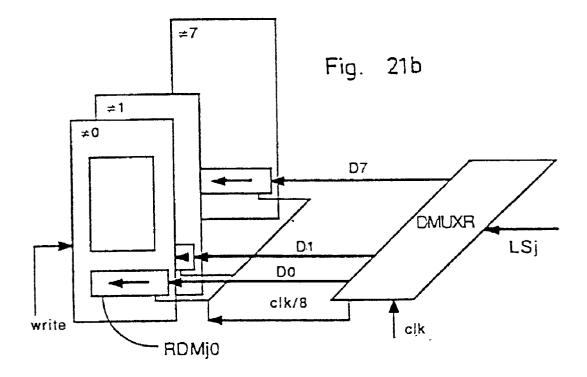

[0081] FIGS. 21a and 21b schematically show another structure of the memory RAM susceptible of equipping said system; and

[0082] FIG. 22 is a block diagram showing the structure of a multiport series memory component, capable of equipping the system.

[0083] The apparatus presented in the form of a block diagram in FIG. 1 is a multiprocessor system having n treatment processors  $CPU_1 \dots CPU_j \dots CPU_n$ . Shown in this figure are two treatment processors CPU1 and  $CPU_j$  with their associated logic. Each of these treatment processors is of a conventional type, for example "Motorola 68020" or "Intel 80386" . . . and with peripheral interfaces and being provided with a virtual memory device.

[0084] The apparatus comprises a central random access memory RAM provided in a conventional manner from integrated memory circuits: in particular dynamic RAM "INTEL," "NEC," "TOSHIBA" . . . of 256 Kbits, 1 Mbits, 4 Mbits . . . depending upon the application. This memory is organized in blocks of information b<sub>o</sub> . . . b<sub>i</sub> . . . of predetermined size t (usually 256 bits per 2 Kbits) and the access front of said memory corresponds to the size of one block

[0085] The central memory is connected in parallel to n shift registers  $RDM_1 \dots RDM_j \dots RDM_n$  called memory registers, each memory register having the size t of one block of information. Each of these registers is provided from high speed technology ("ASGA"), one latch able to be loaded or unloaded in one cycle of the central memory RAM. The number n of registers is equal to the number of processors  $CPU_i$ .

[0086] A cache memory  $MC_j$  is associated in a known manner with each processor  $CPU_j$ . Each cache memory comprises a conventional high speed random access memory, of low capacity with respect to the central memory RAM. A directory  $RG_j$  and a management processor  $PG_j$  are, in a traditional manner, connected to the cache memory and to the treatment processor for managing the information flowing in the cache memory.

[0087] Further, in the system of the invention, a shift register  $RDP_j$  called a processor register is connected by its parallel port to each cache memory  $MC_j$ . Each processor register  $RDP_j$  is of a size corresponding to that of a block bi and of a structure similar to that of the memory registers  $RDM_i$ .

[0088] Each memory register RDM<sub>j</sub> is connected by its series port to the series port of a processor register RDP<sub>j</sub> by a series link LS<sub>j</sub>. Examples of the provision of this series link, which may comprise a bidirectional link or two unidirectional links, are illustrated in FIGS. 4 and 5. The control of the transfer of the blocks b<sub>i</sub> between corresponding registers RDM<sub>j</sub> and RDP<sub>j</sub> is assured by the transfer logic TFR<sub>j</sub> and TFR' which are associated in a symmetrical manner with the memory register RDM<sub>j</sub> and with the processor register RDP<sub>j</sub>. One embodiment of these transfer logics (known in themselves) is detailed in FIG. 3.

[0089] The central memory RAM, memory shift registers  $RDM_1 \dots RDM_n$ , and associated transfer logics  $TFR_1 \dots TFR_n$  comprise a functional assembly called a "multiport series memory" MMS. The treatment processor assembly  $CPU_j$ , cache memory  $MC_j$ , management directory for the cache  $RG_j$ , management processor of the cache  $PG_j$ , shift register processor  $RDP_j$  and the associated transfer logic  $TFR_j$  constitute a "functional" assembly called a "central unit"  $UC_j$ .

[0090] Further, the system comprises means for communication of addresses of blocks of the processors  $CPU_j$  to the central memory RAM, comprising in the example a common parallel communication bus BUSA on which are connected the processors  $CPU_j$  (though their management processor  $PG_j$ ) and the central memory RAM.

[0091] Access to the bus BUSA is controlled in a conventional manner by a bus arbitrator AB.

[0092] The general operation of the architecture hereinabove defined is as follows:

[0093] A processor  $CPU_j$  carries out a program proper comprising instructions, which are found in the form of words in the central memory RAM with extracts in the associated cache memory  $MC_j$ . On these instructions of the program, the processor  $CPU_j$  is brought either to read the words of data which themselves are found in the central memory RAM or in the cache memory  $MC_j$  in the form of extracts, or to write the words of data in the central memory RAM and in the cache memory  $MC_j$ .

[0094] Each operation of a processor CPU<sub>j</sub> called a "request") requires the furnishing of the address adr of the word concerned, the nature r, w of the operation (read, write) and the data exchange of the word concerned.

[0095] Each request of a word activates the processor  $PG_j$  which then consults in a conventional manner the directory of the cache  $RG_j$  which indicates if the block bi containing the word concerned is present in the cache memory  $MC_j$  at, in some cases, the frame of the block in the cache memory where the block searched for is found.

[0096] If the block bi containing the word concerned is in the cache memory  $MC_j$ , then in case of reading, this word is read in said cache memory and sent to the processor  $CPU_j$ . In case of writing, the word furnished by the processor  $CPU_j$  is written in the cache memory: the memory transaction is terminated.

[0097] If the block containing the word concerned is not in the cache memory  $MC_j$ , then a reading of the block bi into the central memory RAM is necessary. Two cases may be produced.

[0098] First Case

[0099] The cache memory MC<sub>i</sub> makes use of at least one free block, determined by the processor PG; with the help of status bits associated with each input of the directory RG<sub>i</sub>. In this case, the processor PG, is requesting, in a conventional manner, the bus BUSA while referring its demand to the bus arbitrator AB. This latter reconciles, in turn, the bus BUSA to the processor PG; which agrees while writing to the central memory RAM, the block read in the memory being loaded into the register RDM; identified by the origin; of the call. The end of the reading cycle translates by the liberation of the bus BUSA and the activation of the transfer with the series link LS<sub>i</sub> permitting the transfer of the contents of the memory register RDM, in the processor register RDP. The end of the transfer activates the writing in the cache memory MC; of the contents of the processor register in the placement of the block reserved for this effect and the transaction may terminate as before.

[0100] Second case

[0101] The cache memory  $MC_j$  is not arranged for free placement then, by a conventional algorithm, a placement of the cache is made a candidate for receiving the block requested. Two situations may be encountered:

[0102] The block contained in the candidate position has not been modified since its installation: it is simply eliminated while freeing the frame of the block by a simple writing of a status bit in the directory  $(RG_j)$  and the transaction may proceed as before.

[0103] The block contained in the candidate position has been modified and an operation of the central memory is required. For this fact, the management processor PG<sub>j</sub> transfers the candidate block to the processor register RDP<sub>j</sub>, activates the transfer of the processor register RDP<sub>j</sub> to the memory register RDM<sub>j</sub>, then requests the common bus BUSA while referring its request to the arbitrator AB. When the arbitrator admits the bus to the management processor PG<sub>j</sub>, the latter activates a write command which has the effect of transferring the contents of the memory register RDM<sub>j</sub> to its position in the central memory RAM. The operation of the memory RAM is terminated and the transaction may continue as before.

[0104] Thus, in the apparatus of the invention, the exchanges between the treatment processors  $CPU_j$  and their cache memory  $MC_j$  and associated logics  $RG_j$ ,  $PG_j$ , are carried out in a conventional manner. By contrast, the transfers of blocks between central memory RAM and cache memories  $MC_j$  proceed, no longer by a common parallel bus, but by the series links  $LS_j$  dedicated to each treatment processor  $CPU_j$ , the common bus BUSA only serving for the transfer of the addresses and having thus a considerably reduced traffic.

[0105] It is known that, for conventional common bus architectures, a modelization studied by "PATEL" ("Analysis of Multiprocessors With Private Cache") JANAK H. PATEL, IEEE Transactions on Computers, Vol C.31, No. 4, April, 1982) has led to the following approximate formula giving the efficiency U as a function of the number of processors present:

$$U = \frac{1}{1 + m(W + tf)}$$

[0106] where the efficiency U is the average rate of utilization of each treatment processor,

[0107] m is the probability for a treatment processor to make a memory request, not present in its the cache memory (this probability m= . Pa is proportional to the probability of the absence Pa of the information in the cache memory and a factor which is a function of the power of the treatment processor expressed as a percentage of the memory requests):

[0108] W is the average waiting time of the common bus, which is a function of the number of processors,

[0109] If is the transfer time of a block from the central memory to a cache memory.

[0110] The hypotheses from which this formula has been established show that it is applicable to the architecture according to the invention, with a level of approximation comparable to the level of approximation of the formula for conventional common bus architecture.

[0111] It is thus possible to compare the performances of the two types of architecture while -assuming that the components common to the two architectures are of identical characteristics.

[0112] FIG. 2 gives the curves obtained of the efficiency U as a function of the number n of processors for the following parameters, the parameters common to the two systems being identical, and all of a usual value:

[0113] size of block  $b_i$ =64 octets,

[0114] size of word for the parallel transfer on common bus=4 octets,

[0115] central memory RAM access time=100 nanoseconds,

[0116] cycle time of the bus BUSA=50 nanoseconds,

[0117] series transfer frequency=500 Mhz,

[0118] probability of absence Pa=0.005 (cache memory of 16 octets),

[0119] power factor of the processors: =0.5.

[0120] It is established by comparing the curves A (architecture of the invention) and B (conventional architecture) that the architecture according to the invention has an efficiency clearly superior to the conventional architecture. The architecture of the invention permits putting in place a number of processors very superior to the conventional common bus architecture which, in practice, cannot exceed about ten processors. For example, in the conventional case, an efficiency of 0.75 is obtained at the tenth processor, whereas it is obtained for more than 80 processors in the case of the invention.

[0121] FIG. 3 presents an embodiment of a transfer logic TFR<sub>j</sub> or TFR'<sub>j</sub> permitting the transfer of a block bi of information from a memory register RDM<sub>i</sub> to a processor

register RDP<sub>j</sub> (the inverse transfer is assured by the symmetric means not shown in this figure). Each logic TFR<sub>j</sub> or TFR'<sub>j</sub> comprises a part for control of the output TFRE<sub>j</sub> and TFRE'<sub>j</sub>, and a part for control of the reception TFRR<sub>j</sub> and TFRR'<sub>j</sub> which are activated in a crossed manner (output TFRE<sub>j</sub> activated in synchronism with the reception TFRR'<sub>j</sub>). The system comprises a clock generator H the frequency of which fixes the speed of transmission and furnishes the clock signal h at the output part TFRE<sub>j</sub> and at the reception part TFRR'<sub>j</sub>.

[0122] In the output part  $\overline{TFRE_j}$  a countdown register DC receiving at its load input  $\overline{load}_2$  the reading signal  $\overline{r}$  from the management processor  $PG_j$  permits allowing to pass t+1 pulses of the clock h through a logic port ET1 controlled by a pass to zero signal "borrow", the output of this port ET1 being connected to the input of the "down" counting of the countdown device DC and to the shift input shift1 of the memory register RDM<sub>j</sub>.

[0123] In the reception part TFRR'<sub>j</sub>, a flip flop B is connected by its data input D to the series output of the processor register RDP<sub>j</sub>, the clock input clk of this flip flop being connected to the clock H for receiving the signal h. An initialization signal "init" furnished by the management processor  $PG_j$  is connected to the input  $\bar{S}$  of the flip flop B and to the loading input load3 of the processor register RDP<sub>j</sub>. The output Q of the flip flop transmits a control signal end-transfer to the logic port ET2, permitting the clock signal h to pass toward the shift input shift2 of the processor register RDP<sub>j</sub>. This control signal is also delivered to the management processor  $PG_j$  for indicating the end of transfer of the block.

[0124] The operation of the assembly is as follows: the management processor PG;, after having obtained access to the central memory RAM via the bus BUSA, carried out its reading of the block bi while furnishing the address of the block concerned and the reading signal r. This signal releases the activation of the output part TFRE;: the final front of the reading signal r provokes the loading of the block bi into the memory register RDM, while activating the signal load1 and the loading of the value t+1, corresponding to the size in bits of the block bi plus one supplementary bit called "start", into the countdown register DC by the signal load2. This has for effect to reset to 1 the signal borrow and authorize the transfer clock H to furnish, through the logic port ET1 conditioned by this borrow signal, t+1 clock pulses h: these pulses have for effect to shift by the input shift1 t+1 bits from the memory register RDM; and to cause to wait for the value 0 from the down input to the countdown device DC: the signal borrow is reset to zero and locks the operation of the output part TFRE<sub>i</sub>.

[0125] Thus, the series connection  $LS_j$ , initially having the logic rest state 1, transfers the start bit 0, then the t bits of the block bi, and then returns to the logic rest state 1, the latter bit sent being the value 1 forced on the series input of the memory register  $RDM_j$ .

[0126] As a preliminary to the reading demand, the management processor  $PG_j$  has initialized the receiving part TFRR' while activating the  $\overline{\text{init}}$  signal which has the effect of loading the processor register  $RDP_j$  with t bits to 1 through the input  $\overline{\text{load}}$ 3 and to set the output Q of the flip flop B to the logic state 1 by the input  $\overline{\text{S}}$ . This output Q then validates the logic port ET2 which allows the clock signal h to pass

toward the input shift2 of the processor register RDP1. At each clock pulse this processor register furnishes a bit on its series output which is stored in the flip flop B. The first bit  $\bf 0$  which is presented has the effect of setting to zero the output Q of the flip flop B and locking the clock signal h on the gate ET2. This first bit  $\bf 0$  being the start bit which precedes the block bi, this latter is then trapped in the processor register RDP $_{\rm j}$  when the management processor PG $_{\rm j}$  is notified of the change of state of the flip flop B by the end-transfer signal: the management processor PG $_{\rm j}$  need only come to read this block bi on the parallel output of the register RDP $_{\rm j}$ .

[0127] The writing of a block bi to the central memory RAM requires the presence of a logic TFRE'<sub>j</sub>, identical to the logic TFRE<sub>j</sub>, associated with the processor register RDP<sub>j</sub>, and a logic TFRR<sub>j</sub>, identical to the logic TFRR'<sub>j</sub>, associated with the memory register RDM<sub>j</sub>. In this case, the signal init of the logic TFRR<sub>j</sub> is connected to the writing signal  $\tilde{w}$ : the liberation of the memory register RDM<sub>j</sub> automatically rearms the receive logic TFRR<sub>i</sub>.

[0128] This embodiment of the transfer control logic is only one possible example: the transmitter register may be in permanent shifting itself, and the receiver register activated for t pulses of the clock on detection of the start bit at the beginning of transfer.

[0129] The clock H may be connected to two registers, or two local independent clocks may be used, the synchronization being obtained in a conventional manner by an introduction of synchronization.

[0130] The system shown in FIG. 4 comprises a divided memory shift register RDM<sub>j</sub> and RDM<sub>2</sub>, a divided processor shift register RDP1<sub>j</sub>, and RDP2<sub>j</sub>, two unidirectional series links LS1<sub>j</sub> and LS2<sub>j</sub>, one connecting the memory register RDM1 to the processor register RDP<sub>j</sub> in such a manner as to transmit the contents of the first to the second, the other connecting the memory register RDM2<sub>j</sub> to the processor register RDP2<sub>j</sub> in such a manner as to transmit the contents of the second to the first, and the associated logics for the control of the transfer: TFRE1<sub>j</sub> for RDM1; TFRR2<sub>j</sub> for RDM2; TFRE2<sub>j</sub> for RDP@<sub>i</sub>; TFRR1<sub>j</sub> for RDP1<sub>j</sub>.

[0131] For reading a block of information bi into the central memory RAM, the management processor PG<sub>j</sub> initializes by the signal init the logic TFRR1<sub>j</sub> associated with the processor register RDP<sub>j</sub>1, then activates its demand to read to the memory RAM by the read signal r. This signal activates the logic TFRE1<sub>j</sub> associated with the memory register RDM1<sub>j</sub>: this assures the transfer on the link LS1<sub>j</sub> of the block bi of information. The end of the transfer is detected by the logic TFRR1<sub>j</sub> associated with the processor register RDP1<sub>j</sub> which notifies the management processor PG<sub>j</sub> of the arrival of the block bi by the signal end\_transfer. The management processor; PG<sub>j</sub> thus transfers the contents of the processor register RDP1<sub>j</sub> into the cache memory MC<sub>j</sub>.

[0132] For writing a memory block bi, the management processor  $PG_j$  loads the processor register RDP2 with the block bi concerned extracted from the cache memory  $MC_j$ , which activates the transfer of this block on the link LS2 $_j$ . The transfer logic TFRR2 $_j$  associated with the memory register RDM2 $_j$  assures the good reception of this block. The management processor  $PG_j$  is notified of the end of transfer by the change of state of the signal borrow issued from the

transmission logic TFRE2 $_j$ . The management processor  $PG_j$  then carries out its writing request which becomes effective at the time of activation of the writing signal w. This has the effect of transferring the contents of the register  $RDM2_j$  into the central memory RAM and to reinitiate for a next transfer the logic TFRR2 $_i$ .

[0133] This system authorizes a simultaneous transfer of blocks in two directions and permits treating more rapidly the defects of blocks bi in the cache memory  $MC_j$  when the latter is saturated. It authorizes also the operation of a conventional mechanism for anticipation of the reading of blocks.

[0134] In another embodiment shown in FIG. 5, the connection  $LS_j$  comprises a single bidirectional link provided at each extremity with a validation logic LV1 and LV2 constituted by a logic gate with two open connector inputs OC1 and OC2, one of the inputs being connected to the series output of the memory register  $RDM_j$  for the gate OC1 and the processor register  $RDP_j$  for the gate OC2, the other input being connected to the output Q of a control flip flop BC1 and BC2; each of these is connected by its inputs  $\bar{S}$  and  $\bar{R}$  to the transfer logic TFR for the flip flop BD1 and TFR' for the flip flop BD2.

[0135] Readings and writings are carried out in an exclusive manner, at the sole initiative of the management processor  $PG_i$ .

[0136] A reading memory activates the reading signal  $\bar{r}$  which causes the setting to 1 of the flip flop BC1 by its input  $\bar{S}$ , the resetting to zero being controlled, on the input  $\bar{R}$  by the transfer logic TFR at the end of the transfer of the block.

[0137] A writing memory releases a mechanism identical to the validation logic LV2.

[0138] Other combinations of registers/links are possible, and in the case of a bidirectional link, bidirectional shift registers may in particular be used, receiving a signal of the direction of transfer. This solution leads to the use of shift registers more complex in logic, therefor a priori less efficient in speed of transfer.

[0139] The speed of transfer coming to be very high, the shift registers RDM<sub>j</sub> and RDP<sub>j</sub>, their associated control logic TFR and TFR', the validation logics LV1 and LV2, are selected from a rapid technology (ECL, ASGA), and synchronized by a clock of a frequency F at least equal to 100 MHz

[0140] Another solution with multiplexed registers shown in FIG. 21 permits, as will be understood below, considerably reducing the quantity of efficient, and therefore costly logic necessary.

[0141] The multiprocessor of FIG. 1 was provided at the same time with a common communications bus for block addresses and data transfer series links. FIG. 6 shows, as a variation, a multiprocessor system of the same general principle, but in which data and addresses transfer by the series connections, in the absence of a common bus.

[0142] This system comprises, besides the memory registers  $RDM_j$ , complementary shift registers  $RDC_j$  able to store the addresses of blocks called for and controlled by a logic of the type  $TFR_j$ . Further, an access management arbitrator ABM is connected to the central memory RAM and to the

complementary registers  $RDC_j$  by their parallel output. Each logic  $TFR_j$  is connected to this arbitrator ABM of conventional structure. The management processor  $PG_j$  of each cache memory  $MC_j$  is connected to one part of the parallel input of the processor register  $RDP_j$ , in order to have access thereto in writing.

[0143] For reading a block bi in central memory RAM, the management processor PGi places the address of the block called for and the nature of the request (by a prefix bit: 1=read, 0=write) in the part of the register processor RDP; to which it is accessible, which has the effect of initializing the transfer of this information. The transfer logic TFR<sub>i</sub> detects the end of the transfer on the complementary register RDC; and activates a demand operation toward the arbitrator ABM. This is loaded for serializing and treating the read requests of the block in the central memory RAM while going to read the address of the block requested in the complementary register RDC; corresponding to the transfer logic selected by the arbitrator ABM, then in going to read the block in the central memory RAM which will then be loaded into the memory register RDM; and transmitted as before.

**[0144]** For writing a block in the central memory RAM, the management processor  $PG_j$  chains the transmission of the address then of the block to be written through the processor register  $RDP_j$ . The complementary register  $RDC_j$  receives at once the address and the nature of the request.

[0145] The transfer logic  $TFR_j$  analyzes this request and validates the reception of the block in the memory register  $RDM_j$  from the fact of the nature of the request (write). The transfer logic  $TFR_j$  is notified of the end of the transfer of the block  $b_i$  and then transmits its request for service to the arbitrator ABM. This request is treated, in turn, by the arbitrator which activates the writing of the block bi into memory.

[0146] Further, the multiprocessor system shown in FIG. 7 comprises means for management of the shared data, permitting treating, in a static manner, the classical problem of maintaining the coherence of the shared data. This system comprises the resources of the system of FIG. 1 (with the same reference characters) with the following logic and supplementary resources:

[0147] A special parallel communication bus for words BUSD connects the processors  $CPU_j$  and the central memory RAM. A partition logic  $LP_j$  is associated with each processor  $CPU_j$ . Each logic  $LP_j$  is constituted in a conventional manner by an assembly of coupled register-comparators connected in parallel on the address bus adr of the processor  $CPU_j$ , in order to provide a division of the memory space of the central memory RAM in the zone of non-shared data and shared data, said logic  $LP_j$  delivering to this effect a signal p (indicating the nature of the data, shared or not). A decoding logic DEC is associated with the central memory RAM, itself arranged to be controlled by a writing by word or by block by said logic DEC.

[0148] The decoding logic DEC is detailed in FIG. 8 and comprises a decoder DECL, receiving on its data input the address portion word adrm of the address adr, and connected through its validation input to the output of a logic gate ET3, each output i of said decoder being connected to a validation buffer of the type BFS<sub>i</sub>. The logic gate ET3 receives on its

inputs the signal p and the inverted signal  $\bar{\mathbf{r}}$ . A decoder DECE is connected through its validation input to the output of a logic gate ET4, its outputs being connected to an assembly of logic gates  $OU1_i$  of a number equal to the number of words in a block. The logic gate ET4 receives on its inputs the signal p and the inverted signal  $\bar{\mathbf{w}}$ . The output of the gate ET4 is also connected to an assembly of validation input buffers BFE1, BFE1... The central memory RAM may be controlled in writing by word. Each clipped word thus defined has its writing control input  $\mathbf{w_i}$ . The output of each logic gate  $OU1_i$  is connected to the input w1 of each clipped word of the central memory RAM.

[0149] FIG. 8 shows further the detail of the addressing of the memory registers RDM<sub>j</sub>, which comprises in the first place a decoder DECEB connected through its data input to the common bus BUSA, in order to receive the number  $_j$  of the processor concerned by the request of the central unit UC<sub>j</sub>. This decoder DECEB is connected through its validation input to the output of a logic gate ET5 and through its outputs  $1, 2 \dots_j$  to the validation buffers BV1, BV $_j \dots$  The logic gate ET5 receives on its inputs the signal p and the inverted signal  $\bar{w}$ . In the same manner, a decoder DECLB is connected through its data input to the field  $_j$  of the common bus BUSA and through its outputs  $1, 2 \dots_j$  of this decoder DECLB are connected to the loading inputs ld1, ld $_j$  of the memory shift registers RDM $_j$ . The logic gate ET6 receives on its inputs the signal p and the inverted signal  $\bar{r}$ .

[0150] The operation of the system is as follows: at each reference memory, the processor CPU<sub>i</sub> provides an address on its address bus adr, and the nature of the request: reading r or writing w. It waits for a datum in case of reading and furnishes a datum in case of writing. The address adr traverses the partition logic LP<sub>j</sub>, which indicates, by the signal p, if the address adr belongs to a zone of non-shared data (p=0) or of shared data (p=1). In the first case, the request is directed to the management processor PG; and is treated according to the mode of operation described in reference to FIG. 1. In the second case, the request is directly sent through the common bus BUSA. The bus address adr permits supplementary address streams permitting identification of the word concerned: the address adr is comprised of a block address part adrb and a word address part adrm. Thus, after agreement of the bus arbitrator AB, the central memory RAM receives either a block transaction request (p=0) and in this case, only the block part adrb of the address adr is significant, or a word transaction request (p=1) and, in this case, the whole address adr (block adrb and word adrm) is significant.

[0151] In case of a reading block, p=0 and r=0, the logic gate  $ET_6$  validates the decoder DECLB which delivers a loading signal  $LD_j$  to the shift register  $RDM_j$ , permitting loading into the latter the block read into the central memory RAM with the address adrb by the reading signal  $\bar{r}$ .

[0152] In the case of a writing block, p=0 and w=0, the logic gate ET5 validates the decoder DECEB which delivers a validation signal to the buffer  $BV_j$ , permitting the contents of this register to be presented to the central memory RAM and to thus be written to the address adrb, the output of the logic gate ET5 providing the block writing signal. This latter is broadcasted on the writing inputs w1, w<sub>j</sub>, ... to the clipped words of the central memory RAM across the logic gates  $OU1_i$ .

[0153] In case of word reading, p=1 and r=0, the logic gate ET3 validates the decoder DFCL which delivers a validation signal to the buffer BFS<sub>i</sub>, permitting the requested word (address adrm in the block adrb) of which the reading is assured by the signal  $\bar{r}$ , to be directed toward the special communication bus BUSD. This word is recovered directly by the processor CPU<sub>i</sub> on its data input data.

[0154] In case of writting word, p=1 and w=0, the logic gate ET4 validates the decoder DECE which furnishes on its output  $_{\rm i}$  a signal directed across the logic gate OU1; toward the writing input  $w_{\rm i}$  of the clipped word of the central memory RAM concerned. This signal present at the input  $w_{\rm i}$  permits writing in this sole clipped word the word furnished by the processor CPU $_{\rm j}$  on the data bus BUSD. The contents of this bus are presented in parallel on all the clipped words of the central memory RAM, due to an activation of the buffers BFE $_{\rm i}$  by the signal emitted by the logic gate ET4.

[0155] An essential characteristic of the architecture of the invention is to present a minimum load of requests on the common bus BUSA. In the architecture shown schematically in FIG. 7, the common bus BUSA is driven by the block addresses and the word addresses. The frequency of the word address requests is a function of the rate of shared data and may lead to a saturation of the common bus BUSA.

[0156] FIG. 9 shows a variation of a solution for reducing this load. The system provided comprises, in addition to the resources of FIG. 7, a bus BUSAM for the word addresses, an arbitrator AB' for arbitrating the access conflicts to the bus BUSAM, an arbitrator ABM for arbitrating the access conflicts in the origin of the busses BUSA and BUSAM, and connected to a multiplexer MUX which in turn is connected through its inputs to the two busses BUSA and BUSAM.

[0157] The operation of this system is as follows:

[0158] If the request concerns non-shared data (p=0), any lack of information generates a memory request of the block type which transfers through the common bus BUSA.

[0159] If the request relates to shared data (p=1), the request is directed toward the common bus BUSAM. Thus, the central memory RAM may receive simultaneous requests on the two busses BUSA and BUSAM, which must then be arbitrated. The arbitrator ABM allows, in a conventional manner, access to the central memory RAM by one of the two requests and reconstructs the signal p from the origin of the request (p=0 for BUSA, p=1 for BUSAM). The signal p thus controls both the multiplexer MUX which allows the signals from the bus concerned to pass through the request, and the decoding logic DEC: one is thus situated as in the preceding system.

[0160] It will be noted that the load is shifted from the common bus to the central memory RAM, since the rate of request at the level of this latter remains the same, and its cycle time is of the same order of magnitude or even greater than that of the bus cycle.

[0161] This solution is therefore only of interest if the central memory RAM comprises central independent memory banks organized according to the description given later with reference to FIG. 20: several transactions may in this case, if they affect different memory banks, take place simultaneously.

[0162] FIG. 10 presents a block diagram of an embodiment of the architecture according to the invention, in which the problem of shared data is treated in a dynamic fashion. To this end, the system conforming to this embodiment comprises an snooper processor with a bus PE<sub>i</sub>, coupled to a management processor with a parallel link PGP<sub>i</sub>. A management processor with a series link PGS; is connected to a snooper processor PE<sub>i</sub> by a waiting line FIFO<sub>i</sub>. A management processor for requests from the central unit PGU; is connected, first to the treatment processor CPU;, and to the parallel link management processors PGP<sub>i</sub> and the series link manager PGS<sub>i</sub>. The logic corresponding to the management processor PG; of each cache memory is in this embodiment split into various processors presented hereabove. The access to the cache memory MC<sub>j</sub> and to its directory RG<sub>j</sub> is controlled by a management processor with a directory and a cache PGR<sub>i</sub>.

[0163] Finally, a management processor PGM of the central memory RAM is connected to the bus BUSA and to the central memory RAM, and to its shift registers RDM<sub>i</sub>.

[0164] The functioning of the assembly is as follows:

[0165] Each transaction on the common bus BUSA corresponds to a reading or writing request of the block b<sub>i</sub>. The snooper processors of the bus PEi are activated by each reading request of the block of data. This operation provided in the same cycle through all of the snooper processors is going to permit protecting the uniqueness of the value of the shared data. The snooper processor PE<sub>i</sub> arranges an access to the directory RG<sub>i</sub>. The function of the application used for the management of the cache memory MCi is in the described embodiment of the direct application type. Each element of the directory is a descriptor of the block which contains a "tag" field (address of the block), conventional status bits of the block: a validation bit v and a modification bit m and two supplementary bits a for noting that the block is known by the cache memory but still in the course of transfer on the series link, f for indicating that the block is in the waiting line FIFO and thus avoiding its being placed several times.

[0166] The management processor memory PGM arranges a waiting line AFIFO of addresses of blocks bi and of addresses of processors, accessible in an associative manner, and a status directory of blocks constituted by 2 bits per block ro and rw indicating the possible states of the following block:

[0167] ro=rw=0: block not yet broadcast,

[0168] ro=1; rw=0: block already broadcast in reading: one or several copies of this block being found in the cache memories.

[0169] The evolution of block status bits is the following, different according to the nature of the request of the treatment processor CPU<sub>i</sub>:

[0170] If the processor CPU<sub>j</sub> makes a request for reading non-shared data (program space or explicitly non-shared data): the block is marked already broadcast in reading (ro=1; rw=0) central memory part at the time of transfer of said block from the central memory RAM to the register RDM<sub>j</sub> and marked non-modified (m=0), cache memory part in the same cycle of operation of the directory RG<sub>j</sub> of the cache memory (valid block). The snoopers have not reacted

to the request on the common bus (the request having been made with the indication "shared" or "non-shared").

[0171] If the processor  $CPU_j$  makes a request for reading data (a priori shared), the common bus BUSA is occupied for the time of passage of the information of addresses and of the type requested, the time of their treatment by the processor PGM and the snoopers of the common bus  $PE_j$ . In the central memory RAM, this block may be:

[0172] 1. Not yet broadcast: ro=rw=0. It is then transmitted to the central unit  $UC_j$  and takes the non-modified state.

[0173] 2. Already broadcast in reading: ro=1; rw=0. It is then transmitted to the central unit UC<sub>j</sub>. Its state does not change.

[0174] 3. Already broadcast in writing: ro=0; rw=1. The open copy of this block is found in a cache memory MCi. The snooper processor associated with this cache memory has noted the request of the central unit UC<sub>i</sub> at the time of passage of the address on the common bus and has attempted its transfer to the central memory RAM as soon as possible on the series link LS<sub>i</sub>. While waiting its effective transfer, the memory management processor PGM places the request while waiting in the associative waiting line which comprises a number of elements equal to the number of processors.

[0175] At the time of the reading request on the common bus BUSA, all the snooper processors  $PE_i$  have reacted by consulting the directory  $RG_i$  associated with their cache memory  $MC_i$ . The common bus BUSA is only freed when all the snooper processors  $PE_i$  have had their access to the management directory  $RG_i$ , which assures the same state of the block in the entire system. The processor which has the current copy in its cache memory carries out, as soon as its series link is free, the transfer of this block into the register  $RDM_i$  and makes a writing request for the block on the common bus which will have the effect to free the request while waiting in the associative file AFIFO and carrying out the operation of the status bits of the block.

[0176] The operation of the block only needs a writing to the central memory RAM without activation of the snooper.

[0177] If the processor CPU; requests the writing of a datum in a block present in its cache memory MC<sub>i</sub> with a non-modified state, an informative writing request must be emitted on the common bus BUSA as it is possible that other cache memories MC<sub>i</sub> have this block with the same status. These other memories must be informed of the change of state. To this end, all the snooper processors PE<sub>i</sub> (activated by the informative writing broadcast on the common bus BUSA) consult their management directory and invalidate this block, while the central memory notes in the same time the change of state of this block as well as the parallel management processor PGP<sub>i</sub>, in the management directory RG<sub>i</sub>. The liberation of the common bus BUSA by all the snooper processors and the central memory RAM permits the processor CPU; to provide the writing in its cache memory MC<sub>i</sub>, the broadcasting of the status bit of the management directory RG; having been carried out.

[0178] If one central unit is awaiting access to the bus BUSA for the same request on the same block, its request is

transformed in simple writing and then follows the protocol of the request of the block in writing.

[0179] If the processor  $CPU_j$  requests writing of a datum in a block absent from the cache memory  $MC_j$ , this block is read into the central memory RAM and brought into the cache memory  $MC_j$  in order that the writing will be carried out effectively.

[0180] In the central memory RAM, this block may be:

[0181] 1. Not yet broadcast: ro=rw=0. The block is then emitted on the series connection LS<sub>i</sub> to the cache memory MC<sub>j</sub>. It takes the states ro=0; rw=1 in the central memory and the modified state (m=1) in the cache memory,

[0182] 2. Already broadcast in writing: ro=1; rw=0. The block is sent on the series connection LS<sub>j</sub> to the cache memory Mc<sub>j</sub>. It takes the states ro=0, rw=1 in the central memory, and the modified state (m=1) in the cache memory. At the time of a request on the common bus BUSA, the (espion) processors PE<sub>i</sub> have noted the request and invalidated this number in the block in their cache memory MC<sub>i</sub>.

[0183] 3. Already broadcast in writing: ro=0; rw=1. The request is placed in the associative waiting line AFIFO and the common bus BUSA is liberated.

[0184] The snooper processor  $PE_i$  of the cache memory  $MC_i$ , winner of the current copy, activates as soon as possible the transfer of the block requested from its cache memory  $MC_i$  to the central memory RAM. This block is then invalidated in the cache memory  $MC_i$ .

[0185] The central unit  $UC_j$  makes a writing request to publish the block in the two following cases:

[0186] a) the cache memory is saturated and the purging of a block requires sending this block into the central memory,

[0187] b) a central unit UC<sub>i</sub> is awaiting a block the only current copy of which is found in the cache memory MC<sub>j</sub>. The snooper processor notes the request and provides as soon as possible the purging of this block.

[0188] The central memory side RAM, each request for a writing operation entails a consultation with the associative waiting line AFIFO, and in the case of discovery of a central unit UC<sub>i</sub> awaiting this block, the loading of this block into the shift register RDM<sub>i</sub> and the publishing of the status bits corresponding to this block. This type of writing request does not drive the (espion) processors.

[0189] The directory management processor PGR<sub>j</sub> which is added in this embodiment, permits the execution of the algorithm mentioned above, while coordinating the accesses to the directory of the cache memory MC<sub>j</sub> which receives the requests of three asynchronous functional units:

[0190] 1. The treatment processor CPU<sub>j</sub>, in order to read the instructions of the program during execution and to read or write the data manipulated by this program,

[0191] 2. The common bus BUSA, in order to maintain the coherence of the data in the cache memory MC<sub>i</sub>,

[0192] 3. The series link LS<sub>i</sub>, in order to load/un-load a block of information from/to the central memory RAM. [0193] Each of these requests arrives at the management directory  $RG_j$  of the cache memory. The serialization of these accesses on said management directory permits assuring the good operation of the algorithm mentioned above with coherence of information in the cache memories. Thus there is obtained a strong coupling of the requests at the level of the management directory  $RG_j$  but the synchronization which must exist at the level of the treatment of these requests is sufficiently low to consider an asynchronous functioning of the treatment logic for these requests, which leads to the following functional segmentation:

[0194] The interface of each processor CPU<sub>j</sub> and of its auxiliaries (PGS<sub>j</sub>, PGU<sub>j</sub>) with the common bus BUSA is composed of two parts having a mutually exclusive functioning: the management processor for the parallel link PGP<sub>j</sub> is loaded to request of the common bus BUSA to the request of the request management processor PGU<sub>j</sub> or of the management series link PGS<sub>j</sub> and to control the common bus BUSA in writing. The snooper processor of the bus PE<sub>j</sub> assures the snooping function, which returns to control the common bus BUSA in reading. It frequently reaches the directory RG<sub>j</sub> of the cache memory MC<sub>j</sub>.

[0195] The management processor of the series link  $PGS_j$  manages the interface with the series link  $LS_j$ . It assures the loading and unloading of blocks of information bi upon request of the request management processor  $PGU_j$  and of the snooper processor of bus  $PE_j$ . It reaches less frequently the cache memory  $MC_j$  and the corresponding management directory  $RG_i$ .

[0196] The request management processor  $PGU_j$  assures the following of the requests issued from the processor  $CPU_j$ . It reaches very frequently into the cache memory  $MC_j$  and the management directory  $RG_j$ . This interface includes possible "MMU" logic (memory management unit) usually associated with the treatment processor  $CPU_j$ .

[0197] The management processor  $PGR_j$  of the management directory  $RG_j$  is the arbitrator charged with granting access to the cache memory  $MC_j$ .

[0198] FIGS. 11, 12, 13, 14, 15, 16 and 17 show by way of examples the embodiments of the various functional units of the system of FIG. 10. The designations of signals or inputs and outputs of these units are chosen in a conventional manner. The signals of the same functionality which are generated in each functional unit from a base signal will be designated by the same reference, for example: dnp=nonshared data, dl=reading request, ma<sub>i</sub>=updating, de=demand writing, ei=informative writing. The system has several processors and the indicia 'i' used heretofore refers to a current processor and its auxiliaries; for alleviating the description, this indicia has been omitted in these figures and it will be understood that the description which follows is directed at each of the functional units which are connected with each treatment processor. Further, the signals denoted x YZ define the name and the origin of the signal in the case where YZ=RG, MC, UC, and the source and the destination of the signal in the other cases, with Y and Z representing: U=PGU, R=PGR, P=PGP or PE, S=PGS.

[0199] The cache memory MC shown in FIG. 11 has, for example, a capacity of 16K. It is organized in 16 modules of high speed read write memory of 1k MC0, ... MC $_{15}$ , each accessible on a front of 4 octets: the address bus of the cache

memory MC (noted adr\_MC) comprises a partial block address adr\_block and a partial word address in the block adr\_mot. The address bus adr\_MC comprises 14 lines, permitting addressing the 16k of the cache memory MC. The partial adr\_bloc comprises 8 lines permitting addressing the 256 block sites in the cache memory, and the adr\_mot part 6 lines permitting addressing a word in the block the size of which is, in the example, 64 octets.

[0200] The address part adr\_bloc is connected to the adress input of each of the memory modules  $MC_0 \dots MC_{15}$ . The word address part adr\_mot is connected to the input of two decoders DECO and DEC1 (only the 4 significant bits of the address bus adr mot are used: the address is an octet address and the cache has an access unit which is a word of 4 octets). The read signal r\_MC is delivered to each of the read inputs of the memory modules MC<sub>0</sub> . . . MC<sub>15</sub> and to one of the inputs of a logic gate OU1. The other input of this logic gate OU1 receives the inverted signal bloc. The writing signal w MC is delivered to one of the two inputs of the logic gates OU2 and OU3. The logic gate OU2 receives on its other input the inverted signal bloc. The logic gate OU3 receives on its other input the signal bloc. The output of the logic gate OU1 is connected to the validation input en1 of the decoder DEC1, and the output of digit position i of this decoder DEC1 activates a validation buffer BVL of digit position i. The output of the logic gate OU2 is connected to the validation input en0 of the decoder DECO and to the validation buffers BVE. The output of the logic gate OU3 is connected to the logic gates  $ET1_0 \dots ET1_{15}$ , which receive on their other input the output of the corresponding logic position of the decoder DEC0. The output i of each logic gate  $ET1_0$  . . .  $ET1_{15}$  is connected to the writing inpout  $\bar{\boldsymbol{w}}_{_{0}}\ldots\bar{\boldsymbol{w}}_{_{15}}$  of each memory module  $MC_{_{0}}\ldots MC_{_{15}}.$  A data bus connects each memory module  $MC_0 \dots MC_{15}$  to one of the validation buffers BVL and to one of the validation buffers BVE. The output of the buffers RVL and the input of the buffers RVE receive in parallel a data bus datamot\_MC (connected to the request management processor PGU).

[0201] The operation of the example of the cache memory described above is as follows:

[**0202**] Case 1

[0203] The request comes from the management processor of the series link PGS. This case is signalled by the presence of a logic state zero on the signal bloc.