(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5475845号

(P5475845)

(45) 発行日 平成26年4月16日(2014.4.16)

(24) 登録日 平成26年2月14日(2014.2.14)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

請求項の数 3 (全 23 頁)

(21) 出願番号 特願2012-163872 (P2012-163872)

(22) 出願日 平成24年7月24日 (2012.7.24)

(62) 分割の表示 特願2007-166207 (P2007-166207)

分割

原出願日 平成19年6月25日 (2007.6.25)

(65) 公開番号 特開2012-196554 (P2012-196554A)

(43) 公開日 平成24年10月18日 (2012.10.18)

審査請求日 平成24年8月23日 (2012.8.23)

(73) 特許権者 000148922

株式会社大一商会

愛知県北名古屋市沖村西ノ川1番地

(74) 代理人 110001151

あいわ特許業務法人

(72) 発明者 市原 高明

愛知県北名古屋市沖村西ノ川1番地 株式

会社大一商会内

(72) 発明者 川上 洋二

愛知県北名古屋市沖村西ノ川1番地 株式

会社大一商会内

(72) 発明者 田中 一成

愛知県北名古屋市沖村西ノ川1番地 株式

会社大一商会内

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

画像表示装置の表示画面に動画像を表示させる映像信号を出力する遊技機用制御装置を有し、始動入賞口に球を入賞させると電気的抽選が行われ、前記画像表示装置に抽選された結果が演出表示される遊技機において、

前記遊技機用制御装置は、

前記映像信号に用いられるデジタル画像データを圧縮した圧縮画像データを記録したフラッシュメモリデバイスと、

前記フラッシュメモリデバイスに記録された圧縮画像データを指定する画像指定部と、

前記画像指定部によって指定された圧縮画像データを前記フラッシュメモリデバイスから読み出すリード処理を実行する画像リード部と、

前記画像リード部によって前記フラッシュメモリデバイスから読み出された圧縮画像データを、一時的に記憶するバッファメモリと、

前記バッファメモリに記憶されている圧縮画像データを、前記デジタル画像データへと伸張する画像伸張部と、

前記バッファメモリの記憶容量以内のデータ量であって、前記フラッシュメモリデバイスに対して読み出しアクセス可能なデータ単位を整数倍したデータ量が、前記画像リード部によって前記フラッシュメモリデバイスから読み出される毎に、前記リード処理の進行を一時的に停止するリード停止部と、

前記バッファメモリに記憶されている圧縮画像データの全てが前記画像伸張部に受け渡

10

20

された場合、前記リード停止部によって停止されたリード処理の進行を再開するリード再開部と

を含む遊技機。

**【請求項 2】**

前記遊技機用制御装置は、更に、

前記バッファメモリおよび前記画像伸張部を構成する複数の伸張ラインと、

前記画像リード部によって前記フラッシュメモリデバイスから読み出された圧縮画像データを、前記複数の伸張ラインにおける前記バッファメモリの各々に分配するデータ分配部と、

前記複数の伸張ラインにおける前記画像伸張部の各々によって伸張されたデータから前記デジタル画像データを合成するデータ合成部と

を含む請求項 1 に記載の遊技機。

**【請求項 3】**

前記画像リード部は、パラレル転送でデータをやり取りするパラレルインターフェースを含み、

前記フラッシュメモリデバイスは、

前記圧縮画像データが記録され、シリアル転送でデータをやり取りする NAND 型フラッシュメモリと、

前記 NAND 型フラッシュメモリと前記パラレルインターフェースとの間のデータ転送を中継する中継部と

を含む請求項 1 または 2 の何れか 1 つに記載の遊技機。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、動画像を表示する表示画面を備える遊技機に関する。

**【背景技術】**

**【0002】**

パチンコ機やスロットマシンなどの遊技機には、液晶ディスプレイなどの画像表示装置に動画像を表示させることによって遊技の興奮を高めたものが知られている。動画像表示の一つである描画表示は、内蔵ストレージに予め記録したキャラクタデータを用いて複数の静止画像を生成し、これら複数の静止画像を連続的に表示することによって動画像表示を実現する。また、動画像表示の一つである再生表示は、内蔵ストレージに予め記録したムービーデータから複数のフレームを再生し、これら複数のフレームを連続的に表示することによって動画像表示を実現する。

**【0003】**

動画像表示の趣向を凝らすに連れて、動画像の元となるキャラクタデータやムービーデータ等のデジタル画像データのデータ量は増大する。従来、内蔵ストレージのデータ記憶領域を節約するために、デジタル動画データを圧縮して内蔵ストレージに記憶した遊技機が提案されていた。下記特許文献 1 には、デジタル画像データを圧縮して内蔵ストレージに記憶した遊技機が開示されている。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献 1】特開 2004 - 8483 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

しかしながら、従来、遊技の進行状態と動画像表示の表示内容との間にズレが生じてしまうことを避けつつ、大容量化した圧縮データを非圧縮データへと伸張して動画像表示を行うことについて十分な考慮がなされていなかった。例えば、圧縮データを記録した内臓

10

20

30

40

50

ストレージから一度に読み出し可能なデータ量と、圧縮データを伸張する回路で一度に受け入れ可能なデータ量とが異なる場合、遊技の進行状態と動画像表示の表示内容との間にズレが生じないようにデータ転送を処理する必要性があった。

#### 【0006】

本発明は、上記した課題を踏まえ、圧縮データを用いた動画像表示における処理効率を向上させることができる遊技機を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

10

#### 【0008】

[適用例1] 適用例1の遊技機用制御装置は、遊技機の表示画面に動画像を表示させる映像信号を出力する遊技機用制御装置であって、前記映像信号に用いられるデジタル画像データを圧縮した圧縮画像データを記録したメモリデバイスと、前記メモリデバイスに記録された圧縮画像データを指定する画像指定部と、前記画像指定部によって指定された圧縮画像データを前記メモリデバイスから読み出すリード処理を実行する画像リード部と、前記画像リード部によって前記メモリデバイスから読み出された圧縮画像データを、一時的に記憶するバッファメモリと、前記バッファメモリに記憶されている圧縮画像データを、前記デジタル画像データへと伸張する画像伸張部と、前記バッファメモリの記憶容量に応じたデータ量が前記画像リード部によって前記メモリデバイスから読み出される毎に、前記リード処理の進行を一時的に停止するリード停止部と、前記バッファメモリに記憶されている圧縮画像データの全てが前記画像伸張部に受け渡された場合、前記リード停止部によって停止されたリード処理の進行を再開するリード再開部とを備えることを特徴とする。適用例1の遊技機用制御装置によれば、メモリデバイスからのデジタル画像データの読み出しが、バッファメモリの記憶容量に応じて分割して実行されるため、バッファメモリの記憶容量よりも大きなデジタル画像データを伸張して動画像表示に用いることができる。

20

#### 【0009】

また、遊技機では、始動入賞口に球を入れると電気的抽選が行われ、その画像表示装置では、抽選された結果が数十秒かけて遊技者に演出表示される。近年では、大画面や高解像表示の画像表示に慣れた遊技者を満足させるために、遊技機においても大画面化や高解像度化、画像の複雑化などの手法が採られる。その観点からすると、適用例1の遊技機用制御装置によれば、大容量のデジタル画像データを伸張して動画像表示に用いることによって、遊技進行に同期させた動画像表示の興奮を向上させることができる。また、近年では、動画像表示や電飾による演出によって遊技機の消費電力は増加する一方である。そのため、一時に、複数の遊技機において抽選に当選した場合には、これらの遊技機が設置されたホールの電力容量を超えてしまい、遊技機に供給される電力が瞬停してしまう虞もあった。この問題に対しても、適用例1の遊技機用制御装置によれば、電飾による演出に頼ることなく、大容量のデジタル画像データを伸張した動画像表示によって、遊技進行に同期させた動画像表示の興奮を向上させることができる。

30

#### 【0010】

[適用例2] 適用例1の遊技機用制御装置であって、前記リード停止部は、前記バッファメモリの記憶容量以内のデータ量であって、前記メモリデバイスに対して読み出しあクセス可能なデータ単位を整数倍したデータ量が、前記画像リード部によって前記メモリデバイスから読み出される毎に、前記リード処理の進行を一時的に停止するとしても良い。適用例2の遊技機用制御装置によれば、メモリデバイスからのデジタル画像データの読み出しが、メモリデバイスに対して読み出しあクセス可能なデータ単位で、バッファメモリの記憶容量に応じて分割して実行されるため、デジタル画像データの読み出しから伸張までの処理効率を向上させることができる。

40

#### 【0011】

50

【適用例 3】 適用例 1 または 2 の遊技機用制御装置であって、更に、前記バッファメモリおよび前記画像伸張部を構成する複数の伸張ラインと、前記画像リード部によって前記メモリデバイスから読み出された圧縮画像データを、前記複数の伸張ラインにおける前記バッファメモリの各々に分配するデータ分配部と、前記複数の伸張ラインにおける前記画像伸張部の各々によって伸張されたデータから前記デジタル画像データを合成するデータ合成部とを備えるとしても良い。適用例 3 の遊技機用制御装置によれば、デジタル画像データの非圧縮データへの伸張を、複数の伸張ラインに分散させることができため、デジタル画像データの伸張処理の速度を向上させることができる。

#### 【0012】

【適用例 4】 適用例 1 ないし 3 のいずれかの遊技機用制御装置であって、前記画像リード部は、パラレル転送でデータをやり取りするパラレルインターフェースを含み、前記メモリデバイスは、前記圧縮画像データが記録され、シリアル転送でデータをやり取りする N A N D 型フラッシュメモリと、前記 N A N D 型フラッシュメモリと前記パラレルインターフェースとの間のデータ転送を中継する中継部とを含むとしても良い。適用例 4 の遊技機用制御装置によれば、大容量化したデジタル画像データに対応可能な記憶領域を、N A N D 型フラッシュメモリによって確保することができる。

#### 【0013】

なお、本発明の態様は、遊技機用制御装置に限るものではなく、遊技機用制御装置を備える遊技機や、遊技機において圧縮データを非圧縮データに伸張する方法、遊技機用制御装置を制御するためのコンピュータプログラムなどの種々の態様に適用することができる。なお、本発明が適用される遊技機は、パチンコ機およびスロットマシンを含む。

#### 【図面の簡単な説明】

#### 【0014】

【図 1】パチンコ機 10 の全体構成を示す正面図である。

【図 2】パチンコ機 10 の電気的な概略構成を示すブロック図である。

【図 3】パチンコ機 10 における表示制御部 60 の電気的構成を主に示すブロック図である。

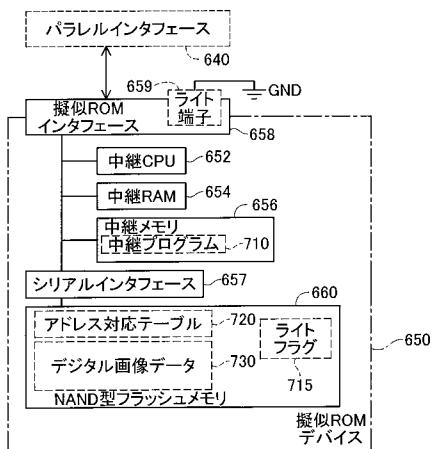

【図 4】表示制御部 60 における擬似 ROM デバイス 650 の詳細構成を主に示すブロック図である。

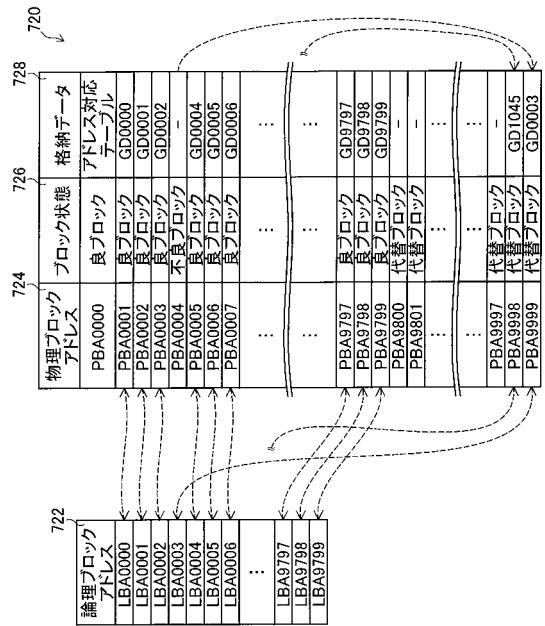

【図 5】中継メモリ 656 に記憶されたアドレス対応テーブル 720 の一例を示す説明図である。

【図 6】表示制御部 60 の伸張コントローラ 672 によって実行される伸張制御処理を示すフローチャートである。

【図 7】擬似 ROM デバイス 650 の中継 C P U 652 によって実行される起動処理を示すフローチャートである。

【図 8】擬似 ROM デバイス 650 の中継 C P U 652 によって実行されるリード中継処理を示すフローチャートである。

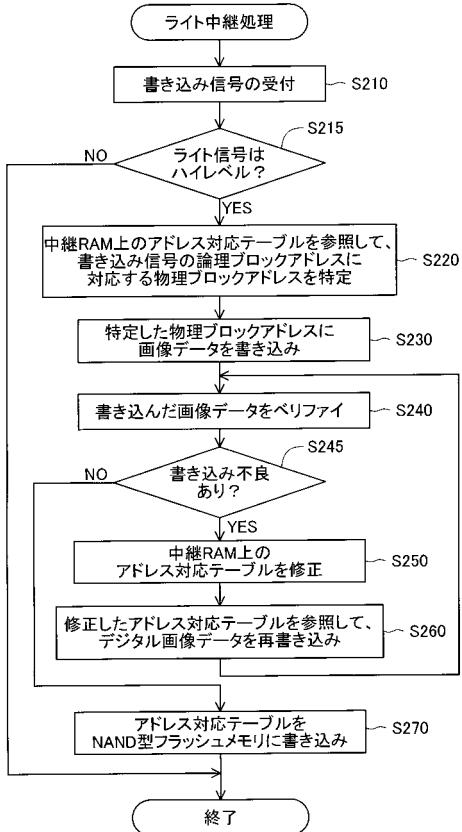

【図 9】擬似 ROM デバイス 650 の中継 C P U 652 によって実行されるライト中継処理を示すフローチャートである。

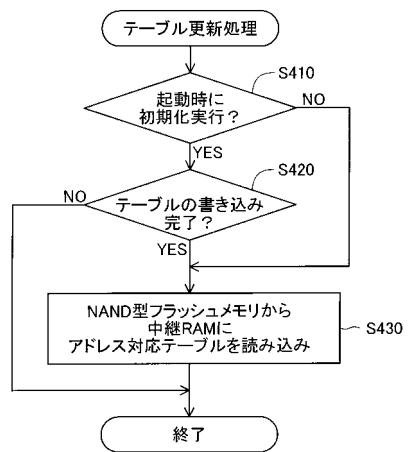

【図 10】擬似 ROM デバイス 650 の中継 C P U 652 によって実行されるテーブル更新処理を示すフローチャートである。

【図 11】第 2 の実施例のパチンコ機 10 における擬似 ROM デバイス 650 の詳細構成を主に示すブロック図である。

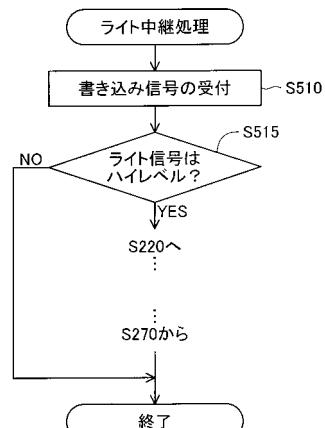

【図 12】第 2 の実施例において擬似 ROM デバイス 650 の中継 C P U 652 によって実行されるライト中継処理を示すフローチャートである。

【図 13】他の実施形態における中継メモリ 656 に記憶されたアドレス対応テーブル 720 の一例を示す説明図である。

#### 【発明を実施するための最良の形態】

#### 【0015】

以上説明した本発明の構成および作用を一層明らかにするために、以下本発明を適用し

10

20

30

40

50

たパチンコ機について説明する。

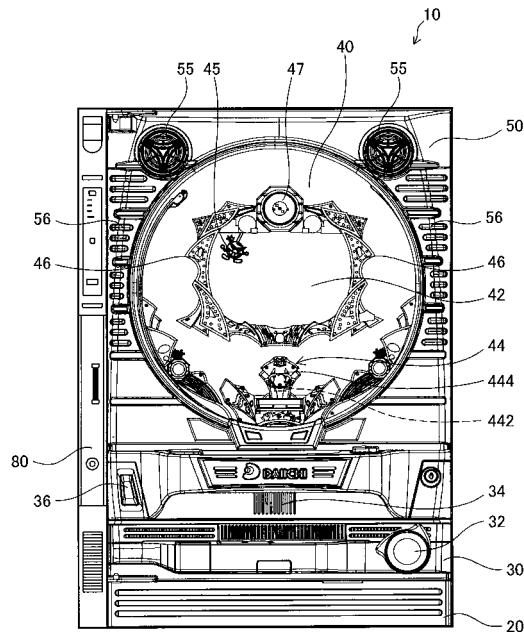

**【0016】**

A. 第1の実施例：

A - 1. パチンコ機10の全体構成：

本発明の実施例の一つであるパチンコ機10の構成について説明する。図1は、パチンコ機10の全体構成を示す正面図である。パチンコ機10は、パチンコ店のいわゆる島設備に固定される外枠20と、外枠20に嵌め込まれる内枠30と、内枠30の中央上寄りに嵌め込まれ遊技球による遊技が行われる遊技パネル40と、遊技パネル40の前面を覆うガラス板を有し内枠30に開閉可能に軸着されるガラス枠50と、プリペイドカードによる遊技球の貸し出しを受け付けるカードユニット80とを備える。

10

**【0017】**

パチンコ機10の遊技パネル40は、遊技球の入賞を受け付ける入賞口44と、遊技の演出として映像の表示を行う液晶ディスプレイ(LCD)42と、遊技の演出として発光する発光ダイオード(LED)462を複数内蔵する電飾部46と、遊技の演出としてキャラクタ人形を動かす演出駆動部45と、遊技者に遊技の演出態様を選定させるために遊技者がかざした手の赤外線を感知する演出センサ47とを備える。入賞口44は、入賞口44に入賞した遊技球を検知する遊技球センサ442と、入賞口44への遊技球の導入経路を拡縮する入賞口駆動部444とを備える。なお、本実施例では、遊技球センサ442は、渦電流方式のセンサを含み、入賞口駆動部444は、ソレノイド(図示しない)を動力源として駆動する機構を含み、演出駆動部45は、ステップモータ(図示しない)を動力源として駆動する機構を含む。

20

**【0018】**

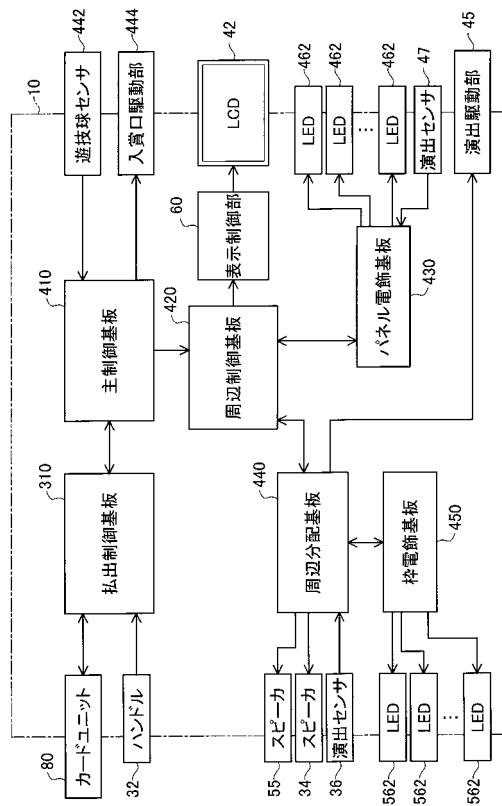

パチンコ機10のガラス枠50は、遊技の演出として高音域の音声を出力するスピーカ55と、遊技の演出として発光する発光ダイオード(LED)562を複数内蔵する電飾部56とを備える。パチンコ機10の内枠30は、遊技パネル40に遊技球を発射するための遊技者による操作を受け付けるハンドル32と、遊技の演出として低音域の音声を出力するスピーカ34と、遊技者に遊技の演出態様を選定させるために遊技者からのボタン入力を検知する演出センサ36とを備える。

**【0019】**

図2は、パチンコ機10の電気的な概略構成を示すブロック図である。パチンコ機10は、遊技球センサ442からの入力に基づいて遊技の進行を制御する主制御基板410と、主制御基板410からの指示である主コマンドに基づいて遊技の進行に応じた各部の演出を制御する周辺制御基板420と、周辺制御基板420からの指示である表示コマンドに基づいてLCD42に表示される動画像の表示態様を制御する表示制御部60と、周辺制御基板420からの指示である階調コマンドに基づいてLED462の輝度階調を制御するパネル電飾基板430と、周辺制御基板420からの各種信号をパチンコ機10の各部に分配する周辺分配基板440と、周辺分配基板440を介した周辺制御基板420からの指示に基づいてLED562の輝度階調を制御する枠電飾基板450と、主制御基板410からの指示である払出コマンドに基づいて遊技球の払い出しを制御する払出制御基板310とを備える。主制御基板410、周辺制御基板420、パネル電飾基板430、周辺分配基板440、表示制御部60、枠電飾基板450、払出制御基板310の各回路基板は、図1に示した内枠30の裏面側(図示しない)に備えられる。

30

**【0020】**

本実施例では、主制御基板410、周辺制御基板420、表示制御部60、払出制御基板310は、種々の演算処理を実行するCPUと、CPUの演算処理を規定したプログラムを予め記憶するリードオンリメモリ(Read Only Memory、以下、「ROM」という)と、CPUが取り扱うデータを一時的に記憶するランダムアクセスメモリ(Random Access Memory、以下、「RAM」という)などの各回路基板の機能に応じた電子部品が実装された電子回路を備える。本実施例では、パネル電飾基板430、周辺分配基板440、枠電飾基板450は、各回路基板の機能に応じた大規模集積回路(Large Scale Integration

40

50

、以下、「LSI」という)などの各回路基板の機能に応じた電子部品が実装された電子回路を備える。

#### 【0021】

主制御基板410から周辺制御基板420に送信される主コマンドは、いわゆる「当たり」や「はずれ」などの遊技に関する基本的な演出を指示する情報を含む。主制御基板410から主コマンドを受信した周辺制御基板420は、主コマンドに基づいてLCD42, LED462, LED562, スピーカ34, スピーカ55, 演出駆動部45などの演出実行部でそれぞれ実施される演出を決定し、各演出実行部に応じた種々の信号を出力する。周辺制御基板420から表示制御部60に対する信号は、LCD42に表示すべき映像の内容を表示制御部60に指示する表示コマンドを含む。周辺制御基板420からパネル電飾基板430に対する信号は、LED462の発光態様を指定した階調コマンドを含む。10

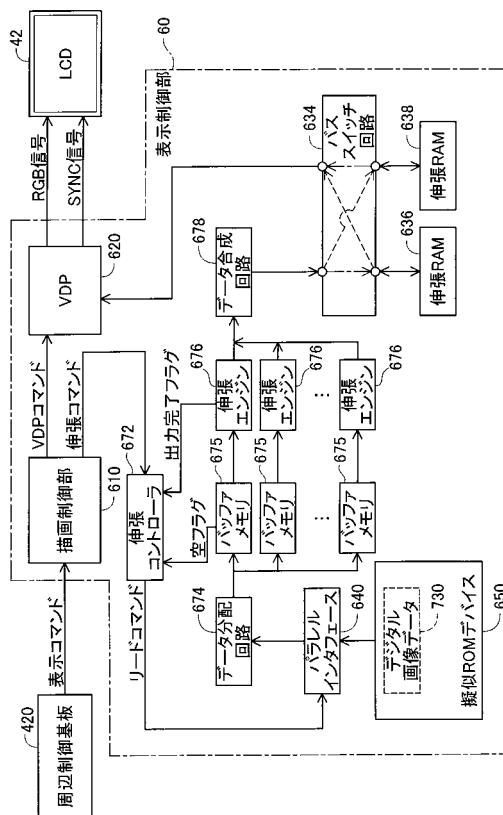

#### 【0022】

A-2. パチンコ機10における表示制御部60の詳細構成：

図3は、パチンコ機10における表示制御部60の電気的構成を主に示すブロック図である。表示制御部60は、遊技機専用に設計された遊技機用制御装置を含み、本実施では、表示制御部60は、周辺制御基板420およびLCD42とは別体の電子回路基板として構成されているが、周辺制御基板420と一体的に構成されても良いし、LCD42と一緒に構成されても良い。

#### 【0023】

表示制御部60は、周辺制御基板420からの表示コマンドに基づいて表示制御部60の各部を制御する描画制御部610と、LCD42における動画像表示に用いられるデジタル画像データ730が記録されたROMとして機能する擬似ROMデバイス650と、擬似ROMデバイス650とのデータのやり取りをパラレル転送方式で行うパラレルインターフェース640と、描画制御部610からのVDPコマンドに基づいて、LCD42を駆動する映像信号を擬似ROMデバイス650のデジタル画像データ730から生成する画像表示プロセッサ(Video Display Processor, VDP)620とを備える。本実施例では、表示制御部60の描画制御部610は、CPU, ROM, RAMなどの電子部品を備えるコンピュータである。本実施例では、表示制御部60のVDP620がLCD42に出力する映像信号は、RGB(Red Green Blue)信号と、SYNC(同期)信号とを含む。20

。本実施例では、擬似ROMデバイス650のデジタル画像データ730は、キャラクタデータやムービーデータ等の動画表示の元となるデータを含み、圧縮された圧縮画像データとして記録されている。表示制御部60の擬似ROMデバイス650についての詳細は後述する。30

#### 【0024】

表示制御部60は、デジタル画像データ730を圧縮画像データから非圧縮データへと伸張(展開, 解凍)するために、伸張コントローラ672と、データ分配回路674と、バッファメモリ675および伸張エンジン676を構成する複数の伸張ラインと、データ合成回路678とを備える。表示制御部60の伸張コントローラ672は、本実施例では、CPU, ROM, RAMを備えるコンピュータである。伸張コントローラ672は、伸張すべきデジタル画像データ730が格納された先頭アドレスとそのデータ量とを示す情報を含む伸張コマンドを、描画制御部610から受け取ると、擬似ROMデバイス650からのデータの読み出しを指示するリードコマンドを、パラレルインターフェース640に送信する。伸張コントローラ672の動作についての詳細は後述する。40

#### 【0025】

パラレルインターフェース640によって擬似ROMデバイス650から読み出されたデジタル画像データ730は、データ分配回路674によって複数のデータに分割され、複数のバッファメモリ675に振り分けられる。本実施例では、バッファメモリ675および伸張エンジン676を構成する伸張ラインは、四系統の回路として用意されており、バッファメモリ675は、それぞれ3キロバイト(KB)の記録容量を有する。これによっ50

て、四系統で合計 12KB の総バッファ容量が構成される。本実施例では、擬似 ROM デバイス 650 のデジタル画像データ 730 は、伸張コントローラ 672 の制御の下で、パラレルインタフェース 640 によって、一つのリードコマンド毎に 12KB 単位で読み出され、読み出されたデジタル画像データ 730 は、データ分配回路 674 によって、先頭データから 3KB ずつに四分割され、四つのバッファメモリ 675 にそれぞれ振り分けられる。

#### 【0026】

表示制御部 60 の伸張エンジン 676 は、デジタル画像データ 730 の圧縮形式に対応した専用のデータ伸張回路である。本実施例では、バッファメモリ 675 に格納されたデータは、FIFO (First In, First Out、先入れ先出し) 方式で伸張エンジン 676 に受け渡され、伸張エンジン 676 によって順次伸張される。本実施例では、バッファメモリ 675 に格納されたデータの全てが伸張エンジン 676 に受け渡されると、その旨が空フラグによってバッファメモリ 675 の各々から伸張コントローラ 672 に通知される。本実施例では、バッファメモリ 675 に格納されたデータの全てが伸張エンジン 676 によって伸張されると、その旨が出力完了フラグによって伸張エンジン 676 の各々から伸張コントローラ 672 に通知される。本実施例では、複数の伸張エンジン 676 によって伸張された複数のデジタル画像データ 730 は、データ合成回路 678 によって一連のデジタル画像データ 730 として合成される。

#### 【0027】

表示制御部 60 は、伸張されたデジタル画像データ 730 を VDP 620 で利用可能に保存しておくために、データ合成回路 678 によって合成されたデジタル画像データ 730 を記憶する二つの伸張 RAM 636, 638 と、伸張 RAM 636, 638 の各々に対してデータ合成回路 678 および VDP 620 とのメモリバス接続を切り替えるバススイッチ回路 634 とを備える。本実施例では、表示制御部 60 のバススイッチ回路 634 は、データ合成回路 678 による伸張 RAM 636, 638 の一方に対するメモリアクセスと、VDP 620 による伸張 RAM 636, 638 の他方に対するメモリアクセスとを同時に実行可能に、描画制御部 610 からの指示に基づいて伸張 RAM 636, 638 の各々に対するメモリバス接続を切り替える。バススイッチ回路 634 によるメモリバス接続の切り替えによって、伸張 RAM 636, 638 におけるアドレス空間の各々は、VDP 620 がメモリアクセスに用いる同じ論理ブロックアドレス空間に共通して対応付けられ、伸張 RAM 636, 638 は、VDP 620 からは単一の RAM として認識される。これによって、データ合成回路 678 によるデジタル画像データ 730 の書き込みと、VDP 620 によるデジタル画像データ 730 の読み出しが同時に実行可能となり、圧縮されたデジタル画像データ 730 を擬似 ROM デバイス 650 から VDP 620 に対して効率良く伸張および伝送することができる。

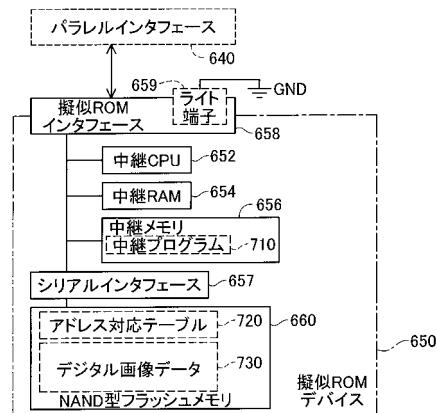

#### 【0028】

A - 3 . 表示制御部 60 における擬似 ROM デバイス 650 の詳細構成 :

図 4 は、表示制御部 60 における擬似 ROM デバイス 650 の詳細構成を主に示すブロック図である。表示制御部 60 の擬似 ROM デバイス 650 は、遊技機専用に設計された遊技機用メモリデバイスであり、デジタル画像データ 730 が記録されシリアル転送でデータをやり取りする NAND 型フラッシュメモリ (NAND type flash memory) 660 と、NAND 型フラッシュメモリ 660 とのデータのやり取りをシリアル転送方式で行うシリアルインタフェース 657 と、擬似 ROM デバイス 650 の各部を制御する中継 CPU 652 と、中継 CPU 652 の動作が規定された中継プログラム 710 を予め記憶する中継メモリ 656 と、中継 CPU 652 が取り扱うデータを一時的に記憶する中継 RAM 654 と、ROM デバイスとしてパラレルインタフェース 640 とのデータのやり取りを行なう擬似 ROM インタフェース 658 とを備える。本実施例では、擬似 ROM デバイス 650 は、NAND 型フラッシュメモリ 660 と共に、中継 CPU 652, 中継 RAM 654, 中継メモリ 656, 擬似 ROM インタフェース 658, シリアルインタフェース 657 を、単一のパッケージとして、電気的絶縁性を有する樹脂で封止した電子部品である。擬似

10

20

30

40

50

R O M デバイス 6 5 0 の中継 C P U 6 5 2 の動作の詳細については後述する。

**【 0 0 2 9 】**

擬似 R O M デバイス 6 5 0 の擬似 R O M インタフェース 6 5 8 は、表示制御部 6 0 へと電気的に接続される種々の端子の一つとして、N A N D 型フラッシュメモリ 6 6 0 に対するデータ書き込みの可否を示すライト信号の入力を受け付けるライト端子 6 5 9 を備える。本実施例では、表示制御部 6 0 に実装された擬似 R O M デバイス 6 5 0 において、擬似 R O M インタフェース 6 5 8 のライト端子 6 5 9 は、グランドに接続されることによって、ライト端子 6 5 9 に入力されるライト信号は、二値信号の「ローレベル（0）」に常時維持される。

**【 0 0 3 0 】**

擬似 R O M デバイス 6 5 0 のN A N D 型フラッシュメモリ 6 6 0 は、一連の物理ブロックアドレスが物理的なメモリ配列順にそれぞれ割り当てられた複数の物理データブロックを有する。本実施例では、N A N D 型フラッシュメモリ 6 6 0 には、物理データブロックあたり 6 4 ページの記憶領域が構成され、一ページあたり 2 0 4 8 バイト（すなわち 2 K B）のユーザデータ領域と 6 4 バイトの冗長領域とが構成されている。本実施例では、N A N D 型フラッシュメモリ 6 6 0 は、一ページ単位（すなわち 2 K B 単位）で、データの読み出しあり書き込みを受け付けるように設計されている。N A N D 型フラッシュメモリ 6 6 0 の物理データブロックには、物理的にデータの記録が可能な「良ブロック」と、物理的にデータの記録が不可能な「不良ブロック」とが含まれる。デジタル画像データ 7 3 0 は、良ブロックにおけるユーザデータ領域に格納されている。本実施例では、物理ブロックが不良ブロックである場合には、その物理ブロックの冗長領域に、不良ブロックを示すフラグが書き込まれている。本実施例では、擬似 R O M デバイス 6 5 0 のデジタル画像データ 7 3 0 は、表示制御部 6 0 への実装に先立って、擬似 R O M デバイス 6 5 0 の擬似 R O M インタフェース 6 5 8 とデータのやり取りを行う擬似 R O M ライタ（図示しない）によって記録される。

**【 0 0 3 1 】**

擬似 R O M デバイス 6 5 0 のN A N D 型フラッシュメモリ 6 6 0 には、擬似 R O M インタフェース 6 5 8 とN A N D 型フラッシュメモリ 6 6 0 との間におけるアドレス対応が規定されたアドレス対応テーブル 7 2 0 が予め記録されている。アドレス対応テーブル 7 2 0 は、N A N D 型フラッシュメモリ 6 6 0 におけるデジタル画像データ 7 3 0 の格納状態に応じて、擬似 R O M デバイス 6 5 0 に搭載された個々のN A N D 型フラッシュメモリ 6 6 0 毎に予め用意されたデータである。本実施例では、アドレス対応テーブル 7 2 0 は、デジタル画像データ 7 3 0 が記録された良ブロックよりも先行する物理ブロックアドレスが割り当てられた良ブロックにおけるユーザデータ領域に格納されている。

**【 0 0 3 2 】**

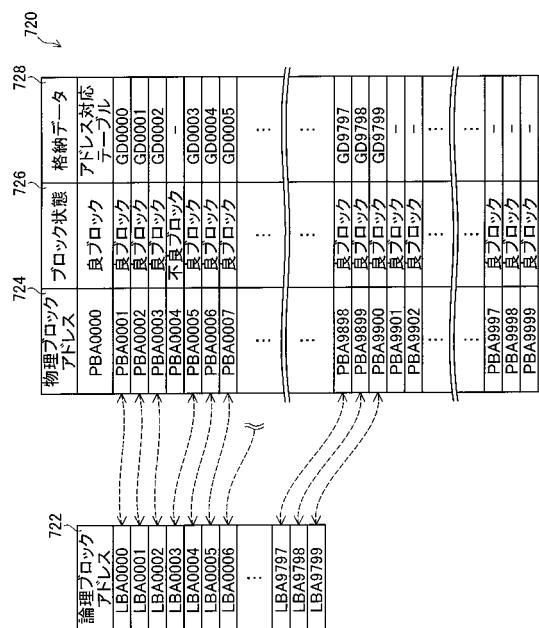

図 5 は、中継メモリ 6 5 6 に記憶されたアドレス対応テーブル 7 2 0 の一例を示す説明図である。アドレス対応テーブル 7 2 0 には、パラレルインタフェース 6 4 0 がデータのやり取りに用いる一連の論理ブロックアドレス 7 2 2 と、N A N D 型フラッシュメモリ 6 6 0 における一連の物理ブロックアドレス 7 2 4 と、各物理ブロックアドレスが良ブロックか不良ブロックであるかを示すブロック状態 7 2 6 と、各物理ブロックアドレスに記録されている格納データ 7 2 8 とが示され、一連の論理ブロックアドレス 7 2 2 は、デジタル画像データ 7 3 0 が記録された良ブロックの物理ブロックアドレスに対応付けられている。

**【 0 0 3 3 】**

本実施例では、N A N D 型フラッシュメモリ 6 6 0 は、一万個の物理データブロックを有し、これらの物理データブロックには、「P B A 0 0 0 0 」から「P B A 9 9 9 9 」までの一万個の物理ブロックアドレスが、N A N D 型フラッシュメモリ 6 6 0 における物理的なメモリ配列順にそれぞれ割り当てられている。本実施例では、N A N D 型フラッシュメモリ 6 6 0 には、9 8 0 0 個分の物理データブロックのデータ量に相当する「G D 0 0 0 0 」から「G D 9 7 9 9 」までの符号で示すデジタル画像データ 7 3 0 が記録されてい

10

20

30

40

50

る。本実施例では、NAND型フラッシュメモリ660に記録されたデジタル画像データ730のデータ量に合わせて、「LBA0000」から「LBA9799」までの9800個の論理ブロックアドレスが用意されている。

#### 【0034】

本実施例では、デジタル画像データ730は、アドレス対応テーブル720に続いて、一連の物理ブロックアドレスの順に従ってNAND型フラッシュメモリ660に順次記録され、記録対象となった物理データブロックが不良ブロックである場合、その不良ブロック以降に記録すべきデータは、その不良ブロックに後続する良ブロック以降に順次記録されている。図5に示す例では、最初の良ブロックである物理ブロックアドレスPBA0000の物理データブロックには、アドレス対応テーブル720が記録されている。図5に示す例では、アドレス対応テーブル720が記録された良ブロックに後続する良ブロックである物理ブロックアドレスPBA0001～PBA0003の物理データブロックには、デジタル画像データGDO000～GDO002が順次記録され、不良ブロックである物理ブロックアドレスPBA0004の物理データブロックを飛ばして、後続の良ブロックである物理ブロックアドレスPBA0005の物理データブロックにデジタル画像データ「GDO003」が記録され、後続のデジタル画像データは、同様に順次記録されている。10

#### 【0035】

本実施例では、一連の論理ブロックアドレス722は、デジタル画像データ730が記録された良ブロックの物理ブロックアドレスを昇順に並べた一連の物理ブロックアドレスに順次対応付けられている。図5に示す例では、論理ブロックアドレスLBA0000は、物理ブロックアドレスPBA0001に対応付けられ、論理ブロックアドレスLBA0001は、物理ブロックアドレスPBA0002に対応付けられ、論理ブロックアドレスLBA0002は、物理ブロックアドレスPBA0003に対応付けられ、論理ブロックアドレスLBA0003は、不良ブロックである物理ブロックアドレスPBA0004を飛ばして、物理ブロックアドレスPBA0005に対応付けられ、後続の論理ブロックアドレスは、同様に物理ブロックアドレスに順次対応付けられている。20

#### 【0036】

A-4. 第1の実施例におけるパチンコ機10の動作：

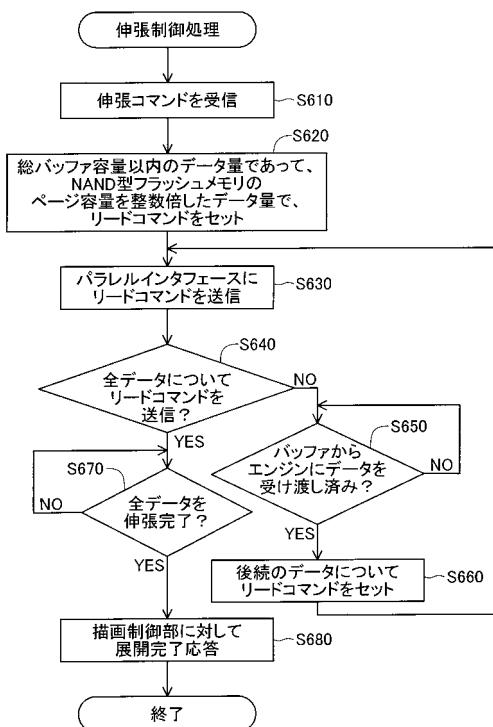

図6は、表示制御部60の伸張コントローラ672によって実行される伸張制御処理を示すフローチャートである。表示制御部60の伸張コントローラ672は、描画制御部610から伸張コマンドが出力されると、図6に示す伸張制御処理を開始する。30

#### 【0037】

伸張コントローラ672は、図6に示す伸張制御処理を開始すると、描画制御部610から伸張コマンドを受信する(ステップS610)。本実施例では、描画制御部610からの伸張コマンドには、論理ブロックアドレス722を用いて擬似ROMデバイス650上の先頭アドレスと、そのデータ量とが指定されており、これによって、擬似ROMデバイス650から読み出して伸張すべきデジタル画像データ730が特定される。

#### 【0038】

伸張コントローラ672は、伸張コマンドを受信した後(ステップS610)、擬似ROMデバイス650からのデジタル画像データ730の読み出しを指示するリードコマンドを準備する(ステップS620)。このリードコマンドで読み出し指示されるデジタル画像データ730のデータ量は、複数のバッファメモリ675の総バッファ容量以内のデータ量であって、擬似ROMデバイス650におけるNAND型フラッシュメモリ660のページ容量を整数倍したデータ量で指定されている。本実施例では、複数のバッファメモリ675によって12KBの総バッファ容量が構成され、NAND型フラッシュメモリ660のページ容量は2KBであることから、ページ容量を六倍した12KBのデジタル画像データ730が、一回のリードコマンドで、読み出し指示される。例えば、伸張コマンドに64KBのデジタル画像データ730が指定された場合、伸張コントローラ672は、その64KBのうちの最初の12KBをリードコマンドで読み出し指示する。4050

**【0039】**

伸張コントローラ672は、リードコマンドを準備した後（ステップS620）、そのリードコマンドをパラレルインタフェース640に送信する（ステップS630）。その後、伸張コントローラ672は、伸張コマンドによって読み出し指定されたデジタル画像データ730の全てについて、パラレルインタフェース640にリードコマンドを送信したか否かを判断する（ステップS640）。

**【0040】**

全データについてリードコマンドを送信していない場合、例えば、伸張コマンドに指定された64KBのデータ量のうち、最初の12KBについてのリードコマンドしか送信していない場合（ステップS640）、伸張コントローラ672は、擬似ROMデバイス650からバッファメモリ675に読み出されたデジタル画像データ730の全てが、伸張エンジン676へと受け渡されたか否かを判断する（ステップS650）。本実施例では、伸張コントローラ672は、バッファメモリ675から空フラグとして出力される値に基づいて、バッファメモリ675の全データが伸張エンジン676へと受け渡されたか否かを判断する。

10

**【0041】**

バッファメモリ675上の全データが伸張エンジン676へと受け渡された場合（ステップS650）、伸張コントローラ672は、リードコマンドで読み出し指示されていない後続のデジタル画像データ730についてリードコマンドを準備する（ステップS660）。例えば、伸張コマンドに指定された64KBのデータ量のうち、最初の12KBについてのリードコマンドしか送信していない場合、伸張コントローラ672は、先行のリードコマンドで指定されたデータに後続する12KBについてのリードコマンドを準備する。伸張コントローラ672は、後続のデータについてのリードコマンドを準備した後（ステップS660）、そのリードコマンドをパラレルインタフェース640に送信する（ステップS630）。その後、伸張コントローラ672は、伸張コマンドによって読み出し指定されたデジタル画像データ730の全てについてリードコマンドを送信するまで、リードコマンドの送信を繰り返す（ステップS640）。これによって、パラレルインタフェース640による擬似ROMデバイス650からのデータ読み出し処理は、停止と再開とを交互に繰り返して進行する。

20

**【0042】**

30

伸張コントローラ672は、伸張コマンドによって読み出し指定されたデジタル画像データ730の全てについてリードコマンドを送信した場合（ステップS640）、その全データが伸張エンジン676によって伸張されたか否かを判断する（ステップS670）。本実施例では、伸張コントローラ672は、伸張エンジン676から出力完了フラグとして出力される値に基づいて、伸張コマンドによって読み出し指定された全データが伸張されたか否かを判断する。伸張コントローラ672は、伸張コマンドによって読み出し指定された全データが伸張された場合（ステップS670）、その旨を描画制御部610に対して応答する（ステップS680）。

**【0043】**

40

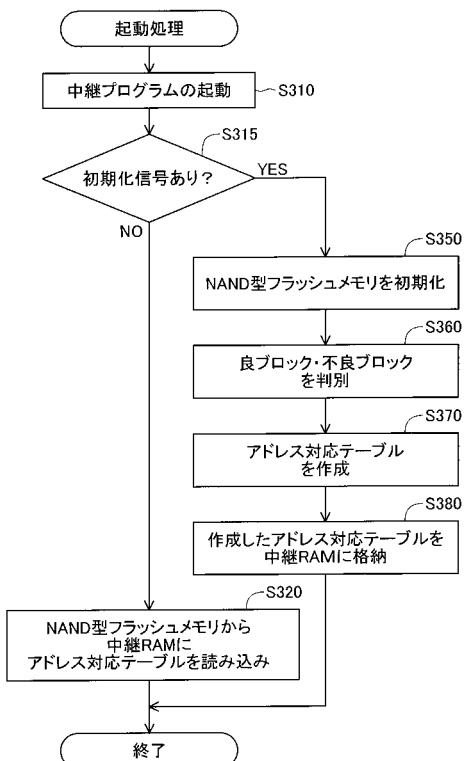

図7は、擬似ROMデバイス650の中継CPU652によって実行される起動処理を示すフローチャートである。擬似ROMデバイス650の中継CPU652は、擬似ROMデバイス650に電源が供給されると、図7に示す起動処理を開始する。

**【0044】**

50

中継CPU652は、図7に示す起動処理を開始すると、中継メモリ656に予め記憶された中継プログラム710を中継メモリ656から中継RAM654に読み込み、読み込んだ中継プログラム710を起動する（ステップS310）。中継プログラム710が起動された後、中継CPU652は、NAND型フラッシュメモリ660の記憶領域を初期化する指示を示す初期化信号が擬似ROMインタフェース658に入力されたか否かを判断する（ステップS315）。本実施例では、初期化信号は、デジタル画像データ730の書き込みを行う擬似ROMライタ（図示しない）から擬似ROMデバイス650に対

して出力される信号であり、擬似 ROM デバイス 650 がパチンコ機 10 の表示制御部 60 に実装された状態にある場合、初期化信号が擬似 ROM デバイス 650 に入力されることはない。

#### 【 0045 】

初期化信号が入力されていない場合（ステップ S315）、例えば、擬似 ROM デバイス 650 が表示制御部 60 に実装された状態にある場合や、擬似 ROM デバイス 650 に接続された擬似 ROM ライタ（図示しない）が初期化信号を出力していない場合、中継 CPU 652 は、NAND 型フラッシュメモリ 660 に記録されているアドレス対応テーブル 720 を NAND 型フラッシュメモリ 660 からシリアルインターフェース 657 を介して中継 RAM 654 に読み込む（ステップ S320）。 10

#### 【 0046 】

一方、初期化信号が入力されている場合（ステップ S315）、例えば、擬似 ROM デバイス 650 に接続された擬似 ROM ライタ（図示しない）が初期化信号を出力する場合、中継 CPU 652 は、NAND 型フラッシュメモリ 660 における記憶領域を初期化する（ステップ S350）。その後、中継 CPU 652 は、NAND 型フラッシュメモリ 660 に含まれる複数の物理データブロックについて良ブロックおよび不良ブロックを判別し（ステップ S360）、アドレス対応テーブル 720 を新規に作成する。その後、中継 CPU 652 は、新規のアドレス対応テーブル 720 を中継 RAM 654 に格納する（ステップ S380）。 20

#### 【 0047 】

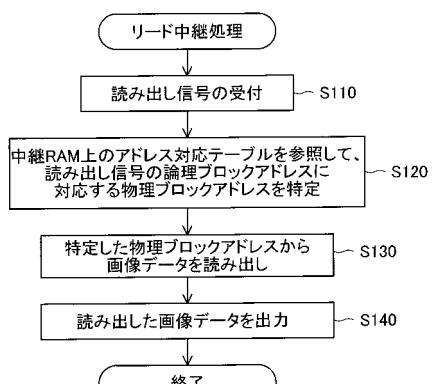

図 8 は、擬似 ROM デバイス 650 の中継 CPU 652 によって実行されるリード中継処理を示すフローチャートである。データの読み出し信号が、擬似 ROM インタフェース 658 に入力されると、中継 CPU 652 は、図 8 に示すリード中継処理を開始する。本実施例では、図 8 のリード中継処理に先立って、パチンコ機 10 の電源投入時に、アドレス対応テーブル 720 は、中継 RAM 654 に記憶されている（図 7 のステップ S320, S380）。 20

#### 【 0048 】

中継 CPU 652 は、図 8 に示すリード中継処理を開始すると、擬似 ROM インタフェース 658 から読み出し信号を受け取る（ステップ S110）。その後、中継 CPU 652 は、中継 RAM 654 に記憶されたアドレス対応テーブル 720 を参照して、受け取った読み出し信号によって指定された論理ブロックアドレスに対応付けられている物理ブロックアドレスを特定する（ステップ S120）。その後、中継 CPU 652 は、特定した物理ブロックアドレスに記録されているデジタル画像データ 730 を NAND 型フラッシュメモリ 660 からシリアルインターフェース 657 を介して読み出す（ステップ S130）。その後、中継 CPU 652 は、読み出したデジタル画像データ 730 を、擬似 ROM インタフェース 658 を介して擬似 ROM デバイス 650 の外部である表示制御部 60 のパラレルインターフェース 640 に提供する（ステップ S140）。 30

#### 【 0049 】

図 9 は、擬似 ROM デバイス 650 の中継 CPU 652 によって実行されるライト中継処理を示すフローチャートである。データの書き込み信号（例えば、擬似 ROM ライタからの信号）が、擬似 ROM インタフェース 658 に入力されると、中継 CPU 652 は、図 9 に示すライト中継処理を開始する。本実施例では、図 9 のライト中継処理に先立って、パチンコ機 10 の電源投入時に、アドレス対応テーブル 720 は、中継 RAM 654 に記憶されている（図 7 のステップ S320, S380）。 40

#### 【 0050 】

中継 CPU 652 は、図 9 に示すライト中継処理を開始すると、擬似 ROM インタフェース 658 から書き込み信号を受け取る（ステップ S210）。その後、中継 CPU 652 は、擬似 ROM インタフェース 658 のライト端子 659 に入力されたライト信号がハイレベル（1）であるか否かを判断する（ステップ S215）。

#### 【 0051 】

10

20

30

40

50

ライト端子 659 に入力されたライト信号がローレベル(0)である場合、例えば、擬似 ROM デバイス 650 が表示制御部 60 に実装されている場合(ステップ S215)、中継 CPU 652 は、擬似 ROM インタフェース 658 から受け取った書き込み信号に基づくデータの書き込みを実行することなく、ライト中継処理を終了する。

#### 【0052】

一方、ライト端子 659 に入力されたライト信号がハイレベル(1)である場合、例えば、表示制御部 60 への実装に先立って擬似 ROM ライタによって擬似 ROM デバイス 650 にデジタル画像データ 730 が記録される場合(ステップ S215)、中継 CPU 652 は、中継 RAM 654 に記憶されたアドレス対応テーブル 720 を参照して、擬似 ROM インタフェース 658 から受け取った書き込み信号によって書き込み指定された論理ブロックアドレスに対応付けられている物理ブロックアドレスを特定する(ステップ S220)。その後、中継 CPU 652 は、アドレス対応テーブル 720 で特定した物理ブロックアドレスに、書き込み信号に含まれるデジタル画像データ 730 をシリアルインタフェース 657 を介して書き込む(ステップ S230)。

#### 【0053】

その後、中継 CPU 652 は、書き込みを実施した同じ物理ブロックアドレスからデータを読み出し、書き込んだデータと読み出したデータとを比較することによって、デジタル画像データ 730 が正確に記録されたか否かを検査するベリファイを実行する(ステップ S240)。

#### 【0054】

ベリファイによって書き込み不良が確認された場合(ステップ S245)、中継 CPU 652 は、中継 RAM 654 に記憶されたアドレス対応テーブル 720 を修正する(ステップ S250)。本実施例では、アドレス対応テーブル 720 の修正によって、書き込み不良が確認された良ブロックは、不良ブロックに変更され、その物理データブロックに対応付けられていた論理データブロックは、他の良ブロックに対応付けられる。中継 RAM 654 に記憶されたアドレス対応テーブル 720 が修正された後(ステップ S250)、中継 CPU 652 は、修正したアドレス対応テーブル 720 を参照して、デジタル画像データ 730 の再書き込みを行う(ステップ S260)。その後、中継 CPU 652 は、ベリファイからの処理を再実行する(ステップ S240)。

#### 【0055】

一方、ベリファイによって書き込み不良が確認されない場合(ステップ S245)、中継 CPU 652 は、書き込み信号に書き込み指定されたデータを全て書き込むために、後続のデータについてライト信号の判断(ステップ S215)からの処理を繰り返し実行する(ステップ S247)。書き込み信号に書き込み指定されたデータが全て NAND 型フラッシュメモリ 660 に記録されると(ステップ S247)、中継 CPU 652 は、中継 RAM 654 に記憶されたアドレス対応テーブル 720 を、NAND 型フラッシュメモリ 660 に記録する(ステップ S270)。

#### 【0056】

図 10 は、擬似 ROM デバイス 650 の中継 CPU 652 によって実行されるテーブル更新処理を示すフローチャートである。本実施例では、擬似 ROM デバイス 650 の中継 CPU 652 は、図 10 のテーブル更新処理を定期的に実行する。中継 CPU 652 は、図 10 のテーブル更新処理を開始すると、起動時にアドレス対応テーブル 720 の初期化を実行していない場合(ステップ S410、図 7 のステップ S320)や、初期化後にデータの書き込みが実行され NAND 型フラッシュメモリ 660 にアドレス対応テーブル 720 が記録された場合(ステップ S420、図 9 のステップ S270)、NAND 型フラッシュメモリ 660 に記録されているアドレス対応テーブル 720 を NAND 型フラッシュメモリ 660 からシリアルインタフェース 657 を介して中継 RAM 654 に読み込むことによって、中継 RAM 654 のアドレス対応テーブル 720 を上書きする(ステップ S430)。

#### 【0057】

10

20

30

40

50

以上説明したパチンコ機 10 によれば、伸張コントローラ 672 が実行する図 6 の伸張制御処理によって、擬似 ROM デバイス 650 からのデジタル画像データ 730 の読み出しが、バッファメモリ 675 の記憶容量に応じて一時的に停止されるため、バッファメモリ 675 の記憶容量よりも大きなデジタル画像データを伸張して動画像表示に用いることができる。また、擬似 ROM デバイス 650 からのデジタル画像データ 730 の読み出しが、擬似 ROM デバイス 650 に対して読み出しアクセス可能なデータ単位である NAND 型フラッシュメモリ 660 のページ単位で、バッファメモリ 675 の記憶容量に応じて分割して実行されるため、デジタル画像データ 730 の読み出しから伸張までの処理効率を向上させることができる。また、バッファメモリ 675 および伸張エンジン 676 を構成する複数のラインに、デジタル画像データ 730 の非圧縮データへの伸張を分散させることができるために、デジタル画像データ 730 の伸張処理の速度を向上させることができる。10

#### 【 0058 】

NAND 型フラッシュメモリ 660においてデジタル画像データ 730 が記録された良プロックの物理ブロックアドレスを並べた一連の物理ブロックアドレスが、パラレルインターフェース 640 で取り扱われる論理ブロックアドレスに対応付けられているため、パラレルインターフェース 640 を介して NAND 型フラッシュメモリ 660 からデジタル画像データ 730 を読み出すことができる。したがって、パチンコ機 10 において、NAND 型フラッシュメモリ 660 をデジタル画像データ 730 の記録媒体として利用することができる。20

#### 【 0059 】

また、擬似 ROM デバイス 650 は、NAND 型フラッシュメモリ 660 と共に、中継 CPU 652、中継 RAM 654、中継メモリ 656、擬似 ROM インタフェース 658、シリアルインターフェース 657 を、単一のパッケージとして封止したものであるため、デジタル画像データ 730 が記録された NAND 型フラッシュメモリ 660 を、パラレルインターフェース 640 によってデータアクセス可能なマスク ROM と同様にして取り扱うことができる。なお、NOR 型のフラッシュメモリの場合、その記憶容量の大きさが変わると、記憶素子の増加に伴いアドレス線の数が変わるが、NAND 型のフラッシュメモリの場合、アドレス線とデータ線とが兼用される構成から、信号線の数が変わらないため、VDP 側にシリアルインターフェース 657 を設けた方が良いと捉えることができる。しかしながら、パチンコ機においてキャラクタ画像を記憶するメモリは、その記憶画像の内容がパチンコ機の申請の段階で第三者機関により検査されるため、そのメモリは、パチンコ機の基板にソケット形式で着脱可能であり、パチンコ機から取り外された状態で ROM チップ等を用いてデータ内容を確認可能である必要がある。そのため、NAND 型のフラッシュメモリのようにバットブロックが発生する場合があるメモリは、そのバットブロック以外の正常なメモリ領域を管理する機能（中継 CPU 652 等）をメモリ側に持たないと、メモリ単独でのデータ内容の確認ができなくなってしまう。それゆえ、中継 CPU 652 等が NAND 型のフラッシュメモリと一体で構成されていることに有用性が生まれる。30

#### 【 0060 】

また、パラレルインターフェース 640 と NAND 型フラッシュメモリ 660 との間のアドレス変換が、NAND 型フラッシュメモリ 660 から中継 RAM 654 に読み出されたアドレス対応テーブル 720 に基づいて実行されるため、NAND 型フラッシュメモリ 660 上からアドレス対応テーブル 720 を参照してアドレス変換を実行するよりも、NAND 型フラッシュメモリ 720 からのデジタル画像データ 730 の読み出し速度を向上させることができる。これによって、デジタル画像データ 730 が記録された NAND 型フラッシュメモリ 660 を、パラレルインターフェース 640 からデータアクセス可能なマスク ROM として取り扱うことができる。40

#### 【 0061 】

また、パラレルインターフェース 640 と NAND 型フラッシュメモリ 660 との間のア50

ドレス変換が、中継RAM654に格納されたアドレス対応テーブル720に基づいて実行されるため、NAND型フラッシュメモリ660に対するデジタル画像データの書き込み速度を向上させることができる。

#### 【0062】

また、NAND型フラッシュメモリ660にデジタル画像データ730を書き込む際に、書き込んだデータについてのベリファイが実行され（ステップS240）、書き込み不良が検知された場合、アドレス対応テーブル720の修正およびデータの再書き込みが実行されるため（ステップS260）、NAND型フラッシュメモリ660におけるデジタル画像データ730の記録不良を防止することができる。

#### 【0063】

また、擬似ROMデバイス650の外部からNAND型フラッシュメモリ660に対するデータの書き込みの可否を、ライト端子659に入力されるライト信号によって管理することができる。また、表示制御部60に実装された擬似ROMデバイス650のライト端子659はグランドに接続されることによって、NAND型フラッシュメモリ660に対するデータの書き込みが常時禁止される。これによって、擬似ROMデバイス650に対する複雑な制御を行うことなしに、NAND型フラッシュメモリ660に書き込まれたデジタル画像データ730の改変を防止することができる。

#### 【0064】

また、中継RAM654に記憶されたアドレス対応テーブル720が定期的に上書きされるため（ステップS430）、中継RAM654上のアドレス対応テーブル720が、静電気や電波などのノイズによって損壊した場合であっても、定期的にアドレス対応テーブル720が更新されるため、デジタル画像データ730の読み出し誤りを抑制することができる。なお、従来、キャラクタROMをVDPに接続するインターフェースは、アドレスバスとデータバスとが独立したパラレルインターフェースであると共に、キャラクタROMに対してランダムアクセス可能なランダムアクセスインターフェースとして構成されていた。近年、遊技機においては、遊技機で取り扱われる画像情報量が増大化する傾向にある。本願発明は、その画像情報量の増大化に対応する一つの手段として、フラッシュメモリを利用する技術を提供する。フラッシュメモリの種類としては、NOR型とNAND型がある。NOR型のフラッシュメモリは、NAND型よりも高速なランダムアクセスが可能であり、NOR型のフラッシュメモリを利用すれば、遊技機における既存のインターフェースに容易に接続することができる。NAND型のフラッシュメモリは、NOR型よりも大容量化や小型化に有利であり、記憶容量あたりのコストパフォーマンスに優れる。しかしながら、NAND型のフラッシュメモリは、アドレスバスとデータバスとを兼用してデータを連続してやり取りするシリアルインターフェースに対応しているため、遊技機における既存のインターフェースに接続することは容易ではなかった。また、従来、遊技機における画像情報を記憶するために、シリアルインターフェースに接続可能なシーケンシャルROMを利用した遊技機もあったが、アクセススピードの点でフラッシュメモリに劣るものであった。パチンコ機では、遊技の進行に基づいて適時液晶表示装置に画像を表示し、パチンコ機内で内部抽選された結果を、おもしろおかしく見せて遊技者の興味を誘う。そのため、突然画像を替えたりすることもあり、その場合、必要な画像情報をいかに早く読み出せるかが重要である。その点では、シーケンシャルROMよりは、フラッシュメモリを採用することが望ましく、更には、記憶容量の点から、NAND型フラッシュメモリを採用することが望ましい。しかしながら、NAND型のフラッシュメモリの場合、バットロックを管理する必要があり、その点では使い勝手が悪い。そういった点では、NOR型の大容量化については、デバイスマーカーで研究が重ねられており、大容量化が進めば、そのまま、NOR型のフラッシュメモリに置き換えることもでき、利に叶なっているといえる。

#### 【0065】

##### B. 第2の実施例：

第2の実施例におけるパチンコ機10の構成は、NAND型フラッシュメモリ660に

10

20

30

40

50

対するデータの書き込みの禁止を管理するために、擬似ROMインターフェース658のライト端子659に代えて、またはライト端子659と共に、擬似ROMデバイス650の内部に設定されたライトフラグ715を有する点を除き、第1の実施例と同様である。

#### 【0066】

図11は、第2の実施例のパチンコ機10における擬似ROMデバイス650の詳細構成を主に示すブロック図である。第2の実施例における表示制御部60に実装された擬似ROMデバイス650のNAND型フラッシュメモリ660には、アドレス対応テーブル720およびデジタル画像データ730に加えて、NAND型フラッシュメモリ660に対するデータの書き込みの可否を示すライトフラグ715が、アドレス対応テーブル720と同じ良ブロックに予め記録されている。本実施例では、ライトフラグ715は、「0」と「1」で表される二値データであり、「0」の場合にNAND型フラッシュメモリ660に対するデータの書き込み可を示し、「1」の場合にデータNAND型フラッシュメモリ660に対するデータの書き込み不可を示す。本実施例では、表示制御部60に実装された擬似ROMデバイス650のNAND型フラッシュメモリ660には、ライトフラグ715が「1」の値で予め設定されている。

10

#### 【0067】

本実施例では、擬似ROMデバイス650のライトフラグ715は、表示制御部60への実装に先立って、擬似ROMデバイス650の擬似ROMインターフェース658とデータのやり取りを行う擬似ROMライタ(図示しない)からのフラグ変更信号に基づいて記録される。本実施例では、擬似ROMデバイス650の中継CPU652は、接続された擬似ROMライタ(図示しない)から擬似ROMデバイス650に書き込まれる予定であるデータの総容量値を取得した後、取得した総容量値に応じた良ブロックを確保するまで、NAND型フラッシュメモリ660の不良ブロックの検出を行い、不良ブロックの検出結果に基づいてアドレス対応テーブル720を作成して、最初の良ブロックにアドレス対応テーブル720を書き込む。本実施例では、中継CPU652は、擬似ROMライタ(図示しない)からのフラグ変更信号に基づいてライトフラグ715を「0」に設定した後、擬似ROMライタ(図示しない)からのデジタル画像データ730の書き込み信号に従って、不良ブロックを避けてデジタル画像データ730をNAND型フラッシュメモリ660に記録する。その後、中継CPU652は、擬似ROMライタ(図示しない)からのフラグ変更信号に基づいてライトフラグ715を「1」に設定する。その後、擬似ROMデバイス650は表示制御部60に実装される。

20

30

#### 【0068】

第2の実施例におけるパチンコ機10の動作は、擬似ROMインターフェース658のライト端子659に代えて、擬似ROMデバイス650の内部に設定されたライトフラグ715に基づいてライト中継処理を行う点を除き、第1の実施例の動作と同様である。

#### 【0069】

図12は、第2の実施例において擬似ROMデバイス650の中継CPU652によって実行されるライト中継処理を示すフローチャートである。データの書き込み信号が、擬似ROMインターフェース658に入力されると、中継CPU652は、図12に示すライト中継処理を開始する。本実施例では、図12のライト中継処理に先立って、パチンコ機10の電源投入時に、アドレス対応テーブル720は、中継RAM654に記憶されている(図7のステップS320, S380)。

40

#### 【0070】

中継CPU652は、図12に示すライト中継処理を開始すると、擬似ROMインターフェース658から書き込み信号を受け取る(ステップS510)。その後、中継CPU652は、ライトフラグ715がハイレベル(1)であるか否かを判断する(ステップS515)。

#### 【0071】

ライトフラグ715がハイレベル(1)である場合、例えば、擬似ROMデバイス650が表示制御部60に実装されている場合(ステップS515)、中継CPU652は、

50

擬似 ROM インタフェース 658 から受け取った書き込み信号に基づくデータの書き込みを実行することなく、ライト中継処理を終了する。

#### 【0072】

一方、ライトフラグ 715 がローレベル(0)である場合、例えば、表示制御部 60 への実装に先立って擬似 ROM デバイス 650 にデジタル画像データ 730 が記録される場合(ステップ S515)、中継 CPU 652 は、中継 RAM 654 に記憶されたアドレス対応テーブル 720 を参照して、擬似 ROM インタフェース 658 から受け取った書き込み信号によって書き込み指定された論理ブロックアドレスに対応付けられている物理ブロックアドレスを特定する(ステップ S220)。その後、中継 CPU 652 は、図 9 のライト中継処理と同様に、デジタル画像データ 730 の書き込みを実行する。

10

#### 【0073】

以上説明した第 2 の実施例におけるパチンコ機 10 によれば、第 1 の実施例と同様に、NAND 型フラッシュメモリ 660 上からアドレス対応テーブル 720 を参照してアドレス変換を実行するよりも、NAND 型フラッシュメモリ 720 からのデジタル画像データ 730 の読み出し速度を向上させることができる。また、擬似 ROM デバイス 650 の外部から NAND 型フラッシュメモリ 660 に対するデータの書き込みの可否を、擬似 ROM デバイス 650 の内部に設定されたライトフラグ 715 によって管理することができる。また、表示制御部 60 に実装された擬似 ROM デバイス 650 のライトフラグ 715 は「1」の値に予め設定されることによって、NAND 型フラッシュメモリ 660 に対するデータの書き込みが常時禁止される。これによって、擬似 ROM デバイス 650 に対する複雑な制御を行うことなしに、NAND 型フラッシュメモリ 660 に書き込まれたデジタル画像データ 730 の改変を防止することができる。

20

#### 【0074】

##### C. その他の実施形態：

以上、本発明の実施の形態について説明したが、本発明はこうした実施の形態に何ら限定されるものではなく、本発明の趣旨を逸脱しない範囲内において様々な形態で実施し得ることは勿論である。例えば、バッファメモリ 675 および伸張エンジン 676 を構成するラインは複数に限るものではなく、単一のラインであっても良い。

#### 【0075】

また、NAND 型フラッシュメモリ 660 は、不良ブロックを飛ばしてデジタル画像データが順次記録されたものに限るものではなく、不良ブロックを他の良ブロックで代替した代替ブロックを利用してデジタル画像データが記録されたものであっても良い。

30

#### 【0076】

図 13 は、他の実施形態における中継メモリ 656 に記憶されたアドレス対応テーブル 720 の一例を示す説明図である。図 13 のアドレス対応テーブル 720 で管理される NAND 型フラッシュメモリ 660 には、良ブロックの一部が代替ブロックとして用意され、デジタル画像データ 730 は、一連の物理ブロックアドレスの順に従って NAND 型フラッシュメモリ 660 に順次記録され、記録対象となった物理データブロックが不良ブロックである場合、その不良ブロックに記録すべきデータは、代替ブロックに記録される。図 13 に示す例では、良ブロックである物理ブロックアドレス PBA0001 ~ PBA0003 の物理データブロックには、デジタル画像データ GDO0000 ~ GDO0002 が順次記録され、不良ブロックである物理ブロックアドレス PBA0004 の物理データブロックに記録すべきデジタル画像データ GDO003 は、代替ブロックである物理ブロックアドレス PBA9999 の物理データブロックに記録され、後続のデジタル画像データは、同様に順次記録されている。図 13 に示す例では、一連の論理ブロックアドレス 722 は、デジタル画像データが記録された良ブロックの物理ブロックアドレスをデジタル画像データの格納順に並べた一連の物理ブロックアドレスに順次対応付けられている。例えば、論理ブロックアドレス LBA0003 は、物理ブロックアドレス PBA0003 の不良ブロックに対応する代替ブロックである物理ブロックアドレス PBA9999 に対応付けられている。

40

50

## 【0077】

また、本実施例では、NAND型フラッシュメモリ660に記録されたデジタル画像データ730は圧縮データとしたが、他の実施形態として、NAND型フラッシュメモリ660に記録されたデジタル画像データ730は非圧縮データであっても良い。また、本実施例では、NAND型フラッシュメモリ660に対するデータの書き込みの禁止は、中継CPU652のソフトウェアに基づく動作によって実現したが、中継CPU652などの機能をASIC(Application Specific Integrated Circuit)でハード的に構成することによって実現しても良い。また、本実施例では、ライト端子659に入力されるライト信号は、ハイレベル(1)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み可を示し、ローレベル(0)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み不可を示すとしたが、他の実施形態として、ローレベル(0)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み可を示し、ハイレベル(1)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み不可を示すとしても良い。また、本実施例では、擬似ROMデバイス650に設定されるライトフラグ715は、ローレベル(0)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み可を示し、ハイレベル(1)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み不可を示すとしたが、他の実施形態として、ハイレベル(1)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み可を示し、ローレベル(0)の値の場合にNAND型フラッシュメモリ660に対するデータの書き込み不可を示すとしても良い。10

## 【0078】

また、本実施例では、図5および図13のアドレス対応テーブル720において、論理ロックアドレスは、物理ロックアドレスに直接的に対応づけられる様としたが、他の実施形態として、個々の論理ロックアドレスに対応する物理ロックアドレスは、その対応する論理ロックアドレスの値との差を示すオフセット値として対応付けられても良い。例えば、図13に示した対応関係では、アドレス対応テーブル720において、論理ロックアドレスLBA0000は、物理ロックアドレスPBA0001とのアドレス値の差を示すオフセット値「1」に対応付けられ、論理ロックアドレスLBA0003は、物理ロックアドレスPBA9999とのアドレス値の差を示すオフセット値「9996」に対応付けられる。20

## 【符号の説明】

## 【0079】

- 10...パチンコ機

- 20...外枠

- 30...内枠

- 32...ハンドル

- 34...スピーカ

- 36...演出センサ

- 40...遊技パネル

- 42...LCD

- 44...入賞口

- 442...遊技球センサ

- 444...入賞口駆動部

- 45...演出駆動部

- 46...電飾部

- 462...LED

- 47...演出センサ

- 50...ガラス枠

- 55...スピーカ

- 56...電飾部

4050

|                             |    |

|-----------------------------|----|

| 5 6 2 . . . L E D           |    |

| 8 0 ... カードユニット             |    |

| 3 1 0 ... 払出制御基板            |    |

| 4 1 0 ... 主制御基板             |    |

| 4 2 0 ... 周辺制御基板            |    |

| 4 3 0 ... パネル電飾基板           |    |

| 4 4 0 ... 周辺分配基板            |    |

| 4 5 0 ... 枠電飾基板             |    |

| 6 0 ... 表示制御部               |    |

| 6 1 0 ... 描画制御部             | 10 |

| 6 2 0 ... V D P             |    |

| 6 3 4 ... バススイッチ回路          |    |

| 6 3 6 , 6 3 8 ... 伸張 R A M  |    |

| 6 4 0 ... パラレルインターフェース      |    |

| 6 5 0 ... 擬似 R O M デバイス     |    |

| 6 5 2 ... 中継 C P U          |    |

| 6 5 4 ... 中継 R A M          |    |

| 6 5 6 ... 中継メモリ             |    |

| 6 5 7 ... シリアルインターフェース      |    |

| 6 5 8 ... 擬似 R O M インタフェース  | 20 |

| 6 5 9 ... ライト端子             |    |

| 6 6 0 ... N A N D 型フラッシュメモリ |    |

| 6 7 2 ... 伸張コントローラ          |    |

| 6 7 4 ... データ分配回路           |    |

| 6 7 5 ... バッファメモリ           |    |

| 6 7 6 ... 伸張エンジン            |    |

| 6 7 8 ... データ合成回路           |    |

| 7 1 0 ... 中継プログラム           |    |

| 7 1 5 ... ライトフラグ            |    |

| 7 2 0 ... アドレス対応テーブル        | 30 |

| 7 2 2 ... 論理ブロックアドレス        |    |

| 7 2 4 ... 物理ブロックアドレス        |    |

| 7 2 6 ... ブロック状態            |    |

| 7 2 8 ... 格納データ             |    |

| 7 3 0 ... デジタル画像データ         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

---

フロントページの続き

審査官 篠崎 正

(56)参考文献 特開2006-075457(JP,A)

特開2005-065120(JP,A)

特開平04-065740(JP,A)

特開平07-129756(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 6 3 F 7 / 0 2