# **PCT**

#### WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>6</sup>:

G05F 3/30, 1/567

A1

(11) International Publication Number: WO 96/39652

(43) International Publication Date: 12 December 1996 (12.12.96)

US

(21) International Application Number: PCT/US95/11320

(22) International Filing Date: 6 September 1995 (06.09.95)

5 June 1995 (05.06.95)

(71) Applicant: ANALOG DEVICES, INC. (ADI) [US/US]; One Technology Way, Norwood, MA 02062 (US).

(72) Inventor: AUDY, Jonathan, M.; 1637 Glenhurst, San Jose, CA 95124 (US).

(74) Agent: GIFFORD, Eric, A.; Koppel & Jacobs, Suite 302, 31255 Cedar Valley Drive, Westlake Village, CA 91362 (US). (81) Designated States: AT, AU, BB, BG, BR, BY, CA, CH, CN, CZ, DE, DK, ES, FI, GB, HU, JP, KP, KR, KZ, LK, LU, LV, MG, MN, MW, NO, NZ, PL, PT, RO, RU, SD, SE, SK, UA, UZ, VN, European patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG).

#### **Published**

With international search report. With amended claims.

(54) Title: INTEGRATED CIRCUIT TEMPERATURE SENSOR WITH A PROGRAMMABLE OFFSET

#### (57) Abstract

į

(30) Priority Data: 08/461.868

Temperature sensor (10), with programmable offset, generates an output voltage (Vo) that is a PTAT voltage VPTAT shifted by offset voltage Voff. Band gap cell (12) generates a basic voltage across first resistor (RPTAT) to produce current (IPTAT). Second resistor (Rgain), connected between first resistor (RPTAT) and reference voltage terminal (Vee), provides voltage gain. Third resistor (Roff) is connected across the base-emitter junction of transistor (Q1) and between second resistor (Rgain) and output terminal (20) where voltage (Vo) is provided. The transistor's baseemitter voltage provides a portion of Voff. Third resistor (Roff) reduces the portion of current (IPTAT) flowing through second resistor (Rgain) to provide the remaining portion of Voff. Current source (IS1) supplies an emitter current and a current for third resistor (Roff). Offset voltage Voff is set by trimming third resistor (Roff) until voltage (Vo) equals a voltage applied to reference voltage terminal (Vee) at a lower end of a desired temperature range. The gain of VPTAT is then set by trimming first resistor (RPTAT).

#### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT<br>AU | Austria                  | ~~ |                              |    |                          |

|----------|--------------------------|----|------------------------------|----|--------------------------|

| ATT      |                          | GE | Georgia                      | MX | Mexico                   |

| AU       | Australia                | GN | Guinea                       | NE | Niger                    |

| BB       | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE       | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF       | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG       | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| BJ       | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR       | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY       | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA       | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF       | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG       | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| . CH     | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI       | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM       | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN       | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS       | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ       | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE       | Germany                  | LV | Latvia                       | TJ | Tajikistan               |

| DK       | Denmark                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| EE       | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES       | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| FI       | Finland                  | ML | Mali                         | US | United States of America |

| FR       | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA       | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

# INTEGRATED CIRCUIT TEMPERATURE SENSOR WITH A PROGRAMMABLE OFFSET

#### BACKGROUND OF THE INVENTION

#### Field of the Invention

5

10

15

20

The present invention generally relates to integrated circuit (IC) proportional to absolute temperature (PTAT) temperature sensors, and more specifically to an IC temperature sensor with a programmable offset.

#### Description of the Related Art

The base-emitter voltage  $V_{be}$  of a forward biased transistor is a linear function of absolute temperature T in degrees Kelvin (°K), and is known to provide a stable and relatively linear temperature sensor.

$$V_{be} = \frac{kT_k}{q} \ln \left( \frac{I_c}{A_c J_c} \right) \tag{1}$$

where k is Boltzmann's constant,  $T_k$  is the absolute temperature (°K), q is the electron charge  $(k/q=86.17\,\mu\text{V/°K})$ ,  $I_c$  is the collector current,  $A_e$  is the emitter area, and  $J_s$  is the saturation-current density. PTAT sensors eliminate the dependence on collector current by using the difference  $\Delta\,V_{be}$  between the base-emitter voltages  $V_{be1}$  and  $V_{be2}$  of two transistors that are operated at a constant ratio between their emitter-current densities to form the PTAT voltage. The emitter-current density is conventionally defined as the ratio of the collector current to the emitter size (this

2

ignores the second order base current). The basic PTAT voltage  $\Delta \text{V}_\text{he}$  is given by:

$$\Delta V_{\text{be}} = V_{\text{be}1} - V_{\text{be}2} \tag{2}$$

$$\Delta V_{be} = \left(\frac{kT_k}{q}\right) \ln\left(\frac{I_{c1}A_{e2}}{I_{c2}A_{c1}}\right)$$

(3)

The basic PTAT voltage is amplified so that its gain, i.e. its sensitivity to changes in absolute temperature, can be calibrated to a desired value, suitably 10mV/°K, and buffered so that a PTAT voltage can be read out without corrupting the basic PTAT voltage.

10

15

20

25

30

A drawback of standard PTAT sensors is that at ordinary operating temperatures for most ICs there is a large offset voltage signal. For example, if the desired operating range for an IC is 0 to 125°C (273 to 398°K) and the sensor has a gain of 10mV/°K, the PTAT sensor will have an offset voltage of 2.73V at 0°C. If the gain of the PTAT sensor is not perfectly stable, a relatively small change in the offset voltage may shift the output temperature by several degrees. To read out a temperature from 0 to 125° C, a reference voltage of precisely 2.73V must be subtracted from the output of the PTAT sensor. Providing a reference voltage with adequate precision and stability is difficult and costly. Furthermore, PTAT sensors require relatively large supply voltages to supply the offset voltage in addition to the voltage needed to respond over the desired operating range and any head voltage needed to operate the sensor. Thus, products such as lap top computers which run off approximately 3V supplies cannot use PTAT sensors.

Pease, "A New Fahrenheit Temperature Sensor," IEEE Journal of Solid-State Circuits, Vol. SC-19, No. 6, Dec.

1984, pages 971-977, discloses a temperature sensor that provides an output voltage scaled proportional to the Fahrenheit temperature without subtracting a large constant offset voltage at the output. Pease generates a PTAT voltage using a conventional transistor pair and internally subtracts two base-emitter voltages to shift the PTAT voltage by a constant offset voltage. A non-inverting amplifier is used to multiply the shifted PTAT voltage by a fixed gain, e.g. 1.86, to simultaneously set the sensor's desired offset voltage, e.g. 770mV at 77°F, and gain, e.g. 10mV/°F. The gain is inherently calibrated by simply trimming the offset error at room temperature. In this manner, Pease effectively subtracts the offset voltage so that the sensor's output voltage is zero at 0°F.

Pease's circuit topology has several drawbacks. The shifted output voltage is produced in two separate stages: a constant offset is first subtracted from the basic PTAT voltage and then the result is multiplied by the amplifier to achieve the desired output. This increases the sensor's complexity. Because the amplifier is used to buffer the output voltage in addition to providing gain, any errors in the amplifier such as offset voltage or offset voltage drift are reflected into the output voltage signal and may cause a temperature shift. For the Fahrenheit sensor to measure 0°F, the inverting input of the amplifier must be able to go to ground potential. This type of amplifier is complex and difficult to design.

National Semiconductor Corporation produces an LM35 series of Precision Centigrade Temperature Sensors which are disclosed in their Data Acquisition Data Book, 1993, pages 5-12 to 5-15 and are the centigrade equivalent of Pease's Fahrenheit sensor. The centigrade sensors exhibit the same problems and require a minimum 4V supply voltage.

4

#### SUMMARY OF THE INVENTION

5

10

15

20

25

30

The present invention provides a temperature sensor with a an accurate programmable offset that generates an output voltage  $V_{\circ}$  over a desired temperature range that is a PTAT voltage  $V_{\text{PTAT}}$  shifted by an offset voltage  $V_{\text{off}}$ , but with a simpler design than prior temperature sensors.

This is accomplished with a band gap cell that generates a basic PTAT voltage across a first resistor to produce a PTAT current  $I_{\text{PTAT}}$ . A second resistor is connected from the first resistor to a reference voltage terminal to provide voltage gain. A transistor has a base that is connected between the first and second resistors, a collector that is tied to a supply voltage, and an emitter that is connected to an output terminal at which Vo is generated. The transistor's base-emitter voltage provides a portion of offset voltage Voff. A third resistor is connected across the transistor's base-emitter junction, which reduces the portion of  $\mathbf{I}_{\mathtt{PTAT}}$  that flows through the second resistor and provides the remaining portion of  $V_{\text{off}}$ . A current source is positioned between the transistor's emitter and the reference voltage terminal to supply its emitter current and the current for the third resistor.

The offset voltage  $V_{\text{off}}$  is set by trimming the third resistor until  $V_o$  equals a voltage applied to the reference voltage terminal at a lower end of the desired temperature range. The desired gain of  $V_{\text{PTAT}}$  is then set by trimming the first resistor.

For a better understanding of the invention, and to show how the same may be carried into effect, reference will now be made, by way of example, to the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

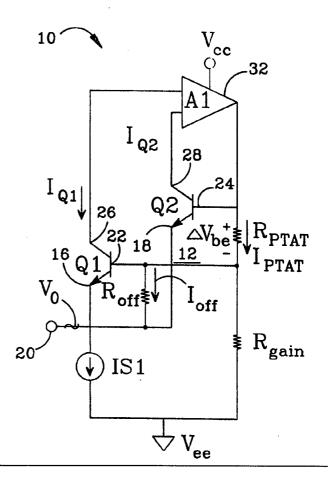

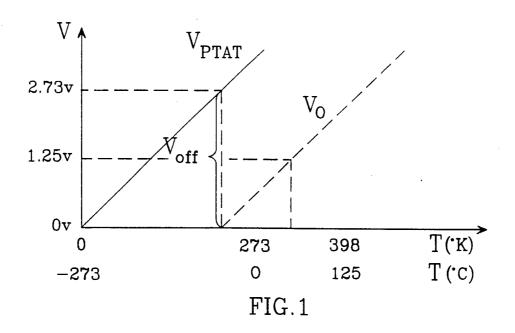

FIG. 1 is a plot of the output voltage for the sensor of the present invention versus absolute temperature;

5

FIG. 2 is a simplified schematic diagram of a band gap temperature sensor with a programmable offset voltage in accordance with the present invention;

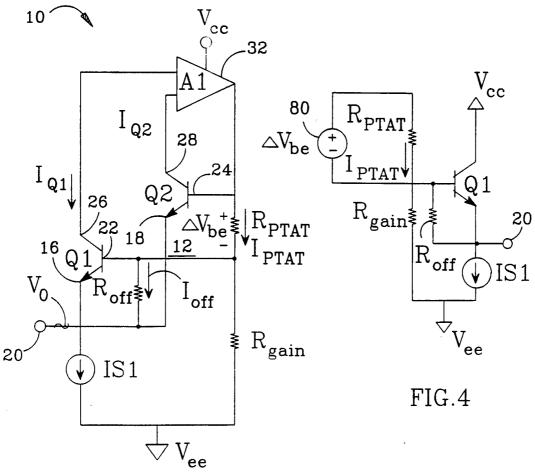

FIG. 3 is a more detailed schematic diagram of a preferred embodiment of the band gap temperature sensor shown in FIG. 2; and

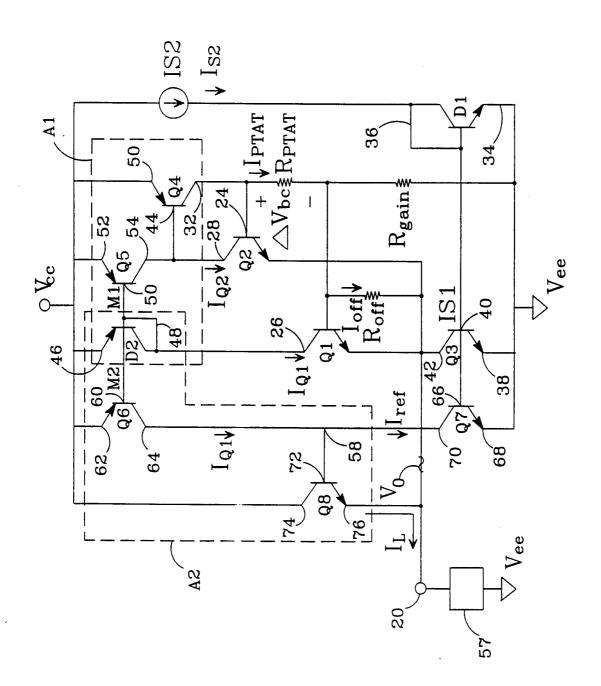

FIG. 4 is a simplified schematic diagram that illustrates the programmable offset capability of the present invention for a general PTAT voltage source.

10

15

20

25

30

35

5

#### DETAILED DESCRIPTION OF THE INVENTION

As shown in FIG. 1, the present invention provides a temperature sensor that generates an output voltage Vo that is a PTAT voltage  $V_{PTAT}$  shifted by a desired offset voltage  $V_{\text{off}}$  so that  $V_{\text{o}}$  goes to the sensor's low supply, typically ground, when the temperature is at the lower end of a desired temperature range. The OV temperature intercept is set by programming the sensor's offset voltage and gain. This increases the sensor's accuracy, removes the need to generate and subtract a reference voltage from the output voltage, and allows the temperature sensor to operate from 0 to 125°C with a gain of 10mV/°C off a single-sided supply voltage of approximately 2.7V. This approach allows the sensor's offset voltage and gain to be adjusted to accommodate both Centigrade and Fahrenheit sensors with a wide range of operating temperatures and gains. Pease's sensor is capable of generating the same graph, but requires more complicated circuitry and at least a 4V supply.

A programmable offset is provided by adding a single offset resistor to a conventional band gap temperature cell and by generating  $V_{\circ}$  at a different point in the cell. The desired offset is programmed by trimming the offset resistor until  $V_{\circ}$  equals 0V at the desired offset temperature. The sensor's gain is programmed independently by trimming another resistor in the band gap cell. An output amplifier

6

is preferably connected to the cell to buffer  $V_{\rm o}$  so that it is not effected by external loading.

This approach is simple and accurate. The offset voltage is programmed in a single stage by trimming a single resistor while the gain is controlled independently by trimming a second resistor. The output amplifier is used only to buffer  $V_{\circ}$ , and hence errors in the amplifier are not reflected into the output voltage. Furthermore, the amplifier is a simple one whose input does not have to be capable of going to ground potential.

5

10

15

20

25

30

35

As shown in FIG. 2, a temperature sensor 10 that has a programmable offset in accordance with the invention includes a band gap cell 12 that provides a basic PTAT voltage  $\Delta V_{be}$ , and an offset resistor  $R_{off}$  that selects an offset voltage so that sensor 10 produces output voltage Vo, where Vo substantially equals the voltage at the low supply Vee, preferably ground potential, at a lower end of a desired temperature range. Band gap cell 12 includes a pair of npn transistors Q1 and Q2 that conduct different current densities to establish the basic PTAT voltage. The ratio of their current densities is preferably set by substantially equating their collector currents  $I_{01}$  and  $I_{02}$ , suitably  $3\,\mu\text{A}$ , and providing transistor Q1 with an emitter area  $A_{e1}$  that is A, suitably 10, times larger than the emitter area  $\rm A_{\rm e2}$  of transistor 02.

The emitters 16 and 18 of transistors Q1 and Q2, respectively, are tied together at an output terminal 20. A current source IS1 is connected between output terminal 20 and ground, and supplies tail current for both transistors. Their bases 22 and 24 are connected across a resistor  $R_{\text{PTAT}}$  and establish the basic PTAT voltage  $\Delta V_{\text{be}}$ , as described in equations 2 and 3, across a resistor  $R_{\text{PTAT}}$ . The PTAT voltage causes a PTAT current  $I_{\text{PTAT}}$  to flow through resistor  $R_{\text{PTAT}}$ . A resistor  $R_{\text{gain}}$  is connected from the base 22 of transistor Q1 to ground to provide gain for the basic PTAT voltage.

10

15

20

25

30

Without the invention and ignoring the base currents of transistors Q1 and Q2,  $I_{\text{PTAT}}$  would flow through resistor  $R_{\text{gain}}$ .

The collector currents  $I_{Q1}$  and  $I_{Q2}$  that flow through the collectors 26 and 28 of transistors Q1 and Q2, respectively, are input to a differential current amplifier A1 which has a current gain of suitably one hundred. The amplifier's output 32 is connected between a high voltage supply  $V_{cc}$  and the base 24 of transistor Q2, and supplies  $I_{PTAT}$  (ignoring the second order effects of Q2's base current) to maintain the basic PTAT voltage across resistor  $R_{PTAT}$ . The purpose of amplifier A1 is to make the band gap cell insensitive to changes in supply voltage  $V_{cc}$ . Alternately, a differential voltage amplifier could be used with pull resistors connecting its differential input and output 32 to the high supply.

In the absence of  $R_{\text{off}},$  the output voltage would be taken from the top of resistor  $R_{\text{PTAT}}$  and would be given by:

$$V_o = (1 + \frac{R_{gain}}{R_{pmax}}) \frac{kT_k}{q} ln(A)$$

(4)

The ratio of  $R_{\text{gain}}$  to  $R_{\text{PTAT}}$  would be set to select the desired gain for the temperature sensor, and the conventional output voltage  $V_{\text{o}}$  would be PTAT, and thus would incorporate a large offset voltage.

In accordance with the invention, resistor  $R_{\rm off}$  is connected across transistor Q1's base 22 and emitter 16, and output voltage Vo is read out at output terminal 20. The effect of taking the output voltage at output terminal 20 is twofold. First, the base-emitter voltage of transistor Q1 is subtracted from the PTAT voltage across resistor  $R_{\rm gain}$  and provides a portion of the desired offset  $V_{\rm off}$ . Second, the output voltage  $V_{\rm o}$  can be reduced to 0V at a desired temperature by collapsing the voltage across current source IS1.

15

The effect of connecting resistor  $R_{\rm off}$  across transistor Q1's base-emitter junction is to provide a current source that sinks a portion of IPTAT from resistor  $R_{\rm PTAT}$ , thereby reducing the portion of  $I_{\rm PTAT}$  that flows through resistor  $R_{\rm gain}$ . This reduces the voltage across resistor  $R_{\rm gain}$  by the remaining portion of the desired offset  $V_{\rm off}$ , which reduces  $V_{\rm o}$  by the same amount.

Because the base-emitter voltage of transistor Q1 is a function of temperature, connecting resistor  $R_{\rm off}$  across its base-emitter junction and moving the output has the additional effect of increasing the gain of output voltage Vo. This reduces the amount of gain that must be provided by the basic PTAT voltage and resistor  $R_{\rm gain}$ , which in turn reduces the supply voltage  $V_{\rm cc}$  required to drive the sensor.

The characteristic equation for output voltage  $V_o$  is given by the following derivation. First, the voltage across resistor  $R_{\text{gain}}$  is described by:

$$V_{R_{gain}} = (I_{PTAT} - I_{Roff}) R_{gain}$$

(5)

where  $I_{\text{PTAT}} = \frac{\Delta V_{\text{be}}}{R_{\text{PTAT}}}$  and  $I_{\text{off}} = \frac{V_{\text{be1}}}{R_{\text{off}}}$ . Substituting these rela-

20 tionships into equation 5 gives:

$$V_{\text{Rgain}} = \left(\frac{kT}{q} \frac{\ln(A)}{R_{\text{PTAT}}} - \frac{V_{\text{bel}}}{R_{\text{off}}}\right) R_{\text{gain}}$$

(6)

Thus, the output voltage, which is  $V_{\text{Rgain}}$  shifted down by a base-emitter voltage, is given by:

$$V_{o} = \left(\frac{kT}{q} \frac{\ln{(A)}}{R_{prat}} - \frac{V_{be1}}{R_{opp}}\right) R_{gain} - V_{be1}$$

(7)

The base-emitter voltage for a transistor is given by:

10

9

$$V_{be} = E_g - BT_k \tag{8}$$

where  $E_g$  is the band gap voltage and B is a constant.  $E_g$  is independent of processing parameters, bias-current levels, and transistor geometry, and thus provides a constant reference value of approximately 1.17V for silicon. The constant B depends on bias current and processing, and has a typical value of  $2mV/^\circ K$ .

Substituting the relation for  $V_{be}$  from equation 8 into equation 7 and rearranging to separate the voltage component that is PTAT from the constant voltage offset gives:

$$V_{o} = \left[ \frac{R_{gain}}{R_{PTAT}} \frac{k}{q} \ln(A) + B\left(1 + \frac{R_{gain}}{R_{off}}\right) \right] T_{k} - \left(1 + \frac{R_{gain}}{R_{off}}\right) E_{g}$$

(9)

Therefore, the desired offset voltage Voff is given by:

$$V_{\text{off}} = -\left(1 + \frac{R_{\text{gain}}}{R_{\text{off}}}\right) E_{g}$$

(10)

and the PTAT voltage  $V_{\text{PTAT}}$  generated at output terminal 20 is:

$$V_{PTAT} = \left[\frac{R_{gain}}{R_{PTAT}} \frac{k}{q} \ln(A) + B\left(1 + \frac{R_{gain}}{R_{off}}\right)\right] T_k \qquad (11)$$

Thus, offset voltage  $V_{off}$  is set by selecting the ratio of  $R_{gain}/R_{off}$ , and the gain of VPTAT is calibrated by selecting the resistance of  $R_{PTAT}$ . In practice  $E_g$  does not vary appreciably, and hence  $R_{gain}/R_{off}$  can be set without trimming. The slope of  $V_{be}$  does vary so that  $R_{PTAT}$  can be trimmed until  $V_{out}$  equals a desired value, for example  $V_{out}$ =0.25V at 25°C.

This configuration has the additional benefit of re-

ducing the amount of supply voltage  $V_{cc}$  that is required to drive the temperature sensor. The supply voltage has to provide approximately the voltage at base 24 of transistor Q2 for the maximum desired temperature plus a  $V_{be}$  for amplifier A1. Simply providing an offset voltage at the output would not reduce this amount. However, the invention reduces the gain of the basic PTAT voltage and offsets the voltage across resistor  $R_{gain}$ . This reduces the voltage at base 24, and thus reduces the required supply voltage.

A good approximation is that the voltage at base 24 is a  $V_{be}$  above the output voltage, and hence the supply voltage  $V_{cc}$  must be at least two  $V_{be}$ 's above the maximum output voltage. For example, a temperature sensor with a temperature range of 0-125°C and a gain of 10mV/°K has a maximum  $V_{o}$  of 1.25V. A  $V_{be}$  is approximately 0.414V at 125°C. Thus, the minimum supply voltage  $V_{cc}$  would be approximately 2.1V. Therefore, a centigrade temperature sensor with a 10mV/°C gain and a range of 0-125°C would run comfortably off a 2.7V supply.

FIG. 3 shows a preferred temperature sensor that 10 includes the band gap cell 12 from FIG. 2 with preferred implementations of current source IS1 and differential amplifier A1, and an output amplifier A2 for buffering  $V_{\rm o}.$  Current source IS1 is implemented with a current source IS2 that provides current  $I_{\rm s2},$  suitably  $3\,\mu\rm A,$  which flows from the positive supply  $V_{\rm cc}$  through a diode D1 to ground. Diode D1 is implemented as a diode-connected npn transistor having an emitter 34 that is connected to ground and a base-collector 36. Another npn transistor Q3 has an emitter 38 that is connected to ground, a base 40 that is connected to base-collector 36 of diode D1, and a collector 42 that mirrors  $I_{\rm s2}$  to output terminal 20 with a fixed amount of gain. This supplies the emitter currents of transistors Q1 and Q2 and the offset current  $I_{\rm off}$  flowing through resistor  $R_{\rm off}.$

Differential current amplifier Al includes a current

mirror M1 that drives a difference current equal to  $IQ1-I_{Q2}$  into the base 44 of a pnp output stage transistor Q4 that amplifies the difference current to supply  $I_{PTAT}$ . One side of current mirror M1 includes a diode D2 that is implemented as a diode connected pnp transistor having an emitter 46 that is connected to  $V_{cc}$  and a base-collector 48 that is connected to transistor Q1's collector 26. The other side of mirror M1 includes a pnp transistor Q5 having a base 50 that is connected to base-collector 48 of diode D2, an emitter 52 that is tied to  $V_{cc}$ , and a collector 54 that is connected to transistor Q2's collector 28 and base 44 of output stage transistor Q4. The emitter 56 of transistor Q4 is connected to  $V_{cc}$  and its collector, which provides amplifier A1's output 32, is connected to the base 24 of transistor Q2.

Current mirror M1 and output stage transistor Q4 together provide a negative feedback path that stabilizes band gap cell 12 and makes it insensitive to fluctuations in the supply voltage  $V_{\rm cc}$ . For example, an increase in the difference current causes an increase in  $I_{\rm PTAT}$ . This in turn increases the voltage at the base 24 of transistor Q2, which increases its collector current  $I_{\rm Q2}$  and consequently reduces the difference current.

Output amplifier A2 is connected between band gap cell 12 and a load 57 such as a read out circuit, and supplies load current  $I_L$  to drive load 57 in accordance with output voltage  $V_o$ . Without amplifier A2, transistors Q1 and Q2 would have to drive the load. Although Q1 and Q2 are capable of providing some current without affecting  $V_o$ , it is preferable to use amplifier A2 to provide a buffer that maintains the integrity of  $V_o$  over a wide range of load conditions.

Amplifier A2 includes a current mirror M2 that mirrors collector current  $I_{\text{Q1}}$  to a current node 58. Current mirror M2 shares diode D2 with mirror M1 and includes a pnp tran-

12

sistor Q6 having a base 60 that is connected to D2's basecollector 48, an emitter 62 that is tied to  $V_{cc}$ , and a collector 64 that is connected to node 58. An npn transistor Q7 having a base 66 that is connected to the base-collector 36 of diode D1, an emitter 68 tied to ground, and a collector 70, sinks a reference current  $I_{\text{ref}}$  from current node 58 so that a difference current of  $I_{\text{Q1}}\text{-}I_{\text{ref}}$  is supplied from node 58 to the base 72 of an output transistor Q8. transistor has a collector 74 that is tied to  $V_{cc}$ , and an emitter 76 that is connected to output terminal 20. Output transistor Q8 amplifies the difference current  $I_{01}$ - $I_{ref}$  by its current gain  $\beta$ , suitably 100, to supply most of the load current  $I_L$  at output terminal 20. Transistors Q1 and Q2 supply a small second order portion of the total load current  $I_L$ , approximately  $I_L/\beta$ , which is not appreciable and does not significantly effect Vo.

5

10

15

20

25

35

the desired offset.

In the preferred embodiments of temperature sensor 10 shown in FIGs. 2 and 3, transistor Q1 served a dual purpose. First, it forms part of the transistor pair Q1/Q2 that sets the basic PTAT voltage. Second, transistor Q1 together with offset resistor  $R_{\rm off}$  provides the programmable offset voltage. However, many different circuit topologies might be used to generate the basic PTAT voltage  $\Delta V_{\rm be}$ . The generalized situation is shown in FIG. 4, in which a PTAT voltage source 80, such as band gap cell 12 in FIGs. 2 and 3, generates the basic PTAT voltage across resistor  $R_{\rm PTAT}$ , which causes  $I_{\rm PTAT}$  to flow through resistor  $R_{\rm gain}$ . The combination of transistor Q1 and resistor  $R_{\rm off}$  reduces the portion of  $I_{\rm PTAT}$  that flows through resistor  $R_{\rm gain}$  so that the output voltage  $V_{\rm o}$  at output terminal 20 is shifted by

While several illustrative embodiments of the invention have been shown and described, numerous variations and alternate embodiments will occur to those skilled in the art. Such variations and alternate embodiments are contem-

13

plated, and can be made without departing from the spirit and scope of the invention as defined in the appended claims.

#### I CLAIM:

5

10

15

25

1. A band gap temperature sensor, comprising: a first resistor  $R_{\text{PTAT}}$ ;

first and second transistors (Q1,Q2) having respective bases that are connected across said first resistor, collectors, and emitters that are connected together, said transistors conducting respective collector currents with different current densities which establishes a basic voltage proportional to absolute temperature (PTAT) across resistor  $R_{\text{PTAT}}$  causing a PTAT current  $I_{\text{PTAT}}$  to flow through resistor  $R_{\text{PTAT}}$ ;

a reference voltage terminal (V<sub>ee</sub>);

a second resistor  $R_{\text{gain}}$  that is connected between the base of the first transistor and said reference voltage terminal and conducts a first portion of  $I_{\text{PTAT}}$ ;

a biasing current source (IS1) that is connected from the emitters of said transistors to said reference voltage terminal and supplies emitter current for said transistors; and

an offset current source  $(R_{\text{off}})$  that sinks a second portion of  $I_{\text{PTAT}}$  to set the first portion of  $I_{\text{PTAT}}$  that flows through resistor  $R_{\text{gain}}$ ,

said temperature sensor responding to  $I_{PTAT}$  by producing an output voltage  $V_o$  at said emitters that is a PTAT voltage  $V_{PTAT}$  shifted by an offset voltage  $V_{off}$ , resistor  $R_{gain}$  being selected to set  $V_{off}$  so that  $V_o$  is substantially the same as a voltage applied to said reference voltage terminal at a desired temperature.

2. The temperature sensor of claim 1, wherein said offset current source comprises a third resistor  $R_{\rm off}$  that is connected across the first transistor's base and emitter and conducts said second portion of  $I_{\rm PTAT}$ , the ratio of  $R_{\rm gain}$  to  $R_{\rm off}$  being selected to set  $V_{\rm off}$ .

5

- 3. The temperature sensor of claims 1 or 2, further comprising:

- a supply voltage terminal for receiving a supply voltage  $(\mbox{\ensuremath{V_{cc}}})\,;$  and

- a differential amplifier (A1) that is connected to the supply voltage terminal, and has a differential input that is connected to the transistors' collectors and an output that is coupled to the base of the second transistor, said differential amplifier stabilizing the temperature sensor so that the basic PTAT voltage is insensitive to changes in said supply voltage.

- 4. The temperature sensor of claims 1,2 or 3, wherein said output voltage  $V_o$  responds to centigrade temperatures from approximately zero degrees centigrade to approximately 125 degrees centigrade with a sensitivity of approximately 10mV/°C, said reference and supply voltages differing by less than 3 volts.

- 5. The temperature sensor of claims 1,2,3 or 4, wherein said reference voltage is ground reference potential.

- 6. The temperature sensor of claims 3,4 or 5, wherein said differential amplifier comprises:

- a current mirror (M1) having a current input that is connected to said supply voltage terminal, said differential input, and a current output;

- an output stage transistor (Q4) having a base that is connected to said current output and a current circuit that supplies current to resistor  $R_{\text{PTAT}}$ .

- 7. The temperature sensor of claims 3,4 or 5, further comprising:

10

5

10

15

a reference current source (IS1) that generates a reference current;

an output amplifier (A2) having a differential input that is connected to said reference current source and the collector of said first transistor, and having a current output that is connected to said first transistor's emitter, said output amplifier comparing said first transistor's collector current to said reference current to supply a drive current at said current output.

8. The temperature sensor of claim 7, wherein said first and second transistors' emitters are connected at an output node (20), said differential and output amplifiers comprising:

a current mirror (M1,M2) having a reference input that is connected to said first transistor's collector and supplies its collector current, first and second inputs that are connected to said second transistor's collector and said reference current source, respectively, and which conduct said first transistor's collector current, and first and second current outputs that supply the difference between the first and second transistors' collector currents and the difference between the first transistor's collector currents and the difference between the first transistor's collector current and said reference current, respectively;

an output stage transistor (Q4) having a base that is connected to said first current output and a current circuit that supplies current to resistor  $R_{\text{PTAT}}$ ; and

a drive transistor (Q8) having a base that is connected to said second current output and a current cir20 cuit that supplies current at said output node.

9. The temperature sensor of claim 8, wherein said output voltage  $V_{\rm o}$  responds to centigrade temperatures from approximate zero degrees centigrade to approximately 125 degrees centigrade with a sensitivity of approximately

17

5 10mV/°C, said reference voltage is ground potential and said supply voltage is less than 3 volts.

# 18 AMENDED CLAIMS

[received by the International Bureau on 29 November 1995 (29.11.95); original claims 3-6 amended; remaining claims unchanged (3 pages)].

1. A band gap temperature sensor, comprising: a first resistor R<sub>PTAT</sub>;

5

10

15

20

25

first and second transistors (Q1,Q2) having respective bases that are connected across said first resistor, collectors, and emitters that are connected together, said transistors conducting respective collector currents with different current densities which establishes a basic voltage proportional to absolute temperature (PTAT) across resistor  $R_{PTAT}$  causing a PTAT current  $I_{PTAT}$  to flow through resistor  $R_{PTAT}$ ;

a reference voltage terminal (Vee);

a second resistor  $R_{\text{gain}}$  that is connected between the base of the first transistor and said reference voltage terminal and conducts a first portion of  $I_{\text{PTAT}}$ ;

a biasing current source (IS1) that is connected from the emitters of said transistors to said reference voltage terminal and supplies emitter current for said transistors; and

an offset current source  $(R_{\text{off}})$  that sinks a second portion of  $I_{\text{PTAT}}$  to set the first portion of  $I_{\text{PTAT}}$  that flows through resistor  $R_{\text{gain}}$ ,

said temperature sensor responding to  $I_{PTAT}$  by producing an output voltage  $V_o$  at said emitters that is a PTAT voltage  $V_{PTAT}$  shifted by an offset voltage  $V_{off}$ , resistor  $R_{gain}$  being selected to set  $V_{off}$  so that  $V_o$  is substantially the same as a voltage applied to said reference voltage terminal at a desired temperature.

2. The temperature sensor of claim 1, wherein said offset current source comprises a third resistor  $R_{\text{off}}$  that is connected across the first transistor's base and emitter and conducts said second portion of  $I_{\text{PTAT}}$ , the ratio of  $R_{\text{gain}}$

5

to  $R_{\text{off}}$  being selected to set  $V_{\text{off}}$ .

- 3. The temperature sensor of claim 1, further comprising:

- a supply voltage terminal for receiving a supply voltage  $(\mbox{\ensuremath{V_{\text{CC}}}})\,;$  and

- a differential amplifier (A1) that is connected to the supply voltage terminal, and has a differential input that is connected to the transistors' collectors and an output that is coupled to the base of the second transistor, said differential amplifier stabilizing the temperature sensor so that the basic PTAT voltage is insensitive to changes in said supply voltage.

- 4. The temperature sensor of claim 1, wherein said output voltage  $V_o$  responds to centigrade temperatures from approximately zero degrees centigrade to approximately 125 degrees centigrade with a sensitivity of approximately  $10\text{mV/}^\circ\text{C}$ , said reference and supply voltages differing by less than 3 volts.

- 5. The temperature sensor of claim 1, wherein said reference voltage is ground reference potential.

- 6. The temperature sensor of claim 3, wherein said differential amplifier comprises:

- a current mirror (M1) having a current input that is connected to said supply voltage terminal, said differential input, and a current output;

- an output stage transistor (Q4) having a base that is connected to said current output and a current circuit that supplies current to resistor  $R_{\text{PTAT}}$ .

- 7. The temperature sensor of claims 3,4 or 5, further comprising:

- a reference current source (IS1) that generates a

10

5

10

15

5

reference current;

- an output amplifier (A2) having a differential input that is connected to said reference current source and the collector of said first transistor, and having a current output that is connected to said first transistor's emitter, said output amplifier comparing said first transistor's collector current to said reference current to supply a drive current at said current output.

- 8. The temperature sensor of claim 7, wherein said first and second transistors' emitters are connected at an output node (20), said differential and output amplifiers comprising:

- a current mirror (M1,M2) having a reference input that is connected to said first transistor's collector and supplies its collector current, first and second inputs that are connected to said second transistor's collector and said reference current source, respectively, and which conduct said first transistor's collector current, and first and second current outputs that supply the difference between the first and second transistors' collector currents and the difference between the first transistor's collector current and said reference current, respectively;

- an output stage transistor (Q4) having a base that is connected to said first current output and a current circuit that supplies current to resistor  $R_{\text{PTAT}}$ ; and

- a drive transistor (Q8) having a base that is connected to said second current output and a current 20 circuit that supplies current at said output node.

- 9. The temperature sensor of claim 8, wherein said output voltage  $V_o$  responds to centigrade temperatures from approximate zero degrees centigrade to approximately 125 degrees centigrade with a sensitivity of approximately 10mV/°C, said reference voltage is ground potential and said supply voltage is less than 3 volts.

FIG.2

FIG. 5

#### INTERNATIONAL SEARCH REPORT

International application No. PCT/US95/11320

| ł                                                                                                                                                                                                                                             | SSIFICATION OF SUBJECT MATTER<br>:G05F 3/30, 1/567                                                    |                                                                                                                                                                              |                        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|

|                                                                                                                                                                                                                                               | : 327/513, 512, 539; 307/651; 374/178; 323/313 o International Patent Classification (IPC) or to both | national classification and IPC                                                                                                                                              |                        |  |  |

| B. FIEI                                                                                                                                                                                                                                       | DS SEARCHED                                                                                           |                                                                                                                                                                              |                        |  |  |

| Minimum d                                                                                                                                                                                                                                     | ocumentation searched (classification system followed                                                 | d by classification symbols)                                                                                                                                                 |                        |  |  |

| U.S. :                                                                                                                                                                                                                                        | 327/513, 512, 539; 307/651; 374/178, 163, 180, 18                                                     | 3; 323/313                                                                                                                                                                   |                        |  |  |

| Documentat                                                                                                                                                                                                                                    | ion searched other than minimum documentation to the                                                  | e extent that such documents are included                                                                                                                                    | in the fields searched |  |  |

|                                                                                                                                                                                                                                               | lata base consulted during the international search (na<br>ee Extra Sheet.                            | ame of data base and, where practicable                                                                                                                                      | , search terms used)   |  |  |

| C. DOC                                                                                                                                                                                                                                        | UMENTS CONSIDERED TO BE RELEVANT                                                                      |                                                                                                                                                                              |                        |  |  |

| Category*                                                                                                                                                                                                                                     | Citation of document, with indication, where ap                                                       | opropriate, of the relevant passages                                                                                                                                         | Relevant to claim No.  |  |  |

| A, P                                                                                                                                                                                                                                          | US, A, 5,430,395 (ICHIMARU) 04                                                                        | 1 July 1995, Fig. 1                                                                                                                                                          | NONE                   |  |  |

| A                                                                                                                                                                                                                                             | US, A, 4,797,577 (HING) 10 Janu                                                                       | uary 1989, Fig. 1                                                                                                                                                            | NONE                   |  |  |

| A                                                                                                                                                                                                                                             | US, A, 4,683,416 (BYNUM) 28 J                                                                         | NONE                                                                                                                                                                         |                        |  |  |

| A                                                                                                                                                                                                                                             | US, A, 4,652,144 (GUNTHER ET 2                                                                        | AL.) 24 March 1987, Fig.                                                                                                                                                     | NONE                   |  |  |

| A                                                                                                                                                                                                                                             | US, A, 4,497,586 (NELSON) 05 F                                                                        | February 1985, Fig. 5                                                                                                                                                        | NONE                   |  |  |

|                                                                                                                                                                                                                                               |                                                                                                       |                                                                                                                                                                              |                        |  |  |

|                                                                                                                                                                                                                                               |                                                                                                       |                                                                                                                                                                              |                        |  |  |

| Furth                                                                                                                                                                                                                                         | ner documents are listed in the continuation of Box C                                                 | . See patent family annex.                                                                                                                                                   |                        |  |  |

| * Special categories of cited documents:  "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |                                                                                                       |                                                                                                                                                                              |                        |  |  |

|                                                                                                                                                                                                                                               | be of particular relevance<br>rlier document published on or after the international filing date      | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone |                        |  |  |

| "L" do<br>cit<br>spe                                                                                                                                                                                                                          | te claimed invention cannot be                                                                        |                                                                                                                                                                              |                        |  |  |

| "O" document referring to an oral disclosure, use, exhibition or other combined with one or more other such documents, such being obvious to a person skilled in the art                                                                      |                                                                                                       |                                                                                                                                                                              |                        |  |  |

| "P" document published prior to the international filing date but later than "&" document member of the same patent family the priority date claimed                                                                                          |                                                                                                       |                                                                                                                                                                              |                        |  |  |

| Date of the actual completion of the international search  O1 NOVEMBER 1995  Date of mailing of the international search  1 3 NOV 1995                                                                                                        |                                                                                                       |                                                                                                                                                                              |                        |  |  |

|                                                                                                                                                                                                                                               | nailing address of the ISA/US                                                                         | Authorized officer                                                                                                                                                           |                        |  |  |

| Commissio<br>Box PCT                                                                                                                                                                                                                          | n, D.C. 20231                                                                                         | TERRY L. ENGLUND                                                                                                                                                             | e oulusi)              |  |  |

| Facsimile N                                                                                                                                                                                                                                   |                                                                                                       | Telephone No. (703)308-4817                                                                                                                                                  |                        |  |  |

# INTERNATIONAL SEARCH REPORT

International application No. PCT/US95/11320

| Box I Observations where certain claims were found unsearchable (Continuation of item 1 of first sheet)                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This international report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:                                                                                             |

| 1. Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:                                                                                                                  |

|                                                                                                                                                                                                                               |

| 2. Claims Nos.: because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically: |

|                                                                                                                                                                                                                               |

| 3. X Claims Nos.: 4 - 9 because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).                                                                               |

| Box II Observations where unity of invention is lacking (Continuation of item 2 of first sheet)                                                                                                                               |

| This International Searching Authority found multiple inventions in this international application, as follows:                                                                                                               |

|                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                               |

| 1. As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.                                                                                   |

| 2. As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.                                                                       |

| 3. As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:                       |

|                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                               |

| 4. No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:           |

| Remark on Protest                                                                                                                                                                                                             |

| No protest accompanied the payment of additional search fees.                                                                                                                                                                 |

# INTERNATIONAL SEARCH REPORT

International application No. PCT/US95/11320

| APS earch terms: temperature sensor, offset, proportional to absolute temperature, PTAT, bandgap, bipolar, offset resistor, |  |  |   |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--|--|---|--|--|--|--|

| offset voltage, programmable offset                                                                                         |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  | • |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

| •                                                                                                                           |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |

|                                                                                                                             |  |  |   |  |  |  |  |