(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6713708号

(P6713708)

(45) 発行日 令和2年6月24日(2020.6.24)

(24) 登録日 令和2年6月8日(2020.6.8)

(51) Int.Cl.

F 1

|        |        |           |

|--------|--------|-----------|

| HO 1 L | 21/76  | (2006.01) |

| HO 1 L | 21/336 | (2006.01) |

| HO 1 L | 29/78  | (2006.01) |

| HO 1 L | 27/088 | (2006.01) |

|        |        |      |

|--------|--------|------|

| HO 1 L | 21/76  | L    |

| HO 1 L | 29/78  | 301D |

| HO 1 L | 27/088 | 331A |

| HO 1 L | 29/78  | 301R |

請求項の数 11 (全 26 頁)

(21) 出願番号 特願2016-527088 (P2016-527088)

(86) (22) 出願日 平成26年7月17日 (2014.7.17)

(65) 公表番号 特表2016-528730 (P2016-528730A)

(43) 公表日 平成28年9月15日 (2016.9.15)

(86) 國際出願番号 PCT/US2014/046955

(87) 國際公開番号 WO2015/009891

(87) 國際公開日 平成27年1月22日 (2015.1.22)

審査請求日 平成29年7月5日 (2017.7.5)

(31) 優先権主張番号 13/944,864

(32) 優先日 平成25年7月17日 (2013.7.17)

(33) 優先権主張国・地域又は機関

米国(US)

前置審査

(73) 特許権者 390020248

日本テキサス・インスツルメンツ合同会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

(72) 発明者 田村 剛仁

日本国 272-0835 市川市中国分

4-12-20

最終頁に続く

(54) 【発明の名称】深いトレンチ隔離構造を備えた半導体構造の方法及び半導体構造

## (57) 【特許請求の範囲】

## 【請求項1】

半導体構造であって、

第1の導電型を有し、頂部表面を有する基板と、

前記第1の導電型を有し、前記基板の前記頂部表面に接する底部表面と、頂部表面とを

有する、エピタキシャル層と、

第2の導電型を有する埋め込み領域であって、前記エピタキシャル層の一部に接してそ

の下に位置する、前記埋め込み領域と、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在する深いト

レンチ隔離構造と、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在して前記深い

トレンチ隔離構造を横方向に囲む内側の深いトレンチ隔離構造と、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在して前記内側

の深いトレンチ隔離構造を横方向に囲む外側の深いトレンチ隔離構造と、

前記第2の導電型を有し、前記埋め込み領域に接するに前記エピタキシャル層の前

記頂部表面から前記エピタキシャル層内へ延在して前記内側及び外側の深いトレンチ隔離

構造の下に延在するドープされた領域であって、前記内側及び外側の深いトレンチ隔離構

造に接し、前記エピタキシャル層の前記一部を横方向に囲む、前記ドープされた領域と、

前記第2の導電型を有し、前記頂部表面において形成されるインターフェース領域であ

って、前記ドープされた領域に接して前記内側の深いトレンチ隔離構造を囲み、前記ドー

づされた領域のドーパント濃度よりも低いドーパント濃度を有する、前記インターフェース領域と、

を含む、半導体構造。

【請求項 2】

請求項 1 に記載の半導体構造であって、

前記インターフェース領域が前記内側の深いトレンチ隔離構造に接する、半導体構造。

【請求項 3】

請求項 1 に記載の半導体構造であって、

前記第 1 の導電型を有し、前記浅いトレンチ隔離構造に接するチャネルトップ領域を更に含み、前記内側の深いトレンチ隔離構造が前記チャネルトップ領域を横方向に囲む、半導体構造。10

【請求項 4】

請求項 1 に記載の半導体構造であって、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在して前記外側の深いトレンチ隔離構造を横方向に囲む絶縁の深いトレンチ構造を更に含み、

前記絶縁の深いトレンチ構造と前記外側の深いトレンチ隔離構造とが実質的に等しい深度を有する、半導体構造。

【請求項 5】

請求項 1 に記載の半導体構造であって、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在する絶縁の深いトレンチ構造を更に含み、20

前記内側の深いトレンチ隔離構造が前記絶縁の深いトレンチ構造を横方向に囲み、前記絶縁の深いトレンチ構造と前記内側の深いトレンチ隔離構造とが実質的に等しい深度を有する、半導体構造。

【請求項 6】

請求項 1 に記載の半導体構造であって、

前記エピタキシャル層の前記一部に形成され、前記第 2 の導電型を有するソースと、

前記エピタキシャル層の前記一部に形成され、前記ソースから横方向に離間され、前記第 2 の導電型を有するドレインと、

を更に含み、30

前記浅いトレンチ隔離構造が前記ソースと前記ドレインとの間に横方向に位置する、半導体構造。

【請求項 7】

請求項 1 に記載の半導体構造であって、

前記インターフェース領域が、前記外側の深いトレンチ隔離構造に接して前記外側の深いトレンチ隔離構造を横方向に囲む、半導体構造。

【請求項 8】

半導体構造を形成する方法であって、

基板に埋め込み領域を形成することであって、前記基板が第 1 の導電型を有し、前記埋め込み領域が第 2 の導電型を有する、前記埋め込み領域を形成することと、40

前記基板上にエピタキシャル層を成長させることであって、前記エピタキシャル層が頂部表面を有して前記第 1 の導電型を有し、前記埋め込み領域が前記エピタキシャル層の一部に接してその下に位置する、前記エピタキシャル層を成長させることと、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在する浅いトレンチ隔離構造を形成することと、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在して前記浅いトレンチ隔離構造を横方向に囲む内側の深いトレンチ隔離構造を形成することと、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在して前記内側の深いトレンチ隔離構造を横方向に囲む外側の深いトレンチ隔離構造を形成することと、

前記第 2 の導電型を有し、前記埋め込み領域に接するために前記エピタキシャル層の前50

記頂部表面から前記エピタキシャル層内へ延在して前記内側及び外側の深いトレンチ隔離構造の下に延在するドープされた領域を形成することであって、前記ドープされた領域が、前記内側及び外側の深いトレンチ隔離構造に接し、前記エピタキシャル層の前記一部を横方向に囲む、前記ドープされた領域を形成することと、

前記第2の導電型を有するインターフェース領域を前記頂部表面において形成することであって、前記インターフェース領域が、前記ドープされた領域に接して前記内側の深いトレンチ隔離構造を囲み、前記インターフェース領域が、前記ドープされた領域のドーパント濃度よりも低いドーパント濃度を有する、前記インターフェース領域を形成することと、

を含む、方法。

10

【請求項9】

請求項8に記載の方法であって、

前記ドープされた領域を形成すること、が前記第2の導電型の複数の離間した領域を形成することを含み、前記第2の導電型の前記複数の離間した領域が、前記内側及び外側の深いトレンチ隔離構造に接し、前記内側及び外側の深いトレンチ隔離構造の間に位置する、方法。

【請求項10】

請求項8に記載の方法であって、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在して前記外側の深いトレンチ隔離構造を横方向に囲む絶縁の深いトレンチ構造を形成することを更に含み、

20

前記絶縁の深いトレンチ構造と前記外側の深いトレンチ隔離構造とが実質的に等しい深さを有する、方法。

【請求項11】

請求項8に記載の方法であって、

前記エピタキシャル層の前記頂部表面から前記エピタキシャル層内へ延在する絶縁の深いトレンチ構造を形成することを更に含み、

前記内側の深いトレンチ隔離構造が前記絶縁の深いトレンチ構造を横方向に囲み、前記絶縁の深いトレンチ構造と前記内側の深いトレンチ隔離構造とが実質的に等しい深さを有する、方法。

30

【発明の詳細な説明】

【技術分野】

【0001】

本願は、一般に半導体構造に関し、特に、深いトレンチ隔離構造を備えた半導体構造及び深いトレンチ隔離構造を備えた半導体構造を形成する方法に関する。

【背景技術】

【0002】

金属酸化物半導体(MOS)トランジスタは、nチャネル(NMOS)デバイス又はpチャネル(PMOS)デバイスのいずれかとして実装され得る、周知の半導体デバイスである。MOSトランジスタは、チャネルによって分離された離間されたソース領域及びドレイン領域、並びにチャネルの上にある金属ゲートを有する。金属ゲートは、ゲート誘電体層によってチャネルから絶縁される。代替として、MOSトランジスタのゲートは、金属の代わりにドープポリシリコンを用いて形成される。

40

【0003】

二重拡散MOS(DOMS)トランジスタは、チャネルを形成する二重拡散ウェル、並びに、チャネルと重くドープされたドレイン領域との間にあり、ドレインドリフト領域と呼ばれる軽くドープされたドレイン領域を有するパワーMOSトランジスタである。横方向DMOS(LDMOS)トランジスタは、ソース領域及びドレイン領域が横方向に離間されたDMOSトランジスタである。LDMOSアレイは、行及び列のアレイなどのパターンに配されるLDMOSトランジスタのグループである。

50

## 【0004】

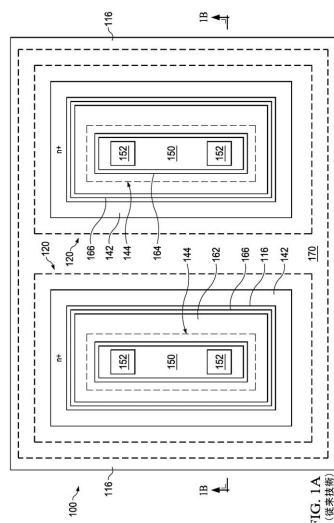

図1A及び図1Bは、従来のLDMOSトランジスタアレイ100の図を示す。図1Aは平面図を示し、図1Bは図1Aの線1B-1Bに沿った断面図を示す。図1A及び図1Bに示されるように、LDMOSトランジスタアレイ100は、p型単結晶シリコン基板領域112と、基板領域112の上に成長されるp型エピタキシャル層114とを有する半導体構造110を含む。また、半導体構造110は、エピタキシャル層114へ下方に延在するようにエピタキシャル層114の頂部表面において形成される、いくつかの浅いトレンチ隔離構造116を含む。

## 【0005】

図1A及び図1Bに示されるように、LDMOSトランジスタアレイ100は更に、エピタキシャル層114に形成される近接するLDMOSトランジスタ120のペアを含む。各LDMOSトランジスタ120は、エピタキシャル層114に形成されるn-ドレインドリフト領域140と、n-ドレインドリフト領域140に形成されるn+ドレイン142とを含む。

10

## 【0006】

また、各LDMOSトランジスタ120は、エピタキシャル層114に形成される二重拡散ウェル(Dウェル)144を含む。Dウェル144は、p型領域146と、p型領域146に接するn型領域148とを含む。各LDMOSトランジスタ120は更に、エピタキシャル層114に形成される、n+ソース150及びp+コンタクト領域152を含む。n+ソース150は、p型領域146及びn型領域148に接する。n+ソース150によって横方向に囲まれるp+コンタクト領域152は、p型領域146及びn+ソース150に接する。

20

## 【0007】

n-ドレインドリフト領域140に接するp型領域146は、n-ドレインドリフト領域140とn型領域148との間にあるチャネル領域154を含む。n+ドレイン142から離間されるp型領域146はまた、エピタキシャル層114のドーパント濃度より高いドーパント濃度を有する。また、n+ソース150はn+ドレイン142から横方向に離間される。また、n+ドレイン142は、ドレイン142とソース150との間で横方向にある浅いトレンチ隔離構造116に接する。

## 【0008】

30

図1A及び図1Bに示されるように、各LDMOSトランジスタ120は、チャネル領域154に接しチャネル領域154の上にあるゲート誘電体構造160と、ゲート誘電体構造160に接しチャネル領域154の上にあるゲート162とを含む。ゲート162は、四角に角がある円形の形状を有する。また、各LDMOSトランジスタ120は、ゲート162に接する内部側壁スペーサ164と、ゲート162に接しゲート162を横方向に囲む外部側壁スペーサ166とを含む。

## 【0009】

図1A及び図1Bに示されるように、半導体構造110は、近接するLDMOSトランジスタ120のn-ドレインドリフト領域140の間のエピタキシャル層114にチャネルストップとして形成される、p型領域170を含む。チャネルストップ領域170は、LDMOSトランジスタ120の各々を横方向に囲む。

40

## 【0010】

動作において、LDMOSトランジスタ120のn+ドレイン142に第1の正電圧(40Vなど)がかけられ、(p+コンタクト領域152を介して)p型領域146に及びn+ソース領域150に接地が設けられる場合、LDMOSトランジスタ120は、ゲート162に接地が設けられたときオフになる。この場合、電子がn+ソース150からn+ドレイン142へ流れることはない。

## 【0011】

LDMOSトランジスタ120は、ゲート162に第2の正電圧( $V_{GS} > V_{TH}$ など)がかけられるときオンになるが、残りのバイアス条件は維持される。この場合、p型領

50

域 146 のチャネル領域 154 は反転し、電子が n+ ソース 150 からチャネル領域 154 を介して n+ ドレイン 142 へ流れる。

【 0012 】

LDMOS ランジスタアレイ 100 に伴う 1 つの問題は、その LDMOS ランジスタ 120 が、必要な電気的隔離を提供するために大幅な横方向の分離及びシリコン実装面積を必要とすることである。例えば、40V 隔離は、しばしば、近接する LDMOS ランジスタ 120 の n- ドレインドリフト領域 140 間に、5.65 μm の最小横方向間隔を必要とする。

【 0013 】

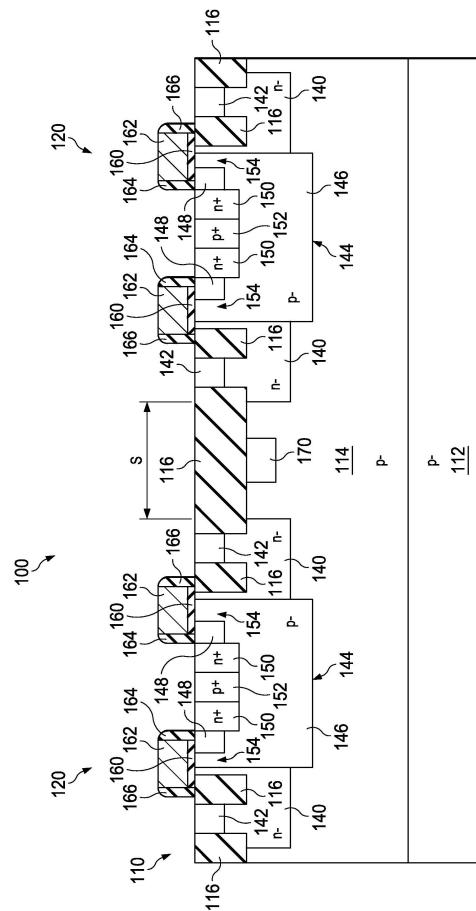

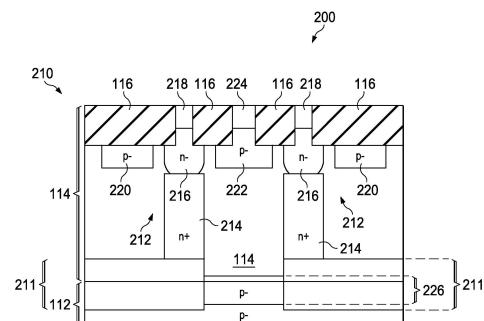

図 2A 及び図 2B は、従来の LDMOS ランジスタアレイ 200 の図を示す。図 2A 10 は平面図を示し、図 2B は図 2A の線 2B-2B に沿った断面図を示す。LDMOS ランジスタアレイ 200 は LDMOS ランジスタアレイ 100 と同様であるため、両方のランジスタアレイに共通の構造を指示するために同じ参照番号を使用している。

【 0014 】

図 2A 及び図 2B に示されるように、LDMOS ランジスタアレイ 200 は、半導体構造 110 の代わりに半導体構造 210 を用いるため、LDMOS ランジスタアレイ 200 は LDMOS ランジスタアレイ 100 とは異なる。半導体構造 210 は、半導体構造 210 が更に、基板領域 112 の頂部及びエピタキシャル層 114 の底部に形成されるいくつかの n+ 埋め込み層 211 を含むことを除いて、半導体構造 110 と同じである。

【 0015 】

半導体構造 210 はまた、半導体構造 210 がエピタキシャル層 114 に形成されるいくつかの n 型接合隔離領域 212 を含むため、半導体構造 110 と異なる。各接合隔離領域 212 は、n+ 埋め込み層 211 に接し n+ 埋め込み層 211 の上に位置するようにエピタキシャル層 114 に形成される n+ 底部領域 214 を含む。また、各接合隔離領域 212 は、n+ 底部領域 214 に接し n+ 底部領域 214 の上に位置するようにエピタキシャル層 114 に形成される n- 頂部領域 216 と、n- 頂部領域 216 に形成される n+ コンタクト領域 218 とを含む。

【 0016 】

半導体構造 210 はまた、半導体構造 210 がエピタキシャル層 114 に形成されるいくつかの p 型チャネルストップ領域 220 を含むため、半導体構造 110 と異なる。各チャネルストップ領域 220 は、n- ドレインドリフト領域 140 と接合隔離領域 212 との間に位置する。

【 0017 】

図 2A 及び図 2B に示されるように、半導体構造 210 はまた、近接する LDMOS ランジスタ 120 の n- 頂部領域 216 間のエピタキシャル層 114 にチャネルストップとして形成される、p 型ウェル領域 222 を含む。また、LDMOS ランジスタアレイ 200 は、p 型ウェル領域 222 に形成される p+ コンタクト領域 224 を含む。

【 0018 】

LDMOS ランジスタアレイ 200 は更に、近接する n+ 埋め込み層 211 間に横方向に位置するように、基板 112 及びエピタキシャル層 114 に形成される p- 埋め込み領域 226 を含む。p- 埋め込み領域 226 は、p 型基板 112 のドーパント濃度よりわずかに高いドーパント濃度を有し、近接する n+ 埋め込み層 211 間の横方向間隔を最小化するのを助ける。

【 0019 】

LDMOS ランジスタアレイ 200 は、LDMOS ランジスタアレイ 200 の各埋め込み層 211 及び接合隔離領域 212 がエピタキシャル層 114 の一部を囲み、エピタキシャル層 114 の残りの部分から接合隔離することを除いて、LDMOS ランジスタアレイ 100 と同様に動作する。30V 以下の動作をサポートするために、p- 埋め込み領域 226 は、図 2B に示されるように近接する n+ 埋め込み層 211 に接することが可能である。しかしながら、40V 動作をサポートするために、n+ 埋め込み層 211 と p 50

- 埋め込み領域 226 との間の接合破壊制限のため、p - 埋め込み領域 226 は近接する n + 埋め込み層 211 から横方向に離間される。

【0020】

LDMOSトランジスタアレイ100と同様、LDMOSトランジスタアレイ200に伴う1つの問題は、必要な電気的隔離を提供するために大幅なシリコン実装面積を必要とすることである。n + 底部領域214を形成するために注入されたドーパントがドライブイン(driven in)されるとき、n + 底部領域214はドーパントの実質的に横方向の拡散を経験する。したがって、必要とするシリコン実装面積がより少ないLDMOSトランジスタアレイが求められている。

【発明の概要】

10

【0021】

説明される例において、半導体構造が、基板及びエピタキシャル層を含む。基板は第1の導電型及び頂部表面を有する。エピタキシャル層は、第1の導電型、基板の頂部表面に接する底面、及び頂部表面を有する。埋め込み領域が第2の導電型を有する。埋め込み領域は、エピタキシャル層の一部に接しエピタキシャル層の一部の下に位置する。浅いトレンチ隔離構造が、エピタキシャル層へ下方に延在するように、エピタキシャル層の頂部表面において形成される。内側の深いトレンチ隔離構造が、エピタキシャル層へ下方に延在するように、エピタキシャル層の頂部表面において形成される。内側の深いトレンチ隔離構造は、浅いトレンチ隔離構造を横方向に囲む。外側の深いトレンチ隔離構造が、エピタキシャル層へ下方に延在するように、エピタキシャル層の頂部表面において形成される。外側の深いトレンチ隔離構造は、内側の深いトレンチ隔離構造を横方向に囲む。ドープ領域が、エピタキシャル層へ下方に延在し、埋め込み領域に接するように、エピタキシャル層の頂部表面において形成される。ドープ領域は、第2の導電型を有し、内側及び外側の深いトレンチ隔離構造に接し、エピタキシャル層の一部を横方向に囲む。

20

【図面の簡単な説明】

【0022】

【図1A】従来のLDMOSトランジスタアレイを示す図である。

【図1B】従来のLDMOSトランジスタアレイを示す図である。

【0023】

【図2A】従来のLDMOSトランジスタアレイを示す図である。

30

【図2B】従来のLDMOSトランジスタアレイを示す図である。

【0024】

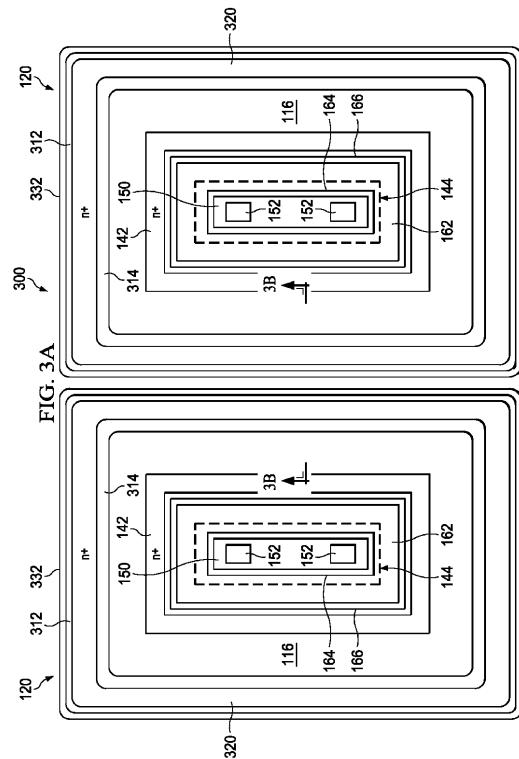

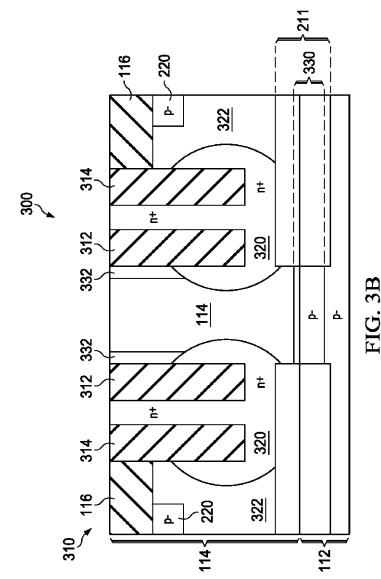

【図3A】例示の実施形態のLDMOSトランジスタアレイを示す図である。

【図3B】例示の実施形態のLDMOSトランジスタアレイを示す図である。

【0025】

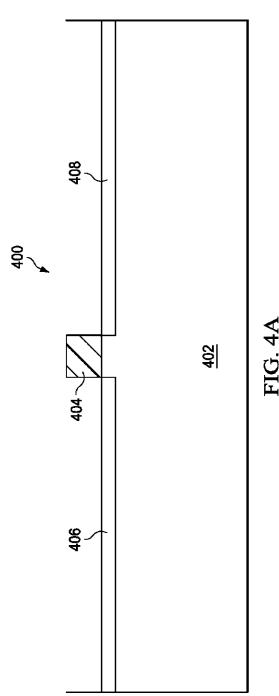

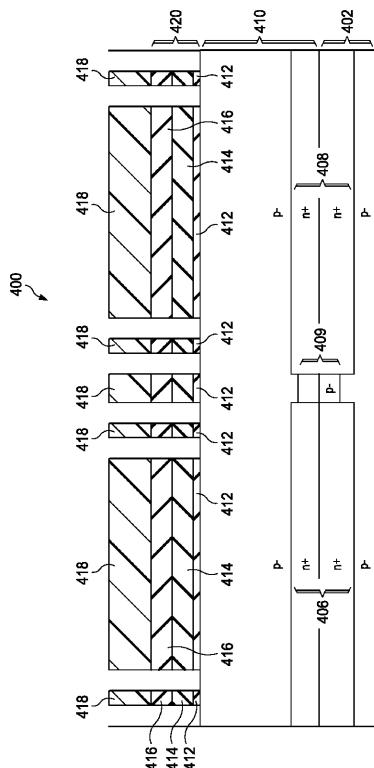

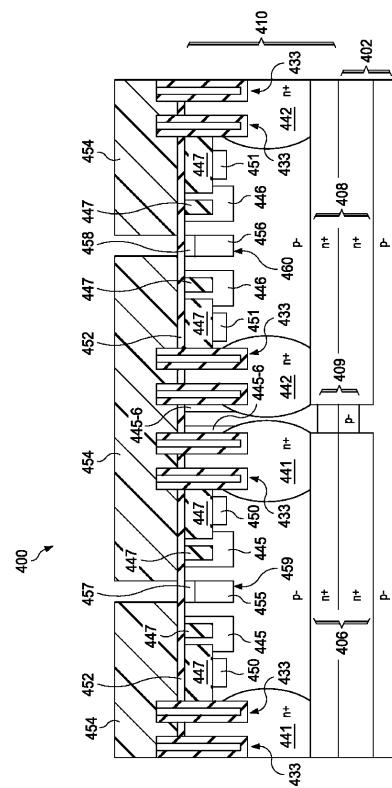

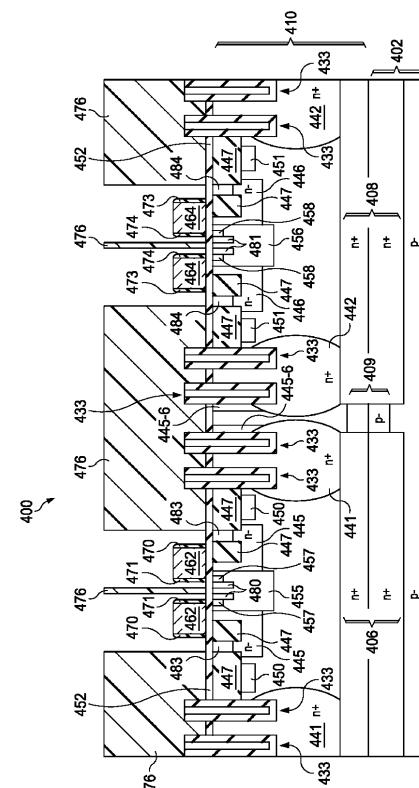

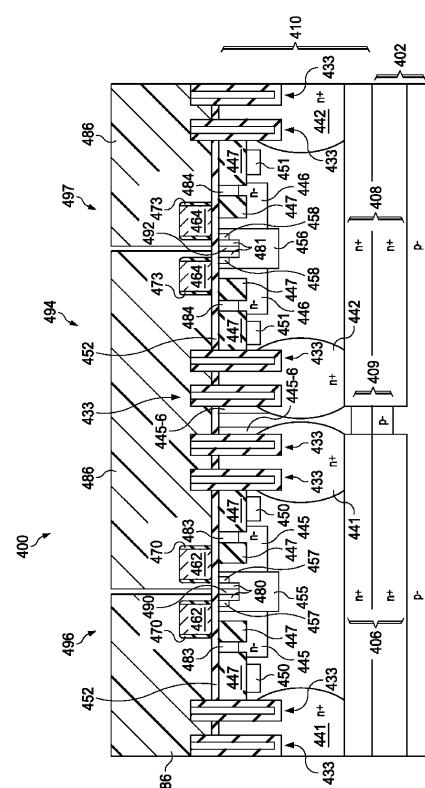

【図4A】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

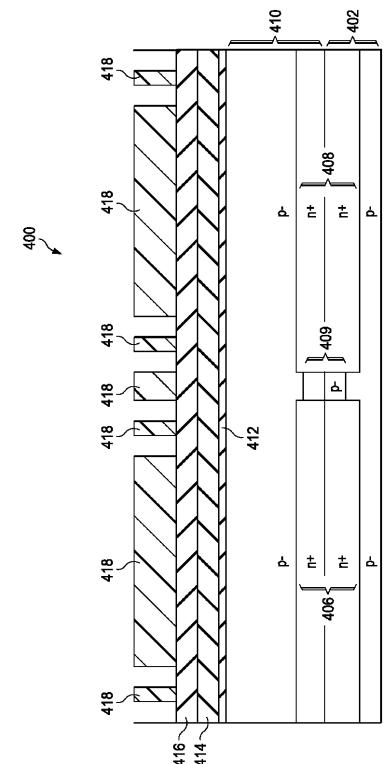

【図4B】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4C】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

40

【図4D】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4E】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4F】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4G】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4H】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図

50

である。

【図4 I】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4 J】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4 K】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4 L】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。

【図4 M】例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す断面図である。 10

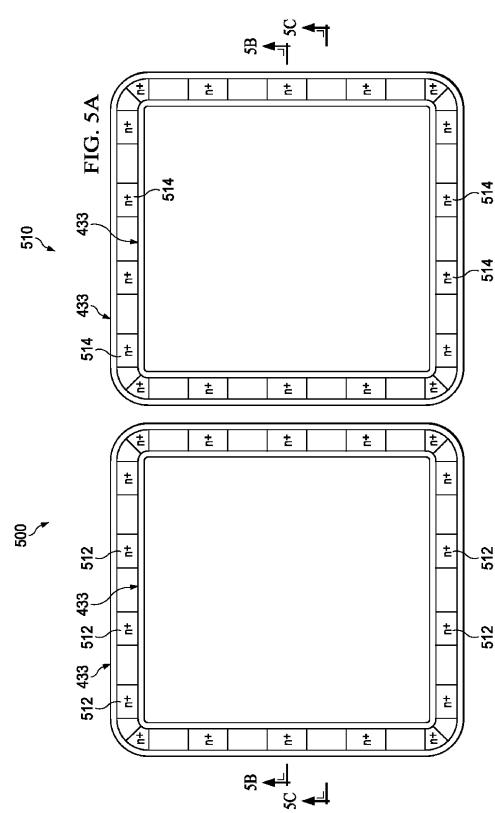

【0026】

【図5 A】別の例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す図である。

【図5 B】別の例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す図である。

【図5 C】別の例示の実施形態のLDMOSトランジスタアレイを形成する方法を示す図である。

【0027】

【図6 A】別の例示の実施形態のLDMOSトランジスタアレイを示す図である。 20

【図6 B】別の例示の実施形態のLDMOSトランジスタアレイを示す図である。

【0028】

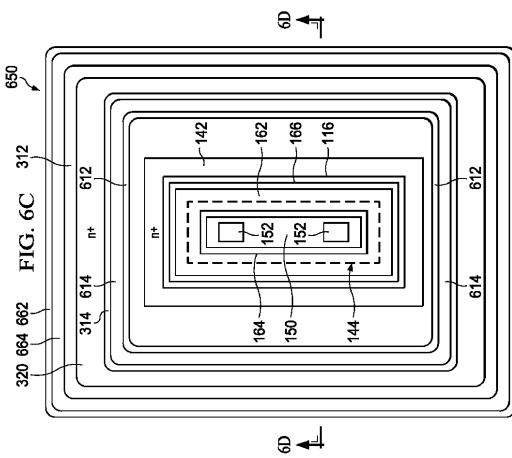

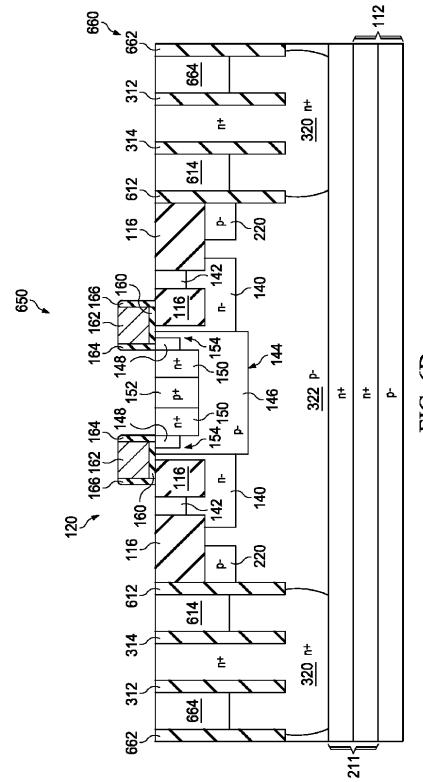

【図6 C】別の例示の実施形態のLDMOSトランジスタアレイを示す図である。

【図6 D】別の例示の実施形態のLDMOSトランジスタアレイを示す図である。

【0029】

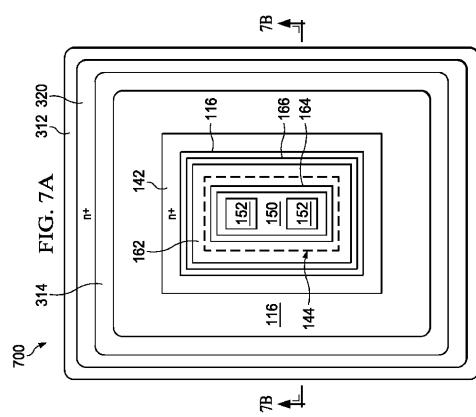

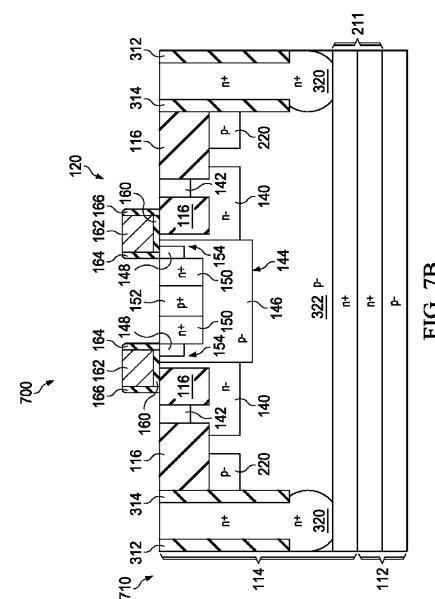

【図7 A】別の例示の実施形態のLDMOSトランジスタアレイを示す図である。

【図7 B】別の例示の実施形態のLDMOSトランジスタアレイを示す図である。

【0030】

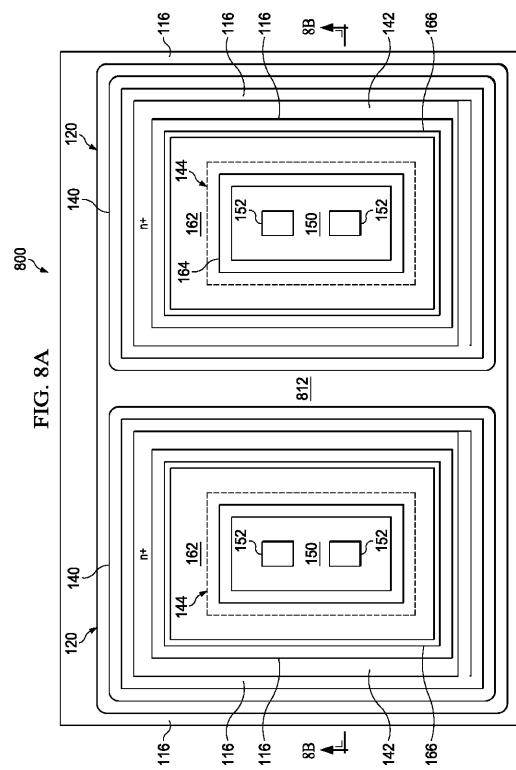

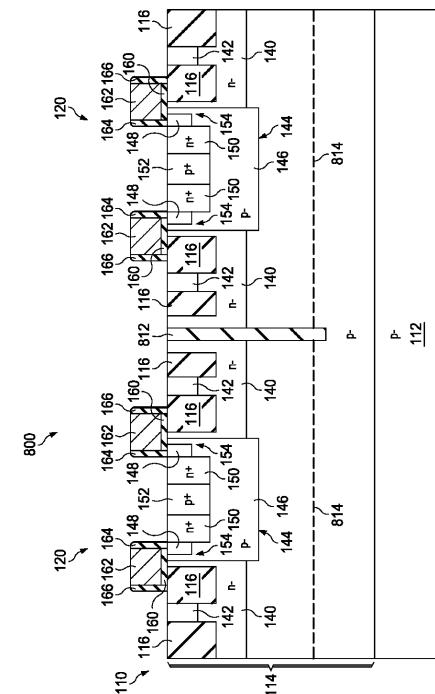

【図8 A】例示の実施形態のLDMOSトランジスタアレイを示す図である。

【図8 B】例示の実施形態のLDMOSトランジスタアレイを示す図である。 30

【発明を実施するための形態】

【0031】

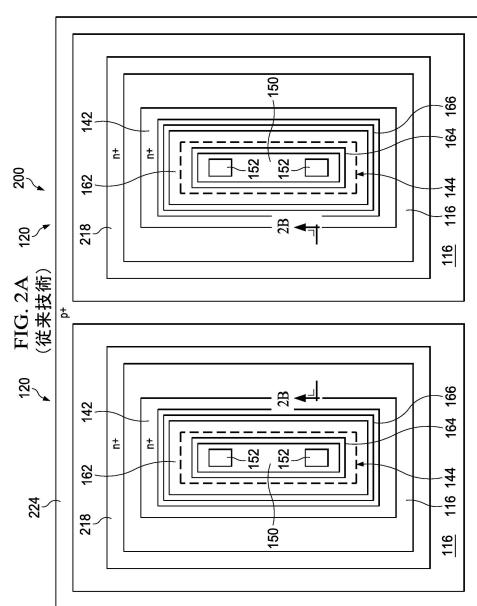

図3 A及び図3 Bは、例示の実施形態のLDMOSトランジスタアレイ300を示す。図3 Aは平面図を示し、図3 Bは図3 Aの線3B-3Bに沿った断面図を示す。以下でより詳細に説明するように、LDMOSトランジスタ300は、必要なシリコン実装面積が従来のLDMOSトランジスタより少ない。

【0032】

LDMOSトランジスタアレイ300はLDMOSトランジスタアレイ200と同様であるため、両方のトランジスタに共通の構造を指示するために同じ参照番号を使用している。図3 A及び図3 Bに示されるように、LDMOSトランジスタアレイ300は、半導体構造210の代わりに半導体構造310を用いるため、LDMOSトランジスタアレイ300はLDMOSトランジスタアレイ200とは異なる。 40

【0033】

半導体構造310は、半導体構造310が、エピタキシャル層114へ下方に延在するようにエピタキシャル層114の頂部表面において形成される、いくつかの外側の深いトレンチ隔離構造312及びいくつかの内側の深いトレンチ隔離構造314も含むことを除いて、半導体構造210と同じである。外側及び内側の深いトレンチ隔離構造312及び314は、浅いトレンチ隔離構造116より著しく深い深さを有する。また、図3 Aに示されるように、外側及び内側の深いトレンチ隔離構造312及び314は丸い角を有する。丸い角は、外側及び内側の深いトレンチ隔離構造312及び314からの応力を最小化 50

する。

【0034】

半導体構造310はまた、接合隔離領域212の代わりにいくつかのn型接合隔離領域320を用いるため、半導体構造210と異なる。この例において、各接合隔離領域320は、n+底部領域214、n-頂部領域216、及びn+コンタクト領域218の代わりに、単一のn+領域を用いるため、接合隔離領域320は接合隔離領域212とは異なる。各接合隔離領域320は、外側及び内側の深いトレンチ隔離構造312及び314のペアに接し、それらの間に位置する。

【0035】

各埋め込み層211は、エピタキシャル層114のいくつかの部分322のうちの1つに接し且つその下に位置し、各部分322は、ドレインドリフト領域140、Dウェル144、及びいくつかの浅いトレンチ隔離構造116を含む。また、埋め込み層211に接する各接合隔離領域320は、エピタキシャル層114の一部322を横方向に囲む。したがって、埋め込み層211及び接合隔離領域320を含むn型領域が、充分にエピタキシャル層114の一部322とエピタキシャル層114の残りの部分との間に位置する。

【0036】

また、外側の深いトレンチ隔離構造312は、エピタキシャル層114の一部322及び内側の深いトレンチ隔離構造314を横方向に囲む。内側の深いトレンチ隔離構造314は、いくつかの浅いトレンチ隔離構造116を横方向に囲む。図3A及び図3Bに示されるように、近接する接合隔離領域320は、p型エピタキシャル層114の一部によって互いから横方向に離間される。

【0037】

LD MOSトランジスタアレイ300はまた、近接するn+埋め込み層211間に横方向に位置するように基板112及びエピタキシャル層114に形成される、p-埋め込み領域330を含む。p-埋め込み領域330は、p型基板112のドーパント濃度よりわずかに高いドーパント濃度を有する。また、p-埋め込み領域330は、40V以下の動作について図3Bに示されるように、近接するn+埋め込み層211に接し得る。

【0038】

図3A及び図3Bに示されるように、トランジスタアレイ300は、任意選択で、外側の深いトレンチ隔離構造312を各n-インターフェース領域332が横方向に囲むように、エピタキシャル層114に形成されるいくつかのn-インターフェース領域332を含み得る。n-インターフェース領域332は、各々がn型接合隔離領域320のドーパント濃度より低いドーパント濃度を有し、40V動作のため、及び、シリコンと酸化物との間のインターフェースでのホットキャリアトラッピングを回避するために、必要とされ得る。LD MOSトランジスタアレイ300がLD MOSトランジスタアレイ200より大きな横方向隔離を提供することを除いて、LD MOSトランジスタアレイ300はLD MOSトランジスタアレイ200と同様に動作する。

【0039】

図3Bに示されるように、外側及び内側の深いトレンチ隔離構造312及び314より下に位置する接合隔離領域320の部分は、外側及び内側の深いトレンチ隔離構造312及び314の間にある接合隔離領域320の部分より幅広い可能性がある。外側及び内側の深いトレンチ隔離構造312及び314は、ドーパントの横方向拡散を排除しない可能性があるが、外側及び内側の深いトレンチ隔離構造312及び314は、ドーパントの横方向拡散を実質的に抑制する。

【0040】

したがって、アレイ300における近接するLD MOSトランジスタ120間の最小横方向間隔は、アレイ200における近接するLD MOSトランジスタ120間の最小横方向間隔よりも著しく小さい。例えば、アレイ200における近接するLD MOSトランジスタ120のための20V隔離はしばしば7μmの最小横方向間隔を必要とするが、アレイ300における近接するLD MOSトランジスタ120のための20V隔離は5.2μ

10

20

30

40

50

mの最小横方向間隔を用いることが可能であり、これは26%の削減である。

【0041】

同様に、アレイ200における近接するLDMOSトランジスタ120のための30V隔離はしばしば8μmの最小横方向間隔を必要とするが、アレイ300における近接するLDMOSトランジスタ120のための30V隔離は5.7μmの最小横方向間隔を用いることが可能であり、これは29%の削減である。また、アレイ200における近接するLDMOSトランジスタ120のための40V隔離はしばしば8.5μmの最小横方向間隔を必要とするが、アレイ300における近接するLDMOSトランジスタ120のための40V隔離は6.2μmの最小横方向間隔を用いることが可能であり、これは27%の削減である。

10

【0042】

したがって、ドーパントの横方向拡散を抑制することによって、外側及び内側の深いトレンチ隔離構造312及び314は、アレイ300における近接するLDMOSトランジスタ120間の最小横方向間隔を著しく削減し、これが、LDMOSトランジスタアレイ300を実装するために必要なシリコン実装面積を著しく削減する。

【0043】

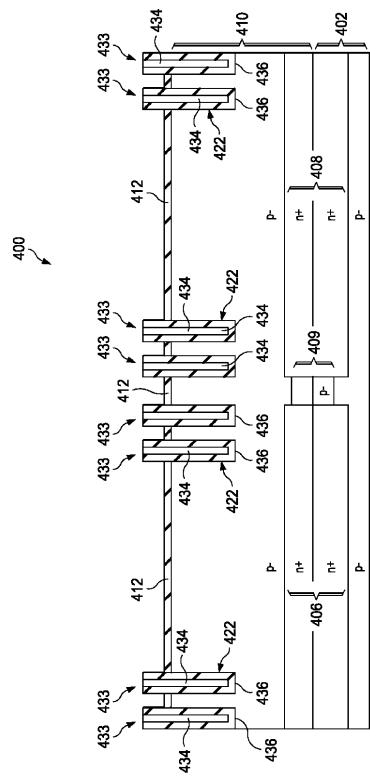

図4A～図4Mは、例示の実施形態のLDMOSトランジスタアレイを形成する方法400を示す。図4Aに示されるように、方法400は、従来のように形成されるp型の単結晶シリコン基板402を用い、パターニングされたフォトレジスト層404を基板402の頂部表面に形成することによって開始される。

20

【0044】

パターニングされたフォトレジスト層404は従来の様式で形成され、この様式は、フォトレジストの層を堆積させること、パターニングされたイメージをフォトレジストの層上に形成するためにマスクとして知られているパターニングされた黒／透明ガラスプレートを介して光を投影すること、及び、光に曝されることによって軟化された画像化されたフォトレジスト領域を除去することを含む。

【0045】

パターニングされたフォトレジスト層404が形成された後、基板402の頂部表面において横方向に離間されたn+埋め込み領域406及び408を形成するために、基板402の露出された領域にアンチモンなどのn型ドーパントが注入される。アンチモンは、後に形成されるエピタキシャル層へのドーパントの上向き拡散を最小化する、小さい拡散係数を有する。n+埋め込み領域406及び408が形成された後、パターニングされたフォトレジスト層404は、灰化処理を用いるなど、従来の様式で除去される。

30

【0046】

図4Bに示されるように、パターニングされたフォトレジスト層404が除去された後、基板402は、1700KeVの注入エネルギーでp型ドーパント（ホウ素など）でブランケット注入される。この注入により、横方向に離間されたn+埋め込み領域406及び408間の基板402の頂部表面においてp-埋め込み領域409が形成される。p-埋め込み領域409のドーパント濃度は、p-基板402のドーパント濃度よりわずかに高い。したがって、この注入は、n+埋め込み領域406及び408のプロファイルに実質的に影響を与えない。p型ブランケット注入は、40V以下の動作に充分である。

40

【0047】

p-埋め込み領域409が形成された後、その結果の構造は、注入をドライブインするために1200で従来のようにアニールされる。ドライブインは、n+埋め込み領域406及び408並びにp-埋め込み領域409を下方に拡散させ、これは、後に形成されるエピタキシャル層へのn+埋め込み領域406及び408並びにp-埋め込み領域409の上方拡散を制限する。

【0048】

また、ドライブインは、基板402におけるn+埋め込み領域406及び408並びにp-埋め込み領域409を、後に形成されるエピタキシャル層におけるn+埋め込み領域

50

406 及び 408 並びに p - 埋め込み領域 409 より厚くする。p 型注入の分量は n 型注入の分量よりずっと少ないため、p - 埋め込み領域 409 の厚みは、n + 埋め込み領域 706 及び 708 の厚みより薄い。

#### 【0049】

ドライブインに続き、従来の様式で基板 402 の頂部表面上に p 型エピタキシャル層 410 が成長される。エピタキシャル層 410 の形成の間、n + 埋め込み領域 406 及び 408 並びに p - 埋め込み領域 409 は、エピタキシャル層 410 の底部へと上方に拡散する。

#### 【0050】

エピタキシャル層 410 の形成の間の n + 埋め込み領域 406 及び 408 の上方拡散は 10 p - 埋め込み領域 409 の上方拡散よりずっと大きい。これは、p - 埋め込み領域 409 を形成する際に用いられる注入の投射レンジが非常に大きく、p - 埋め込み領域 409 を形成する際に用いられる分量は、n + 埋め込み領域 406 及び 408 を形成する際に用いられる分量よりずっと少ないためである。したがって、p - 埋め込み領域 409 の大部分は p 型基板 402 内に存在する。

#### 【0051】

エピタキシャル層 410 が形成された後、エピタキシャル層 410 の頂部表面上にハーダマスクが形成される。この例において、ハーダマスクは、エピタキシャル層 410 上に酸化物層 412 を堆積させることによって形成される。続いて、酸化物層 412 上に窒化物層 414 が堆積され、窒化物層 414 上に酸化物層 416 が堆積される。 20

#### 【0052】

酸化物層 412、窒化物層 414、及び酸化物層 416 は、各々様々な厚みを有し得る。この例において、酸化物層 412 はおよそ 150 の厚みを有し、窒化物層 414 はおよそ 2000 の厚みを有し、酸化物層 416 はおよそ 3000 の厚みを有する。また、酸化物層 412 は熱成長酸化物で実装され得、一方、酸化物層 416 は任意の種類の堆積された二酸化シリコン (SiO<sub>2</sub>) 層で実装され得る。次に、厚みおよそ 1 μm のパターニングされたフォトレジスト層 418 が、酸化物層 416 の頂部表面上に形成される。パターニングされたフォトレジスト層 418 は、(平面図で見た場合) 丸い角を有するように従来の様式で形成される。

#### 【0053】

図 4C に示されるように、パターニングされたフォトレジスト層 418 が形成された後、酸化物層 416、並びに下にある窒化物層 414 及び酸化物層 412 の領域の露出された領域は、エッチングされてハーダマスク 420 を形成し、ハーダマスク 420 は(平面図で見た場合の) 丸い角と、ハーダマスク 420 を完全に介して延在するいくつかの開口とを有する。ハーダマスク 420 が形成された後、パターニングされたフォトレジスト層 418 は従来の様式で除去される。 30

#### 【0054】

図 4D に示されるように、パターニングされたフォトレジスト層 418 の除去に続き、エピタキシャル層 410 におけるいくつかのトレンチ開口 422 を形成するために、ハーダマスク 420 における開口を介してエピタキシャル層 410 がエッチングされる。トレンチ開口 422 は、様々な幅及び深さを有し得る。この例において、各トレンチ開口 422 は 0.7 μm の幅及び 2.5 μm の深さを有する。 40

#### 【0055】

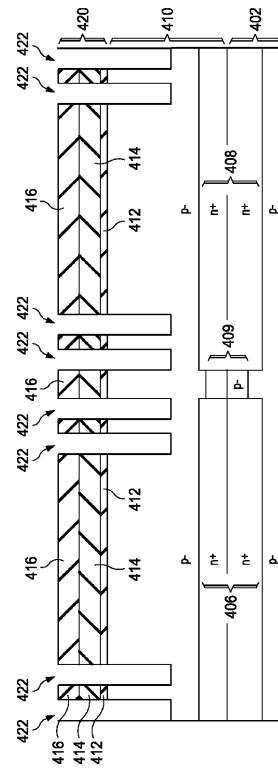

また、トレンチ開口 422 は、様々な側壁角度を有し得る側壁を有し、90° の側壁角度がエピタキシャル層 410 の頂部表面に対して実質的に直角である。この例において、各トレンチ開口 422 は 88° の側壁角度を有する。また、トレンチ開口 422 は(上から見た場合) 丸い角を有する。

#### 【0056】

図 4E に示されるように、トレンチ開口 422 が形成された後、トレンチ開口 422 をライニングする (line) ように、ハーダマスク 420 とエピタキシャル層 410 の露出領 50

域との上に非導電ライナー 430 がコンフォーマルに (conformally) 形成される。例えば、ライナー 430 は、およそ 200 の深さまで酸化物を熱成長させ、それに続いて、準大気圧化学気相成長 (SACVD) を用いておよそ 200 の深さまで酸化物層を堆積させることによって形成され得る。

【0057】

次に、非導電ライナー 430 が形成された後、トレンチ開口 422 の残りを充填するように非導電ライナー 430 上に導電層 432 が堆積される。この例において、導電層 432 は、トレンチ開口 422 の残りを充填するように非導電ライナー 430 上にポリシリコン層を従来のように堆積させることによって形成される。ポリシリコン層は、その場でドープされ得るか、又は従来の様式での堆積の後ドーパントで注入され得る。この例において、ポリシリコン層は、n 導電型を有するようにドープされる。10

【0058】

その後、図 4F に示されるように、導電層 432、非導電ライナー 430、及び酸化物層 416 が、エッチバック又は化学機械研磨を用いるなど、従来の様式で平坦化される。この平坦化は、トレンチ開口 422 を充填するいくつかの深いトレンチ隔離構造 433 を形成するように、窒化物層 414 の頂部表面から酸化物層 416 が除去されるまで続く。深いトレンチ隔離構造 433 は、トレンチ開口 422 の丸い角のため、(上から見た場合) 丸い角を有する。

【0059】

したがって、この例において、各トレンチ隔離構造 433 はポリシリコンコア 434 及び非導電性外側構造 436 を有する。非導電性外側構造 436 は、トレンチ開口 422 によって露出される、エピタキシャル層 410 に接する非導電性外側表面 437 を有する。20

【0060】

ポリシリコンコア 434 及び非導電性外側構造 436 を用いて深いトレンチ隔離構造 433 を実装する代わりに、非導電性材料のみを用いて深いトレンチ隔離構造 433 を実装することができる。この場合、非導電性材料を用いてトレンチ開口 422 をライニングする代わりに、トレンチ開口 422 は非導電性材料で充填される。

【0061】

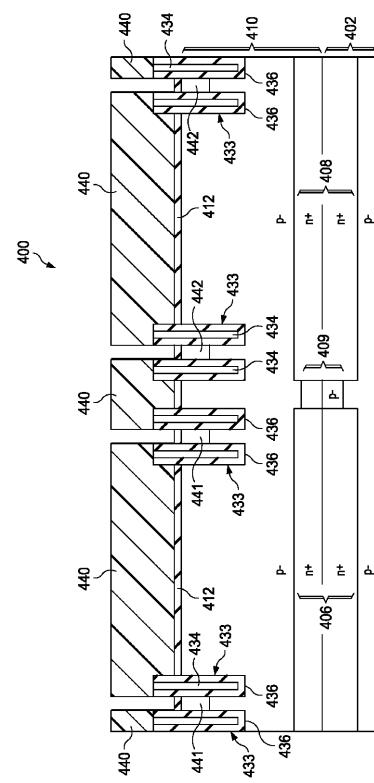

図 4G に示されるように、深いトレンチ隔離構造 433 が形成された後、窒化物層 414 は従来の手順を用いて除去される。その後、図 4H に示されるように、パターニングされたフォトレジスト層 440 が、従来の様式で酸化物層 412 及び深いトレンチ隔離構造 433 の頂部表面上に形成される。30

【0062】

任意選択で、平坦化ステップの間、窒化物層 414 及び酸化物層 412 が除去され得、そのため、深いトレンチ隔離構造 433 の頂部表面及びエピタキシャル層 410 の頂部表面は、同じ水平面内に位置することになる。その後、パターニングされたフォトレジスト層 440 は、エピタキシャル層 410 上に、又は、平坦化ステップに続いてエピタキシャル層 440 (410?) 上に形成される犠牲酸化物層上に形成され得る。

【0063】

パターニングされたフォトレジスト層 440 が形成された後、エピタキシャル層 410 において n+ 埋め込み層 406 の上にありエピタキシャル層 410 の頂部表面まで延在する n+ 領域 441 を形成するように、(リン又はヒ素などの) n 型ドーパントがエピタキシャル層 410 に数回、いくらかの注入エネルギーで注入される。40

【0064】

この注入はまた、エピタキシャル層 410 において n+ 埋め込み層 408 の上にありエピタキシャル層 410 の頂部表面まで延在する n+ 領域 442 を形成する。n+ 領域 441 及び 442 は、およそ 1500 の最大深さを有し、深いトレンチ隔離構造 433 間に位置し、それらに接する。その後、パターニングされたフォトレジスト層 440 は従来の様式で除去される。

【0065】

10

20

30

40

50

図4 Iに示されるように、パターニングされたフォトレジスト層440が除去された後、その結果の構造は、注入をドライブインするように1150で従来のようにアニールされる。ドライブインは、n+領域441及び442を、下方に及びその後外方に拡散させる。導電層432を実装するためにポリシリコンが用いられる場合、ポリシリコンは有害な応力の影響なしに、1150アニールに耐えることができる。

#### 【0066】

ドライブインの後、パターニングされたフォトレジスト層444が酸化物層412及び深いトレンチ隔離構造433の頂部表面上に従来の様式で形成される。パターニングされたフォトレジスト層444が形成された後、エピタキシャル層410においてn+埋め込み層406の上にあるn-ドリフト領域445を形成するように、(リン又はヒ素などの)n型ドーパントがエピタキシャル層410に数回、いくらかの注入エネルギーで注入される。

#### 【0067】

この注入はまた、エピタキシャル層410においてn+埋め込み層408の上にあるn-ドリフト領域446を形成する。また、図4 Iで破線で示されるように、40V動作をサポートするために、n-ドリフト領域445及び446が形成されると同時に、エピタキシャル層410の頂部表面においていくつかのn-領域445-6が形成され得るよう、パターニングされたフォトレジスト層444が形成され得る。各n-領域445-6は、p-埋め込み領域409の上に位置し、深いトレンチ隔離構造433のペアを横方向に囲む。その後、パターニングされたフォトレジスト層444は従来の様式で除去される。パターニングされたフォトレジスト層444が除去された後、その結果の構造は、注入をドライブインするために従来のように1100でアニールされる。

#### 【0068】

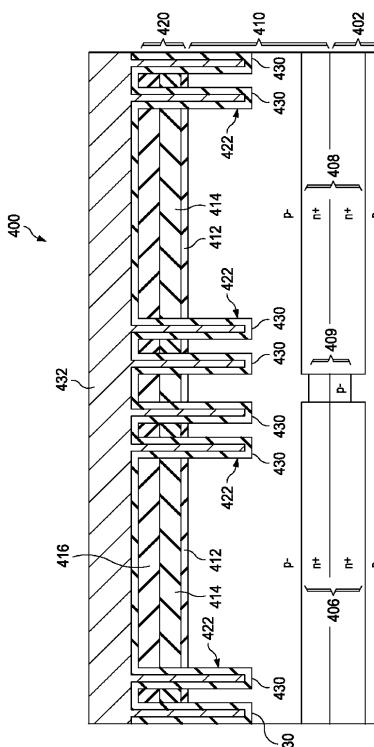

図4 Jに示されるように、ドライブインの後、およそ4000深さのいくつかの浅いトレンチ隔離構造447が、従来の様式でエピタキシャル層410の頂部において形成される。不具合の発生を防ぐために、浅いトレンチ隔離構造447が形成された後、高温拡散は回避されるべきである。この例において、浅いトレンチ隔離構造447のうちの1つはn-ドリフト領域445に形成され、浅いトレンチ隔離構造447のうちの1つはn-ドリフト領域446に形成される。

#### 【0069】

浅いトレンチ隔離構造447が形成された後、パターニングされたフォトレジスト層448が、従来の様式で酸化物層412及び深いトレンチ隔離構造433の頂部表面上に形成される。パターニングされたフォトレジスト層410が形成された後、n+埋め込み層406の上に位置するエピタキシャル層410の一部においてp型チャネルトップ領域450を形成するように、(ホウ素などの)p型ドーパントがエピタキシャル層410に数回、いくらかの注入エネルギーで注入される。チャネルトップ領域450はまた、浅いトレンチ隔離構造447に接し、その下に位置する。

#### 【0070】

この注入はまた、n+埋め込み層408の上に位置するエピタキシャル層410の一部において、p型チャネルトップ領域451を形成する。チャネルトップ領域451はまた、浅いトレンチ隔離構造447に接し、その下に位置する。その後、パターニングされたフォトレジスト層448は従来の様式で除去される。パターニングされたフォトレジスト層448が除去された後、その結果の構造は、注入からの格子損傷を修復するために、従来のように1050で高速熱アニール(RTA)される。RTAは実質的に拡散を許さない短いプロセスである。

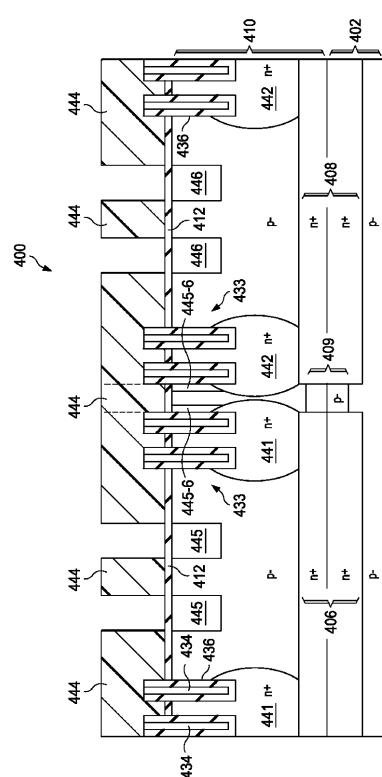

#### 【0071】

次に、図4 Kに示されるように、チャネルトップ領域450及び451が形成された後、酸化物層412が従来の様式で除去される。酸化物層412が除去された後、従来の様式でp型領域450及び451並びにn型領域445及び446上にゲート酸化物層452が形成される。

10

20

30

40

50

## 【0072】

その後、パターニングされたフォトレジスト層454が、従来の様式でゲート酸化物層452及び深いトレンチ隔離構造433の頂部表面上に形成される。パターニングされたフォトレジスト層454が形成された後、n+埋め込み層406の上に位置するエピタキシャル層410の一部にp型領域455を形成するように、(ホウ素などの)p型ドーパントがエピタキシャル層410に数回、いくらかの注入エネルギーで注入される。この注入はまた、n+埋め込み層408の上に位置するエピタキシャル層410の一部にp型領域456を形成する。

## 【0073】

p型領域455及び456の形成に続いて、p型領域455においてn型領域457を10及びp型領域456においてn型領域458を形成するように、(ヒ素などの)n型ドーパントがエピタキシャル層410に数回、いくらかの注入エネルギーで注入される。

## 【0074】

したがって、p型及びn型のドーパントは、フォトレジスト層454において同じ開口を介して注入される。また、p型領域455及びn型領域457は第1の二重拡散ウェル(Dウェル)459を形成し、p型領域456及びn型領域458は第2のDウェル460を形成する。その後、パターニングされたフォトレジスト層454は従来の様式で除去される。

## 【0075】

ホウ素とヒ素の拡散係数の差により、チャネル長さは、形成されるべきゲートの寸法ではなく、熱量によって決定される。ホウ素の注入分量はターゲットしきい値電圧に合致するように最適化され、Dウェル459及び460の深さはホウ素注入エネルギーによって制御される。20

## 【0076】

図4Lに示されるように、パターニングされたフォトレジスト層454が除去された後、p型領域455の上に位置するようにゲート酸化物層452上にゲート462が形成され、p型領域456の上に位置するようにゲート酸化物層452上にゲート464が形成される。ゲート462及び464は従来のように形成される。例えば、ゲート462及び464は、ポリシリコンの層を堆積させることによって形成され得、マスク及びエッチングステップが続く。30

## 【0077】

その後、側壁スペーサ470及び471が、ゲート462のそれぞれ外側及び内側の側壁に接するように形成される。ゲート464のそれぞれ外側及び内側の側壁に接するように側壁スペーサ473及び474が形成される。側壁スペーサ470、471、473、及び474は従来のように形成される。例えば、側壁スペーサ470、471、473、及び474は、酸化物層及び窒化物層を堆積させることによって形成され得、異方性エッチングが続く。

## 【0078】

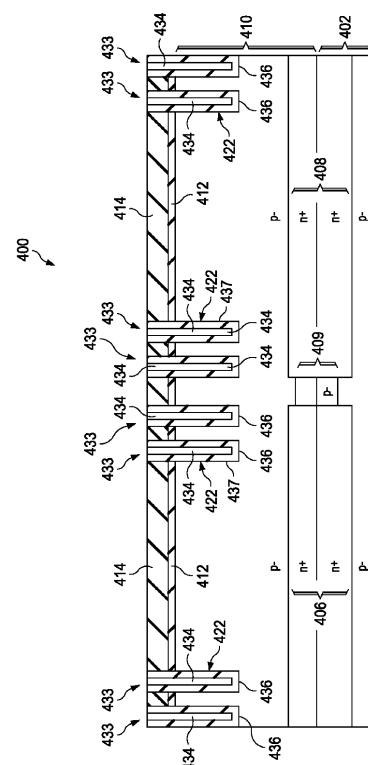

側壁スペーサ470、471、473、及び474が形成された後、深いトレンチ隔離構造433、ゲート酸化物層452、ゲート462及び464、並びに側壁スペーサ470、471、473、及び474の頂部表面上に、パターニングされたフォトレジスト層476が従来の様式で形成される。40

## 【0079】

パターニングされたフォトレジスト層476が形成された後、p型領域455に接するn+ソース領域480、p型領域456に接するn+ソース領域481、n-ドリフト領域445に接するn+ドレイン領域483、及びn-ドリフト領域446に接するn+ドレイン領域484を形成するように、(リン又はヒ素などの)n型ドーパントがエピタキシャル層410に注入される。その後、パターニングされたフォトレジスト層476は従来の様式で除去される。

## 【0080】

10

20

30

40

50

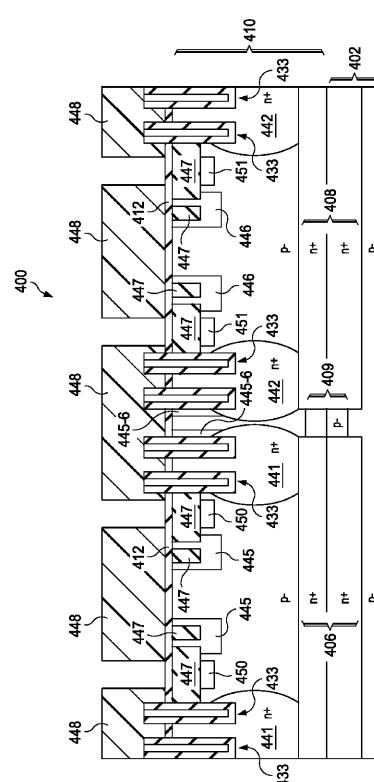

図4Mに示されるように、パターニングされたフォトレジスト層476が除去された後、深いトレンチ隔離構造433、ゲート酸化物層452、ゲート462及び464、並びに側壁スペーサ470、471、473、及び474の頂部表面上に、パターニングされたフォトレジスト層486が従来の様式で形成される。

【0081】

パターニングされたフォトレジスト層486が形成された後、p型領域455に接するp+コンタクト領域490、及びp型領域456に接するp+コンタクト領域492を形成するように、(ホウ素などの)p型ドーパントがエピタキシャル層410に注入される。その後、第1のLDMOSトランジスタ496及び第2のLDMOSトランジスタ497を備えるLDMOSトランジスタアレイ494を形成するように、パターニングされたフォトレジスト層486は従来の様式で除去される。

10

【0082】

第1のLDMOSトランジスタ496は、ドレインドリフト領域445、p型領域455、ソース領域480、及びドレイン領域483を含む。第2のLDMOSトランジスタ497は、ドレインドリフト領域446、p型領域456、ソース領域481、及びドレイン領域484を含む。その後、方法400は、LDMOSトランジスタのアレイの形成を完了するため従来のステップを続ける。

【0083】

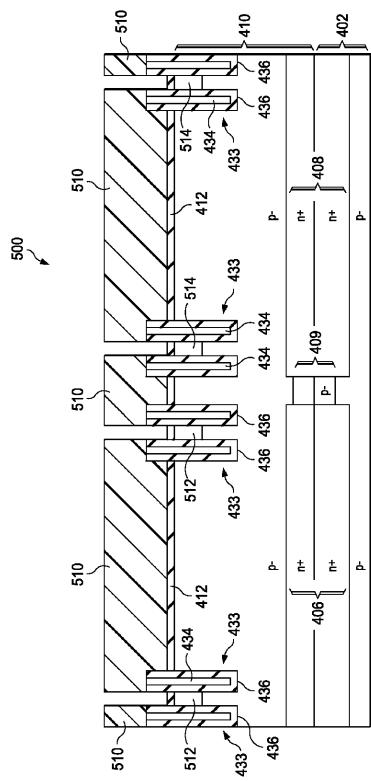

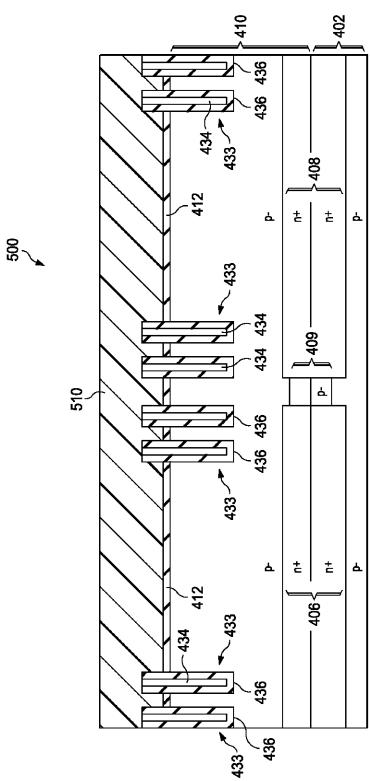

図5A～図5Cは、別の例示の実施形態のLDMOSトランジスタアレイを形成する方法500を示す。図5Aは平面図を示し、図5Bは図5Aの線5B-5Bに沿った断面図を示し、図5Cは図5Aの線5C-5Cに沿った断面図を示す。

20

【0084】

方法500は方法400に類似しているため、両方の方法に共通の構造を指示するため同じ参照番号を使用している。方法500は、窒化物層414の除去(図4Gに示される)まで方法400と同じであり、パターニングされたフォトレジスト層440の代わりにパターニングされたフォトレジスト層510を形成することが異なる。パターニングされたフォトレジスト層510が形成された後、(リン又はヒ素などの)n型ドーパントがエピタキシャル層410に数回、いくらかの注入エネルギーで注入される。

【0085】

この注入は、エピタキシャル層410において、n+埋め込み層406の上に各々位置するいくつかの離間された第1のn+領域512を形成する。この注入はまた、エピタキシャル層410において、n+埋め込み層408の上に各々位置するいくつかの離間された第2のn+領域514を形成する。n+領域512及び514は、深いトレンチ隔離構造433間に位置し、深いトレンチ隔離構造433に接する。注入に続き、パターニングされたフォトレジスト層510は従来の様式で除去される。その後、方法500は方法400と同様に続行する。

30

【0086】

したがって、n+埋め込み層406の上に位置する連続する円形開口、及びn+埋め込み層408の上に位置する連続する円形開口を有するパターニングされたフォトレジスト層440とは異なり、パターニングされたフォトレジスト層510は、n+埋め込み層406の上に円形に配置構成されるいくつかの離間された第1の開口、及び、n+埋め込み層408の上に円形に配されるいくつかの離間された第2の開口を有する。

40

【0087】

その後n+領域512及び514がドライブインされるとき、n+領域512はともにn+領域441を形成するように横方向に拡散し、n+領域514はともにn+領域442を形成するように横方向に拡散する。離間されたn+領域512及び514を形成することによって、深いトレンチ隔離構造433より下にあるn+領域441及び442の一部の最大幅を減らすことができる。

【0088】

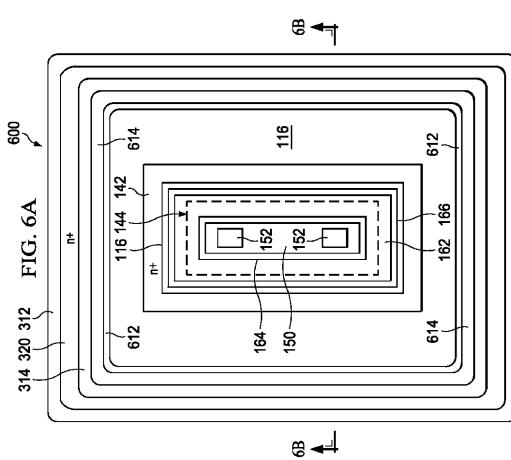

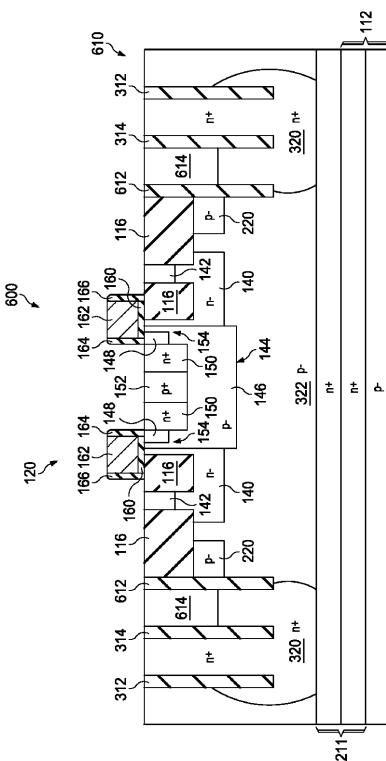

図6A及び図6Bは、別の例示の実施形態のLDMOSトランジスタアレイ600を示

50

す。図6Aは平面図を示し、図6Bは図6Aの線6B-6Bに沿った断面図を示す。LD MOSトランジスタアレイ600はLD MOSトランジスタアレイ300と同様であるため、両方のトランジスタに共通の構造を指示するために同じ参照番号を使用している。図6A及び図6Bには1つのトランジスタ120のみが示されている。

#### 【0089】

図6A及び図6Bに示されるように、LD MOSトランジスタアレイ600は半導体構造310の代わりに半導体構造610を用いるため、LD MOSトランジスタアレイ600はLD MOSトランジスタアレイ300とは異なる。半導体構造610がエピタキシャル層114の頂部表面に形成されるいくつかの絶縁の深いトレンチ構造612も含むことを除いて、半導体構造610は半導体構造310と同じである。1つの構造612のみが示されている。内側の深いトレンチ隔離構造314は、絶縁の深いトレンチ隔離構造612を横方向に囲む。

10

#### 【0090】

半導体構造610はまた、各々が、内側の深いトレンチ隔離構造314及び絶縁の深いトレンチ隔離構造612に接し、内側の深いトレンチ隔離構造314と絶縁の深いトレンチ隔離構造612との間に位置する、いくつかのn型インターフェース領域614を含むため、半導体構造610は半導体構造310と異なる。1つの領域614のみが示されている。n型インターフェース領域614は、エピタキシャル層114の頂部表面から下方に延在するが、n+領域320より浅い。n型インターフェース領域614は、隔離の早期接合破壊を起こす可能性のある浮動接合(floating junction)をなくす。

20

#### 【0091】

図6C及び図6Dは、別の例示の実施形態のLD MOSトランジスタアレイ650を示す。図6Cは平面図を示し、図6Dは図6Cの線6D-6Dに沿った断面図を示す。LD MOSトランジスタ650アレイはLD MOSトランジスタアレイ600と同様であるため、両方のトランジスタに共通の構造を指示するために同じ参照番号を使用している。

#### 【0092】

図6C及び図6Dに示されるように、LD MOSトランジスタアレイ650は半導体構造610の代わりに半導体構造660を用いるため、LD MOSトランジスタアレイ650はLD MOSトランジスタアレイ600とは異なる。半導体構造660がエピタキシャル層114の頂部表面において形成されるいくつかの絶縁の深いトレンチ構造662も含むことを除いて、半導体構造660は半導体構造610と同じである。1つの構造662のみが示されている。各絶縁の深いトレンチ隔離構造662は、外側の深いトレンチ隔離構造312を横方向に囲む。

30

#### 【0093】

半導体構造660はまた、各々、外側の深いトレンチ隔離構造312及び絶縁の深いトレンチ隔離構造662に接し、外側の深いトレンチ隔離構造312と絶縁の深いトレンチ隔離構造662との間に位置する、いくつかのn型インターフェース領域664を含むため、半導体構造660は半導体構造610と異なる。各n型インターフェース領域664は、エピタキシャル層114の頂部表面から下方に延在するが、n+領域320より浅い。

40

#### 【0094】

LD MOSトランジスタアレイ600及び650は、トランジスタアレイ600及び650がトランジスタアレイ300より小さくなるように形成され得ることを除いて、LD MOSトランジスタアレイ300と同様に動作する。図6A及び図6Bの例において、内側の深いトレンチ隔離構造314の或る距離内側に絶縁の深いトレンチ構造612を置くことによって、n+領域320の外側横方向及び上方への拡散が抑制され得る。内側の深いトレンチ隔離構造314の或る距離内側に絶縁の深いトレンチ構造612を置くことによって、n-ドレインドリフト領域140と内側の深いトレンチ隔離構造314との間の距離が低減され得る。したがって、LD MOSトランジスタアレイ600の専有面積は、LD MOSトランジスタアレイ300の専有面積より小さくなる。

50

## 【0095】

図6C及び図6Dの例において、外側の深いトレンチ隔離構造312の或る距離外側に絶縁の深いトレンチ構造662を置くことによって、n+領域320の外側横方向及び上方への拡散も抑制され得る。外側の深いトレンチ隔離構造312の或る距離外側に絶縁の深いトレンチ構造662を置くことによって、トランジスタアレイにおいて近接するトランジスタ間の距離が低減され得る。

## 【0096】

絶縁の深いトレンチ構造612及び絶縁の深いトレンチ構造662は、深いトレンチ隔離構造433と同様に及び同時に形成され得る。また、n型インターフェース領域614及びn型インターフェース領域664は、n型ドレインドリフト領域445及び446と同様に及び同時に形成され得る。 10

## 【0097】

図7A及び図7Bは、別の例示の実施形態のLD MOSトランジスタアレイ700を示す。図7Aは平面図を示し、図7Bは図7Aの線7B-7Bに沿った断面図を示す。LD MOSトランジスタアレイ700はLD MOSトランジスタアレイ300と同様であるため、両方のトランジスタに共通の構造を指示するために同じ参照番号を使用している。1つのトランジスタ120のみが示されている。

## 【0098】

図7A及び図7Bに示されるように、LD MOSトランジスタアレイ700は半導体構造310の代わりに半導体構造710を用いるため、LD MOSトランジスタアレイ700はLD MOSトランジスタアレイ300とは異なる。半導体構造710は、深いトレンチ隔離構造312及び314が半導体構造710において更に離間されることを除いて、半導体構造310と同じである。 20

## 【0099】

LD MOSトランジスタアレイ700はLD MOSトランジスタアレイ300と同様に動作する。n+領域320のためのドーパントが、注入後、深いトレンチ隔離構造312と314の間にそれらから離間して位置するが、ドライブイン後、深いトレンチ隔離構造312と314の間にそれらに接して位置することを除いて、LD MOSトランジスタアレイ700はLD MOSトランジスタ496及び497と同様に形成される。深いトレンチ隔離構造312と314の間の横方向の間隔を大きくすることによって、n+領域320はドライブインの間横方向に拡散し、これが深いトレンチ隔離構造312及び314の底部でのドーパントの横方向及び上方への拡散を制限する。 30

## 【0100】

図8A及び図8Bは例示の実施形態のLD MOSトランジスタアレイ800を示す。図8Aは平面図を示し、図8Bは図8Aの線8B-8Bに沿った断面図を示す。アレイ800はアレイ200と同様であるため、両方のアレイに共通の構造を指示するために同じ参照番号を使用している。

## 【0101】

アレイ800は近接するトランジスタ120のドレインドリフト領域140に接する深いトレンチ隔離構造812を含むため、アレイ800はアレイ200とは異なる。深いトレンチ隔離構造812は、(上から見た場合)丸い角と、p型領域(エピタキシャル層114)に接する底部表面とを有する。また、深い隔離構造812は、浅いトレンチ隔離構造116の深さより著しく深い深さを有する。 40

## 【0102】

また、深い隔離構造812は、エピタキシャル層114のいくつかの部分814を横方向に囲む。深い隔離構造812によって囲まれたエピタキシャル層114の各部分814は、トランジスタ120のドレインドリフト領域140及びDウェル144を含む。アレイ800は、アレイ800にない構造を形成するステップを除き、方法400と同じステップを用いて形成され得る。

## 【0103】

トランジスタアレイ 800 の利点の 1 つは、近接する LDMOS トランジスタ 120 間の最小横方向間隔が、アレイ 200 における近接する LDMOS トランジスタ 120 間の最小横方向間隔より著しく小さいことである。例えば、アレイ 200 における近接する LDMOS トランジスタ 120 のための 40V 隔離はしばしば 5.65 μm の最小横方向間隔を必要とするが、アレイ 800 における近接する LDMOS トランジスタ 120 のための 40V 隔離は 0.7 μm の最小横方向間隔を用いることが可能であり、これは 88 % の削減である。

#### 【 0104 】

したがって、半導体構造がドーパントの横方向拡散及び電荷キャリアの横方向動きを制限し、これによってシリコン実装面積の必要量が削減される。

10

#### 【 0105 】

説明する一例において、トランジスタアレイが、第 1 の導電型を有する半導体材料を含む。また、トランジスタアレイは 2 つ又はそれ以上のトランジスタ構造を含む。各トランジスタ構造は半導体材料に形成されるソース及びドレインを有する。ソース及びドレインは第 2 の導電型を有する。ドレインはソースから横方向に離間される。また、各トランジスタ構造は、半導体材料に形成される浅いトレンチ隔離構造を有する。浅いトレンチ隔離構造はドレインに接する。また、トランジスタアレイは、半導体材料に形成される深い隔離構造を含む。深い隔離構造は、アレイにおけるトランジスタ構造のソース及びドレインを横方向に囲む。

#### 【 0106 】

別の説明する例において、半導体構造を形成する方法が、ドーパントの横方向拡散及び電荷キャリアの横方向動きを制限する。この方法は、基板に埋め込み領域を形成することを含む。基板は第 1 の導電型を有する。埋め込み領域は第 2 の導電型を有する。この方法はまた、基板上にエピタキシャル層を成長させることを含む。エピタキシャル層は頂部表面及び第 1 の導電型を有する。埋め込み領域は、エピタキシャル層の一部に接し、それより下に位置する。また、この方法は、エピタキシャル層へ下方に延在するように、エピタキシャル層の頂部表面において浅いトレンチ隔離構造を形成することを含む。また、この方法は、エピタキシャル層へ下方に延在するように、エピタキシャル層の頂部表面において内側の深いトレンチ隔離構造を形成することを含む。内側の深いトレンチ隔離構造は、浅いトレンチ隔離構造を横方向に囲む。更に、この方法は、エピタキシャル層へ下方に延在するように、エピタキシャル層の頂部表面において外側の深いトレンチ隔離構造を形成することを含む。外側の深いトレンチ隔離構造は、内側の深いトレンチ隔離構造を横方向に囲む。また、この方法は、エピタキシャル層へ下方に延在し、埋め込み領域に接するように、エピタキシャル層の頂部表面においてドープされた領域を形成することを含む。ドープされた領域は第 2 の導電型を有する。ドープされた領域も、内側及び外側の深いトレンチ隔離構造に接し、エピタキシャル層の一部を横方向に囲む。

20

30

#### 【 0107 】

特許請求の範囲内で、説明した実施形態における改変が可能であり、他の実施形態が可能である。例えば、例示の実施形態を LDMOS トランジスタに関して説明してきたが、他の MOS ベースの構造にも同様に適用する。

40

【図1A】

【図1B】

FIG. 1B

(従来技術)

### 【図2A】

## 【図2B】

FIG. 2B

(従来技術)

【図3A】

【 図 3 B 】

【図4A】

【 図 4 B 】

### 【図4C】

FIG. 4C

## 【図4-D】

FIG. 4D

### 【 図 4 E 】

FIG. 4E

【 図 4 F 】

FIG. 4F

## 【図4G】

### 【図4H】

FIG. 4G

FIG. 4H

### 【図4-1】

FIG. 4I

FIG 4T

【図4】

1

【図4K】

FIG. 4K

【図 4 L】

FIG. 4L

【図4M】

FIG. 4M

【図5A】

【図 5 B】

FIG. 5B

【図 5 C】

FIG. 5C

【図 6 A】

【図 6 B】

FIG. 6B

【図 6 C】

【図 6 D】

### 【図 7 A】

【図7B】

【図 8 A】

【 図 8 B 】

FIG. 8B

---

フロントページの続き

(72)発明者 ピンホワ フー

アメリカ合衆国 75024 テキサス州 プラノ, スタテン アイランド ドライブ 431

3

(72)発明者 サミール ペンハルカル

アメリカ合衆国 75013 テキサス州 アレン, バーンサイド ドライブ 2032

(72)発明者 グル マトゥル

アメリカ合衆国 75025 テキサス州 プラノ, オクサデンタル ロード 7117

審査官 綿引 隆

(56)参考文献 特開2013-115166 (JP, A)

特開2011-066067 (JP, A)

特表2005-536060 (JP, A)

特表2011-514675 (JP, A)

特表2009-539260 (JP, A)

特開平08-195441 (JP, A)

特開平07-029987 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 21/336

H01L 27/088

H01L 29/78