**【特許請求の範囲】****【請求項 1】**

基材上に画像表示領域を備え、前記画像表示領域に画素となる発光領域が複数配列された表示装置であって、

前記各画素に映像信号に応じた量のキャリアを供給する画素電極と、

前記画素の境界に沿って形成されたバンクと、

キャリア輸送層又はキャリア注入層を含むキャリア移動性を有した層であり前記画素電極及び前記バンク上に積層された補助層と当該補助層の上に積層され前記キャリアを注入されて発光する発光層とを含む発光素子層と、

前記発光素子層の上に配置され前記画素電極と共に前記発光素子層に電圧を印加する対向電極と、

を有し、

前記補助層には前記バンク上に分断領域が設けられ、当該分断領域は隣接画素間での前記補助層を介した前記キャリアの移動を阻害すること、

を特徴とする表示装置。

**【請求項 2】**

請求項 1 に記載の表示装置において、

前記分断領域は前記補助層のパターニングにおける当該補助層の非形成領域であること、を特徴とする表示装置。

**【請求項 3】**

請求項 1 に記載の表示装置において、

前記分断領域は、当該分断領域に形成された前記補助層の材料の変質により前記キャリア移動性を喪失していること、を特徴とする表示装置。

**【請求項 4】**

請求項 1 から請求項 3 のいずれか 1 つに記載の表示装置において、

前記補助層は、前記分断領域により前記画素ごとに分かれていること、を特徴とする表示装置。

**【請求項 5】**

請求項 1 から請求項 3 のいずれか 1 つに記載の表示装置において、

前記画像表示領域は発光色の異なる複数種類の前記画素を含み、

前記分断領域は、前記発光色が異なる隣接した各画素対において当該画素間の境界の少なくとも一部に沿って配置されていること、

を特徴とする表示装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は電圧印加により発光する自発光素子を用いた表示装置に関する。

**【背景技術】****【0 0 0 2】**

表示装置として、有機エレクトロルミネッセンス (electroluminescence : E L ) 素子などの自発光素子を用いたものの開発が進められている。有機エレクトロルミネッセンス素子は一般に O L E D (organic light emitting diode) と称され、発光ダイオードの一種である。O L E D は有機化合物からなる発光層にキャリア (電子や正孔) を注入され発光する。O L E D は電圧の印加時に発光層に効率的にキャリアが注入されるように、電極と発光層との間などに、キャリア移動性を有した補助的な層を設ける構造とされることが一般的となっている。

**【0 0 0 3】**

例えば、補助的な層として、アノードと発光層 (emitting layer : E M L ) との間に、正孔輸送層 (hole transport layer : H T L ) や正孔注入層 (hole injection layer : H I L ) が設けられる。また、カソードと発光層との間には、電子輸送層 (electron trans

10

20

30

40

50

port layer : E T L ) や電子注入層 (electron injection layer : E I L ) が設けられる。これら補助層は C V D ( chemical vapor deposition ) 法、スパッタ法、蒸着法などにより、複数の画素が配列された画像表示領域全体に亘って共通に形成される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2012-155953号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述したO L E DにおけるH T L , H I L のようなキャリア移動性を有した層が画像表示領域に亘って連続する共通層として形成される発光素子を用いた表示装置は、当該共通層を通して隣接する画素間でのキャリアのリークが発生し得る。隣接画素へのリーク電流は当該隣接画素の意図しない発光を招くという問題があった。具体的には、リーク電流は画像の解像度の劣化を生じるほか、発光色が異なる画素間におけるリーク電流は色再現性(色純度)の低下を生じるという問題があった。特に、画素サイズの縮小による高精細化に伴い隣接画素の開口部(又は発光領域)が接近することにより当該問題が顕著となる。

【0006】

本発明は上記問題点を解決するためになされたものであり、隣接する画素の自発光素子へのリーク電流が抑制され、隣接画素の意図しない発光が防止される表示装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る表示装置は、基材上に画像表示領域を備え、前記画像表示領域に画素となる発光領域が複数配列された表示装置であって、前記各画素に映像信号に応じた量のキャリアを供給する画素電極と、前記画素の境界に沿って形成されたバンクと、キャリア輸送層又はキャリア注入層を含むキャリア移動性を有した層であり前記画素電極及び前記バンク上に積層された補助層と当該補助層の上に積層され前記キャリアを注入されて発光する発光層とを含む発光素子層と、前記発光素子層の上に配置され前記画素電極と共に前記発光素子層に電圧を印加する対向電極と、を有し、前記補助層には前記バンク上に分断領域が設けられ、当該分断領域は隣接画素間での前記補助層を介した前記キャリアの移動を阻害する。

【図面の簡単な説明】

【0008】

【図1】本発明の実施形態に係る有機E L 表示装置の概略の構成を示す模式図である。

【図2】本発明の実施形態に係る有機E L 表示装置の表示パネルの模式的な平面図である。

【図3】本発明の第1の実施形態に係る表示パネルの図2に示すI I I - I I I 線に沿った位置での模式的な垂直断面図である。

【図4】下部電極の形成後の表示パネルの製造工程の概略のプロセスフロー図である。

【図5】本発明の第2の実施形態に係る表示パネルの図2に示すI I I - I I I 線に沿った位置での模式的な垂直断面図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施の形態(以下実施形態という)について、図面に基づいて説明する。

【0010】

なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保つての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等

について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

【0011】

以下に説明する各実施形態の表示装置は有機EL表示装置である。有機EL表示装置は、アクティブマトリックス型表示装置であり、テレビ、パソコン、携帯端末、携帯電話等に搭載される。

【0012】

表示装置の画像表示領域には、画像を構成する複数の画素が2次元配列される。ここで、画像に対応する2次元の直交座標系の1つの座標軸に沿った方向を行方向、もう1つの座標軸に沿った方向を列方向とする。以降の説明では、行方向、列方向は基本的には画像の水平方向、垂直方向とするが、これは便宜的な定義である。例えば、同一の画像表示領域にて画像の縦横を切り換えて表示することができる表示装置では、画像表示領域の行方向、列方向はそれぞれ画像の垂直方向、水平方向となる場合がある。また、表示装置の構造自体も、以下に説明するものに対し行方向と列方向とを入れ替えたものとすることができる。

【0013】

また、以下の実施形態では、画像表示領域には発光色が互いに異なる複数種類の画素（サブピクセル）が配列されカラー画像を表示可能な表示装置を説明する。なお、カラー画像における画素は、表示装置における複数種類のサブピクセルからなる一組のサブピクセルに対応するが、表示装置ではサブピクセルが構成上の単位であり、例えば、サブピクセルごとにOLEDや画素回路が形成される。そこで以下の説明では、基本的にサブピクセルを画素と扱う。

【0014】

【第1の実施形態】

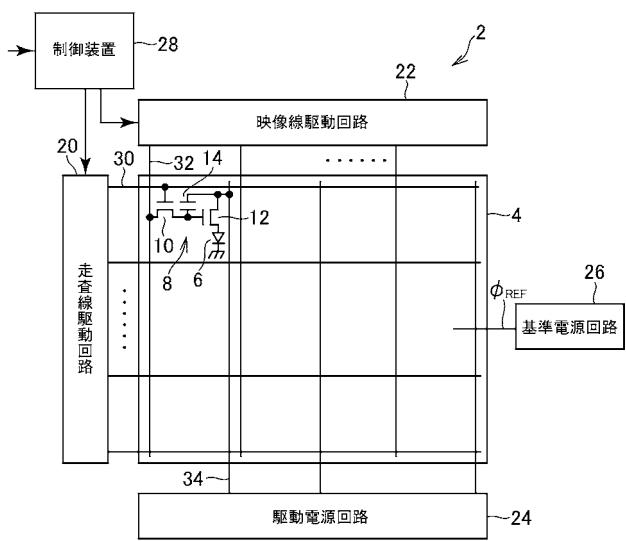

図1は実施形態に係る有機EL表示装置2の概略の構成を示す模式図である。有機EL表示装置2は、画像を表示する画素アレイ部4と、当該画素アレイ部を駆動する駆動部とを備える。有機EL表示装置2はガラス基板や可撓性を有した樹脂フィルムなどからなる基材の上に薄膜トランジスタ（thin film transistor：TFT）やOLEDなどの積層構造を形成されている。

【0015】

画素アレイ部4には画素に対応してOLED6及び画素回路8がマトリックス状に配置される。画素回路8は複数のTFT10, 12やキャパシタ14で構成される。

【0016】

一方、駆動部は走査線駆動回路20、映像線駆動回路22、駆動電源回路24、基準電源回路26及び制御装置28を含み、画素回路8を駆動しOLED6の発光を制御するなどの機能を担う。

【0017】

走査線駆動回路20は画素の水平方向の並び（画素行）ごとに設けられた走査信号線30に接続されている。走査線駆動回路20は制御装置28から入力されるタイミング信号に応じて走査信号線30を順番に選択し、選択した走査信号線30に、点灯TFT10をオンする電圧を印加する。

【0018】

映像線駆動回路22は画素の垂直方向の並び（画素列）ごとに設けられた映像信号線32に接続されている。映像線駆動回路22は制御装置28から映像信号を入力され、走査線駆動回路20による走査信号線30の選択に合わせて、選択された画素行の映像信号に応じた電圧を各映像信号線32に出力する。当該電圧は、選択された画素行にて点灯TFT10を介してキャパシタ14に書き込まれる。駆動TFT12は書き込まれた電圧に応じた電流をOLED6に供給し、これにより、選択された走査信号線30に対応する画素のOLED6が発光する。

## 【0019】

駆動電源回路 24 は画素列ごとに設けられた駆動電源線 34 に接続され、駆動電源線 34 及び選択された画素行の駆動 TFT12 を介して OLED6 に電流を供給する。

## 【0020】

基準電源回路 26 は、OLED6 のカソード電極を構成する共通電極（図示せず）に定電位  $V_{REF}$  を与える。 $V_{REF}$  は例えば、接地電位 GND (0V) に設定することができる。

## 【0021】

本実施形態において OLED6 の下部電極は画素ごとに形成された画素電極であり、OLED6 の上部電極が画素電極に対向配置された対向電極となる。下部電極は駆動 TFT12 に接続される。一方、上部電極は全画素の OLED6 に共通の電極で構成される。本実施形態では下部電極が OLED6 の陽極（アノード）であり、上部電極が陰極（カソード）である。

10

## 【0022】

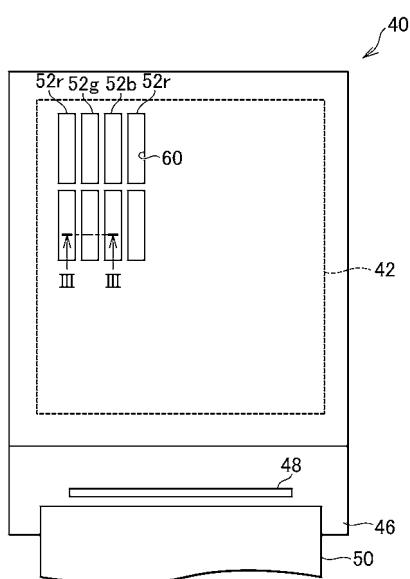

図 2 は有機 EL 表示装置 2 の表示パネル 40 の模式的な平面図である。表示パネル 40 の表示領域 42 に図 1 に示した画素アレイ部 4 が設けられ、上述したように画素アレイ部 4 には OLED が配列される。矩形である表示パネル 40 の一辺には部品実装領域 46 が設けられ、表示領域 42 につながる配線が配置される。さらに部品実装領域 46 には駆動部を構成するドライバ IC 48 が搭載されたり、FPC 50 が接続されたりする。FPC 50 は制御装置 28 やその他の回路 20, 22, 24, 26 等に接続されたり、その上に IC を搭載されたりする。

20

## 【0023】

本実施形態の表示パネル 40 はカラー画像を表示し、カラー画像における画素は例えば、赤色 (R)、緑色 (G) 及び青色 (B) に対応する光を出射する画素（サブピクセル）で構成される。

## 【0024】

本実施形態では R 画素 52r、G 画素 52g、B 画素 52b が表示領域にストライプ配列される例を説明する。当該配列では、画像の垂直方向に同じ種類（色）の画素が並び、水平方向に RGB が周期的に並ぶ。なお、図 2 において R 画素 52r、G 画素 52g、B 画素 52b はそれぞれ有効な発光領域を模式的に示しており、構造上は画素開口 60 に対応し、それらの間の領域はバンクに対応している。

30

## 【0025】

表示パネル 40 は例えば、TFT 基板と対向基板とを、間に充填材を挟んで貼り合わせた構造とされる。TFT 基板には TFT72 などからなる回路や OLED6 などが形成される。対向基板には偏光板やタッチパネルが設けられ得る。また表示パネル 40 のカラー化方式がカラーフィルタ方式である場合、例えば、対向基板にはカラーフィルタが形成され、OLED6 にて白色光を生成し、当該白色光をカラーフィルタを通すことで RGB 各色を得る。

## 【0026】

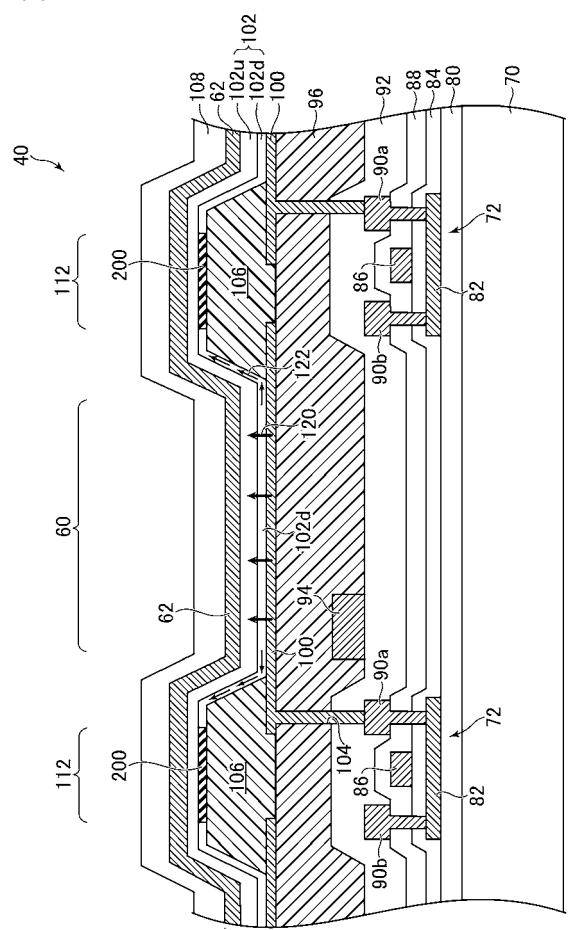

図 3 は図 2 に示す III-I-II 線に沿った位置での表示パネル 40 の模式的な垂直断面図である。図 3 は上述の TFT 基板の断面構造を示しており、この上に形成される充填材層と対向基板の構造とは図示を省略されている。本実施形態において画素アレイ部 4 はトップエミッション型であり、TFT 基板上に形成された OLED6 で生じた光を対向基板から出射する。すなわち、図 3 において OLED6 の光は上向きに出射する。

40

## 【0027】

TFT 基板の構造はガラスや樹脂フィルムからなる基材 70 の上に各種の層を積み重ね、またパターニングすることによって形成される。

## 【0028】

具体的には基材 70 の上に窒化シリコン (SiN<sub>y</sub>) や酸化シリコン (SiO<sub>x</sub>) などの無機絶縁材料からなる下地層 80 を介してポリシリコン (p-Si) 膜が形成され、当

50

該 p - Si 膜をパターニングし、回路層で用いる箇所の p - Si 膜を選択的に残す。例えば、p - Si 膜を用いてトップゲート型の TFT72 のチャネル部及びソース・ドレイン部となる半導体領域 82 が形成される。TFT72 のチャネル部の上にはゲート絶縁膜 84 を介してゲート電極 86 が配置される。ゲート電極 86 はスパッタリング等で形成した金属膜をパターニングして形成される。この後、ゲート電極 86 を覆う層間絶縁膜 88 を積層する。TFT72 のソース部、ドレイン部となる p - Si にはイオン注入により不純物が導入され、さらにそれらに電気的に接続されたソース電極 90a 及びドレイン電極 90b が形成される。このようにして TFT72 を形成した後、層間絶縁膜 92 を積層する。層間絶縁膜 92 の表面には、スパッタリング等で形成した金属膜をパターニングして配線 94 等を形成することができ、当該金属膜とゲート電極 86 、ソース電極 90a 及びドレイン電極 90b の形成に用いた金属膜とで例えば、図 1 に示した走査信号線 30 、映像信号線 32 、駆動電源線 34 を多層配線構造で形成することができる。この上に例えば、アクリル樹脂等の有機材料を積層して平坦化膜 96 が形成され、これにより平坦化された表示領域 42 の表面に OLED6 が形成される。

10

## 【0029】

OLED6 は下部電極 100 、発光素子層 102 及び上部電極 62 で構成され、これら下部電極 100 、発光素子層 102 及び上部電極 62 は基材 70 側から順に積層される。

## 【0030】

図 3 に示す TFT72 が n チャネルを有した駆動 TFT12 であるとすると、下部電極 100 は TFT72 のソース電極 90a に接続される。具体的には、上述した平坦化膜 96 の形成後、下部電極 100 を TFT72 に接続するためのコンタクトホール 104 が形成され、平坦化膜 96 表面及びコンタクトホール 104 内に形成した導電体膜をパターニングして、TFT72 に接続された下部電極 100 が画素ごとに分離して形成される。

20

## 【0031】

例えば、下部電極 100 はITO、IZO などで形成される。また、本実施形態はトップエミッショ型であるので、下部電極 100 は光反射率が高い材料で形成された反射層上に透明導電膜を積層した構造とすることができる。例えば、反射層はアルミニウム (Al) や銀 (Ag) 等で形成することができ、発光層からの光を表示面、つまり上部電極 62 側へ反射させる。

30

## 【0032】

上述したように、駆動 TFT12 は各画素の映像信号に応じて OLED6 に流れる電流を制御し、下部電極 100 は各画素の映像信号に応じた量のキャリアを発光素子層 102 へ供給する。具体的には本実施形態では下部電極 100 はアノードであり、キャリアとして正孔が下部電極 100 から発光素子層 102 へ供給される。

## 【0033】

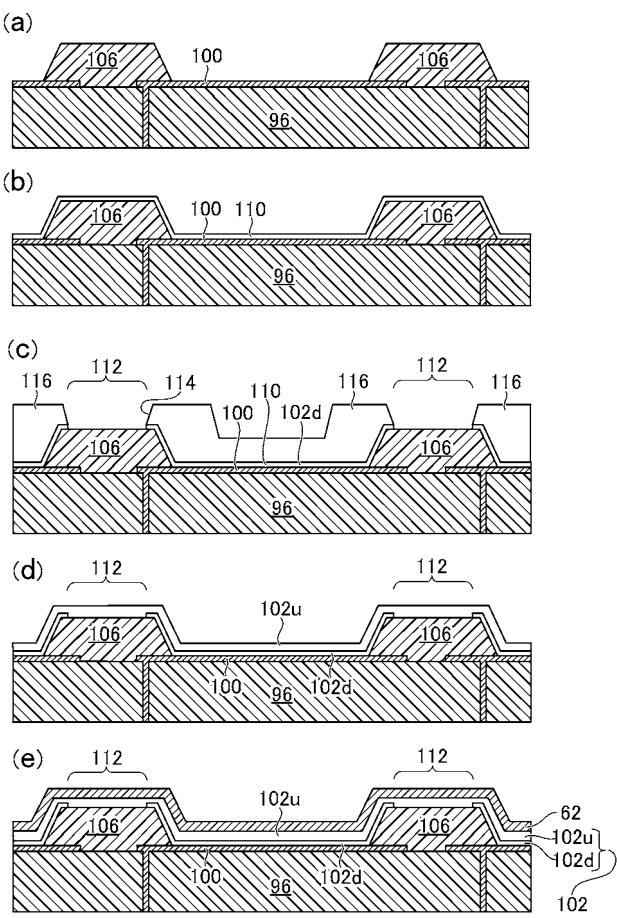

図 4 は、下部電極 100 の形成後の表示パネル 40 の製造工程の概略のプロセスフロー図であり、OLED6 を形成する際の主要な工程における TFT 基板の部分断面図を示している。以下、図 4 を用いて OLED6 の形成工程を説明する。

## 【0034】

下部電極 100 の形成後、バンク 106 を形成する (図 4 (a))。バンク 106 は例えば、アクリル、ポリイミド等の感光性樹脂をフォトリソグラフィ技術やインクジェット方式でパターニングして画素境界に形成され下部電極 100 間を電気的に分離する。なお、バンク 106 は SiN<sub>y</sub> や SiO<sub>x</sub> などの無機絶縁材料で形成することもできる。バンク 106 で囲まれた領域が図 2 に示す画素開口 60 となり、当該領域には下部電極 100 が露出する。

40

## 【0035】

バンク 106 の形成後、発光素子層 102 を構成する各層が下部電極 100 の上に順番に積層される。発光素子層 102 は注入されて発光する発光層 (EML) 、及び発光層への効率的にキャリアを供給する機能を担う補助層を含む。発光素子層 102 は補助層として HIL 及び HTL の少なくとも一方を含む。

50

## 【0036】

例えば、OLED 6 は RGB 画素それぞれの発光色に対応した単色発光の OLED であり、アノードである下部電極 100 側から順に HIL、HTL、EML、ETL が積層された構造である。当該構造では HIL、HTL 及び ETL が補助層である。このうち HIL 及び HLT は正孔を供給するアノード（下部電極 100）と EML 及び ETL との間に設けられる。図 3 では発光素子層 102 を HIL 及び HLT からなる下層 102d と EML 及び ETL からなる上層 102u とに分けて示している。

## 【0037】

バンク 106 の形成後、まず、下層 102d が形成される。下層 102d を構成する HTL / HIL は例えば、ポリ(3,4-エチレンジオキシチオフェン) - ポリ(スチレンスルホン酸)(PEDOT - PSS) やその他の導電性有機材料で形成される。バンク 106 が形成された表示領域 42 の表面の全体に亘って HTL / HIL 層 110 が例えば、スパッタリングや CVD で成膜される（図 4 (b)）。

10

## 【0038】

しかる後、バンク 106 上に HTL / HIL 層 110 の分断領域 112 が形成され（図 4 (c)）、残る領域の HTL / HIL 層 110 が発光素子層 102 の下層 102d となる（図 4 (d), (e)）。分断領域 112 は隣接画素間での HTL / HIL 層 110 を介したキャリアの移動を阻害する機能を有する。図に示すように、分断領域 112 の幅はバンク 106 の幅の一部分で足り、下層 102d の縁はバンク 106 の表面にオーバーラップさせることができる。

20

## 【0039】

本実施形態では、分断領域 112 は HTL / HIL 層 110 の非形成領域である。例えば、フォトリソグラフィ技術を用いたパターニングにより HTL / HIL 層 110 を除去することで分断領域 112 が形成される。具体的には、HTL / HIL 層 110 の表面にフォトレジスト膜を成膜し、当該フォトレジスト膜を用いて分断領域 112 を形成する領域に開口部 114 を備えたマスク 116 を形成する。そして、当該マスク 116 を用いて、開口部 114 から HTL / HIL 層 110 をエッチング除去する（図 4 (c)）。

20

## 【0040】

なお、下層 102d として、印刷法などで当初から分断領域 112 を備えたパターンの HTL / HIL 層 110 を形成することもできる。

30

## 【0041】

次に下層 102d の上に EML、ETL が表示領域 42 全体に亘って成膜され、上層 102u が形成される（図 4 (d)）。例えば、上層 102u は蒸着により形成される。また、単色発光の OLED では EML は発光色ごとに異なる有機発光材料で形成される。この場合、EML はインクジェット法などで形成することもできる。

## 【0042】

下層 102d 及び上層 102u からなる発光素子層 102 の上に上部電極 62 が例えば、スパッタリングで成膜される（図 4 (e)）。上部電極 62 は基本的に表示領域 42 全体に亘って共通に形成される。

40

## 【0043】

このようにして OLED 6 が形成される。なお、上部電極 62 表面には図 3 に示すように封止膜 108 が形成される。封止膜 108 は、水分などの透過を阻止し、OLED 6 を保護する機能を有する。封止膜 108 として例えば、 $\text{SiN}_y$  膜が CVD 法によって成膜される。

## 【0044】

なお、TFT 基板に対向基板を貼り合わせない構造とすることもでき、この場合には TFT 基板の表面の機械的な強度を確保するため、封止膜 108 の上ないし下、または両方に保護膜を形成することができる。保護膜が下に形成される場合は、バンク 106 で生じる凹凸を平坦化させる効果を持たせ、封止膜 108 の凹凸を低減させてもよい。これにより封止膜の内部応力を低減させることができ、封止膜が剥がれにくい構造とすることがで

50

きる。

【0045】

上述したように、有機EL表示装置2の駆動時には各画素のOLED6は映像信号に応じたキャリアを供給されて発光する。図5には当該駆動時に下部電極100から発光素子層102へ供給されるキャリアである正孔の流れを矢印で模式的に示している。上部電極62は下部電極100より低い電位を印加され、各画素の下部電極100から発光素子層102の下層102dへ供給される正孔は基本的には当該下部電極100とこれに対向配置された上部電極62との間の電界に従い、矢印120で示すように発光素子層102の上層102uへ引き寄せられ当該画素のEMLに注入される。

【0046】

一方、下部電極100から下層102dに供給された正孔の一部は矢印122で示すように画素開口60の外側へ向けて下層102d内を移動し得る。このキャリア移動が隣接する画素へのリーク電流となると上述した問題を生じる。この点、有機EL表示装置2では発光素子層102の下層102dは画素境界に分断領域112を形成されていることにより、隣接画素へのリーク電流の到達を阻止することができ、リーク電流による隣接画素の発光が防止される。よって、画像の解像度の低下が抑制される。また、分断領域112を発光色が異なる画素間の境界に配置することで、リーク電流による混色が抑制され高い色純度が得られ、好適な色再現性を実現できる。

【0047】

なお、補助層のうち下層102dを構成するものは他の補助層より比較的厚く形成されることが多く、それに伴い下層102d内を移動してリーク電流となるキャリア量が大きくなる。この点、本実施形態では下層102dに分断領域112を設けることで、画素間のリーク電流を好適に抑制することができる。

【0048】

また、OLED6は白色発光とすることもできる。例えば、白色発光のOLED6は発光色が異なる複数のOLEDを光透過性の中間層を介して電気的に直列接続したタンデム構造とすることができます。タンデム構造では中間層として設けられる電荷発生層(charge generation layer: CGL)もHIL、HTL等と同様、キャリア移動性を有する補助層である。本発明はタンデム構造のOLED6を有する有機EL表示装置2に適用することができる。この場合も上述の単色発光のOLED6と同様、下部電極100の上に積層されるHTL/HIL層110に分断領域112が設けられ、これにより画素間のリーク電流を好適に抑制することができる。

【0049】

分断領域112は各画素を取り囲む画素境界の全周に沿って配置することができる。すなわち、HTL/HIL層110が分断領域112により画素ごとに分かれた構造とすることができます。

【0050】

また、既に述べたように分断領域112を発光色が互いに異なる隣接画素間の境界に沿って配置することにより好適な色再現性を実現できる。例えば、本実施形態ではRGB画素がストライプ配列され、行方向に隣り合う各画素対は互いに発光色が異なる。この場合、分断領域112を列方向に延びる画素境界に沿って設けることで隣接画素間の混色を防止できる。

【0051】

なお、分断領域112は発光色が互いに異なる隣接画素間の境界の全体に沿ってではなく一部のみに沿って形成されてもよい。

【0052】

さて、表示パネル40の製造では、生産効率を高めるために、1枚の大きな基材70上に複数面の表示パネル40を同時に形成する手法が採用される。この製造手法では基材上へのTFTの形成などの工程は複数面の表示パネル40を一体に行われ、一方、OLED形成工程は複数面の表示パネル40を分割して行われる。つまり、この製造方法は、複数

10

20

30

40

50

面の表示パネル 4 0 がつながった状態で加工される前段工程と、表示パネル 4 0 ごとに分割されて残りの加工が施される後段工程とに分けられ、ここでは前段工程を TFT 工程、後段工程を OLED 工程と呼ぶ。

【 0 0 5 3 】

TFT 工程は基本的に、集積回路などを製造する半導体製造プロセスを利用して行うことができる工程からなり、比較的にプロセス条件の自由度が高く、例えば、数百 程度の高温プロセスを利用するように製造工程を設計することも可能である。一方、OLED 工程は、有機材料からなる発光素子層の劣化を防ぐため、雰囲気温度の上限が数十 程度に制限され得る。つまり、OLED 工程は、表示パネル 4 0 をそれぞれ加工することにより工数が増加し、また TFT 工程に比べてより確実にプロセス条件を制御する必要がある。そのため、表示パネル 4 0 の製造工程において TFT 工程の占める割合を大きくし、OLED 工程の占める割合を小さくすることで、表示パネル 4 0 の製造コストの低減や製造期間の短縮を図ることができる。10

【 0 0 5 4 】

本実施形態では、図 4 ( a ) に示す構造を形成する工程が TFT 工程として行われる。すなわち、基材 7 0 の上に TFT 7 2 などからなる回路を形成し、その上に平坦化膜 9 6 を積層し、また下部電極 1 0 0 及びバンク 1 0 6 が形成される。

【 0 0 5 5 】

本実施形態では、さらに発光素子層 1 0 2 の下層 1 0 2 d を形成する工程が TFT 工程として行われ、これにより、上に述べた製造コスト低減や製造期間短縮の効果が得られる。つまり、境界領域にバンク 1 0 6 が形成された後、さらに TFT 工程において、表示領域 4 2 の全面に HTL / HIL 層 1 1 0 を形成し(図 4 ( b ) )、HTL / HIL 層 1 1 0 の上にマスク 1 1 6 を形成し、このマスク 1 1 6 を用いて分断領域 1 1 2 を形成する。20

【 0 0 5 6 】

なお、OLED 工程は発光素子層 1 0 2 の上層 1 0 2 u を形成する工程(図 4 ( d ) )、上部電極 6 2 を形成する工程(図 4 ( e ) )、及びその後の工程を含む。

【 0 0 5 7 】

[ 第 2 の実施形態 ]

以下、本発明の第 2 の実施形態に係る有機 EL 表示装置 2 b を説明する。本実施形態と上記第 1 の実施形態とは分断領域 1 1 2 の構造及び形成方法に相違点を有し、その他の点では基本的に共通である。以下、第 2 の実施形態について第 1 の実施形態との相違点を中心に説明する。30

【 0 0 5 8 】

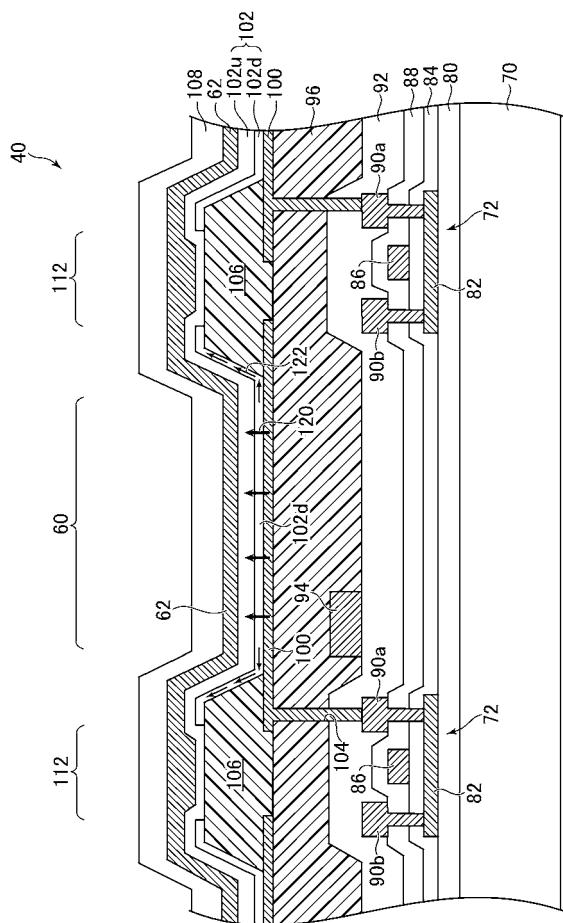

有機 EL 表示装置 2 b の表示パネル 4 0 の模式的な平面図は、第 1 の実施形態について示した図 2 と基本的には同じであり、これを援用する。図 5 は図 2 に示す I II - I II 線に沿った位置での本実施形態の表示パネル 4 0 の模式的な垂直断面図である。第 1 の実施形態の分断領域 1 1 2 は、発光素子層 1 0 2 における HTL / HIL 層 1 1 0 といったキャリア移動性を有した補助層である下層 1 0 2 d が存在しない領域であった。これに対し、本実施形態の分断領域 1 1 2 は、下層 1 0 2 d においてその材料の変質・変性によりキャリア移動性を喪失した領域であり、図 5 においてバンク 1 0 6 の上の分断領域 1 1 2 には、キャリア移動性を喪失した下層 1 0 2 d である変質層 2 0 0 が存在する。40

【 0 0 5 9 】

例えば、第 1 の実施形態と同様にして下層 1 0 2 d 、及び分断領域 1 1 2 を形成する領域に開口部 1 1 4 を備えたマスク 1 1 6 を形成する(図 4 ( c ) )。本実施形態では当該マスク 1 1 6 を用いて、例えば、イオン注入やエネルギー線照射を行う。これにより、開口部 1 1 4 の下層 1 0 2 d ( HTL / HIL 層 1 1 0 )に化学的变化を起こさせたり、分子構造の破壊を起こさせたりすることで、下層 1 0 2 d が有していた導電性を失わせ変質層 2 0 0 を形成する。

【 0 0 6 0 】

変質層 2 0 0 を形成した後は、第 1 の実施形態における有機 EL 表示装置 2 と基本的に

同様の工程で本実施形態の有機EL表示装置2bが完成される。例えば、変質層200の形成後、まず上層102uを積層して発光素子層102を形成し(図4(d))、次に発光素子層102の上に上部電極62を形成してOLED6が形成される(図4(e))。

#### 【0061】

上記各実施形態ではRGB画素がストライプ配列された有機EL表示装置2にて分断領域112を設けてリーク電流を抑制する構造を説明したが、当該リーク電流抑制構造は他の画素配列においても適用することができる。

#### 【0062】

また上記各実施形態及び変形例では、下部電極100がOLED6のアノード、上部電極62がOLED6のカソードである場合を説明した。しかし、本発明は、下部電極100がOLED6のカソード、上部電極62がOLED6のアノードである場合にも適用できる。その場合、発光素子層102における各層の積層順序は上述の構成とは逆転する。例えば、カソードである下部電極100側から順にEIL、ETL、EML、HTL、HILが積層された構造となる。

#### 【0063】

本発明の実施形態として上述した有機EL表示装置2, 2bを基にして、当業者が適宜設計変更して実施し得る全ての有機EL表示装置も、本発明の要旨を包含する限り、本発明の範囲に属する。また、有機EL表示装置以外の表示装置、例えば発光層として量子ドット素子を採用した量子ドット表示装置等も本発明の範囲に属する。

#### 【0064】

本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。例えば、前述の各実施形態に対して、当業者が適宜、構成要素の追加、削除若しくは設計変更を行ったもの、又は、工程の追加、省略若しくは条件変更を行ったものも、本発明の要旨を備えている限り、本発明の範囲に含まれる。

#### 【0065】

また、本実施形態において述べた態様によりもたらされる他の作用効果について本明細書記載から明らかなもの、又は当業者において適宜想到し得るものについては、当然に本発明によりもたらされるものと解される。

#### 【符号の説明】

#### 【0066】

2 有機EL表示装置、4 画素アレイ部、6 OLED、8 画素回路、10 点灯TFT、12 駆動TFT、14 キャパシタ、20 走査線駆動回路、22 映像線駆動回路、24 駆動電源回路、26 基準電源回路、28 制御装置、30 走査信号線、32 映像信号線、34 駆動電源線、40 表示パネル、42 表示領域、44 陰極、46 部品実装領域、48 ドライバIC、50 FPC、60 画素開口、62 上部電極、70 基材、72 TFT、80 下地層、82 半導体領域、84 ゲート絶縁膜、86 ゲート電極、88, 92 層間絶縁膜、90a ソース電極、90b ドレイン電極、94 配線、96 平坦化膜、100 下部電極、102 発光素子層、104 コンタクトホール、106 バンク、108 封止膜、110 HTL/HIL層、112 分断領域、200 変質層。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】