# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl. G09G 3/28 (2006.01) H01J 17/49 (2006.01) (45) 공고일자 2006년11월29일 (11) 등록번호 10-0650968

(24) 등록일자 2006년11월22일

(21) 출원번호10-2005-0088994(22) 출원일자2005년09월23일심사청구일자2005년09월23일

(65) 공개번호10-2006-0051623(43) 공개일자2006년05월19일

(30) 우선권주장 JP-P-2004-00276976 2004년09월24일 일본(JP) JP-P-2004-00296001 2004년10월08일 일본(JP)

(73) 특허권자 파이오니아 가부시키가이샤

일본 도쿄도 메구로쿠 메구로 1쵸메 4반 1고

(72) 발명자 도쿠나가 츠토무

일본 야마나시켕 나카코마군 다토미쵸 니시하나와 2680

사토 요시치카

일본 야마나시켕 나카코마군 다토미쵸 니시하나와 2680

사에구사 노부히코

일본 야마나시켕 나카코마군 다토미쵸 니시하나와 2680

(74) 대리인 특허법인코리아나

심사관: 정재헌

전체 청구항 수 : 총 20 항

## (54) 플라즈마 디스플레이 장치

#### (57) 요약

플라즈마 디스플레이 장치는 플라즈마 디스플레이 패널을 포함한다. 플라즈마 디스플레이 패널에 인가되는 다양한 구동 펄스들의 펄스 전압치들 및/또는 펄스 폭들은 플라즈마 디스플레이 패널의 축적된 사용 시간에 따라 조정된다.

#### 대표도

도 1

## 특허청구의 범위

## 청구항 1.

플라즈마 디스플레이 장치로서,

플라즈마 디스플레이 패널의 행 방향으로 연장된 복수의 행 전극 쌍들,

상기 플라즈마 디스플레이 패널의 열 방향으로 연장된 복수의 열 전극들, 및

상기 복수의 행 전극 쌍들과 상기 복수의 열 전극들 사이의 교차점들에서 픽셀들로서 기능하고, 각각 방전 스페이스를 가지는, 복수의 방전 셀을 포함하는, 플라즈마 디스플레이 패널;

상기 방전 스페이스에 연결된 상기 방전 셀 각각의 소정의 면 상에 형성되고 전자 빔 조사로 여기된 결과로서 200 내지 300 nm 파장 대역에서 피크를 가지는 캐소드 발광 광 방출을 수행하는 마그네슘 산화물 결정들을 가지는 마그네슘 산화물 층;

영상 신호의 유닛 디스플레이 기간을 구성하는 복수의 서브필드들의 각각에서의 상기 영상 신호에 따라 상기 행 전극 쌍들의 각각과 상기 열 전극들의 각각에 구동 펼스를 인가함으로써 상기 방전 스페이스에서 방전을 일으키는 구동부; 및

상기 플라즈마 디스플레이 패널의 축적된 사용 시간에 따라 상기 구동 펄스의 펄스 전압치 및/또는 펄스 폭을 조정하는 제 어부를 포함하는, 플라즈마 디스플레이 장치.

## 청구항 2.

제 1 항에 있어서,

상기 서브필드 각각은 어드레스 기간 및 유지 기간을 가지고,

상기 구동부는,

상기 서브필드 각각의 상기 어드레스 기간에서 상기 행 전극 쌍 중 하나의 행 전극에 스캔 펼스를 인가하고, 상기 영상 신호에 기초하여 상기 열 전극들에 픽셀 데이터의 픽셀 데이터 펼스를 인가함으로써, 상기 방전 셀에서 어드레스 방전을 선택적으로 유도하는 것에 의하여, 상기 방전 셀을 점등 상태 또는 소등 상태 중 하나로 세팅하는 어드레스 수단;

각 상기 서브필드의 상기 유지 기간에서 상기 행 전극 쌍들의 각각에 유지 필스를 인가함으로써 상기 점등 상태로 세팅된 상기 방전 셀에서만 유지 방전을 일으키는 유지 수단; 및

적어도 하나의 상기 서브필드의 상기 어드레스 기간 전에 상기 행 전극 쌍들 모두에 리셋 펄스를 인가함으로써 상기 방전 셀들 모두에서 리셋 방전을 유도하는 리셋 수단을 포함하는, 플라즈마 디스플레이 장치.

#### 청구항 3.

제 2 항에 있어서,

상기 제어부는,

축적된 사용 시간을 카운팅하는 축적 사용 시간 클락킹 수단; 및

상기 축적된 사용 시간에 따라 상기 리셋 펄스, 상기 스캔 펄스, 및 상기 유지 펄스의 적어도 하나의 상기 펄스 전압치 및/ 또는 펄스 폭을 조정하는 펄스 조정 수단를 포함하는, 플라즈마 디스플레이 장치.

## 청구항 4.

제 3 항에 있어서,

상기 펄스 조정 수단은 상기 서브필드들의 각각의 상기 유지 기간에서 처음으로 인가되는 상기 유지 펄스 상에서만 펄스 폭 조정을 수행하는, 플라즈마 디스플레이 장치.

## 청구항 5.

제 1 항에 있어서,

상기 제어부는 상기 축적된 사용 시간에 따라 상기 유닛 디스플레이 기간을 구성하는 상기 서브필드들의 개수를 변경하는, 플라즈마 디스플레이 장치.

## 청구항 6.

제 1 항에 있어서,

상기 제어부는 상기 축적된 사용 시간에 따라 상기 영상 신호의 각 색상의 신호 레벨을 조정하는, 플라즈마 디스플레이 장치.

## 청구항 7.

제 1 항에 있어서,

상기 마그네슘 산화물 결정들은 마그네슘을 가열한 결과로서 생산되는 마그네슘 증기의 증기 산화를 통해 얻어지는 마그네슘 산화물 단결정들을 포함하는, 플라즈마 디스플레이 장치.

## 청구항 8.

제 1 항에 있어서,

상기 마그네슘 산화물 결정들은 2000 옹스트롬 이상의 입자 직경을 가지는, 플라즈마 디스플레이 장치.

## 청구항 9.

제 1 항에 있어서,

상기 마그네슘 산화물 결정들은 230 내지 250nm 파장 대역에서 피크를 가지는 상기 캐소드 발광 광 방출을 수행하는, 플라즈마 디스플레이 장치.

## 청구항 10.

제 1 항에 있어서,

상기 플라즈마 디스플레이 패널은 상기 행 전국 쌍들을 커버링하는 유전체층을 더 포함하고, 상기 마그네슘 산화물층은 상기 유전체층 상에 형성되는, 플라즈마 디스플레이 장치.

### 청구항 11.

플라즈마 디스플레이 장치로서.

플라즈마 디스플레이 패널의 행 방향으로 연장된 복수의 행 전극 쌍들,

상기 플라즈마 디스플레이 패널의 열 방향으로 연장된 복수의 열 전극들, 및

각각 방전 스페이스를 가지는, 상기 복수의 행 전극 쌍들과 상기 복수의 열 전극들 사이의 교차점들에서의 복수의 방전 셀을 포함하는, 플라즈마 디스플레이 패널;

상기 방전 스페이스에 연결된 상기 방전 셀 각각의 소정의 면 상에 형성되고 전자 빔 조사로 여기된 결과로서 200 내지 300 nm 파장 대역에서 피크를 가지는 캐소드 발광 광 방출을 수행하는 마그네슘 산화물 결정들을 가지는 마그네슘 산화물 층;

영상 신호의 유닛 디스플레이 기간을 구성하는 복수의 서브필드들의 각각에서의 상기 영상 신호에 따라 상기 행 전극 쌍들의 각각과 상기 열 전극들의 각각에 구동 펄스를 인가함으로써 상기 방전 스페이스에서 방전을 일으키는 구동부;

상기 플라즈마 디스플레이 패널의 온도를 검출하는 패널 온도 센서; 및

상기 플라즈마 디스플레이 패널의 검출된 온도에 따라 상기 구동 펄스의 펄스 폭을 변경하는 제어부를 포함하는, 플라즈마 디스플레이 장치.

#### 청구항 12.

제 11 항에 있어서,

상기 서브필드 각각은 어드레스 기간 및 유지 기간을 가지고,

상기 서브필드 각각에 그 자체 가중치가 할당되며,

상기 구동부는,

상기 서브필드 각각의 상기 어드레스 기간에서 상기 행 전극 쌍 중 하나의 행 전극에 스캔 펄스를 인가하고 상기 영상 신호에 기초하여, 상기 열 전극들에 픽셀 데이터의 픽셀 데이터 펄스를 인가함으로써, 상기 방전 셀에서 어드레스 방전을 선택적으로 유도하는 것에 의하여 각 상기 방전 셀을 점등 상태 또는 소등 상태 중 하나로 세팅하는 어드레스 수단; 및

상기 서브필드 각각의 상기 유지 기간에서, 관련된 상기 서브필드의 상기 가중치에 의해 결정된 회수로 상기 행 전극 쌍들의 각각에 유지 필스를 반복적으로 인가함으로써 상기 점등 상태로 세팅된 상기 방전 셀에서만 유지 방전을 일으키는 유지수단을 포함하고,

상기 제어부는 상기 플라즈마 디스플레이 패널의 상기 검출된 온도에 따라 상기 스캔 펄스 및 상기 유지 펄스의 펄스 폭을 변경하는, 플라즈마 디스플레이 장치.

## 청구항 13.

제 12 항에 있어서,

상기 플라즈마 디스플레이 패널의 상기 검출된 온도가 소정치보다 낮을 때에, 상기 제어부는 상기 디스플레이 패널의 상기 검출된 온도가 소정치보다 높은 경우와 비교하여 각각 상기 스캔 펄스 및 상기 유지 펄스의 펄스 폭을 넓게 하는, 플라즈마 디스플레이 장치.

## 청구항 14.

제 11 항에 있어서,

상기 제어부는 상기 유지 기간에서 인가되는 상기 유지 펄스들 중 처음으로 인가되는 상기 유지 펄스만의 펄스 폭을 변경하는, 플라즈마 디스플레이 장치.

## 청구항 15.

제 11 항에 있어서,

상기 제어부는 상기 플라즈마 디스플레이 패널의 상기 검출된 온도에 따라 상기 유닛 디스플레이 기간을 구성하는 서브필드들의 개수를 변경하는 서브필드 제어 수단을 포함하는, 플라즈마 디스플레이 장치.

## 청구항 16.

제 15 항에 있어서,

상기 플라즈마 디스플레이 패널의 상기 검출된 온도가 소정치보다 낮을 때에, 상기 서브필드 제어부는 상기 디스플레이 패널의 상기 검출된 온도가 소정치보다 높은 경우와 비교하여 상기 서브필드들의 개수를 감소시키는, 플라즈마 디스플레이 장치.

### 청구항 17.

제 11 항에 있어서,

상기 마그네슘 산화물 결정들은 2000 옹스트롬 이상의 입자 직경을 가지는, 플라즈마 디스플레이 장치.

## 청구항 18.

제 11 항에 있어서,

상기 마그네슘 산화물 결정들은 마그네슘을 가열한 때 생성되는 마그네슘 증기의 증기 산화를 통해 생성되는 마그네슘 산화물 단결정들을 포함하는, 플라즈마 디스플레이 장치.

#### 청구항 19.

제 11 항에 있어서,

상기 마그네슘 산화물 결정들은 230 내지 250nm 파장 대역에서 피크를 가지는 상기 캐소드 발광 광 방출을 수행하는, 플라즈마 디스플레이 장치.

## 청구항 20.

제 11 항에 있어서.

상기 플라즈마 디스플레이 패널은 상기 행 전극 쌍들을 커버링하는 유전체층을 더 포함하고, 상기 마그네슘 산화물층은 상기 유전체층 상에 형성되는, 플라즈마 디스플레이 장치.

#### 명세서

## 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 플라즈마 디스플레이 패널을 가진 플라즈마 디스플레이 장치에 관한 것이다.

플라즈마 디스플레이 패널을 가진 플라즈마 디스플레이 장치 (이하 "PDP") 는 박형인 대형 스크린 디스플레이 장치들로서 시장에 나와 있다. PDP 에서, 픽셀들에 대응된 방전 셀들이 매트릭스형으로 정렬된다. PDP 는 방전 셀들의 각각 내에서 유도되는 방전에 따른 광 방출의 현상을 이용함으로써 영상 디스플레이를 구현한다. 그러므로, 방전 셀들의 방전 전압이 장기간 사용의 결과로 감소하여 PDP 는 오류 방전 (erroneous discharge) 을 생성하는 경향이 있다. 이 문제를 해결하기 위해서, 몇몇 디스플레이 장치는 PDP 사용 시간에 따라 방전 셀들에 인가하는 방전-유지 전압을 제어한다. 이러한 장치중 하나가 일본 특개평 제 9-138668 호에서 개시되어 있다. 이 디스플레이 장치에서는, 사용 시간에 따른 방전-유지 전압의 예상되는 전이를 지시하는 정보를 참조함으로써 (일본 특개평 제 9-138668 호의 도 6 참조), 전원 회로의 출력 전압은 방전-유지 전압이 장치 사용 시간을 반영하는 적당한 값을 가지도록 제어된다.

하지만, 이러한 전원 회로의 출력 전압 제어는 장기간 사용으로 인해 일어난 영상 품질 저하를 적당히 억제할 수 없다.

또한, 다른 문제가 있다. 플라즈마 디스플레이 장치가 사용되는 환경의 온도가 떨어질 때, PDP 의 방전 셀들은 오류 방전 하고 디스플레이 품질은 떨어진다. 이 문제를 극복하기 위해, 몇몇 플라즈마 디스플레이 장치는, PDP 의 온도가 낮을 때, PDP 를 가열한다. 이러한 장치 중 하나가 일본 특개평 제 9-6283 호에서 개시되어 있다.

하지만, 이러한 방법으로는, PDP 의 전체를 균일하게 가열하기 위한 가열기가 장착되어야 하므로 디스플레이 장치의 구조가 복잡해진다.

#### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 장기간 사용에 의해 일어나는 영상 저하를 억제할 수 있는 플라즈마 디스플레이 장치를 제공하는 것이다.

본 발명의 다른 목적은 낮은 온도에서 오류 방전을 억제함으로써, 낮은 온도에서도 좋은 영상 품질을 유지할 수 있는 플라즈마 디스플레이 장치를 제공하는 것이다.

본 발명의 일 양태에 따르면, 플라즈마 디스플레이 패널을 가지는 플라즈마 디스플레이 장치가 제공된다. 플라즈마 디스플레이 패널은 복수의 행 전극 쌍들 및 복수의 열 전극들을 가진다. 행 전극 쌍은 열 전극들에 수직으로 연장된다. 플라즈마 디스플레이 패널에서, 복수의 방전 셀들은 행 전극 쌍들과 열 전극들 사이의 교차점에 형성된다. 방전 셀들은 픽셀들로서 기능한다. 각 방전 셀은 방전 스페이스를 가진다. 플라즈마 디스플레이 장치는, 방전 스페이스에 연결된 각 방전 셀의 소정의 면 상에 형성되고 전자 빔 조사로 여기된 결과로서 200 내지 300 nm 파장 대역에서 피크를 가지는 캐소드 발광 광 방출을 수행하는 마그네슘 산화물 결정들을 가지는 마그네슘 산화물층을 포함한다. 플라즈마 디스플레이 장치는 또한 복수의 서브필드들의 각각에서의 영상 신호에 따라 행 전극 쌍들의 각각과 열 전극들의 각각에 구동 펄스를 인가함으로써 상기 방

전 스페이스에서 방전을 일으키는 구동부를 포함한다. 이 서브필드들은 영상 신호의 유닛 디스플레이 기간 (unit display period) 을 구성한다. 플라즈마 디스레이 장치는 또한 플라즈마 디스플레이 패널의 축적된 사용 시간에 따라 상기 구동 펄스의 펄스 전압치 및/또는 펄스 폭을 조정하는 제어부를 포함한다.

본 발명의 다른 양태에 따르면, 플라즈마 디스플레이 패널을 가지는 플라즈마 디스플레이 장치가 제공된다. 플라즈마 디스플레이 패널은 복수의 행 전극 쌍 및 복수의 열 전극들을 가진다. 행 전극 쌍들은 열 전극들에 수직으로 연장된다. 복수의 방전 셀들은 행 전극 쌍들과 열 전극들 사이의 교차점에서 형성된다. 각 방전 셀들은 방전 스페이스를 가진다. 플라즈마 디스플레이 장치는 방전 스페이스에 연결된 각 방전 셀의 소정의 면 상에 형성되고 전자 빔 조사로 여기된 결과로서 200 내지 300 nm 파장 대역에서 피크를 가지는 캐소드 발광 광 방출을 수행하는 마그네슘 산화물 결정들을 가지는 마그네슘 산화물층을 포함한다. 플라즈마 디스플레이 장치는 또한 복수의 서브필드들의 각각에서의 영상 신호에 따라 행 전극 쌍들의 각각과 열 전극들의 각각에 구동 펄스를 인가함으로써 방전 스페이스에서 방전을 일으키는 구동부를 포함한다. 이 서브필드들은 영상 신호의 유닛 디스플레이 기간을 구성한다. 또한, 플라즈마 디스플레이 장치는 플라즈마 디스플레이 패널의 온도를 검출하는 패널 온도 검출기를 포함한다. 플라즈마 디스플레이 장치는 또한 플라즈마 디스플레이 패널의 검출된 온도에 따라 구동 펄스의 펄스 폭을 변경하는 제어부를 포함한다.

## 발명의 구성

본 발명의 실시형태들은 도면을 참조하여 이하에서 상세하게 설명된다.

#### <u>제 1 실시형태</u>

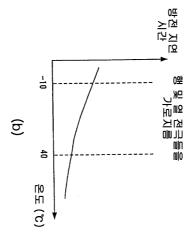

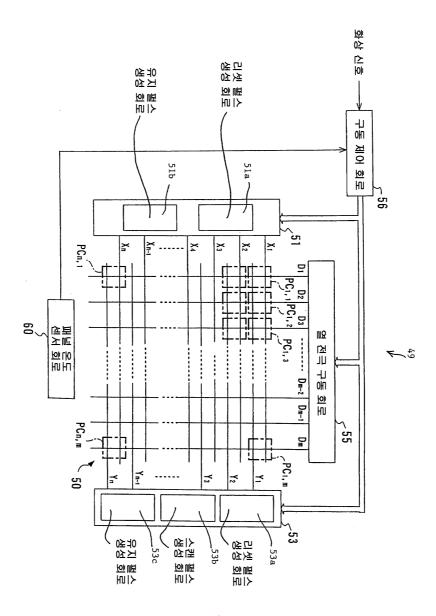

도 1 내지 도 16을 참조하여, 본 발명의 제 1 실시형태에 따른 플라즈마 디스플레이 장치 (49) 가 설명된다.

도 1 에 나타난 바와 같이, 플라즈마 디스플레이 장치 (49) 는 PDP (플라즈마 디스플레이 패널; plasma display panel; 50), 행 전극 X 구동 회로 (51), 행 전극 Y 구동 회로 (53), 열 전극 구동 회로 (55), 구동 제어 회로 (56), 사용 시간 카운터 (타이머) (57) 및 시변 (time-variant) 데이터 메모리 (58) 를 포함한다.

PDP (50) 는 열 전극들  $(D_1$  내지  $D_m$ ) 및 행 전극들  $(X_1$  내지  $X_n$  및  $Y_1$  내지  $Y_n$ ) 을 가진다. 열 전극들  $(D_1$  내지  $D_m$ ) 은 PDP (50) 의 2 차원의 디스플레이 스크린의 높이 방향 (수평 방향) 으로 연장된다. 행 전극들  $(X_1$  내지  $X_n$  및  $Y_1$  내지  $Y_n$ ) 은 PDP (50) 의 디스플레이 스크린의 폭 방향 (수평 방향) 으로 연장된다. 2 개의 인접한 열 전극들  $(X_i$  및  $Y_i$ ) 각각은 하나의 행 전극 쌍을 정의한다. 이 행 전극 쌍들  $((X_1, Y_1), (X_2, Y_2), (X_3, Y_3), ..., (X_n, Y_n))$  은 PDP (50) 내에 제 1 내지 1 대지 1 대 1 대지 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대 1 대

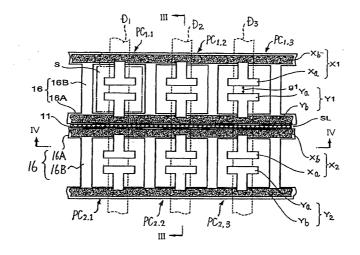

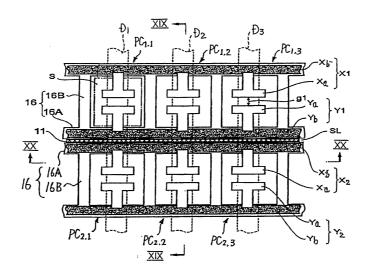

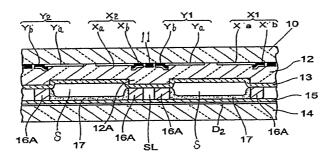

도 2는 디스플레이 스크린 측면으로부터 바라볼 때 PDP (50) 의 내부 구조를 개략적으로 나타낸 도면이다. 도 2는 PDP (50) 의 일부만을 도시한다. 구체적으로는, 열 전극들 ( $D_1$  내지  $D_3$ ) 과 PDP (50) 의 제 1 디스플레이 라인 ( $Y_1$ ,  $X_1$ ) 및 제 2 디스플레이 라인 ( $Y_2$ ,  $X_2$ ) 사이의 교차점들만이 도시된다. 도 3은 도 2의 선 III-III 을 따른 PDP (50) 의 단면도이고 도 4는 도 2의 선 IV-IV 을 따른 PDP (50) 의 단면도이다.

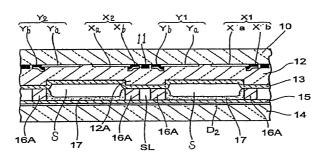

도 2 에 나타난 바와 같이, 행 전극들 (X) 의 각각은 디스플레이 스크린의 수평 방향으로 연장된 버스 전극 (Xb), 및 버스 전극 (Xb) 로부터 수직으로 연장된 복수의 T-형 투명 전극들 (Xa) 을 가진다. 각 T-형 투명 전극 (Xa) 은 방전 셀 (PC) 에 대응하여 제공된다. 행 전극들 (Y) 의 각각은 디스플레이 스크린의 수평 방향으로 연장된 버스 전극 (Yb), 및 버스 전극 (Yb) 으로부터 수직으로 연장된 복수의 T-형 투명 전극들 (Ya) 을 가진다. 각 T-형 투명 전극 (Ya) 은 방전 셀 (PC) 에 대응하여 제공된다. 투명 전극들 (Xa 및 Ya) 은 예를 들면, ITO 등의 투명 전기적 도전성 막으로 이루어지고, 버스 전극들 (Xb 및 Yb) 은 예를 들면, 금속막으로 이루어진다. 도 3 에 나타난 바와 같이, 행 전극들 (X) 및 행 전극들 (Y) 는 투명 기판 (10) 의 배면 측 상에 형성된다. 기판 (10) 은 PDP (50) 의 정면 (디스플레이 스크린) 이다. 각 행 전극 쌍 (X,Y) 에서, 투명 전극 (Xa) 는 짝 투명 전극 (Ya) 을 향해 연장되고, 이 투명 전극들 (Xa 및 Ya) 의 2 개의 T-헤드들 (head) 사이의 간격이 소정치의 방전 갭 (g1) 을 정의한다. 디스플레이 스크린의 수평 방향으로 연장된 흑색 또는 어두운 색상의 광 흡수층 (광-차단층; 11) 은 기판 (10) 의 배면 측 상에 2 개의 인접한 열 전극 쌍들 ((X1, Y1) 및 (X2, Y2)) 사이에 형성된다. 유전체층

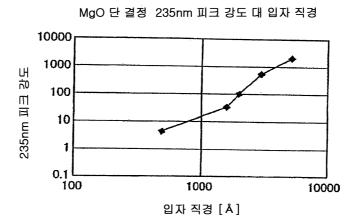

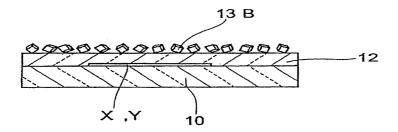

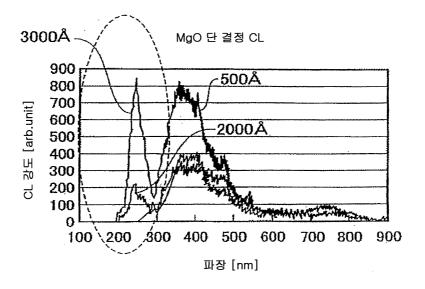

(12) 는 기판 (10) 의 배면 측 상에서 열 전극 쌍들 (X, Y) 를 커버링하도록 형성된다. 유전체층 (12) 는 상승된 (두꺼운) 부분 (12A) 을 가진다. 각 상승된 유전체층 (12A) 는 광 흡수층 (11) 과 인접한 버스 전극들 (Xb 및 Yb) 이 형성된 지역에 대응하는 부분에서 형성된다. 마그네슘 산화물 (MgO) 결정들을 포함하는 마그네슘 산화물층 (13) 은 유전체층과 상승된 부분들 (12A) 의 표면 상에 형성된다. 마그네슘 산화물층 (13) 은 전자 빔에 의해 조사된 때 여기된 200 내지 300nm 파장 대역에서 피크를 가지는 캐소드 발광 광 방출 (이하, 'CL 광 방출') 을 수행한다.

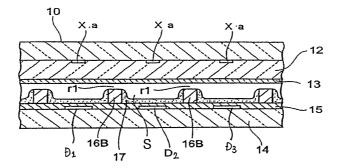

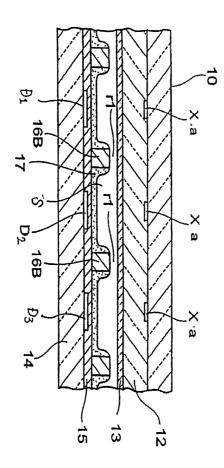

열 전극들 (D) 은 PDP (50) 의 배면 기판 (14) 상에 열 전극 쌍들 (X, Y) 과 수직인 방향으로 연장된다. 배면 기판 (14) 은 전면 기판 (10) 과 평행하다. 각 열 전극 (D) 은 열 전극 쌍들 (X, Y) 의 대응하는 투명 전극들 (Xa 및 Ya) 에 면한다. 또한 열 전극들 (D) 을 커버링하는 열 전극 보호층 (15) 도 배면 기판 (14) 상에 형성된다. 열 전극 보호층 (15) 은 백색이다. 배 리어 벽들 (barrier wall; 16) 은 열 전극 보호층 (15) 상에 형성된다. 각 배리어 벽 (16) 은 2 개의 수평 벽들 (16A) 및 복수 의 수직 벽들 (16B) 에 의해 격자 형태로 형성된다. 수평 벽들 (16A) 는 행 전극 쌍 (X, Y) 의 버스 전극들 (Xb 및 Yb) 에 대 응하는 위치에서 디스플레이 스크린의 폭 (수평) 방향으로 연장된다. 수직 벽들 (16B) 는 각각의 인접한 열 전극들 (D) 사 이의 중간 위치들에서 디스플레이 스크린의 높이 (수직) 방향으로 연장된다. 격자-형 배리어 벽 (16) 은 PDP (50) 의 디스 플레이 라인들의 각각에 대해 형성되고, 갭 (SL) 은 도 2 에 나타난 것처럼, 각 인접한 배리어 벽들 (16) 사이에 존재한다. 배리어 벽 (16) 은 복수의 방전 셀들 (PC) 을 규정한다. 각 방전 셀 (PC) 은 독립된 방전 스페이스 (S) 및 투명 전극들 (Xa 및 Yb) 을 가진다. 크세논 가스를 포함하는 방전 가스는 각 방전 스페이스 (S) 를 채운다. 도 3 에 나타난 바와 같이, 형광체 층 (17) 은 각 방전 셀 (PC) 내의 수평 벽 (16A) 의 측면, 수직 벽 (16B) 의 측면, 및 열 전극 보호층 (15) 의 표면을 완전히 커버링하도록 형성된다. 형광체층 (17) 은 적색 광을 방출하는 형광 물질, 녹색 광을 방출하는 형광 물질, 및 청색 광을 방 출하는 형광 물질인, 형광 물질의 3 가지 유형 중 하나이다. 도 3 에 나타난 바와 같이 마그네슘 산화물층 (13) 이 수평 벽 (16A) 에 접하기 때문에, 각 방전 셀 (PC) 내의 방전 스페이스 (S) 및 갭 (SL) 은 서로 고립된다. 반면에, 도 4 에 나타난 바 와 같이, 수직 벽 (16B) 은 마그네슘 산화물층 (13) 에 접하지 않기 때문에, 갭 (r1) 은 수직 벽 (16B) 과 마그네슘 산화물층 (13) 사이에 존재한다. 즉, 디스플레이 스크린의 폭 방향으로 연속적으로 배열된 각각의 방전 셀들 (PC) 의 방전 스페이스 들 (S) 은 갭들 (r1) 을 통해 서로 통신한다.

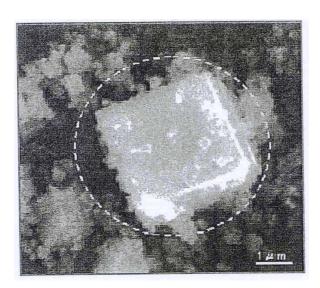

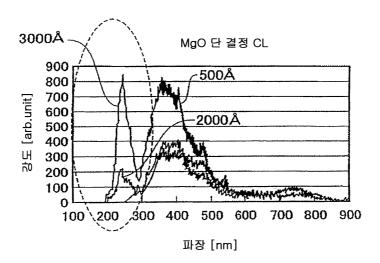

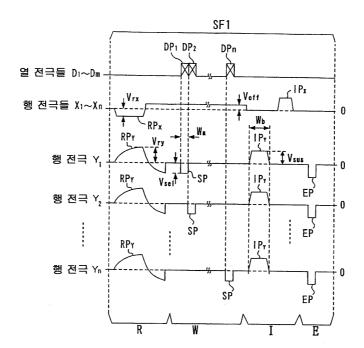

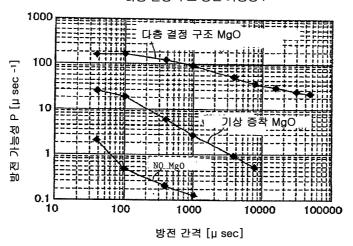

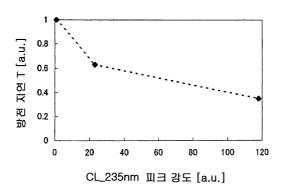

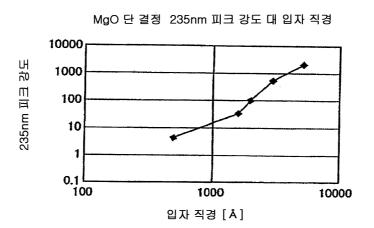

마그네슘 산화물층 (13) 의 마그네슘 산화 결정들은 마그네슘 증기를 기상 산화 (vapor phase oxidation) 시킴으로써 얻 어지는 기상 마그네슘 산화물 결정들을 포함한다. 마그네슘 증기는 마그네슘을 가열함으로써 생성된다. 기상 마그네슘 산 화물 결정들은 2000 옹스트롬 이상의 입자 직경의 마그네슘 단결정을 포함한다. 마그네슘 단결정들은 도 5a 의 SEM 사진 에서 나타난 바와 같은 큐빅 (cubic) 결정들이 함께 끼워져 있는 다층 결정 구조, 또는 도 5b 의 SEM 사진에서 나타난 바 와 같은 큐빅 단결정 구조를 가진다. 마그네슘 단결정들은 전자-빔 조사에 의해 여기된 때, 도 6 에 나타난 바와 같이 200 내지 300nm 파장 대역 (특히, 230 내지 250nm 내에서, 특히 235nm 부근) 에서 피크를 가지는 CL 광 방출을 수행한다. 이 러한 광 방출에서, 도 7 에 나타난 것과 같이, 기상 마그네슘 산화물 결정들의 입자 직경이 클수록, CL 광 방출의 피크 강도 가 크다. 즉, 마그네슘이 기상 마그네슘 산화물 결정들의 생성 중에 정상보다 높은 온도로 가열될 때, 도 5a 또는 5b 에 나 타난 것과 같이, 500 옹스트롬의 평균 입자 직경을 가지는 기상 마그네슘 산화물 단결정들 및 적어도 2000 옹스트롬의 입 자 직경을 가지는 상대적으로 큰 단결정들이 형성된다. 마그네슘의 가열 온도가 정상 온도보다 높기 때문에, 마그네슘이 산소와 반응할 때의 플레임 (flame) 들의 크기가 또한 커진다. 그러므로, 이 플레임들과 주변 사이에 온도 차이가 크고, 결 과적으로, 기상 마그네슘 산화물 단결정들의 입자 직경이 클수록, 200 내지 300nm (특히 235nm) 에 해당하는 높은 에너 지 레벨을 가지는 단결정들이 보다 많이 포함된다. 다른 방법으로 생성된 마그네슘 산화물과 비교해서, 기상 마그네슘 산 화물 결정들은 높은 순도 (pure), 미세한 입자, 및 작은 입자 응집력 (cohesion) 과 같은 특성을 가진다. 본 실시형태에서, 500 옹스트롬 이상의 평균 입자 직경을 가지고. 바람직하게는 2000 옹스트롬 이상의 평균 입자 직경을 가지는 기상 마그 네슘 산화물 단결정들이 채용된다. 입자 직경은 BET 방식으로 측정된다. 마그네슘 산화물층 (13) 은 스프레잉, 전자 코팅 등의 방식으로, 이러한 기상 마그네슘 산화물 단결정들이 도 8 에 도시된 것과 같이 유전체층 (12) 의 표면에 접착하도록 함으로써 형성된다. 다른 방법으로는, 마그네슘 산화물층 (13) 은 상승된 부분 (12A) 및 유전체층 (12) 의 표면 상에 기상 증착 또는 스퍼터링의 방식으로 박막 마그네슘 산화물층을 형성하고, 그 다음, 기상 마그네슘 산화물 단결정들이 박막 마 그네슘 산화물층에 접착하게 함으로써 형성된다.

행 전극 X 구동 회로 (51) 는 리셋 펄스 생성 회로 (51a) 및 유지 펄스 생성 회로 (51b) 를 포함한다. 행 전극 X 구동 회로 (51) 의 리셋 펄스 생성 회로 (51a) 는 구동 제어 회로 (56) 에 의해 공급되는 리셋 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 리셋 펄스를 생성하고, PDP (50) 의 행 전극들 (X) 에 리셋 펄스를 인가한다. 행 전극 X 구동 회로 (51) 의 유지 펄스 생성 회로 (51b) 는 구동 제어 회로 (56) 에 의해 공급되는 유지 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 유지 펄스를 생성하고, PDP (50) 의 행 전극들 (X) 에 유지 펄스를 인가한다. 행 전극 Y 구동 회로 (53) 은 리셋 펄스 생성 회로 (53a), 스캔 펄스 생성 회로 (52b), 및 유지 펄스 생성 회로 (53c) 를 포함한다. 행 전극 Y 구동 회로 (53) 의 리셋 펄스 생성 회로 (53a) 는 구동 제어 회로 (56) 에 의해 공급되는 리셋 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 리셋 펄스를 생성하고, PDP (50) 의 행 전극들 (Y) 에 리셋 펄스를 인가한다. 행 전극 Y 구동 회로 (53) 의 스캔 펄스 생성 회로 (53b) 는 구동 제어 회로 (56) 에 의해 공급되는 스캔 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 스캔 펄스

를 생성하고, PDP (50) 의 행 전극들  $(Y_1$  내지  $Y_n)$  에 스캔 펄스를 연속적으로 인가한다. 행 전극 Y 구동 회로 (53) 의 유지 펄스 생성 회로 (53c) 는 구동 제어 회로 (56) 에 의해 공급되는 유지 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 유지 펄스를 생성하고, PDP (50) 의 행 전극들 (Y) 에 유지 펄스를 인가한다. 열 전극 구동 회로 (55) 는 구동 제어 회로 (56) 에 의해 공급되는 픽셀 데이터 펄스 생성 신호에 따라 PDP (50) 의 열 전극들 (D) 에 인가되는 픽셀 데이터 펄스를 생성한다.

축적된 사용 시간 카운터 (57) 는 플라즈마 디스플레이 장치 (49) 가 켜진 상태일 때의 축적된 시간을 측정하고 구동 제어회로 (56) 와 시변 데이터 메모리 (58) 에 축적된 시간을 지시하는 축적된 사용 시간 정보를 공급한다.

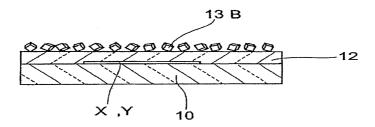

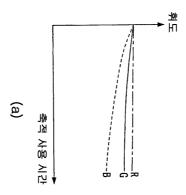

시변 데이터 메모리 (58) 는 예를 들어 도 9a 의 실선에 의해 지시되는 축적된 사용 시간에 대한 리셋 펄스의 최적 펄스 전압을 지시하는 정보, 도 9b 의 실선에 의해 지시되는 축적된 사용 시간에 대한 스캔 펄스의 최적 펄스 전압을 지시하는 정보, 및 도 9c 의 실선에 의해 지시되는 축적된 사용 시간에 대한 유지 펄스의 최적 펄스 전압을 지시하는 정보를 사전-저장한다. 시변 데이터 메모리 (58) 는 축적된 사용 시간 정보을 수신하고, 축적된 사용 시간 정보에 기초한 리셋 펄스, 스캔 펄스, 및 유지 펄스에 대한 최적의 펄스 전압치를 지시하는 정보를 판독하며, 구동 제어 회로 (56) 에 전압치 정보를 공급한다. 도 9b 및 9c 의 점선은 유지 펄스와 스캔 펄스의 펄스 전압에 대해 취해질 수 있는 최대 전압치의 전이를 지시하고, 도 9a 내지 9c 의 일점 쇄선은 리셋 펄스, 유지 펄스 및 스캔 펄스의 펄스 전압에 대해 취해질 수 있는 최소 전압치의 전이를지시한다. 도 9a 내지 9 c 로부터, 축적된 사용 시간이 증가할 때, 스캔 펄스의 최적 펄스 전압치는 유지 펄스의 최적 펄스 전압치보다 커지고, 리셋 펄스의 최적 펄스 전압치는 스캔 펄스의 최적 펄스 전압보다 커진다는 것이 이해된다.

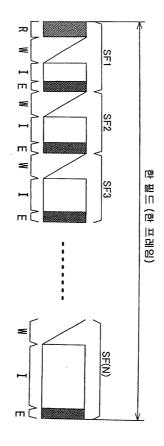

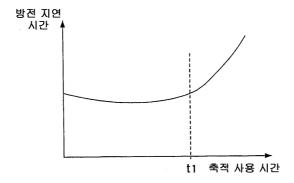

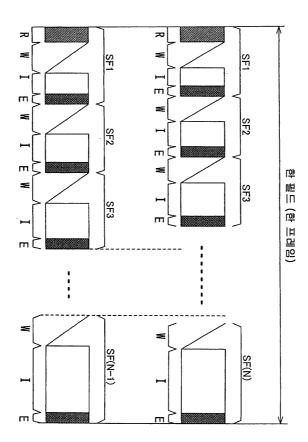

구동 제어 회로 (56) 는 도 10 에 나타난 광 방출 구동 시퀀스에 따라 PDP (50) 을 구동하기 위한 다양한 제어 신호들이, 행전극 X 구동 회로 (51), 행전극 Y 구동 회로 (53) 및 열전극 구동 회로 (55) 에 각각 공급된다. 도 10 의 광 방출 구동 시퀀스는 서브 필드 방법 (서브프레임 방법; subframe method) 에 기초한다. 한 필드 (한 프레임) 의 디스플레이 기간은 서브 필드 방법으로 N 개의 서브필드들로 나뉜다. 각 서브필드는 그 자체 가중치를 가진다. 이 광 방출 구동 시퀀스에서, 어드레스 프로세스 (W), 유지 프로세스 (I), 및 소거 프로세스 (E) 는 N 개의 서브필드들 (SF1 내지 SF(N)) 의 각각에서 연속적으로 실행된다. 리셋 프로세스 (R) 은 선두 (leading) 서브필드 (SF1) 에서만 어드레스 프로세스 (W) 전에 실행된다.

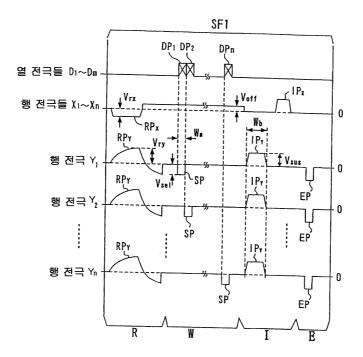

도 11 은 서브필드 (SF1) 에서 PDP (50) 의 열 전극들 (D) 및 행 전극들 (X 및 Y) 에 인가되는 다양한 구동 펄스들의 인가 타이밍을 나타낸다.

먼저, 리셋 프로세스 (R) 에서, 구동 제어 회로 (56) 는 행 전극 Y 구동 회로 (53) 와 행 전극 X 구동 회로 (51) 에 각각, 시 변 데이터 메모리 (58) 로부터 판독된 리셋 필스에 대한 최적 필스 전압치 (E 9a) 의 실선에 의해 지시됨) 를 지시하는 리셋 필스 생성 신호를 공급한다. 결과적으로, 도 11 에 나타난 바와 같이, 행 전극 Y 구동 회로 (53) 는, 행 전극들 (Y) 에 걸친 전압이 시간 경과에 따라 천천히 상승하는 선두 부분을 가지는 리셋 필스  $(RP_Y)$  를 생성하고 양극의 피크 전압 (Vry) 과 전 압치가 음극의 전압에 도달하도록 천천히 하강하는 트레일링 (Trailing) 부분에 도달하며, 리셋 필스  $(RP_Y)$  를 행 전극들  $(Y_1 \text{ 내지 } Y_n)$  에 동시에 인가한다. 행 전극 X 구동 회로 (51) 는 리셋 필스  $(RP_Y)$  의 전압치의 상승하는 부분의 길이 만큼, 도 11 에 도시된 것 같은 음극의 전압 (Vrx) 을 가진 리셋 필스  $(RP_X)$  를 생성하고 리셋 필스  $(RP_X)$  를 행 전극들  $(X_1 \text{ 내지 } X_n)$  에 각각 인가한다. 행 전극 Y 구동 회로 (53) 와 행 전극 X 구동 회로 (51) 는, 전압 (Vry) 의 절대치 및 전압 (Vrx) 의 절대치의 합이 리셋 필스 생성 신호에 의해 지시되는 최적의 필스 전압치와 같도록, 리셋 필스들  $(RP_Y)$  의 필스 전압 (Vry) 의 필스 전압 (Vry) 의 필스 전압 (Vrx) 의 필스 전압 (Vrx) 의 절대치와 리셋 필스  $(RP_Y)$  의 필스 전압 (Vrx) 의 절대치와 리셋 필스  $(RP_Y)$  의 필스 전압 (Vrx) 의 절대치와 리셋 필스  $(RP_Y)$  의 필스 전압 (Vrx) 의 절대치와 리셋 필스  $(RP_Y)$  의 필스 전압 (Vrx) 의 절대치와 리셋 필스  $(RP_Y)$  의 필스 전압 (Vrx) 의 절대치의 합이 그 시점에서 축적된 사용 시간에 의해 결정되는 최적 필스 전압치 (E 9a) 일선에 의해 지시됨) 와 같도록, 조정된다.

약한 기록 리셋 방전 (weak write reset discharge) 은 리셋 펄스들  $(RP_Y \ Q \ RP_X)$  이 인가되는 동안에 전체 방전 셀들  $(PC_{1,1} \ \text{내지 PC}_{n,m})$  의 각각에서 행 전극들  $(X \ Q \ Y)$  간에 유도된다. 기록 리셋 방전이 끝난 후에, 소정 양의 벽 전하가 각 방전 셀 (PC) 의 방전 스페이스 (S) 에서의 마그네슘 산화물층 (13) 의 표면에서 형성된다. 구체적으로는, 양극의 전하는 마그네슘 산화물층 (13) 의 표면 상의 행 전극들 (X) 의 근처에 형성되고 음극의 전하는 행 전극들 (Y) 의 근처에 형성된다. 그 후, 리셋 펄스  $(RP_X)$  의 전압이 Vry로부터 천천히 떨어질때, 약한 소거 리셋 방전이 방전 셀들  $(PC_{1,1} \ \text{내지 PC}_{n,m})$  의 전체에서 행 전극들  $(X \ Q \ Y)$  간의 간격 상에서 유도된다. 방전 셀들  $(PC_{1,1} \ \text{내지 PC}_{n,m})$  의 전체에서 형성된 벽 전하는 소거 리셋 방전의 결과로 없어진다. 즉, 리셋 프로세스 (R) 의 결과로, 방전 셀들  $(PC_{1,1} \ \text{내지 PC}_{n,m})$  의 전체는, 벽 전하의 양이 소정치보다 작은 소등 상태로서 초기화된다.

그 후, 어드레스 프로세스 (W) 에서, 구동 제어 회로 (56) 는 픽셀 데이터 펄스 생성 신호를 열 전극 구동 회로 (55) 에 공급 하고, 시변 데이터 메모리 (58) 로부터 판독되는 스캔 펄스의 최적 펄스 전압치 (도 9b 의 실선에 의해 지시됨) 를 지시하는 스캔 펄스 생성 신호를 행 전극 Y 구동 회로 (53) 에 공급한다. 결과적으로, 열 전극 구동 회로 (55) 는 먼저, 입력 영상 신 호를 기초하여, 방전 셀 (PC) 들 각각이 관련된 서브필드에서 광을 방출하도록 할 것인지를 결정하는 픽셀 데이터 펄스를 생성한다. 예를 들면, 열 전극 구동 회로 (55) 는 방전 셀 (PC) 이 광을 방출하도록 할 때에는 각 방전 셀 (PC) 에 대해 높은 전압의 픽셀 데이터 를 생성하고, 방전 셀 (PC) 이 광을 방출하도록 하지 않을 때에는 각 방전 셀 (PC) 에 대해 낮은 전압의 픽셀 데이터 펄스를 생성한다. 열 전극 구동 회로 (55) 는, 열 전극들 (D<sub>1</sub> 내지 D<sub>m</sub>) 에 픽셀 데이터 펄스 그룹들 (DP<sub>1</sub>,  $DP_2$ , ...  $DP_n$ ) 를 인가하는 것과 같이 하나의 디스플레이 라인에 해당하는 방전 셀들 (m 개의 방전 셀들) 에 이 픽셀 데이터 펄스를 연속적으로 한번에 인가한다. 행 전극 Y 구동 회로 (53) 는 픽셀 데이터 펄스 그룹들 (DP1, DP2, ... DP2) 의 각각의 타이밍과 동기로 열 전극들  $(Y_1 \ \text{내지}\ Y_n)$  에 음극의 전압 (Vsel) 을 가지는 스캔 펄스 (SP) 를 연속적으로 인가한다. 행 전 극 Y 구동 회로 (53) 는 전압 (Vsel) 이 스캔 펄스 생성 신호에 의해 지시된 최적 펄스 전압치와 같도록 스캔 펄스 (SP) 를 생성한다. 즉, 스캔 펄스 (SP) 의 펄스 전압 (Vsel) 은 그 시점에서 축적된 시간에 의해 결정되는 최적 펄스 전압치 (도 9b 의 실선으로 지시됨) 와 같도록 조정된다. 어드레스 방전은 스캔 펄스 (SP) 가 인가되고 높은 전압 픽셀 데이터 펄스가 인 가되는 방전 셀들 (PC) 에서만 유도되고, 소정 량의 벽 전하는 방전 셀 (PC) 의 방전 스페이스 (S) 에서 마그네슘 산화물층 (13) 및 형광체층 (17) 의 표면들에 각각 형성된다. 반면에, 어드레스 방전은 스캔 펄스 (SP) 가 인가되지만 낮은 전압 픽셀 데이터 펄스가 인가되는 방전 셀들 (PC) 에서는 유도되지 않아서, 이 시점 직전까지의 벽-전하 형성 상태가 유지된다. 즉, 어드레스 프로세스 (W) 의 실행의 결과로서, 방전 셀들 (PC) 의 각각은 입력 영상 신호에 기초하여 소정 양의 벽 전하가 존 재하는 점등 상태이거나 소정 양의 벽 전하가 존재하지 않는 소등 상태 중 하나로 된다.

유지 프로세스 (I) 에서, 구동 제어 회로 (56) 는 시변 데이터 메모리 (58) 으로부터 판독된 유지 펄스의 최적 펄스 전압치 (도 9c 의 실선으로 지시됨) 를 지시하는 유지 펄스 생성 신호를 행 전극 X 구동 회로 (51) 및 행 전극 Y 구동 회로 (53) 의 각각에 공급한다. 결과적으로, 행 전극 X 구동 회로 (51) 및 행 전극 Y 구동 회로 (53) 는 양자택일적으로 음극의 전압 (Vsus) 를 가지는 유지 펄스들 ( $\mathrm{IP}_{\mathrm{X}}$  및  $\mathrm{IP}_{\mathrm{Y}}$ ) 을 반복적으로 생성한다. 행 전극 Y 구동 회로 (53) 및 행 전극 X 구동 회로 (51) 는 전압 (Vsus) 가 유지 펄스 생성 신호에 의해 지시되는 최적 펄스 전압치와 같도록 유지 펄스들 ( $\mathrm{IP}_{\mathrm{Y}}$  및  $\mathrm{IP}_{\mathrm{Y}}$ ) 의 펄스 전압 (Vsus) 은 축적된 사용 시간에 의해 결정되는 최적 펄스 전압치 (도 9c 의 실선에 의해 지시됨) 와 같도록 조절된다. 유지 펄스들 ( $\mathrm{IP}_{\mathrm{X}}$  및  $\mathrm{IP}_{\mathrm{Y}}$ ) 이 인가되는 회수는 각 서브필드의 발광의 가중치에 의존한다. 유지 펄스들 ( $\mathrm{IP}_{\mathrm{X}}$  및  $\mathrm{IP}_{\mathrm{Y}}$ ) 이 인가되는 때마다, 소정 양의 벽 전하가 형성된 점등 모드 상태로 셋팅된 방전 셀들 (PC) 이 유지 방전을 일으키며, 이로써 형광체층 (17) 은 방전에 따라 광을 방출하고 영상은 패널의 디스플레이스크린 상에 형성된다.

소거 프로세스 (E) 에서, 행 전극 Y 구동 회로 (53) 은 양극의 소거 펄스 (EP) 를 모든 행 전극들 ( $Y_1$  내지  $Y_n$ ) 에 동시에 인가한다. 소거 방전은 소거 펄스 (EP) 의 이 인가의 결과로서 모든 방전 셀들 (PC) 에서 유도되고, 방전 셀들 (PC) 내에 남아있는 벽 전하들은 모두 제거 (소거) 된다.

상술한 바와 같이, 방전 셀들 (PC) 의 각각에서 형성된 마그네슘 산화물층 (13) 은 도 5a 및 5b 에 나타난 바와 같은 형상의 비교적 큰 (적어도 2000 옹스트롬) 기상 마그네슘 산화물 단결정들을 포함한다. 도 6 에서 나타난 바와 같이, 이 단결정들이 전자 범으로 조사될 때, 파장 대역 300 내지 400 nm 에서 피크를 가지는 CL 광 방출 및 파장 대역 200 내지 300 nm (구체적으로 230 내지 250nm, 보다 구체적으로 235 근처)에서 피크를 가지는 CL 광 방출이 유도되어서, 기상 마그네슘 산화물 단결정들은 235nm에 대응하는 에너지 레벨을 가지도록 고려된다. 235nm에 대응하는 에너지 레벨을 가지는 결과로서, 기상 마그네슘 산화물 단결정들은 장시간 (수 msec) 동안 전자들을 포획 (capture)한다. 전자가 선택적 방전 동안에 전기장의 인가를 통해 방전되도록 함으로써 방전에 요구되는 초기 전자들이 빠르게 획득되는 것이 추정된다. 따라서, 200 내지 300nm의 피크를 가지는 CL 광 방출에 대한 기상 마그네슘 산화물 단결정들은 도 3 에 나타난 바와 같이 마그네슘 산화물층 (13) 내에 포함되고, 방전 스페이스 (S)에서 방전이 유도되도록 요구되는 적당한 양의 전자들이 항상 존재한다. 따라서, 방전 스페이스 (S)에서의 방전 확률은 상당히 높다.

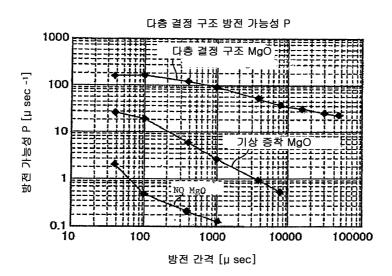

도 12 는 마그네슘 산화물층이 방전 셀들 (PC) 에 제공되지 않는 경우, 마그네슘 산화물층이 종래의 기상 증착 방식으로 형성되는 경우, 및 전자 범이 조사시 200 내지 300nm 의 피크를 가지는 CL 광 방출을 생성하는 다층 단결정 구조의 기상 마그네슘 산화물 단결정들로 이루어진 마그네슘 산화물층이 제공된 경우의 방전 확률을 나타낸다. 도 12 의 수평 축은 비방전 시간 또는 방전 간격, 즉 즉 방전이 유도된 때부터 다음 방전이 유도될 때까지를 나타낸다. 따라서, 전자 빔 조사의 결과로서 200 내지 300nm 의 피크을 가지는 CL 광 방출을 일으키는 기상 마그네슘 산화물 단결정들로 이루어진 마그네슘

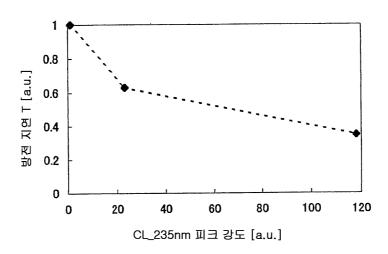

산화물층 (13) 이 각 방전 셀 (PC) 의 방전 스페이스 (S) 에서 형성될 때, 방전 확률이 마그네슘 산화물층이 종래의 기상 증착 방식으로 형성된 경우와 비교하여 증가한다. 도 13 에 나타난 바와 같이, 기상 마그네슘 산화물 단결정들이 전자 빔으로 조사될 때 CL 광 방출의 강도가 클수록, 구체적으로는 235nm의 피크를 가지는 CL 광 방출의 강도가 클수록, 방전 스페이스 (S) 에서 유도되는 방전 지연이 보다 크게 감소될 수 있다.

따라서, 리셋 방전이, 디스플레이 영상에 참여하지 않는 리셋 방전에 따라 광 방출을 억제함으로써 명암비 (contrast) 를 증가시키기 위해 도 11 에 나타난 것과 같이 행 전극들 (T) 에 인가되는 리셋 펼스 (RP<sub>Y</sub>) 의 전압 전이를 천천히 생성함으로써 약해지는 경우까지도, 약한 리셋 방전이 단기간 동안 안정적으로 유도될 수 있다. 구체적으로는, 방전 셀들 (PC) 의 각각은 T-형 투명 전극들 (Xa 및 Ya) 근처에서 국재된 (localized) 방전을 유도하기 위한 구조를 채택한다. 따라서, 행 전극의 전부의 방전을 일으키는 갑작스런 강한 리셋 방전은 억제되고 열 전극들과 행 전극들 상이의 강한 오류 방전도 또한 방지된다. 방전 확률이 높기 (방전 지연은 작음) 때문에, 리셋 프로세스 (R) 에서 기록 리셋 방전 및 소거 리셋 방전으로부터 생기는 프라이밍 (priming) 효과가 장시간 계속된다. 그러므로, 어드레스 프로세스 (W) 에서 유도된 어드레스 방전 및 유지 프로세스 (I) 에서 유도된 유지 방전이 가속된다. 결과적으로, 어드레스 방전을 유도하는 열 전극들 (D) 및 행 전극들 (Y) 에 인가되는 도 11 에 도시된 것과 같은 픽셀 테이터 펄스 (DP) 및 스캔 펄스 (SP) 의 펄스 폭 (Wa) 과 어드레스 프로세스 (W) 에 전용되는 처리 시간이 동일한 정도까지 짧아질 수 있다. 또한, 유지 방전을 유도하기 위한 행 전극들 (Y) 에 인가되는 도 11 에 도시된 것과 같은 유지 펄스 (IP<sub>Y</sub>) 의 펄스 폭 (Wb) 과 유지 프로세스 (I) 에 전용되는 처리 시간도 동일한 정도로 짧아질 수 있다. 따라서, 한 필드 (또는 한 프레임) 의 디스플레이 기간에 제공될 서브필드들의 개수는 어드레스 프로세스 (W) 및 유지 프로세스 (I) 에 각각 전용되는 처리 시간이 짧아지는 정도로 증가될 수 있다. 결국, 계조 (grayscale) 의 개수가 증가될 수 있다.

상술한 바와 같이, 각각의 방전 셀에서의 방전 확률은 전자 빔 조사시 200 내지 300nm 의 피크를 가지는 CL 광 방출을 일으키는 기상 마그네슘 산화물 단결정들로 이루어진 마그네슘 산화물층 (13) 을 제공함으로써 증가될 수 있다. 다만, 각 방전 셀에서의 방전 시작시의 전압이 증가하고, 오류 방전은 영년 변화 (secular variation) 의 결과로서 쉽게 생성된다.

이를 막기 위해, 도 1 에 도시된 플라즈마 디스플레이 장치에서는, 정확하게 리셋 방전, 어드레스 방전 및 유지 방전을 유도하는 것을 가능하게 하는 최적 펼스 전압치들에 대한 예측 정보가, 영년 변화를 수반하는 방전 시작 전압의 전이에 따라 도 9a 내지 9c 에 나타난 것처럼 사전 저장된다. 현재의 PDP (50) 의 축적된 사용 시간에 따른 리셋 펼스, 스캔 펼스, 및 유지 펼스 각각의 최적 펼스 전압치가 예측 정보로부터 추출되고, 리셋 펼스, 스캔 펼스, 및 유지 펼스의 펼스 전압치들이 각각의 최적 펼스 전압치들과 같도록 개별적으로 조정된다. 따라서, 방전 시작 전압이 시간을 거쳐 상승할 때에도, 오류 방전이 적거나 없는 양호한 디스플레이 품질이 장시간 동안 유지될 수 있다.

PDP (50) 의 축적된 사용 시간이 장시간에 이를 때, 방전 시작 전압의 증가가 발생하고 형광체층 (17) 의 저하를 수반하는 발광의 감소가 발생한다. 도 14a 에 나타난 것처럼, 형광체층 (17) 으로서 채용된 녹색 광 방출을 생기게 하는 형광을 가지는 방전 셀 (PC) 의 축적된 사용 시간에 따른 발광 감소 (실선으로 지시됨) 은 적색 광 방출을 생기게 하는 형광을 가지는 방전 셀 (PC) 의 발광 감소 (일점 쇄선으로 지시됨) 과 비교하여 크다. 청색 광 방출을 생기게 하는 형광에 대한 방전 셀 (PC) 의 축적된 사용 시간에 관련한 발광 감소 (점선으로 지시됨) 은 채용된 녹색 광 방출을 생기게 하는 형광에 대한 방전 셀 (PC) 의 발광 감소 (일점 쇄선으로 지시됨) 과 비교하여 크다. 따라서, 적색 광 방출을 일으키는 방전 셀들 (PC), 녹색 광 방출을 일으키는 방전 셀들 (PC), 및 청색 광 방출을 일으키는 방전 셀들 (PC) 의 발광 레벨의 변동은 영년 변화에 따라 증가한다. 이것이 백색 밸런스 (white balace) 가 적당한 값으로부터 시프팅되는 문제를 발생시킨다.

백색 밸런스에서의 이 시프팅을 보정하기 위해서, 도 14b 에 나타난 축적된 사용 시간에 대응하는 색상들 (R,G,B) 의 각각의 레벨 시프트 양을 지시하는 정보가 도 9a 내지 9c 에 나타난 것과 같은 정보와 함께 시변 데이터 메모리 (58) 에 저장된다. 시변 데이터 메모리 (58)는 현재 PDP (50)의 축적된 사용 시간에 대응하는 도 14b에 나타난 것과 같은 청색 신호 성분에 대한 레벨 시프트 양 (점선에 의해 지시됨), 녹색 신호 성분에 대한 레벨 시프트 양 (실선에 의해 지시됨), 및 적색 신호 성분에 대한 레벨 시프트 양 (일점 쇄선에 의해 지시됨)을 지시하는 정보를 판독하고, 구동 제어 회로 (56)에 이 정보를 공급한다. 구동 제어 회로 (56)는 시변 데이터 메모리 (58)로부터 이와 같이 판독되는 각 색상의 레벨 시프트 양들을이용하여 입력 영상 신호에서 적색 신호 성분, 녹색 신호 성분, 및 청색 신호 성분을 각각 조정한다. 도 14b에 나타난 것같이, PDP (50)의 축적된 사용 시간이 길어질수록, 적색 신호 성분에 에 대한 레벨 감소 양 (일점 쇄선에 의해 지시됨)이 녹색 신호 성분에 대한 레벨 감소 양 (실선에 의해 지시됨)보다 더 커진다. 녹색 신호 성분에 대한 레벨 감소 양은 청색 신호에 대한 레벨 감소 양 (점선에 의해 지시됨)보다 커진다.

따라서, 영년 변화의 결과로서 적색 광 방출을 일으키는 방전 셀 (PC), 녹색 광 방출을 일으키는 방전 셀 (PC), 및 청색 광 방출을 일으키는 방전 셀 (PC) 의 발광 레벨들의 불일치가 있을 때에도, 입력 영상 신호 스테이지에서 각 색상에 대한 레벨조정이 이루어져서, 이 레벨 조정이 장기간에 걸친 발광 레벨 불일치를 오프셋 (offset) 하는 적당한 백색 밸런스를 유지하는 것을 가능하게 한다.

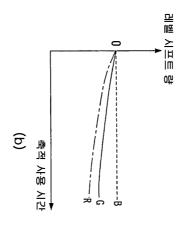

도 15 에 나타난 바와 같이, PDP (50) 의 축적된 사용 시간이 증가하고 소정의 시간 (t1) 이 경과한 때, 방전 지연이 행 전극들 (Y) 와 열 전극들 (D) 을 거쳐서 유도되는 어드레스 방전에서 상승하기 시작한다.

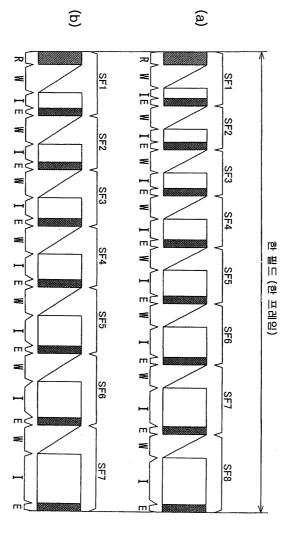

이 방전 지연을 해결하기 위해, 구동 제어 회로 (56) 은, 현재 PDP (50) 의 축적된 사용 시간이 도 15 에 나타난 것과 같은 소정의 시간 (t1) 을 초과할 때까지, 도 16a 에 나타난 것과 같은 광 방출 구동 시퀀스에 따른 계조 구동을 실행하고, 구동 제어 회로 (56) 는 시간 (t1) 이 초과될 때 도 16b 에 도시된 것과 같은 광 방출 구동 시퀀스에 따른 계조 구동을 실행한다. 도 16a 에 도시된 것과 같은 광 방출 구동 시퀀스에 따른 계조 구동을 실행한다. 도 16a 에 도시된 것과 같은 광 방출 구동 시퀀스는 한 필드 디스플레이 기간을 N 개의 서브필드들 (SF1 내지 SF(N)) 으로 분할함으로써 계조 구동을 수행하고, 도 10 에 도시된 것과 같은 광 방출 구동 시퀀스와 같다. 반면에, 도 16b 에 나타난 광 방출 구동 시퀀스는 도 10 에 나타난 광 방출 구동 시퀀스에서의 서브필드들의 개수를 하나씩 줄임으로써 (N-1) 개의 서 브필드들을 생성하는 것에 의해 만들어진다. 어드레스 프로세스 (W), 유지 프로세스 (I) 및 소거 프로세스 (E) 가 각 서브 필드에서 연속적으로 실행된다는 사실, 및 리셋 프로세스 (R) 이 제 1 서브필드 (SF1) 에서만 홀로 어드레스 프로세스 전에 실행된다는 사실은 도 10 에 나타난 광 방출 구동 시퀀스에 관하여 동일하다. 도 16b 에 나타난 구동이 실행될 때, 각 서브 필드의 어드레스 프로세스 (W) 에서 인가된 스캔 펄스 (SP) (또는 픽셀 데이터 펄스 (DP)) 의 펄스 폭 (Wa) 및 각 서브 필드의 유지 프로세스 (I) 에서 처음 인가된 유지 펄스 (IP<sub>Y</sub>) 의 펄스 폭 (Wb) 은 서브필드들의 개수를 하나씩 줄임으로써 생성되는 양 (시간) 에 의해 각각 넓어진다.

결과적으로, 심지어 방전 지연이 장시간 사용의 결과로서 어드레스 방전에서 일어날 때에도, 방전은 신뢰성이 높게 유도될 수 있다.

상술한 실시형태에서는 행 전극들 (X 및 Y) 은 전면 기판 (10) 상에 형성되고 열 전극 (D) 및 형광체층 (17) 은 배면 기판 (14) 상에 형성되지만, 행 전극들 (X 및 Y) 은 전면 기판 (10) 상에 열 전극들 (D) 과 함께 형성될 수 있고 형광체층 (17) 은 배면 기판 (14) 상에 형성될 수 있다.

#### 제 2 실시형태

이하, 본 발명의 제 2 실시형태가 도 17 내지 29 를 참조하여 상세하게 설명된다.

도 17 은 본 발명의 제 2 실시형태의 플라즈마 디스플레이 장치 (49) 의 개략적인 구성을 나타낸다. 유사한 도면 번호들과 기호들은 제 1 및 제 2 실시형태들에서 유사한 구성요소들에게 할당된다.

도 17 에 나타난 바와 같이, 플라즈마 디스플레이 장치 (49) 는 PDP (50), 행 전극 X 구동 회로 (51), 행 전극 Y 구동 회로 (53), 열 전극 구동 회로 (55), 구동 제어 회로 (56), 패널 온도 센서 (60) 를 포함한다.

$D_m$ ) 사이의 교차점 (도 1 에서 일점 쇄선으로 둘러싸인 지역들) 에서 형성된다. 구체적으로는, 제 1 디스플레이 라인에 속한 방전 셀들 ( $PC_{1,1}$  내지  $PC_{1,m}$ ), 제 2 디스플레이 라인에 속한 방전 셀들 ( $PC_{2,1}$  내지  $PC_{2,m}$ ), ... 제 n 디스플레이 라인에 속한 방전 셀들 ( $PC_{n-1}$  내지  $PC_{n-m}$ ) 은 PDP (50) 내에 매트릭스 형으로 정렬된다.

도 18는 디스플레이 스크린 측면으로부터 바라볼 때 PDP (50) 의 내부 구조를 개략적으로 나타낸 도면이다. 도 18 에서는, 열 전극들  $(D_1$  내지  $D_3)$  과 PDP (50) 의 제 1 디스플레이 라인  $(Y_1, X_1)$  및 제 2 디스플레이 라인  $(Y_2, X_2)$  사이의 교차 점들이 도시된다. 도 19은 도 18의 선 XIX-XIX 을 따른 PDP (50) 의 단면도이고 도 20는 도 18의 선 XX-XX 을 따른 PDP (50) 의 단면도이다.

도 18 에 나타난 바와 같이, 행 전극들 (X) 의 각각은 디스플레이 스크린의 수평 방향으로 연장된 버스 전극 (Xb), 및 버스 전극 (Xb) 로부터 수직으로 연장된 복수의 T-형 투명 전극들 (Xa) 을 가진다. 각 투명 전극 (Xa) 은 대응하는 방전 셀 (PC) 의 위치에 연장된다. 행 전극들 (Y) 의 각각은 디스플레이 스크린의 수평 방향으로 연장된 버스 전극 (Yb), 및 버스 전극 (Yb) 으로부터 수직으로 연장된 복수의 T-형 투명 전극들 (Ya) 을 가진다. 각 투명 전극 (Ya) 은 대응하는 방전 셀 (PC) 의 위치에 제공된다. 투명 전극들 (Xa 및 Ya) 은 예를 들면, ITO 등의 투명 전기적 도전성 막으로 이루어지고, 버스 전극들 (Xb 및 Yb) 은 예를 들면, 금속막으로 이루어진다. 도 19 에 나타난 바와 같이, 행 전극들 (X) 및 행 전극들 (Y) 는 전면 투명 기판 (10) 의 배면 측 상에 형성된다. 전면 기판 (10) 은 PDP (50) 의 디스플레이 스크린 면이다. 각 행 전극 쌍 (X,Y) 에서, 투명 전극 (Xa) 는 짝 투명 전극 (Ya) 을 향해 연장된다. 소정 길이의 방전 갭 (g1) 이 짝 T-헤드 전극들 (Xa 및 Ya) 사이에 형성된다. 디스플레이 스크린의 수평 방향으로 연장된 흑색 또는 어두운 색상의 광 흡수층 (광-차단층; 11) 은 전면 기판 (10) 의 배면 측 상에 행 전극 쌍 (X<sub>1</sub>, Y<sub>1</sub>) 과 인접한 행 전극 쌍 (X<sub>2</sub>, Y<sub>2</sub>) 사이에 형성된다. 유전체층 (12) 는 전면 기판 (10) 의 배면 측 상에서 행 전극 쌍들 (X, Y) 를 커버링하도록 형성된다. 유전체층 (12) 는 아래로 연장되는 상승된 부분 (12A) 을 가진다. 도 19 에 나타난 바와 같이, 상승된 유전체층 (12A) 는 광 흡수층 (11) 과 인접한 버스 전극들 (Xb 및 Yb) 이 형성된 지역에 대응하는 부분에서 형성된다. 마그네슘 산화물층 (13) 은 유전체층 (12) 과 상승된 유전체층 (12A) 의 표면 상에 형성된다. 마그네슘 산화물층 (13) 은 전자 빔에 의해 조사에 의해 여기된 때 200 내지 300nm 파장 대역에서 피크를 가지는 캐소드 발광 광 방출을 수행한다.

열 전극들 (D) 의 각각은 행 전극 쌍들 (X, Y) 의 투명 전극들 (Xa 및 Ya) 에 면하도록 배면 기판 (14) 상에 행 전극 쌍들 (X, Y) 과 수직인 방향으로 연장된다. 배면 기판 (14) 은 전면 투명 전극 (10) 과 평행하게 배열된다. 또한, 열 전극들 (D) 을 커버링하는 백색 열 전극 보호층 (15) 도 배면 기판 (14) 상에 형성된다. 배리어 벽들 (16) 은 열 전극 보호층 (15) 상에 형성된다. 각 배리어 벽 (16) 은 2 개의 수평 벽들 (16A) 및 복수의 수직 벽들 (16B) 에 의해 격자 형태로 형성된다. 수평 벽들 (16A) 는 행 전극 쌍 (X, Y) 의 버스 전극들 (Xb 및 Yb) 에 대응하는 위치에서 디스플레이 스크린의 폭 방향으로 연장 되고, 수직 벽들 (16B) 는 각각의 인접한 열 전극들 (D) 사이의 중간 위치들에서 디스플레이 스크린의 수직 방향으로 연장 된다. 격자-형 배리어 벽 (16) 은 도 18 에서 나타난 것과 같이 PDP (50) 의 디스플레이 라인들의 각각에 대해 형성되고, 갭 (SL) 은 도 18 에 나타난 것처럼, 각 인접한 배리어 벽들 (16) 사이에 존재한다. 각각 독립된 방전 스페이스 (S) 및 투명 전극들 (Xa 및 Yb) 을 가진 방전 셀들 (PC) 은 격자형 배리어 벽 (16) 에 의해 분할된다. 크세논 가스를 포함하는 방전 가스 는 각 방전 스페이스 (S) 를 채운다. 도 19 에 나타난 바와 같이, 형광체층 (17) 은 각 방전 셀 (PC) 내의 수평 벽 (16A) 의 측면, 수직 벽 (16B) 의 측면, 및 열 전극 보호층 (15) 의 표면을 완전히 커버링하도록 형성된다. 형광체층 (17) 은 적색 광 을 방출하는 형광 물질, 녹색 광을 방출하는 형광 물질, 및 청색 광을 방출하는 형광 물질인, 형광 물질의 3 가지 유형 중 하 나이다. 도 19 에 나타난 바와 같이 마그네슘 산화물층 (13) 이 수평 벽 (16A) 에 접하기 때문에, 각 방전 셀 (PC) 의 방전 스페이스 (S) 및 갭 (SL) 은 서로 고립된다. 반면에, 도 20 에 나타난 바와 같이, 수직 벽 (16B) 은 마그네슘 산화물층 (13) 에 면하지 않기 때문에, 갭 (r1) 은 수직 벽 (16B) 과 마그네슘 산화물층 (13) 사이에 존재한다. 즉, 디스플레이 스크린의 폭 방향으로 인접한 각각의 방전 셀들 (PC) 의 방전 스페이스들 (S) 은 갭들 (r1) 을 통해 서로 통신한다.

마그네슘 산화물층 (13) 의 마그네슘 산화 결정들은 마그네슘을 가열하여 생산된 마그네슘 증기를 기상 산화시킴으로써 얻어지는 단결정들이다. 이러한 단결정들의 일 실시예는 예를 들면 전자 빔 조사에 의해 여기된 때 200 내지 300nm 파장 대역 (특히, 230 내지 250nm 의 대역에서 235nm 에 근접) 에서 피크를 가지는 CL 광 방출을 수행하는 기상 마그네슘 산화물 결정들은, 도 21a 의 SEM 사진 영상에서 나타난 바와 같은 큐빅 (cubic) 결정들이함께 끼워져 있는 다층 결정 구조, 또는 도 21b 의 SEM 사진 영상에서 나타난 바와 같은 큐빅 단결정 구조를 가지는 2000 옹스트롬 이상의 입자 직경의 마그네슘 단결정들을 포함한다. 다른 방법으로 생성된 마그네슘 산화물과 비교해서, 이 마그네슘 단결정들은 높은 순도, 미세한 입자, 및 작은 입자 응집력 (덩어리; agglomeration) 과 같은 특성들을 가진다. 이 특성들은 방전 지연과 같은 방전 특성들에서의 향상에 기여한다. 이 실시형태에서, 이 실시형태에서, BET 방식으로 측정된 500 옹스트롬 이상의 평균 입자 직경을 가지고, 바람직하게는 2000 옹스트롬 이상의 평균 입자 직경을 가지는 기상 마그네슘 산화물 단결정들이 채용된다. 마그네슘 산화물층 (13) 은 스프레잉, 정전기 코팅 등의 방식으로 도 22 에 도시된 것과

같이, 이러한 기상 마그네슘 산화물 단결정들이 유전체층 (12) 의 표면에 접착하도록 함으로써 형성된다. 다른 방법으로는, 마그네슘 산화물층 (13) 은 상승된 부분 (12A) 및 유전체층 (12) 의 표면 상에 기상 증착 또는 스퍼터링의 방식으로 박막 마그네슘 산화물층을 형성하고, 그 다음, 기상 마그네슘 산화물 단결정들이 박막 마그네슘 산화물층에 접착하게 함으로써 형성된다.

행 전극 X 구동 회로 (51) 는 리셋 펄스 생성 회로 (51a) 및 유지 펄스 생성 회로 (51b) 를 가진다.

행 전극 X 구동 회로 (51) 의 리셋 펄스 생성 회로 (51a) 는 구동 제어 회로 (56) 에 의해 공급되는 리셋 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 리셋 펄스를 생성하고, PDP (50) 의 행 전극들 (X) 에 리셋 펄스를 인가한다. 행 전극 X 구동 회로 (51) 의 유지 펄스 생성 회로 (51b) 는 구동 제어 회로 (56) 에 의해 공급되는 유지 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 리셋 펄스를 생성하고, PDP (50) 의 행 전극들 (X) 에 유지 펄스를 인가한다.

행 전국 Y 구동 회로 (53) 은 리셋 펄스 생성 회로 (53a), 스캔 펄스 생성 회로 (52b), 및 유지 펄스 생성 회로 (53c) 를 포함 한다.

행 전극 Y 구동 회로 (53) 의 리셋 펼스 생성 회로 (53a) 는 구동 제어 회로 (56) 에 의해 공급되는 리셋 펼스 생성 신호에 의해 지시되는 펼스 전압을 가지는 리셋 펄스를 생성하고, PDP (50) 의 행 전극들 (Y) 에 리셋 펄스를 인가한다. 행 전극 Y 구동 회로 (53) 의 스캔 펄스 생성 회로 (53b) 는 구동 제어 회로 (56) 에 의해 공급되는 스캔 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 스캔 펄스를 생성하고, PDP (50) 의 행 전극들  $(Y_1 \text{ 내지 } Y_n)$  에 스캔 펄스를 연속적으로 인가한다. 행 전극 Y 구동 회로 (53) 의 유지 펄스 생성 회로 (53c) 는 구동 제어 회로 (56) 에 의해 공급되는 유지 펄스 생성 신호에 의해 지시되는 펄스 전압을 가지는 유지 펄스를 생성하고, PDP (50) 의 행 전극들 (Y) 에 유지 펄스를 인가한다. 열 전극 구동 회로 (55) 는 구동 제어 회로 (56) 에 의해 공급되는 픽셀 데이터 펄스 생성 신호에 따라 PDP (50) 의 열 전극들 (D) 에 인가되는 픽셀 데이터 펄스를 생성한다.

패널 온도 센서 (60) 는 PDP (50) 의 온도를 측정하고 검출된 온도를 나타내는 패널 온도 신호를 구동 제어 회로 (56) 에 제공한다. 예를 들어, 패널 온도 센서 (60) 는 소정의 간격으로 PDP 온도를 측정한다.

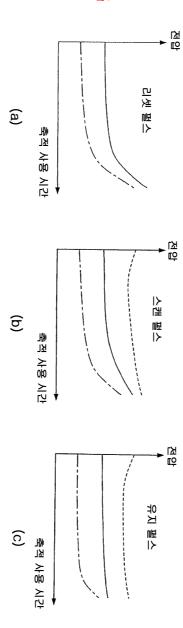

구동 제어 회로 (56) 는, 패널 온도 신호에 의해 나타나는 PDP (50) 의 온도가 소정의 온도 (예를 들어, 10 ℃) 이상인 경우에는, 도 23a 에 도시된 광 방출 구동 시퀀스에 따르고, PDP (50) 의 온도가 소정의 온도보다 낮은 경우에는, 도 23b 에 도시된 광 방출 구동 시퀀스에 따라, PDP (50) 를 구동시키는 다양한 제어 신호들을 행 전극 X 구동 회로 (51), 행 전극 Y 구동 회로 (53) 및 열 전극 구동 회로 (55) 로 제공한다.

도 23a 및 도 23b 에 도시된 광 방출 구동 시퀀스는 상술한 서브필드 방법에 기초하여 PDP (50) 의 중간계조 구동을 구현한다. 도 23a 에 도시된 광 방출 구동 시퀀스에서, 이미지 디스플레이의 한 필드 (또는 한 프레임) 에 해당하는 8 개의 서브필드들 (SF1 내지 SF8) 로 나누어지며, 도 23b 에 도시된 광 방출 구동 시퀀스에서, 이미지 디스플레이의 한 필드 (또는 한 프레임의) 에 해당하는 7 개의 서브필드들 (SF1 내지 SF7) 로 나누어진다. 도 23a 및 도 23b 에 도시된 광 방출 구동 시퀀스들 모두에서, 어드레스 프로세스 (W), 유지 프로세스 (I) 및 소거 프로세스 (E) 는 서브필드들 각각에서 순차적으로 수행된다. 리셋 프로세스 (R) 는 선두 서브필드 (SF1) 에서만 어드레스 프로세스 (W) 이전에 수행된다. 각 서브필드는 각자의가중치를 가진다.

도 24 는 제 1 서브필드 (SF1) 동안 PDP (50) 의 행 전극들 (X 및 Y) 및 열 전극 (D) 에 인가되는 다양한 구동 펄스들의 인가 시간을 도시한다.

우선, 도 24 에 나타난 바와 같이, 리셋 프로세스 (R) 에서, 행 전극 (Y) 구동 회로 (53) 는, 시간이 경과함에 따라 행 전극 (Y) 의 전압이 서서히 상승하여 양의 피크 전압  $(V_{ry})$  에 이르는 선두 부분 및 전압 값이 서서히 낮아져 음의 전압에 이르는 트레일링 부분을 가지는 리셋 펄스  $(RP_Y)$  를 생성하고, 동시에 상술한 리셋 펄스  $(RP_Y)$  를 행 전극들  $(Y_1$  내지  $Y_n)$  에 인가한다. 행 전극 (X) 구동 회로 (51) 는 리셋 펄스  $(RP_Y)$  의 전압 값이 상승하는 부분만큼 도 24 에 도시된 바와 같은 음의 전압  $V_{rx}$  를 가지는 리셋 펄스  $(RP_X)$  를 생성하여, 상술한 리셋 펄스  $(RP_X)$  를 행 전극들  $(X_1$  내지  $(X_1)$  에 각각 인가한다. 리셋 펄스  $(RP_Y)$  및  $(RP_Y)$  가 인가되는 동안, 약한 기록 리셋 방전이 모든 방전 셀들  $(PC_{1,1})$  내지  $(RP_1)$  가 인가되는 동안, 약한 기록 리셋 방전이 종료된 후, 소정 양의 벽  $(RP_1)$  가 안전 셀  $(RP_2)$  의 방전 공간 내의 마그네슘 산화물층 (13) 의 표면에 형성된다. 특히, 양의 전하가 마그네슘 산화물층 (13) 의 표면상의 행 전극들 (X) 의 근방에 형성되고, 음의 전하가 행 전극들 (Y) 의 근방에 형성된다. 그 후, 리셋 펄스  $(RP_Y)$  의 전압이  $(P_1)$  로부

터 서서히 감소하는 경우, 약한 소거 리셋 방전이 모든 방전 셀들  $(PC_{1,1}$  내지  $PC_{n,m}$ ) 내의 행 전극들  $(X \ Q \ Y)$  에 걸쳐 이 간격으로 유도된다. 모든 방전 셀들  $(PC_{1,1}$  내지  $PC_{n,m}$ ) 내에 형성된 벽 전하들은 소거 리셋 방전의 결과 제거된다. 즉, 리셋 프로세스 (R) 의 결과에 따라, 모든 방전 셀들  $(PC_{1,1}$  내지  $PC_{n,m}$ ) 이 벽 전하의 양이 소정 양보다 적은 소등 상태로 초기화된다.

어드레스 프로세서 (W) 에서, 열 전극 구동 회로 (55)는 입력 영상 신호에 기초하여, 관련된 서브필드에서 방전 셀들 (PC) 각각이 광을 방출하도록 할 것인지 여부를 판단하기 위해 픽셀 데이터 필스를 생성한다. 예를 들어, 열 전극 구동 회로 (55)는, 방전 셀 (PC)가 광을 방출하도록 하는 경우에는, 각 방전 셀 (PC)을 위해 고 전압의 픽셀 데이터 필스를, 방전 셀 (PC)가 광을 방출하도록 하지 않는 경우에는, 저 전압의 픽셀 데이터 필스를 생성한다. 열 전극 구동 회로 (55)는 한번에 하나의 디스플레이 라인 (m) 대의 디스플레이 라인)에 대해 이 픽셀 데이터 필스를 픽셀 데이터 필스 그룹  $(DP_1,DP_2,...,DP_n)$ 으로서 열 전극들  $(D_1$  내지  $D_m)$ 에 순차적으로 인가한다. 행 전극 (Y) 구동 회로 (53)는 음의 전압을 가진 스캔 필스를 행 전극들  $(Y_1$  내지  $Y_n)$ 에 픽셀 데이터 필스 그룹들  $(DP_1$  내지 (PC)0가 각각의 타이밍과 동기로 순차적으로 인가한다. 어드레스 방전은 스캔 필스 (SP)7가 인가되고, 고 전압 픽셀 데이터 필스가 인가되는 이러한 방전 셀들 (PC)1에서만 유도된다. 이 어드레스 방전이 종료된 후, 소정 양의 벽 전하는 방전 셀 (PC)1의 방전 공간 (PC)2가 인가되지만 저 전압 픽셀 데이터 필스가 인가되는 방전 셀들 (PC)3에서는 유도되지 않는다. 따라서, 벽-전하 형성은 이러한 방전 셀들 (PC)4가 인지되기 기 직전까지 진행된다(State-up). 즉, 어드레스 프로세스 (W)4의 실행의 결과로서, 방전 셀들 (PC)4 각각은, 입력 영상 신호에 기초하여 소정 양의 벽 전하가 존재하는 점등 상태 또는 소정 양의 벽 전하가 존재하지 않는 소등 상태로 설정된다.

도 23b 에 도시된 구동이 수행되는 경우, 열 전극 구동 회로 (55) 및 행 전극 구동 회로 (53) 는, 도 23a 에 도시된 구동이 수행되는 경우와 비교하여 넓은 펄스 폭 (Wa) 을 가지는 픽셀 데이터 펄스 (DP) 및 스캔 펄스 (SP) 를 생성한다. 즉, PDP (50) 의 패널 온도가 소정의 온도보다 낮은 경우에는, 픽셀 데이터 펄스 (DP) 및 스캔 펄스 (SP) 의 펄스 폭 (Wa) 은 PDP (50) 의 패널 온도가 소정의 온도보다 높은 경우와 비교하여 넓게 된다.

유지 프로세스 (I) 에서, 행 전극 (X) 구동 회로 (51) 및 행 전극 (Y) 구동 회로 (53) 은 양의 전압 ( $V_{SUS}$ ) 를 가지는 유지 필스 ( $IP_X$  및  $IP_Y$ ) 를 관련된 서브필드의 가중치에 대응하는 많은 횟수에 걸쳐 반복적으로 생성하고, 반대로 도 24 에 나타난 바와 같이 유지 필스 ( $IP_X$  및  $IP_Y$ ) 를 행 전극들 ( $X_1$  내지  $X_n$ ) 및 행 전극들 ( $Y_1$  내지  $Y_n$ ) 로 인가한다. 유지 필스들 ( $IP_X$  및  $IP_Y$ ) 이 인가될 때마다, 소정 양의 벽 전하가 형성된 점등 상태로 설정되었던 방전 셀들 (PC) 에서만 유지 방전을 생성하며, 이에 의해 형광체층 (17) 은 방전에 따라 광을 방출하고 영상은 패널의 면 (디스플레이 스크린) 상에 형성된다.

도 23b 에 도시된 구동이 수행되는 경우, 행 전극 (X) 구동 회로 (51) 및 행 전극 (Y) 구동 회로 (53) 는 유지 프로세스 (I) 에서 우선 인가되는 유지 펄스  $(IP_Y)$  에 대하여만 도 23a 에 도시된 구동이 수행되는 경우와 비교하여 넓어진 펄스 폭 (Wb) 를 가지는 유지 펄스를 생성한다.

소거 프로세스 (E) 에서, 행 전극 (Y) 구동 회로 (53) 은 양의 극성을 가지는 소거 펄스 (EP) 를 모든 행 전극  $(Y_1$  내지  $Y_n)$ 에 동시에 인가한다. 소거 펄스 (EP) 의 인가 결과로서, 소거 방전이 모든 방전 셀들 (PC) 에서 유도되며, 방전 셀들 (PC) 내에 남아있는 벽 전하는 제거된다.

상술한 바와 같이, 각 디스플레이 셀들 (PC) 에 형성된 마그네슘 산화물층 (13) 내에 포함된 기상 마그네슘 산화물 단결정은, 전자 빔 조사에 의한 여기 시 도 25 에 나타난 바와 같이 200 내지 300 nm (특히 230 내지 250 nm 이내인 234 nm 에 근처) 파장대역을 가지는 CL 광 방출을 수행한다. 도 26 에 나타난 바와 같이, 기상 마그네슘 산화물 결정들의 입자 직경이 클수록, CL 광 방출의 피크 강도는 더 커진다. 즉, 증기-상태 마그네슘 산화물 결정들의 생성 동안 일반적인 온도보다 높은 온도에서 마그네슘을 가열하는 경우, 500 옹스트롬의 평균 입자 직경을 가지는 증기-상태 마그네슘 산화물 단결정들 및 2000 옹스트롬 이상의 입자 직경을 가지는 상대적으로 큰 단결정들이 도 21a 또는 도 21b 에 나타난 바와 같이 형성된다. 또한, 마그네슘이 가열될 때의 온도가 일반적인 온도보다 높기 때문에, 마그네슘이 산소와 반응할 때의 플레임들의 크기는 크다. 따라서, 이러한 플레임들과 주변 사이의 온도 차이는 크며, 그 결과 증기-상태 마그네슘 산화물 단결정이 큰 입자 직경을 가질 때, 200 내지 300 nm (특히, 235 nm 에 근방) 에 대응하는 높은 에너지 레벨을 가지는 많은 단결정들이 포함된다.

도 27 은 마그네슘 산화물층이 방전 셀 (PC) 에 제공되지 않는 경우, 마그네슘 산화물층이 종래의 기상 증착에 의해 형성되는 경우, 및 전자 빔 조사에 의해 200 nm 내지 300 nm (자세하게는 230 nm 내지 250 nm, 더 자세하게는 235 nm 근처)의 파장 대역에서 피크를 갖는 CL 광 방출을 생성하는 기상 마그네슘 산화물 단결정들을 갖는 마그네슘 산화물층이 제공되는 경우의 방전 확률을 도시한다. 도 27 에서의 수평 축은 방전 간격, 즉 방전이 유도되는 때로부터 후속의 방전이 유도되는 때까지의 시간 간격을 나타낸다.

따라서, 도 21a 또는 도 21b 에 나타난 바와 같이, 전자 빔 조사의 결과로 200 nm 내지 300 nm (자세하게는 230 nm 내지 250 nm, 더 자세하게는 235 nm 근처) 자의 파장 대역에서 피크를 갖는 CL 광 방출에 영향을 미치는 기상 마그네슘 산화물 단결정들을 포함하는 마그네슘 산화물층 (13) 이 방전 셀 (PC) 각각의 방전 스페이스 (S) 에서 형성되면, 방전 확률은 마그네슘 산화물층이 종래의 기상 증착 방식에 의해 형성되는 경우와 비교하여 증가한다. 도 28 에 나타난 바와 같이, 특히, 기상 마그네슘 산화물 단결정이 전자 빔으로 조사될 때 235 nm 파장 대역의 피크를 갖는 CL 광 방출의 강도가 커질수록, 방전 스페이스 (S) 에서 유도된 방전 지연은 감소될 수 있다.

따라서, 디스플레이 영상에서 역할을 하지 않는 리셋 방전에 따라 광 방출을 억제하여 콘트라스트를 증가시키기 위해서, 도 24 에 나타난 바와 같이 행 전극 Y 에 인가되는 리셋 펼스  $RP_Y$  의 전압 변화를 천천히 발생시켜, 리셋 방전을 약하게 하는 때에도, 이 약한 리셋 방전은 단시간 내에 안정적으로 유도될 수 있다. 특히, 방전 셀 (PC) 각각은 T-형 투명 전극들 (Xa 및 Ya) 사이의 방전 갭 근처에서 국재된 방전을 유도하는 구조를 채용한다. 따라서, 행 전극 전체의 방전을 초래하는 갑작스런 강한 리셋 방전은 억제되고, 열 전극과 행 전극 사이의 강한 오류 방전 또한 방지된다. 방전 확률은 증가되기 때문에, 리셋 프로세스 (R) 의 기록 리셋 방전 및 소거 리셋 방전으로부터 초래되는 프라이밍 효과는 오랫동안 지속된다. 따라서, 어드레스 프로세스 (W) 에서 유도된 어드레스 방전 및 유지 프로세스 (I) 에서 유도된 유지 방전은 가속화된다. 결과적으로, 도 24 에 나타난 바와 같이, 어드레스 방전을 유도하도록 열 전극 (D) 및 행 전극 (Y) 에 인가되는 픽셀 테이터 펼스 (DP) 및 스캔 펼스 (SP) 의 펼스 폭 (Wa) 은 감소될 수 있으며, 어드레스 프로세스 (W) 에 소요되는 처리 시간은 동일한 정도로 감소될 수 있다. 또한, 유지 방전을 유도하기 위해서 행 전극 X 및 Y 에 인가되는 유지 펄스 (IP) 의 펼스 폭도 감소될 수 있으며, 유지 프로세스 (I) 에 소요되는 처리 시간도 동일한 정도로 감소될 수 있다. 따라서, 한 필드 (또는 한 프레임)의 디스플레이 기간에 제공될 서브필드의 수는, 어드레스 프로세스 (W) 및 유지 프로세스 (I) 에 각각 소요되는 처리 시간 이 감소되는 정도로 증가될 수 있다. 따라서, 계조의 수는 증가될 수 있다.

상술한 바와 같이, 각 방전 셀의 방전 확률은, 전자 빔 조사의 결과로써 200 nm 내지 300 nm 파장 대역의 피크를 갖는 CL 광 방출에 영향을 미치는 기상 마그네슘 산화물 단결정들을 갖는 마그네슘 산화물층 (13) 을 제공함으로써 증가될 수 있다.

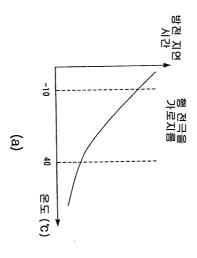

그러나, PDP (50) 의 패널 온도가 떨어질 때, 도 29a 에 도시된 바와 같은 방전 지연은 각 방전 셀의 행 전극 X 및 Y 를 통해 유도된 유지 방전에서 생성되며, 도 29b 에 도시된 바와 같은 방전 지연은 행 전극 Y 및 열 전극 D 를 통해 유도된 어드 레스 방전에서 생성된다. 따라서, 어드레스 방전 및 유지 방전을 유도하기 위해서 인가되는 스캔 펼스 및 유지 펼스의 펄스 폭이 감소될 때, 방전은 쉽게 유도되지 않는다.

따라서, 이러한 실시형태에서는, PDP (50) 의 패널 온도가 소정의 온도 이상일 때, PDP (50) 은 도 23a 에 나타난 바와 같이 8 개의 서브필드 SF1 내지 SF8 에서 계조-구동되며, PDP (50) 의 패널 온도가 소정의 온도 미만일 때, PDP (50) 은 도 23b 에 나타난 바와 같이 7 개의 서브필드 SF1 내지 SF7 에서 계조-구동된다. 즉, PDP (50) 의 패널 온도가 낮을 때, 한 필드 (또는 프레임) 디스플레이 기간을 구동시키기 위한 서브필드의 수는 감소되고, 스캔 펼스 (픽셀 데이터 펄스) 및 유지 펄스의 펄스 폭은 이 서브필드 감소만큼 확대된다. 결과적으로, 방전 지연이 온도 하강에 의해 야기될 때조차도, 방전이 쉽게 유도될 수 있다.

본 발명은 상술한 설명 및 도시된 실시형태에 한정되지 않는다. 예를 들어, 상술한 실시형태에서는 방전 셀 (PC) 은 각 행전극 쌍  $(X_1,Y_1), (X_2,Y_2), (X_3,Y_3),...,(X_n,Y_n)$ 의 행 전극 (X) 및 행 전극 (Y) 사이에서 형성되지만, 방전 셀 (PC) 은 모든 인접한 행 전극들 사이에서 형성될 수도 있다. 더 자세하게는, 방전 셀 (PC)은 행 전극  $(X_1,Y_1)$ , 행 전극  $(Y_1,Y_1)$ , 행 전극  $(Y_1,Y_2)$ , 행 전극  $(X_2,Y_2)$ , ..., 행 전극  $(Y_1,Y_2)$ , 및 행 전극  $(X_2,Y_1)$  사이에서 형성될 수도 있다.

상술한 실시형태에서 행 전국 (X 및 Y) 는 전면 기판 (10) 상에서 형성되고, 열 전국 D 와 형광체층 (17) 은 배면 기판 (14) 상에 형성되지만, 행 전국 (X 및 Y) 은 전면 기판 (10) 상에서 열 전국 (D) 와 함께 형성될 수도 있으며, 형광체층 (17) 은 배면 기판 (14) 상에서 형성될 수도 있다.

이 명세서는 2004 년 9 월 24 일에 출원된 일본 특허 출원 제 2004-276976 호 및 2004 년 10 월 8 일에 출원된 일본 특허 출원 제 2004-0296001 호에 기초하며, 이들 2 개의 출원에 개시된 전체는 여기에 참조로서 포함된다.

#### 발명의 효과

본 발명은 장기간 사용에 의해 일어나는 영상 저하를 억제할 수 있는 플라즈마 디스플레이 장치를 제공한다.

본 발명은 낮은 온도에서 오류 방전을 억제함으로써, 낮은 온도에서 조차 좋은 영상 품질을 유지할 수 있는 플라즈마 디스 플레이 장치를 제공한다.

## 도면의 간단한 설명

도 1 은 본 발명의 제 1 실시형태에 따른 플라즈마 디스플레이 장치의 개략적인 구성도.

도 2 는 디스플레이 스크린 측면으로부터 바라볼 때 도 1 에 도시된 플라즈마 디스플레이 장치에 장착된 PDP 의 내부 구조를 개략적으로 도시한 정면도.

도 3 은 도 2 에서의 선 III-III 에 따라 취해진 단면도.

도 4 는 도 2 에서의 선 IV-IV 에 따라 취해진 단면도.

도 5a 는 마그네슘 산화물 단결정들의 실시예의 도면.

도 5b 는 마그네슘 산화물 단결정들의 다른 실시예의 도면.

도 6 은 마그네슘 산화물 단결정들의 입자 직경과 CL 광 방출의 파장 사이의 관계를 나타낸 그래프.

도 7 은 마그네슘 산화물 단결정들의 입자 직경과 235nm CL 광 방출의 강도 사이의 관계를 나타낸 그래프.

도 8 은 마그네슘 산화물 단결정 미세 파우더가 상승된 부분을 포함하는 유전체층의 표면에 부착되도록 함으로써 형성된 마그네슘 산화물층의 도면.

도 9a 는 PDP 의 축적된 사용 시간에 관련하여 리셋 펄스의 최적의 펄스 전압에 대한 예측 정보를 도시한 그래프.

도 9b 는 PDP 의 축적된 사용 시간에 관련하여 스캔 펄스의 최적의 펄스 전압에 대한 예측 정보를 도시한 그래프.

도 9c 는 PDP 의 축적된 사용 시간에 관련하여 유지 펄스의 최적의 펄스 전압에 대한 예측 정보를 도시한 그래프.

도 10 은 도 1 에 도시된 플라즈마 디스플레이 장치에 적합한 광 방출 구동 시퀸스의 실시예의 도면.

도 11 은 도 10 에 도시된 광 방출 구동 시퀸스에 따라 PDP 에 인가되는 다양한 구동 펄스들과 구동 펄스들의 인가 타이밍의 도면.

도 12는 마그네슘 산화물층이 방전 셀에 제공되지 않는 경우, 마그네슘 산화물이 종래의 기상 증착의 방식으로 형성되는 경우, 및 전자 빔 조사된 때 200 내지 300 nm 의 피크를 가지는 CL 광 방출을 생성하는 기상 마그네슘 산화물 단결정들을 가지는 마그네슘 산화물층이 제공되는 경우의 방전 확률들의 그래프.

도 13 은 235 nm 피크 CL 광 방출 강도와 방전 지연 시간 사이의 관계의 그래프.

도 14a 는 PDP 의 축적된 사용 시간 동안의 각 색상의 발광 저하의 전이의 그래프.

도 14b 는 PDP 의 축적된 사용 시간 동안의 각 색상에 대한 영상 신호의 레벨 시프트의 전이의 그래프.

도 15 는 PDP 의 축적된 사용 시간 동안 어드레스 방전의 방전 지연 시간의 전이의 그래프.

도 16a 및 16b 는 도 1 에 도시된 플라즈마 디스플레이 장치에 의해 구성된 광 방출 구동 시퀀스들의 다른 실시예들의 도면.

도 17 은 본 발명의 제 2 실시형태에 따른 플라즈마 디스플레이 장치의 개략적인 구성도.

도 18 은 디스플레이 스크린 측면으로부터 바라볼 때 도 17 의 플라즈마 디스플레이 장치에 장착된 PDP 의 내부 구조를 개략적으로 도시한 정면도.

도 19 는 도 18 에 도시된 선 XIX-XIX 을 따른 단면도.

도 20 은 도 18 에 도시된 선 XX-XX 을 따른 단면도.

도 21a 은 마그네슘 산화물 단결정들의 실시예의 도면.

도 21b 는 마그네슘 산화물 단결정들의 다른 실시예의 도면.

도 22 는 마그네슘 산화물 단결정들이 상승된 부분을 포함하는 유전체층의 표면에 부착되도록 함으로써 형성된 마그네슘 산화물층의 도면.

도 23a 및 23b 도 17 에 도시된 플라즈마 디스플레이 장치에 의해 구성된 광 방출 구동 시퀀스들의 실시예의 도면

도 24 는 도 23a 및 도 23b 에 도시된 광 방출 구동 시쿼스에 따라 PDP 에 인가되는 다양한 구동 펄스들과 구동 펄스들의 인가 타이밍의 도면.

도 25는 마그네슘 산화물 단결정들의 입자 직경과 CL 광 방출의 파장 사이의 관계를 나타낸 그래프.

도 26 은 마그네슘 산화물 단결정들의 입자 직경과 235nm CL 광 방출의 강도 사이의 관계를 나타낸 그래프.

도 27 은 마그네슘 산화물층이 방전 셀에 제공되지 않는 경우, 마그네슘 산화물이 종래의 기상 증착의 방식으로 형성되는 경우, 및 전자 빔 조사된 때 200 내지 300 nm 의 피크를 가지는 CL 광 방출을 생성하는 기상 마그네슘 산화물 단결정들을 가지는 마그네슘 산화물층이 제공되는 경우의 방전 확률들의 그래프.

도 28 은 235 nm 피크 CL 광 방출 강도와 방전 지연 시간 사이의 관계를 나타낸 그래프.

도 29a 는 디스플레이 패널 온도와 행 전극들 사이에 생성된 방전 지연 사이의 관계를 나타낸 그래프.

도 29b 는 디스플레이 패널 온도와, 행 전극과 열 전극 사이에 생성된 방전 지연 사이의 관계를 나타낸 그래프.

\*도면의 주요부분에 대한 부호의 설명\*

50: PDP 10: 전면 기판

11 : 광 흡수층 12 : 유전체층

13: 마그네슘 산화물층 14: 배면 기판

15 : 열 전극 보호층 16 : 배리어 벽

51: 행 전극 X 구동 회로 51a: 리셋 펄스 생성 회로

51b : 스캔 펄스 생성 회로 51c : 유지 펄스 생성 회로

53 : 행 전극 Y 구동 회로 53a : 리셋 펄스 생성 회로

53b: 스캔 펄스 생성 회로 53c: 유지 펄스 생성 회로

56 : 구동 제어 회로 57 : 축적된 사용 시간 카운터

58: 시변 데이터 메모리

## 도면

도면3

도면4

도면5a

도면5b

도면6

도면11

다층 결정 구조 방전 가능성 P

도면14

도면15

도면18

도면20

도면21a

도면21b

도면22

도면26

도면27

도면28