(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5173758号

(P5173758)

(45) 発行日 平成25年4月3日(2013.4.3)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl.

F 1

|              |           |              |   |

|--------------|-----------|--------------|---|

| HO 1 L 25/04 | (2006.01) | HO 1 L 25/04 | Z |

| HO 1 L 25/18 | (2006.01) | HO 1 L 23/12 | L |

| HO 1 L 23/12 | (2006.01) | HO 5 K 3/46  | Q |

| HO 5 K 3/46  | (2006.01) |              |   |

請求項の数 10 (全 11 頁)

(21) 出願番号

特願2008-292987 (P2008-292987)

(22) 出願日

平成20年11月17日 (2008.11.17)

(65) 公開番号

特開2010-123592 (P2010-123592A)

(43) 公開日

平成22年6月3日 (2010.6.3)

審査請求日

平成23年9月22日 (2011.9.22)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100077621

弁理士 綿貫 隆夫

(74) 代理人 100092819

弁理士 堀米 和春

(74) 代理人 100141450

弁理士 堀内 刚

(72) 発明者 国本 裕治

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 石野 忠志

最終頁に続く

(54) 【発明の名称】半導体パッケージの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

厚さの異なる複数の半導体素子を、それぞれの電極端子の端子面が同一面となるように、該電極端子が形成された端子形成面側で板体の一面側に剥離可能に接着した後、前記複数の半導体素子を、前記端子形成面に対して反対面側で支持板の一面側に形成した樹脂層に固着し、

次いで、前記板体を剥離して露出した前記半導体素子の電極端子の端子面にバンプを形成した後、前記バンプを含む前記複数の半導体素子の各端子形成面を覆う絶縁層を形成し、

その後、前記絶縁層を研磨又は切削して前記バンプの先端面を露出した後、前記絶縁層上に、前記バンプの先端面に接続する配線パターンを形成することを特徴とする半導体パッケージの製造方法。

## 【請求項 2】

前記複数の半導体素子の電極端子に形成された前記バンプが、前記先端面が前記端子面よりも小面積に形成された先細り状のバンプである請求項1記載の半導体パッケージの製造方法。

## 【請求項 3】

厚さの異なる複数の半導体素子を、それぞれの電極端子の端子面が同一面となるように、該電極端子が形成された端子形成面側で板体の一面側に剥離可能に接着した後、前記複数の半導体素子を、前記端子形成面に対して反対面側で支持板の一面側に形成した樹脂層

10

20

に固着し、

次いで、前記板体を剥離して露出した前記半導体素子の一部の電極端子の端子面に、先端面が該端子面よりも小面積に形成された先細り状のバンプを形成した後、該先細り状のバンプを含む前記複数の半導体素子の各端子形成面を覆う絶縁層を形成し、

その後、前記絶縁層を研磨又は切削して前記先細り状のバンプの先端面を露出した後、前記先細り状のバンプを形成しない電極端子の端子面が底面に露出するように前記絶縁層に凹部を形成し、その後、該凹部をめっき金属で充填することによって柱状のバンプを形成し、

その後、前記絶縁層上に、前記先細り状のバンプの先端面に接続する配線パターンと前記柱状のバンプに接続する配線パターンとを各々形成することを特徴とする半導体パッケージの製造方法。

#### 【請求項 4】

前記半導体素子の電極端子に金属ワイヤの端部を圧着した後、該金属ワイヤを引き千切って形成した先端部をコイニングして前記先細り状のバンプを形成する請求項 2 または 3 記載の半導体パッケージの製造方法。

#### 【請求項 5】

前記金属ワイヤを、金から成るワイヤとする請求項 4 記載の半導体パッケージの製造方法。

#### 【請求項 6】

前記支持板を金属製の支持板とする請求項 1 ~ 5 のいずれか一項記載の半導体パッケージの製造方法。

#### 【請求項 7】

厚さの薄い半導体素子を、該厚さの薄い半導体素子の端子形成面に対して反対面と前記支持板の一面との間に前記樹脂層を介在させて、前記支持板の一面側に前記樹脂層によって固着し、

前記厚さの薄い半導体素子よりも厚さの厚い半導体素子を、該厚さの厚い半導体素子の端子形成面に対して反対面が前記支持板の一面に直接接触した状態で、前記支持板の一面側に前記樹脂層によって固着する請求項 1 ~ 6 のいずれか一項記載の半導体パッケージの製造方法。

#### 【請求項 8】

厚さの薄い半導体素子を、該厚さの薄い半導体素子の端子形成面に対して反対面と前記支持板の一面との間に前記樹脂層を介在させて、前記支持板の一面側に前記樹脂層によって固着し、

前記厚さの薄い半導体素子よりも厚さの厚い半導体素子を、該厚さの厚い半導体素子の端子形成面に対して反対面と前記支持板の一面との間に前記樹脂層を介在させて、前記支持板の一面側に前記樹脂層によって固着し、

前記厚さの薄い半導体素子の反対面と前記支持板の一面との間に介在する前記樹脂層の高さを、前記厚さの厚い半導体素子の反対面と前記支持板の一面との間に介在する前記樹脂層の高さよりも高くする請求項 1 ~ 6 のいずれか一項記載の半導体パッケージの製造方法。

#### 【請求項 9】

前記半導体素子の端子形成面から側面の少なくとも一部にかけて該半導体素子を前記絶縁層で覆う請求項 1 ~ 8 のいずれか一項記載の半導体パッケージの製造方法。

#### 【請求項 10】

前記配線パターン上に、更に他の絶縁層と配線パターンを多層に積層する請求項 1 ~ 9 のいずれか一項記載の半導体パッケージの製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は半導体パッケージの製造方法に関し、更に詳細には複数の半導体素子が搭載さ

10

20

30

40

50

れている半導体パッケージの製造方法に関する。

**【背景技術】**

**【0002】**

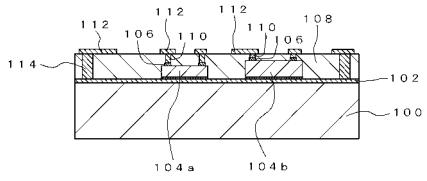

複数の半導体素子が搭載された半導体パッケージについては、例えば下記特許文献1に記載されている。かかる半導体パッケージを図6に示す。図6に示す半導体パッケージでは、ベース基板100の一面側に形成された、アース用の導体層102に、厚さの異なる半導体素子104a, 104bの底面が接着されている。かかる半導体素子104a, 104bの表面側に形成された各電極端子106は、絶縁層108を貫通するバンプ110を介して、絶縁樹脂層108の表面に形成された配線パターン112に電気的に接続されている。

10

また、導体層102に一端が接続された導電プロック114の他端が、絶縁層108の表面に形成された配線パターン112に電気的に接続されている。

**【0003】**

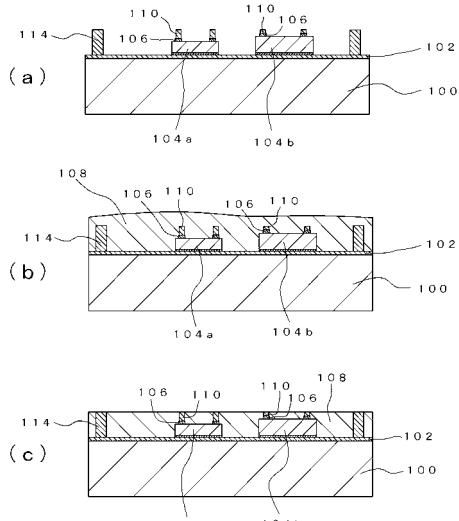

図6に示す半導体パッケージは、図7に示す製造方法で得ることができる。図7に示す製造方法では、先ず、図7(a)に示す様に、ベース基板100の一面側に形成した、アース用の導体層102に、導電プロック114を立設すると共に、厚さの異なる半導体素子104a, 104bの底面を接着し、その表面側に形成された電極端子106, 106···の各々に、電極端子106と略同一径のバンプ110を形成する。形成したバンプ110, 110···の各長さは、半導体素子104a, 104bで異なるが、バンプ110, 110···の各先端面は、導電プロック114の先端面と同一面内である。

20

次いで、図7(b)に示す様に、形成した導電プロック114、バンプ110を含む半導体素子104a, 104bの端子形成面側を絶縁樹脂層108によって覆った後、絶縁樹脂層108の表面を研磨又は研削して平坦面として、図7(c)に示す様に、導電プロック114、バンプ110の先端面を露出する。

その後、導電プロック114、バンプ110の各先端面が露出した絶縁樹脂層108の平坦面に、配線パターン112, 112···を形成して、図6に示す半導体パッケージを得ることができる。

**【特許文献1】特開平10-223832号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

30

**【0004】**

図6及び図7に示す半導体パッケージでは、同一の半導体パッケージ内に厚さの異なる複数の半導体素子を設けることができる。

しかし、図6及び図7に示す半導体パッケージでは、ベース基板100の一面側に底面を接着した厚さの異なる半導体素子104a, 104bの電極端子106, 106···の各々に、形成する電極端子106と略同一径のバンプ110を、各先端面が同一面となるように形成している。

一方、近年、半導体素子104a, 104bの小型化等に伴って、電極端子106, 106···の形成密度が高密度化してきている。

しかし、図6及び図7に示す半導体パッケージでは、電極端子106と略同一径のバンプ110を形成しているため、バンプ110の露出面から引き出す配線パターンの微細化は困難である。

40

しかも、隣接するバンプ110, 110の露出面間の間隙(バンプの露出面間隙と称することがある)が狭いため、バンプ110の露出面から引き出す配線パターンの微細化が困難であることと相俟って、バンプの露出面間隙を通して引き回すことのできる配線パターン数が著しく制限され、配線パターンの高密度化を図ることは困難である。

また、一般的には、図6及び図7に示す半導体パッケージの如く、厚さの異なる半導体素子104a, 104bの各電極端子106に、先端面が同一面となるように、長さの異なるバンプ110, 110···を形成する際には、半導体素子104a, 104bの各電極端子106を覆う樹脂層を形成した後、この樹脂層に各電極端子106の表面が底面に

50

露出する凹部をレーザによって形成し、次いで、電解めっきによってめっき金属を凹部内に充填してバンプ 110 を形成することが考えられる。

しかしながら、レーザによって樹脂層に形成した凹部は、通常、底面積よりも開口部面積が大きくなるテーパ状凹部に形成されるため、最終的に得られるバンプは電極端子 106 に接続する接続面よりも絶縁樹脂層 108 の表面に露出する露出面の面積が大きくなる。このため、バンプ 110 の露出面から引き出す配線パターンが幅広化され、且つ隣接するバンプ 110, 110 のバンプの露出面間隙も半導体素子 104a, 104b の隣接する電極端子 106, 106 の間隙よりも更に狭くなり、バンプの露出面間隙を通して引き回すことのできる配線パターン数が更に一層制限される。

そこで、本発明の課題は、支持板の一面側に固着された厚さの異なる複数の半導体素子の各電極端子に形成されたバンプの露出面間隙を通して引き回すことのできる配線パターンの高密度化を図ることが困難な従来の半導体パッケージの課題を解決し、支持板の一面側に固着された厚さの異なる複数の半導体素子の各電極端子に形成されたバンプの露出面間隙を通して引き回すことのできる配線パターンの高密度化を図ることができる半導体パッケージ及びその製造方法を提供することにある。10

#### 【課題を解決するための手段】

##### 【0005】

本発明者は、前記課題を解決すべく検討した結果、厚さの異なる複数の半導体素子を、電極端子の端子面が同一面となるように支持板の一面側に固着し、且つ半導体素子の電極端子に形成した先細り状のバンプを、半導体素子の端子形成面側を覆う絶縁層を貫通して形成することによって、絶縁層の表面に露出するバンプの露出面間を通して引き回すことのできる配線パターンの高密度化を図ることを見出し、本発明に到達した。20

すなわち、本発明は、厚さの異なる複数の半導体素子を、それぞれの電極端子の端子面が同一面となるように、該電極端子が形成された端子形成面側で板体の一面側に剥離可能に接着した後、前記複数の半導体素子を、前記端子形成面に対して反対面側で支持板的一面側に形成した樹脂層に固着し、次いで、前記板体を剥離して露出した前記半導体素子の電極端子の端子面にバンプを形成した後、前記バンプを含む前記複数の半導体素子の各端子形成面を覆う絶縁層を形成し、その後、前記絶縁層を研磨又は切削して前記バンプの先端面を露出した後、前記絶縁層上に、前記バンプの先端面に接続する配線パターンを形成することを特徴とする半導体パッケージの製造方法にある。30

##### 【0006】

かかる本発明において、前記複数の半導体素子の電極端子に形成された前記バンプが、前記先端面が前記端子面よりも小面積に形成された先細り状のバンプであることによつて、各半導体素子の電極端子に亘ってバンプの露出面間隙を通して引き回すことのできる配線パターンの高密度化を図ることができる。

また、前記複数の半導体素子の電極端子に形成された前記バンプが、前記先細り状のバンプと柱状のバンプとからなることによつて、電極端子の用途に応じて最適なバンプ、例えば信号用の電極端子には先細り状のバンプを形成し、電源用や接地用の電極端子には柱状のバンプを形成できる。

かかる前記先細り状のバンプとしては、前記半導体素子の電極端子に一端部を圧着した金属ワイヤにより形成できる。この前記金属ワイヤが、金から成るワイヤであることが好みしい。

更に、前記支持板を、放熱板として用いることのできる金属製の支持板とすることによつて、半導体パッケージの放熱性を向上できる。

また、厚さの薄い半導体素子は、該厚さの薄い半導体素子の端子形成面に対して反対面と前記支持板の一面との間に前記樹脂層が介在して、前記支持板の一面側に前記樹脂層によって固着され、前記厚さの薄い半導体素子よりも厚さの厚い半導体素子は、該厚さの厚い半導体素子の端子形成面に対して反対面が前記支持板の一面に直接接触した状態で、前記支持板の一面側に前記樹脂層によって固着されている。

また、厚さの薄い半導体素子は、該厚さの薄い半導体素子の端子形成面に対して反対面50

と前記支持板の一面との間に前記樹脂層が介在して、前記支持板の一面側に前記樹脂層によって固着され、前記厚さの薄い半導体素子よりも厚さの厚い半導体素子は、該厚さの厚い半導体素子の端子形成面に対して反対面と前記支持板の一面との間に前記樹脂層が介在して、前記支持板の一面側に前記樹脂層によって固着され、前記厚さの薄い半導体素子の反対面と前記支持板の一面との間に介在する前記樹脂層の高さは、前記厚さの厚い半導体素子の反対面と前記支持板の一面との間に介在する前記樹脂層の高さよりも高い。

また、前記絶縁層が、前記半導体素子の端子形成面から側面の少なくとも一部にかけて該半導体素子を覆う。

また、前記配線パターン上には、更に他の絶縁層と配線パターンが多層に積層されている。

10

### 【発明の効果】

#### 【0007】

本発明では、厚さの異なる複数の半導体素子を、電極端子の端子面が同一面となるように支持板の一面側に固着している。このため、厚さの異なる複数の半導体素子の端子形成面側を覆う絶縁層を貫通する同一長さのバンプを、半導体素子の各電極端子の端子面に形成でき、半導体素子の各電極端子の端子面に長さの異なるバンプを形成する場合に比較して、バンプを容易に形成できる。

しかも、本発明に係る半導体パッケージでは、半導体素子の電極端子の端子面に形成した、先細り状のバンプの先端面を絶縁層の表面に露出し、配線パターンと接続している。かかる先細り状のバンプの先端面は、半導体素子の電極端子の端子面よりも小面積に形成できる。

20

従って、厚さの異なる複数の半導体素子の端子形成面側を覆う絶縁層を貫通する同一長さのバンプを、半導体素子の電極端子の端子面に形成できることと相俟って、バンプの露出面から微細な配線パターンを引き出すことができ、且つバンプの露出面間を広くできるため、バンプの露出面間隙を通して引き回すことのできる配線パターンの高密度化を図ることができる。

その結果、半導体素子の小型化等に伴う半導体素子の電極端子の高密度化に対応できる。

### 【発明を実施するための最良の形態】

#### 【0008】

30

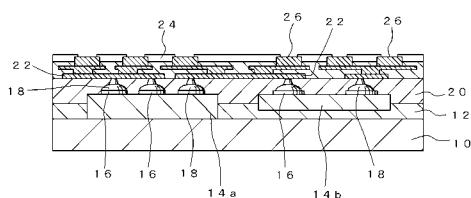

本発明に係る半導体パッケージの一例を図1に示す。図1に示す半導体パッケージは、鉄、銅、アルミニウム等の熱伝導性に優れた金属製であって、放熱板としての役割を果たすことのできる支持板10の一面側に、樹脂層12によって半導体素子としての半導体素子14a, 14bが固着されている。半導体素子14a, 14bは、その厚さが異なっているが、半導体素子14a, 14bに形成された電極端子16, 16, …の各端子面が同一面となるように位置決めされている。

かかる電極端子16, 16, …の各端子面には、先細り状のバンプ18が、半導体素子14a, 14bの端子形成面側を覆う樹脂製の絶縁層20を貫通して形成されている。この先細り状のバンプ18は、後述する様に、金ワイヤの端部を電極端子16の端子面に圧着した後、この金ワイヤを引き千切って形成した先端部をコイニングして、先端面を平坦化し且つ高さを揃えて形成したものである。

40

#### 【0009】

かかるバンプ18, 18, …の各先端面は、絶縁層20の表面に露出しており、その露出面積は、バンプ18の他端が接続されている電極端子16の端子面よりも小面積に形成されている。このため、絶縁層20の表面に形成され、先細り状のバンプ18, 18, …の各先端面から引き出された配線パターン22を、電極端子16の端子面よりも微細化できる。

従って、各電極端子18に形成された先細り状のバンプ18の先端面から配線パターン22を引き出すことができ、且つ隣接するバンプ18, 18の露出面間の間隙（バンプの露出面間隙）を広くできる。このため、バンプの露出面間隙を通して引き回せる配線バタ

50

ーンの高密度化を図ることができ、半導体素子 14a, 14b の電極端子 16, 16··· に高密度化に対応できる。

かかる配線パターン 22, 22··· 上には、図 1 に示す様に、必要に応じて複数の配線パターンを絶縁層を介して多層に積層し、絶縁層を貫通するヴィアによって配線パターン間を電気的に接続するようにしてもよい。

また、図 1 に示す半導体パッケージの最上層には、ソルダレジスト層 24 が形成され、外部接続端子としてのはんだボールを装着するパッド 26, 26··· がソルダレジスト層 24 から露出している。かかるパッド 26, 26··· には、チップキャバシタ、抵抗、インダクタ等の任意の電子部品を搭載することもできる。

この様な、図 1 に示す半導体パッケージでは、搭載した半導体素子 14a の電極端子 16 と、半導体素子 14b の電極端子 16 とが、バンプ 18, 18 の露出面に接続された配線パターン 22 によって電気的に接続することができる。

尚、図 1 に示す半導体パッケージでは、支持板 10 として、放熱板としての役割を果たすことができるように、熱伝導性に優れた金属製の支持板を用いていたが、支持体 10 が放熱板としての役割を考慮しなくてもよい場合には、ガラス板やシリコン板等から成る支持板を用いることができる。

#### 【0010】

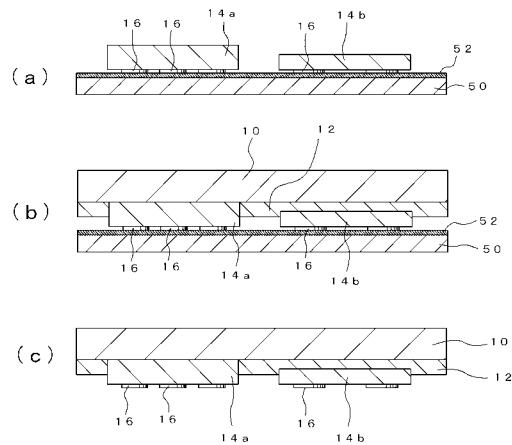

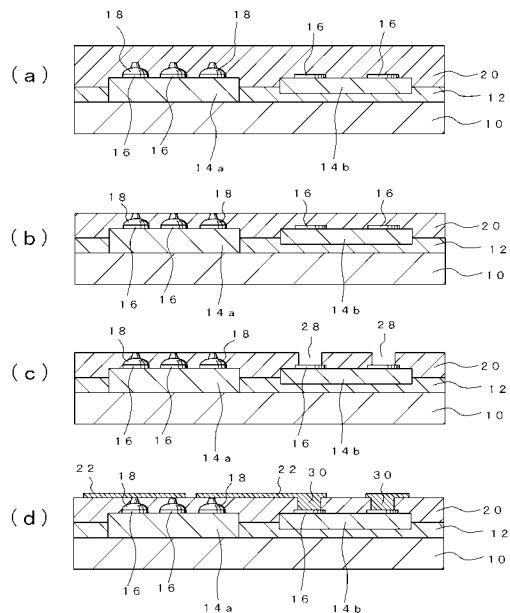

図 1 に示す半導体パッケージは、図 2 及び図 3 に製造方法によって製造できる。先ず、図 2 (a) に示す様に、ガラス板等の剛性を有する板体 50 の一面側に、厚さの異なる半導体素子としての半導体素子 14a, 14b の電極端子 16, 16··· が形成された端子形成面側を、接着層 52 によって剥離可能に接着する。この際に、半導体素子 14a, 14b の各々に形成された電極端子 16, 16··· の各端子面が同一面となるように、半導体素子 14a, 14b の各々を位置調整する。

更に、図 2 (b) に示す様に、板体 50 の一面側に、端子形成面側を接着層 52 によって接着した半導体素子 14a, 14b の各端子形成面側の反対面側を、支持板 10 の一面側に形成した樹脂層 12 によって固着する。

次いで、板体 50 及び接着層 52 を剥離し、図 2 (c) に示す様に、支持板 10 の一面側に樹脂層 12 により固着した半導体素子 14a, 14b の電極端子 16, 16··· を露出する。露出された電極端子 16, 16··· の各端子面は、厚さの異なる半導体素子 14a, 14b であっても、同一面とすることができます。

#### 【0011】

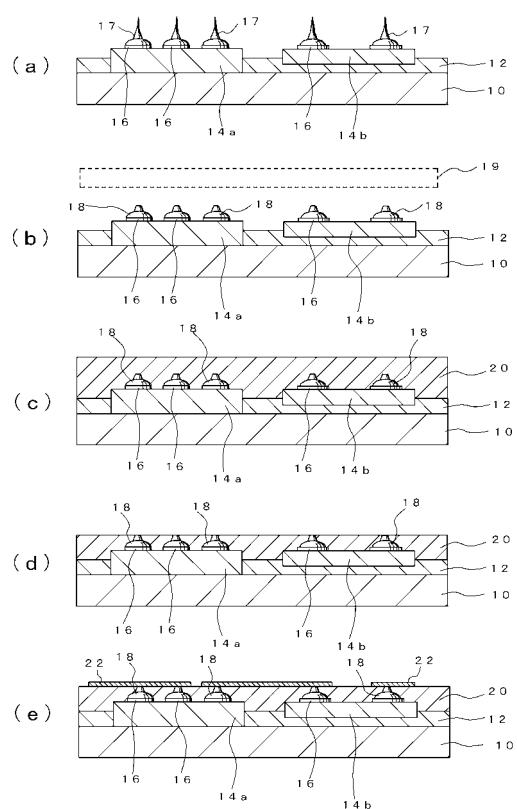

図 2 (c) に示す半導体素子 14a, 14b の電極端子 16, 16··· の各端子面には、図 3 (a) に示す様に、先端部が細長く形成されたバンプ 17 を形成する。このバンプ 17 は、金ワイヤの端部を電極端子 16 の端子面に圧着した後、この金ワイヤを引き千切って形成したものである。かかるバンプ 17 は、半導体装置の製造で用いられているボンディング装置を用いて形成できる。

図 3 (a) に示すバンプ 17, 17··· は、図 3 (b) に示す様に、その先端部をコイニング板（金型）19 によってコイニングして平坦化する。これによって、先細り状のバンプ 18, 18··· を形成する。かかる先細り状のバンプ 18, 18··· の各先端面は、電極端子 16 の端子面よりも小面積であって、同一高さで且つ略同一面積である。

#### 【0012】

次いで、形成した先細り状のバンプ 18, 18··· を含む半導体素子 14a, 14b の各端子形成面を、図 3 (c) に示す様に、絶縁性樹脂から成る絶縁層 20 によって被覆する。この絶縁層 20 は、エポキシ樹脂やポリイミド樹脂等の絶縁性樹脂の塗布、或いはこれらの絶縁性樹脂から成るフィルムの積層によって形成できる。

かかる絶縁層 20 には、図 3 (d) に示す様に、研磨又は研削を施して、先細り状のバンプ 18, 18··· の各先端面を露出する。

その後、露出した先細り状のバンプ 18, 18··· の各先端面が接続される配線パターン 22, 22··· を、絶縁層 20 の表面に形成する。絶縁層 20 の表面に露出する先細り状のバンプ 18, 18··· の各先端面は、半導体素子 14a, 14b に形成された電極端

10

20

30

40

50

子 1 6 , 1 6 · · の端子面よりも小面積に形成できる。このため、配線パターン 2 2 は、接続する先細り状のバンプ 1 8 が形成された電極端子 1 6 の端子面よりも幅狭に形成でき、微細化された配線パターン 2 2 を形成できる。

また、隣接するバンプ 1 8 , 1 8 のバンプの露出面間隙を、バンプ 1 8 , 1 8 を形成した電極端子 1 6 , 1 6 の端子面間隙よりも広くできる。

従って、バンプの露出面間隙から引き回す配線パターン 2 2 , 2 2 · · の高密度化を可能にでき、半導体素子 1 4 a , 1 4 b の小型化等に因る電極端子 1 6 , 1 6 · · の高密度化に対しても対応できる。

配線パターン 2 2 , 2 2 · · 上には、必要に応じて複数の配線パターンを絶縁層を介して多層に積層し、絶縁層を貫通するヴィアによって配線パターン間を電気的に接続することによって、図 1 に示す半導体パッケージを得ることができる。

10

この様に、配線パターン 2 2 , 2 2 · · 上に複数の配線パターンを絶縁層を介して多層に積層する際には、公知のアディティブ法やセミアディティブ法を利用できる。

#### 【 0 0 1 3 】

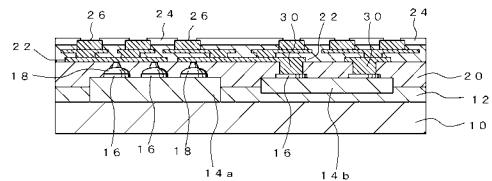

図 1 ~ 図 3 に示す半導体パッケージには、支持板 1 0 の一面側に載置された半導体素子 1 4 a , 1 4 b の全電極端子 1 6 の端子面に先細り状のバンプ 1 8 が形成されているが、図 4 に示す半導体パッケージの様に、半導体素子 1 4 a の電極端子 1 6 , 1 6 · · の各端子面に、先細り状のバンプ 1 8 を形成し、半導体素子 1 4 b の電極端子 1 6 , 1 6 · · の各端子面に、柱状のバンプ 3 0 を形成してもよい。

図 4 に示す半導体パッケージの半導体素子 1 4 b では、電極端子 1 6 , 1 6 · · の形成密度が、高密度化されておらず、柱状のバンプ 3 0 を形成しても、バンプ 3 0 と接続する配線パターン 2 2 を容易に形成できるためである。

20

この様に、先細り状のバンプ 1 8 と柱状のバンプ 3 0 とを混在して形成することによって、電極端子 1 6 , 1 6 · · の各用途に応じて最適なバンプ、例えば信号用の電極端子には先細り状のバンプ 1 8 を形成し、電源用や接地用の電極端子には柱状のバンプ 3 0 を形成できる。

#### 【 0 0 1 4 】

図 4 に示す様に、先細り状のバンプ 1 8 と柱状のバンプ 3 0 とが混在して形成された半導体パッケージを製造する際には、前述した図 2 ( a ) ~ ( c ) に示す工程と同様にして、支持板 1 0 の一面側に樹脂層 1 2 によって固着した半導体素子 1 4 a , 1 4 b の電極端子 1 6 , 1 6 · · の各端子面を露出する。

30

この半導体素子 1 4 a の電極端子 1 6 , 1 6 · · の各端子面には、図 3 ( a ) ~ ( b ) に示す工程と同様にして、先細り状のバンプ 1 8 を形成する。この際に、半導体素子 1 4 b の電極端子 1 6 , 1 6 · · の各端子面には、バンプを何等形成しない。

次いで、図 5 ( a ) に示す様に、半導体素子 1 4 の電極端子 1 6 , 1 6 · · の各端子面に形成したバンプ 1 8 を含む半導体素子 1 4 a , 1 4 b の各端子形成面を、絶縁性樹脂から成る絶縁層 2 0 によって被覆した後、図 5 ( b ) に示す様に、絶縁層 2 0 を研磨又は研削して、半導体素子 1 4 に形成した先細り状のバンプ 1 8 , 1 8 · · の各先端面を露出する。

更に、図 5 ( c ) に示す様に、半導体素子 1 4 b の電極端子 1 6 , 1 6 · · の各端子面が底面に露出するように、凹部 2 8 , 2 8 · · をレーザによって形成する。

40

その後、図 5 ( d ) に示す様に、凹部 2 8 , 2 8 · · をめっき金属で充填して柱状のバンプ 3 0 を形成すると共に、先細り状のバンプ 1 8 の先端面と柱状のバンプ 3 0 との各々に接続する配線パターン 2 2 , 2 2 · · を形成する。

#### 【 0 0 1 5 】

かかる柱状のバンプ 3 0 と配線パターン 2 2 , 2 2 · · を形成する際には、例えば図 5 ( c ) に示す凹部 2 8 , 2 8 · · の各内壁面を含む絶縁層 2 0 の全面に、無電解めっき、蒸着又はスパッタによって薄金属層を形成する。

更に、この薄金属層の表面に形成した感光性樹脂層に、形成する配線パターンに沿って薄金属層が露出するようにパターニングを施した後、薄金属層を給電層とする電解めっき

50

を施して、凹部 28, 28···をめっき金属で充填する共に、配線パターン 22, 22···を形成する。

次いで、感光性樹脂層を剥離して、露出した薄金属層をエッチングすることによって、図 5 (d) に示す柱状のバンプ 30 と配線パターン 22, 22···を形成できる。

かかる配線パターン 22, 22···上には、必要に応じて複数の配線パターンを絶縁層を介して多層に積層し、絶縁層を貫通するヴィアによって配線パターン間を電気的に接続することによって、図 4 に示す半導体パッケージを得ることができる。

この様に、配線パターン 22, 22···上に複数の配線パターンを絶縁層を介して多層に積層する際には、公知のアディティブ法やセミアディティブ法を利用できる。

尚、図 4 及び図 5 では、半導体素子 14b のみに柱状のバンプ 30 を形成したが、半導体素子 14a, 14b の一方又は両方に、先細り状のバンプ 18 と柱状のバンプ 30 とを混在させてもよい。

#### 【0016】

図 1 ~ 図 5 に示す半導体パッケージでは、厚さの異なる半導体素子 14a, 14b を、それらの電極端子 16, 16···の端子面が同一面となるように支持板 10 の一面側に固定している。このため、半導体素子 14a, 14b の電極端子 16, 16···の各端子面に、同一長さのバンプを形成でき、半導体素子 14a の電極端子 16, 16···と、半導体素子 14b の電極端子 16, 16···との各端子面に形成するバンプの長さが異なる場合に比較して、バンプを容易に形成できる。

また、図 1 ~ 図 5 に示す半導体パッケージでは、半導体素子 14a, 14b の両方又は一方の電極端子 16, 16···の各端子面に先細り状のバンプ 18 を形成している。このため、先細り状のバンプ 18 の絶縁層 20 の表面に露出する先端面の面積を、電極端子 16 の端子面の面積よりも小さくでき、先細り状のバンプ 18 の先端面と接続する配線パターン 22 の微細化を図ることができ、且つ隣接するバンプ 18, 18 の露出面間隙を、バンプ 18, 18 を形成した電極端子 16, 16 の端子面間隙よりも広くできる。

かかる図 1 ~ 図 5 に示す半導体パッケージでは、隣接するバンプ 18, 18 のバンプの露出面間隙を通して引き回す配線パターン 22, 22···の高密度化を図ることができ、半導体素子 14a, 14b の小型化等に伴う電極端子 16, 16···の高密度化に対応できる。

尚、図 1 ~ 図 5 に示す半導体パッケージでは、半導体素子のみを搭載した例について説明したが、半導体素子と共に、例えばコンデンサ、抵抗、インダクタ等を搭載できる。

#### 【図面の簡単な説明】

#### 【0017】

【図 1】本発明に係る半導体パッケージの一例を説明するための縦断面図である。

【図 2】図 1 に示す半導体パッケージの製造工程の一部を説明する工程図である。

【図 3】図 1 に示す半導体パッケージの製造工程の残りを説明する工程図である。

【図 4】本発明に係る半導体パッケージの他の例を説明するための縦断面図である。

【図 5】図 5 に示す半導体パッケージの製造工程を説明する工程図である。

【図 6】従来の半導体パッケージを説明するための縦断面図である。

【図 7】図 6 に示す半導体パッケージの製造工程を説明する工程図である。

#### 【符号の説明】

#### 【0018】

10 支持板

12 樹脂層

14a, 14b 半導体素子

16 電極端子

18 先細り状のバンプ

19 コイニング板

20 絶縁層

22 配線パターン

10

20

30

40

50

- 2 4 ソルダレジスト層

2 6 パッド

2 8 凹部

3 0 柱状のバンプ

5 0 板体

5 2 接着層

【図 1】

【図 2】

【図 3】

【図4】

【図6】

【図5】

【図7】

---

フロントページの続き

(56)参考文献 特開2004-172489(JP,A)

特開2005-223183(JP,A)

特開平08-162604(JP,A)

特開平07-007134(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 25/04

H01L 25/18