(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4729661号

(P4729661)

(45) 発行日 平成23年7月20日(2011.7.20)

(24) 登録日 平成23年4月28日(2011.4.28)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/3205 | (2006.01) | HO1L 21/88 | N    |

| HO1L 23/52   | (2006.01) | HO1L 21/88 | R    |

| HO1L 21/28   | (2006.01) | HO1L 21/28 | 301R |

| HO1L 29/423  | (2006.01) | HO1L 29/58 | G    |

| HO1L 29/49   | (2006.01) | HO1L 29/78 | 617L |

請求項の数 5 外国語出願 (全 20 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2004-193115 (P2004-193115) |

| (22) 出願日     | 平成16年6月30日 (2004.6.30)       |

| (65) 公開番号    | 特開2005-33198 (P2005-33198A)  |

| (43) 公開日     | 平成17年2月3日 (2005.2.3)         |

| 審査請求日        | 平成19年6月14日 (2007.6.14)       |

| (31) 優先権主張番号 | 92119085                     |

| (32) 優先日     | 平成15年7月11日 (2003.7.11)       |

| (33) 優先権主張国  | 台灣(TW)                       |

| (31) 優先権主張番号 | 93103832                     |

| (32) 優先日     | 平成16年2月17日 (2004.2.17)       |

| (33) 優先権主張国  | 台灣(TW)                       |

|           |                                                                                                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 510134581<br>奇美電子股▲ふん▼有限公司<br>Chime i Innolux Corp<br>oration<br>台灣苗栗縣竹南鎮科學路160號 新竹<br>科學工業園區<br>No. 160 Kesyue Rd., C<br>hu-Nan Site, Hsinchu<br>Science Park, Chu-N<br>an 350, Miao-Li Coun<br>ty, Taiwan,<br>(74) 代理人 100089118<br>弁理士 酒井 宏明 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】 ヒロックが無いアルミニウム層及びその形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ガラス基板上に形成された導電パターンを少なくとも備えた電子デバイスにおいて、前記導電パターンは、

前記ガラス基板上に形成された実質的に純粋なアルミニウム層（実質的純 A 1 層）と、前記実質的純 A 1 層と前記ガラス基板との間に形成されたバリアアルミニウム層（バリア A 1 層）と、を備え、

前記バリア A 1 層は、酸化アルミニウム（Al<sub>2</sub>O<sub>x</sub>）または窒化酸化アルミニウム（Al<sub>2</sub>O<sub>x</sub>N<sub>y</sub>）からなり、

前記バリア A 1 層の実質的純 A 1 層に対する厚さ比率は 1 : 6 . 25 から 1 : 1 の範囲である電子デバイス。 10

## 【請求項 2】

前記実質的純 A 1 層は前記バリア A 1 層よりも物理的に厚い、請求項 1 に記載の電子デバイス。

## 【請求項 3】

前記実質的純 A 1 層のアルミニウムは純度が少なくとも 99 . 0 重量 % である、請求項 1 に記載の電子デバイス。

## 【請求項 4】

前記実質的純 A 1 層上に更に保護層が形成された、請求項 1 に記載の電子デバイス。

**【請求項 5】**

前記保護層は、モリブデン(Mo)、窒化モリブデン(MoN)、チタン(Ti)、または、これらの組み合わせから成る合金から選択された材料によって形成されている、

請求項4に記載の電子デバイス。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、一般に、アルミニウム(Al)導電層に関し、特に、ヒロックが無いAl層及びその形成方法に関する。

**【背景技術】****【0002】**

高集積度の集積回路(IC)の半導体製造が必要になるにつれて、ICのために必要な相互接続を形成できる十分な面積を基板に確保することが難しくなる場合がある。ICの金属酸化膜半導体(MOS)のサイズの減少に伴って数が増加した相互接続を形成するという要件を満たすため、2層以上の金属層を互いに接続することは、多くのIC製造で適用されている、必須の技術になってきている。特に、マイクロプロセッサ等の高度な機能を持つ幾つかの集積回路においては、集積回路の構成部品を互いに接続するため、4層または5層の金属層が必要とされる。一方、薄膜トランジスタ液晶ディスプレイ(TFT-LCD)パネルの製造においては、金属膜が電極および相互接続部として使用され、また、これらは、金属膜から成る多層構造中に形成されている。

**【0003】**

金属膜の多層構造においては、層間短絡が生じないように、任意の2つの金属層間に誘電体等の絶縁層が形成されている。また、金属層の材料として、電気抵抗が低い純金属または合金が適切に使用される。一般に、純金属としては、例えば、Cr、Al、Cu、Mo、Ta、及びWを使用することができる。電気抵抗が低い合金としては、例えば、Al-Cu、Al-Cu-Si、Al-Pd、及びAl-Nd等のその他の元素から選択された1または複数の元素を含むアルミニウム合金が使用されている。金属層の材料としては、純アルミニウムを使用することが好ましい。これは、アルミニウムが、基板との高い密着性、製造時における高いエッチング特性、低い電気抵抗率を有するためである。また、地球には、アルミニウムが他の金属元素よりも多く含まれている。したがって、アルミニウムは、入手可能であり、コストが低い。

**【0004】**

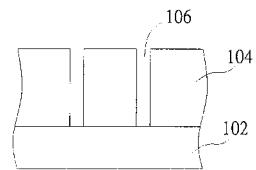

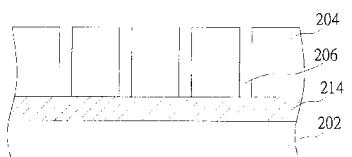

しかしながら、金属層のための元素として、他の金属よりも融点が低い純アルミニウムを使用することは、未だ不都合がある。図1には、ガラス基板上に金属を堆積させた状態が示されている。薄膜トランジスタの製造においては、最初に、比較的低い温度(約150)でガラス基板102上に金属を堆積させることにより、グレイン104が形成されるとともに、グレイン間にグレイン境界106が形成される。実際には、グレインは、図1に示されるような規則的な状態で形成されない。図1に示される規則的なグレインは、図示のためである。次に、アニーリングが行なわれ、これにより、高温加熱によってグレインの振動が大きくなることで、グレインの原子が再配列され、その結果、グレインの欠陥が減少して、グレインが再び結晶化される。この再結晶の後、転位等の欠陥の密度の減少により、グレインの内部応力が急速に減少する。アニール温度が上昇し、再結晶で形成されたグレインがグレイン間の界面エネルギーを超える高いエネルギーレベルまで引き上げられると、グレインは、それらのうちの小さなグレインが消失しながら、成長し始める。このように、グレインの成長によって大きなグレインが生じ、小さなグレインのグレイン境界が消失する。したがって、グレインの内部応力は、低いレベルまで更に減少する。

**【0005】**

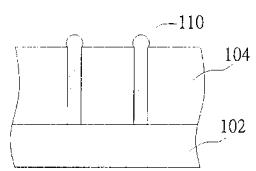

純アルミニウムが配線層材料として使用されると、ヒロック等が生じる場合がある。図2は、アニーリング後の配線層材料として純アルミニウムを用いたガラス基板を図示することにより、ヒロックを示している。アニーリングにおいては、高温により、Alグレイ

10

20

30

40

50

ン 104 およびガラス基板 102 が熱膨張する。アルミニウムはガラスよりも大きい熱膨張係数を有するため、A1 グレイン 104 による大きな圧縮応力がガラス基板 102 に加わる。この圧縮応力により、アルミニウム原子がグレイン境界 106 に沿って移動し、ヒロック 110 が生じる。ヒロック等、例えばヒロック 110 は、その後の製造プロセスでの他の層の厚さを不均一にする。また、下側の金属層と上側の金属層との間に形成される絶縁層（図示せず）を大きなヒロックが貫通して、このヒロックが上側の金属層に接触すると、最悪の場合、層間短絡が生じる虞がある。

#### 【0006】

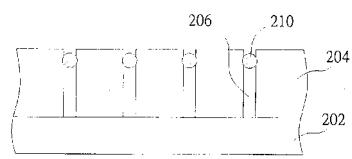

したがって、配線材料として A1 を使用するためには、ヒロックの問題を解決する必要がある。従来、この問題に対しては、2つの手法がある。第1の手法は、融点が高い他の元素、例えば Nd、Ti、Zr、Ta、Si、及び Cu を配線材料として使用することである。図3は、ガラス基板 202 上に形成された A1 合金のグレイン 204 のアニーリング後を示している。図3に示されるように、A1 合金のグレイン 204 のグレイン境界 206 間には、ヒロックが形成されていない。A1 合金の追加元素の原子は A1 グレイン中に溶解することができないため、グレイン 240 が成長すると、追加元素の原子は、グレイン境界 206 へと移動し、グレイン境界 206 間に徐々に粒子 210 を形成する。したがって、A1 原子がグレイン境界 206 に沿って移動する場合、小さな粒子 210 によって、グレイン 204 の上側への A1 原子の移動が妨げられ、それにより、ヒロックの形成が抑制される。

#### 【0007】

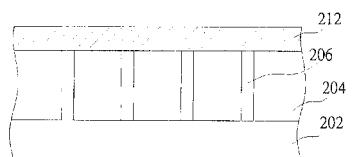

第2の手法は、A1 グレインを覆う高融点の金属層を形成することにより、ヒロックの成長を抑制することである。図4は、A1 グレインを上側から覆う金属層を示す。高融点の金属層 212 が A1 グレイン 204 上に配置された後、アニーリングが行なわれる。金属層 212 は、A1 グレイン 204 間にグレイン境界 206 によって形成される出口を覆うキャップとして機能するため、A1 原子がブロックされ、グレイン境界 206 に沿うヒロックの形成が妨げられる。また、金属層 212 の代わりにアモルファス相の A1 層を使用する第2の手法の変形例もある。ヒロックの形成を抑制するため、アモルファス状態の A1 層をグレイン 204 上に形成することができる。

#### 【0008】

ヒロック形成の問題に対するこれらの従来の手法においては、第1の手法が最も効果的で且つ通常において使用される。例えば、日本の会社コベルコは、金属層のための配線材料として A1 - Nd 合金を提供しており、これについては、ヤマモト等に対して付与された特許文献1に記載されている。Nd は、原子量が大きく且つ融点が高いため、小さな粒子を形成して、A1 原子がグレイン境界に沿って移動してヒロックを形成することを妨げることができる。このようにすると、温度が 300 に達する場合でも、ヒロックが生じない。

#### 【0009】

【特許文献1】米国特許第 6033542 号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

しかしながら、Nd は希土類元素であるため、製造コストが高く、スプラッシュ欠陥を回避するために低いスペッタリングレートを適用する必要がある。また、Nd の抵抗率が高いため、A1 - Nd 合金は、純アルミニウムの抵抗率よりも高い抵抗率を有する。

#### 【0011】

前述したように、一般的な半導体製造および液晶ディスプレイ製造においては配線材料または電極材料として A1 を使用することが望ましいため、A1 が使用される際のヒロックの形成を防止する研究が非常に重要となる。

#### 【0012】

したがって、本発明の目的は、ヒロックを防止するための導電層及びその形成方法を提

10

20

30

40

50

供することである。

【課題を解決するための手段】

【0013】

本発明は、ガラス基板上に形成された少なくとも2つのアルミニウム(A1)層を含み且つヒロックを防止できる導電層を提供することにより、前記目的を達成する。前記少なくとも2つのA1層は、ガラス基板上に形成されたバリアアルミニウム層(バリアA1層)と、バリアA1層上に形成された実質的に純粋なアルミニウム層(実質的純A1層)とを含む。実質的純A1層は、その純度が少なくとも約99.0重量%であり、好ましくは少なくとも約99.9重量%である。以下、実質的に純粋なA1層(実質的純A1層)を省略して単に純A1層という。また、バリアA1層の熱膨張係数は、純A1層の熱膨張係数よりも小さい。10

【0014】

バリアA1層は、酸化アルミニウム(A1Ox)、酸窒化アルミニウム(A1OxNy)のうちの1つの化合物を少なくとも含んでいる。バリアA1層の純A1層に対する厚さ比率が約1:6.25から1:1の範囲である場合には、ヒロック等を効果的に防止できる。バリアA1層の純A1層に対する厚さ比率が約1:6.25から1:2の範囲である場合には、デバイスをエッチングした後、良好な断面形状が得られる。10

【0015】

また、バリアA1層は、A1-Nd合金層であっても良い。この場合、A1-Nd合金は、約100から4000の範囲の厚さを有し、好ましくは約300及び900の厚さである。純A1層は、約500から4500の範囲の厚さを有し、好ましくは約1500及び3000の厚さである。また、A1-Nd合金層の純A1層に対する厚さ比率は、約1:6.67から1:0.55の範囲である。20

【発明の効果】

【0016】

バリア層の熱膨張係数が純A1層の熱膨張係数と基板の熱膨張係数との間にあるバリアアルミニウム(A1)層を緩衝層として使用することにより、ヒロック等が効果的に防止される。また、抵抗が下がり、製造コストが低減される。

本発明の他の目的、特徴、利点は、好ましいが制限的でない実施形態の以下の詳細な説明から明らかになる。以下、添付図面を参照しながら説明する。30

【発明を実施するための最良の形態】

【0017】

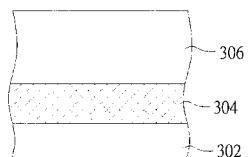

図6は、基板上に少なくとも2つのアルミニウム層を有する本発明の実施形態に係る導電層を示す。基板302上にバリアアルミニウム(A1)層304が形成され、その後、バリアA1層304上に純A1層306が形成され、これにより、以下の熱処理を受けた後、アルミニウムヒロック(hilllock)の発生が抑制される。

【0018】

第1の実施形態において、バリアA1層は、窒化アルミニウム(A1Nx)、酸化アルミニウム(A1Ox)、酸窒化アルミニウム(A1OxNy)のうちの1つの化合物を少なくとも含む。第2の実施形態においては、特定の研究のため、バリアA1層の材料として、アルミニウム-ネオジウム(A1-Nd)合金が使用されている。これにより、関連する実験結果も開示されている。40

(第1の実施形態)

【0019】

図6も参照されたい。第1の実施形態においては、ガラス基板304が設けられ、窒化アルミニウム(A1Nx)層、酸化アルミニウム(A1Ox)層、酸窒化アルミニウム(A1OxNy)層、または、これらの任意の2つの層あるいは3つの層の組み合わせ等のバリアA1層304がこの基板304上にわたって形成されている。その後、バリアA1層304上にわたって純A1層(少なくとも99.0重量%、好ましくは少なくとも99.9重量%)306が形成されている。バリアA1層の材料に関しては、バリアA1層350

0 4 の熱膨張係数が純 A 1 層 3 0 6 のそれ（熱膨張係数）よりも小さく且つガラス基板 3 0 2 のそれよりも大きくなるように選択された。したがって、以下のプロセスにおいてデバイスが高温（または、熱衝撃）に晒された後、A 1 ヒロックの形成をうまく防止することができる。また、バリア A 1 層 3 0 4 の抵抗率は、純 A 1 層 3 0 6 のそれよりも高い。

【 0 0 2 0 】

表 1 には、純 A 1 、 A 1 N x 、 A 1 O x 、 A 1 O x N y および 3 つの異なるガラス基板のアニーリング前の熱膨張係数および抵抗率が示されている。

【 0 0 2 1 】

【表1】

|                                                | コーニング<br>(ガラス基板) | NHT<br>(ガラス基板) | アサヒ<br>(ガラス基板) | アルミニウム<br>(Al) | 窒化<br>アルミニウム<br>(Al <sub>2</sub> O <sub>3</sub> )<br>層 | 酸化<br>アルミニウム<br>(Al <sub>2</sub> O <sub>3</sub> )<br>(Al-OxNy) | 酸塗化<br>アルミニウム<br>(Al <sub>2</sub> O <sub>3</sub> )<br>(Al-OxNy) |

|------------------------------------------------|------------------|----------------|----------------|----------------|--------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------|

| サンプル                                           | 1737             | E2000          | NA35           | NA25           | NA30                                                   | AN100                                                          |                                                                 |

| 熱膨張係数<br>( $\times 10^{-7}/^{\circ}\text{C}$ ) | 37.8             | 32             | 37             | 26             | 32                                                     | 38                                                             |                                                                 |

| 低効率<br>( $\Omega \text{ cm}$ )                 | NA               | NA             | NA             | NA             | NA                                                     | $2.65 \times 10^{-6}$                                          | $5.6 \times 10^{13}$                                            |

## 【0022】

アニーリング(加熱)プロセス中、ガラス基板302と純A1層306との間の熱膨張係数の違いによって生じる熱応力によりアルミニウム原子がグレイン境界に沿って移動するため、ヒロック等が生じる。本発明の特徴は、ガラス基板302と純A1層306との間にバリアA1層304を介挿することである。この場合、バリアA1層304の熱膨張係数は、ガラス基板302の熱膨張係数(それ)よりも大きいが、純A1層306のそれよりも小さい。したがって、バリアA1層304は、ヒロック等を形成するA1原子のグ

10

20

30

40

50

レイン境界に沿う移動を防止する緩衝層として機能する。また、かなり低い低効率（電気抵抗）および後処理（例えばエッティング処理）の施されたデバイスの良好な形状を得るために、純A1層306は、物理的に、バリアA1層304よりも厚い。

#### 【0023】

本発明の第1の実施形態のヒロックが無いデバイスの状態を調べるために、実験が行なわれている。先ず最初に、スパッタリングする純アルミニウムターゲットが、スパッタリング装置の真空チャンバ内に装着される。堆積パラメータ、すなわち、全圧、排ガス中の窒素含有量、および基板バイアス電圧において異なる値を用い、窒素／アルゴン（N<sub>2</sub>／Ar）ガス混合体中でアルミニウムターゲットを反応性スパッタリングすることにより窒化アルミニウム（AlNx）膜を成長させた。同様に、酸素／アルゴン（O<sub>2</sub>／Ar）ガス混合体中でアルミニウムターゲットを反応性スパッタリングすることにより酸化アルミニウム（AlOx）膜を成長させるとともに、窒素／酸素／アルゴン（N<sub>2</sub>／O<sub>2</sub>／Ar）ガス混合体中で酸窒化アルミニウム（AlOxNy）膜を成長させた。

10

#### 【0024】

その後、2つのA1層を含む積層構造体を340℃の温度で30分間加熱する（アニールする）。処理後、走査型電子顕微鏡（SEM）により積層構造体の最上層を観察して、ヒロック等が生じているか否か、また、構造体の断面形状が良好か否かを調べる。その結果が表2に示されている。

#### 【0025】

【表2】

20

| 実施例 | バリアA1層の厚さ(Å) | 純A1層の厚さ(Å) | バリアA1層／純A1層の比率 | アニーリング後のヒロックの発生 | 積層構造体の断面形状 |

|-----|--------------|------------|----------------|-----------------|------------|

| 1   | 0            | 2000       | 0              | 有               | 一          |

| 2   | 200          | 2000       | 1:10           | 有               | 不良         |

| 3   | 300          | 2000       | 1:6.7          | 有               | 不良         |

| 4   | 400          | 2000       | 1:5            | 無               | 良好         |

| 5   | 500          | 2000       | 1:4            | 無               | 良好         |

| 6   | 600          | 2000       | 1:3.3          | 無               | 良好         |

| 7   | 1000         | 2000       | 1:2            | 無               | 良好         |

| 8   | 1500         | 2000       | 1:1.3          | 無               | 不良         |

| 9   | 2000         | 2000       | 1:1            | 無               | 不良         |

| 10  | 250          | 1800       | 1:7.2          | 有               | 不良         |

| 11  | 300          | 1800       | 1:6            | 無               | 良好         |

| 12  | 900          | 1800       | 1:2            | 無               | 良好         |

| 13  | 1800         | 1800       | 1:1            | 無               | 不良         |

| 14  | 300          | 2500       | 1:8.3          | 有               | 不良         |

| 15  | 400          | 2500       | 1:6.25         | 無               | 良好         |

| 16  | 600          | 2500       | 1:4.2          | 無               | 良好         |

| 17  | 700          | 2500       | 1:3.6          | 無               | 良好         |

| 18  | 1250         | 2500       | 1:2            | 無               | 良好         |

| 19  | 2500         | 2500       | 1:1            | 無               | 不良         |

| 20  | 600          | 4500       | 1:7.5          | 有               | 不良         |

| 21  | 750          | 4500       | 1:6            | 無               | 良好         |

| 22  | 1500         | 4500       | 1:3            | 無               | 良好         |

| 23  | 2250         | 4500       | 1:2            | 無               | 良好         |

| 24  | 4500         | 4500       | 1:1            | 無               | 不良         |

30

#### 【0026】

（実施例1（比較例））

0.3Paの成膜圧力およびArガスのスパッタリング条件下で、厚さが2000Åの純A1膜がガラス基板上に形成されている。その後、構造体が340℃の温度で30分間アニールされている。このアニール処理後、走査型電子顕微鏡（SEM）により積層構造体を観察する。

40

50

**【0027】**

結果は、緩衝層が存在しない場合にはヒロック等が生じることを示している。

**【0028】****(実施例2)**

先ず最初に、0.5 Paの成膜圧力下で、反応性スパッタリングにより、厚さが200の窒化アルミニウムから成るバリアA1膜がガラス基板上に形成されている。0.3 Paの成膜圧力下で、厚さが2000の純A1膜がバリアA1膜上に形成されている。バリアA1層の純A1層に対する厚さ比率は、約1:10である。したがって、純A1層(2000)/AINx(200)/基板を含む積層構造体が、340の温度で30分間アニールされた後、SEMによって観察されている。

10

**【0029】**

結果は、ヒロック等が生じることを示している。バリアA1層の純A1層に対する厚さ比率(1:10)が非常に低いため、ガラス基板とA1原子との間で熱応力を緩和することができない。また、後処理(例えばフォトリソグラフィおよびエッチング)を行なった後においては、バリアA1層がオーバーエッチングされていて、これらの積層構造体の断面形状は良好ではない。

**【0030】****(実施例3)**

実施例2の処理に従って、ガラス基板上に厚さが300のバリアA1層(AINx)を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:6.7である。

20

**【0031】**

積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。結果は、ヒロック等が依然として生じていることを示している。バリアA1層の純A1層に対する厚さ比率(1:6.7)が非常に低いため、ガラス基板とA1原子との間で熱応力を緩和することができない。また、後処理(例えばフォトリソグラフィおよびエッチング)を行なった後においては、バリアA1層がオーバーエッチングされていて、これらの積層構造体の断面形状は良好ではない。

**【0032】****(実施例4)**

30

実施例2の処理に従って、ガラス基板上に厚さが400のバリアA1層を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:5である。

**【0033】**

純A1層(2000)/AINx(400)/基板を含む積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

**【0034】**

結果は、アニール後にヒロック等が生じないことを示している。バリアA1層の純A1層に対する厚さ比率が1:5である場合には、ガラス基板とA1原子との間の熱応力を効果的に緩和することができる。また、後処理(例えばフォトリソグラフィおよびエッチング)を行なった後においては、これらの積層構造体の断面形状は良好である。

40

**【0035】****(実施例5)**

実施例2の処理に従って、ガラス基板上に厚さが500のバリアA1層を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:4である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

**【0036】**

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

50

## 【0037】

(実施例6)

実施例2の処理に従って、ガラス基板上に厚さが600のバリアA1層を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:3.3である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

## 【0038】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

## 【0039】

10

(実施例7)

実施例2の処理に従って、ガラス基板上に厚さが1000のバリアA1層を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:2である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

## 【0040】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

## 【0041】

20

(実施例8)

実施例2の処理に従って、ガラス基板上に厚さが1500のバリアA1層を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:1.3である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

結果は、ヒロック等が効果的に抑制されていることを示している。しかしながら、構造体の断面形状は良好ではない。純A1層がオーバーエッティングされ、バリアA1層がアンダーエッティングされ、それにより、バリアA1層が過剰に残った。

## 【0042】

(実施例9)

実施例2の処理に従って、ガラス基板上に厚さが2000のバリアA1層を有し且つバリアA1層上にわたって厚さが2000の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:1である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

## 【0043】

結果は、ヒロック等が効果的に抑制されていることを示している。しかしながら、構造体の断面形状は良好ではない。純A1層がオーバーエッティングされ、バリアA1層がアンダーエッティングされ、それにより、バリアA1層が過剰に残った。

## 【0044】

(実施例10)

30

実施例2の処理に従って、ガラス基板上に厚さが250のバリアA1層を有し且つバリアA1層上にわたって厚さが1800の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:7.2である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

## 【0045】

結果は、ヒロック等が依然として生じていることを示している。バリアA1層の純A1層に対する厚さ比率(1:7.2)が非常に低いため、ガラス基板とA1原子との間で熱応力を緩和することができない。また、バリアA1層がオーバーエッティングされ、これらの積層構造体の断面形状は良好ではない。

## 【0046】

(実施例11)

40

50

実施例 2 の処理に従って、ガラス基板上に厚さが 300 のバリア A1 層を有し且つバリア A1 層上にわたって厚さが 1800 の純 A1 層を有する積層構造体を形成した。バリア A1 層の純 A1 層に対する厚さ比率は、約 1 : 6 である。これらの積層構造体は、340 の温度で 30 分間アニールされた後、SEM によって観察されている。

#### 【0047】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

#### 【0048】

##### (実施例 12)

実施例 2 の処理に従って、ガラス基板上に厚さが 900 のバリア A1 層を有し且つバリア A1 層上にわたって厚さが 1800 の純 A1 层を有する積層構造体を形成した。10 バリア A1 層の純 A1 層に対する厚さ比率は、約 1 : 2 である。これらの積層構造体は、340 の温度で 30 分間アニールされた後、SEM によって観察されている。

#### 【0049】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

#### 【0050】

##### (実施例 13)

実施例 2 の処理に従って、ガラス基板上に厚さが 1800 のバリア A1 層を有し且つバリア A1 層上にわたって厚さが 1800 の純 A1 层を有する積層構造体を形成した。20 バリア A1 層の純 A1 層に対する厚さ比率は、約 1 : 1 である。これらの積層構造体は、340 の温度で 30 分間アニールされた後、SEM によって観察されている。

#### 【0051】

結果は、ヒロック等が効果的に抑制されていることを示している。しかしながら、構造体の断面形状は良好ではない。純 A1 層がオーバーエッチングされ、バリア A1 層がアンダーエッチングされ、それにより、バリア A1 層が過剰に残った。

#### 【0052】

##### (実施例 14)

実施例 2 の処理に従って、ガラス基板上に厚さが 300 のバリア A1 層を有し且つバリア A1 層上にわたって厚さが 2500 の純 A1 层を有する積層構造体を形成した。30 バリア A1 層の純 A1 層に対する厚さ比率は、約 1 : 8 . 3 である。これらの積層構造体は、340 の温度で 30 分間アニールされた後、SEM によって観察されている。

#### 【0053】

結果は、ヒロック等が依然として生じていることを示している。バリア A1 層の純 A1 層に対する厚さ比率 (1 : 8 . 3) が非常に低いため、ガラス基板と A1 原子との間で熱応力を緩和することができない。また、バリア A1 層がオーバーエッチングされ、これらの積層構造体の断面形状は良好ではない。

#### 【0054】

##### (実施例 15)

実施例 2 の処理に従って、ガラス基板上に厚さが 400 のバリア A1 層を有し且つバリア A1 層上にわたって厚さが 2500 の純 A1 层を有する積層構造体を形成した。40 バリア A1 層の純 A1 層に対する厚さ比率は、約 1 : 6 . 25 である。これらの積層構造体は、340 の温度で 30 分間アニールされた後、SEM によって観察されている。

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

#### 【0055】

##### (実施例 16)

実施例 2 の処理に従って、ガラス基板上に厚さが 600 のバリア A1 層を有し且つバリア A1 層上にわたって厚さが 2500 の純 A1 层を有する積層構造体を形成した。50 バリア A1 層の純 A1 層に対する厚さ比率は、約 1 : 4 . 2 である。これらの積層構造体は

、340 の温度で30分間アニールされた後、SEMによって観察されている。結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

#### 【0056】

(実施例17)

実施例2の処理に従って、ガラス基板上に厚さが700 のバリアA1層を有し且つバリアA1層上にわたって厚さが2500 の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:3.6である。これらの積層構造体は、340 の温度で30分間アニールされた後、SEMによって観察されている。

#### 【0057】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

#### 【0058】

(実施例18)

実施例2の処理に従って、ガラス基板上に厚さが1250 のバリアA1層を有し且つバリアA1層上にわたって厚さが2500 の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:2である。これらの積層構造体は、340 の温度で30分間アニールされた後、SEMによって観察されている。

#### 【0059】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

#### 【0060】

(実施例19)

実施例2の処理に従って、ガラス基板上に厚さが2500 のバリアA1層を有し且つバリアA1層上にわたって厚さが2500 の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:1である。これらの積層構造体は、340 の温度で30分間アニールされた後、SEMによって観察されている。

#### 【0061】

結果は、ヒロック等が効果的に抑制されていることを示している。しかしながら、構造体の断面形状は良好ではない。純A1層がオーバーエッティングされ、バリアA1層がアンダーエッティングされ、それにより、バリアA1層が過剰に残った。

#### 【0062】

(実施例20)

実施例2の処理に従って、ガラス基板上に厚さが600 のバリアA1層を有し且つバリアA1層上にわたって厚さが4500 の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:7.5である。これらの積層構造体は、340 の温度で30分間アニールされた後、SEMによって観察されている。

#### 【0063】

結果は、ヒロック等が依然として生じていることを示している。バリアA1層の純A1層に対する厚さ比率(1:7.5)が非常に低いため、ガラス基板とA1原子との間で熱応力を緩和することができない。また、バリアA1層がオーバーエッティングされ、これらの積層構造体の断面形状は良好ではない。

#### 【0064】

(実施例21)

実施例2の処理に従って、ガラス基板上に厚さが750 のバリアA1層を有し且つバリアA1層上にわたって厚さが4500 の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:6である。これらの積層構造体は、340 の温度で30分間アニールされた後、SEMによって観察されている。

#### 【0065】

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示して

10

20

30

40

50

いる。

**【0066】**

(実施例22)

実施例2の処理に従って、ガラス基板上に厚さが1500のバリアA1層を有し且つバリアA1層上にわたって厚さが4500の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:3である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

**【0067】**

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

10

**【0068】**

(実施例23)

実施例2の処理に従って、ガラス基板上に厚さが2250のバリアA1層を有し且つバリアA1層上にわたって厚さが4500の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:2である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

**【0069】**

結果は、ヒロック等が効果的に抑制され、構造体の断面形状が良好であることを示している。

**【0070】**

(実施例24)

実施例2の処理に従って、ガラス基板上に厚さが4500のバリアA1層を有し且つバリアA1層上にわたって厚さが4500の純A1層を有する積層構造体を形成した。バリアA1層の純A1層に対する厚さ比率は、約1:1である。これらの積層構造体は、340の温度で30分間アニールされた後、SEMによって観察されている。

20

**【0071】**

結果は、ヒロック等が効果的に抑制されていることを示している。しかしながら、構造体の断面形状は良好ではない。純A1層がオーバーエッティングされ、バリアA1層がアンダーエッティングされ、それにより、バリアA1層が過剰に残った。

**【0072】**

実施例1～24の結果は、ヒロックが無い導電層が基板上に形成された少なくとも2層のアルミニウム(A1)層を備えており、そのアルミニウム層は、基板上に形成されたバリアA1層とバリアA1層上に形成された純A1層とを含み、純A1層が約1000オングストロームから4500オングストロームの範囲の厚さを有し、バリアA1層の純A1層に対する厚さ比率が約1:6.25から1:1の範囲にあることを示している。したがって、ガラス基板と純A1層との間の熱膨張の差に基づいて生じる熱応力が効果的に緩和されている。また、第1の実施形態において、バリアA1層として使用される材料は、窒化アルミニウム(A1Nx)、酸化アルミニウム(A1Ox)、酸窒化アルミニウム(A1OxNy)であっても良い。

30

**【0073】**

また、表2に記載された複数の実施例の結果は、純A1層が約1000オングストロームから4500オングストロームの範囲の厚さを有し、バリアA1層は純A1層よりも物理的に薄く、特に、バリアA1層の純A1層に対する厚さ比率が約1:6.25から1:2の範囲にある場合に、これらの積層構造体の断面形状が良好であることを示している。

40

**【0074】**

以上においては、たった1層の純A1層が示されているが、本発明がこれに限定されないことは言うまでもない。バリアA1層上に複数(2、3、4、5層、そしてそれ以上)の純A1層が形成される場合であっても、ヒロック等の発生は、依然として防止されている。実際の用途において、純A1層は、例えばA1-Cu、A1-Cu-Si、A1-Pd、A1-Cr、A1-Ti等のA1系の層と置き換えることができる。また、バリアA

50

1層が複数の層を含んでいても良い。例えば、バリアA1層は、窒素含有量が異なる第1のA1N<sub>x</sub>層と第2のA1N<sub>x</sub>層と第3のA1N<sub>x</sub>層とを含んでいても良く、あるいは、酸素含有量が異なる第1のA1O<sub>x</sub>層と第2のA1O<sub>x</sub>層と第3のA1O<sub>x</sub>層とを含んでいても良く、あるいは、酸素の窒素に対する含有率が異なる第1のA1O<sub>x</sub>N<sub>y</sub>層と第2のA1O<sub>x</sub>N<sub>y</sub>層と第3のA1O<sub>x</sub>N<sub>y</sub>層とを含んでいても良い。また、バリアA1層は、異なる化合物を有する複数の層、例えば、A1N<sub>x</sub>層/A1O<sub>x</sub>層、または、A1N<sub>x</sub>層/A1O<sub>x</sub>N<sub>y</sub>層、または、A1O<sub>x</sub>層/A1O<sub>x</sub>N<sub>y</sub>層、または、A1N<sub>x</sub>層/A1O<sub>x</sub>N<sub>y</sub>層を含んでいても良い。

## 【0075】

(第2の実施形態)

10

第2の実施形態においては、ヒロック等の発生を防止するためのバリアA1層として、アルミニウム-ネオジウム(A1-Nd)合金層が使用される。この積層構造体は、多くの場合、薄膜トランジスタ(TFT)の電極パターンとして使用されている。

## 【0076】

図6も参照されたい。第2の実施形態においては、ガラス基板304が設けられていて、この基板304上にわたってA1-Nd合金層(バリアA1層304として)が形成されている。A1-Nd合金層は、約100オングストロームから4000オングストロームの範囲の厚さ、好ましくは約300オングストローム及び900オングストロームの厚さを有する。

## 【0077】

20

その後、A1-Nd合金層上にわたって純A1層306が形成されている。純A1層は、約500オングストロームから4500オングストロームの範囲の厚さ、好ましくは約1500オングストローム及び3000オングストロームの厚さを有する。

## 【0078】

A1-Nd合金層および純A1層306の成膜条件は限定されない。一般的な成膜圧力、例えば0.3Paまたは0.4Paを適合させることができる。熱処理中に生じる応力をA1-Nd合金層が解放し、これにより、ヒロックを効果的に抑制することができる。

## 【0079】

また、A1層の酸化を防止するための保護層(図6に図示しない)が、純A1層306上にわたって更に形成されていても良い。保護層の材料として、モリブデン(Mo)、チタン(Ti)、窒化モリブデン化合物(MoN)等の金属を使用しても良い。

30

## 【0080】

本発明の第2の実施形態のヒロックが無いデバイスの状態を調べるために、実験が行なわれている。同様に、積層構造体(基板上のA1-Nd合金層とA1-Nd合金層上の純A1層とを含む)が320で10分間アニールされている。このアニール処理後、走査型電子顕微鏡(SEM)により積層構造体の最上層を観察して、任意のヒロック等が生じているか否かを調べる。また、純A1層上にわたってMo層が保護層として更に形成されていて、構造体の断面形状がSEMによって観察されている。その結果が表3に示されている。

## 【0081】

40

【表3】

| 実施例 | A1-Nd合金層の厚さ(Å) | 純A1層の厚さ(Å) | A1-Nd層の純A1層に対する比率 | アニーリング後のヒロックの発生 | 積層構造体の断面形状 |

|-----|----------------|------------|-------------------|-----------------|------------|

| 25  | 0              | 2000       | 0                 | 有               | —          |

| 26  | 1800           | 0          | —                 | 無               | 良好         |

| 27  | 300            | 1000       | 1:3.3             | 無               | 良好         |

| 28  | 300            | 2000       | 1:6.7             | 無               | 良好         |

| 29  | 450            | 2000       | 1:4.4             | 無               | 良好         |

| 30  | 450            | 1000       | 1:2.2             | 無               | 良好         |

| 31  | 900            | 2000       | 1:2.2             | 無               | 良好         |

| 32  | 900            | 1000       | 1:1.1             | 無               | 良好         |

| 33  | 1800           | 2000       | 1:1.1             | 無               | 良好         |

| 34  | 1800           | 1000       | 1:0.55            | 無               | 良好         |

## 【0082】

(実施例25(比較例))

0.3Paの成膜圧力のスパッタリング条件下で、厚さが2000の純A1膜が基板上に形成されている。その後、構造体が320の温度で10分間アニールされている。このアニール処理後、走査型電子顕微鏡(SEM)により積層構造体を観察する。

## 【0083】

結果は、純A1層だけが使用されている場合にヒロック等が生じることを示している。

## 【0084】

(実施例26(比較例))

0.3Paの成膜圧力のスパッタリング条件下で、厚さが1800のAl-Nd合金膜が基板上に形成されている。その後、構造体が320の温度で10分間アニールされている。このアニール処理後、走査型電子顕微鏡(SEM)により積層構造体を観察する。

## 【0085】

結果は、Al-Nd合金層のみが導電層として使用されている場合にヒロック等が生じないことを示している。

## 【0086】

また、Al-Nd合金層上に1000の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

## 【0087】

しかしながら、Al-Nd合金の材料は高価であり、導電層の唯一の材料としてAl-Nd合金を使用することは、あまり有益ではない。また、Al-Nd合金の電気抵抗は非常に高く(A1における値の約2倍)、デバイスの電気的要件を満たすべく厚い膜を形成するために、多くの成膜時間を要する。

## 【0088】

(実施例27)

0.3Paの成膜圧力のスパッタリング条件下で、厚さが300のAl-Nd合金膜が基板上に形成された後、厚さが1000の純A1層がAl-Nd合金膜上に形成されている。その後、構造体が320の温度で10分間アニールされる。このアニール処理後、走査型電子顕微鏡(SEM)により積層構造体を観察する。結果は、ヒロック等の発生が無いことを示している。

## 【0089】

また、純A1層上に900の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

## 【0090】

(実施例28)

厚さが300のAl-Nd合金膜が基板上に形成(0.3Paの成膜圧力)された後

10

20

30

40

50

、厚さが2000の純Al層がAl-Nd合金膜上に形成されている。その後、構造体が320の温度で10分間アニールされている。このアニール処理後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。

**【0091】**

純Al層上に900の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0092】**

(実施例29)

厚さが450のAl-Nd合金膜が基板上に形成(0.3Paの成膜圧力)された後<sup>10</sup>、厚さが2000の純Al層がAl-Nd合金膜上に形成されている。その後、構造体が320の温度で10分間アニールされている。このアニール処理後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。

**【0093】**

純Al層上に900の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0094】**

(実施例30)

厚さが450のAl-Nd合金膜が基板上に形成(0.3Paの成膜圧力)された後<sup>20</sup>、厚さが1000の純Al層がAl-Nd合金膜上に形成されている。構造体が320の温度で10分間アニールされ、その後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。

**【0095】**

純Al層上に900の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0096】**

(実施例31)

厚さが900のAl-Nd合金膜が基板上に形成された後、厚さが2000の純Al層がAl-Nd合金膜上に形成される。構造体が320の温度で10分間アニールされ、その後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。<sup>30</sup>

**【0097】**

純Al層上に900の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0098】**

(実施例32)

厚さが900のAl-Nd合金膜が基板上に形成された後、厚さが1000の純Al層がAl-Nd合金膜上に形成されている。構造体が320の温度で10分間アニールされ、その後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。<sup>40</sup>

**【0099】**

純Al層上に900の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0100】**

(実施例33)

厚さが1800のAl-Nd合金膜が基板上に形成された後、厚さが2000の純Al層がAl-Nd合金膜上に形成されている。構造体が320の温度で10分間アニールされ、その後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。<sup>50</sup>

**【0101】**

純A1層上に900 の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0102】**

(実施例34)

厚さが1800 のA1-Nd合金膜が基板上に形成された後、厚さが1000 の純A1層がA1-Nd合金膜上に形成されている。A1-Nd合金層の純A1層に対する厚さ比率は、約1:0.55である。構造体が320 の温度で10分間アニールされ、その後、走査型電子顕微鏡(SEM)により積層構造体を観察する。この結果も、ヒロック等の発生が無いことを示している。

10

**【0103】**

純A1層上に900 の厚さで金属Mo層が更に形成されている。SEM下で、構造体が良好な断面形状を有することが分かった。

**【0104】**

なお、第2の実施形態(実施例27~33)において、純A1層は、一般に、A1-Nd合金(バリア層)よりも厚いが、ヒロック等を効果的に防止するため、純A1層がA1-Nd合金層よりも薄くても良い(実施例34)。

**【0105】**

実施例27~34において、基板と純A1層との間に介挿されたA1-Nd合金層は、ヒロック等の発生を効果的に防止する。

20

**【0106】**

実施例27~34の結果は、導電層が基板上に形成された少なくとも2層のアルミニウム(A1)層を備えており、そのアルミニウム層は、基板上に形成されたバリアA1(A1-Nd合金)層とバリアA1層上に形成された純A1層とを含み、バリアA1層が約300オングストロームから1800オングストロームの範囲の厚さを有し、純A1層が約1000オングストロームから2000オングストロームの範囲の厚さを有することを示している。バリアA1層の純A1層に対する厚さ比率は、約1:6.67から1:0.55の範囲である。そのため、ガラス基板と純A1層との間の熱膨張の差に基づいて生じる熱応力が効果的に緩和されている。したがって、ヒロックの発生を防止するとともに、これらの積層構造体の良好な断面形状を維持するために、A1-Nd合金層は、約100オングストロームから400オングストロームの範囲の厚さ、好ましくは約300オングストロームから900オングストロームの範囲の厚さを有する。純A1層は、約500オングストロームから4500オングストロームの範囲の厚さ、好ましくは約1500オングストロームから3000オングストロームの範囲の厚さを有する。

30

**【0107】**

実際の用途において、本発明の第2の実施形態に係る殆どの積層構造体(実施例27~33)は、製造コストを考慮して、非常に厚い純A1層と、非常に薄いA1-Nd合金層とを備えている。例えば、450 のA1-Nd合金層と2000 の純A1層とを備える構造体のコストは、1800 のA1-Nd合金層だけを備える構造体のコストの66%である。また、A1の電気抵抗は、A1-Nd合金のそれよりも低い(約50%)。したがって、A1Nd/A1から成る更に薄い複合体を使用して、サイズを減少させるとともに、デバイスの均一性を向上させることにより、デバイス要件を満たすことができる。

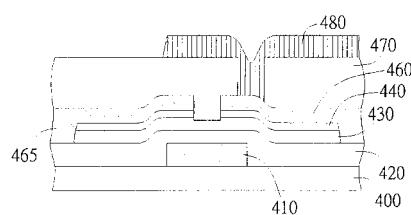

40

**【0108】**

本発明の実施形態に係る構造体は、電子デバイスの配線パターンまたは電子パターン等の導電パターンとして使用することができる。以下の説明において、本発明の構造体は、薄膜トランジスタ(TFT)の金属ゲート電極として使用されている。図7は、本発明の実施形態に係るTFTのボトムゲートの断面図である。先ず最初に、基板400が設けられている。基板400上にわたって導電層が堆積され、この導電層がエッチングされることにより、ゲート電極410が形成されている。

**【0109】**

50

本発明の第1の実施形態において、ゲート電極410は、基板400上に形成されたバリアA1層およびバリアA1層上に形成された純A1層を含む少なくとも2層のA1層を備えている。バリアA1層は、窒化アルミニウム(A1Nx)、酸化アルミニウム(A1Ox)、酸窒化アルミニウム(A1OxNy)のうちの1つの化合物を少なくとも含む。デバイスがエッティングされた後に良好な断面形状を得るために、バリアA1層の純A1層に対する厚さ比率は、約1:6.25から1:2の範囲である。また、保護の目的のため、純A1層上に300から1200の厚さでMo層またはMoN層が更に形成されても良い。

#### 【0110】

本発明の第2の実施形態において、ゲート電極410は、基板400上に形成されたAl-Nd合金層およびAl-Nd合金層上に形成された純A1層を含む少なくとも2つのA1層を備えている。Al-Nd合金層は、約100から4000の範囲の厚さ、好ましくは約300及び900の範囲の厚さを有する。純A1層は、約500オングストロームから4500オングストロームの範囲の厚さ、好ましくは約1500オングストローム及び3000オングストロームの範囲の厚さを有する。バリアA1層の純A1層に対する厚さ比率は、約1:6.67から1:0.55の範囲である。同様に、保護の目的のため、純A1層上に300から1200の厚さでMo層またはMoN層が更に形成されても良い。

#### 【0111】

その後、ゲート電極410上にわたってゲート絶縁層420が形成されている。その後、堆積およびフォトリソグラフィにより、アモルファスシリコン層430およびオーム接觸層440がゲート絶縁層420上に形成されている。

#### 【0112】

次に、ソース領域460およびドレイン領域465は、基板400上にわたって金属(例えばCrおよびAl)層を堆積しパターニングすることにより形成されている。また、アモルファスシリコン層430の表面を露出させるため、チャネル領域も形成されている。この場合、このチャネルによってソース領域460とドレイン領域465とが分割されている。

#### 【0113】

その後、ソース領域460、ドレイン領域465、チャネルを覆うため、基板400上にわたってパッシベーション層470が形成される。フォトリソグラフィおよびエッティングにより、パッシベーション層470に開口が形成され、ドレイン領域460が露出される。最後に、パッシベーション層470上にわたってパターン化された透明電極(ITO)380が形成されるとともに、透明電極によって開口が満たされている。

#### 【0114】

無論、本発明を様々な電子装置に適用でき、本発明がTFTデバイスの用途に限定されないことは言うまでもない。本発明の積層構造体によれば、製造コストをかなり減らすことができ、ヒロック等を効果的に抑制することができる。また、A1層の組み合わせ(純A1層の下側にバリア層)の電気抵抗は、A1系の層(例えばAl-Nd合金層)だけの電気抵抗よりも十分に低く、そのため、適用されるデバイスの電気的特性が向上する。

#### 【0115】

実施例および好ましい実施形態において本発明を説明してきたが、本発明がこれらに限定されないことは言うまでもない。逆に、本発明は、様々な変形例、同様の配置構成、手続きを網羅しようとするものであり、したがって、添付の請求の範囲は、そのような変形例、同様の配置構成、手続きの全てを包含するように最も広く解釈されるべきである。

#### 【図面の簡単な説明】

#### 【0116】

【図1】ガラス基板上に金属を堆積させる一例(従来技術)を示す図である。

【図2】ガラス基板上に形成されたA1配線層中でアニーリング後に生じるヒロックの一例(従来技術)を示す図である。

10

20

30

40

50

【図3】ガラス基板上に形成されたA1合金のグレインのアニーリング後の一例（従来技術）を示す図である。

【図4】ガラス基板上に形成されてA1グレインを上側から覆う金属層の一例（従来技術）を示す図である。

【図5】ガラス基板とA1グレインとの間に挟まれたバリア金属層の一例（従来技術）を示す図である。

【図6】基板上に少なくとも2つのアルミニウム層を有する本発明の実施形態に係る導電層を示す図である。

【図7】本発明の実施形態に係るTFTのボトムゲートの断面図である。

【符号の説明】

【0117】

102, 202, 302, 304 ガラス基板

104 グレイン

106 グレイン境界

110 ヒロック

204, 240 グレイン

206 グレイン境界

210 粒子

212 金属層

304 バリアA1層

302, 304, 400 基板

306 純A1層層

410 ゲート電極

420 ゲート絶縁層

430 アモルファスシリコン層

440 オーム接触層

460 ソース領域

460, 465 ドレイン領域

470 パッシベーション層

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/786 (2006.01) H 01 L 29/78 617M

(72)発明者 クン - ハオ , チャン

台湾台南県台南科学工業園区新市郷奇業路1号 奇美電子股 ふん 有限公司内

(72)発明者 シイ - ミン , イエー<sup>一</sup>

台灣台南市新市區奇業路1號 奇美電子股 ふん 有限公司内

(72)発明者 ジュイ - タン , イン

台湾台南県台南科学工業園区新市郷奇業路1号 奇美電子股 ふん 有限公司内

審査官 辻 弘輔

(56)参考文献 特開2002-368202 (JP, A)

特開2000-208773 (JP, A)

特表2003-517514 (JP, A)

特開2002-151810 (JP, A)

特開昭63-080550 (JP, A)

特開2002-367928 (JP, A)

特開平10-199827 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/3205

H 01 L 21/3213

H 01 L 21/768

H 01 L 21/28

H 01 L 23/52

H 01 L 29/423

H 01 L 29/49

H 01 L 29/786

H 01 L 21/336