(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-297048

(P2004-297048A)

(43) 公開日 平成16年10月21日(2004.10.21)

(51) Int.Cl.<sup>7</sup>

**H01L 21/8242**

**G11C 11/404**

**G11C 11/56**

**H01L 27/10**

**H01L 27/108**

F 1

H01L 27/10 321

H01L 27/10 461

H01L 29/78 613B

H01L 29/78 612B

G11C 11/34 352C

テーマコード(参考)

5FO83

5F110

5MO24

審査請求 未請求 請求項の数 16 O L (全 32 頁) 最終頁に続く

(21) 出願番号 特願2004-63307 (P2004-63307)

(22) 出願日 平成16年3月8日 (2004.3.8)

(31) 優先権主張番号 特願2003-65314 (P2003-65314)

(32) 優先日 平成15年3月11日 (2003.3.11)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2003-65393 (P2003-65393)

(32) 優先日 平成15年3月11日 (2003.3.11)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 加藤 清

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 5F083 AD02 AD10 AD69 GA05 GA09

GA27 HA02 JA01 JA33 JA36

JA37 JA39 JA40 MA06 MA19

PR03 PR05 PR33 PR34 PR40

ZA12 ZA13 ZA21

最終頁に続く

(54) 【発明の名称】集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法

## (57) 【要約】

【課題】 作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供を課題とする。

【解決手段】 DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

D R A M を有し、

前記 D R A M には、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、活性層と、前記活性層を間に挟んで重なり合っている第 1 の電極及び第 2 の電極とを有することを特徴とする集積回路。

**【請求項 2】**

D R A M を有し、

前記 D R A M には、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、活性層と、前記活性層が有するチャネル形成領域を間に挟んで重なり合っている第 1 の電極及び第 2 の電極とを有しており、10

データに従って前記薄膜トランジスタのドレイン電圧を制御することで、前記チャネル形成領域における正孔の蓄積の有無を選択し、

前記正孔の蓄積の有無を把握することで前記データを読み出すことを特徴とする集積回路。

**【請求項 3】**

請求項 2 において、前記正孔の蓄積の有無は、前記薄膜トランジスタのドレイン電流または前記薄膜トランジスタの閾値電圧を用いて把握することを特徴とする集積回路。

**【請求項 4】**

D R A M を有し、

前記 D R A M には、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、活性層と、前記活性層が有するチャネル形成領域を間に挟んで重なり合っている第 1 の電極及び第 2 の電極とを有しており、20

前記チャネル形成領域に蓄積された正孔の量によって情報を格納し、前記正孔はインパクトイオン化によって前記チャネル形成領域に蓄積することを特徴とする集積回路。

**【請求項 5】**

請求項 4 において、前記メモリセルに格納された情報は、前記薄膜トランジスタのドレイン電流または閾値電圧を用いて読み出すことを特徴とする集積回路。

**【請求項 6】**

D R A M を有し、

前記 D R A M には、記憶素子を備えたメモリセルが複数設けられており、

前記記憶素子として、第 1 の電極と、第 2 の電極と、活性層と、第 1 の絶縁膜と、第 2 の絶縁膜とを有する薄膜トランジスタを用いており、30

前記第 1 の電極は前記第 1 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 2 の電極は前記第 2 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 1 の電極と前記第 2 の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっていることを特徴とする集積回路。

**【請求項 7】**

D R A M を有し、

前記 D R A M には、第 1 の薄膜トランジスタ及び第 2 の薄膜トランジスタを備えたメモリセルが複数設けられており、40

前記第 1 の薄膜トランジスタは、第 1 の電極と、第 2 の電極と、活性層と、第 1 の絶縁膜と、第 2 の絶縁膜とを有し、

前記活性層は、チャネル形成領域と、前記チャネル形成領域を間に挟んで存在するソース領域及びドレイン領域とを有し、

前記第 1 の電極は前記第 1 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 2 の電極は前記第 2 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 1 の電極と前記第 2 の電極は、前記チャネル形成領域を間に挟んで重なっていることを特徴とする集積回路。

、前記第 2 の薄膜トランジスタによって、前記ドレイン領域に与えられる電位が制御され50

ていることを特徴とする集積回路。

**【請求項 8】**

D R A M を有し、

前記 D R A M には、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、第 1 の電極と、第 2 の電極と、活性層と、第 1 の絶縁膜と、第 2 の絶縁膜とを有し、

前記活性層は、チャネル形成領域と、前記チャネル形成領域を間に挟んで存在するソース領域及びドレイン領域とを有し、

前記第 1 の電極は前記第 1 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 2 の電極は前記第 2 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 1 の電極と前記第 2 の電極は、前記活性層を間に挟んで重なっており、

前記チャネル形成領域は、前記第 1 の電極及び前記第 2 の電極と重なる領域と、前記第 1 の電極と前記第 2 の電極のうち、前記第 2 の電極のみと重なる領域とを有しており、

前記第 2 の電極のみと重なる領域は、前記第 1 の電極及び前記第 2 の電極と重なる領域よりも、前記ドレイン領域側に存在することを特徴とする集積回路。

**【請求項 9】**

第 1 の電極、第 2 の電極及び活性層を有する薄膜トランジスタを各メモリセルに備えた D R A M と、前記薄膜トランジスタのドレイン電圧を制御する第 1 の手段と、前記第 1 の電極の電位を制御する第 2 の手段と、前記活性層のチャネル形成領域における正孔の蓄積量を把握する第 3 の手段とを有し、

前記第 1 の電極及び前記第 2 の電極は、前記活性層を間に挟んで重なり合っており、

前記第 1 の手段及び前記第 2 の手段を用いて前記電荷の蓄積量を制御することで、データを書き込み、前記第 3 の手段によって前記正孔の蓄積量を把握することで前記データを読み出すことを特徴とする集積回路。

**【請求項 10】**

第 1 の電極、第 2 の電極及び活性層を有する薄膜トランジスタを各メモリセルに備えた D R A M と、前記薄膜トランジスタのドレイン電圧を制御する第 1 の手段と、前記第 1 の電極の電位を制御する第 2 の手段と、前記活性層のチャネル形成領域における正孔の蓄積量を把握する第 3 の手段とを有し、

前記第 1 の電極及び前記第 2 の電極は、前記活性層を間に挟んで重なり合っており、

前記第 1 の手段及び前記第 2 の手段を用いて前記電荷の蓄積量を制御することで、3 値以上のデータを書き込み、前記第 3 の手段によって前記正孔の蓄積量を把握することで前記データを読み出すことを特徴とする集積回路。

**【請求項 11】**

請求項 9 または請求項 10 において、

前記正孔の蓄積量は、前記薄膜トランジスタのドレイン電流、前記薄膜トランジスタの閾値電圧または前記活性層に含まれるソース領域とドレイン領域間の電圧を用いて把握することを特徴とする集積回路。

**【請求項 12】**

D R A M を有する集積回路と、前記集積回路によって駆動が制御される画素部とを有し、

前記 D R A M には、記憶素子を備えたメモリセルが複数設けられており、

前記記憶素子として、第 1 の電極と、第 2 の電極と、活性層と、第 1 の絶縁膜と、第 2 の絶縁膜とを有する第 2 の薄膜トランジスタを用いており、

前記第 1 の電極は前記第 1 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 2 の電極は前記第 2 の絶縁膜を間に挟んで前記活性層と重なっており、

前記第 1 の電極と前記第 2 の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっていることを特徴とする半導体表示装置。

**【請求項 13】**

各メモリセルに薄膜トランジスタを備えた D R A M を有し、

10

20

30

40

50

前記薄膜トランジスタは、活性層と、前記活性層を間に挟んで重なり合っている第1の電極及び第2の電極とを有し、

データの書き込みは、前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記活性層が有するチャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって行ない、

前記データの読み出しは、前記薄膜トランジスタのドレイン電流または閾値電圧を用いて行なうことを特徴とする集積回路の駆動方法。

#### 【請求項14】

各メモリセルに薄膜トランジスタを備えたDRAMを有し、

10

前記薄膜トランジスタは、活性層と、前記活性層を間に挟んで重なり合っている第1の電極及び第2の電極とを有し、

前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記活性層が有するチャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって、3値以上のデータの書き込みを行ない、

前記薄膜トランジスタのドレイン電流または閾値電圧を用いて前記データの読み出しを行なうことを特徴とする集積回路の駆動方法。

#### 【請求項15】

各メモリセルに薄膜トランジスタを備えたDRAMを有し、

20

前記薄膜トランジスタは、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有し、前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、前記第1の電極と前記第2の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっており、

データの書き込みは、前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記チャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって行ない、

前記データの読み出しは、前記薄膜トランジスタのドレイン電流または閾値電圧を用いて行なうことを特徴とする集積回路の駆動方法。

30

#### 【請求項16】

各メモリセルに薄膜トランジスタを備えたDRAMを有し、

前記薄膜トランジスタは、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有し、前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、前記第1の電極と前記第2の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっており、

前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記活性層が有するチャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって、3値以上のデータの書き込みを行ない、

40

前記薄膜トランジスタのドレイン電流または閾値電圧を用いて前記データの読み出しを行なうことを特徴とする集積回路の駆動方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、薄膜の半導体膜を用いて形成された、DRAM混載の集積回路に関し、さら

50

には該集積回路を用いた半導体表示装置及び該集積回路の駆動方法に関する。

【背景技術】

【0002】

安価なガラス基板を用いて形成されるフラットパネルディスプレイは、解像度が高くなるにつれて、実装に用いる画素部周辺の領域（額縁領域）の基板に占める割合が増大し、小型化が妨げられる傾向がある。そのため、単結晶のシリコンウェハを用いて形成されたI Cを実装する方式には限界があると考えられており、集積回路を画素部と同じガラス基板上に一体形成する技術、所謂システムオンパネル化が重要視されている。

【0003】

下記特許文献1には、ガラス基板上に形成された半導体素子の一つである、デュアルゲート型の薄膜トランジスタの構成について記載されている。 10

【0004】

【特許文献1】特開2002-359376号公報

【0005】

ガラス基板上に形成される集積回路は、単結晶のシリコンウェハに形成された集積回路に比べて集積度が低いため、実用化に際し高集積化が重要な課題である。特に、集積回路の高機能化を実現するためには、高集積化のみならず半導体メモリの大容量化も不可欠である。半導体メモリの中でも、DRAM (Dynamic Random Access Memory) は、他の半導体メモリと比べて大容量化と低コスト化に優れている。DRAMは、通常、1つのトランジスタと1つのキャパシタでメモリセルを構成する単純な構造を有しており、SRAM等の他の半導体メモリに比べてメモリセルを構成するための半導体素子が少ない。よって、1チップの中に多数のメモリセルを作り込むことが可能であり、大記憶容量のLSIを作りやすく、結果的に他の半導体メモリに比べてピット当たりのコストを安くすることができる。 20

【0006】

従ってDRAMは、ガラス基板上に形成された集積回路の高集積化を推し進める上で、欠くことのできない半導体メモリの一つであるといえる。

【発明の開示】

【発明が解決しようとする課題】

【0007】

このようにDRAMは大容量化に適しているが、チップサイズの増大を抑えつつ、LSIの集積度をより高めるためには、他の半導体メモリと同様にもっとメモリの占める面積を抑えなくてはならない。そのためには、当然、各メモリセルの面積をさらに小さくする必要性がある。DRAMの場合、メモリセルの微細化にあたって、リフレッシュ動作の頻度低減、センス動作時の動作余裕確保、および一線によるソフトエラー率低減のために、蓄積容量を常に一定の値以上確保しなくてはならない。そこで、誘電体膜の材料の最適化、キャパシタの三次元化等、メモリセルの占有面積を抑えつつ蓄積容量を確保するための様々な試みがなされている。 30

【0008】

しかし、誘電体膜の材料の最適化には限界があり、飛躍的に誘電率の低い材料を得ることは難しい。また、例えばスタック型メモリセルやトレンチ型メモリセルのような、三次元構造のキャパシタを用いたDRAMは、チップサイズの縮小化には有効であるが、ブレーナ型メモリセルを用いたDRAMに比べて、作製工程が複雑化するため、1ピット当たりのコストが高くなるという難点がある。よって、大容量化と低コスト化に優れるという長所を生かしつつ、DRAMの高集積化を図るのは困難であった。 40

【0009】

本発明は上述した問題に鑑み、作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供及びその駆動方法の提供を課題とする。また更には、該集積回路を用いた半導体表示装置に関する。

【課題を解決するための手段】

50

## 【0010】

上記課題を解決するために、本発明の集積回路に積載するDRAMは、第1のゲート電極と、第2のゲート電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有するデュアルゲート型の薄膜トランジスタを、各メモリセルに備える。活性層は、第1のゲート電極と第2のゲート電極の間に存在し、さらに活性層と第1のゲート電極との間には第1の絶縁膜が、また活性層と第2のゲート電極との間には第2の絶縁膜が存在する。そして本発明では、上記構成を有する薄膜トランジスタにおいて、インパクトイオン化によるチャネル形成領域への電荷の蓄積を利用して、データの書き込み、読み出しを行なう。

## 【0011】

インパクトイオン化の発生は、ドレイン電圧により制御することができる。ドレイン電圧を高め、約100kV/cm以上の高電界状態を形成すると、イオン化の閾値エネルギーに達したキャリアがインパクトイオン化を引き起こし、電子・正孔対が発生する。発生した電子はドレイン領域に流れ、正孔はソース領域に流れるが、第1のゲート電極の電位を制御することによって、発生した正孔をチャネル形成領域に蓄積させることができある。具体的には、第1のゲート電極の電位をソース領域の電位以上とすると正孔はソース領域に流れ込み、第1のゲート電極の電位をソース領域の電位より低くすると正孔はチャネル形成領域に蓄積する。正孔の蓄積は、チャネル形成領域の第1のゲート電極側の電位が、ソース領域の電位と等しくなるまで行なわれるため、その蓄積量は第1のゲート電極の電位によって制御することができる。

## 【0012】

正孔がチャネル形成領域に蓄積すると、チャネル形成領域の第1のゲート電極側の電位が上昇することによって閾値がシフトし、ドレイン電流が増大するので、得られるドレイン電流の大きさから正孔（電荷）の蓄積の状態を把握することができる。よって、チャネル形成領域への電荷の蓄積によりデータを書き込み、ドレイン電流または閾値によりデータを読み出すことができる。

## 【0013】

なお正孔の蓄積は、チャネル形成領域の第1のゲート電極側の電位が、ソース領域の電位と等しくなるまで行なわれるため、その蓄積量は、第1のゲート電極の電位によって制御することができる。そこで本発明では、書き込み時において、第1のゲート電極に与える電位の高さを複数選択できるようにし、書き込み後の正孔の蓄積量に差を持たせることで、3値以上のデータの書き込みを行なっても良い。そして、正孔の蓄積量が増加するに従い閾値電圧またはドレイン電流が高くなる特性を利用し、3値以上のデータの読み出しを行なう。上記構成によって、面積を抑えつつ、DRAMの記憶容量を増やすことができる。

## 【0014】

本発明では、ドレイン電流によりデータを読み出した後でも、キャパシタを用いた一般的な構成のDRAMとは異なり、電荷が蓄積された状態をある程度維持できるので、再び書き込みを行なわずにデータを読み出すことが可能である。よって同じデータを必要とする際、再び書き込む回数を削減し、DRAMの低消費電力化を図ることができる。その代わり、一旦データを書き込んだ後に別のデータを上書きする場合は、第1のゲート電極の電位を高くすることで蓄積した電荷を放出（バージ）させ、前のデータを完全に消去してから、データの書き込みを行なうことが必要である。

## 【0015】

なお、本発明においても、一般的なDRAMと同様に、リフレッシュ動作が必要である。これは、チャネル形成領域に電荷が蓄積された状態と蓄積されていない状態の電荷量の差が、主に熱的な電子正孔対生成によって、徐々に減少するためである。リフレッシュは、別のデータを上書きする場合と同様に、第1のゲート電極の電位を高くして蓄積されている電荷をバージしてから、再びデータを書き込むようにする。

## 【0016】

また一般的に薄膜トランジスタは、単結晶の半導体膜で形成されたトランジスタと比較

10

20

30

40

50

すると、活性層中に存在する粒界によって電荷がリークしやすく、電荷の保持時間が短くなる傾向にあると考えられる。特に3値以上の多値のデータの場合、値が4値、5値と増えていくにつれて各値どうしの電荷量の差が小さくなるため、この傾向が顕著であり、データの正確さを維持するのが困難となる。しかし単結晶の半導体膜で形成されたトランジスタでは、活性層を間に挟んで存在する2つのゲート電極を形成する際に、従来のプロセスを大幅に変更する必要があり、工程が複雑化してコストが高くなる。そこで本発明では、金属触媒を用いて結晶化した半導体膜を、薄膜トランジスタの活性層として用いる。

金属触媒を用いて結晶化された半導体膜は、例えば特開2001-5426号公報に記載されているように、結晶粒界において異なる二つの結晶粒が極めて整合性よく接合することが実証されている。即ち、結晶粒界において結晶格子が連続的に連なり、結晶欠陥等に起因するトラップ準位を非常に作りにくい構成となっている。その結果、電子正孔対の生成の核となる場所が少なく、電荷保持特性の高い薄膜トランジスタを実現することができ、特に多値化に伴う保持時間の短縮化を抑えることができる。そして、単結晶のトランジスタに比べて、然程工程を複雑化させずに、2つ目のゲート電極の作製工程を容易に追加することができる。従って、単結晶の場合と異なり、工程の複雑化によるコストの上昇を抑えることができる。

#### 【0017】

なお本発明において薄膜トランジスタは、完全空乏型のSOIトランジスタである。完全空乏型のSOIトランジスタは、活性層の膜厚が薄く、空乏層が活性層全体に広がる場合に実現される。単結晶SOI基板では、非常に薄い単結晶のシリコン膜を得ることが難しいという問題があるが、薄膜トランジスタでは、半導体膜を堆積することによって形成するため、薄い活性層を作製することは容易である。

#### 【0018】

また金属触媒を用いた方法の他に、薄膜の半導体膜の結晶化方法には、電熱炉を使用した熱結晶化方法、レーザ光を用いたレーザ結晶化法、赤外光を用いたランプアニール結晶化法等がある。しかし、他の結晶化方法において結晶化された半導体膜は、金属触媒を用いた場合と比べて、結晶粒界における異なる二つの結晶粒の整合性が劣り、その結果、結晶粒界での結晶欠陥等に起因するトラップ準位が多数存在する傾向がある。このようなトラップ準位が多数あると、これを核として電子正孔対が生成されるため、電荷保持特性が劣ることになる。電荷保持特性が低いと、リフレッシュ動作の頻度を高くする必要があり、書き込みや読み出し動作との衝突を避ける必要から、動作速度が遅くなると言った不具合が生じてしまう。

#### 【0019】

また、金属触媒を用いて結晶化された半導体膜は、他の結晶化方法に比べて、結晶粒の大きさや結晶方位が比較的揃っているため、電荷保持を行なう薄膜トランジスタの特性のばらつきを小さくすることができる。メモリの動作条件は、多数のメモリセルの特性の分布（ばらつき）を考慮して決定されるため、ばらつきの小さい薄膜トランジスタを得ることは、リフレッシュ動作の頻度、ビット線やワード線に供給する電位といったあらゆる動作条件において有利であり、消費電力や動作速度といったメモリの性能を向上することが可能である。

#### 【0020】

上述した通り本発明では、1つの薄膜トランジスタでデータを記憶することができるの、キャパシタを別途設ける必要がなく、メモリセルの面積を抑えることができる。よって、コストを抑えつつ、DRAM混載の集積回路の高集積化、大容量化を実現することができる。そして集積回路の高集積化、大容量化の実現により、フラットパネルディスプレイの画素部と同じ基板上に一体形成することが可能な、集積回路の範囲を広げることができ、システムオンパネルの高機能化を実現することができる。

#### 【0021】

なお本発明では、各メモリセルに最低限1つの薄膜トランジスタを設けることで、DRAMを機能させることができるが、これに限定されず、薄膜トランジスタの数は複数

10

20

30

40

50

であっても良い。例えばデータを記憶するための薄膜トランジスタに加えて、スイッチング用の薄膜トランジスタを設け、薄膜トランジスタに記憶されたデータをより確実に保持できるようにしても良い。ただしこの場合、スイッチング用の薄膜トランジスタはデュアルゲート型である必要はなく、活性層の一方の側にのみ存在するシングルゲート型の薄膜トランジスタであっても良い。

#### 【0022】

なお本発明の範疇に含まれる集積回路には、マイクロプロセッサ、画像処理回路等、DRAMを用いることができる、ありとあらゆる集積回路が含まれる。また本発明の半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)等や、半導体膜を用いた回路素子を駆動回路に有しているその他の表示装置がその範疇に含まれる。10

#### 【発明の効果】

#### 【0023】

本発明では、薄膜トランジスタにデータを記憶することができるので、キャパシタを別途設ける必要がなく、メモリセルの面積を抑えることができる。よって、コストを抑えつつ、DRAM混載の集積回路の高集積化、大容量化を実現することができる。そして集積回路の高集積化、大容量化の実現により、フラットパネルディスプレイの画素部と同じ基板上に一体形成することが可能な、集積回路の範囲を広げることができ、システムオンパネルの高機能化を実現することができる。20

#### 【0024】

また本発明では、書き込み時において、第1のゲート電極に与える電位の高さを複数選択できるようにし、3値以上のデータの書き込みを行なうことで、面積を抑えつつ、DRAMの記憶容量を増やすことができる。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本実施の形態の記載内容に限定して解釈されるものではない。30

#### 【0026】

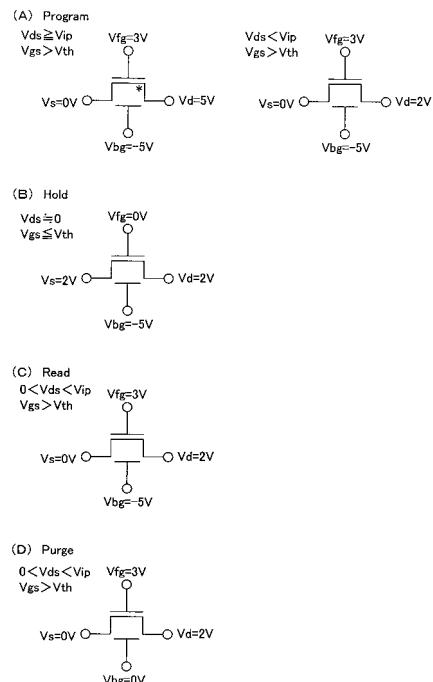

図1を用いて、本発明の集積回路に用いられるDRAMの構成について説明する。図1(A)に、各メモリセルに設けられるデュアルゲート型の薄膜トランジスタ(TFT)100の、断面図を示す。

#### 【0027】

本発明において記憶素子として用いるTFT100は、2つの電極(以下、第1のゲート電極101、第2のゲート電極102と呼ぶ)、活性層103、第1の絶縁膜104、第2の絶縁膜105を有している。活性層103は、ソース領域106と、ドレイン領域107と、ソース領域106とドレイン領域107の間に存在するチャネル形成領域108とを有している。40

#### 【0028】

図1(A)に示すように、第1のゲート電極101と第2のゲート電極102の間に活性層103が存在しており、さらに第1のゲート電極101と活性層103の間には第1の絶縁膜104が、第2のゲート電極102と活性層103の間には第2の絶縁膜105が存在している。

#### 【0029】

なお活性層103は図1(A)に示した構成に限定されず、例えばLDD(Light Doped Drain)領域や、第1または第2のゲート電極101、102と重なる不純物領域を、単数または複数を有していても良い。またチャネル形成領域108の一部が、第1または第2のゲート電極101と重ならないような構成を有していても良い。50

## 【0030】

そして、第1のゲート電極101、第2のゲート電極102、ソース領域106、ドレイン領域107に与える電位によって、DRAMの各種動作を制御することができる。特に、データの書き込み(Program)の際のインパクトイオノ化は、ソース領域106、ドレイン領域107に与える電位によって制御可能である。

## 【0031】

図1(B)に、インパクトイオノ化の際に正孔が蓄積する様子を、模式的に示す。図1(B)は、図1(A)に示したTFTの拡大図であり、第1のゲート電極101の電位をVbg、第2のゲート電極102の電位をVfg、ソース領域106の電位をVs、ドレイン領域107の電位をVdsとして示す。

10

## 【0032】

インパクトイオノ化は、ドレイン領域107の電位Vdsからソース領域の電位Vsを差し引いた電圧に相当するドレイン電圧(Vdssとする)を高めることで、生じさせることができ。キャリアがイオン化の閾値エネルギーに達する程度の高電界の状態を形成するように、ドレイン電圧Vdssを調整する。インパクトイオノ化を引き起こすドレイン電圧Vdssの値は、TFTの構造や特性、具体的には活性層の結晶性や不純物濃度などによって異なる。本発明は、インパクトイオノ化に起因する閾値またはドレイン電流の変動で、データを書き込んだり読み出したりすることができるよう、ドレイン電圧Vdssの値を定めれば良い。

## 【0033】

インパクトイオノ化が生じると電子・正孔対が生じ、発生した電子はドレイン領域に、正孔はソース領域に流れる。その正孔の一部は、図1(B)に「+」で示すように、チャネル形成領域108に蓄積される。そして第1のゲート電極101の電位をソース領域の電位Vsより低くすることで、蓄積される正孔の量を制御することができ、また保持することができる。

20

## 【0034】

さらに本発明では、第1のゲート電極に与える電位の高さを、電位Vsより低い値において複数選択できるようにすることで、正孔の蓄積量のレベルを制御しても良い。

## 【0035】

正孔が蓄積されると、チャネル形成領域の第1のゲート電極側の電位がその蓄積量に見合った分だけ高まり、それによってTFTの閾値電圧及びドレイン電流が変動する。具体的には、正孔の蓄積量が多いほど閾値電圧が高くなり、ドレイン電流も大きくなる。データは、インパクトイオノ化により変動する閾値またはドレイン電流の値を利用して、読み出すことができる。データは1ビットにつき2値の値を有していても良いし、3値以上の値を有していても良い。

30

## 【0036】

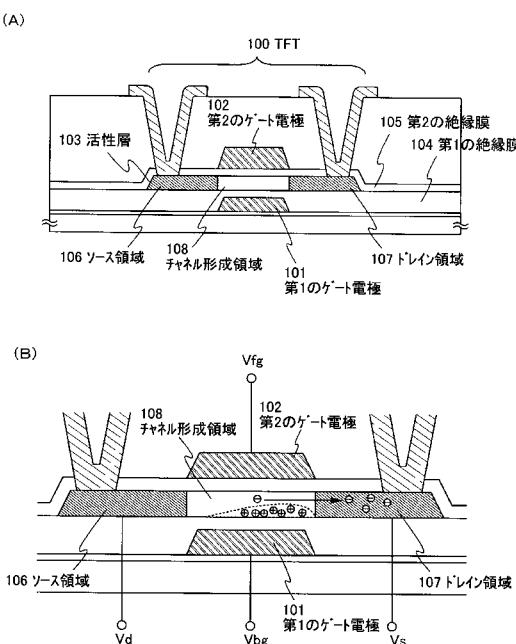

次に図2を用いて、データを記憶するためのTFTの、各動作時における電位の制御の仕方について説明する。

## 【0037】

まず、データの書き込み(Program)時の動作について説明する。図2(A)に、書き込み時におけるTFTの回路図と、各部位に与えられる電位の一例を示す。なお図2では、DRAMに2値のデータを記憶する場合を例示している。

40

## 【0038】

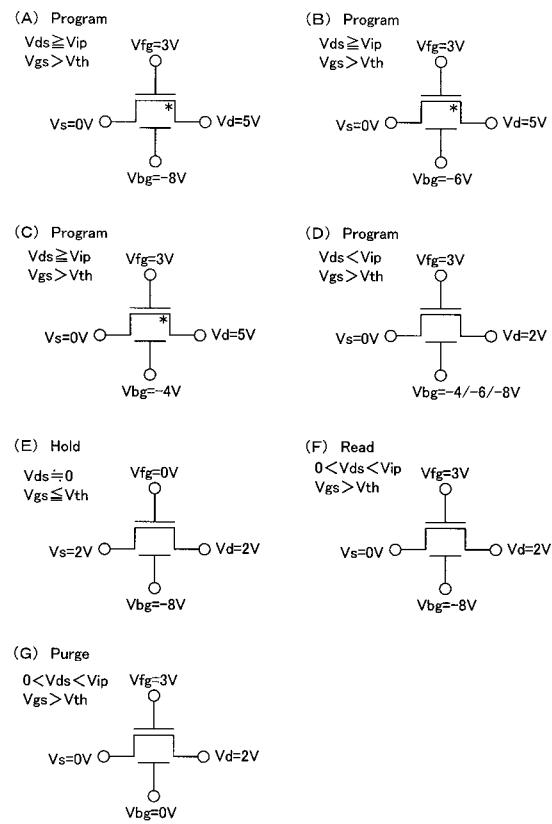

データの書き込み時には、第2のゲート電極の電位Vfgからソース領域の電位Vsを差し引いた電圧に相当するゲート電圧(Vgssとする)を、TFTの閾値電圧Vthより高くし、TFTをオンにする。ドレイン電圧Vdsは、インパクトイオノ化により正孔を蓄積する場合と、蓄積させない場合とで異なる。インパクトイオノ化により正孔を蓄積させる場合は、図2(A)の左に示すように、ドレイン電圧Vdsを、インパクトイオノ化が生じる電圧(ここではVipとする)以上に保つ。逆に、正孔を意図的に蓄積させない場合は、図2(A)の右に示すように、ドレイン電圧Vdsを電圧Vipよりも低くする

50

。そして、いずれの場合も、第1のゲート電極の電位 $V_{bg}$ をソース領域の電位 $V_s$ より低く保ち、チャネル形成領域の電荷の状態を保持させる。

#### 【0039】

図2(A)では、例えば左側を $V_s = 0\text{ V}$ 、 $V_d = 5\text{ V}$ 、 $V_{bg} = -5\text{ V}$ 、 $V_{fg} = 3\text{ V}$ とし、右側を $V_s = 0\text{ V}$ 、 $V_d = 2\text{ V}$ 、 $V_{bg} = -5\text{ V}$ 、 $V_{fg} = 3\text{ V}$ とする。

#### 【0040】

次に、図2(A)において書き込まれたデータの保持(Hold)時における、TFTの回路図と、各部位に与えられる電位の一例を、図2(B)に示す。保持時においては、書き込まれたデータを保持するためにゲート電圧 $V_{gs}$ 、閾値電圧 $V_{th}$ とし、TFTをオフにする。そして、インパクトイオン化を生じさせず、電荷の状態を維持するために、 $V_d = 0$ とし、第1のゲート電極の電位 $V_{bg}$ をソース領域の電位 $V_s$ より低く保ったままにする。10

#### 【0041】

図2(B)では、例えば $V_s = 2\text{ V}$ 、 $V_d = 2\text{ V}$ 、 $V_{bg} = -5\text{ V}$ 、 $V_{fg} = 0\text{ V}$ とする。

#### 【0042】

次に、図2(B)において保持されているデータの読み出し(Read)時における、TFTの回路図と、各部位に与えられる電位の一例を、図2(C)に示す。読み出し時においては、保持されているデータを読み出すために、ゲート電圧 $V_{gs} > V_{th}$ とし、TFTをオンにする。そして、インパクトイオン化を生じさせずに、電荷の状態を維持しつつ、その読み出しを行なうために、 $0 < V_{ds} < V_{ip}$ とし、第1のゲート電極の電位 $V_{bg}$ もソース領域の電位 $V_s$ より低く保ったままにする。20

#### 【0043】

図2(C)では、例えば $V_s = 0\text{ V}$ 、 $V_d = 2\text{ V}$ 、 $V_{bg} = -5\text{ V}$ 、 $V_{fg} = 3\text{ V}$ とする。

#### 【0044】

次に、データを再び書き込むかまたはリフレッシュ(Refresh)する際に行なう、ページ(Purge)の動作について説明する。図2(D)に、ページ時におけるTFTの回路図と、各部位に与えられる電位の一例を示す。ページする時には、保持されている電荷を放出するために、ゲート電圧 $V_{gs} > V_{th}$ とし、TFTをオンにする。そしてインパクトイオン化を生じさせずに電荷を放出するために、 $0 < V_{ds} < V_{ip}$ とする。なお第1のゲート電極の電位 $V_{bg}$ は、他の書き込み、保持、読み出しの動作時よりも、高めに設定することが望ましい。第1のゲート電極の電位 $V_{bg}$ をソース領域の電位 $V_s$ より低く保ったままでも $V_{fg}$ に高電位を与えることで電荷の放出は行なわれる所以必須ではないが、より望ましくは $V_{bg} = V_s$ とすることで、高速に電荷の放出を行なうことができ、ページの動作にかかる時間を短くすることができる。30

#### 【0045】

図2(D)では、例えば $V_s = 0\text{ V}$ 、 $V_d = 2\text{ V}$ 、 $V_{bg} = 0\text{ V}$ 、 $V_{fg} = 3\text{ V}$ とする。

#### 【0046】

このように、書き込み、読み出し、保持、ページの一連の動作を、TFTを用いて行なうことができる。なお、図2において示した、 $V_s$ 、 $V_d$ 、 $V_{bg}$ 、 $V_{fg}$ の具体的な値は一例に過ぎず、本発明はこれに限定されない。40

#### 【0047】

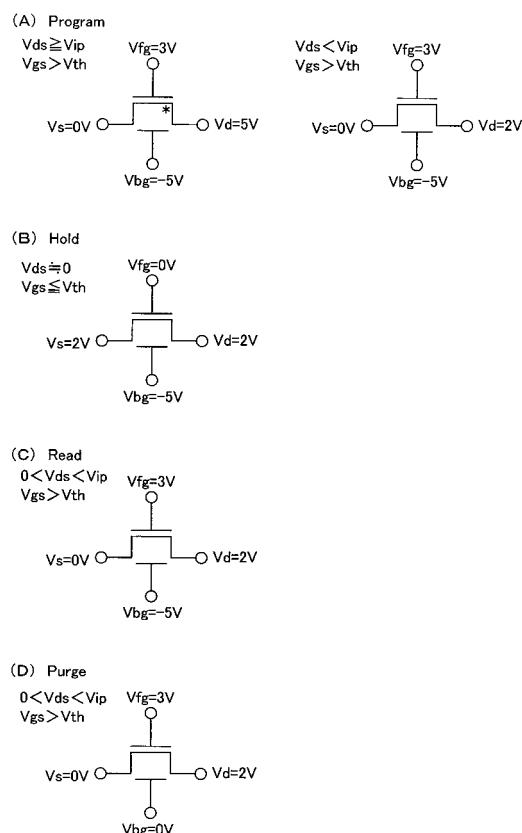

次に図3を用いて、4値のデータを記憶するTFTの、各動作時における電位の制御の仕方について説明する。

#### 【0048】

まず、データの書き込み(Program)時の動作について説明する。図3(A)～図3(D)に、4値の各データの書き込み時におけるTFTの回路図と、各部位に与えられる電位の一例を示す。なお図3では、DRAMに4値のデータを記憶する場合を示しているが50

、記憶するデータが取り得る値は4つに限定されず、3または5以上の値も取り得る。

#### 【0049】

書き込み時にはデータの内容に関わらず、図3(A)～図3(D)の全ての場合において、第2のゲート電極の電位 $V_{fg}$ からソース領域の電位 $V_s$ を差し引いた電圧に相当するゲート電圧( $V_{gs}$ と示す)を、TFTの閾値電圧 $V_{th}$ より高くし、TFTをオンにする。

#### 【0050】

そしてドレイン電圧 $V_{ds}$ は、インパクトイオノ化により正孔を蓄積する場合と、蓄積させない場合とで異なる。インパクトイオノ化により正孔を蓄積させる場合は、図3(A)～図3(C)に示すように、ドレイン電圧 $V_{ds}$ を、インパクトイオノ化が生じる電圧(ここでは $V_{ip}$ とする)以上に保つ。逆に、正孔を意図的に蓄積させない場合は、図3(D)に示すように、ドレイン電圧 $V_{ds}$ を電圧 $V_{ip}$ よりも低くする。

#### 【0051】

そして図3(A)～図3(D)の全ての場合において、第1のゲート電極の電位 $V_{bg}$ をソース領域の電位 $V_s$ より低く保つことで、チャネル形成領域の電荷の状態を保持する。さらに本発明では、図3(A)～図3(C)において、第1のゲート電極の電位 $V_{bg}$ の高さをえることで、正孔の蓄積量に差を持たせる。具体的には、図3(A)において第1のゲート電極の電位 $V_{bg}$ が最も低い状態、その次に図3(B)において第1のゲート電極の電位 $V_{bg}$ が低い状態、図3(C)において他の2つの場合に比べ第1のゲート電極の電位 $V_{bg}$ が最も高い状態とする。よって電荷の蓄積量は、図3(C)、図3(B)、図3(A)の順に多くなる。

#### 【0052】

図3(A)では、例えば $V_s = 0V$ 、 $V_d = 5V$ 、 $V_{bg} = -8V$ 、 $V_{fg} = 3V$ とする。図3(B)では、例えば $V_s = 0V$ 、 $V_d = 5V$ 、 $V_{bg} = -6V$ 、 $V_{fg} = 3V$ とする。図3(C)では、例えば $V_s = 0V$ 、 $V_d = 5V$ 、 $V_{bg} = -4V$ 、 $V_{fg} = 3V$ とする。図3(D)では、例えば $V_s = 0V$ 、 $V_d = 5V$ 、 $V_{bg} = -4V$ 、 $V_{fg} = 3V$ とする。

#### 【0053】

なお、同一行のメモリセルには共通のワード線が接続されている、通常のメモリセルアレイでは、書き込みは、異なるデータ毎に複数回に分けて行なう。つまり、例えば、図3(A)、図3(B)、図3(C)、図3(D)の状態をそれぞれ、“3”、“2”、“1”、“0”的状態と呼ぶことにすると、まず、“1”を書き込むメモリセルの電位を図3(C)の状態とし、他のメモリセルは、図3(D)( $V_{bg}=-4V$ )として何もしないておく。同様に、“2”を書き込むメモリセルの電位を図3(B)の状態とし、他のメモリセルは図3(D)( $V_{bg}=-6V$ )とする書き込みと、“3”を書き込むメモリセルの電位を図3(A)の状態とし、他のメモリセルは、図3(D)( $V_{bg}=-8V$ )とする書き込みを行なうことで、全てのメモリセルに所望の状態の書き込みを行なうことができる。なお、書き込みの順番は、“1”、“2”、“3”的順に限られるわけではない。

#### 【0054】

次に、図3(A)～図3(D)において書き込まれたデータの保持(Hold)時における、TFTの回路図と、各部位に与えられる電位の一例を、図3(E)に示す。保持時においては、書き込まれたデータを保持するためにゲート電圧 $V_{gs}$ 、閾値電圧 $V_{th}$ とし、TFTをオフにする。そして、インパクトイオノ化を生じさせず、電荷の状態を維持するために、 $V_{ds} = 0$ とし、第1のゲート電極の電位 $V_{bg}$ を書き込み時の状態以下に保つ。

#### 【0055】

書き込み後の正孔の蓄積量に関わらず、保持が可能であるように、図3(E)では、例えば $V_s = 2V$ 、 $V_d = 2V$ 、 $V_{bg} = -8V$ 、 $V_{fg} = 0V$ とする。

#### 【0056】

次に、図3(E)において保持されているデータの読み出し(Read)時における、TFT

10

20

30

40

50

Tの回路図と、各部位に与えられる電位の一例を、図3(F)に示す。読み出し時においては、保持されているデータを読み出すために、ゲート電圧 $V_{gs}$  > 閾値電圧 $V_{th}$ とし、TFTをオンにする。そして、インパクトイオノ化を生じさせずに、電荷の状態を維持しつつ、その読み出しを行なうために、 $0 < V_{ds} < V_{ip}$ とし、第1のゲート電極の電位 $V_{bg}$ を書き込み時の状態以下に保つ。

#### 【0057】

このような電圧を印加することによって、保持されている正孔の量に従って決まる、TFTのしきい値電圧や、ドレイン電流もしくはオン抵抗の違いから、保持されているデータを読み出すことができる。なお、多値データの読み出しを、複数回に分ける方法も可能である。

10

#### 【0058】

図3(F)では、例えば $V_s = 0\text{V}$ 、 $V_d = 2\text{V}$ 、 $V_{bg} = -8\text{V}$ 、 $V_{fg} = 3\text{V}$ とする。

#### 【0059】

次に、データを再び書き込むかまたはリフレッシュ(Refresh)する際に行なう、ページ(Purge)の動作について説明する。図3(G)に、ページ時におけるTFTの回路図と、各部位に与えられる電位の一例を示す。ページする時には、保持されている電荷を放出するために、ゲート電圧 $V_{gs}$  > 閾値電圧 $V_{th}$ とし、TFTをオンにする。そしてインパクトイオノ化を生じさせずに電荷を放出するために、 $0 < V_{ds} < V_{ip}$ とする。なお第1のゲート電極の電位 $V_{bg}$ は、他の書き込み、保持、読み出しの動作時よりも、高めに設定することが望ましい。第1のゲート電極の電位 $V_{bg}$ をソース領域の電位 $V_s$ より低く保ったままでも $V_{fg}$ に高電位を与えることで電荷の放出は行なわれる所以必須ではないが、より望ましくは $V_{bg} = V_s$ とすることで、高速に電荷の放出を行なうことができ、ページの動作にかかる時間を短くすることができる。

20

#### 【0060】

図3(G)では、例えば $V_s = 0\text{V}$ 、 $V_d = 2\text{V}$ 、 $V_{bg} = 0\text{V}$ 、 $V_{fg} = 3\text{V}$ とする。

#### 【0061】

このように、書き込み、読み出し、保持、ページの一連の動作を、TFTを用いて行なうことができる。また上述したように、第1のゲート電極の電位 $V_{bg}$ を複数選択させることで多値のデータを記憶することができるので、例えば「11」、「10」、「01」、「00」のような2ビットのデータを1つのメモリセルに記憶することができる。なお、図3において示した、 $V_s$ 、 $V_d$ 、 $V_{bg}$ 、 $V_{fg}$ の具体的な値は一例に過ぎず、本発明はこれに限定されない。

30

#### 【0062】

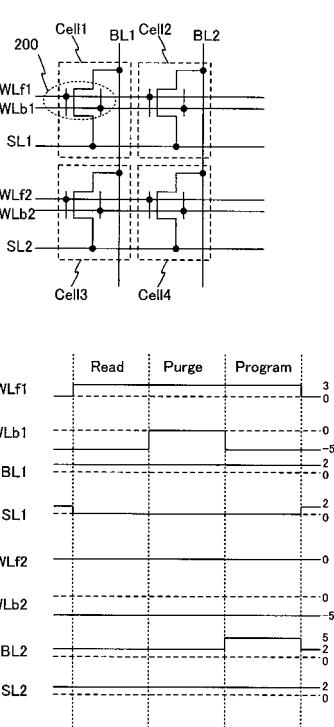

実際にDRAMには、上述したTFTを有する複数のメモリセルが、セルアレイに設かれている。図4を用いて、複数のメモリセルを有するセルアレイにおける、上記各動作について説明する。

#### 【0063】

まず図4(A)に、各メモリセルどうしの配線の接続を、一例として示す。図4(A)は、4つのメモリセル(Cell1、Cell2、Cell3、Cell4)を有するセルアレイの回路図であり、各メモリセルにはデータを記憶するためのTFT200が設けられている。なお図4(A)ではメモリセルが4つ設けられたセルアレイを示しているが、無論メモリセルの数はこれに限定されない。

40

#### 【0064】

各メモリセルのTFT200は、2つのワード線 $WL_b$ 、 $WL_f$ によって電位 $V_{bg}$ 、 $V_{fg}$ が、ビット線 $BL$ によって電位 $V_d$ が、ソース線 $SL$ によって電位 $V_s$ が与えられている。なお各配線のレイアウトは、図4(A)に示した構成に限定されない。

#### 【0065】

具体的に図4(A)では、メモリセル(Cell1)には、ワード線 $WL_b$ 、 $WL_f$ 、

50

ビット線 B L 1、ソース線 S L 1 が対応しており、メモリセル (Cell1) には、ワード線 W L b 1、W L f 1、ビット線 B L 2、ソース線 S L 1 が対応している。また、メモリセル (Cell2) には、ワード線 W L b 2、W L f 2、ビット線 B L 1、ソース線 S L 2 が対応しており、メモリセル (Cell3) には、ワード線 W L b 3、W L f 3、ビット線 B L 2、ソース線 S L 2 が対応している。

#### 【0066】

図4(B)に、タイミングチャートの一例として、一行目のメモリセル(Cell1)及び(Cell2)に対してリフレッシュ動作を行なう場合を示す。なお図4(B)では、図2を参考にして、各期間において各メモリセルに与えられる電位 V<sub>s</sub>、V<sub>d</sub>、V<sub>b g</sub>、V<sub>f g</sub>の関係を示しているが、図3を参考にしても良い。

10

#### 【0067】

リフレッシュ動作は、メモリセルに格納された情報が時間と共に失われるのを防ぐために行なう。具体的には、メモリセルに格納された情報を一旦読み出して、その情報を再び同じメモリセルへ書き込む動作である。リフレッシュは、所定の期間ごとに行なう必要があり、本発明では、トランジスタのチャネル形成領域に蓄積された正孔がどれくらい保持されるかによってその期間が決まってくる。また、本発明のリフレッシュ動作は、読み出し、ページ、書き込みという一連の動作によって行われる。ページは、トランジスタのチャネル形成領域に蓄積された正孔をすべて掃き出して、一旦メモリセルの状態をリセットする動作である。

#### 【0068】

なお、本発明において、ページ(ページを含むリフレッシュ)は、ワード線 W L b を共有するメモリセル、つまり、メモリセル一行に対して同時に行われる。一方、書き込み、読み出しは、個々のメモリセルに対して行なうこともできるし、ページと同様に、メモリセル一行に対して同時に行なうこともできる。従って、読み出しや書き込みは、バス幅に合わせたビット数単位で行なう形態や、メモリセル一行単位で行なう形態が考えられるが、リフレッシュはメモリセル一行単位で行われる。また、多値データの格納はストレスに対して繊細であるため、書き込みや読み出しも一行ごとに行なうことが好ましい。

20

#### 【0069】

最初に読み出されたデータは一旦ラッチ(図示せず)に格納され、ページ後にそのデータを再び書き込む。本実施の形態では、メモリセル(Cell1)には正孔が蓄積されない状態(前述した“0”的状態)、メモリセル(Cell2)には正孔が蓄積された状態(前述した“1”的状態)への書き込みが行われる。なお、書き込み時には B L 2 によってメモリセル(Cell4)への電位も変化するが(書き込み時のストレス)、この電位変動によってメモリセル(Cell4)に蓄積された正孔に影響がないように電位を設定することが重要である。

30

#### 【0070】

なお電源投入直後最初にデータを書き込む場合には、熱や静電気などによって既に電荷が蓄積されている場合も想定されるので、ページを行なってからデータの書き込みを行なうのが望ましい。

#### 【0071】

次に、DRAM混載の集積回路と画素部とを同一基板上に有する、発光装置の作製方法について説明する。ここでは、集積回路に積載されたDRAMに加え、OLEDに供給する電流を制御するTFTを例示して説明する。

40

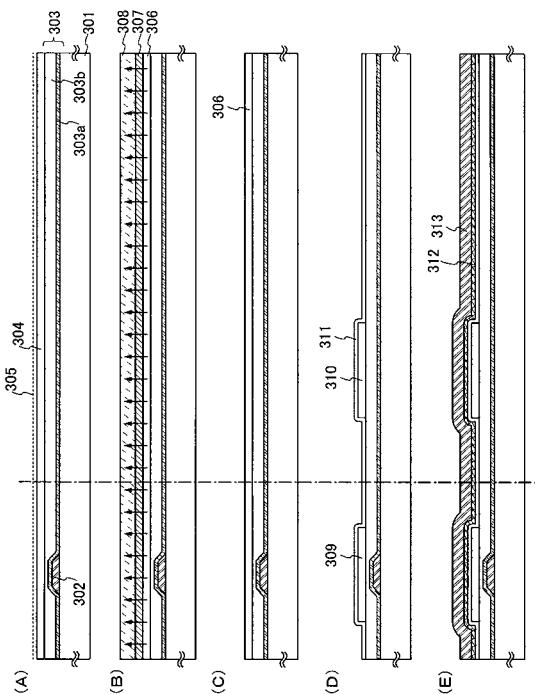

#### 【0072】

まず図5(A)に示すように、基板301の絶縁表面上に、本発明のDRAMの第1の電極302を形成する。第1の電極302は、Al、W、Mo、Ti、Taから選ばれた一種又は複数種からなる導電性の材料で形成することができる。本実施の形態ではWを用いたが、TaNの上にWを積層したものを第1の電極302として用いても良い。また、単層ではなく複数の層で構成していても良い。

#### 【0073】

基板301には、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなど

50

のガラス基板、石英基板、セラミック基板等を用いることができる。また、SUS基板を含む金属基板またはシリコン基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

#### 【0074】

次に、第1の電極302を覆うように第1の絶縁膜303を成膜する。本実施の形態では、第1の絶縁膜303は、2つの絶縁膜(第1の絶縁膜A 303a、第1の絶縁膜B 303b)を積層することで形成されている。第1の絶縁膜A 303aは酸窒化珪素膜を用い、10~50nmの厚さで形成する。第1の絶縁膜B 303bは酸化珪素膜又は酸窒化珪素膜を用い、0.5~1μmの厚さで形成する。なお第1の絶縁膜303はこの構成に限定されず、単層の絶縁膜で形成されていても良いし、3層以上の絶縁膜で形成されていても良い。また材料もこれに限定されない。10

#### 【0075】

第1の絶縁膜303の表面(ここでは第1の絶縁膜B 303bの表面)は、先に形成した第1の電極302に起因する凹凸を有している場合がある。この場合、凹凸を平坦化する工程を設けることが望ましい。本実施の形態ではCMPを用いて平坦化を行なう。第1の絶縁膜303に対するCMPの研磨剤(スラリー)には、例えば、塩化シリコンガスを熱分解して得られるフュームドシリカ粒子をKOH添加水溶液に分散したものを用いると良い。CMPにより第1の絶縁膜を0.1~0.5μm程度除去して、表面を平坦化する。20

#### 【0076】

次に、第1の絶縁膜303の上に50nmの厚さの、非晶質半導体膜304をプラズマCVD法で形成する。非晶質半導体膜304は含有水素量にもよるが、好ましくは400~550で数時間加熱して脱水素処理を行い、含有水素量を5atom%以下として、結晶化の工程を行なうことが望ましい。また、非晶質半導体膜をスパッタ法や蒸着法などの他の作製方法で形成しても良いが、膜中に含まれる酸素、窒素などの不純物元素を十分低減させておくことが望ましい。30

#### 【0077】

用いる半導体は珪素のみに限定されず、例えばシリコングルマニウムを用いることができる。シリコングルマニウムを用いる場合、ゲルマニウムの濃度は0.01~4.5atom%程度であることが好ましい。30

#### 【0078】

なお、第1の絶縁膜303と非晶質半導体膜304をいずれもプラズマCVD法で作製する場合、これらの2つの膜を大気に曝すことなく連続して形成しても良い。連続成膜することによって、大気による表面の汚染を極力抑え、よって作製されるTFTの特性バラツキを低減させることができる。

#### 【0079】

次に、非晶質半導体膜304への触媒の添加を行なう。本実施の形態では、重量換算で1~100ppmのニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布した。なお、酢酸ニッケル塩溶液の馴染みをよくするために、非晶質半導体膜304の表面をオゾン含有水溶液で処理することで極薄い酸化膜を形成し、その酸化膜をフッ酸と過酸化水素水の混合液でエッチングして清浄な表面を形成した後、再度オゾン含有水溶液で処理して極薄い酸化膜を形成しておいても良い。半導体膜の表面は本来疎水性なので、このように酸化膜を形成しておくことにより酢酸ニッケル塩溶液を均一に塗布することができる(図5(A))。40

#### 【0080】

勿論、非晶質半導体膜への触媒の添加は上記方法に限定されず、スパッタ法、蒸着法、プラズマ処理などを用いて添加するようにしても良い。

#### 【0081】

次に、500～650で4～24時間、例えば570、14時間の加熱処理を行った。加熱処理を施すことで、ニッケル含有層305により結晶化が進行し、結晶性の高められた結晶性半導体膜が形成される。

#### 【0082】

加熱処理の方法としては、電熱炉を用いるファーネスアニール法や、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどを用いたRTA法を用いることができる。または、加熱した不活性気体を用いるガス加熱方式のRTAを用いることも可能である。

#### 【0083】

RTA法で行なう場合には、加熱用のランプ光源を1～60秒、好ましくは30～60秒点灯させ、それを1～10回、好ましくは2～6回繰り返す。ランプ光源の発光強度は任意なものとするが、非晶質半導体膜304が瞬間的には600～1000、好ましくは650～750程度にまで加熱されるようにする。このような高温になったとしても、半導体膜が瞬間に加熱されるのみであり、基板301はそれ自身が歪んで変形することはない。

#### 【0084】

その他の方法としてファーネスアニール法を用いる場合には、加熱処理に先立ち、500にて1時間程度の加熱処理を行い、非晶質半導体膜304が含有する水素を放出させておく。そして、電熱炉を用いて窒素雰囲気中にて550～600、好ましくは580で4時間の加熱処理を行い、非晶質半導体膜304を結晶化させる。

#### 【0085】

なお、本実施の形態では触媒元素としてニッケル(Ni)を用いているが、その以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)といった元素を用いても良い。

#### 【0086】

次に、結晶性半導体膜306内に存在する触媒元素のゲッタリングについて説明する。触媒元素を用いる結晶化により、結晶性半導体膜306内には、触媒元素(ここではニッケル)が平均的な濃度として $1 \times 10^{19}/\text{cm}^3$ を越える程度に残存しているものと考えられる。触媒元素が残留していると TFT の特性に悪影響を及ぼす可能性があるため、触媒元素濃度を低減させる工程を設ける必要がある。

#### 【0087】

ゲッタリングの方法は様々であるが、本実施の形態では結晶性半導体膜306をパターンングする前に行なうゲッタリングの一例について説明する。まず、図5(B)に示すように結晶性半導体膜306の表面にバリア層307を形成する。バリア層307は、後にゲッタリングサイトを除去する際に、結晶性半導体膜306がエッチングされるのを防ぐために設ける。

#### 【0088】

バリア層307の厚さは1～10nm程度とする。オゾン水で処理することにより形成されるケミカルオキサイドをバリア層として用いても良い。また、硫酸、塩酸、硝酸などと過酸化水素水を混合させた水溶液で処理しても同様にケミカルオキサイドを形成することができる。他には、酸化雰囲気中のプラズマ処理する方法や、酸素含有雰囲気中の紫外線照射によりオゾンを発生させて酸化処理を行なう方法等を用いても良い。また、クリーンオーブンを用い、200～350程度に加熱して薄い酸化膜を形成しバリア層としても良い。或いは、プラズマCVD法やスパッタ法、蒸着法などで1～5nm程度の酸化膜を堆積してバリア層としても良い。いずれにしても、ゲッタリング工程時に、触媒元素がゲッタリングサイト側に移動できて、ゲッタリングサイトの除去工程時には、エッチング液がしみこまない(結晶性半導体膜306をエッチング液から保護する)膜、例えば、オゾン水で処理することにより形成されるケミカルオキサイド膜、酸化シリコン膜(SiO<sub>x</sub>)、または多孔質膜を用いればよい。

10

20

30

40

50

## 【0089】

次いで、バリア層307上にスパッタ法でゲッタリングサイト308として、膜中に希ガス元素を $1 \times 10^{20}/\text{cm}^3$ 以上の濃度で含むゲッタリング用の半導体膜（代表的には、非晶質シリコン膜）を25~250nmの厚さで形成する。後に除去されるゲッタリングサイト308は結晶性半導体膜306とエッチングの選択比を大きくするため、密度の低い膜を形成することが好ましい。

## 【0090】

なお、希ガス元素は半導体膜中でそれ自体は不活性であるため、結晶性半導体膜306に悪影響を及ぼすことはない。また、希ガス元素としてはヘリウム（He）、ネオン（Ne）、アルゴン（Ar）、クリプトン（Kr）、キセノン（Xe）から選ばれた一種または複数種を用いる。10

## 【0091】

次に、加熱処理を施することでゲッタリングを行なう（図5（B））。加熱処理はファーネスアニール法やRTA法で行なう。ファーネスアニール法で行なう場合には、窒素雰囲気中にて450~600で0.5~12時間の加熱処理を行なう。また、RTA法を用いる場合には、加熱用のランプ光源を1~60秒、好ましくは30~60秒点灯させ、それを1~10回、好ましくは2~6回繰り返す。ランプ光源の発光強度は任意なものとするが、半導体膜が瞬間的には600~1000、好ましくは700~750程度にまで加熱されるようとする。

## 【0092】

加熱処理により、結晶性半導体膜306にある触媒元素が熱エネルギーにより放出され、拡散により矢印に示すようにゲッタリングサイト308に移動する。従って、ゲッタリングは処理温度に依存し、より高温であるほど短時間でゲッタリングが進むことになる。20

## 【0093】

ゲッタリング工程終了後、ゲッタリングサイト308を選択的にエッチングして除去する。エッチングの方法としては、CF<sub>3</sub>によるプラズマを用いないドライエッチング、或いはヒドラジンや、テトラエチルアンモニウムハイドロオキサイド（化学式（CH<sub>3</sub>）<sub>4</sub>N OH）を含む水溶液などアルカリ溶液によるウェットエッチングで行なうことができる。この時バリア層307はエッチングストッパーとして機能する。また、バリア層307はその後フッ酸により除去する（図5（C））。30

## 【0094】

次に、バリア層307除去後の結晶性半導体膜306をパターニングし、島状の半導体膜309、310を形成する（図5（D））。半導体膜309、310の膜厚は25~100nm（好ましくは30~60nm）とする。次に、半導体膜309、310を覆うように第2の絶縁膜311を成膜する。第2の絶縁膜311は、後の第2の電極を形成するために行なうドライエッチングにおいて、その膜厚が10~40nm程度減少するので、その減少分を考慮に入れて膜厚を設定するのが望ましい。具体的には40~150nm（より好ましくは60~120nm）程度の厚さに第2の絶縁膜311を成膜する。

## 【0095】

第2の絶縁膜311には、例えば酸化珪素、窒化珪素または窒化酸化珪素等を用いることができる。本実施の形態では、第2の絶縁膜311を単層の絶縁膜で構成しているが、2層以上の複数の絶縁膜で構成されていても良い。また成膜方法は、プラズマCVD法、スパッタ法などを用いることができる。例えば、プラズマCVD法を用い、酸化珪素で第2の絶縁膜311を成膜する場合、TEOS（Tetraethyl Orthosilicate）とO<sub>2</sub>を混合したガスを用い、反応圧力40Pa、基板温度300~400、高周波（13.56MHz）電力密度0.5~0.8W/cm<sup>2</sup>とし、成膜する。40

## 【0096】

また窒化アルミニウムを第2の絶縁膜311として用いることができる。窒化アルミニウムは熱伝導率が比較的高く、TFTで発生した熱を効率的に発散させることができる。またアルミニウムの含まれない酸化珪素や酸化窒化珪素等を形成した後、窒化アルミニウ50

ムを積層したものを第2の絶縁膜311として用いても良い。

#### 【0097】

次に、第2の絶縁膜311上に導電膜を成膜する(図5(E))。本実施の形態ではTaNからなる第1の導電膜312aを20~100nmの厚さで、Wからなる第2の導電膜312bを100~400nmの厚さで成膜する。具体的に、第1の導電膜312aに用いるTaNは、ターゲットに純度99.99%のTaを用い、チャンバー内の温度を室温、Arの流量を50ml/min、N<sub>2</sub>の流量を10ml/min、チャンバー内の圧力0.6Pa、成膜電力1kWとし、成膜速度約40nm/minで成膜した。また第2の導電膜312bに用いるWは、ターゲットに純度99.99%のWを用い、チャンバー内の温度を230°C、Arの流量を100ml/min、チャンバー内の圧力1.5Pa、成膜電力6kWとし、成膜速度約390nm/minで成膜した。10

#### 【0098】

なお本実施の形態では、2層の導電膜を用いて第2の電極を形成する例について説明するが、導電膜は単層であっても良いし、また3層以上の複数の層で形成されていても良い。また各導電層の材料は本実施の形態に示したものに限定されない。

#### 【0099】

具体的に各導電膜には、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金もしくは化合物で形成することができる。例えば1層目がTaで2層目がW、または1層目がTaNで2層目がAl、1層目がTaNで2層目がCuといった組み合わせも考えられる。また1層目と2層目のいずれか一方にAgPdCu合金を用いても良い。W、AlとSiの合金(Al-Si)、TiNを順次積層した3層構造としてもよい。Wの代わりに窒化タンゲステンを用いてもよいし、AlとSiの合金(Al-Si)に代えてAlとTiの合金膜(Al-Ti)を用いてもよいし、TiNに代えてTiを用いてもよい。ただし、複数の導電膜を成膜する場合、エッティング後に各層の導電膜の、チャネル長方向における幅に差を持たせたいならば、互いにエッティングの選択比のとれる材料を用いる。20

#### 【0100】

なお、導電膜の材料によって、適宜最適なエッティングガスを選択することが重要である。30

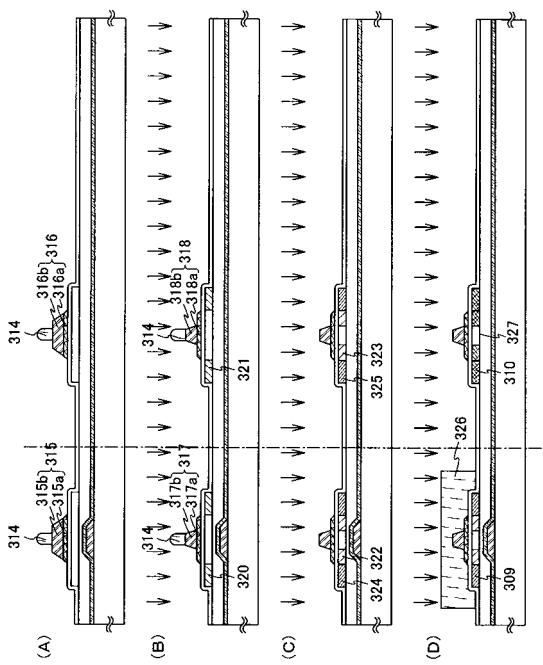

#### 【0101】

次にマスク314を形成し、図6(A)に示すように第1の導電膜312a及び第2の導電膜312bをエッティングする(第1のエッティング処理)。本実施の形態ではICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッティング法を用いて行なった。エッティングガスとしてCl<sub>2</sub>とCF<sub>4</sub>とO<sub>2</sub>を混合したガスを用い、チャンバー内のエッティングガスの圧力を1.0Paとする。そして、コイル型の電極に500W、13.56MHzの高周波(RF)電力を投入し、プラズマを生成する。また基板が載置されたステージ(下部電極)に150W、13.56MHzの高周波(RF)電力を投入し、これにより基板に自己バイアス電圧が印加される。その後、エッティングガスをCl<sub>2</sub>とCF<sub>4</sub>に変更し、トータルの圧力を1.0Paとした。またコイル型の電極に500Wの高周波(13.56MHz)電力を投入し、基板側(試料ステージ)には20Wの高周波(13.56MHz)電力を投入した。40

#### 【0102】

CF<sub>4</sub>とCl<sub>2</sub>をエッティングガスとして用いると、第1の導電膜312aであるTaNと、第2の導電膜312bであるWのエッティングレートがほぼ等しくなり、共に同じ程度エッティングされる。

#### 【0103】

この第1のエッティング処理により、下層315aと上層315bとで構成された第1の形状の導電膜315と、下層316aと上層316bとで構成された第1の形状の導電膜316とが形成される。なおこの第1のエッティング処理において、下層315a、316aと上層315b、316bの側面がややテーパー状になる。また導電膜の残渣を残さな50

いようにエッティングすると、第1の形状の導電膜315、316で覆われていない第2の絶縁膜311の表面が、5~10nm程度またはそれ以上エッティングされることがある。

#### 【0104】

次に図6(B)に示すように、第1のエッティング処理で表面がエッティングされて幅が小さくなったマスク314を用い、第1の形状の導電膜315、316をエッティング(第2のエッティング処理)する。第2のエッティング処理でも第1のエッティング処理と同じくICPエッティング法を用いる。エッティングガスはSF<sub>6</sub>、Cl<sub>2</sub>、O<sub>2</sub>を混合したガスを用い、チャンバー内のエッティングガスの圧力を1.3Paとする。そして、コイル型の電極に700W、13.56MHzの高周波電力を投入し、プラズマを生成する。また基板が載置されたステージ(下部電極)に10W、13.56MHzの高周波電力を投入し、これにより基板に自己バイアス電圧が印加される。

#### 【0105】

SF<sub>6</sub>とCl<sub>2</sub>を混合したガスにO<sub>2</sub>を加えることで、Wのエッティングレートが増加し、また第1の形状の導電膜315、316の下層315b、316bを形成しているTaNのエッティングレートが極端に低下するため、選択比をとることができる。

#### 【0106】

第2のエッティング処理によって、第2の形状の導電膜317(下層を317a、上層を317bとする)と、第2の形状の導電膜318(下層を318a、上層を318bとする)が形成される。上層317b、318bのチャネル長方向における幅は、下層317a、317bの幅よりも短くなっている。第2の形状の導電膜317は、DRAMの第2の電極として機能し、第2の形状の導電膜318は、OLEDに供給する電流を制御するTFTのゲート電極として機能する。なお第2のエッティング処理によって、第2の形状の導電膜317、318で覆われていない第2の絶縁膜311の表面が、5~10nm程度またはそれ以上エッティングされる。

#### 【0107】

次に図6(B)に示すように、第2の形状の導電膜317、318をマスクとして用い、半導体膜309、310にn型の導電性を付与する不純物を添加する(第1のドーピング処理)。ドーピングはイオン注入法で行なう。ドーピングは、ドーズ量を $1 \times 10^{13} \sim 5 \times 10^{14}$ atoms/cm<sup>2</sup>、加速電圧を40~80kVとして行なう。n型を付与する不純物元素は、ドナーとして機能するP、As、Sb等の5族原子やS、Te、Se等の6族原子を用いるが、本実施の形態ではPを用いる。第1のドーピング処理により、自己整合的に第1の不純物領域320、321が形成される。第1の不純物領域320、321には $1 \times 10^{18} \sim 1 \times 10^{20}$ atoms/cm<sup>3</sup>の濃度範囲でn型を付与する不純物元素が添加されている。

#### 【0108】

次に図6(C)に示すように、第2の形状の導電膜317、318の上層317b、318bをマスクとして、第2のドーピング処理を行なう。第2のドーピング処理では、第2の形状の導電膜317、318の下層317a、317aを不純物が通過するように、第1のドーピング処理よりも加速電圧を高くする。そして第2のドーピング処理によりLD領域を形成するので、第1のドーピング処理よりもn型の不純物のドーズ量を下げる。具体的には、加速電圧を60~120kVとし、ドーズ量を $1 \times 10^{13} \sim 1 \times 10^{15}$ atoms/cm<sup>2</sup>とする。

#### 【0109】

続いて、第2のドーピング処理より加速電圧を下げて第3のドーピング処理を行って、図6(C)の状態を得る。第3のドーピング処理は、加速電圧を50~100kVとし、ドーズ量を $1 \times 10^{15} \sim 1 \times 10^{17}$ atoms/cm<sup>2</sup>とする。第2のドーピング処理および第3のドーピング処理により、第2の形状の導電膜317、318の下層317a、317aと重なる第2の不純物領域322、323と、第1の不純物領域320、321に不純物がさらに添加されることで形成される第3の不純物領域324、325とが形成される。第2の不純物領域322、323には $1 \times 10^{18} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>

10

20

30

40

50

の濃度範囲で n 型を付与する不純物元素を添加され、第 3 の不純物領域 324、325 には  $1 \times 10^{19} \sim 5 \times 10^{21}$  atoms/cm<sup>3</sup> の濃度範囲で n 型を付与する不純物元素が添加される。

#### 【0110】

第 2 の不純物領域 322、323 は第 3 の不純物領域 324、325 の内側に形成されており、第 2 の不純物領域 322、323 は LDD 領域、第 3 の不純物領域 324、325 はソース / ドレイン領域として機能する。

#### 【0111】

もちろん、適当な加速電圧にすることで、第 2 のドーピング処理および第 3 のドーピング処理を 1 回のドーピング処理で済まし、低濃度不純物領域および高濃度不純物領域を形成することも可能である。10

#### 【0112】

なお、p チャネル型の TFT が形成される島状の半導体膜 310 には、図 6 (B)、図 6 (C) に示した第 2、第 3 のドーピング処理により n 型の不純物をドーピングする必要はないため、n 型の不純物のドーピングの際に、マスクで覆っておいても良い。また、マスク数削減のために敢えてマスクを設けず、p 型の導電型を付与する不純物の濃度を高くして、島状の半導体膜の極性を p 型に反転させても良い。本実施の形態では、島状の半導体膜の極性を p 型に反転させる場合について説明する。

#### 【0113】

図 6 (D) に示すように、レジストからなるマスク 326 で n チャネル型の島状の半導体膜 309 を覆い、島状の半導体膜 310 に p 型の導電型を付与する不純物をドーピングする（第 4 のドーピング処理）。この第 4 のドーピング処理において、第 2 の形状の導電膜 317、318 の上層 317b、318b がマスクとして機能し、p チャネル型 TFT に用いる島状の半導体膜 310 に p 型を付与する不純物元素が添加された第 4 の不純物領域 327 が形成される。本実施の形態ではジボラン (B<sub>2</sub>H<sub>6</sub>) を用いたイオンドープ法で形成する。第 4 の不純物領域は、実際には第 2 の形状の導電膜 317、318 の下層 317a、318a と重なる領域と、それ以外の領域とで、p 型を付与する不純物元素及び n 型を付与する不純物領域の濃度が異なっている。しかしいずれの領域においても、p 型を付与する不純物元素の濃度が  $2 \times 10^{20} \sim 2 \times 10^{21}$  atoms/cm<sup>3</sup> となるようにドーピング処理することで、p 型が優勢となるため、p チャネル型 TFT のソース領域およびドレン領域として機能するのに何ら問題は生じない。2030

#### 【0114】

以上までの工程でそれぞれの島状の半導体膜に不純物領域が形成される。

#### 【0115】

次に、島状の半導体膜 309、310 と、第 2 の絶縁膜 311 と、第 2 の形状の導電膜 317、318 と覆って、第 1 の層間絶縁膜 330 を成膜する（図 7 (A)）。第 1 の層間絶縁膜 330 は、珪素を含む酸化珪素、窒化珪素、酸化窒化珪素などの絶縁膜を用いることができ、その厚さは 100 ~ 200 nm 程度とする。

#### 【0116】

次に、島状の半導体膜 309、310 に添加された不純物元素を活性化するために、熱処理を行なう。この工程はファーネスアニール炉を用いる熱アニール法、レーザーアニール法、またはラピッドサーマルアニール法 (RTA 法) を用いることができる。例えば熱アニール法で活性化を行なう場合、酸素濃度が 1 ppm 以下、好ましくは 0.1 ppm 以下の窒素雰囲気中で、400 ~ 700 (好ましくは 500 ~ 600) で行なう。さらに、3 ~ 100 % の水素を含む雰囲気中で、300 ~ 450 で 1 ~ 12 時間の熱処理を行い、島状の半導体膜を水素化する工程を行なう。この工程は、熱的に励起された水素によりダンギングボンドを終端する目的で行なわれる。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。また活性化処理は第 1 の層間絶縁膜 330 を成膜する前に行なっても良い。

#### 【0117】

10

20

30

40

50

上記一連の工程によって、DRAMとして用いるnチャネル型TFT331と、OLEDに供給する電流を制御するpチャネル型TFT332を形成することができる。

#### 【0118】

また本実施の形態では、LCD領域として機能する第2の不純物領域322全体が、第2の形状の導電膜317、318の下層317a、318aと重なっているが、本発明はこれに限定されない。例えば、第1のエッチング処理と第2のエッチング処理の間にドーピング処理を行なってソース／ドレイン領域を形成し、なおかつ第2のエッチング処理で下層をチャネル長方向において短くなるようにエッチングすることで、第2の形状の導電膜317、318の下層317a、318aと重なる領域と、それ以外の領域を、両方形成することができる。

10

#### 【0119】

なお上記プラズマエッチングはICPエッチング法に限定されない。例えば、ECR(Electron Cyclotron Resonance:電子サイクロトロン共鳴)エッチング法、RIEエッチング法、ヘリコン波エッチング法、ヘリカル共鳴エッチング法、パルス変調エッチング法やその他のプラズマエッチング法を用いていても良い。

#### 【0120】

本実施の形態では、触媒元素による結晶化方法のみを用いた例を示したが、本発明はこれに限定されない。触媒元素を用いて結晶化を行なった後に、より結晶性を高めるために、パルス発振のレーザ光照射を行なうようにしても良い。また本発明において用いるゲッタリング工程は、本実施の形態に示した方法に限定されない。その他の方法を用いて半導体膜中の触媒元素を低減するようにしても良い。例えば、特開平10-135468号公報または特開平10-135469号公報に記載されているように、触媒元素をリンのゲッタリング作用を用いて除去するようにしても良い。

20

#### 【0121】

次に、第1の層間絶縁膜330を覆うように、第2の層間絶縁膜333と第3の層間絶縁膜を成膜する。本実施の形態では、第2の層間絶縁膜333を有機樹脂、例えば非感光性のアクリルを用いて形成する。第3の層間絶縁膜334は、水分や酸素などのOLEDの劣化を促進させる原因となる物質を、他の絶縁膜と比較して透過させにくい膜を用いる。代表的には、例えばDLC膜、窒化炭素膜、RFスパッタ法で形成された窒化珪素膜等を用いるのが望ましい。

30

#### 【0122】

次いで、第2の絶縁膜311、第1の層間絶縁膜330、第2の層間絶縁膜333及び第3の層間絶縁膜334をエッチングし、コンタクトホールを形成する。そして、島状の半導体膜309、310とコンタクトを形成する配線335～338を形成する。

#### 【0123】

次に、第3の層間絶縁膜334及び配線335～338を覆って透明導電膜を成膜し、パターニングすることで、pチャネル型TFT332の島状の半導体膜310とコンタクトを形成している配線338に接続した、画素電極(陽極)340を形成する(図7(B))。画素電極340に用いる透明導電膜は、ITOのみならず、酸化インジウムに2～20%の酸化亜鉛(ZnO)を混合した透明導電膜を用いても良い。画素電極340は、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体を用いた拭净で研磨しても良い。またCMP法を用いた研磨後に、画素電極340の表面に紫外線照射、酸素プラズマ処理などを行ってもよい。

40

#### 【0124】

そして、隔壁として用いる有機樹脂膜341を、第3の層間絶縁膜334上に形成する。有機樹脂膜341は、画素電極340と重なる領域において開口部を有するようにする。有機樹脂膜341は、次に電界発光層を成膜する前に、吸着した水分や酸素等を除去するために真空雰囲気下で加熱しておく。具体的には、100～200、0.5～1時間程度、真空雰囲気下で加熱処理を行なう。望ましくは $3 \times 10^{-7}$  Torr以下とし、可能であるならば $3 \times 10^{-8}$  Torr以下とするのが最も望ましい。そして、有機樹脂膜3

50

41に真空雰囲気下で加熱処理を施した後に電界発光層を成膜する場合、成膜直前まで真空雰囲気下に保つことで、信頼性をより高めることができる。

#### 【0125】

有機樹脂膜341の開口部における端部は、該端部において後に成膜される電界発光層に穴があかないように、丸みを帯びさせることができ。具体的には、開口部における有機樹脂膜341の断面が描いている曲線の曲率半径が、0.2~2μm程度であることが望ましい。

#### 【0126】

図7(C)では、有機樹脂膜341として、ポジ型の感光性のアクリル樹脂を用いた例を示している。感光性の有機樹脂には、光、電子、イオンなどのエネルギー線が露光された箇所が除去されるポジ型と、露光された箇所が残るネガ型がある。本発明ではネガ型の有機樹脂膜を用いても良い。また感光性のポリイミドを用いて有機樹脂膜341を形成しても良い。

#### 【0127】

ネガ型のアクリルを用いて有機樹脂膜341を形成した場合、開口部における端部が、S字状の断面形状となる。このとき開口部の上端部及び下端部における曲率半径は、0.2~2μmとすることが望ましい。

#### 【0128】

上記構成により、後に形成される電界発光層や陰極のカバーレッジを良好とすることができ、画素電極340と陰極が電界発光層に形成された穴においてショートするのを防ぐことができる。また電界発光層の応力を緩和させることで、発光領域が減少するシュリンクとよばれる不良を低減させることができ、信頼性を高めることができる。

#### 【0129】

次に、画素電極340上に電界発光層342を成膜する。電界発光層342は、単数または複数の層からなり、有機物のみならず無機物の層が含まれていても良い。

#### 【0130】

次に、電界発光層342を覆って、陰極343を成膜する。陰極343は、仕事関数の小さい導電膜であれば公知の他の材料を用いることができる。例えば、Ca、Al、CaF、MgAg、AlLi等が望ましい。

#### 【0131】

画素電極340、電界発光層342、陰極343は、有機樹脂膜341の開口部において重なり合っており、該重なり合っている部分がOLED344に相当する。

#### 【0132】

次に、有機樹脂膜341及び陰極343上に、保護膜345が成膜されている。保護膜345は第3の層間絶縁膜334と同様に、水分や酸素などのOLEDの劣化を促進させる原因となる物質を、他の絶縁膜と比較して透過させにくい膜を用いる。代表的には、例えばDLC膜、窒化炭素膜、RFスパッタ法で形成された窒化珪素膜等を用いるのが望ましい。また上述した水分や酸素などの物質を透過させにくい膜と、該膜に比べて水分や酸素などの物質を透過させやすい膜とを積層させて、保護膜として用いることも可能である。

#### 【0133】

なお図7(C)では、OLEDから発せられる光が基板301側に照射される構成を示しているが、光が基板とは反対側に向かうような構造のOLEDとしても良い。

#### 【0134】

なお、実際には図7(C)まで完成したら、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のカバー材でパッケージング(封入)することが好ましい。その際、カバー材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとOLEDの信頼性が向上する。

#### 【0135】

10

20

30

40

50

上述した作製方法を用いることで、DRAMの記憶素子として用いられるnチャネル型TFT331と、画素部に形成されるpチャネル型TFTとを同一基板上に形成することができる。

#### 【0136】

なお、DRAMを含む集積回路と、画素部とを基板上に形成した後、該集積回路と画素部を基板から剥離し、別の基板に転写するようにしても良い。転写は、基板と集積回路及び画素部の間に金属酸化膜を設け、該金属酸化膜を結晶化により脆弱化して集積回路及び画素部を剥離し、転写する方法、基板と集積回路及び画素部の間に水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッチングにより該非晶質珪素膜を除去することで基板と集積回路及び画素部とを剥離し、転写する方法、集積回路及び画素部が形成された基板を機械的に削除または溶液やガスによるエッチングで除去することで集積回路及び画素部を基板から切り離し、転写する方法等、様々な方法を用いることができる。いずれの方法を用いる場合でも、転写は、画素部において表示素子の形成が完了する前に行なうのが良い。例えば液晶表示装置の場合は対向電極を貼り合わせて液晶を注入する前、発光装置の場合は電界発光層を成膜する前に行なうのが望ましい。

#### 【0137】

なお本発明の半導体表示装置は、必ずしも本実施の形態に示す発光装置に限定されない。上述した発光装置は本発明の一実施形態について具体的に説明しただけであり、本発明は、上述した実施の形態に限定されるものではなく、発明の技術的思想に基づく各種の変形が可能である。

#### 【0138】

上述した通り本発明では、薄膜トランジスタにデータを記憶することができるので、キヤパシタを別途設ける必要がなく、メモリセルの面積を抑えることができる。よって、コストを抑えつつ、DRAM混載の集積回路の高集積化、大容量化を実現することができる。そして集積回路の高集積化、大容量化の実現により、フラットパネルディスプレイの画素部と同じ基板上に一体形成することが可能な、集積回路の範囲を広げることができ、システムオンパネルの高機能化を実現することができる。

#### 【実施例1】

#### 【0139】

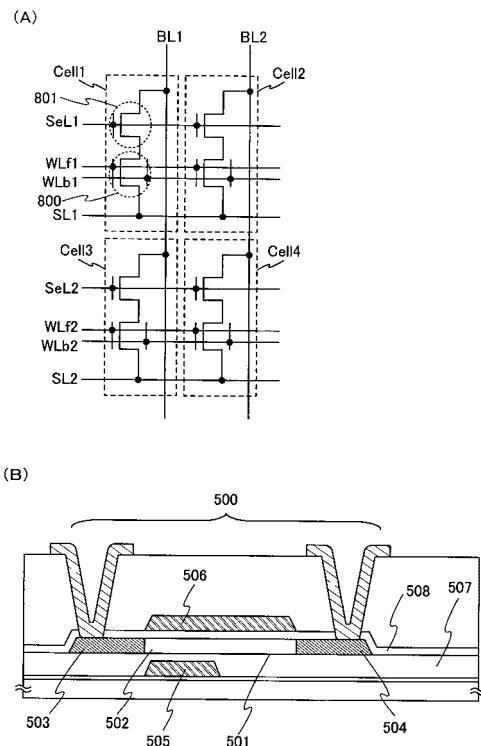

次に、各メモリセルに記憶素子として用いるTFTに加えて、スイッチング素子として用いるTFTを設ける、DRAMの一例について説明する。

#### 【0140】

本実施例のDRAMが有するセルアレイの回路図を、図8(A)に一例として示す。図8(A)は、4つのメモリセル(Cell11, Cell12, Cell13, Cell14)を有するセルアレイの回路図であり、各メモリセルには記憶素子として機能するTFT800と、スイッチング素子として機能するTFT801が設けられている。なお図8(A)ではメモリセルが4つ設けられたセルアレイを示しているが、無論メモリセルの数はこれに限定されない。

#### 【0141】

各メモリセルのTFT800には、2つのワード線WLb、WLfによって電位Vbg、Vfgが、ソース線SLによって電位Vsが与えられている。またビット線BLからの電位Vdの供給が、TFT801によって制御されている。TFT801のスイッチングは、選択線SELからそのゲート電極に供給される電位によって制御される。なお各配線のレイアウトは、図8(A)に示した構成に限定されない。そしてこれらの配線に加えて、さらに別の配線が各メモリセルに設けられていても良い。

#### 【0142】

TFT801はスイッチング素子として機能するので、導電型に特に限定はなく、n型であってもp型であってもどちらでも良い。そして、TFT801は、書き込み、読み出し、ページの際にオンに、保持の際にはオフになるように動作させる。

#### 【0143】

本実施例のように、スイッチング素子として用いるTFTを設けることで、メモリセル

10

20

20

30

40

50

の選択性が向上する。具体的には、メモリセル(Cell1)に書き込みを行なうためにBL1に5V印加される場合の同列のメモリセル(Cell3)を考える。この場合、スイッチング素子がないと、メモリセル(Cell3)を構成するTFTのソースドレイン間には電位差が生じ、メモリセル(Cell3)の状態に影響を与えるおそれがある(書き込み時のストレス)。一方、スイッチング素子がオフの状態では、そのような電位差が生じないため、メモリセル(Cell3)へはストレスがかからない。その結果、ストレスによる誤動作の低減や、リフレッシュ間隔の向上が可能となる。

#### 【0144】

また、スイッチング素子を有さない場合には、ソース線を一行ごとに独立に制御していたのに対し、スイッチング素子を有することで非選択メモリセルのソースドレイン間の余計な電位差を除去することが可能となるため、全てのソース線電位を共通にすることが可能となる。その結果、駆動回路を単純にしたり、ソース線の面積を削減したりすることが可能となる。10

#### 【0145】

なお、TFT800において効率よくインパクトイオン化を起こすためには、或いは読み出し時においてTFT800の電流値の差をより効率よく読み出すためには、選択時のTFT801のゲート電極の電位VgsをTFT800のゲート電極の電位Vgsより大きめにすることが好ましい。

#### 【0146】

また、TFT800とTFT801が共にnチャネル型であるならば、敢えて選択線SELとワード線WLfとを共通の配線にし、電源数を抑えるようにしても良い。さらにこの場合、TFT800とTFT801の活性層を連続させることで、1つのTFTとすることができる。図8(B)に、TFT800とTFT801の活性層を互いに連続させることで得られる、TFT500の断面図を示す。20

#### 【0147】

図8(B)において、501は活性層であり、チャネル形成領域502、ソース領域503、ドレイン領域504を有する。また505は第1の電極、506は第2の電極、507は第1の絶縁膜、508は第2の絶縁膜に相当する。第1の電極505は活性層501を間に挟んで第2の電極506と重なっている。そして、第1の電極505は第1の絶縁膜507を間に挟んでチャネル形成領域502と重なっている。また第2の電極506は、第2の絶縁膜508を間に挟んでチャネル形成領域502と重なっている。30

#### 【0148】

そして図8(B)では、第1の電極505はチャネル形成領域502の一部とのみ重なっており、チャネル形成領域502のドレイン領域504には、第1の電極505とは重ならず、第2の電極506と重なる領域が存在する。このようにワード線WLfと選択線SELを共通化し、また活性層を連続させる事で、TFTを2つ設ける場合よりも、メモリセルの面積を抑えることができ、なおかつTFTを2つ設けた場合と同様に、電荷の保持を確実に行なうことができる。

#### 【実施例2】

#### 【0149】

本実施例では、本発明の集積回路に積載されたDRAMのメモリセルの構成について説明する。40

#### 【0150】

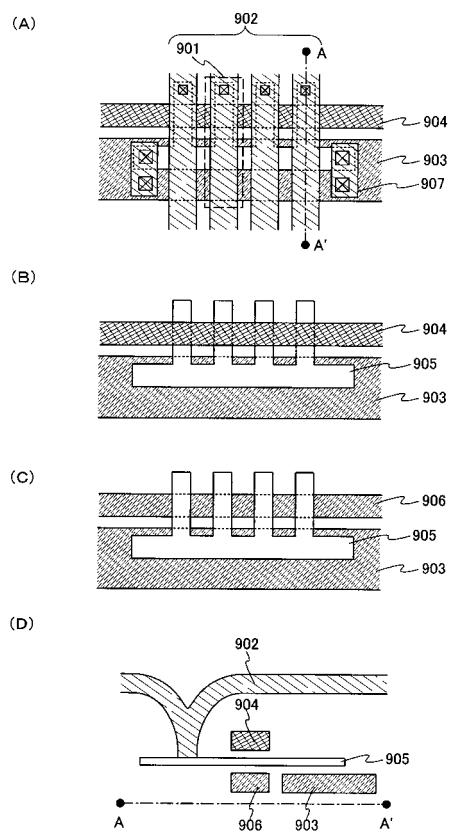

図9(A)に、本実施例のメモリセルの上面図を示す。図9(A)に示すメモリセルには、記憶素子として機能するTFT901が設けられている。そして、902はビット線BL、903はソース線SL、904はワード線WLfに相当する。図9(A)に示すように、本実施例では、ソース線SL903がワード線WLb906と同一の導電膜をパターニングすることで得られる。

#### 【0151】

図9(B)は、図9(A)に示した上面図のうち、最も最上層に設けられたビット線B50

L 902 が形成される前の、メモリセルの上面図に相当する。905 は TFT901 が有する活性層に相当する。ワード線 WL f 904 の一部は第2の絶縁膜（図示せず）を間に挟んで活性層 905 と重なっており、第2の電極として機能している。本実施例でワード線 WL f 904 は、活性層 905 と、ビット線 BL 902 との間の層に設けられている。

### 【0152】

図 9 (C) は、図 9 (B) に示した上面図のうち、ワード線 WL f 904 が形成される前の、メモリセルの上面図に相当する。ワード線 WL b 906 の一部は第1の絶縁膜（図示せず）を間に挟んで活性層 905 と重なっており、第1の電極として機能している。本実施例でソース線 SL 903 及びワード線 WL b 906 は、活性層 905 よりも下の層（基板側）に設けられている。

10

### 【0153】

図 9 (D) に、図 9 (A) の A - A' における断面図を示す。図 9 (D) に示すようにワード線 WL f 904 とワード線 WL b 906 は、活性層 905 を間に挟んで重なっている。なお本実施例ではソース線 SL 903 をワード線 WL b 906 と同じ導電膜から形成しているが、ソース線 SL 903 をビット線 BL 902 より上部の導電膜で形成しても良い。

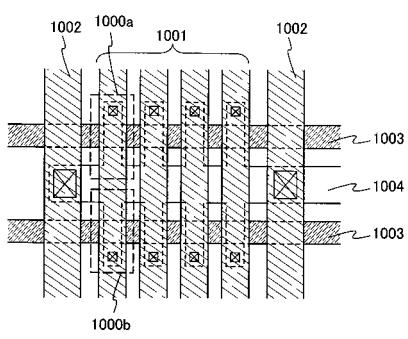

### 【0154】

なお、ソース線の電位を固定にする場合、異なるワード線を有する隣り合ったメモリセルどうしで、共通のソース線を有していても良い。図 11 に、図 9 とは異なる本発明のメモリセルの上面図を示す。図 11 にはメモリセル 1000a、1000b がレイアウトされており、1001 はビット線 BL、1002 はソース線 SL、1003 はワード線 WL f に相当する。図 11 ではメモリセル 1000a、1000b で活性層 1004 とビット線 BL 1001 を共有している。なお図 11 に示す上面図では図示されないが、活性層 1004 の下層においてワード線 WL f 1003 と重なる領域に、ワード線 WL b が設けられている。図 11 に示すように活性層またはソース線を隣り合うメモリセルで共有することによって、レイアウトの面積をより縮小することができる。

20

### 【実施例 3】

### 【0155】

本実施例では、本発明の集積回路の一つであるマイクロプロセッサの構成について説明する。

30

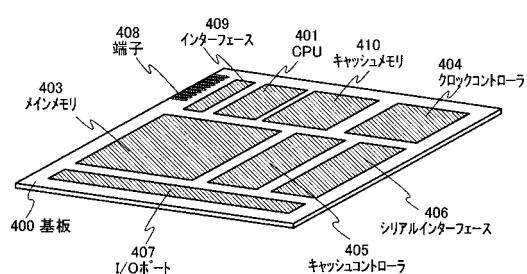

### 【0156】

図 10 に、本実施例のマイクロプロセッサの斜視図を示す。図 10 に示すマイクロプロセッサは、基板 400 上に、CPU401、メインメモリ 403、クロックコントローラ 404、キャッシュコントローラ 405、シリアルインターフェース 406、I/O ポート 407、端子 408、インターフェース 409、キャッシュメモリ 410 等が形成されている。勿論、図 10 に示すマイクロプロセッサは、その構成を簡略化して示した一例にすぎず、実際のマイクロプロセッサはその用途によって多種多様な構成を有している。

### 【0157】

CPU401 をより高速に動作させるには、それに見合う程度の高速なメモリを必要とする。しかし、CPU401 の動作スピードにあったアクセスタイムをもつ高速の大容量メモリを使用した場合、一般的にコストが高くなってしまう。そこで大容量のメインメモリ 403 の他に、メインメモリ 403 よりも小容量であるが高速のメモリであるキャッシュメモリ 410 を、CPU401 とメインメモリ 403 の間に介在させる。CPU401 がキャッシュメモリ 410 にアクセスすることにより、メインメモリ 403 のスピードによらず、高速で動作することが可能となる。

40

### 【0158】

本発明の集積回路では、メインメモリ 403 に低コスト化、大容量化に優れるDRAM を用い、キャッシュメモリ 410 には高速な動作が可能なSRAM を用いる。

### 【0159】

なおメインメモリ 403 には、CPU401 で実行されるプログラムが格納されている

50

。そして例えば実行初期において、メインメモリ 403 に格納されているプログラムは、キャッシュメモリ 410 にダウンロードされる。ダウンロードされるプログラムは、メインメモリ 403 に格納されているものに限定されず、他の外付のメモリからダウンロードすることもできる。キャッシュメモリ 410 は、CPU 401 で実行されるプログラムを格納するだけでなく、ワーク領域としても機能し、CPU 401 の計算結果等を一時的に格納する。

#### 【0160】

なお CPU は単数に限られず、複数設けていても良い。CPU を複数設け、並列処理を行なうことで、動作速度の向上を図ることができる。その場合、CPU 間の処理速度がまちまちだと処理全体で見たときに不都合が起きる場合があるので、スレーブとなる各 CPU の処理速度のバランスを、マスターとなる CPU でとるようにしても良い。10

#### 【0161】

なお本実施例では集積回路としてマイクロプロセッサを例示したが、本発明の集積回路に用いられるDRAM は、マイクロプロセッサのメインメモリにその用途が限られるわけではない。例えば表示装置の駆動回路に用いられるビデオラムや、画像処理回路に必要となる大容量メモリとしての用途も好ましい。その他、様々なシステムLSIにおいても、大容量もしくは小型用途のメモリとして用いることができる。

#### 【実施例4】

#### 【0162】

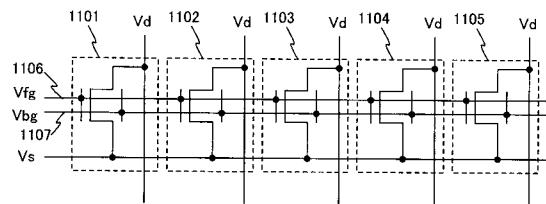

本実施例では、共通の配線から複数のメモリセルに電位  $V_{bg}$  が与えられる場合の、具体的な書き込みの手順について、説明する。20

#### 【0163】

図 12 に、本実施例のセルアレイの一部を、回路図で示す。図 12 に示す全てのメモリセル 1101 ~ 1105 には、共通の配線 1106 から第 1 のゲート電極の電位  $V_{bg}$  が与えられる。またメモリセル 1101 ~ 1105 には、共通の配線 1107 から第 2 のゲート電極の電位  $V_{fg}$  が与えられる。そして図 12 では、メモリセル 1101 ~ 1105 を用いて 3 値のデータを書き込むものとする。

#### 【0164】

具体的にメモリセル 1101 ~ 1105 に書き込むデータは、順に "0"、"1"、"0"、"2"、"1" とする。そして "0" のデータは、ドレイン電圧をインパクトイオン化の閾値電圧よりも低い場合に、"1" と "2" のデータは、インパクトイオン化により正孔を蓄積する場合に対応し、"2" のデータの電荷の蓄積量は、"1" のデータの電荷の蓄積量よりも高いものとする。30

#### 【0165】

まず 1 回目の書き込み時には、データ "0" に対応するメモリセル 1101、1103において、ドレイン電圧をインパクトイオン化の閾値電圧よりも低くする。またデータ "1" に対応するメモリセル 1102、1104、1105において、ドレイン電圧をインパクトイオン化の閾値電圧よりも高くする。上記動作により、メモリセル 1101、1103、1104 では電荷の蓄積が行なわれず、メモリセル 1102、1105 ではデータ "1" に見合った量の正孔が蓄積される。具体的に TFT に与えられる電位  $V_d$  は、各メモリセル 1101 ~ 1105 においてそれぞれ 2V、5V、2V、2V、5V とする。そして全てのメモリセル 1101 ~ 1105 において、TFT に与えられる電位  $V_s$  を 0V、電位  $V_{fg}$  を 3V、電位  $V_{bg}$  を -4V とする。40

#### 【0166】

次に 2 回目の書き込み時には、データ "0" と "1" に対応するメモリセル 1101、1102、1103、1105において、ドレイン電圧をインパクトイオン化の閾値電圧よりも低くする。そして、データ "2" に対応するメモリセル 1105において、ドレイン電圧をインパクトイオン化の閾値電圧よりも高くする。このとき、配線 1107 に与えられる電位  $V_{bg}$  は、1 回目の書き込み時よりも低くし、メモリセル 1105 に蓄積される電荷の量が 1 回目の書き込み時よりも増えるようにする。上記動作により、メモリセル50

1101、1103にはデータ”0”が、またメモリセル1102、1105にはデータ”1”が保持されたまま、メモリセル1104にはデータ”2”に見合った量の正孔が蓄積される。具体的にTFTに与えられる電位Vdは、各メモリセル1101～1105においてそれぞれ2V、2V、2V、5V、2Vとする。そして全てのメモリセル1101～1105において、TFTに与えられる電位Vsを0V、電位Vfgを3V、電位Vbgを-6Vとする。

#### 【0167】

なお本発明は、必ずしも正孔の蓄積量の少ないメモリセルから順に書き込みを行なう必要はない。

#### 【0168】

また、本実施例では3値のデータを記憶するためのDRAMの場合について説明したが、データの値をn(nは3以上の自然数)と一般化すると、書き込みの回数は(n-1)回と表される。

#### 【実施例5】

#### 【0169】

本実施例では、メモリセルからデータを読み出すための手段について説明する。本実施例では3値のデータを読み出す場合について説明するが、本実施例ではこれに限定されず、4値以上のデータの読み出しにも対応させることができる。

#### 【0170】

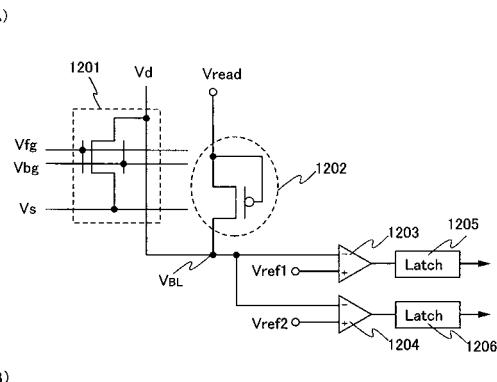

図13(A)に、メモリセルに設けられたTFT1201と、該TFT1201からデータを読み出すための、トランジスタ1202及び2つのオペアンプ1203、1204とを示す。トランジスタ1202はゲート電極とソース領域が電気的に接続(所謂ダイオード接続)されており、抵抗として機能する。なお本実施例ではダイオード接続されたトランジスタを抵抗として用いたが、本実施例はこれに限定されず、抵抗として機能する素子であれば代替が可能である。また本実施例では、データの読み出しに用いるオペアンプは2つであるが、オペアンプの数はこれに限定されず、n値(nは3以上の自然数)のデータの場合は(n-1)のオペアンプを用いる。

#### 【0171】

TFT1201のドレイン電流の大きさは、そのチャネル形成領域に蓄積される正孔の量に左右される。具体的には正孔の蓄積量が多いほど大きいドレイン電流が得られ、逆に正孔の蓄積量が少ないほど小さいドレイン電流が得られる。すなわち、TFT1201のソース領域とドレイン領域間の抵抗は、正孔の蓄積量が多いほど低くなり、逆に少ないほど高くなると考えられる。そこで本実施例では、TFT1201のドレイン領域と、抵抗として機能するトランジスタ1202とを直列に接続し、該接続のノードにおける電位VBLの高さで、間接的にドレイン電流の高さを測定する。

#### 【0172】

具体的には、TFT1201のドレイン領域と、抵抗として機能するトランジスタ1202のドレイン領域とを接続し、そのノードを2つの各オペアンプ1203、1204の反転入力端子に接続する。またトランジスタ1202のソース領域には一定の電位Vreadを、またオペアンプ1203の非反転入力端子には電位Vref1、オペアンプ1204の非反転入力端子には電位Vref2を与えておく。各電位の関係は、Vread > Vref2 > Vref1とする。従って、ノードの電位VBLの高さが電位Vref1に対して高いか低いか、また電位Vref2に対して高いか低いかによって、各オペアンプ1203、1204の出力端子の電位が異なる。各オペアンプ1203、1204の出力端子の電位は、ラッチ1205、1206において記憶される。

#### 【0173】

図13(B)に、正孔の蓄積量に対するメモリセルの分布と、各データ”0”、“1”、“2”とノードの電位VBLの相関関係を示す。各データが記憶されているメモリセルの正孔蓄積量は、ある程度幅を有している。そのため、同じデータが記憶されているメモリセルであっても、対応するノードの電位VBLの高さにも幅が生じる。基準となる電位Vr

10

20

30

40

50

$e_{f1}$ 、 $V_{ref2}$ の高さは、各データの値を正確に読み取るために、ノードの電位 $V_{BL}$ が分布している幅を考慮して定める。

【0174】

なお本実施例では、抵抗分割を利用して正孔の蓄積量を相対的に把握することで、データを読み出しているが、データの読み出し方は本実施例に示した方法に限定されない。

【実施例6】

【0175】

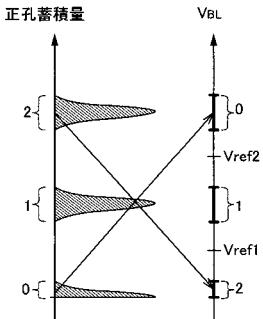

本発明の集積回路または半導体表示装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パソコン、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。10

【0176】

本発明の半導体表示装置を用いることで、画素部周辺の額縁領域の面積を抑えることができ、電子機器の小型化が図れる。また、本発明の集積回路を用いることで、集積回路の有するDRAMの大容量化により、電子機器の高機能化を実現することができる。これら電子機器の具体例を図14に示す。

【0177】

図14(A)は表示装置であり、筐体2001、表示部2002、スピーカー部2003等を含む。本発明の半導体表示装置は、表示部2002に用いることができる。また本発明の集積回路は、その他の信号処理用の回路として用いることができる。なお、表示装置には、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。20

【0178】

図14(B)はノート型パソコンコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、マウス2205等を含む。本発明の半導体表示装置は、表示部2203に用いることができる。また本発明の集積回路は、その他の信号処理用の回路として用いることができる。30

【0179】

図14(C)は記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）であり、本体2401、筐体2402、表示部2403、記録媒体(DVD等)読み込み部2404、操作キー2405、スピーカー部2406等を含む。記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明の半導体表示装置は、表示部2403に用いることができる。また本発明の集積回路は、その他の信号処理用の回路として用いることができる。

【0180】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は、実施例1～5に示したいずれの構成を用いても良い。40

【図面の簡単な説明】

【0181】

【図1】本発明において記憶素子として用いられるTFTの断面図。

【図2】記憶素子として用いられるTFTの動作を説明するための回路図。

【図3】記憶素子として用いられるTFTの動作を説明するための回路図。

【図4】DRAMのセルアレイの回路図と、タイミングチャート。

【図5】本発明の半導体表示装置の作製方法を示す図。

【図6】本発明の半導体表示装置の作製方法を示す図。

【図7】本発明の半導体表示装置の作製方法を示す図。

10

20

30

40

50

【図8】DRAMのセルアレイの回路図と、タイミングチャート。

【図9】DRAMのメモリセルの上面図及び断面図。

【図10】本発明の集積回路の1つであるマイクロプロセッサの斜視図。

【図11】DRAMのメモリセルの上面図。

【図12】DRAMのセルアレイの一部を示す回路図。

【図13】メモリセルと、メモリセルからデータを読み出すための手段の一例を示す図。

【図14】本発明の半導体表示装置または集積回路を用いた電子機器の一実施例を示す図。

### 【符号の説明】

【0182】

10

100 TFT

101 第1のゲート電極

102 第2のゲート電極

103 活性層

104 第1の絶縁膜

105 第2の絶縁膜

106 ソース領域

107 ドレイン領域

108 チャネル形成領域

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

(B)

【図14】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

H 01 L 29/786

F I

G 11 C 11/34 381A

H 01 L 29/78 617N

テーマコード(参考)

F ターム(参考) 5F110 AA04 BB02 BB04 BB05 BB06 CC02 DD01 DD02 DD03 DD05

EE01 EE02 EE03 EE04 EE06 EE14 EE15 EE23 EE30 EE44

FF01 FF02 FF03 FF04 FF09 FF28 FF30 GG01 GG02 GG25

GG42 GG43 GG45 HJ01 HJ04 HJ13 HJ23 HM15 NN03 NN04

NN22 NN23 NN24 NN27 NN71 NN72 PP01 PP02 PP03 PP10

PP29 PP34 PP35 QQ04 QQ09 QQ19 QQ21 QQ28

5M024 AA70 BB02 CC10 CC20 PP02 PP03 PP04 PP05 PP10