(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3964501号

(P3964501)

(45) 発行日 平成19年8月22日(2007.8.22)

(24) 登録日 平成19年6月1日(2007.6.1)

(51) Int.C1.

F 1

|      |        |           |      |        |     |

|------|--------|-----------|------|--------|-----|

| GO2F | 1/1339 | (2006.01) | GO2F | 1/1339 | 500 |

| GO2F | 1/1341 | (2006.01) | GO2F | 1/1339 | 505 |

| GO2F | 1/1345 | (2006.01) | GO2F | 1/1341 |     |

| GO2F | 1/1347 | (2006.01) | GO2F | 1/1345 |     |

GO2F 1/1347 (2006.01)

請求項の数 3 (全 16 頁)

(21) 出願番号

特願平9-207462

(22) 出願日

平成9年8月1日(1997.8.1)

(65) 公開番号

特開平11-52401

(43) 公開日

平成11年2月26日(1999.2.26)

審査請求日

平成16年7月12日(2004.7.12)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(72) 発明者 関口 金孝

埼玉県所沢市大字下富字武野840番地

シチズン時計株式会社技術研究所内

審査官 右田 昌士

最終頁に続く

(54) 【発明の名称】 液晶表示装置および該液晶表示装置を有する腕時計装置

## (57) 【特許請求の範囲】

## 【請求項1】

3枚またはそれ以上の基板を積層して基板間に液晶を封入した液晶表示装置であつて、両外側の2枚の基板は液晶層側の面のみ電極を設け、中間の基板は両面に電極を設け、

隣接する基板同士をシール部で貼り合わせ、さらに中間に1枚またはそれ以上の他の基板が介在する基板同士をもシール部で貼り合わせ、

中間に他の基板が介在する基板群の両外側の基板同士を貼り合わせるシール部は、中間に介在する基板を隣接する基板と貼り合わせるシール部の外側、または中間に介在する基板を中間にさらに基板を介在させて別の基板と貼り合わせるシール部の外側に位置し、

前記シール部はいずれも導電粒を含有する構成により、各電極の接続部を一枚の基板上に集中して設ける液晶表示装置において、

異なる液晶層に面する複数の基板面に、同じ方向に同じピッチでストライプ状にそれぞれ走査電極群を設け、異なる基板面上の対応する走査電極同士を、各電極の接続部を集中させて設ける基板上で共通接続することを特徴とする液晶表示装置。

## 【請求項2】

外装と風防ガラスと液晶表示装置を駆動する回路とを有し、さらに、請求項1に記載の液晶表示装置を表示部とすることを特徴とする腕時計装置。

## 【請求項3】

外装と風防ガラスと液晶表示装置を駆動する回路と時針と分針を少なくとも有し、さらに、請求項1に記載の液晶表示装置を表示部とし、

10

20

前記液晶表示装置は時計の風防側に設け、各電極の接続部を集中して設ける基板上にて、駆動回路からの信号を各電極へ印加する接続を行うことを特徴とする腕時計装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、複数の液晶層と各液晶層を挟む各電極を有する液晶表示装置により、複雑な表示あるいは、明るいカラー表示を行う液晶表示装置の外部回路との接続を第1の基板上に設ける各電極と重なり合う接続電極とシール部に含む導電粒を介して、各電極を第1の基板上の接続電極と接続し、第1の基板上の電極と外部回路との接続により、多層構造の液晶表示装置の駆動を簡便にするものである。さらに、前記液晶表示装置の簡便な実装構造と第1の基板上にのみ実装する特徴を利用し、腕時計装置の構造に関するものである。

10

##### 【0002】

##### 【従来の技術】

近年、各種情報端末用、計測器、パーソナルコンピュータ用のディスプレイに数多くのマトリクス型液晶表示パネルが利用されている。この液晶表示パネルを駆動するために外部信号を供給する手段として液晶表示パネルの外部に設ける駆動用集積回路（I C）から信号を印加する手法がある。外部回路と液晶表示パネルの接続方法として色々な方法が利用されている。特に、大容量のマトリクス型液晶表示パネルの場合には、駆動用集積回路を直接液晶表示パネル上に実装する手法が集積度、コスト等の優位性のために開発されてきている。

20

##### 【0003】

上記の駆動用集積回路を直接液晶表示パネル上に実装する手法は、COG（Chip on Glass）実装法と呼ばれ、広く利用されている。このCOG実装法以外の実装法として、例えば、導電性薄膜と絶縁性樹脂を利用し形成する薄膜フィルム上に集積回路を実装し、薄膜フィルム上の導電性薄膜と液晶表示パネルの電極を異方性導電性フィルム（ACF）で接続するTAB（Tape Automated Bonding）実装法、あるいは、一度プリント基板上に集積回路を実装し、さらに導電性薄膜と絶縁性樹脂を利用し形成する薄膜フィルムをプリント基板と液晶表示パネルの接続に利用するCOB（Chip on Board）実装法等がある。COG実装法は、他の実装法に比較し、高密度、小面積、低コスト等の優位性がある。

30

##### 【0004】

しかし、第1の基板と第2の基板上に実装する場合には、第1の基板と第2の基板の電極面が相対向するため、実装面が反対となるため、第1の基板上に第2の基板上の電極と対向し重なり合う接続電極部分を設け、第2の基板上の電極と前記第1の基板上の接続電極とを、シール部に含む導電粒により接続する方法が提案されている。いわゆる異方性導電性シール（ACS）法である。

##### 【0005】

次に従来例を図面に基づいて説明する。図11は、液晶表示装置の全体を示す平面図であり、図12は、図11に示すA-A線における断面図である。以下図11と図12とを交互に用いて従来例を説明する。

40

##### 【0006】

第1の基板1上には、L列のストライプ状の第1の電極4（端部が第1の接続部4である）とM行の第2の接続部6とを有する。第2の基板2上には、M行の第2の電極5を有する。第1の基板1と第2の基板2の液晶層25に接する側には液晶層25を配列するための配向膜（図示せず）を有する。また、図11に示すように、第1の電極4と第2の電極5が重なり合う部分が液晶表示装置の表示画素部15となり、表示画素部15の周囲には、液晶層25を第1の基板1と第2の基板2により気密性を保つために、シール材からなるシール部12と封口部14とを有する。

##### 【0007】

また、シール部12には、接着剤と導電粒18とを有する。導電粒18は、スチレン製

50

ビーズにクロム( Cr )膜とニッケル( Ni )膜を被服したもの、あるいは、スチレン製ビーズにクロム( Cr )膜と金( Au )膜を被服したものを用いる。さらに、導電粒 18 の分散性を向上するために、導電粒 18 と非導電性粒子を混合する方法もある。図 12 に示すように、第 2 の基板 2 上の第 2 の電極 5 は、第 1 の基板 1 上の第 2 の接続部 6 に対向する部分で、かつ、シール部 12 の領域で止まり、シール部 12 の導電粒 18 により、第 1 の基板 1 上の第 2 の接続部 6 に接続している。そのため、図 11 に示すように、第 1 の基板 1 は、シール部 12 の外側に、L 列の第 1 の電極 4 と M 行の第 2 の接続部 6 を有する。これに対し、第 2 の基板 2 は、ほぼシール部 12 の外周までの大ささである。

#### 【 0 0 0 8 】

以上により、第 2 の基板 2 上の第 2 の電極 5 は、シール部 12 の導電粒 18 と第 1 の基板 1 上の第 2 の接続部 6 により、第 1 の基板 1 上に接続部を転換することが可能となる。 10

#### 【 0 0 0 9 】

#### 【発明が解決しようとする課題】

上記に示す第 1 の基板上の第 1 の接続部に第 2 の基板上の第 2 の電極を導電粒を利用して接続する方法は、有効であり、さらに、高密度 COG 法と組み合わせることにより、第 2 の電極のパターン形成精度を向上させることなく、第 1 の接続部を利用することにより、高密度の実装を可能とする。

#### 【 0 0 1 0 】

しかし、複数の液晶層を利用し、さらに第 1 の基板と第 2 の基板と第 3 の基板あるいは、さらに多くの基板を利用する場合に、各基板上の電極を第 1 の基板上の接続部に導電粒を利用し接続する方法に関して示唆するところがなく改善が必要となる。 20

#### 【 0 0 1 1 】

さらに、複数の液晶層と複数の基板を利用する場合には、各基板が重なり合い、液晶層に電圧を印加するための外部回路との接続が非常に複雑となり、簡易的な接続法が必要となる。

#### 【 0 0 1 2 】

特に、外部回路との接続に必要な容積は、腕時計装置のように、非常に容積が小さい場合には特に重要となり、従来の実装方式では、十分な対応ができなかった。さらに、時計の風防側に液晶表示装置を配置する場合には、時針あるいは分針、文字板を遮蔽する面積が大きくなることは、時計のデザインの制約、あるいは、腕時計装置の時刻の視認性を著しく悪くする。 30

#### 【 0 0 1 3 】

本発明は、かかる点に着目しその目的とするところは、複数の電極間に応する導電粒とシール材を利用し、各電極と導電粒と第 1 の基板上の接続部の接続を行い、第 1 の基板上にて外部回路との接続を可能とする構造を提供することである。

#### 【 0 0 1 4 】

#### 【課題を解決するための手段】

上記の目的を解決するために本発明は、以下の構造を採用する。

#### 【 0 0 1 5 】

本発明の液晶表示装置は、第 1 の基板の液晶層側の面に設ける電極と、これに対向する第 2 の基板の面に設ける電極と、前記第 2 の基板上で、かつ第 1 の基板に対向して電極を設ける面と反対側の面に電極を設け、さらに、これに対向して第 3 の基板上に設ける電極とを少なくとも有し、第 1 の基板の電極とこれに対向する第 2 の基板の電極とを第 1 の液晶層を介して第 1 のシール部にて貼り合わせ、第 2 の基板の反対側の面の電極と第 3 の基板の電極とを、第 2 の液晶層を介して第 2 のシール部にて貼り合わせる構成の、複数の液晶層と複数の基板とシール材とを有する液晶表示装置であって、前記シール部には、導電粒を含有し、さらに、導電粒の粒径が複数種類であることを特徴とする。 40

#### 【 0 0 1 6 】

本発明の液晶表示装置は、第 1 の基板の液晶層側の面に設ける電極と、これに対向する第 2 の基板の面に設ける電極と、前記第 2 の基板上で、かつ第 1 の基板に対向して電極を 50

設ける面と反対側の面に電極を設け、さらに、これに対向して第3の基板上に設ける電極とを少なくとも有し、第1の基板の電極とこれに対向する第2の基板の電極とを第1の液晶層を介して第1のシール部にて貼り合わせ、第2の基板の反対側の面の電極と第3の基板の電極とを、第2の液晶層を介して第2のシール部にて貼り合わせる構成の、複数の液晶層と複数の基板とシール部とを有する液晶表示装置であつて、前記第1の基板と第2の基板間の第1のシール部には、第1の導電粒を含有し、第2の基板と第3の基板間の第2のシール部には、第2の導電粒を含有し、さらに、第1の基板と第3の基板間には第3のシール部を有し、第3のシール部には第3の導電粒を含有し、少なくとも第1の導電粒と第3の導電粒とは異なる粒径であることを特徴とする。

【0017】

10

本発明の液晶表示装置は、第1の基板の液晶層側の面に設ける電極と、これに対向する第2の基板の面に設ける電極と、前記第2の基板上で、かつ第1の基板に対向して電極を設ける面と反対側の面に電極を設け、さらに、第2の基板と同様に両面に電極を有するN基板まで有し、N+1基板上には、N基板に面する基板上のみ2×N番目の電極を設け、第1の基板の電極とこれに対向する第2の基板の電極とを第1の液晶層を介して第1のシール部にて貼り合わせ、隣接するN-1基板とN基板との基板間には、第(N-1)の液晶層を介し、第(N-1)のシール部にて貼り合わせ、各シール部には、各液晶層の厚さと同程度の粒径を有する導電粒を含有し、さらに、第(N-2)の基板と第Nの基板間、あるいは第(N-3)の基板と第Nの基板間等、隣接しない基板間にも、シール材と導電粒を有し、後者の導電粒と前者の導電粒の粒径が異なることを特徴とする。

【0018】

20

本発明の液晶表示装置は、第1の基板の液晶層側の面に設ける電極と、これに対向する第2の基板の面に設ける電極と、前記第2の基板上で、かつ第1の基板に対向して電極を設ける面と反対側の面に電極を設け、さらに、第2の基板と同様に両面に電極を有するN基板まで有し、N+1基板上には、N基板に面する基板上のみ2×N番目の電極を設け、第1の基板の電極とこれに対向する第2の基板の電極とを第1の液晶層を介して第1のシール部にて貼り合わせ、隣接するN-1基板とN基板との基板間には、第(N-1)の液晶層を介し、第(N-1)のシール部にて貼り合わせ、各シール部には、各液晶層の厚さと同程度の粒径を有する導電粒を含有し、さらに、第(N-2)の基板と第Nの基板間、あるいは第(N-3)の基板と第Nの基板間等、隣接しない基板間にも、シール材と導電粒を有し、後者の導電粒と前者の導電粒との粒径と材質が異なることを特徴とする。

【0019】

30

本発明の液晶表示装置は、N+1枚の基板を積層して各基板間に液晶を挟持し、第1および第N+1基板は液晶層側の片面のみに電極を設け、第2の基板から第N基板は両面に電極を設けてあり、これらN+1枚の基板のうち隣接して液晶層を挟む2枚の基板の組の少なくとも一つにて、相対するそれぞれの基板面の一方に画素電極、他方に対向電極を形成し、対向電極は大面積であって画素電極群をほぼ全部覆い、隣接する基板同士をシール部で貼り合わせ、シール部の近傍には、各液晶層の厚さより小さい粒径の導電粒を含有し、さらに中間に1枚またはそれ以上の他の基板が介在する基板同士をも導電粒を含有するシール部で貼り合わせ、こちらの導電粒は隣接する基板同士を貼り合わせるシール部の導電粒と粒径が異なることを特徴とする。

【0020】

40

本発明の腕時計装置は、外装と風防ガラスと液晶表示装置を駆動する回路とを有し、さらに、異なる導電粒を利用し、複数の電極間の接続を有する液晶表示装置を表示部とすることを特徴とする。

【0021】

本発明の腕時計装置は、外装と風防ガラスと液晶表示装置を駆動する回路と時針と分針を少なくとも有し、さらに、異なる導電粒を利用し、複数の電極間の接続を有する液晶表示装置を表示部とし、さらに、前記液晶表示装置は時計の風防側に設け、さらに、第1の基板上にて、駆動回路と各電極へ駆動電圧を印加する接続を行うことを特徴とする。

50

## 【0022】

(作用)

本発明の液晶表示装置を利用する、複数の液晶層に電圧を印加するために設ける複数の基板上に設ける複数の電極を異なる径の導電粒を含むシール部からなる異方性導電シールを利用し、第1の基板上の電極に各電極を転換することにより、チップ・オン・ガラス(COG)法のIC基板を複数の基板上の電極の接続に共用することが可能となり、IC基板の実装面積と実装工程数を低減することが可能となり、複数の基板を積層することの障害を防止することができる。

## 【0023】

さらに、各液晶層に対応する走査電極は、積層構造の各液晶層に対して同一の選択期間に所定のデーター電圧を印加するため、各液晶層に対応する各走査電極を第1の基板上で、導電粒により相互接続する方法を採用することにより、実装を行うIC基板の個数を低減、あるいはIC基板の面積の低減、あるいは、IC基板に外部回路より電圧を印加するための実装面積の低減が可能となる。

## 【0024】

さらに、第1の基板上に電極を転換することが可能なため、導電体部と非導電体部が交互に積層されている異方性導電ゴム(ゼブラゴム)による実装方式には第1の基板上の電極と接続を行えばよいため非常に有効となる。

## 【0025】

さらに、薄膜トランジスタ(TFT)の場合には、薄膜トランジスタを設けるアクティブ基板(第1の基板)に対して対向基板(第2の基板)は電極のパターン形成を必要としないため、第1の基板と第2の基板間の一部に異方性導電シール部を設ければ良いため、複数のアクティブ基板と複数の対向基板を積層する場合には、本発明の異なる径の導電粒を含むシール部を利用することにより簡単に第1の基板上の電極へ転換することができる。

## 【0026】

さらに、本発明の液晶表示装置を腕時計装置に利用することにより、腕時計装置は液晶表示装置自体、あるいはIC基板の実装面積、あるいはIC基板へ電圧を印加する外部回路との接続面積を低減し、液晶層の多層構造による液晶表示装置の表示品質の向上が可能となり、さらに、実装による腕時計装置のデザインの制限を除去することが可能となる。

## 【0027】

## 【発明の実施の形態】

本発明の最良の実施形態における液晶表示装置の構造を図面に基づいて説明する。

## 【0028】

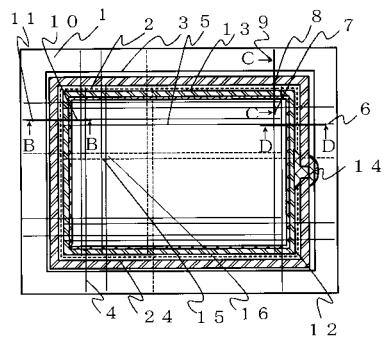

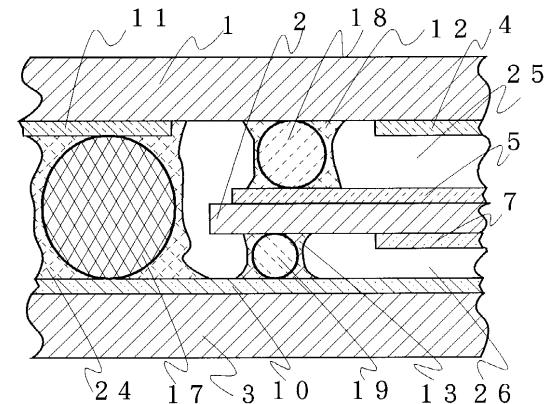

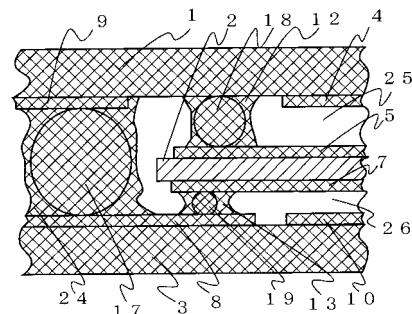

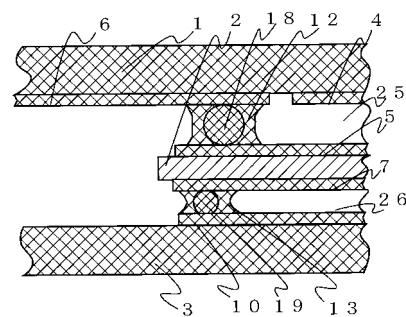

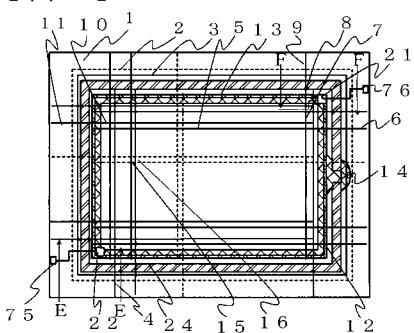

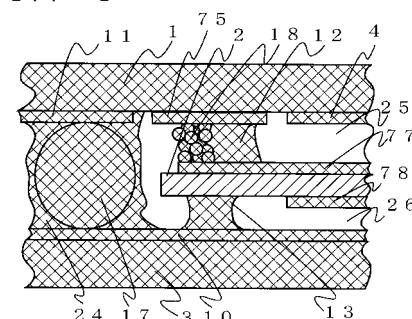

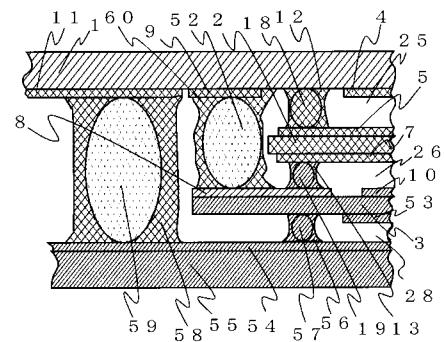

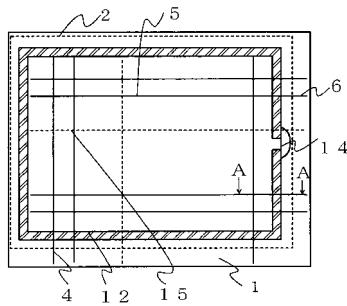

図1は、第1の実施形態における液晶表示装置の全体を示す平面図である。図2は、図1のB-B線における断面図である。図3は、図1のC-C線における断面図である。図4は、図1のD-D線における断面図である。以下図1と図2と図3と図4とを交互に用いて本発明の第1の実施形態を説明する。

## 【0029】

液晶表示装置は、紙面上面に設ける第1の基板1と、紙面下面に設ける第3の基板3と、第1の基板1と第3の基板3との間に設ける第2の基板2からなる3種類の基板1、2、3を有する。第1の基板1上には、ストライプ状の第1の電極4と第1の接続部4(これは第1の電極4の端部なので、同じく符号4とする)と第2の接続部6と第3の接続部9と第4の接続部11とを有する。第1の基板1は、第1から第4の接続部4、6、9、11を画素部15、16の周囲に設け、外部の回路との接続を行つたため、第2の基板2と第3の基板3より大きな面積を有する。

## 【0030】

同様に、第2の基板2の第1の基板1に面する面上には、第1の電極4と直交するストライプ状の第2の電極5を設ける。また、第2の電極5を設ける面と反対の面には、ストライプ状の第3の電極7を設ける。さらに、第3の電極7と直交するストライプ状の第4の電極10を第3の基板上に設ける。また、各電極4、5、7、10上とその周囲には、

10

20

30

40

50

液晶層を配列するために配向膜(図示せず)を有する。

**【0031】**

また、第1の電極4を有する第1の基板1と第2の電極5を有する第2の基板2とは、第1のシール材からなる第1のシール部12と封口部14により第1の液晶層25を封入する構造を有する。

**【0032】**

同様に、第3の電極7を有する第2の基板2と第4の電極10を有する第3の基板3とは、第2のシール材からなる第2のシール部13と封口部14により第2の液晶層26を封入する構造を有する。本実施形態においては、第1の液晶層25は、2色性色素を含む液晶、すなわちゲストホストモード液晶を利用し、第2の液晶層26においては、紫外線硬化型液晶ポリマーを有するポリマー分散型液晶(PDLC)を用いている。そのため、偏光板は用いていない。10

**【0033】**

さらに、第1の基板1と第3基板3とは、第3のシール材からなる第3のシール部24により接着する構造を有し、第3のシール部24は、第1のシール部12と第2のシール部13より外側に配置する構造を有する。

**【0034】**

また、第1のシール部12は、第1の導電粒18を含み、第2のシール部13には第2の導電粒19を含み、第3のシール部24には、第3の導電粒17を含む構成である。

**【0035】**

また、第3の基板3上には、ストライプ状の第4の電極10と第5の接続部8とを有する。第3の基板3上の第4の電極10は、図2に示すように、第3のシール部24と第3の導電粒17とにより第1の基板1上の第4の接続部11に接続している。すなわち、機械的接続は、エポキシ樹脂からなる第3のシール部によりなされ、電気的接続は、第3の導電粒17によりなされる。以上により、第3の基板3上の第4の電極10は、第3の導電粒17と第1の基板1上の第4の接続部11により、第1の基板1上に配置転換される。20

**【0036】**

同様に、第2の基板2上の第3の電極7は、図3に示すように、第2のシール部13と第2の導電粒19とにより第3の基板3上の第5の接続部8に接続している。第5の接続部8の接続は、第4の電極10と第1の基板1上の第4の接続部11との接続と同様な構造からなり、第3のシール部24と第3の導電粒17とにより第1の基板1上の第3の接続部9に接続している。すなわち、機械的接続は、エポキシ樹脂からなる第3のシール部によりなされ、電気的接続は、第3の導電粒17によりなされる。以上により、第2の基板2上の第3の電極7は、第2の導電粒19により、第3の基板3上の第5の接続部8に転換し、さらに、第3の導電粒17により第1の基板1上の第3の接続部9に接続する構造となる。30

**【0037】**

さらに、第2の基板2上の第2の電極5は、図4に示すように、第1のシール部12と第1の導電粒18とにより第1の基板1上の第2の接続部6に接続している。すなわち、機械的接続は、エポキシ樹脂からなる第1のシール部によりなされ、電気的接続は、第1の導電粒18によりなされる。以上により、第2の基板2上の第2の電極5は、第1の導電粒18と第1の基板1上の第2の接続部6により、第1の基板1上に配置転換される。40

**【0038】**

以上の構造を採用することにより、機械(物理)的強度は、第1の基板1に持たせることにより、第2の基板2、あるいは第3の基板3の基板を薄板化することが可能となる。そのため、観察者と液晶表示装置の位置により発生していた、第1の液晶層25と第2の液晶層26とが構成する各画素部15と16の表示のずれを、非常に有効に防止することが可能となる。さらに、本実施形態を反射型液晶表示装置として利用し、第3の基板3の裏面に反射板を設ける場合には、第3の基板3の薄板化と第2の基板2の薄板化により、50

表示の二重像の防止ができ、液晶表示装置の表示品質の向上が可能となる。

#### 【0039】

さらに、第1の基板1上に設ける複数の各接続部と、第2の基板2上に設ける第2の電極5と第3の電極7と、第3の基板3上に設ける第4の電極10とを各導電粒18、19、17を介して電気的に接続することにより、各基板2、3上の各配線5、7、10と外部回路との接続端子を第1の基板1上に転移することができるため、外部回路との接続(実装)工程のスピードアップ化、実装高さの均一化が可能となり、安定な特性を有する実装が可能となった。

#### 【0040】

さらに、第2の基板2上の第2の電極5と第3の基板3上の第4の電極10はいずれも液晶表示装置の走査線であり、各画素部15と16の画素ピッチが同等のため、第1の基板1上の第2の接続部6と第4の電極10用の第4の接続部11を接続し、図1に示す液晶表示装置の左側に設ける。これにより、第2の電極5と第4の電極10とはそれぞれの接続部である第2の接続部6、第4の接続部11を共通化して第1の基板1上に転移でき、そのため、第1の基板1の右側の第2の接続部6の部分の面積の低減と外部回路との接続数を低減することができる。これにより、液晶表示装置の表示に利用する面積の比率を大きくすることができる。さらに、当然外部回路のコスト、フレキシブルプリント回路(FPC)の面積とコストの低減も可能となる。

10

#### 【0041】

また、本発明の実施形態においては、外部回路との接続方法にFPCを利用する方式を利用したが、第1の基板1上に集積回路(IC)を直接実装するCOG法の場合には、FPCを利用する方法と同様に第2の電極5と第4の電極10のそれぞれの接続部である第2の接続部6と第4の接続部11を共通化し、さらに、第1の電極4と第3の電極7の接続部9とを第2と第4の接続部6と11の周間に接近して配置することにより、1個の集積回路のみの実装により各電極へ信号波形を印加することが可能となり、多層構造を有する液晶表示装置でありながら、非常に簡単に外部回路を実装することが可能となる。

20

#### 【0042】

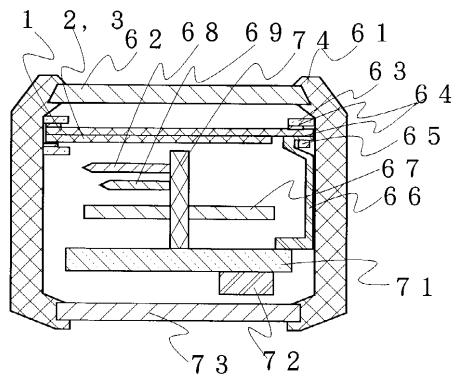

つぎに、本発明の第2の実施形態における液晶表示装置の構造を図面に基づいて説明する。第2の実施形態は、第1の基板1と第3の基板3上にスイッチング素子として薄膜トランジスタ(TFT)を有する場合に関するものである。

30

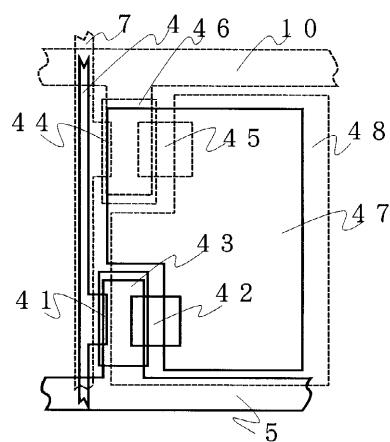

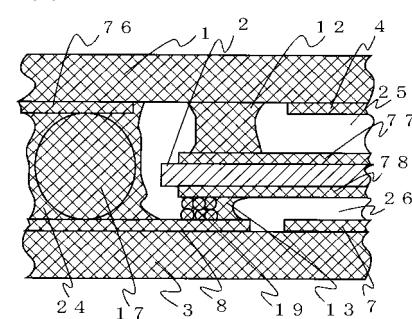

#### 【0043】

図5は、第2の実施形態における液晶表示装置の全体を示す平面図である。図6は、薄膜トランジスタの部分を拡大する平面図である。図7は、図5のE-Eにおける断面図である。図8は、図5のF-F線における断面図である。以下図5と図6と図7と図8とを交互に用いて本発明の第2の実施形態を説明する。

#### 【0044】

液晶表示装置は、紙面上面に設ける第1の基板1と紙面下面に設ける第3の基板3と第1の基板1と第3の基板3との間に設ける第2の基板2からなる3種類の基板1、2、3を有する。第1の基板1上には、図6に実線にて示す薄膜トランジスタを有し、第3の基板3上には、図6の破線にて示す薄膜トランジスタを有する。第2の実施形態においては、実線で示す薄膜トランジスタと破線の薄膜トランジスタの位置を便宜上違えたが、実際には画素部の内の薄膜トランジスタの占める面積を低減することが理想のため、同一箇所に配置することが望ましい。

40

#### 【0045】

薄膜トランジスタの構造は、図6に示すように、第2の電極5(本実施形態では第1の基板1上に形成)の一部にゲート電極を形成して、ゲート電極上にはゲート絶縁膜(図示せず)を有し、ゲート絶縁膜上には、アモルファスシリコン(Si)からなる半導体層43を有し、半導体層43上でゲート電極と重なり合う部分に第1の電極4の一部に形成したソース電極41とドレイン電極42を有する。半導体層43とソース電極41とドレイン電極42との間には、不純物イオンを含む半導体層(図示せず)を有する。また、ドレ

50

イン電極 4 2 は、画素電極 4 7 と接続している。

【0046】

同様に、第3の基板3上には、第4の電極10の一部にゲート電極を形成して、ゲート電極上にはゲート絶縁膜(図示せず)を有し、ゲート絶縁膜上には、アモルファスシリコン(Si)からなる半導体層46を有し、半導体層46上でゲート電極と重なり合う部分に第3の電極7(本実施形態では第3の基板3上に形成)の一部に形成したソース電極44とドレイン電極45を有する。半導体層46とソース電極44とドレイン電極45との間には、不純物イオンを含む半導体層(図示せず)を有する。また、ドレイン電極45は、画素電極48と接続している。

【0047】

また、スイッチング素子として薄膜トランジスタを使用する場合には、第2の基板上の電極はパターン形成する必要がなく、第1の実施形態に示すストライプ状の第1の電極4と第2の電極5とが第1の基板1上に配置される。同様に、第3の電極7と第4の電極10とが、第3の基板3上に配置される構造となる。そのため、第2の基板2上の電極は、特にパターン形成する必要がないため、第2の実施形態では、第1の実施形態のストライプ状の電極とは異なる名称を使用し、第1の基板1に対向する電極を第1の対向電極77とし、第3の基板3に対応する電極を第2の対向電極78とする。

【0048】

また、第1の基板1の外周部には、ストライプ状の第1の電極(ソース電極)4と第1の接続部(第1の電極と共に通)4と第2の接続部6と第3の接続部9と第4の接続部11とを有する。第1の基板1は、第1から第4の接続部4、6、9、11を画素部15、16の周囲に設け、外部の回路との接続を行うため、第2の基板2と第3の基板3より大きな面積を有する。

【0049】

第1の基板1と第2の基板2と第3の基板3上の画素電極47、48と対向電極77、78上とその周囲には、液晶層を配列するために配向膜(図示せず)を有する。

【0050】

また、第1の基板1と第2の基板2とは、第1のシール部12と封口部14により第1の液晶層25を封入する構造を有する。

【0051】

同様に、第2の基板2と第3の基板3とは、第2のシール部13と封口部14により第2の液晶層26を封入する構造を有する。本実施形態においては、第1の液晶層25は、液晶層25に印加する電圧により黒着色と透明となる2色性色素を含む液晶、すなわちゲストホストモード液晶を利用し、第2の液晶層26においては、液晶層26に印加する電圧によりシアンと透明となる2色性色素を含む液晶、すなわちゲストホストモード液晶を用いている。そのため、偏光板は用いていない。封口部14は、第1のシール部12と第2のシール部13と第3のシール部24のそれぞれの開口部(封口部)を封止する構造を採用している。

【0052】

さらに、第1の基板1と第3基板3とは、第3のシール部24により接着する構造を有し、第3のシール部24は、第1のシール部12と第2のシール部13より外側に配置する構造を有する。

【0053】

また、第1のシール部12は、第1の導電粒18を含み、第2のシール部13には第2の導電粒19を含み、第3のシール部24には、第3の導電粒17を含む構成である。

【0054】

また、第3の基板3上には、一部にゲート電極を形成したストライプ状の第4の電極10と一部にソース電極44を形成した第3の電極7と第5の接続部8とを有する。第3の基板3上の第4の電極10は、図7に示すように、第3のシール部24と第3の導電粒17とにより第1の基板1上の第4の接続部11に接続している。すなわち、機械的接続は

10

20

30

40

50

、エポキシ樹脂からなる第3のシール部により接続され、電気的接続は、第3の導電粒17により接続される。以上により、第3の基板3上の第4の電極10は、第3の導電粒17と第1の基板1上の第4の接続部11により、第1の基板1上に配置転換される。

#### 【0055】

同様に、第3の基板3上のソース電極である第3の電極7は、第3のシール部24と第3の導電粒17とにより第1の基板1上の第3の接続部9に接続している。以上により、第3の基板3上のソース電極である第3の電極7は、第3の導電粒17と第1の基板1上の第3の接続部9により、第1の基板1上に配置転換される。

#### 【0056】

さらに、第2の基板2上の第2の対向電極78は、ストライプ状にパターン形成せずに面積の大きな一体型の電極のため、第3の基板3と第2の基板2との角部21において、第2の導電粒19により第3の基板上の第5の接続電極8に接続し、さらに、第3のシール部24と第3の導電粒17とにより第1の基板1上の第2の引き出し電極76に接続する。こうして、第2の基板2上の第3の基板3に面する第2の対向電極78も第1の基板1上に配置転換される。

#### 【0057】

同様に、第2の基板2上の第1の基板1に面する第1の対向電極77は、第2の対向電極78と同様に面積の大きな一体型の電極のため、第2の基板2の角部22において、第1の導電粒18により第1の基板1上の第1の引き出し電極75に接続する。こうして、第2の基板2上の第1の基板1に面する第1の対向電極77も第1の基板1上に配置転換される。

#### 【0058】

以上により、第1の基板1上の各接続電極4、6、9と11と引き出し電極75と76により、各基板1、2と3上の各電極は、全て導電粒18、19、17を介して第1の基板1上の配置転換することが可能となる。そのため、薄膜トランジスタを有する複数の液晶表示パネルを有する場合においても、外部回路との接続（実装）工程のスピードアップ化、実装高さの均一化が可能となり、安定な特性を有する実装が可能となった。

#### 【0059】

さらに、本第2の実施形態を変形し、第1の液晶層25と第1の薄膜トランジスタに接続する第1の画素電極47と第1の対向電極77より構成する第1の画素部15と、第2の液晶層26と第2の薄膜トランジスタに接続する第2の画素電極48と第2の対向電極78より構成する第2の画素部16とが同一の画素ピッチのため、第1の基板1上の第1のゲート電極である第2の電極5と第3の基板3上の第2のゲート電極である第4の電極10とを第3の導電粒17により接続し、第1の基板1上の同一の接続電極を利用して外部回路との接続を行うことにより、第1の基板1の第2の接続部6の部分の面積の低減と外部回路との接続数を低減することができる。そのため、液晶表示装置の表示に利用する面積の比率を大きくすることができます。さらに、当然外部回路のコスト、フレキシブルプリント回路（FPC）の面積とコストの低減も可能となる。

#### 【0060】

また、本発明の実施形態においては、外部回路との接続方法にFPCを利用する方式を利用したが、第1の基板1上に集積回路（IC）を直接実装するCOG法の場合には、第1のゲート電極である第2の電極5と第2のゲート電極である第4の電極10とを同一の接続電極に第3の導電粒17を利用して相互に接続し、さらに、第1のソース電極である第1の電極4と第2のソース電極である第3の電極7とを相互に接近して配置することにより、1個の集積回路のみの実装により各電極へ信号波形を印加することができる、多層構造を有する液晶表示装置でありながら、非常に簡単に外部回路を実装することが可能となる。

#### 【0061】

つぎに、本発明の第3の実施形態における液晶表示装置の構造を図面に基づいて説明する。本第3の実施形態は、第1の基板1と第2の基板2と第3の基板3と第4の基板55

10

20

30

40

50

とを有している。

#### 【0062】

図9は、第1の実施形態を示す図1のB-B線における断面図に相当する箇所の基板数を4枚にした場合の断面図である。符号に関しては、第1の実施形態、あるいは第2の実施形態と同様な部分に関しては、同一の符号を使用して説明を行う。

#### 【0063】

第1の基板1上には、ストライプ状の第1の電極4と、第1の電極4に接続するので同じ符号を与えた第1の接続部4と、第2の接続部6と、第3の接続部9と、第4の接続部11と、さらに第6の接続部と第7の接続部とを有する。ただし、第5の接続部は他の基板上にある。

10

#### 【0064】

同様に、第2の基板2上には、第1の基板1に面する面には、第1の電極4と直交し、かつストライプ状の第2の電極5を有し、反対側の面には、ストライプ状の第3の電極7を形成する。第1の基板1と第2の基板2との間隙には、第1の液晶層25を有する。同様に、第3の基板3上には、第2の基板2に面する面には、第3の電極7と直交し、かつストライプ状の第4の電極10を有し、反対側の面には、ストライプ状の第5の電極53を形成する。第2の基板2と第3の基板3との間隙には、第2の液晶層26を有する。同様に、第4の基板55上には、第3の基板3に面する面に、第5の電極53と直交し、かつストライプ状の第6の電極54を有し、第3の基板3と第4の基板55との間隙には、第3の液晶層28を有する。

20

#### 【0065】

各液晶層25、26と28に面する基板1、2、3と55と各電極4、5、7、10、53と54上には、液晶層を配列するための配向膜(図示せず)を有する。

#### 【0066】

第1の液晶層25の周囲には、第1の導電粒18を含む第1のシール部12を有し、第2の液晶層26の周囲には、第2の導電粒19を含む第2のシール部13を有する。さらに、第1の基板1と第3の基板3との間には、第4の導電粒52を含む第4のシール部60を有する。さらに、第3の液晶層28の周囲には、第3の導電粒57を含む第3のシール部56を有し、第6の電極54と第1の基板1との間には、第5の導電粒59を含む第5のシール部58を有する。

30

#### 【0067】

つぎに、各電極を第1の基板1上の電極へ配置転換する経路を説明する。第1の基板1上の第1の電極4は第1の接続部に接続するが、第1の接続部は第1の電極4と一体構造なのでこれと同符号の4とする。第2の基板2上の第2の電極5は、第1の導電粒18を介して第1の基板1上の第2の接続部6(図4参照)に接続する。第2の基板2上の第3の電極7は、第2の導電粒19により第3の基板3上の第5の接続部8に一度配置転換を行い、さらに、第4の導電粒52により第1の基板1上の第3の接続部9に接続する。第3の基板3上の第4の電極10は、第4の導電粒52により第1の基板1上の第6の接続部(図示せず)に接続する。第3の基板3上の第5の電極53は、一度第4の基板55上の電極に第3の導電粒57により接続し、さらに、第5の導電粒59を介して第1の基板1上の第7の接続部(図示せず)に接続する。第4の基板55上の第6の電極54は、第5の導電粒59を介して第1の基板1上の第4の接続部11に接続する。以上により、電極間を粒径の異なる導電粒を介して接続を行うことにより、複数の液晶層25、26と28を有する液晶表示装置においても、第1の基板1上の配線へ配置転換を行うことができる。

40

#### 【0068】

さらに多数の液晶層を有する構造においても、第1の実施形態から第3の実施形態に示す異なる粒径の導電粒をシール部に混入し、各電極間を導電粒で接続することにより、第1の基板上の配線への配置転換が可能となる。

#### 【0069】

50

以上の第1の実施形態から第3の実施形態と同様に、粒径の異なる導電粒を利用することにより、第1の基板からN+1の基板構成の液晶表示装置においても、各基板上の電極を第1の基板上に配置転換を行うことができる。

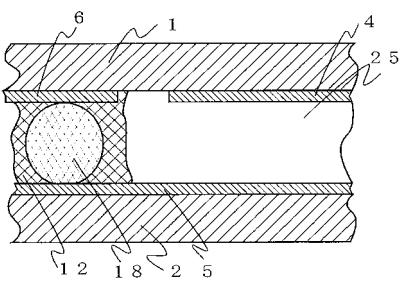

#### 【0070】

つぎに、本発明の第4の実施形態を図面に基づいて説明する。第4の実施形態は、第1の実施形態から第3の実施形態に示す複数の液晶層を有する液晶表示装置を使用する腕時計装置の実施形態である。図10は、複数の液晶層からなる液晶表示装置を有する腕時計装置の断面図である。以下に図面に基づいて説明する。

#### 【0071】

本実施形態に用いる腕時計装置の構造は、液晶表示装置を時針、分針より観察者側に配置する構成である。

10

#### 【0072】

時計ケース61には、風防ガラス62と裏蓋部73を有する。風防ガラス62側より、第1の基板1と第2の基板2と第3の基板3を配置する。第1の液晶層は、2色性色素を液晶に含むゲスト・ホスト型の液晶層を有し、第2の液晶層は高分子散乱型液晶層からなる。散乱型液晶表示パネルは、液晶に有機物モノマーとコレステリック液晶とを混合し、第2の基板2と第3の基板との間隙に封入した後に紫外線により高分子ポリマー化し、液晶の光学異方性と高分子ポリマーとの屈折率の差を利用して、外部光を散乱するものを採用する。散乱型液晶表示パネルは、小さい電圧印加により透明であり、電圧の増加により散乱強度が増加する。このため、表示していない場合には、常に表示電力を低く保つことができる。

20

#### 【0073】

また、第1の液晶表示パネルと第2の液晶表示パネルとを時針69あるいは分針68上で保持する必要があるため、ゴム製の液晶表示パネルの上押さえ63とコの字型の上下押さえ64により第1と第2の液晶表示パネルを保持する。さらに、駆動回路72を搭載した回路基板71と第1の基板1上の接続部との接続をコネクター66により行う。コネクター66により各液晶層へ所定の駆動信号を印加する。

#### 【0074】

以上に示すように、腕時計装置の時針69と分針68上の風防ガラス62側に液晶表示装置を配置し、第2の液晶層により文字板67あるいは、時針69、分針68、指針軸74等の第2の液晶層の下方に位置する部材を遮蔽することにより、時針69あるいは、分針68の影響を受けることなく第1の液晶層による表示を行うため、情報の認識性が非常に向上する。

30

#### 【0075】

以上に示すように、液晶表示装置を腕時計装置の風防ガラス62側に配置する場合には、腕時計装置の特徴として非常に容積と厚さの限定が厳しいため、有効表示面積の比率が大きく、さらに、回路基板71と液晶表示装置の接続に要する容積の低減が非常に要求される。そのため、多層の液晶層に所定の信号を印加して制御するための電極をまとめ、さらに、同一基板上へ配置転換することを利用し、腕時計装置の装飾性を妨げることなく、複数の液晶層を用い、従来の液晶表示装置では、表示することができなかった表示を可能とし、腕時計装置の品質の向上を可能とする。

40

#### 【0076】

#### 【発明の効果】

以上の説明から明らかなように、異なる粒径の導電粒を利用し、複数の液晶層へ所定の信号を印加する電極を導電粒を介して第1の基板上の接続部に電気的接続を行う方法を採用することにより、第1の基板上へ全ての電極を電気的に配置転換することができる。そのため、外部回路との接続を行う基板面を単一面とすることができます、実装のコスト、安定性の向上、実装時間の短縮ができる。

#### 【0077】

さらに、異なる径を有する導電粒を利用し、複数の基板に配置する電極を相互に接続し

50

、同一の信号を印加することにより、実装面積の縮小、実装のための配線本数の低減により、表示品質の向上と、実装面積の点で非常に条件の厳しい製品等への利用が可能となる。

#### 【0078】

さらに、第1の基板上に各電極を配置転換することができるため、チップ・オン・ガラス実装法の場合には、各接続部を近接し、実装する集積回路の個数を減少することが可能となる。

#### 【0079】

特に、腕時計装置の場合には、液晶表示装置の実装面積が品質に影響を与えるため、第1の基板上へ各電極を配置転換し、単一基板面にて実装を行うことにより、腕時計装置の小型化、軽量化、薄型化が可能となり、装飾性を重要とする腕時計装置においては、非常に有効となる。

10

#### 【0080】

本発明の実施形態においては、電極のみを設ける、いわゆるモノクロ表示の実施形態を示したが、カラーフィルターを有する場合にも当然本発明の効果は有効である。

#### 【0081】

本発明の実施形態に用いる導電粒子を含むシール部の基板上への形成方法は、印刷法、ディスペ ns方式、ノズルによるジェット法が有効である。

#### 【0082】

各シール部の封口部は、各液晶層により異なる位置に設ける場合においても、本発明の効果は、当然有効であり、さらに、内側の封口部を外周側のシール材にて封口を行うことも当然可能である。

20

#### 【0083】

本腕時計装置の実施形態に置いては、液晶表示装置を風防側に利用する例を示したが、時針と分針より回路基板側に配置する場合においても当然有効であり、さらに、機械的表示を行わない、いわゆるデジタル腕時計装置においても当然有効である。

#### 【図面の簡単な説明】

【図1】 本発明の第1の実施例における液晶表示装置を示す平面図である。

【図2】 本発明の第1の実施例における液晶表示装置の一部を拡大する断面図である。

30

【図3】 本発明の第1の実施例における液晶表示装置の一部を拡大する断面図である。

【図4】 本発明の第1の実施例における液晶表示装置の一部を拡大する断面図である。

【図5】 本発明の第2の実施例における液晶表示装置を示す平面図である。

【図6】 本発明の第2の実施例における液晶表示装置の一部を拡大する平面図である。

【図7】 本発明の第2の実施例における液晶表示装置の一部を拡大する断面図である。

【図8】 本発明の第2の実施例における液晶表示装置の一部を拡大する断面図である。

【図9】 本発明の第3の実施例における液晶表示装置の一部を拡大する断面図である。

【図10】 本発明の第4の実施例における腕時計装置を示す断面図である。

【図11】 従来例における液晶表示装置を示す平面図である。

【図12】 従来例における液晶表示装置の一部を拡大して示す断面図である。

#### 【符号の説明】

40

1 第1の基板

2 第2の基板

3 第3の基板

4 第1の電極（第1の接続部）

5 第2の電極

6 第2の接続部

7 第3の電極

8 第5の接続部

9 第3の接続部

10 第4の電極

50

|     |                    |    |

|-----|--------------------|----|

| 1 1 | 第 4 の接続部           |    |

| 1 2 | 第 1 のシール部          |    |

| 1 3 | 第 2 のシール部          |    |

| 1 4 | 封口部                |    |

| 1 5 | <u>画素部</u>         |    |

| 1 6 | <u>画素部</u>         |    |

| 1 7 | 第 3 の導電粒           |    |

| 1 8 | 第 1 の導電粒           |    |

| 1 9 | 第 2 の導電粒           |    |

| 2 4 | <u>第 3 のシール部</u>   | 10 |

| 2 5 | 第 1 の液晶層           |    |

| 2 6 | 第 2 の液晶層           |    |

| 2 8 | <u>第 3 の液晶層</u>    |    |

| 4 7 | <u>画素電極</u>        |    |

| 4 8 | <u>画素電極</u>        |    |

| 5 2 | <u>第 4 の導電粒</u>    |    |

| 5 3 | <u>第 5 の電極</u>     |    |

| 5 4 | <u>第 6 の電極</u>     |    |

| 5 5 | <u>第 4 の基板</u>     |    |

| 5 6 | <u>第 3 のシール部</u>   | 20 |

| 5 7 | 第 3 の導電粒           |    |

| 5 8 | <u>第 5 のシール部</u>   |    |

| 5 9 | 第 5 の導電粒           |    |

| 6 0 | <u>第 4 のシール部</u>   |    |

| 6 8 | 分針                 |    |

| 6 9 | 時針                 |    |

| 7 1 | <u>回路基板</u>        |    |

| 7 2 | <u>駆動回路</u>        |    |

| 7 5 | <u>第 1 の引き出し電極</u> |    |

| 7 6 | <u>第 2 の引き出し電極</u> | 30 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

---

フロントページの続き

(56)参考文献 特開平06-273790(JP,A)

特開昭58-088722(JP,A)

特開平07-198865(JP,A)

特開昭58-154819(JP,A)

特開昭59-060420(JP,A)

特開昭57-173815(JP,A)

特開平05-165060(JP,A)

特開平09-096832(JP,A)

特開昭55-113024(JP,A)

特開昭52-010096(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1339

G02F 1/1341

G02F 1/1345

G02F 1/1347

G02F 1/1333

G02F 1/13 505