(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-520089

(P2006-520089A)

(43) 公表日 平成18年8月31日(2006.8.31)

(51) Int.C1.

|             |           |

|-------------|-----------|

| HO1L 21/822 | (2006.01) |

| HO1L 27/04  | (2006.01) |

| HO1L 27/00  | (2006.01) |

| HO1L 25/18  | (2006.01) |

| HO1L 25/07  | (2006.01) |

F 1

|            |      |

|------------|------|

| HO1L 27/04 | U    |

| HO1L 27/00 | 301H |

| HO1L 25/08 | Z    |

テーマコード(参考)

5FO38

審査請求 未請求 予備審査請求 未請求 (全 78 頁) 最終頁に続く

|               |                              |           |                                                                                 |

|---------------|------------------------------|-----------|---------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2005-500831 (P2005-500831) | (71) 出願人  | 503251662<br>レビオ インコーポレーティッド<br>アメリカ合衆国 10523 ニューヨーク州, エルムスフォード エグゼクティブブルバード 85 |

| (86) (22) 出願日 | 平成15年11月20日 (2003.11.20)     | (74) 代理人  | 100091683<br>弁理士 ▲吉▼川 俊雄                                                        |

| (85) 翻訳文提出日   | 平成17年7月15日 (2005.7.15)       | (72) 発明者  | ファリス, サデグ, エム.<br>アメリカ合衆国 ニューヨーク州 10570, プリーザントビル, ポカンティコリバー ロード 24             |

| (86) 國際出願番号   | PCT/US2003/037304            | F ターム(参考) | 5F038 CA03 CA12 CA15 CA16 DF14 EZ20                                             |

| (87) 國際公開番号   | W02004/112089                |           |                                                                                 |

| (87) 國際公開日    | 平成16年12月23日 (2004.12.23)     |           |                                                                                 |

| (31) 優先権主張番号  | 60/428,125                   |           |                                                                                 |

| (32) 優先日      | 平成14年11月20日 (2002.11.20)     |           |                                                                                 |

| (33) 優先権主張国   | 米国(US)                       |           |                                                                                 |

最終頁に続く

(54) 【発明の名称】基板上に多層素子を製造する方法およびシステム

## (57) 【要約】

バルク性基板上に多層能動素子を製造する方法が開示される。多層微小電気機械および微小流体素子は、素子の分解された層がある または、弱い結合領域上の所定の弱いおよび強い結合領域の層を有する基板に製造される。所定の弱いおよび強い結合領域の層を有する基板に製造される多層集積回路が開示される。任意の数の層は、基板上に所定の素子を作成するため、結合され、スタックされることができる。また、層とその装置の上との間の相互接続を形成するため、エッジ相互接続を作成する方法および基板を通じたバイアが開示される。

**【特許請求の範囲】****【請求項 1】**

垂直の微小電気機械装置を製造する方法であって、バルク性基板の提供ステップ；前記基板上での強い結合領域作成および弱い結合領域の選択的な作成ステップ；前記基板上での垂直に支持される第1の接合された半導体層の提供ステップ；前記第1の接合された半導体層上での電極の作成ステップであって、前記電極は、前記弱い結合領域に対応する；前記電極の反対側に配置された作動可能な要素の作成；前記バルク性基板から前記第1の半導体層の除去ステップ；および第2の半導体層への前記第1の半導体層の結合ステップからなる方法。

**【請求項 2】**

請求項1の方法であって、前記第1の半導体層を同様に配置された電極を有する前記第2の半導体層に整列配置するステップをさらに含む方法。

**【請求項 3】**

請求項2の方法であって、前記整列配置ステップは機械的な整列である方法。

**【請求項 4】**

請求項2の方法であって、前記整列配置ステップは光学的な整列である方法。

**【請求項 5】**

請求項1の方法であって、前記第2の半導体層上に電極を作成するステップをさらに含む方法。

**【請求項 6】**

請求項5の方法であって、前記第2の半導体層は、前記弱い結合領域上に半導体素子部を有する方法。

**【請求項 7】**

請求項1の方法であって、前記弱い結合領域に対する前記強い結合領域の領域比率は、1より大きい方法。

**【請求項 8】**

請求項1の方法であって、前記弱い結合領域に対する前記強い結合領域の結合強さの比率は、1より大きい方法。

**【請求項 9】**

請求項1の方法であって、前記第2の半導体層と前記第1の半導体層を相互接続するステップをさらに含む方法。

**【請求項 10】**

請求項9の方法であって、前記相互接続ステップは、前記半導体層のエッジで実行される方法。

**【請求項 11】**

請求項10の方法であって、前記相互接続ステップは、電気的な連結である方法。

**【請求項 12】**

請求項10の方法であって、前記相互接続ステップは、光学的な連結である方法。

**【請求項 13】**

請求項9の方法であって、前記相互接続ステップは、前記半導体層を通じて垂直に実行される方法。

**【請求項 14】**

請求項5の方法であって、前記バルク性基板からの前記第2の半導体層の除去ステップ；および、前記第1の半導体層への前記第2の半導体層の結合ステップをさらに含む方法。

**【請求項 15】**

請求項1の方法であって、前記バルク性基板で垂直に支持されるN番目の半導体層の提供ステップであって、前記N番目の半導体層は、強い結合領域および弱い結合領域を有する；前記N番目の半導体層上での電極の作成ステップであって、前記電極は、前記弱い結合領域に対応する；前記バルク性基板からの前記N番目の半導体層の除去ステップ；およ

10

20

30

40

50

び（N-1）番目の半導体層への前記N番目の半導体層の結合ステップをさらに含む方法。

。

【請求項16】

請求項15の方法であって、MEMS装置が前記N半導体層の2つから形成される方法。

。

【請求項17】

請求項1の方法であって、1つまたはそれ以上のダイを形成するため前記接合された半導体層をダイシングするステップをさらに含む方法。

【請求項18】

請求項17の方法であって、前記ダイシングステップの後、前記接合された半導体層を相互接続するステップをさらに含む方法。 10

【請求項19】

請求項18の方法であって、前記1つまたはそれ以上ダイの境界上にエッジコネクタ形成するステップをさらに含む方法。

【請求項20】

請求項19の方法であって、前記エッジコネクタが個々のダイ層の健康を決定する診断導体として役立つ方法。

【請求項21】

垂直のMEMS装置であって、ウェーハ上のバルク性基板；前記基板上で垂直に支持される第1の選択的に接合された半導体層であって、前記接合された半導体層は弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された半導体層上で、垂直に支持される第2の選択的に接合された半導体層；から構成され、 20

ここにおいて、電極および作動可能な要素は、前記弱い結合領域において、またはその中で作成される；またここにおいて、前記電極および前記作動可能な要素は、互いに対向して配置される、そして前記電極および前記作動可能な要素は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層において垂直にわたる垂直のMEMS装置。

【請求項22】

ダイの上に形成された垂直のMEMS装置であって、

ウェーハ上のバルク性基板；前記基板上で垂直に支持される第1の選択的に接合された半導体層であって、前記接合された半導体層は弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された半導体層上で、垂直に支持される第2の選択的に接合された半導体層；から構成され、 30

ここにおいて、要素および作動可能な要素は、前記弱い結合領域において、またはその中で作成される；またここにおいて、前記要素および前記作動可能な要素は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層において垂直にわたり、そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される垂直のMEMS装置。

【請求項23】

請求項22の回路であって、前記ダイが配線スタックを形成するためその垂直軸の周囲で回転する回路。 40

【請求項24】

請求項1の方法であって、前記バルク性基板が埋込み酸化物層を含む方法。

【請求項25】

請求項24の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

。

【請求項26】

多層微小流体素子を製造する方法であって、バルク性基板の提供ステップ；前記基板上への強い結合領域および弱い結合領域の選択的な作成ステップ；前記基板上への垂直に支持される第1の接合層の提供ステップ；前記第1の接合層上のポートの作成であって 50

、前記ポートは前記弱い結合領域に対応する；前記ポートに機械的に連結するチャネルの作成ステップ；前記バルク性基板からの前記第1の層の除去ステップ；および第2の層への前記第1の層の結合ステップからなる方法。

【請求項27】

請求項26の方法であって、前記第1の半導体層を同様に配置されたポートを有する前記第2の半導体層に整列配置するステップをさらに含む方法。

【請求項28】

請求項27の方法であって、前記整列配置ステップは機械的な整列である方法。

【請求項29】

請求項27の方法であって、前記整列配置ステップは光学的な整列である方法。

10

【請求項30】

請求項26の方法であって、前記第2の層上にポートを作成するステップをさらに含む方法。

【請求項31】

請求項30の方法であって、前記第2の層は、前記弱い結合領域上に微小流体素子部を有する方法。

【請求項32】

請求項26の方法であって、前記弱い結合領域に対する前記強い結合領域の領域比率は、1より大きい方法。

【請求項33】

請求項26の方法であって、前記弱い結合領域に対する前記強い結合領域の結合強さの比率は、1より大きい方法。

20

【請求項34】

請求項26の方法であって、前記第2の層と前記第1の層を相互接続するステップをさらに含む方法。

【請求項35】

請求項34の方法であって、前記相互接続ステップは前記第1および前記第2の層のエッジで実行される方法。

【請求項36】

請求項35の方法であって、前記相互接続ステップは、前記第1の層および前記第2の層を通じて垂直に実行される方法。

30

【請求項37】

請求項34の方法であって、前記バルク性基板からの前記第2の層の除去ステップ；および、前記第1の層への前記第2の層の結合ステップをさらに含む方法。

【請求項38】

請求項26の方法であって、前記バルク性基板で垂直に支持されるN番目の層の提供ステップであって、前記N番目の層は、強い結合領域および弱い結合領域を有する；前記N番目の層上でのポートの作成ステップであって、前記ポートは、前記弱い結合領域に対応する；前記バルク性基板からの前記N番目の層の除去ステップ；および(N-1)番目の層への前記N番目の層の結合ステップをさらに含む方法。

40

【請求項39】

請求項38の方法であって、微小流体素子が前記N層の2つから形成される方法。

【請求項40】

請求項26の方法であって、1つまたはそれ以上のダイを形成するため前記接合された層をダイシングするステップをさらに含む方法。

【請求項41】

請求項40の方法であって、前記ダイシングステップの後、前記接合された層を相互接続するステップをさらに含む方法。

【請求項42】

請求項41の方法であって、前記1つまたはそれ以上ダイの境界上にエッジコネクタ形

50

成するステップをさらに含む方法。

【請求項 4 3】

請求項 4 2 の方法であって、前記エッジコネクタが個々のダイ層の健康を決定する診断導体として役立つ方法。

【請求項 4 4】

請求項 2 6 の方法であって、前記バルク性基板が埋込み酸化物層を含む方法。

【請求項 4 5】

請求項 4 4 の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

。

【請求項 4 6】

多層微小流体素子であって、ウェーハ上のバルク性基板；前記基板上に垂直に支持される第 1 の選択的に接合された層であって、前記接合された層は、前記弱い結合領域および前記強い結合領域を含む；前記第 1 の接合層上で垂直に支持される第 2 の選択的に接合された層からなり、；ここにおいて、分解されたポートおよび分解されたチャネルは、前記弱い結合領域においてまたはその中で、作成される、そして、前記ポートおよびチャネルは、前記第 1 の選択的に接合された層および前記第 2 の選択的に接合された層に垂直にわたる多層微小流体素子。

【請求項 4 7】

ダイの上に形成された多層微小流体素子であって、ウェーハ上のバルク性基板；前記基板上に垂直に支持される第 1 の選択的に接合された層であって、前記接合された層は、前記弱い結合領域および前記強い結合領域を含む；前記第 1 の接合層上で垂直に支持される第 2 の選択的に接合された層からなり、；ここにおいて、分解されたポートおよび分解されたチャネルは、前記弱い結合領域においてまたはその中で、作成される；またここにおいて、前記ポートおよびチャネルは、前記第 1 の選択的に接合された層および前記第 2 の選択的に接合された層に垂直にわたり、そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される多層微小流体素子。

【請求項 4 8】

請求項 4 7 の回路であって、前記ダイがスタックを形成するためその垂直軸の周りで回転する回路。

【請求項 4 9】

垂直に集積化された回路を製造する方法であって、バルク性基板の提供ステップ；前記基板上への強い結合領域およびの弱い結合領域の選択的な作成ステップ；前記基板上への垂直に支持される第 1 の接合された半導体層の提供ステップ；前記第 1 の接合された半導体層上の半導体デバイス部の作成であって、前記半導体デバイス部は前記弱い結合領域に対応する；前記バルク性基板からの前記第 1 の半導体層の除去ステップ；および第 2 の半導体層への前記第 1 の半導体層の結合ステップからなる方法。

【請求項 5 0】

請求項 4 9 の方法であって、前記第 1 の半導体層を同様に配置された半導体素子部を有する前記第 2 の半導体層に整列配置するステップをさらに含む方法。

【請求項 5 1】

請求項 5 0 の方法であって、前記整列配置ステップは機械的な整列である方法。

【請求項 5 2】

請求項 5 0 の方法であって、前記整列配置ステップは光学的な整列である方法。

【請求項 5 3】

請求項 4 9 の方法であって、前記第 2 の半導体層上に半導体素子部を作成するステップをさらに含む方法。

【請求項 5 4】

請求項 5 3 の方法であって、前記第 2 の半導体層は、前記弱い結合領域上に半導体素子部を有する方法。

【請求項 5 5】

10

20

30

40

50

請求項 4 9 の方法であって、前記弱い結合領域に対する前記強い結合領域の領域比率は、1より大きい方法。

【請求項 5 6】

請求項 4 9 の方法であって、前記弱い結合領域に対する前記強い結合領域の結合強さの比率は、1より大きい方法。

【請求項 5 7】

請求項 4 9 の方法であって、前記第 2 の半導体層と前記第 1 の半導体層を相互接続するステップをさらに含む方法。

【請求項 5 8】

請求項 5 7 の方法であって、前記相互接続ステップは前記第 1 および前記第 2 の半導体層のエッジで実行される方法。 10

【請求項 5 9】

請求項 5 8 の方法であって、前記相互接続ステップは電気的な連結である方法。

【請求項 6 0】

請求項 5 8 の方法であって、前記相互接続ステップは光学的な連結である方法。

【請求項 6 1】

請求項 5 7 の方法であって、前記相互接続ステップは、前記半導体層を通じて垂直に実行される方法。

【請求項 6 2】

請求項 5 3 の方法であって、前記バルク性基板からの前記第 2 の半導体層の除去ステップ；および、前記第 1 の半導体層への前記第 2 の半導体層の結合ステップをさらに含む方法。 20

【請求項 6 3】

請求項 4 9 の方法であって、前記バルク性基板で垂直に支持される N 番目の半導体層の提供ステップであって、前記 N 番目の半導体層は、強い結合領域および弱い結合領域を有する；前記 N 番目の半導体層上での半導体素子部の作成ステップであって、前記半導体素子部は、前記弱い結合領域に対応する；前記バルク性基板からの前記 N 番目の半導体層の除去ステップ；および (N - 1) 番目の半導体層への前記 N 番目の半導体層の結合ステップをさらに含む方法。

【請求項 6 4】

請求項 6 3 の方法であって、能動半導体要素が前記 N 半導体層の 2 つから形成される方法。

【請求項 6 5】

請求項 4 9 の方法であって、1 つまたはそれ以上のダイを形成するため前記接合された半導体層をダイシングするステップをさらに含む方法。

【請求項 6 6】

請求項 6 5 の方法であって、前記ダイシングステップの後、前記接合された半導体層を相互接続するステップをさらに含む方法。

【請求項 6 7】

請求項 6 6 の方法であって、前記 1 つまたはそれ以上ダイの境界上にエッジコネクタ形成するステップをさらに含む方法。 40

【請求項 6 8】

請求項 6 7 の方法であって、前記エッジコネクタが個々のダイ層の健康を決定する診断導体として役立つ方法。

【請求項 6 9】

請求項 4 9 の方法であって、前記バルク性基板が埋込み酸化物層を含む方法。

【請求項 7 0】

請求項 6 9 の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

【請求項 7 1】

垂直の集積回路であって、ウェーハ上のバルク性基板；前記基板上に垂直に支持される 50

第1の選択的に接合された半導体層であって、前記接合された半導体層は、前記弱い結合領域および前記強い結合領域を含む；前記第1の接合された半導体層上で垂直に支持される第2の選択的に接合された半導体層からなり、；ここにおいて、分解された半導体素子部は、前記弱い結合領域においてまたはその中で、作成される、そして、前記半導体素子部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたる集積回路。

【請求項 7 2】

ダイの上に形成された垂直の集積回路であって、ウェーハ上のバルク性基板；前記基板上に垂直に支持される第1の選択的に接合された半導体層であって、前記接合された半導体層は、前記弱い結合領域および前記強い結合領域を含む；前記第1の接合された半導体層上で垂直に支持される第2の選択的に接合された半導体層；ここにおいて、半導体素子部は、前記弱い結合領域においてまたはその中で、作成される、またここで、前記半導体素子部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたり、そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される集積回路。

【請求項 7 3】

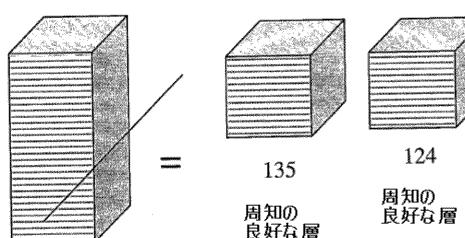

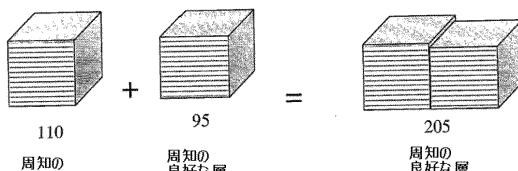

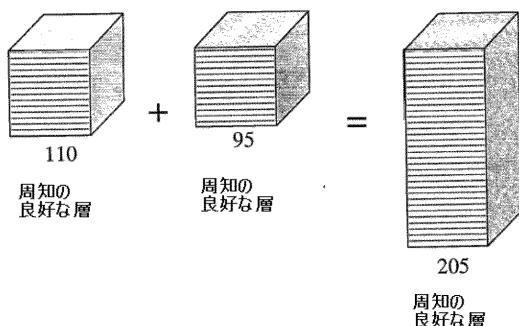

所定の装置の生産イールドを増加させる方法であって、前記装置は1つまたはそれ以上の多層ダイからなり、前記多層ダイの各々の機能している層の数を診断により決定するステップ；および、前記機能している層の数に基づいた前記多層ダイの各々をソートするステップからなる方法。

【請求項 7 4】

請求項73の方法であって、前記多層ダイの2つまたはそれ以上の結合をさらに含み、前記多層ダイの各々の機能している層が互いに相互連結する方法。

【請求項 7 5】

請求項73の方法であって、前記決定ステップは、1つまたはそれ以上の前記多層ダイのエッジ相互接続の試験によって実行される方法。

【請求項 7 6】

請求項74の方法であって、前記結合ステップは、2つまたはそれ以上のダイの垂直のスタッキングからなる方法。

【請求項 7 7】

請求項74の方法であって、前記結合ステップは、2つまたはそれ以上のダイのエッジのスタッキングからなる方法。

【請求項 7 8】

請求項73の方法であって、1つまたはそれ以上の層または1つまたはそれ以上の層の一部の上に前記多層ダイの各々と関連する健康データの格納をさらに含む方法。

【請求項 7 9】

請求項78の方法であって、前記健康データは、前記多層ダイの各々の上の周知の良好な層または周知の不良層の表示からなる方法。

【請求項 8 0】

請求項73の方法であって、前記少なくとも1つの前記多層ダイは基板で垂直に支えられる第1の選択的に接合された半導体層であって、前記接合された半導体層は、前記弱い結合領域および前記強い結合領域を含み；前記第1の接合された半導体層上で垂直に支持される第2の選択的に接合された半導体層からなり、；ここにおいて、半導体素子部は、前記弱い結合領域においてまたはその中で作成され、またここで、前記半導体素子部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたり、そして、前記ダイは前記接合された半導体層をダイシングすることによって形成される方法。

【請求項 8 1】

少なくとも所定数の周知の良好な層を有する素子を提供する方法において、前記装置は1つまたはそれ以上の多層ダイから構成される方法であって、

10

20

30

40

50

前記多層ダイの各々の機能している層の数の診断による決定ステップ；

複数のピンへの前記機能している層の数に基づいた前記多層ダイの各々のソートステップであって、各々のピンは、関連する最小の数の周知の良好な層を有し、；

および、前記所定数の周知の良好な層と少なくとも等しい関連する最小の数の周知の良好な層を有する前記ピンの1つから前記所定数の周知の良好な層を有する前記多層ダイの1つの選択ステップからなる方法。

【請求項 8 2】

請求項 8 1 の方法であって、前記少なくとも1つの前記多層ダイは、基板で垂直に支えられる第1の選択的に接合された半導体層であって、前記接合された半導体層は、前記弱い結合領域および前記強い結合領域を含み、；前記第1の接合された半導体層上で垂直に支持される第2の選択的に接合された半導体層からなり、；ここにおいて、半導体素子部は、前記弱い結合領域においてまたはその中で、作成される、またここで、前記半導体素子部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたり、；そして前記ダイは、前記接合された半導体層をダイシングすることによって形成される方法。

【請求項 8 3】

少なくとも所定数の周知の良好な層を有する素子を提供する方法において、前記装置は1つまたはそれ以上の多層ダイから構成される方法であって、前記多層ダイの各々の機能している層の数の診断による決定ステップ；複数のピンへの前記機能している層の数に基づいた前記多層ダイの各々のソートステップであって、各々のピンは、関連する最小の数の周知の良好な層を有し、；前記所定数の周知の良好な層と少なくとも等しい周知の良好な層の合計を有する前記複数の多層ダイの選択ステップ；および、少なくとも前記所定数の周知の良好な層に等しい周知の良好な層数を有する結合されたダイを形成するため、前記選択された複数の多層ダイの結合ステップからなる方法。

【請求項 8 4】

請求項 8 3 の方法であって、前記選択された複数の多層ダイは、水平に結合され、前記選択された複数の多層ダイの各々の上の1つまたはそれ以上のエッジ相互接続を通じて相互に連結する方法。

【請求項 8 5】

請求項 8 3 の方法であって、前記選択された複数の多層ダイは、垂直に結合される方法。

【請求項 8 6】

請求項 8 3 の方法であって、前記少なくとも1つの前記多層ダイは、基板で垂直に支えられる第1の選択的に接合された半導体層からなり、前記接合された半導体層は、弱い結合領域および強い結合領域を含み；前記第1の選択的に接合された半導体層で、垂直に支えられる第2の選択的に接合された半導体層からなり；ここにおいて、半導体素子部は、前記弱い結合領域においてまたはその中で、作成される、またここで、前記半導体素子部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたり、；そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される方法。

【請求項 8 7】

少なくとも所定数の周知の良好な層を有する素子を提供する方法において、前記装置は1つまたはそれ以上の多層ダイから構成される方法であって、前記多層ダイの各々の機能している層の数の診断による決定ステップ；複数のピンへの前記機能している層の数に基づいた前記多層ダイの各々のソートステップであって、各々のピンは、関連する最小の数の周知の良好な層を有し、；前記所定数の周知の良好な層よりも大きい周知の良好な層数の前記多層ダイの1つの選択ステップ；少なくとも前記所定数の周知の良好な層および第2の多層ダイ部に等しい周知の良好な層数を有する第1の多層ダイを形成するため、前記選択された複数の多層ダイのスライシングステップ；および、前記第2の多層ダイ部の周知の良好な層数に対応する最小数の周知の良好な層を有する前記ピンの1つへの前記

10

20

30

40

50

第 2 の多層ダイ部のソートステップからなる方法。

【請求項 8 8】

請求項 8 7 の方法であって、前記スライシングは、前記選択された多層ダイの周知の不良層で発生する方法。

【請求項 8 9】

請求項 8 7 の方法であって、前記少なくとも 1 つの前記多層ダイが、基板で垂直に支えられる第 1 の選択的に接合された半導体層であって、前記接合された半導体層は、弱い結合領域および強い結合領域を含み；前記第 1 の選択的に接合された半導体層で、垂直に支えられる第 2 の選択的に接合された半導体層からなり；ここにおいて、半導体素子部は、前記弱い結合領域においてまたはその中で、作成される、またここで、前記半導体素子部は、前記第 1 の選択的に接合された半導体層および前記第 2 の選択的に接合された半導体層に垂直にわたり、；そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される方法。10

【請求項 9 0】

複数のウェーハ・スタックをソートする方法において、前記ウェーハ・スタックの各々は、複数の垂直に集積化された装置からなる方法であって、ウェーハ上の 1 つまたはすべての素子の診断の実行；および、どれくらい前記ウェーハ・スタックの（続いてダイシングされる）垂直に集積された素子が所定数の周知の良好な層を有するかに基づいた前記ウェーハ・スタックのソートからなる方法。

【請求項 9 1】

複数のウェーハ・スタックをソートする方法において、前記ウェーハ・スタックの各々は、複数の垂直に集積化された装置からなる方法であって、ウェーハ上の 1 つまたはすべての素子の診断の実行；および、前記ウェーハ・スタックに配置される素子のすべての周知の良好な層の最小の数に基づいた前記ウェーハ・スタックのソートからなる方法。20

【請求項 9 2】

垂直に集積化された回路を製造する方法であって、バルク性基板の提供ステップであって、前記バルク性基板は、埋込み酸化物層を含み；前記基板上での弱い結合領域および強い結合領域の選択的な作成ステップ；前記基板で垂直に支えられる第 1 の接合された半導体層の提供ステップ；前記第 1 の接合された半導体層での半導体素子部の作成ステップであって、前記半導体素子部は、前記弱い結合領域に対応する；前記バルク性基板からの前記第 1 の半導体層の除去ステップ；および、前記第 1 の半導体層と前記第 2 の半導体層との接合ステップからなる方法。30

【請求項 9 3】

請求項 9 2 の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

【請求項 9 4】

請求項 9 3 の方法であって、前記埋込み酸化物層が酸素注入によって形成される方法。

【請求項 9 5】

垂直に集積化された回路を製造する方法であって、バルク性基板の提供ステップ；前記基板上での強い結合領域および弱い結合領域の選択的な作成ステップ；前記基板で垂直に支えられる第 1 の接合された半導体層の提供ステップ；前記第 1 の接合された半導体層での半導体素子部の作成ステップであって、前記半導体素子部は、前記弱い結合領域に対応する；前記第 1 の半導体層と前記バルク性基板と間の界面で埋込み酸化物層を形成ステップ；前記バルク性基板からの前記第 1 の半導体層の除去ステップ；および、前記第 1 の半導体層と前記第 2 の半導体層との接合ステップからなる方法。40

【請求項 9 6】

請求項 9 5 の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

【請求項 9 7】

垂直の微小電気機械装置を製造する方法であって、バルク性基板の提供ステップで、前50

記バルク性基板は埋込み酸化物層を含み；前記基板上での強い結合領域および弱い結合領域の選択的な作成ステップ；前記基板で垂直に支えられる第1の接合された半導体層の提供ステップ；前記第1の接合された半導体層での電極の作成ステップであって、前記電極は、前記弱い結合領域に対応する；前記電極の反対側に配置された作動可能な要素の作成ステップ；前記バルク性基板からの前記第1の半導体層の除去ステップ；および、前記第1の半導体層と前記第2の半導体層との接合ステップからなる方法。

**【請求項 9 8】**

請求項97の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

**【請求項 9 9】**

垂直の微小電気機械装置を製造する方法であって、バルク性基板の提供ステップで、前記バルク性基板は埋込み酸化物層を含み；前記基板上での強い結合領域および弱い結合領域の選択的な作成ステップ；前記基板で垂直に支えられる第1の接合された半導体層の提供ステップ；前記第1の接合された半導体層での電極の作成ステップであって、前記電極は、前記弱い結合領域に対応する；前記電極の反対側に配置された作動可能な要素の作成ステップ；前記第1の半導体層と前記バルク性基板との間の界面での埋込み酸化物層の形成ステップ；前記バルク性基板からの前記第1の半導体層の除去ステップ；および、前記第1の半導体層と前記第2の半導体層との接合ステップからなる方法。

**【請求項 1 0 0】**

請求項99の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

**【請求項 1 0 1】**

多層微小流体素子を製造する方法であって、バルク性基板の提供ステップで、前記バルク性基板は埋込み酸化物層を含み；前記基板上での強い結合領域および弱い結合領域の選択的な作成ステップ；前記基板で垂直に支えられる第1の接合された層の提供ステップ；前記第1の接合された層でのポートの作成ステップであって、前記ポートは、前記弱い結合領域に対応する；前記ポートに機械的に連結するチャネルの作成ステップ；前記バルク性基板からの前記第1の層の除去ステップ；および、前記第1の層と前記第2の層との接合ステップからなる方法。

**【請求項 1 0 2】**

請求項101の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

**【請求項 1 0 3】**

多層微小流体素子を製造する方法であって、バルク性基板の提供ステップ；前記基板上での強い結合領域および弱い結合領域の選択的な作成ステップ；前記基板で垂直に支えられる第1の接合された層の提供ステップ；前記第1の接合された層と前記バルク性基板との間の前記界面での埋込み酸化物層の形成ステップ；前記第1の接合された層でのポートの作成ステップであって、前記ポートは、前記弱い結合領域に対応する；前記ポートに機械的に連結するチャネルの作成ステップ；前記バルク性基板からの前記第1の層の除去ステップ；および、前記第1の層と前記第2の層との接合ステップからなる方法。

**【請求項 1 0 4】**

請求項103の方法であって、前記埋込み酸化物層がイオン注入によって形成される方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

**関連出願の相互参照**

本出願は、米国特許法119(e)の下で、本願明細書において参照されたものとする

10

20

30

40

50

2002年11月20日に出願の暫定的な米国出願番号第60/428,125号の利益を請求する。

#### 【0002】

この発明は、基板上に多層能動素子を製造するための方法およびシステムに関し、特に、基板上の垂直の集積回路、微小電気機械装置、および、微小流体素子の製造に関する。 10

#### 【背景技術】

#### 【0003】

より高速かつより安価な集積回路の需要は、ますます増大している。ムーアの法則は、平方インチごとのトランジスタの数は毎年2倍になると断定する。しかしながら、従来の二次元の（または平らな）チップ製造方法がその限界に達しているので、ムーアの法則の予言を成し遂げるために、チップ製造の新領域を広げるためのより革新的な技術が必要である。 10

#### 【0004】

これまで、より密度の高い集積回路を求める大部分の要求は、比較的平らな構造上に製造される縮小する能動素子によって応じられた。すなわち、二次元のチップ製造は半導体製造の支配的な方法であった。大部分の半導体（訳注\*1）素子は、平らは単結晶の半導体基板において造られてきた。 20

#### 【0005】

この方法は、第三次元への非常に制限された垂直の集積化のみを許容する。 20

二次元のチップ製造の限界が近づいているので、性能における大きな進展は、三次元のチップ製造（すなわちZ次元のチップ製造）から派生する。 20

#### 【0006】

同じパッケージへのマイクロデバイスの垂直統合またはスタッキングは、荷造り量を減少させる、回路密度を増加させかつ基盤スペースを節約する、性能および機能を増加させるための魅力的な方法である。内部チップ遅延および消費電力の減少は、両方ともスタックされた集積における利益である。素子が薄くなりかつ互いの上に積み重なる場合、費用および回路密度における利点は潜在的に莫大である。集積回路および微小電気機械のプロセスのため、シリコン・ウェーハの第三次元は、主に未開発のままである。 30

#### 【0007】

二次元の装置の垂直のスタッキングへの現行の商用アプローチは、概してチップ・スケールであって、研磨によるウェーハの薄層化に依存する。大部分の方法は、貫通孔を通じたまたはワイヤ接着の積み重なったマザー ドウターチップの相互接続に依存する。 30

現行の方法はすべて、パッケージ・サイズ、費用、信頼性およびイールド・インパクトに関する限界を有する。前記の問題点にもかかわらず、三次元集積化を達成するスタッキング装置は、微小電気機械システム「MEMS」と特定用途向けIC「ASIC」コントローラとの結合において特に、応用対象を見つけている。個々のチップのスタッキングにより作成される高密度メモリー・パッケージは、専門の応用対象を見つけた。 40

#### 【0008】

IBMの米国特許NO.6,355,501は、三次元集積回路アセンブリ、概してオンチップ・スケールを製造する方法を開示する。その中に開示されているのは、三次元のスタッキングされたシリコンオンインシュレータ「SOI」チップからなるアセンブリ、およびこのような集積回路アセンブリを形成する方法である。SOIチップの各々は、半導体デバイスに電気的な接触させる第1のメタライゼーション・パターンへ機械的な接触をさせるハンドラを含む。金属化パターン（訳注\*2）は、順番に、半導体デバイスの対向する表面上に配置される第2のメタライゼーション・パターンに接触する。 40

#### 【0009】

開示された方法は、以下のステップを含む：

a) 基板の第1の表面上に第3の金属化パターンを有する基板の提供； b) SOIチップの第2のメタライゼーション・パターンを基板の第3の金属化パターンと電気接觸させることによる、基板の第1の表面上へのSOIチップのうちの1つの整列配置； c) SOI 50

チップからのハンドラの除去、および、S O Iチップの第1のメタライゼーション・パターンの露出；d) 第1のS O Iチップの露出された第1のメタライゼーション・パターンを第2のS O Iチップの第2のメタライゼーション・パターンと電気接触させることによる、第2のS O Iチップの1つの第1のS O Iチップとの整列配置；およびe) 他方の上に以降のS O Iチップを取付けるため、ステップc) およびd) の繰返し。

#### 【0010】

しかしながら、この参照は、極端に高価でかつ別々に機能上制限されるかもしれない方法を教示する。

#### 【0011】

上述した米国特許N O . 6 , 3 3 5 , 5 0 1において教示される方法の主要な不都合は、その出願人は、三次元回路をウェーハ・スケール上に形成することは低イールドにつながることを強調していることである。さらに、各々のチップの整列は、ウェーハ・スケールのスタッキングを妨げる本質的な問題であると考えられる。各々のチップのスタッキングステップは、互いに結合される層の整列を含む。透明な接着材、および、ウインドウは、互いに結合される両方の表面上の整列マークへの光学アクセスを可能にするために提供されなければならない。

#### 【0012】

さらに、ハンドラは整列マークに透過的でなければならない。他の不都合は、連続して起こる繰返されたプロセスのステップの数に関する。その中に記載されたように、スタッカされた層の間で電気接触（訳注\*3）させるため、それがスタッカされ、かつ、整列配置される場合、ハンダ・リフロー・ステップが各々の層の間で実行される。リフローの後、チップ・スタッカは、端で結合される。その上、ハンドラは、（レーザーまたは他の加熱によって）接着剤除去剤により除去され、研磨されなければならず、次の層の前の他の準備ステップは、結合されることができる。最後に、過剰基板は、研磨される、または、それでなければ除去のためエッチバックされる。

#### 【0013】

これらの欠点は、費用および機能に関連したいくつかの不都合を導く。費用損失は、研磨削除；多数の連続して起こるステップ；ウェーハ・スケールスタッキングに対するチップ・スケール。ここにおいて、ウェーハ・スケールは費用を減少させることは公知である；ウェーハ・スケール上に発生するイールドを克服の不可能性、したがってチップ・スケールへの逆戻り；層の数の限定、したがって、より高い数のスタッカを形成するため、スタッカは、他のスタッキングの上に積み重ならなければならない；連続して起こる統計学的に依存している数は相互接続によるので、全体のイールドは減少する；多数のリフロー・ステップは、潜在的に他の層にダメージを与える；点について見出される。機能上の欠点は、診断の欠如；相互接続汎用性の欠如；相互接続のための限られたスペース；大きいスタッカ（特にメモリー・スタッカ）の限られたアドレス指定能力；ノイズ・シールドを集積化する能力の欠如；熱散逸を集積化する能力の欠如；接地面の能力の欠如；層の数の限定；を含む。

#### 【0014】

三次元パッケージングの実施は、アーヴィンセンサ社、カリフォルニア大学アーヴィン校、およびI B Mによって行われた。不連続なダイは、スタッカされ、端剥離プロセスを利用して相互接続された。周知の良好なダイ（K G D）は、薄くされる。ダイエッジのはんだパンプは、スタッカされたダイを整列配置しつつ相互接続するために使用される。ダイは、エポキシ・マトリックスにおいて詰められる。

#### 【0015】

エポキシは、異なるサイズのダイの整列配置を補助し、かつ、相互接続表面として使用される。個々のダイのスタッキングおよび相互接続は、K G Dのための必要条件とともに、非常に費用のかかる製造方法になる。

#### 【0016】

三次元パッケージングの他の実施は、ウェーハ全体のポリイミドの絶縁層上に堆積する

10

20

30

40

50

金の相互接続トレースを適用することにより、高密度のスタックメモリーモジュールを製造するキュービックメモリーによって行われた。

【0017】

しかしながら、スタッキングおよび垂直の相互接続は、個々のチップ・スケールにおいて生じる。

【0018】

三次元パッケージングのさらなる実施は、マイクロボール・グリッドアレイ結合経由で可撓性基体上にチップを取り付け、そしてチップが搭載されたテープをそれ自体の上へZ折りすることにより、チップ・スケール、スタックパッケージを発展させるため、インテルと提携して、カリフォルニア州サンノゼのテセラ社によって行われた。

10

【0019】

ジプトニクス社は、明らかに集積回路のウェーハスケールスタックを開発している。整列、応力管理、熱的な管理、高密度相互接続、および、イールドでの少なからぬ挑戦は、依然として対処されている。

【0020】

上で示されたように、利用可能な垂直の集積化について様々な欠如がある。1つの主要な欠如は、イールド損失による。現在市場にあるスタッキング装置へのすべてのアプローチは、ダイ・スケールである。個々のダイは、準備され、整列配置され、スタックされ、かつ、結合される。処理は費用がかり、スタックのためのイールド損失は、層における各々の素子のための混合されたイールド損失である。増加するイールド損失は、S R A Mスタックのような安価な装置のために時折許容される。しかし、より費用のかかる素子がスタックされる場合、解決案は、周知の良好なダイ（K G D）を使用することである。K G Dのために、各々のパッケージされないダイは、バーンインおよび試験を受ける。さらに、スタックは各々の層の完成後、電気的試験を必要とする。そのプロセスは非常に費用がかかり、応用対象は、軍隊および衛星技術のような上等のエンドユーザに限られた。

20

【0021】

従来の垂直の集積化の他の欠如は、技術がダイ・スケールに限られるという事実のためである。ジプトニクス社の未到達のマーケットアプローチを除いては、スタッキング装置へのすべてのアプローチは、ダイ・スケールにある。ウェーハ・スケール製造の本質的な経済利点は、これらの技術には完全に利用できない。個々のダイの出荷および試験にかかる高費用は、これらの方法を最高級の応用対象に制限する。

30

【0022】

従来の製造工程成形回路の全体にわたって公知である他の問題は、基板上の処理装置を支持する必要があることである。処理中、基板は機械的な支持および耐熱性の提供を必要とする。被処理基板はしたがって、化学的およびエネルギー露出と同様に高圧および高温を含む苛酷な処理環境に耐えるために十分に厚くなければならない。存続可能な薄膜デバイスが求められる場合、さらなる処理はしたがって、必要である。

【0023】

回路または他の構造が処理に耐えるために十分に厚い基板の上に形成された後、保証される1つの処理方法は、機械的な方法により基板の層厚を除去することである。切削または研磨のようなこれらの機械的な方法は、おびただしい量の材料および労働を浪費する。切削または研磨された材料は、しばしばリサイクルできず、または、それがリサイクル可能な場合であっても、材料は再利用の前にさらなる処理を受けなければならない。さらに、薄くされる基板は、表面を滑らかにするために概して研磨加工または他のプロセスを受けさせられる。他の技術は、装置製造の前に基板上へのエッチストップ層の形成を含む。しかしながら、基板はまだ典型的に、エッチストップ層に概して基板にエッチングする選択エッチング・ステップの前に研磨される、またはそうでなければ機械的に除去される。これらの技術のすべてでは、品質管理懸念を示すと同様に、結果として時間および材料の浪費になる。

40

【0024】

50

薄膜デバイスを形成する他の技術は、イオン注入法を利用することである。イオン注入の一般的な使用は、概して半導体材料の薄膜層を導くことである。

#### 【0025】

このような方法は、例えば、両方とも「水素イオン注入分離方法によるS O I ウェーハの製造方法、および、前記方法により製造されたS O I ウェーハ」の名称で、両方とも本願明細書において参照に組み込まれたE P 0 1 0 4 5 4 4 8 およびW O 0 0 / 0 2 4 0 5 9において開示される。特に、水素イオンまたはヘリウム・イオンのようなイオンは、酸化されたシリコン・ウェーハの上面に注入される。イオンは、上面内の深さに注入される。その後で、概して約500 を超える高温処理を受けさせられるバルクシリコン基板から薄膜層は剥離されることができる。この薄膜層は、それから絶縁体層および基板に支持されることができ、マイクロエレクトロニクスまたは他の構造がその上に形成されることがある。マイクロエレクトロニクスは、しかしながら、イオン注入が不利益にマイクロエレクトロニクスに影響を及ぼすので、薄膜層の剥離に続いて形成されなければならない。

特に、薄膜層はゆがめられ、素子はイオン注入によってダメージを受ける可能性がある、または、素子は層間剥離の間、ダメージを受ける可能性がある。

#### 【0026】

ブリュエルほかによるW O 9 8 / 3 3 2 0 9 名称「被保護イオン領域からなり、かつ、イオン注入を含む、特定の半導体において薄膜を得る方法」は、金属酸化物半導体「M O S」を含んでいる薄膜を提供する方法を開示する。一般に、M O Sトランジスタは半導体基板の表面の上に形成される。トランジスタの領域はマスキングされ、囲む領域は、破面の意図された線を定義するためにイオン注入される（すなわちここで、微小気泡はイオン注入ステップから展開する）。その上にトランジスタを有する薄膜を分離するため、劈開は微小気泡の近くで破面の意図された線で始まり、およびトランジスタの下の結晶面で伝播する（すなわちここで、微小気泡は存在しない）。

#### 【0027】

W O 9 8 / 3 3 2 0 9 の教示を使用したトランジスタをその上に有する薄膜を実現することは可能である一方、基板材料の結晶構造はトランジスタのすぐ近くで破碎されなければならないので、トランジスタは、劈開伝播の望ましくない応力を受けさせられる。

#### 【0028】

アスパルほかの米国特許N o . 6 , 1 0 3 , 5 9 7 名称「半導体材料の薄膜を得る方法」は、その中にマイクロエレクトロニクスまたは他の構造を有する薄膜基板にイオン衝撃を受けさせることを概して教示する。気体の微小気泡はしたがって、薄膜の層厚を定義するその中の深さに形成される。しかしながら、基板の上に形成されることがあるマイクロエレクトロニクスおよび構造の多くのタイプは、要素に与えられたダメージまたは他の欠陥を修復するため、続いて起こるアニールステップを必要とする。

#### 【0029】

その後で、薄膜層は、微小気泡の線に沿って破面を生じる熱的な処理によって、下側基板材料と分離可能であることが教示される。

#### 【0030】

サカグチほかによる米国特許N o . 6 , 2 2 1 , 7 3 8 名称「基板およびその製造方法」、および、N O . 6 , 1 0 0 , 1 6 6 名称「半導体製品を生じるためのプロセス」は、両方とも本願明細書において参照され、多孔性半導体層への基板の結合を教示する。

#### 【0031】

多孔質層の結合は、機械的により弱くなると教示され、したがって、外部の力の適用による削除が容易になる。米国特許N o . 6 , 1 0 0 , 1 6 6 は、剥脱方向における力によって層が除去できることを教示する。しかしながら、これらの参照の両方は、層の間の全体の界面における弱い多孔性分離メカニズムの使用を開示する。これは、中間構造および多孔性半導体材料上に形成されたいかなる半導体デバイスもの全体の機械的保全性を損なう可能性がある。

10

20

30

40

50

**【 0 0 3 2 】**

本願明細書において参照されたものとするヘンリーほかによる米国特許N o . 6 , 1 8 4 , 1 1 1 名称「半導体前処理注入および後処理フィルム分離」は、シリコン水表面の下の選択された深さにおける応力を加えられた層の使用を開示する。素子は、応力を加えられた層より上に形成される。注入は、ウェーハの直径を横切る異なる適用量で同じエネルギー・レベルにおいて概して実行される。制御劈開伝播は、その上にいかなる素子も含む応力を加えられた層より上で層を分離するために開始される。応力を加えられた層を形成するための処理がその上に形成される素子にダメージを与え、したがって、続いて起こる修理アニールが典型的に必要とされることを強調される。それゆえに、マイクロエレクトロニクスまたは他の構造をその上に含む薄膜は、薄い半導体に反りまたは他のダメージなくイオン注入されることができないという点で、従来のイオン注入および層間剥離方法は不足している。

**【 0 0 3 3 】**

したがって、現在の回路プロセスの欠如を考慮すると、従来の方法の欠点および欠点を回避するように、チップまたはウェーハ・スケールに、三次元集積回路を提供することが望ましい。

**【 0 0 3 4 】**

ゆえに、主要な本発明の目的は、低コストの三次元集積回路を提供することである。本発明の別の目的は、役に立つ素子の製造のために多層をなした基板を提供することである。

**【 0 0 3 5 】**

本発明の追加的な目的は、垂直に集積化された素子のための生産イールドを増加させる方法およびシステムを提供することである。

本発明のさらに別の目的は、垂直に集積化された素子の分類方法およびシステムを提供することである。

**【 0 0 3 6 】**

以下の記載が添付の図面とともに読まれる場合、本発明の上記のおよび他の目的および利点はより直ちに明らかになる。

**【 発明の開示 】****【 0 0 3 7 】**

本発明のいくつかの方法および装置によって、従来技術の上記の検討された問題、その他問題および欠如は、克服または軽減され、かつ、本発明の目的は達成される。

**【 0 0 3 8 】**

一態様において、本発明は垂直の微小電気機械装置を製造する方法である。そして、この方法は、バルク性基板を提供するステップ；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合半導体層を提供するステップ；前記第1の接合半導体層上の電極を作成するステップ。前記電極前記弱い結合領域に対応する；前記電極の反対側に配置した作動可能な要素を作成するステップ；前記バルク性基板から前記第1の半導体層を除去するステップ；および、前記第1の半導体層を第2の半導体層に接合するステップ；からなる。

**【 0 0 3 9 】**

別の態様においては、本発明は、以下の構成からなる垂直のMEMS装置である：ウェーハ上のバルク性基板；前記基板に垂直に支持される第1の選択的に接合された半導体層。前記接合半導体層は、弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された半導体層に垂直に支持される第2の選択的に接合された半導体層；ここにおいて、電極および作動可能な要素は、前記弱い結合領域に、またはその中に作成される；またここにおいて、前記電極および前記作動可能な要素は、互いの反対側に配置されて、そして、前記電極および作動可能な要素は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたる；。

**【 0 0 4 0 】**

10

20

30

40

50

また別の態様においては、本発明は、以下の構成からなるダイの上に形成された垂直のMEMS装置である：ウェーハ上のバルク性基板；前記基板に垂直に支持される第1の選択的に接合された半導体層。前記接合半導体層は、弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された半導体層に垂直に支持される第2の選択的に接合された半導体層；ここにおいて、要素および作動可能な要素は、前記弱い結合領域に、またはその中に作成される；またここにおいて、前記要素および前記作動可能な要素は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたる。そして、前記ダイは、前記接合半導体層をダイシングすることによって形成される；

さらに別の態様においては、本発明は多層微小流体素子を製造する方法であり、その方法は、バルク性基板を提供するステップ；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合層を提供するステップ；前記第1の接合層上にポートを作成するステップ。前記ポートは、前記弱い結合領域に対応する；前記ポートに機械的に連結するチャネルを作成するステップ；前記バルク性基板から前記第1の層を除去するステップ；および第2の層に前記第1の層を結合するステップ；からなる。

#### 【0041】

別の態様においては、本発明は、以下の構成からなる多層微小流体素子である：ウェーハ上のバルク性基板；前記基板に垂直に支持される第1の選択的に接合された層。前記接合層は、弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された層に垂直に支持された第2の選択的に接合された層；ここにおいて、分解されたポートおよび分解されたチャネルは、前記弱い結合領域で、または、その中で作成される。そして、前記ポートおよびチャネルは、前記第1の選択的に接合された層および前記第2の選択的に接合された層に垂直にわたる。

#### 【0042】

また別の態様においては、本発明は、以下の構成からなるダイの上に形成された多層微小流体素子である；ウェーハ上のバルク性基板；前記基板に垂直に支持される第1の選択的に接合された層。前記接合層は、弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された層に垂直に支持された第2の選択的に接合された層；ここにおいて、分解されたポートおよび分解されたチャネルは、前記弱い結合領域で、または、その中で作成される。またここにおいて、前記ポートおよびチャネルは、前記第1の選択的に接合された層および前記第2の選択的に接合された層に垂直にわたる。そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される；

さらに別の態様においては、本発明は垂直に集積化された回路を製造する方法である。その方法は、バルク性基板を提供するステップ；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合半導体層を提供するステップ；前記第1の接合半導体層上に半導体デバイス部を作成するステップ。前記半導体デバイス部は、前記弱い結合領域に対応する；前記バルク性基板から前記第1の半導体層を除去するステップ；および第2の半導体層に前記第1の半導体層を結合するステップ；からなる。

#### 【0043】

別の態様においては、本発明は以下の構成からなる垂直の集積回路である：ウェーハ上のバルク性基板；前記基板に垂直に支持される第1の選択的に接合された半導体層。前記接合された半導体層は、弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された半導体層に垂直に支持された第2の選択的に接合された半導体層；ここにおいて、半導体デバイス部は、前記弱い結合領域で、または、その中で作成される。またここにおいて、前記半導体デバイス部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたる；

また別の態様においては、本発明は、以下の構成からなるダイの上に形成された垂直の集積回路である：ウェーハ上のバルク性基板；前記基板に垂直に支持される第1の選択的

10

20

30

40

50

に接合された半導体層。前記接合された半導体層は、弱い結合領域および強い結合領域を含む；前記第1の選択的に接合された半導体層に垂直に支持された第2の選択的に接合された半導体層；ここにおいて、半導体デバイス部は、前記弱い結合領域で、または、その中で作成される。またここにおいて、前記半導体デバイス部は、前記第1の選択的に接合された半導体層および前記第2の選択的に接合された半導体層に垂直にわたる。そして、前記ダイは、前記接合された半導体層をダイシングすることによって形成される；

さらに別の態様においては、本発明は、所定の装置の生産イールドを増加させる方法であり、前記装置は、1つまたはそれ以上の多層ダイからなる。前記方法は、各々の前記多層ダイの各々の機能している層の数を診断によって決定するステップ；および前記機能している層の数に基づいて前記多層ダイの各々を分類するステップ；からなる。

10

#### 【0044】

別の態様においては、本発明は、少なくとも所定数の周知の良好な層を有する素子を提供する方法であり、前記素子は、1つまたはそれ以上の多層ダイからなる。前記方法は、各々の前記多層ダイの各々の機能している層の数を診断によって決定するステップ；および前記機能している層の数に基づいて前記多層ダイの各々を複数のビンに分類するステップ。各々のビンは周知の良好な層の関連する最小の数を有する；および、前記所定の数の周知の良好な層と少なくとも等しい周知の良好な層の関連する最小の数を有する前記ビンの1つから前記所定の数の周知の良好な層を有する前記多層ダイのうちの1つを選択するステップ；からなる。

#### 【0045】

別の態様においては、本発明は、少なくとも所定数の周知の良好な層を有する素子を提供する方法であり、前記素子は、1つまたはそれ以上の多層ダイからなる。前記方法は、各々の前記多層ダイの各々の機能している層の数を診断によって決定するステップ；および前記機能している層の数に基づいて前記多層ダイの各々を複数のビンに分類するステップ。各々のビンは周知の良好な層の関連する最小の数を有する；前記所定の数の周知の良好な層と少なくとも等しい周知の良好な層の合計を有する複数の前記多層ダイを選択するステップ；および、前記所定の数の周知の良好な層と少なくとも等しい周知の良好な層の数を有する結合されたダイを形成するため、前記選択された複数の多層ダイを結合するステップからなる。

20

#### 【0046】

また別の態様においては、本発明は、少なくとも所定数の周知の良好な層を有する素子を提供する方法であり、前記素子は、1つまたはそれ以上の多層ダイからなる。前記方法は、各々の前記多層ダイの各々の機能している層の数を診断によって決定するステップ；および前記機能している層の数に基づいて前記多層ダイの各々を複数のビンに分類するステップ。各々のビンは周知の良好な層の関連する最小の数を有する；前記所定の数の周知の良好な層よりも大きい数の周知の良好な層を有する（訳注\*4）多層ダイの1つを選択するステップ；前記所定の数の周知の良好な層と少なくとも等しい周知の良好な層の数を有する第1の多層ダイ部および第2の多層ダイ部を形成するため、前記選択された多層ダイをスライシングするステップ；および、前記第2の多層ダイ部の周知の良好な層の数に対応する最小の数の周知の良好な層を有する前記ビンの1つに前記第2の多層ダイ部を分類するステップ；からなる。

30

#### 【0047】

さらに別の態様においては、本発明は、複数のウェーハ・スタックを分類する方法であり、前記ウェーハ・スタックの各々は、以下のステップからなる複数の垂直に集積化された素子からなる。ウェーハ上の1つまたはすべての素子の診断を実行するステップ；およびいくつのウェーハ・スタックの垂直集積化素子（後にダイシングされるために）が、所定の数の周知の良好な層を有するかに基づいて、ウェーハ・スタックを分類するステップ；。

別の態様においては、本発明は、複数のウェーハ・スタックを分類する方法であり、前記ウェーハ・スタックの各々は、以下のステップからなる複数の垂直に集積化された素子か

40

50

らなる。ウェーハ上の1つまたはすべての素子の診断を実行するステップ；および、ウェーハ・スタックに配置されるすべての素子の周知の良好な層の最小の数に基づいて、ウェーハ・スタックを分類するステップ；。

【0048】

また別の態様においては、本発明は垂直に集積化された回路を製造する方法であり、その方法は、以下のステップからなる：バルク性基板を提供するステップ。前記バルク性基板は、埋設酸化物層を含む；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合された半導体層を提供するステップ；前記第1の接合された半導体層上に半導体デバイス部を作成するステップ。前記半導体デバイス部は、前記弱い結合領域に対応する；前記バルク性基板から前記第1の半導体層を除去するステップ；および、第2の半導体層に前記第1の半導体層を接合するステップ；。

10

【0049】

さらに別の態様においては、本発明は垂直に集積化された回路を製造する方法であり、その方法は、以下のステップからなる：バルク性基板を提供するステップ；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合された半導体層を提供するステップ；前記第1の接合された半導体層上に半導体デバイス部を作成するステップ。前記半導体デバイス部は、前記弱い結合領域に対応する；前記第1の半導体層と前記バルク性基板との間の界面で埋設酸化物層を形成するステップ；前記バルク性基板から前記第1の半導体層を除去するステップ；および、第2の半導体層に前記第1の半導体層を接合するステップ；。

20

【0050】

別の態様においては、本発明は垂直な微小電気機械装置を製造する方法であり、その方法は、以下のステップからなる：バルク性基板を提供するステップ。前記バルク性基板は、埋設酸化物層を含む；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合された半導体層を提供するステップ；前記第1の接合された半導体層上に電極を作成するステップ。前記電極は、前記弱い結合領域に対応する；前記電極の反対側に配置された作動可能な要素を作成するステップ；前記バルク性基板から前記第1の半導体層を除去するステップ；および、第2の半導体層に前記第1の半導体層を接合するステップ；。

30

【0051】

また別の態様においては、本発明は垂直な微小電気機械装置を製造する方法であり、その方法は、以下のステップからなる：バルク性基板を提供するステップ。前記バルク性基板は、埋設酸化物層を含む；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合された半導体層を提供するステップ；前記第1の接合された半導体層上に電極を作成するステップ。前記電極は、前記弱い結合領域に対応する；前記電極の反対側に配置された作動可能な要素を作成するステップ；前記第1の半導体層と前記バルク性基板との間の界面で埋設酸化物層を形成するステップ；前記バルク性基板から前記第1の半導体層を除去するステップ；および、第2の半導体層に前記第1の半導体層を接合するステップ；。

40

【0052】

さらに別の態様においては、本発明は多層微小流体素子を製造する方法であり、その方法は、以下のステップからなる：バルク性基板を提供するステップ。前記バルク性基板は、埋設酸化物層を含む；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合された層を提供するステップ；前記第1の接合された層上にポートを作成するステップ。前記ポートは、前記弱い結合領域に対応する；前記ポートに機械的に連結するチャネルを作成するステップ；前記バルク性基板から前記第1の層を除去するステップ；および、第2の層に前記第1の層を接合するステップ；。

【0053】

50

別の態様においては、本発明は多層微小流体素子を製造する方法であり、その方法は、以下のステップからなる：バルク性基板を提供するステップ；前記基板上に強い結合領域および弱い結合領域を選択的に作成するステップ；前記基板上に垂直に支持される第1の接合された層を提供するステップ；前記第1の接合層と前記バルク性基板と間の界面で埋設酸化物層を形成するステップ；前記第1の接合層上にポートを作成するステップ。前記ポートは、前記弱い結合領域に対応する；前記ポートに機械的に連結するチャネルを作成するステップ；前記バルク性基板から前記第1の層を除去するステップ；および、第2層に前記第1の層を結合するステップ；。

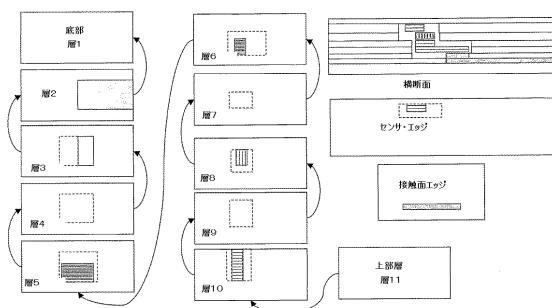

【図面の簡単な説明】

【0054】

前述の概要是本発明の好ましい実施例の以下の詳細な説明と同様に、添付の図面とともに読み込まれる場合、よりよく理解される。発明を図示するために、目下のところ好適である図面の実施例に示される。しかしながら、本発明は、図示される正確な配置および手段に限られないと理解される。その図面で、ここにおいて：

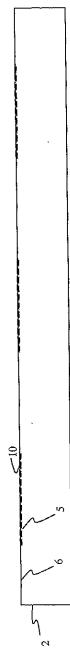

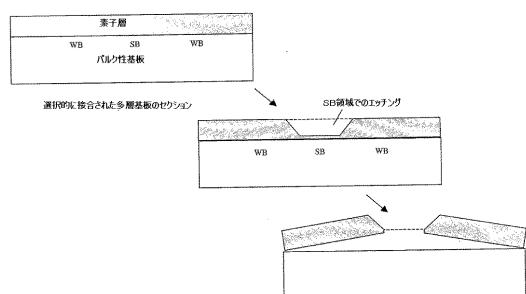

- 【図1】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図2】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図3】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図4】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図5】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図6】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図7】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図8】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図9】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図10】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図11】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図12】発明の原則による選択的に接合された多層基板の概略断面線図である；

- 【図13】発明の原則による選択的に接合された多層基板の概略断面線図である；

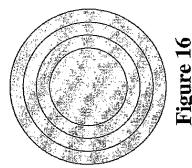

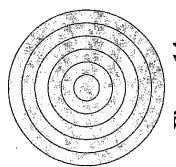

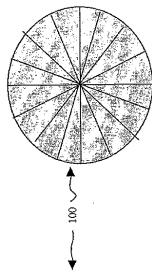

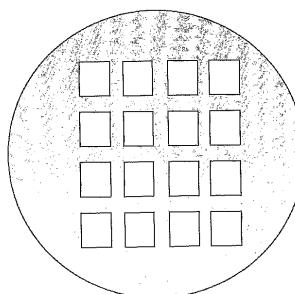

- 【図14】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

- 【図15】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

- 【図16】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

- 【図17】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

- 【図18】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

- 【図19】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

- 【図20】発明の原則によるウェーハの結合領域の形状の水平な断面線図である；

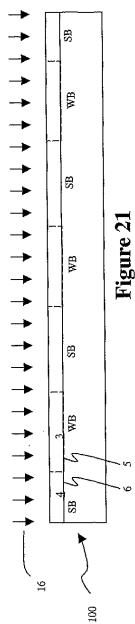

- 【図21】発明の原則によるウェーハのための剥離技術の概略断面線図である；

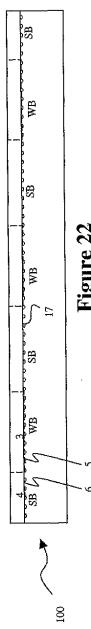

- 【図22】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図23】発明の原則によるウェーハのための剥離技術の概略断面線図である；

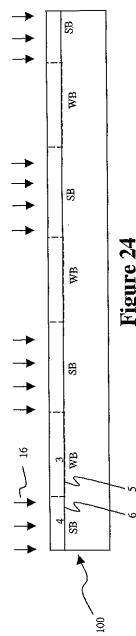

- 【図24】発明の原則によるウェーハのための剥離技術の概略断面線図である；

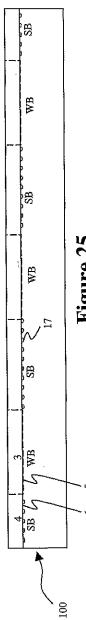

- 【図25】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図26】発明の原則によるウェーハのための剥離技術の概略断面線図である；

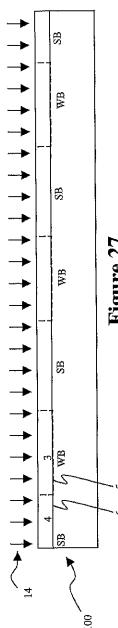

- 【図27】発明の原則によるウェーハのための剥離技術の概略断面線図である；

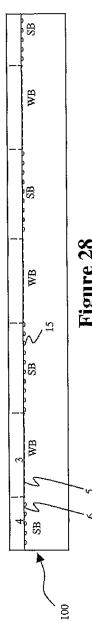

- 【図28】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図29】発明の原則によるウェーハのための剥離技術の概略断面線図である；

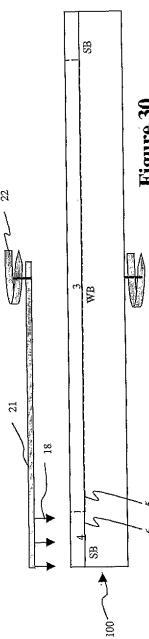

- 【図30】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図31】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図32】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図33】発明の原則によるウェーハのための剥離技術の概略断面線図である；

- 【図34】発明の原則による回路部の概略断面図である；

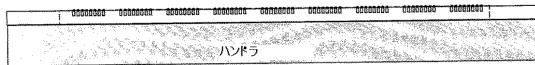

- 【図35】発明の原則による基板およびハンドラの概略断面図である；

- 【図36】発明の原則による回路部および整列配置しあつスタックされた導線の概略断面

10

20

30

40

50

線図である；

【図37】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図38】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図39】発明の原則による回路部の概略断面線図である；

【図40】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図41】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

10

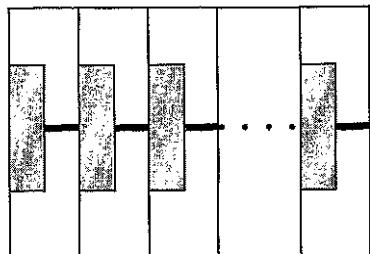

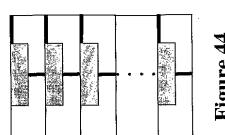

【図42】発明の原則による回路部の概略断面線図である；

【図43】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図44】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図45】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

20

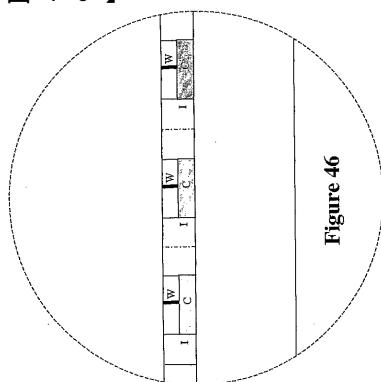

【図46】発明の原則による回路部の概略断面線図である；

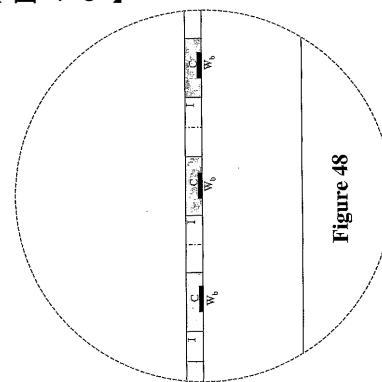

【図47】発明の原則による回路部の概略断面線図である；

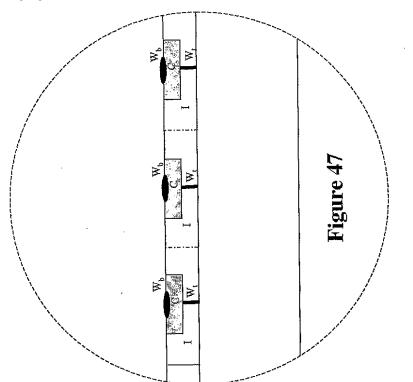

【図48】発明の原則による回路部の概略断面線図である；

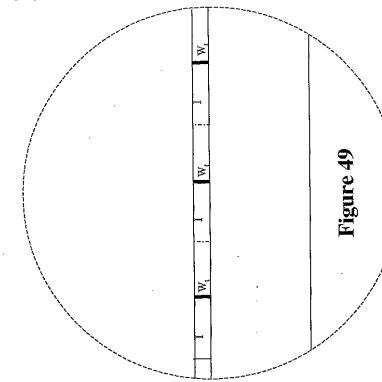

【図49】発明の原則による回路部の概略断面線図である；

【図50】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図51】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図52】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図53】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図54】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

30

【図55】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図56】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図57】発明の原則による回路部および整列配置しかつスタックされた導線の概略断面線図である；

【図58】発明の原則による整列配置されかつスタックされた回路部の概略断面線図である；

【図59】発明の原則による整列配置されかつスタックされた回路部の概略断面線図である；

40

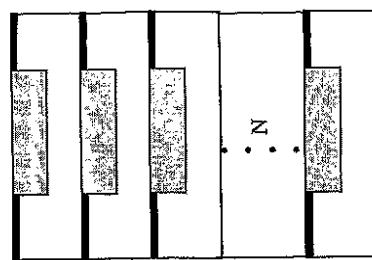

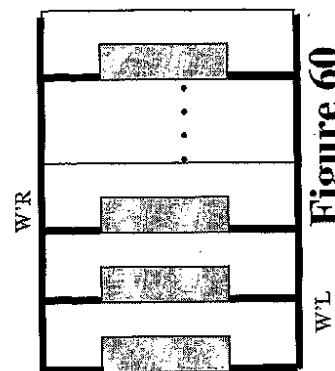

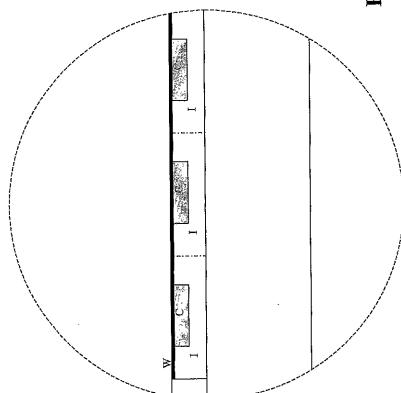

【図60】発明の原則による端の相互接続および回路部の概略断面線図である；

【図61】発明の原則による端の相互接続の概略断面図である；

【図62】発明の原則による端の相互接続の概略断面図である；

【図63】発明の原則による整列配置されかつスタックされた回路部の概略断面線図である；

【図64】発明の原則による整列配置されかつスタックされた回路部の概略断面線図である；

【図65】発明の原則による隣接する層の間で提供されるシールド層の概略断面線図である；

50

- 【図66】発明の原則による層の間で提供されるチャネルの概略断面線図である；

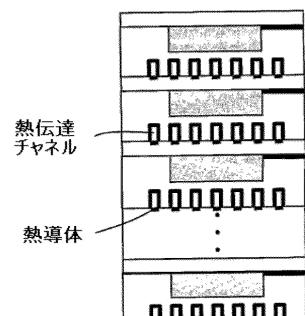

【図67】発明の原則による層の間の熱伝導チャネルの概略断面線図である；

【図68】発明の原則による素子層の下側の概略断面線図である；

【図69】発明の原則による回路成形領域を示す概略断面線図である；

【図70】発明の原則による選択的に接合された回路部の概略側面図である；

【図71】発明の原則による剥離技術を図示する概略断面線図である；

【図72】発明の原則による層の整列を図示する回路図である；

【図73】発明の原則による層の整列を図示する回路図である；

【図74】発明の原則による層の整列を図示する回路図である；

【図75】発明の原則による層の整列を図示する回路図である；

【図76】発明の原則による層の整列を図示する回路図である；

【図77】発明の原則による層の整列を図示する回路図である；

【図78】発明の原則による層の整列を図示する回路図である；

【図79】発明の原則による層の整列を図示する回路図である；

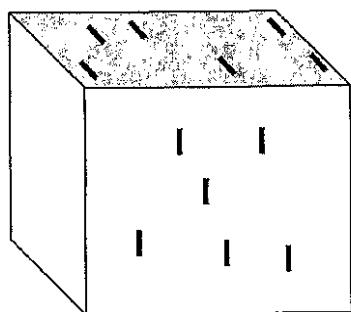

【図80】発明の原則による層のスタックの等大の概略図である；

【図81】発明の原則によるメタライゼーションの概略等大図である；

【図82】従来技術におけるメタライゼーションの概略等大図である；

【図83】発明の原則によるメタライゼーションの概略図である；

【図84】発明の原則によるメタライゼーションの概略図である；

【図85】発明の原則による剥離技術の概略図である；

【図86】発明の原則による整列配置技術の概略図である；

【図87】発明の原則による整列配置技術の概略図である；

【図88】発明の原則によるプラグ・フィル方法の概略図である；

【図89】発明の原則による相互接続を通じた概略図である；

【図90】発明の原則による機械的な整列の概略図である；

【図91】発明の原則による機械的な整列の概略図である；

【図92】発明の原則による層の分類の概略図である；

【図93】発明の原則による層の分類の概略図である；

【図94】発明の原則による層の分類の概略図である；

【図95】発明の原則による層の分類の概略図である；

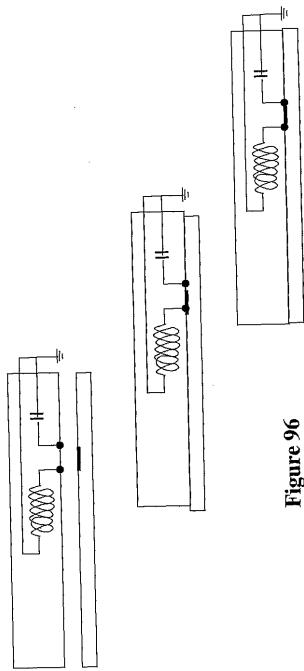

【図96】発明の原則によるハンドラの概略図である；

【図97】発明の原則によるハンドラの概略図である；

【図98】発明の原則による選択的に接合された装置の概略図である；

【図99】発明の原則によるMEMS装置のための処理ステップの概略図である；

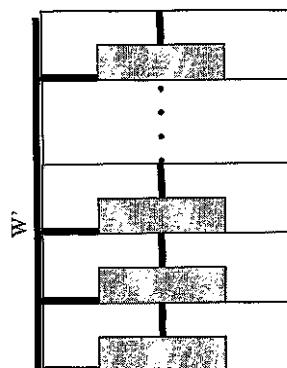

【図100】発明の原則によるMEMS装置のための処理ステップの概略図である。図面の詳細な説明 本発明は、三次元集積回路の形成に関する。

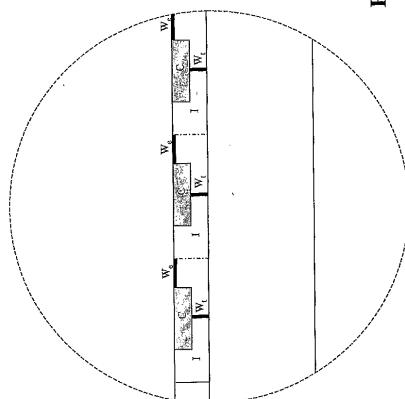

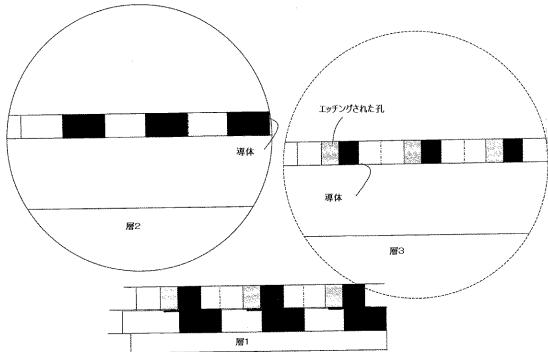

#### 【0055】

これらの三次元集積回路の特定の形成の議論の前に、出願人の出願中である米国特許出願番号09/950,909、2001年9月12日出願 名称「薄膜およびその製造方法」にて説明されたように、起動基板の議論が提示される。選択的に接合された多層基板と称されたこの基板は、周知のようにウェーハ上のマルチプル・チップの処理を可能にするが、好ましくは機械的な研磨または他のエッチバック技術なしでのウェーハのチップ層の早急な除去を可能とする。このチップ層は、後述するように、それから他のチップ層にスタックされることができる、あるいは、チップ層は、個々のチップにダイシング、および、スタックされることができる。

#### 【0056】

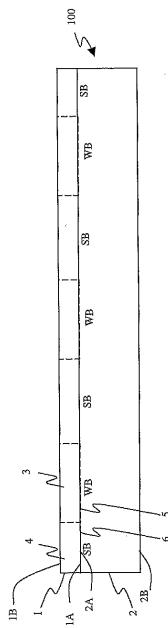

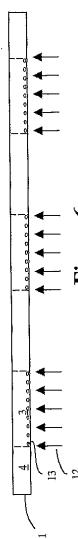

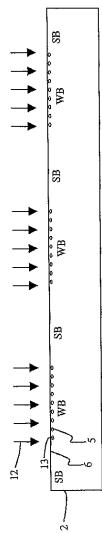

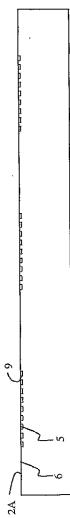

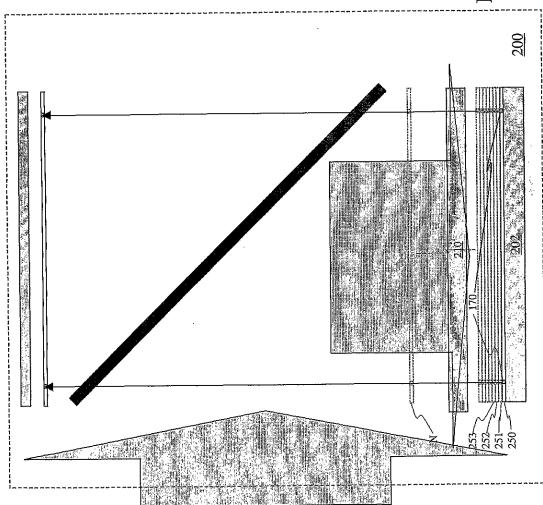

図1を参照する。選択的に接合された多層基板100が示される。多層基板100は、露出された表面1Bを有する層1、および、選択的に層2の表面2Aに接着された層1Aを含む。層2は、対向する表面2Bをさらに含む。一般に、選択的に接合された多層基板100を形成するため、層1、層2または両方の層1および2は、弱い結合5および強い

10

20

30

40

50

結合 6 の領域を定義するために処理されて、続いて接合される。ここにおいて、弱い結合 5 の領域は、有用な素子または構造の処理を可能にする状態にある。

概して、層 1 および 2 は互換性を持つ。すなわち、層 1 および 2 は、互換的、熱的、機械的、および / または結晶質の特性を構成する。特定の好ましい実施例において、層 1 および 2 は同じ材料である。もちろん、異なる材料は使用されることができるが、互換性のために好ましくは選ばれることができる。

#### 【 0 0 5 7 】

層 1 の 1 つまたはそれ以上の領域は、1 つまたはそれ以上の構造内またはその上で、マイクロエレクトロニクスは形成される能够るように基板領域として役立つように定義される。本願明細書においてさらに記載されるように、これらの領域は、いかなる所望のパターンであることができる。層 1 の選択された領域は、それから結合を最小化するために処理され、弱い結合領域 5 を形成する。代替的に、( 層 1 の処理と連動して、または層 1 に対する処理の代わりに ) 層 2 の対応する領域は、結合を最小化するために処理されることがある。さらなる選択肢は、強い結合領域 6 の結合強さを強化するため、構造を形成するのに選ばれたそれら以外の領域における処理された層 1 および / または層 2 を含む。

層 1 および / または層 2 の処理後、層は、整列配置され、かつ、結合される能够である。さらに本願明細書において記載されるように、結合はいかなる適切な方法であってもよい。さらに、層の整列は、機械的、光学的またはその組合せであってよい。現段階では、やはり、概して層 1 の上に形成される構造がないので、整列は重大ではないと理解される。しかしながら、層 1 および 2 の両方が処理される場合、整列は選択された基板領域からの変化を最小化するために必要とされる可能性がある。

#### 【 0 0 5 8 】

多層基板 100 は、層 1 の中にまたは上の所望の構造を処理するユーザに提供される能够である。したがって、多層基板 100 は、ユーザが従来の製造技術、または、様々な関連した技術が発展して公知となった他の技術を用いて構造または素子を処理する能够のように形成される。特定の製造技術により基板は、高温度、圧力、苛酷な化学製品またはその組合せのような極端な状況にさらされる。したがって、多層基板 100 はこれらの状況に耐えるために好ましくは形成される。

#### 【 0 0 5 9 】

有用な構造または素子は、部分的にまたは実質的に弱い結合領域 5 に重なる領域 3 の中または上で形成される能够である。したがって、部分的にまたは実質的に強い結合領域 6 に重なる領域 4 は、その中またはその上に構造を概して有しない。ユーザが多層基板 100 の層 1 の中または上に有用な素子を形成した後、層 1 は後に剥離される能够である。剥離は、有用な素子に不利益な層間剥離技術を直接受けさせる必要なく剥脱のような周知の技術により行われる能够である。有用な素子は概して領域 4 の中または上に形成されないので、これらの領域は、領域 3 の中または上に形成される構造を損なわずにイオン注入のような剥離処理を受けさせられる能够である。

#### 【 0 0 6 0 】

弱い結合領域 5 を形成するため、表面 1A、2A、または両方は、弱い結合領域 5 の現場で実質的に非結合または弱い結合を形成するために処理される能够である。あるいは、弱い結合領域 5 は処理されないままにできる。それによって、強い結合領域 6 は強い結合を誘発するために処理される。領域 4 は、部分的にまたは実質的に強い結合領域 6 に重なる。強い領域 4 を形成するため、表面 1A、2A、または両方は、強い結合領域 6 の現場で処理される能够である。あるいは、強い結合領域 6 は処理されないままにできる。それによって、弱い結合領域 5 は弱い結合を誘発するために処理される。さらに、両方の領域 5 および 6 は、異なる処理技術により処理される能够である。そこにおいて、処理は質的にまたは量的に異なる可能性がある。

#### 【 0 0 6 1 】

弱い結合領域 5 および強い結合領域 6 の群の一方または両方の処理後、層 1 および 2 は

10

20

30

40

50

、本質的に一体的な多層基板 100 を形成するために共に接合される。したがって形成されたように、例えば、特に層 1 の領域 3 の中または上に、構造または素子の中またはその上に形成するため、多層基板 100 はエンドユーザによって苛酷な環境を受けさせられる。

本明細書のため、「弱い結び付き」または「弱い結合」という語句は、例えば剥脱、他の機械的な分離、前述の剥離技術のうちの少なくとも 1 つからなる熱、光、圧力またはその組合せのような剥離技術によって直ちに克服ができる層の層または部分の間の結合を概して称する。これらの剥離技術は、特に弱い結合領域 5 の近くで層 1 および 2 を最小限に離脱する、または、損なう。

#### 【 0 0 6 2 】

弱い結合領域 5 および強い結合領域 6 の群の一方または両方の処理は、様々な方法によって達成されることができる。処理の重要な様態は、その弱い結合領域 5 が、(さらに本願明細書において記載される次の剥離ステップにおいて) 強い結合領域 6 においてよりもより直ちに剥離されるということである。これが、剥離する間、その上に有用な構造を含むことができる領域 3 へのダメージを最小化する、または、防ぐ。さらに、強い結合領域 6 の介在物は、特に構造処理の間、多層基板 100 の機械的な保全性を強化する。したがって、その中またはその上の有用な構造によって除去される場合、層 1 の続いて起こる処理は最小化される、または、削除される。

#### 【 0 0 6 3 】

弱い結合領域に対する強い結合領域の結合強さの比率 (S B / W B ) は、一般に 1 より大きい。強い結合領域と弱い結合領域との特定の構成、および、強い結合領域と弱い結合領域との相対的な領域サイズ次第では、S B / W B の数値は、無限に接近することができる。すなわち、強い結合領域が処理の間、機械的および熱的な安定性を維持するためにサイズおよび濃度において十分な場合、弱い結合領域の結合強さは、ゼロに近づくことができる。

#### 【 0 0 6 4 】

しかしながら、従来技術において教示されているように、強い結合強さは、(SiO<sub>2</sub> ウェーハのような典型的シリコンおよびシリコン派生物において) 約 500 ミリニュール / 平方メートル (mJ / m<sup>2</sup>) から、5000 mJ / m<sup>2</sup> 以上まで変化することができるので、比率 S B / W B は、相当に変化することができる。(本願明細書に参照された、Q. Y. Tong, U. Goesle 半導体ウェーハ結合、『科学および技術』pp. 104 - 118, John Wiley and Sons社、ニューヨーク、NY 1999 を参照のこと)

しかし、材料、意図された有用な構造(公知の場合)、選択された結合および剥離技術、弱い結合の領域と比較した強い結合の領域、ウェーハ上の強い結合および弱い結合構成またはパターンのなど次第で、弱い結合強さは、よりさらに相当変化することができる。例えば、イオン注入が層を剥離するステップとして使われるところで、有用な弱い結合領域の結合強さは、イオン注入および/または注入された領域での微小気泡の関連した放出の後強い結合領域の結合強さと同等であることができる。したがって、選択された剥離技術、および、弱い結合領域において形成されるおそらく有用な構造または素子の選択次第で、結合強さ S B / W B の比率は、概して 1 より大きく、好ましくは 2、5、10 を超えるかまたはより高い。

#### 【 0 0 6 5 】

弱い結合領域 5 および強い結合領域 6 の群の一方または両方の処理の特定のタイプは、概して選ばれる材料次第で始められる。さらに、層 1 および 2 の結合技術の選択は、少なくとも一部分で、選択された処理手順次第である可能性がある。加えて、続いて起こる剥離は、処理技術、結合方法、材料、有用な構造の存在のタイプ、前述の要因のうちの少なくとも 1 つからなる組合せのような要因次第である可能性がある。特定の実施例において、処理、結合および続いて起こる剥離(すなわち領域 3、または、代替的により高水準装置における中間の構成要素における有用な構造を形成するエンドユーザにより行われる)の選択された組合せは、層 2 から層 1 を剥離するために劈開伝播、または層 2 を除去する

10

20

30

40

50

機械的な薄層化の必要性を除去し、好ましくは、劈開伝播および機械的な薄層化の両方を除去する。したがって、従来の教示に従う劈開伝播または機械的な薄層化は層 2 ダメージを与え、さらに大幅な処理なしでは本質的に役立たなくさせてるので、下側基板は、最小のまたは未処理で再利用されることができる。

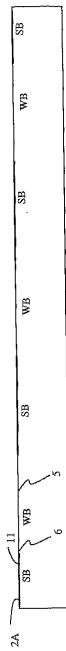

#### 【 0 0 6 6 】

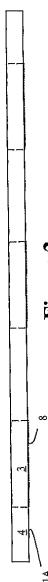

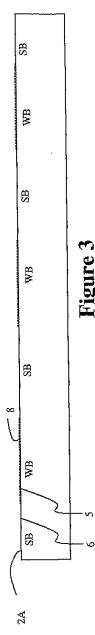

図 2 および 3 を参照する。ここにおいて、同様に状態にある領域は、参照の数字のように参照される。ある処理技術は、表面 1 A、2 A または 1 A および 2 A の両方の上に固体の構成要素および分解できる構成要素を含むスラリーの使用を含む。固体の構成要素は、例えば、アルミナ、酸化シリコン (SiO(x))、他の固体の金属または金属酸化物、または層 1 および 2 の結合を最小化する他の材料である可能性がある。分解できる構成要素は、例えば、ポリビニルアルコール (PVA) または適切な分解できる他のポリマーである可能性がある。概して、スラリー 8 は表面 1 A (図 2)、2 A (図 3) または両方の 1 A および 2 A で弱い結合領域 5 において適用される。続いて、層 1 および / または 2 は、ポリマーを分解するため、好ましくは不活発な環境で加熱されることができる。したがって、多孔性構造 (スラリーの固体の構成要素からなる) は弱い結合領域 5 で残り、結合の時点で層 1 および 2 は弱い結合領域 5 で結合をしない。

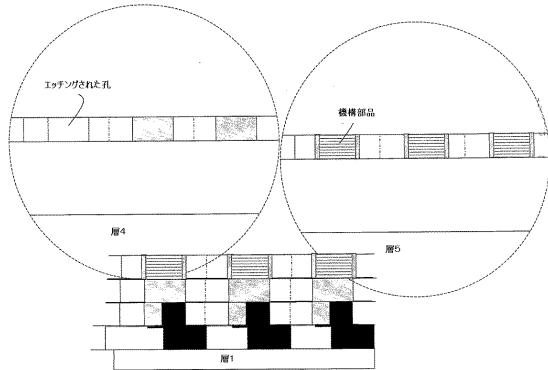

#### 【 0 0 6 7 】

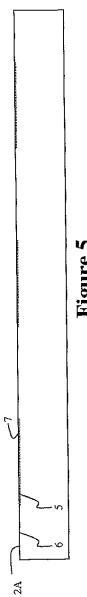

図 4 および 5 を参照すると、他の処理技術は、弱い結合領域 5 と強い結合領域 6 との間の表面粗さにおける変化に依存する可能性がある。表面粗さは、表面 1 A (図 4)、表面 2 A (図 5) または、表面 1 A および 2 A の両方で変更されることがある。一般に、弱い結合領域 5 は、強い結合領域 6 より高い表面粗さ 7 (図 4 および 5) を有する。半導体材料において、例えば、弱い結合領域 5 は、約 0.5 ナノメートル (nm) を超える表面粗さを有することができ、強い結合領域 4 は、概して約 0.5 nm 未満のより低い表面粗さを有することができる。

#### 【 0 0 6 8 】

他の例では、弱い結合領域 5 は約 1 nm を超える表面粗さを有することができ、強い結合領域 4 は概して約 1 nm 未満のより低い表面粗さを有することができる。さらなる例において、弱い結合領域 5 は約 5 nm を超える表面粗さを有することができ、強い結合領域 4 は概して約 5 nm 未満より低い表面粗さを有することができる。表面粗さは、エッチング (例えば、KOH または HF 溶液において)、または、沈着プロセス (例えば、低圧化学蒸着法「LPCVD」またはプラズマ拡張化学蒸着法「PECVD」) によって変更されることができる。表面粗さと関連した結合強度は、本願明細書において参照された、例えば、Guide その他のによる「表面粗さ制御による選択的なウェーハ結合」電気化学会ジャーナル 148(4) G225 - G228 (2001)において、より完全に記載される。

#### 【 0 0 6 9 】

これと同様の方法で (ここにおいて、同様な状態にある領域は、図 4 および 5 に記載の類似した参照番号によって参照される) 多孔性領域 7 は、弱い結合領域 5 で形成されることができ、強い結合領域 6 は処理されていないままである可能性がある。したがって、層 1 はその多孔性の性質のために弱い結合領域 5 の現場で、層 2 と最小限に結合する。有孔率は、表面 1 A (図 4)、表面 2 A (図 5) または 1 A および 2 A の両方の表面において変更されることがある。一般に、弱い結合領域 5 は、多孔性領域 7 (図 4 および 5) において、強い結合領域 6 よりも高い有孔率を有する。

#### 【 0 0 7 0 】

他の処理技術は、エッチングされた領域においてフォトレジストまたは炭素を含む他の材料の沈着 (例えば、重合体ベースの分解できる材料を含む) に続いて (表面 1 A (図 4)、2 A (図 5) または 1 A および 2 A の両方ともにおいて) 弱い結合領域 5 の選択的なエッチングに依存する可能性がある。キャリア部材を分解するために十分な温度で好ましくは、層 1 および 2 が結合すると、弱い結合領域 5 は、多孔性炭素材料をその中に含む。したがって、弱い結合領域 5 の層 1 と 2 と間の結合は、強い結合領域 6 における層 1 と 2

10

20

30

40

50

との間の結合と比較して、非常に弱い。当業者は、状況次第で、分解材料は、除気しない、汚染しない、または、他の点で基板層1または2、または領域3の中または上に形成される有用な構造を汚染しないものが選ばれることを認識するであろう。

#### 【0071】

さらなる処理技術は、強い結合領域6および/または弱い結合領域5を達成するため照射を使用することができる。この技術においては、層1および/または2は、必要に応じて、強いおよび/または弱い結合を達成するために中性子、イオン、粒子線またはその組合せによって照射を受ける。例えば、 $\text{He}^+$ 、 $\text{H}^+$ のような粒子、または、他の適切なイオンまたは粒子、電磁エネルギー、または、レーザー光線は、(表面1A(図10)、2A(図11)または1Aおよび2Aの両方ともにおける)強い結合領域6で照射を受けることができる。照射のこの方法は、照射量および/または注入エネルギーが概して非常に少ない(例えば、剥離のために使用する適用量は順に百分の一から千分の一である)ということにおいて、層の剥離のためのイオン注入と異なると理解されるべきである。

#### 【0072】

図8および9を参照する。なおさらなる処理技術は、弱い結合領域5の表面エッチングを含む。このエッチング・ステップの間、柱9は、表面1A(図8)、2A(図9)または1Aおよび2Aの両方との上の弱い結合領域5において定義される。柱は、柱を残した選択エッチングによって定義されることがある。柱の形状は、三角形、ピラミッド型、矩形、半球状、または他の適切な形状である可能性がある。

#### 【0073】

あるいは、柱は伸ばされる、またはエッチングされた領域に置かれることができる。結合材料のための結合位置が少ないので、弱い結合領域5の全体の結合強さは、強い結合領域6の結合強さよりも非常に弱い。

#### 【0074】

さらにもう1つの処理技術は、層1(図12)、2(図13)において弱い結合領域5に、例えばエッチング、機械加工または両方(使用される材料に次第で)によって形成されたボイド領域10(図12および13)の介在物を含む。したがって、第1の層1が第2の層2に接合する場合、続いて起こる剥離を容易にする強い結合領域6と比較すると、ボイド領域10は結合を最小化する。

#### 【0075】

再び図2および3を参照すると、他の処理技術は、表面1A(図2)、2A(図3)または1Aおよび2Aの両方の弱い結合領域5で、1つまたはそれ以上の金属領域8の使用を含む。例えば、Cu、Au、Pt、または、その組合せまたは合金を含むがそれらに限定されない金属は、弱い結合領域5に置かれる。層1および2が結合すると、弱い結合領域5は、弱く結合される。強い結合領域は、処理されていない今まであり、(ここにおいて、結合強さの差は、弱い結合層5および強い結合領域6に関して弱い結合比に対する必要な強い結合を提供する)または、強い凝着を促進するため、上記に記載された、または下記のように処理されることがある。

#### 【0076】

さらなる処理技術は、表面1A(図10)、2A(図11)または1Aおよび2Aの両方の上の強い結合領域6で、1つまたはそれ以上の凝着促進剤11の使用を含む。適切な凝着促進剤は、TiO(x)、タンタル酸化物または他の凝着促進剤を含むが、これに限定されるものではない。代わりとして、凝着促進剤は表面1Aおよび/または2Aの実質的にすべてに使われることができ、ここにおいて、金属材料は、凝着促進剤と表面1Aまたは2A(凝着促進剤の現場に次第で)との間で、弱い結合領域5において配置される。結合すると、したがって金属材料は、弱い結合領域5での強い結合を妨げ、一方で、強い結合領域6で残っている凝着促進剤は、強い結合を促進する。

#### 【0077】

さらにもう1つの処理技術は、疎水性および/または親水性(訳注\*5)の異なる領域の提供を含む。例えば、シリコンのような材料は自然に室温で結合するので、親水性領域

10

20

30

40

50

は特に強い結合領域 6 のために有用である。

【 0 0 7 8 】

室温および上昇された温度の両方における疎水性および親水性の結合技術は、例えば、本願明細書において参照された、Q. Y. Tong, U. Goesle 半導体ウェーハ結合、『科学および技術』pp. 49 - 135、John Wiley and Sons社、ニューヨーク、NY 1999 に記載されているように、公知である。

【 0 0 7 9 】

なおさらなる処理技術は、選択的に照射を受ける 1 つまたはそれ以上の剥脱層を含む。例えば、1 つまたはそれ以上の剥脱層は、表面 1 Å および / または 2 Å に配置することができる。照射なしでは、剥脱層は接着材として作用する。

10

【 0 0 8 0 】

弱い結合領域 5 における紫外照射のような照射に露出されると、接着特性は最小化される。有用な構造は、弱い結合領域 5 の中または上で形成されることができ、次の紫外照射ステップまたは他の剥離技術は、強い結合領域 6 で、層 1 および 2 を分離するために用いることができる。

【 0 0 8 1 】

図 6 および 7 を参照する。追加的な処理技術は、熱的に処理されると、弱い領域 3 の層 1 ( 図 6 ) 、層 2 ( 図 7 ) または層 1 および層 2 の両方で複数の微小気泡 13 の形成を可能にするため、注入イオン 12 ( 図 6 および 7 ) を含む。したがって、層 1 および 2 が接合する場合、弱い結合領域 5 の層 1 および 2 の次の剥離が容易にされるように、強い結合領域 6 以外の弱い結合領域 5 は結合する。

20

【 0 0 8 2 】

他の処理技術は、エッチング・ステップに続くイオン注入ステップを含む。一実施例において、この技術は、表面 1B の実質的にすべてを通じてイオン注入が実行される。続いて、弱い結合領域 5 は、選択的にエッチングされることができる。この方法は、本願明細書において参照されたシンプソンその他の、「燐化インジウムの選択的な化学エッチングの誘発された注入」電気化学および固体物理会報 4 ( 3 ) G 26 - G 27 において、欠陥を除去するためのダメージ選択エッチングに関して記載される。

20

【 0 0 8 3 】

なおさらなる処理技術においては、弱い結合領域 5 および / または強い結合領域 6 に選択的に置かれる 1 つまたはそれ以上の層が、狭いまたは広い波長範囲に基づく放射線を吸収および / または反射する特性を有するということが認識される。例えば、強い結合領域 6 に選択的に置かれる 1 つまたはそれ以上の層は、特定の放射線波長に露出されると、層が強い結合領域 6 で放射線を吸収し、層 1 および 2 を結合するように接着特性を有することができる。

30

【 0 0 8 4 】

当業者は、前述の処理技術のうちの少なくとも 1 つからなる組合せと同様に、追加的な処理技術が使用されることができると認識するであろう。しかしながら、使用されるいかなる処理の主な特長は、1 より大きい S B / W B 結合強さ比率を提供する弱い結合の 1 つまたはそれ以上の領域および強い結合の 1 つまたはそれ以上の領域を形成する能力である。

40

層 1 および 2 の界面における弱い結合領域 5 および強い結合領域 6 の形状は、領域 3 においてまたはその中に形成される有用な構造のタイプ、選択された剥離 / 結合のタイプ、選択された処理技術、および他の要因を含むがこれに限らない要因に従って変化する可能性がある。

【 0 0 8 5 】

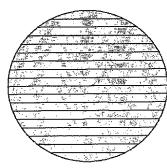

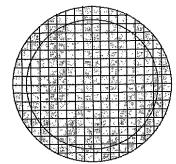

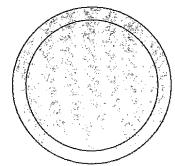

図 14 - 20 を参照する。多層基板 100 は、同心円 ( 図 14 、 16 、および 18 ) 、縞模様 ( 図 15 ) 、放射状 ( 図 17 ) 、格子縞模様 ( 図 20 ) 、格子縞および環状の組合せ ( 図 19 ) 、または、そのいかなる組合せによって弱い結合および強い結合領域を有することができる。もちろん、当業者は、いかなる形状も選ばれることができると認識

50

するであろう。さらに、強い結合の領域と比較した弱い結合の領域の比率は、変化することができる。一般に比率は、特に構造処理の間、多層構造 100 の完全性を包含しないように（すなわち強い結合領域 6 で）十分な結合を提供する。

#### 【0086】

好みしくは、比率は、また構造処理のための有用な領域（すなわち弱い結合領域 5）を最大にする。

#### 【0087】

上述のように弱い結合領域 5 および / または強い結合領域 6 の実質的に現場において表面 1A および 2A の一方または両方の処理後、層 1 および 2 は、実質的に一体的な多層基板 100 を形成するために共に接合する。層 1 および 2 は、共晶、融解、陽極、真空、ファン・デル・ワールス、化学的な凝着、疎水性現象、親水性現象、水素結合、クーロン力、毛管の力、非常に短い範囲の力、または前述の結合技術および / または物理的な現象のうちの少なくとも 1 つからなる組合せを含むがこれに限らない、様々な技術および / または物理的な現象は、ある程度使用される 1 つまたはそれ以上の処理技術、その上にまたはその中に形成される有用な構造のタイプまたは存在、予期された剥離方法、または、他の要因次第であることは当業者にとって明らかである。10

#### 【0088】

代替的に、埋込み酸化物層は、素子層の底面で形成されることがある。酸化物層は、バルク性基板への素子層の選択的な結合の前に形成されることがある。さらに、酸化物層は、所望の埋込み酸化物層の深さに酸素を注入して形成されることがある。20

酸化物層を多層基板の上に形成するための様々な技術がある。

#### 【0089】

第 1 の技術は、1300 より高温でのアニールに続く高照射量での酸素の注入によるシリコン基板の埋込み SiO<sub>2</sub> 層の形成から構成される。イオン注入を通じて、埋込み SiO<sub>2</sub> 層の所望の層厚が形成されることがある。

#### 【0090】

埋込み酸化物層を構成するための代替技術は、細い SiO<sub>2</sub> フィルムの多層基板の表面上への形成、そして SiO<sub>2</sub> フィルムによる第 2 のシリコン基板への基板の結合から構成される。周知の機械的な研磨および研磨加工プロセスは、それから埋込みシリコン酸化層より上に所望の層厚シリコン層を形成するために用いられる。多層基板上のシリコン酸化層は、所望の層厚を得るために形成された酸化物層のエッチングに続いて、表面の連続した酸化によって形成される。30

#### 【0091】

埋込み酸化物層を形成するための他の技術は、酸化による第 1 の多層基板上の細いシリコン酸化層の形成、それから、細いシリコン酸化層の下で空洞平面を形成するため、H+ イオンの第 1 の多層基板の中への注入から構成される。

#### 【0092】

続いて、細いシリコン酸化層によって、この第 1 の本体は第 2 の多層基板に接合し、そうすると、全体のアセンブリは割れている平面に空洞平面を変換するために熱的な活性化を受けさせられる。これは、使用可能な SOI 基板の回復を可能にさせる。40

#### 【0093】

多層基板 100 は、したがってエンドユーザ（埋込み酸化物層の有無にかかわらず）に提供されることができる。あるいは、導線の特定のパターンは、多層基板と一体的に形成されることがある。エンドユーザは、実質的にまたは部分的に、表面 1A および 2A の界面で弱い結合領域 5 に重なる領域 3 の中または上で 1 つまたはそれ以上の有用な構造（図示せず）続いて形成することができる。有用な構造は、1 つまたはそれ以上の能動または受動的な要素、素子、道具、ツール、チャネル、他の有用な構造、または、前述の有用な構造のうちの少なくとも 1 つからなるいかなる組合せを含むことができる。例えば、有用な構造は集積回路または太陽電池を含むことができる。もちろん、当業者は様々なマイ50

クロ技術および微小工学ベースの素子が形成されることを認識する。

【0094】

例えば、能動素子は多層SOIウェーハまたは基板の上に形成されることがある。これらの能動素子は、SOI基板の埋込み酸化膜上の単結晶シリコン活動層において形成される。シリコン活動層の層厚は、その中に形成される能動素子の目的に依存する。SOI要素が高速および低消費電力で作動しているCMOS要素である場合、能動層の層厚は、約50から100nmである。SOI要素が高降伏電圧要素である場合、能動層の層厚は、数マイクロメートルである。能動素子の例は、保護用ダイオードである。保護用ダイオードは、コネクション・ピンからの過電流を基板および半導体デバイスの外側まで導き、このことにより半導体デバイスの内部回路を保護するため、半導体デバイスに提供される半導体要素である。

【0095】

他の能動素子が、単結晶シリコン基板またはSOI基板のどちらかの動作領域の選択的なドープおよびマスキングによって製造されることは、当業者にとって明らかである。これらの能動素子は、バイポーラ接合トランジスタ、MOSトランジスタ、電界効果トランジスタ、ダイオード、絶縁ゲート・バイポーラトランジスタなどを含むが、これに限定されるものではない。

【0096】

多層基板上に製造されることができる他の能動素子は、MEMS装置である。概して、MEMS装置は、基板上に製造された電極に対向して配置された電極および作動可能な要素からなる。作動可能な要素は、マシン構造上に電気的制御を提供するため、電極からの制御を搬送する。

【0097】

MEMS装置を製造する1つの技術は、それがMEMS構造を形成するため、単一の基板層から材料をエッチングして離すことを含むので減ずる製造技術と考えられる深いエッチング処理を用いた基板のバルク性ミクロ機械加工である。

【0098】

基板層は、およそ何十ミクロンで比較的厚く、このプロセスの高度の知識により、カンチレバー、ブリッジ、溝、空腔、ノズルおよび膜のような、基板上の異なる構造のミクロ機械加工を可能にする。

【0099】

多層基板上にMEMS装置を製造する他の技術は、表面ミクロ機械加工技術による。代替的な構造上の層および犠牲のスペーサ層が、必要な機械的なおよび電気特性でMEMS構造を造るために“組み立てられ”ているので、それは添加処理と考えられる。多結晶シリコン（ポリシリコン）は最も一般に使われる構造材料であり、酸化シリコン・ガラスは最も一般的には使用される犠牲材料である。従来のミクロ機械加工プロセスにおいて、これらの層は、窒化ケイ素の層によって絶縁されるシリコン基板上のポリシリコン／酸化物の対において形成される。層は、モーター、ギア、鏡およびビームのような複雑な構造を形成するため、フォトリトグラフィ技術を使用してパターン化される。層が造られると、切削は、酸化物層で作成され、上部構造上の層を基板にまたは下にある構造上の層に固定するためにポリシリコンで満たされる。

【0100】

1つまたはそれ以上構造が、層1の1つまたはそれ以上の選択された領域3の上に形成された後、層1は様々な方法により剥離ができる。いうまでもなく、構造が部分的にまたは実質的に弱い結合領域5に重なる領域4の中または上で形成されるので、層1の剥離は、構造上の欠陥または変形のような、剥離に関連する構造への典型的損害を最小化または除去する一方で、生じることができる。

剥離は、様々な周知の技術によって達成されることがある。一般に剥離は、少なくとも一部において、処理技術、結合技術、材料、有用な構造のタイプまたは存在、または他の要因の存在次第である可能性がある。

10

20

30

40

50

## 【0101】

一般に図21-32を参照すると、剥離技術は、概して層1の層厚と同等の基準深で微小気泡を形成するためにイオンまたは粒子の注入に基づくことができる。イオンまたは粒子は、酸素、水素、ヘリウムまたは他の粒子14から生じられる。注入(訳注\*6)は、粒子またはイオンに微小気泡15を生じさせるため、強い電磁放射、熱、光(例えば赤外線または紫外線)、圧力、または前述のうちの少なくとも1つからなる組合せへの露出によって続き、層1および2を最終的に展開および剥離させる。注入および任意に熱、光、および/または圧力はまた、例えば、層1および2の平面に並列である層1および2の平面に垂直の方向、層1および2の平面の他の角度の剥脱方向(図23、26、29、32で破線により示された)またはその組合せにおいて機械的な分離ステップ(図23、26、29、32)によって続くことができる。薄膜層の分離のためのイオン注入は、本願明細書において参考されたチャンその他による米国特許No.6,027,988名称「プラズマ浸入イオン注入によりフィルムをバルク性基板から分離する方法」においてさらに詳細に記載される。

## 【0102】

特に図21-23および24-26を参照すると、層1および2の間の界面は、特に強い結合領域6で微小気泡17を特に形成するため、選択的に注入されることができる。このように、領域3(その中またはその上に1つまたはそれ以上の有用な構造を有する)の粒子16の注入は、最小化され、したがって、領域3において1つまたはそれ以上の有用な構造に発生する修理可能または回復不能なダメージの可能性を減少することができる。選択的な注入は、強い結合領域4(図24-26)の選択的なイオンビーム走査または領域3(図21-23)のマスキングによって実行されることができる。選択的なイオンビーム走査は、構造100の機械的な操作および/または注入されるイオンまたは粒子を誘導するのに用いられる素子を指す。当業者に公知であるように、様々な装置および技術は、集中するイオンビームおよび電磁ビームを含むがそれに限られない選択的な走査を実行するために使用されることができる。さらに、様々なマスキング材料および技術もまた公知である。

## 【0103】

図27-29を参照すると、注入は、表面1Bまたは2B全体を実質的に横切って達成されることができる。注入は、ターゲット、注入材料および注入の所望の深さに従う適切なレベルにある。したがって、層2が層1より非常に厚い所で、表面2Bを通じて注入するのは実際的でないかもしれないが;層2が適切な注入層厚である場合、(例えば、実行可能な注入エネルギーの範囲内で)、表面2Bを通じて注入することは、望ましい可能性がある。これは、領域3の1つまたはそれ以上の有用な構造に発生する可能性がある修理可能または回復不能なダメージの可能性を最小化するかまたは除去する。

一実施例において、図18と関連して図30-32を参照すると、強い結合領域6は、層1と2との間の界面の外周で形成される。

## 【0104】

したがって、層1を層2から剥離するため、イオン18は、例えば、層1および1の界面で微小気泡を形成するために領域4を通じて注入されることがある。好ましくは、選択的な走査が使用される。ここにおいて、構造100(矢印20で示された)は、回転することができ、走査装置21(矢印22で示された)、またはその組合せは、回転することができる。本実施例におけるさらなる利点は、その中またはその上に形成される有用な構造の選択をエンドユーザに与える可撓性である。強い結合領域6の寸法(すなわち幅)は、多層基板100の機械的および熱的な保全性を維持するために適切である。好ましくは、強い結合領域6の寸法は最小化され、したがって構造処理のための弱い結合領域5の領域を最大にする。例えば、強い結合領域6は、8インチのウェーハ上での1ミクロンである。

さらに、層1の層2からの剥離は、例えば強い結合領域6でエッティングを作成するための(表面に並行した)エッティングのように他の従来の方法によって始められることができる

。このような実施例では処理技術は、特に互換性を持ち、例えばここにおいて、強い結合領域 6 は、その集合体（すなわち層 1 および 2）の選択性よりも非常に高いエッティング選択性を有する酸化物層で処理される。弱い結合領域 5 は、選択された処理またはその欠如が層 1 と層 2 との接合ステップにおいて接合が妨げるので、弱い結合領域 5 の現場で層 2 から層 1 を剥離するために好ましくはエッティングを必要としない。

これに対して、劈開伝播は、層 1 の層 2 からの剥離を始めるために用いることができる。また、弱い結合領域 5 の結合は限られるので、剥離は好ましくは強い結合領域 6 の現場で必要とされるのみである。さらに、剥離は、従来公知であるように、エッティング（表面に垂直の）によって始められ、好ましくは、領域 4 の現場（すなわち、部分的にまたは実質的に、強い結合領域 6 が重なる）に限られる。

10

### 【 0 1 0 5 】

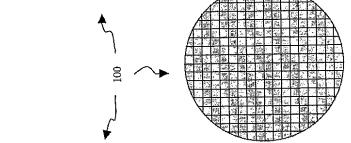

他の実施例において、次に図 8 5 を参照して、剥離する方法が示される。方法は、多層基板 1 0 0 の提供；W B 領域 5 における 1 つまたはそれ以上の有用な構造（図示せず）の処理；好ましくは先細角（例えば 4 5 °）で、S B 領域 6 のエッティング；素子層への、好ましくはエッティングされた S B 領域 6 だけへの低エネルギー・イオン注入；および、W B 領域での素子層部の剥離、または速やかな除去；を含む。W B 層の 2 つの素子層部は除去されると示される一方で、これが 1 つの素子層部上の解放を容易にするために用いることができると理解されることに留意する。W B 領域の先細端は、機械的に削除を容易にする。有益に、元々の素子層厚を貫通するため、必要とされる注入エネルギーと比較すると非常に低いイオン注入エネルギーが使われることができる。

20

### 【 0 1 0 6 】

層 1 および 2 は、同じまたは異なる材料であることができ、プラスチック（例えばポリカーボネート）、金属、半導体、絶縁物、単結晶、アモルファス、非結晶、生物学的材料（例えば、DNA ベースのフィルム）、または、前述の材料のタイプの少なくとも 1 つからなる組合せを含むがこれに限らない材料を含むことができる。例えば、材料の特定のタイプの材料は、シリコン（例えば、単結晶、多結晶、非結晶、ポリシリコン、および、Si<sub>3</sub>N<sub>4</sub>、SiC、SiO<sub>2</sub> のような派生物）、GaAs、InP、CdSe、CdTe、SiGe、GaAsP、GaN、SiC、GaAlAs、InAs、AlGaSb、InGaAs、ZnS、AlN、TiN、他の IIIA - VA 材料群、IIB 材料群、VIa 材料群、サファイヤ、クォーツ（結晶またはガラス）、ダイヤモンド、シリカおよび／またはシリケートベースの材料、前述の材料の少なくとも 1 つからなる材料の組合せを含む。もちろん、他のタイプの材料の処理は、所望の組成物の多層基板 1 0 0 を提供するため、本願明細書において記載されるプロセスから利益を得ることができる。特に本願明細書において記載された方法のために適切である好適な材料は、層 1 として半導体材料（例えばシリコン）および層 2 として半導体材料（例えばシリコン）を含み、半導体（層 1）またはガラス（層 2）；シリコンカーバイド（層 2）上の半導体（層 1）、サファイヤ（層 2）上の半導体（層 1）；サファイヤ（層 2）上の GaN（層 1）；ガラス（層 2）上の GaN（層 1）；シリコンカーバイド（層 2）上の GaN（層 1）；プラスチック（層 2）上のプラスチック（層 1）、ここでにおいて、層 1 および 2 は、同じまたは異なるプラスチックである；および、ガラス（層 2）上のプラスチック（層 1）の組合せを含むが、これに限定されるものではない。

30

層 1 および 2 は、フィルムおよび／または基板構造を形成するため堆積するウェーハまたは流体材料を含む様々な供給源に由来することができる。ここで開始材料は、ウェーハの形であり、いかなる従来のプロセスも、層 1 および／または 2 を導くために用いることができる。例えば、層 2 はウェーハから構成されることができ、層 1 は同じまたは異なるウェーハの一部から構成されることができる。層 1 を構成しているウェーハの部分は、機械的な薄層化（例えば、機械的な研磨、切断、研磨加工；化学的な機械研磨；研磨停止；または前述の少なくとも 1 つを含む組合せ）、劈開伝播、機械的な分離（例えば、構造 1 0 0 の平面に垂直で、かつ、剥脱方向において構造 1 0 0 の平面に並列の劈開伝播、または、その組合せ）に続くイオン注入、層分割を誘発する熱、光および／または圧力によって

40

50

続くイオン注入、化学エッティング等から導かれる。さらに、層1および2のどちらかまたは両方は、例えば化学蒸着法、エピタキシャル成長方法等により、堆積または伸張されることができる。

#### 【0107】

即時のこととして発生する多層基板または多層基板に由来する薄膜の重要な利益は、構造は、部分的にまたは実質的に弱い結合領域5に重なる領域3の中または上に形成されることである。このことは、層1が層2から除去される場合、実質的に有用な構造へのダメージの可能性を最小化または除去する。剥離ステップは、一般に注入(例えばイオン注入)、力の適用、または、層1および2を剥離するために必要とされる他の技術を必要とする。

#### 【0108】

特定の実施例において、構造は、構造に回復可能または回復不能なダメージを与える可能性がある局所的注入、力の適用または他の処理ステップを必要としない領域3の中または上にあるので、層1は除去され、構造を修復する次の処理なしで、構造はそこから導かれることができる。強い結合領域6に部分的にまたは実質的に重なる領域4は、一般にその上に構造を有しない。したがって、これらの領域4は、構造へのダメージなく注入または力を受けることができる。

#### 【0109】

層1は、自立したフィルムまたは支持されたフィルムとして除去されることができる。例えば、ハンドルは、層1が層2から除去されるように、層1への取付けのために一般に使用され、ハンドルによって支持されたままである。一般にハンドルは、続いてフィルム、または、その部分(例えば1つまたはそれ以上有用な構造を有する)、他の処理されたまたは代替的にハンドル上に残留するフィルムを意図された基板上に配置するために用いることができる。

#### 【0110】

即時のことの1つの利益は、層2を構成している材料が再利用およびリサイクルされることである。単一ウェーハは、例えば、いかなる周知の方法によって層1を導くために使われることができる。導かれた層1は、上記に記載の残りの部分(層2)に選択的に接合されることができる。薄膜が剥離される場合、次の層1として使用される薄膜を得るため、層2の残りの部分を用いて、プロセスは反復される、層1のための薄膜を導くための層2の残りの部分の使用は、それがもはや実行可能または実用的でなくなるまで、反復されることができる。

#### 【0111】

上記のように、選択的に接合された多層基板の形成が詳述され、三次元集積回路の形成が、選択的に接合された多層基板を使用して次に記載される。

#### 【0112】

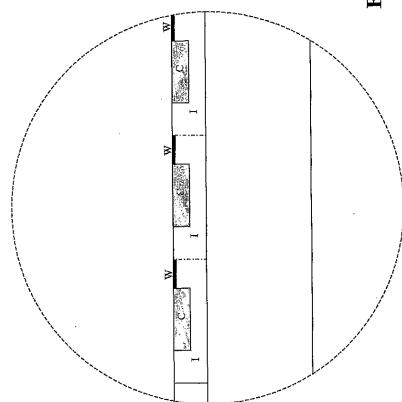

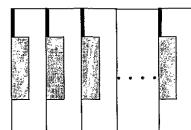

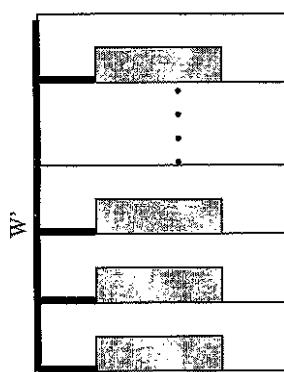

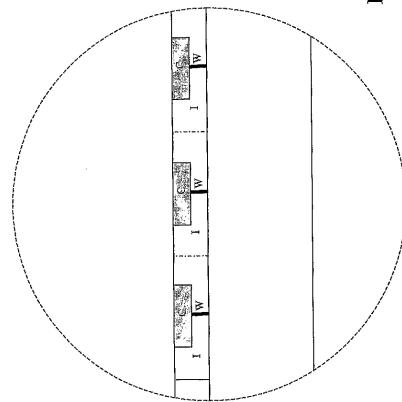

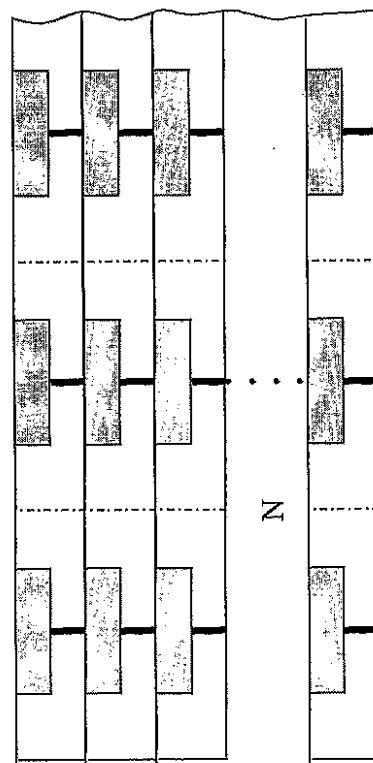

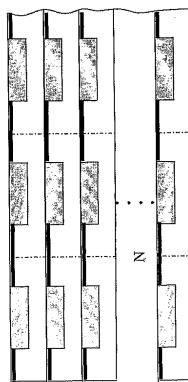

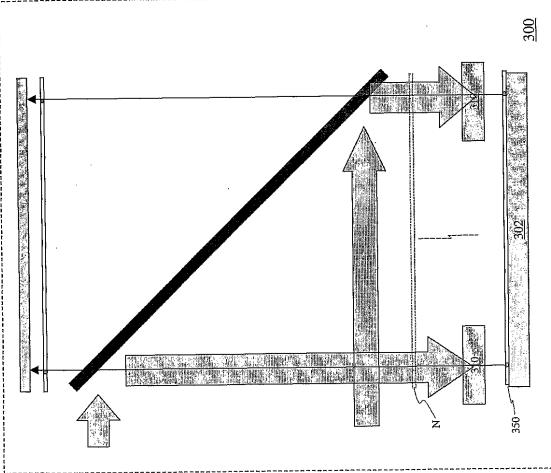

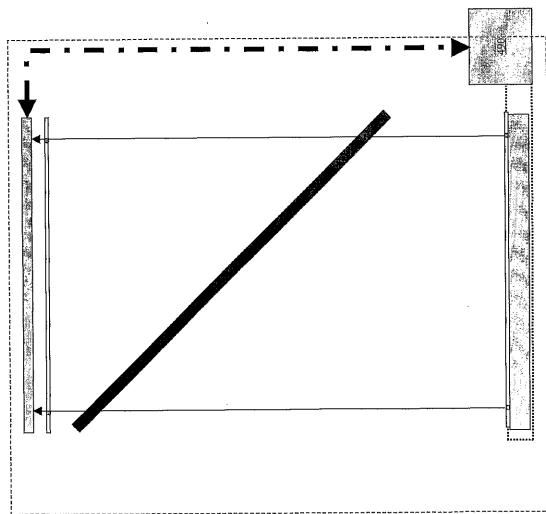

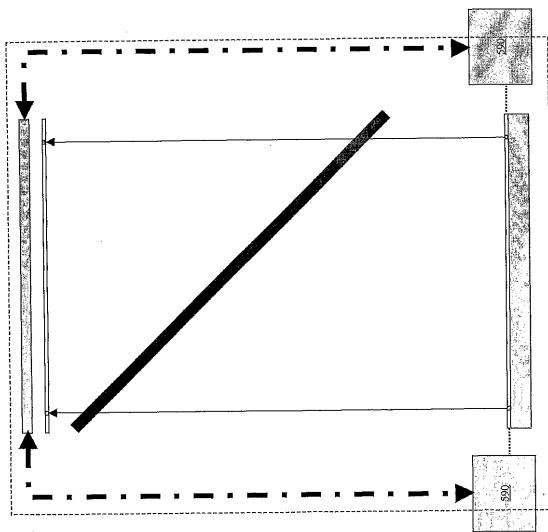

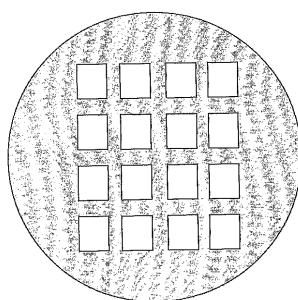

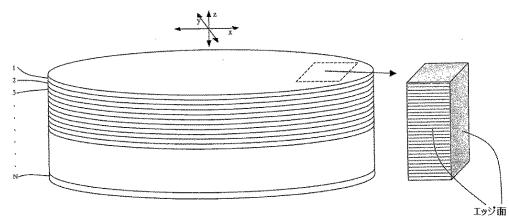

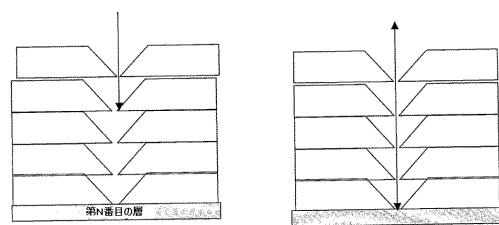

図80を参照する。スタック1...Nウェーハおよびそこからのダイカットの等大の概略図が、示される。明確にするため、座標および定義が示されている。ダイおよびウェーハのスタックは、本願明細書において一般に平面方向として指されるxおよびy座標方向において延長する上部および底面および中間の層を一般に有する。平面方向が表面または中間の層に延長しているいかなる方向も含むことに注意する。いくつかの層は、本願明細書において垂直または三次元と一般に指されるz方向においてスタックされる。

#### 【0113】

ダイカットの後、中間の層および上部および底面に加えて、ダイはz方向において一般に延長している4つのエッジ面を有する。

#### 【0114】

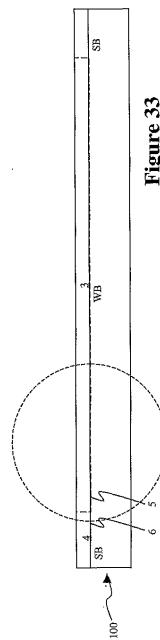

次に図33を参照すると、上述の通り、強い接合領域3および弱い接合領域4を有する選択的に接合された基板100が提供される。図示された実施例が図18で一般に強い結合パターンを有するにもかかわらず、強い結合領域3および弱い結合領域4のいかなるパターンも利用されると理解される。ここにおいて、上記に記載および言及されたように、

回路網または他の有用な素子は、弱い結合領域で形成される。

【0115】

特に本発明は、逐次処理ステップの数を減少させる一方で、機能強化と同様、様々な追加的な機能が提供されることができるという点で、上述したIBMの米国特許No. 6,355,501において都合が良い。

【0116】

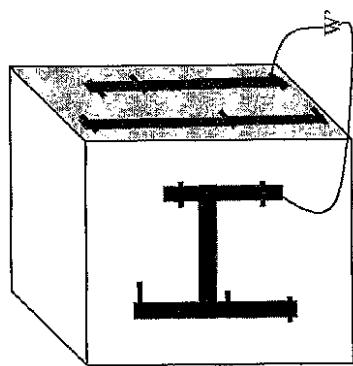

例示的な目的のため、領域は破線の円によって示され、この領域の代替物は、三次元スタックのために適切な回路領域の形成を説明するために様々な分解立体図で記載される。図34を参照する。回路部の1つの例は、三次元集積化のために適切なチップ・エッジ相互接続構成を有して示される。さらに、エッジ端相互接続構成に関するさらなる詳細は、両方とも本願明細書において参照されたものとするファリスによる米国特許No. 5,786,629および、No. 6,355,976において見つけることができる。

10

【0117】

回路部分Cは、選択的に接合された重なった基板の素子層の絶縁領域Iの範囲内で形成される。使用可能な状態で回路部において始まり、回路パッケージの端に延長し、ダッシュドット線で表される電気または光学導体である導体Wは、形成される。導体Wは、x-y平面において、一般にいかなる方向にも延長することができる。バルク領域は、回路部および導体の処理の間、機械的および熱的なサポートとして役立つ。

【0118】

単一の導体だけが、(前述および以下に記載の実施例のすべてにおいて)示される一方で、x-y平面において、一般にいかなる方向にも延長する各々の回路部と関連して複数の導体は、提供されることができる事が認識される。

20

【0119】

導体：これらの導体は、それ自体のアドレスで各々の回路部を符合化し；外部アドレスラインからアドレス情報を受容し；各々の回路部にデータおよび電源を導き；回路部(メモリ)からのデータを受容し；または他の所望の機能に役立つことができる。多導体が使われる場合、それらは独立または冗長構成であることができる。

実施例において、特にそこにおいて、いくつかの独立導体が形成される場合、重なり合う領域は半導体処理では周知のように、絶縁される。

30

【0120】

回路部は、同じまたは異なる可能性があり、様々なトランジスタおよびダイオード配置から形成されることができる。

【0121】

これらの装置は、(同じ垂直に集積化された回路内で)、同じまたは異なるマイクロプロセッサ(電気または光学)(バイポーラ回路、CMOS回路または他の処理回路網)ワンデバイス・メモリーセルのようなメモリ回路部、DRAM、SRAM、フラッシュ、信号受容および/または伝送回路機能などを含む。したがって、様々な製品が現在の方法で形成されることができる。

【0122】

集積化された製品には、プロセッサおよびメモリ、または、プロセッサ、様々なワイヤードおよび無線装置のためのメモリ信号受容および/または伝送回路機能を含む。垂直に集積化する(z方向において)ことによって、極めて高密度チップは、N倍まで(Nは集積化された層の総数を表し、10代、100代または1000代の大きさでさえあることができる)処理速度またはメモリ記憶を改善することができる。

40

【0123】

図35を参照する。ハンドラは、素子層の削除を助けるために用いられる。上記の通り、強い結合領域はイオン注入のような剥離を容易にさせるステップを一般に受けさせられる。素子層はそれから、上記の通り、従来の研磨および他のエッチバック・ステップなしで直ちに除去される(例えば、図23, 26, 29、および32に関する)。回路部および導体が弱い結合領域において形成されるので、これらは一般にこの削除ステップの間、

50

ダメージを受けない。

【0124】

好ましい実施例では、使用されるハンドラは、完全に本願明細書において参照された2002年10月2日出願のPCT特許出願シリアルNo.PCT/US/02/31348名称「壊れやすい対象物を扱う装置と方法、およびその装置の製造方法」に記載されたものである。

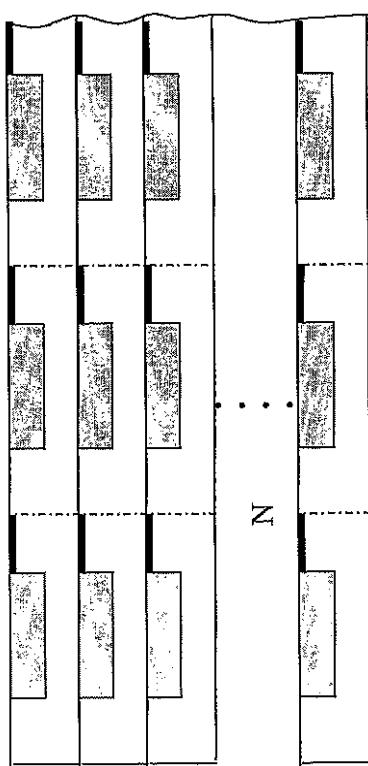

【0125】

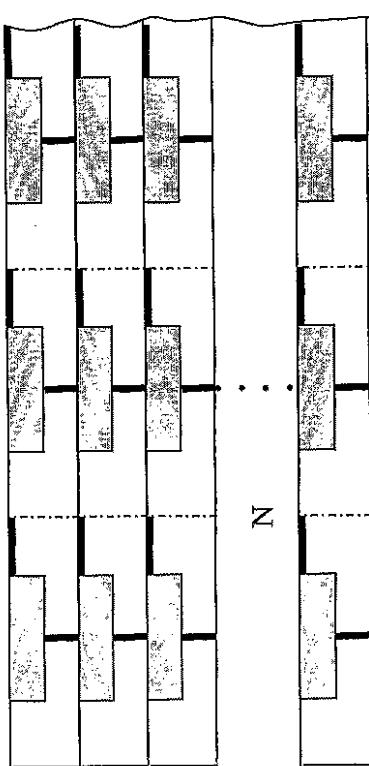

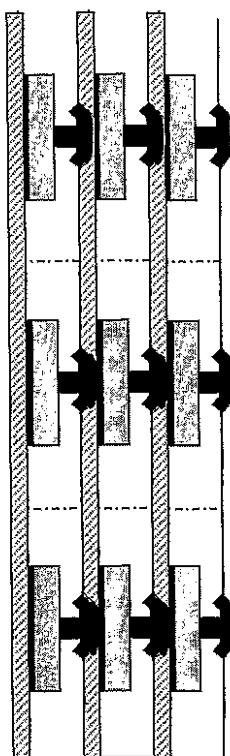

複数の回路部およびエッジが延長した導体を有する素子層は、それから整列配置され、図36に示されるようにスタックされ、さらに本願明細書において詳細に記載される。複数の回路部が垂直に集積化されたスタックを形成するように、層は整列配置され、スタックされる。所望の垂直に集積化された素子に従い、各々の層の回路部は、同じまたは異なる可能性がある。10

【0126】

好ましい実施例において、N層はスタックされ、後に続くすべてのN層は单一のステップにおいて接合される。例えば、これは層間でUVまたは熱的な硬化接着材を用いて達成されることができる。相互接続が各々のチップのエッジにあるので、特定の実施例では、必要とされないにもかかわらず、処理ステップおよび最終的に費用を減少することができる接着材への回路部自体の露出は、不利益ではないことに注意する。10

【0127】

次に図37を参照すると、周知の技術に従って回路部の各々のスタックはダイシングされる。ダイシングが滑らかな平面エッジを提供しない場合、ワイヤリング・エッジは、各々の回路部の導体を露出させるために研磨することができる。20

【0128】

図38は、導体W'（電気または光学）での複数の回路部のエッジ相互接続を示す。これは、各々の回路部の導体を電気的に接触させるため、伝導材料の堆積された薄膜を周知の方法でマスキングおよびエッチングすることによって達成されることがある。他の相互接続方式は、上述した米国特許No.5,786,629および6,355,976においてさらに詳細に記載される。30

【0129】

顕著な重要性は、エッジ相互接続が垂直に集積化されたチップおよび最終生成物（垂直に集積化されたチップ）の処理の間、機能性を提供することである。処理中、エッジ相互接続は診断の目的のために使われることができる。30

【0130】

正しく作動しない回路部は、それから複数の回路部の相互接続の間、避けられることができる。あるいは、このような正しく作動しない回路部は、修復されることがある。なおさらなる代替物として、Nより少ない2つ以上のスタッ�を提供して、正しく作動しない回路部を除去するため、N回路部のスタッ�は、減少することができる（すなわち水平に回路部の平面に沿って切削される）。これは、1つまたはそれ以上の正しく作動しない回路部のスタッ�Nを廃棄する代わりに、劇的に周知の良好なダイ（KGD）の全体のイールドを増加させることができ、各々がN回路部より少ない層を有する2つ以上のスタッ�が、特定の用途のために使われることができる。40

【0131】

図38を参照すると、別の実施例において、エッジ相互接続の垂直に集積化されたスタッ�は、本発明の第2の垂直に集積化されたチップとの垂直的統一を提供することができる。図38で示されるように、エッジ相互接続の集積化されたスタッ�は、実質的にワイヤリング・スタッ�を形成するため、その垂直軸の周りを回転する。回転されたエッジ相互接続の集積化されたスタッ�を第2の垂直に集積化されたチップに結合することによって、ワイヤリング可撓性が達成されることができる。例えば、回転されたエッジ相互接続の集積化されたスタッ�は、横軸上にワイヤリング可撓性を有する複数の層を提供することができる。これは例えば、多数のアドレスラインおよび制御装置回路網がアドレス指定50

能力および制御装置のために必要とされる重いデータ記憶チップのために必要な制御回路において有用である。

#### 【0132】

他の実施例では、例えば上述した米国特許No. 6,355,976において説明されたように、エッジ相互接続が大規模記憶アドレス指定(MSA)のために使われることができる。

#### 【0133】

図39を参照すると、三次元集積化のために適切な相互接続構成を有する、回路部の他の例が示される。回路部分Cは、選択的に接合された重なった基板の素子層の絶縁領域I内で形成される。電気または光学導体であることができ、使用可能な状態で回路部で始まりかつ多層基板の素子層の底部に延長する導体Wが形成される。各々の回路パッケージは、ダッシュドット線によって表される。バルク領域は、回路部および導体の処理の間、機械的および熱的なサポートとして役立つ。導体W(上記したように、その複数が各々の回路部と関連することができる)は、素子層の底部のエッジに延長する、または、代替的に素子層の底部のエッジの方向に延長することができる。それによって、研磨加工ステップは、垂直の相互接続のため、導体を露出させるように実行される。

ハンドラは、それから図35に示されるように一般に素子層を除去するために利用することができます。

#### 【0134】

複数の回路部を有しつつ導体を通じた素子層は、図40に示されるように、それから整列配置されかつスタックされ、本願明細書においてさらに詳細に記載される。複数の回路部が垂直に集積化されたスタックを形成するように、層は整列配置されかつスタックされる。

#### 【0135】

所望に垂直に集積化された素子に従って、各々の層のための回路部は、同じであるまたは異なる可能性がある。

#### 【0136】

好みの実施例において、N層はスタックされ、続くすべてのN層は単一のステップにおいて接合される。これは、例えば層間でUVまたは熱的な硬化接着材を用いて達成される。垂直の層間の接触の問題を避けるために、接点における接着材は避けられる。

図41に最も示されるように、回路部の各々のスタックは、周知の技術によってダイシングされる。

#### 【0137】

図42を参照する。回路部の他の例が、複合型エッジ相互接続を有し、かつ、三次元集積化に適切な相互接続構成を通じて示される。回路部分Cは、選択的に接合された重なった基板の素子層の絶縁領域I内で形成される。電気または光学導体であることができ、使用可能な状態で回路部において始まりかつ多層基板の素子層の底部に延長する導体Wtが形成される。Wtはまた、MEMS装置に用いられる、例えばメカニカルカプラであると理解される。使用可能な状態で回路部において始まりかつ回路パッケージのエッジに延長するダッシュドット線によって表される他の導体Weが提供される。バルク領域は、回路部および導体の処理の間、機械的および熱的な支持として役立つ。導体Wt(上記したように、その複数が各々の回路部と関連することができる)は、素子層の底部のエッジに延長する、または、代替的に素子層の底部のエッジの方向に延長することができる。それによって、研磨加工ステップは、垂直の相互接続のため、導体を露出させるように実行される。WtおよびWeがウェーハに沿って所定の位置に製造され、その結果、エッジが延長する導体は、ウェーハ・エッジに沿ってどこにでも製造されると理解される。

ハンドラは、それから図35に示されるように一般に素子層を除去するために利用することができます。

#### 【0138】

10

20

30

40

50

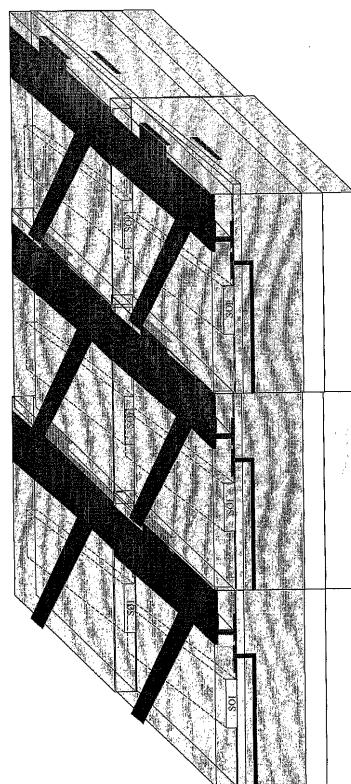

複数の回路部を有しつつ導体が延長した素子層は、図43に示されるように、それから整列配置されかつスタックされ、本願明細書においてさらに詳細に記載される。複数の回路部が垂直に集積化されたスタックを形成するように、層は整列配置されかつスタックされる。所望に垂直に集積化された素子に従って、各々の層のための回路部は、同じであるまたは異なる可能性がある。

好みしい実施例において、N層はスタックされ、続くすべてのN層は单一のステップにおいて接合される。これは、例えば層間でUVまたは熱的な硬化接着材を用いて達成される。

#### 【0139】

次に図44を参照すると、回路部の各々のスタックは周知の技術によりダイシングされる。ダイシングが滑らかな平面エッジを提供しない場合、ワイヤリング・エッジは、各々の回路部のために導体Weを露出させるように研磨されることができる。

#### 【0140】

図45は、全体の相互接続、導体W'（電気または光学）との複数の回路部のエッジ相互接続の一態様を示す。これは、各々の回路部の伝導部分を電気的に接触させるため、伝導材料の堆積された薄膜を周知の方法でマスキングおよびエッチングして達成されることができる。他の相互接続方式は、上述した米国特許No.5,786,629とNo.6,355,976とにさらに詳細に記載される。

#### 【0141】

両方のエッジおよび直通相互接続が使用された場合、一方または両方のタイプが、回路部を相互接続するために用いることができることに注意する。異なる相互接続は、冗長または独立していることができる。あるいは、上記の通り、エッジ相互接続は、主に診断目的のために提供されることがある。さらに代替実施例において、相互接続の両方のタイプは冗長構成を提供するために用いることができる。このことにより、チップ部間の相互接続による垂直に集積化されたチップ故障の可能性を減少させる。

#### 【0142】

直通導体を形成するため、（図39および42に示されるように）、各々のチップ部のための各々の直通導体は、最初に形成され、（例えば、孔にエッチングし、その孔を導電材料で埋めることによって）、そして、続いて回路部は導体の上に形成される。

#### 【0143】

あるいは、図46に記載のように、回路部分Cは、素子層の上または中において最初に形成され、直通導体Wは、回路部分の上部から素子層の上部まで延長する。回路部より上の領域は、示されるように、導体Wおよび絶縁体I（例えば、最適互換性のための絶縁物と同じ材料）を提供するために処理されることができる。

#### 【0144】

次に参照符号が前の図46と同じ構造を指す図47を参照すると、垂直の回路部の相互接続を強化する任意の他の特徴が、示される。各々の回路部の最上位で一般に導体Wbが提供される。この導体Wbは、スタッキング上の層の直通導体Wtからの伝導を最適化するのに役立つ。スタッキングに導かれる接触が層間の接触を提供するために十分であるように、この導体は固体化される材料から構成されることができる。あるいは、隣接した導体は加熱でつながれるように、導体Wbはソルダーバンプから構成することができる。さらに、導体Wbは、隣接した回路部間の電気的接続から構成されることができる。またさらに、導体Wbは、単に光学コネクションのための光導波管から構成されることができる。上述したIBM米国特許No.6,355,501にて説明されたように、各々の層がスタックされる、または、好みしくはすべてのN層がスタックされた後、導体の併合は達成されることができ、いくつかのリフロー動作によって生じるコネクションを伝導するダメージを最小化する。

#### 【0145】

直通導体を形成する他の方法（図39および42示されるように）において、次に図4-50を参照すると、別々の素子層は、回路部分層を形成することができる。

10

20

30

40

50

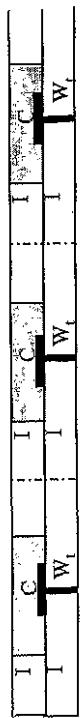

図48を参照する。直通接触を有する他の素子層との接触のために、各々が導体Wbを持つ回路部を有する素子層が示される。

#### 【0146】

導体Wbは、ソルダーバンプまたは固体化された永続導体を有することができる。第2の導体Wb部は、スタックされると上の層の直通導体Wtからの伝導のため、図47に関して前述のように提供されることができることに注意する。

#### 【0147】

図49は、直通導体Wtを有する素子層を示す。図50に示されるように、回路部分層および導体層からなるサブスタックを提供するため、層は、スタックされ、接合され、電気接觸はつながることができる。

10

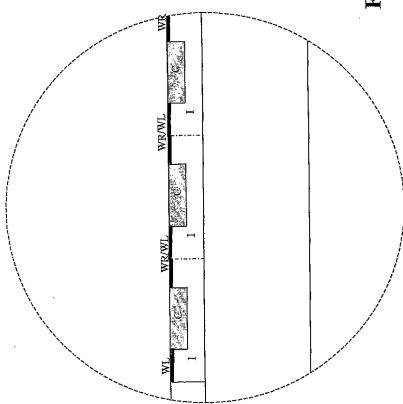

#### 【0148】

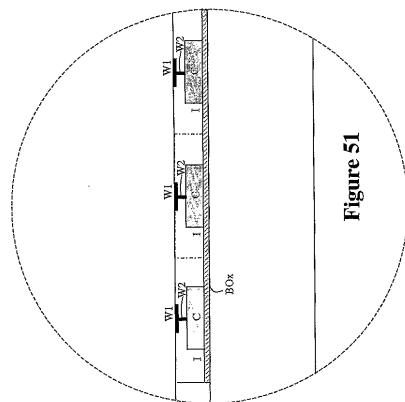

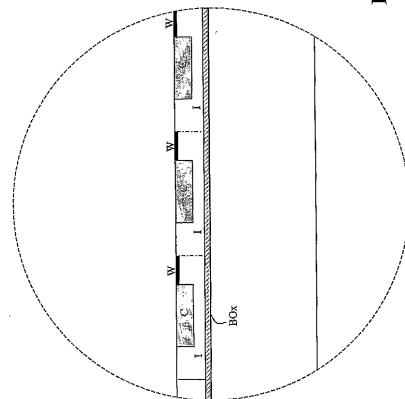

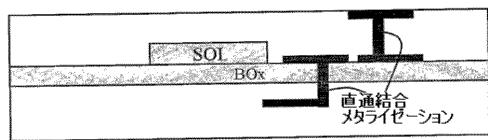

次に図51を参照すると、代替の回路部分層が示される。埋込み酸化物層(BOX)は、バルク性基板および素子層の界面で、一般に素子層において形成される。この埋込み酸化物層は、O<sup>+</sup>イオン注入のような従来技術において公知である様々な方法により、形成されることができる。さらに、素子層がバルク性基板と選択的に接合された前または後に、埋込み酸化物層は形成されることができる。

#### 【0149】

素子層がバルク性基板に選択的に接合される前に、埋込み酸化物層が形成される場合の実施例において、SiOX層は、バルク性基板への選択的な結合の前に素子層の表面で形成されることができる。素子層は、それからバルク性基板に選択的に接合される。強い結合を強化するために結合の前に酸化物層を処理することが望ましいということに注意する。

20

素子層がバルク性基板に選択的に接合された後に、埋込み酸化物層が形成される場合の実施例において、素子層は、例えば、所望の深さ、すなわちバルク性基板および素子層の界面で酸化物層を形成するために注入される酸素であってもよい。強い結合領域の酸化を局所的に妨げるため、素子層の意図された強い結合領域をマスキングすることが望ましい可能性がある。

#### 【0150】

埋込み酸化物層の形成の後、回路部分Cは、素子層の弱い結合領域の埋込み酸化物層に隣接して形成される。導体W2は、回路部と電気的または光学的に接觸して、形成され(例えば、堆積される)、導体W1は、導体W2と電気的または光学的に接觸する。導体W1およびW2が1つのステップまたは複数のステップで形成されることが可能であることに注意する。また、導体W1およびW2がT型を形成することが示される一方で、これらの導体(または同じ目的である単一の導体)はL型、矩形、または他のいかなる適切な形状であることができる。

30

#### 【0151】

素子層がバルク性基板から(上記の通り)除去された後、埋込み酸化物層はそれから露出される。図52に示されるように、埋込み酸化物層の領域は離れてエッチングされ、直通導体W3はその中に形成される。この導体W3は、スタックすると即座に、隣接した素子層の導体W1と相互接続するのに役立つ。

40

#### 【0152】

記載された方法が多少の態様の点において、チップ・スケールで、上述したIBM米国特許No.6,335,501において教示されたものと同様である一方で、現在の方法は、いくつかの利点を有する。上述したIBM米国特許No.6,335,501においては、バルク性基板の削除は、研磨およびエッチバックだけにより、一方で、現在の方法においては、上記の通り、剥脱または他の簡単な削除方法が、弱い結合領域上での回路部の形成、およびバルク性支持物基板に層を支持するための強い結合層の存在のために可能である。さらに、現在の方法は、ウェーハ・スケールにおいて達成可能である。満足なイールドは、層を試験し、続けてN層のスタックを利用して起こることができ、上記の通り、これらのスタックはN層より少ない層を有する。

50

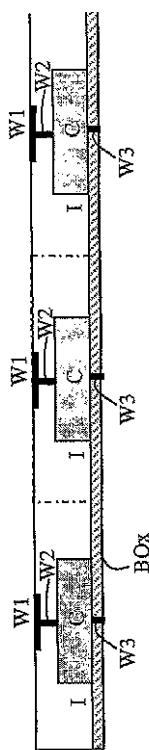

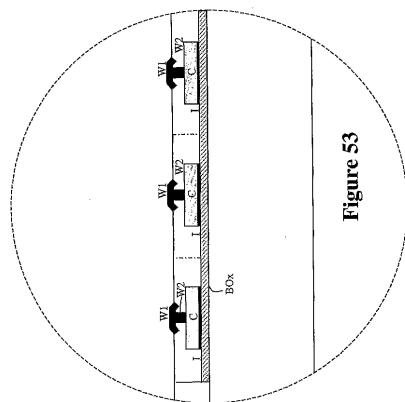

## 【0153】

次に図53を参照する。代替物回路部分層および関連する導体の実施例が示される。埋込み酸化物層(BO<sub>x</sub>)は、バルク性基板および素子層の界面で、一般に素子層において形成される。回路部が形成される領域で、導体はBO<sub>x</sub>の上に形成される。回路領域は形成され、導体W2およびW3(または一体的な導体)回路部の上に形成される。

導体(または導体部)W1は、先細エッジおよび突出した腹部の部分で形成されることに注意する。-とりわけ、これは整列を容易にしておよび導体の機械的な保全性を強化するのに役立つ。

## 【0154】

次に図54を参照すると、素子層がバルク性基板から(上記の通り、好ましくは剥脱によって)除去された後、埋込み酸化物層は、W3領域を形成するため、それから露出される(例えばエッチングされる)。好ましくは、これらの領域は、先細エッジの導体または導体部分W1の形状およびサイズに適合される。

## 【0155】

図55に示されるように、W3領域でソルダープラグは、最終的に導体W3を形成するために提供される。

## 【0156】

図56に示されるように、この導体W3は、スタッキングすると、隣接した素子層の導体W1との相互接続に役に立つ。

## 【0157】

一実施例において、層がスタッキングされると、スタッキングされた層はリフローされることができる。好ましい実施例において、N層が形成された後、全体のスタッキングはリフロー処理を受ける。別の実施例では、スタッキングはセクションにおいてリフローされることができる。

別々の層の導体W1およびW3の形状および勾配は、スタッキングされた層の機械的な整列配置を助けるのにさらに役立つことに注意する。

## 【0158】

次に図64を参照すると、三次元の回路または記憶装置を形成するための素子層のさらなる実施例が、示される。埋込み酸化物層(BO<sub>x</sub>)は、バルク性基板および素子層の界面で、一般に素子層において形成される。この埋込み酸化物層は、公知技術の様々な方法によって形成されることがある。さらに、素子層がバルク性基板に選択的に接合される前または後に埋込み酸化物層は形成されることがある。顧客に提供される、または、後の処理のために格納されることがある「未処理」SOIウェーハ層を導くため、BO<sub>x</sub>層を有する素子層は、上記の通り、除去されることに注意する。

## 【0159】

素子層がバルク性基板に選択的に接合される前に埋込み酸化物層が形成される場合の実施例において、バルク性基板との選択的な結合の前に、SiO<sub>2</sub>層は素子層の表面で形成されることがある。素子層は、それからバルク性基板に選択的に接合される。

## 【0160】

強い結合を強化するため結合の前に酸化物層を処理する、または、局所的に酸化を妨げるため素子層の意図された強い結合をマスキングすることは望ましいということに注意する。

## 【0161】

素子層がバルク性基板に選択的に接合された後に埋込み酸化物層が形成される場合の実施例において、素子層は、例えば、所望の深さ、すなわちバルク性基板および素子層の界面で酸化物層を形成するために注入される酸素である可能性がある。

## 【0162】

埋込み酸化物層の形成の後、回路部分Cは、素子層の弱い結合領域の埋込み酸化物層に隣接して形成される。1つまたはそれ以上の導体Wは、回路部と電気的または光学的に接触して、形成され(例えば、堆積される)、上記の通り、チップのどんな次元のエッジに

10

20

30

40

50

も延長することができる。素子層がバルク性基板（上記の通り）から除去された後、埋込み酸化物層はそれから露出される。

#### 【0163】

B O X 層は、透過的絶縁体層として役立ち、および、層がスタックされる場合、本願明細書において記載されるように他の層から一方の層を保護するために役立つことができる。

さらに、B O X 層は、回路部を絶縁または導体のノイズ・シールドを提供するため、即座の絶縁物を提供する。さらに、例えば図 5 2 および 5 4 と IBM 米国特許 N o . 6 , 3 5 5 , 5 0 1 とに関連して上記に記載されたように、孔は B O X 層においてエッティングされることができる。

10

#### 【0164】

図 5 7 を参照すると、回路部の他の例は、三次元集積化に適切なチップ・エッジ相互接続構成を有して示される。エッジ相互接続構成に関するさらなる詳細は、上述のファリスによる米国特許 N o . 5 , 7 8 6 , 6 2 9 および、N o . 6 , 3 5 5 , 9 7 6 において見つけることができる。本実施例において、回路部分 C は、選択的に接合された重なった基板の素子層の絶縁領域 I の範囲内で形成される。ここで、導体は、W L 、W R および W R / W L として表される各々の回路部の多数のエッジの上に形成される。しかしながら、その導体は、層に対して全方向に（例えば、回路部のすべての 4 つの主なエッジに）垂直な方向に延長する、または任意に延長することに注意する。

20

#### 【0165】

複数の回路部および多数のエッジが延長している導体を有する素子層は、図 5 8 に示されるように、それから整列配置され、スタックされる。複数の回路部が垂直に集積化されたスタックを形成するように、層は整列配置されておよびスタックされる。所望の垂直に集積化された素子に従い、各々の層のための回路部は、同じまたは異なる可能性がある。さらに、エッジ相互接続が各々の層に示されるにもかかわらず、特定の層が 1 つ、2 つ、3 つ、または 4 つのエッジ相互接続を有することができる予測される。いくつかの層が直通の相互接続（1 つまたはそれ以上）のみを有することはさらに予測される。いくつかの層が 1 つ、2 つ、3 つ、または 4 つのエッジ相互接続および 1 つまたはそれ以上の直通の相互接続を有することは、またさらに予測される。

30

#### 【0166】

好みの実施例において、N 層はスタックされ、後に続くすべての N 層は单一のステップにおいて接合される。例えば、これは層間で U V または熱的な硬化接着材を用いて達成されることができる。相互接続が各々のチップのエッジにあるので、特定の実施例では、必要とされないにもかかわらず、処理ステップおよび最終的に費用を減少することができる接着材への回路部自体の露出は、不利益ではないことに注意する。

30

#### 【0167】

次に図 5 9 を参照すると、周知の技術に従って回路部の各々のスタックはダイシングされる。ダイシングが滑らかな平面エッジを提供しない場合、ワイヤリング・エッジは、各々の回路部の導体を露出させるために研磨されることがある。

40

#### 【0168】

図 6 0 を参照すると、いくつかのまたはすべての層もまたページに（前および / または後に）垂直なエッジ相互接続を有することができる予測されるにもかかわらず、導体 W ' R と W ' L （電気または光学）との複数の回路部のエッジ相互接続が示される。これは、電気的に各々の回路部の導体を接触させるため、伝導材料の堆積する薄膜を周知の方法でマスキングおよびエッティングすることによって達成されることがある。他の相互接続方式は、米国特許 N o . 5 , 7 8 6 , 6 2 9 および、N o . 6 , 3 5 5 , 9 7 6 に記載される。

40

#### 【0169】

顕著な重要性は、エッジ相互接続が垂直に集積化されたチップおよび最終生成物（垂直に集積化されたチップ）の処理の間、機能性を提供することができる。処理中、エッジ相互接続は診断の目的のために使われることができる。様々な選択が利用できる

50

。例えば、エッジ相互接続の1つまたはそれ以上は、診断のために存在することができ、他のものは、電源、データ、メモリーアクセスまたは個々の回路部の他の機能のために存在することができる。素子イールドを改良するために、エッジ相互接続の1つまたはそれ以上は、冗長構成であることができる。エッジ相互接続は、増加する機能のための回路部の異なる領域に独立して入ることができる。カスタマイズされた相互接続が高密度記憶装置において提供されると、大規模な記憶アドレス指定もまた使用可能である。

#### 【0170】

図61は、相互接続W'なしで示された垂直に集積化されたチップの等角図を示す。

#### 【0171】

図62は、相互接続Wによって示される可能な垂直に集積化されたチップを示す。所望の機能に従い、相互接続Wの様々な組合せが提供されることに注意する。 10

#### 【0172】

1つ、2つ、3つまたは4つのエッジの使用は、任意の直通導体と同様に（例えば、スタックの上部および底部層で）、三次元の垂直に集積化されたチップの6つ（または、他の形状は提供される場合、それ以上）のすべての側面を使い果たして、（相互接続だけと比較すると）桁違いの相互接続位置および非常に高いトラフィック相互接続をさらに許容する。さらに多導体は、例えば、特に層における回路部の異なる部分または多重性と関連して各々のエッジから延長することができる。

#### 【0173】

図63を参照する。回路部の他の例は、三次元集積化のために適切なチップ・エッジ相互接続構成を有して示される。本実施例において、回路部分Cは、選択的に接合された重なった基板の素子層の絶縁領域I内で形成される。ここで、1つまたはそれ以上の導体は、回路部の上に素子層の表面全体にわたり形成される。一般に、チップ部全体に延長する（図63に示されるように左右の）部分は、片方の故障、または、垂直に集積化されたチップの製造において相互接続できない場合にイールドを増加させるための冗長構成のために提供される。上記の通りに、例えば、回路部の異なる領域に入るために多導体はウェーハ全体に提供されることに注意する。 20

#### 【0174】

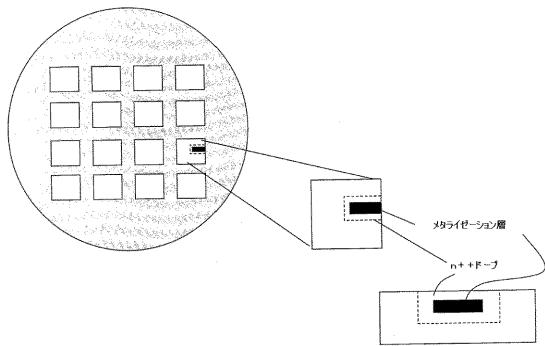

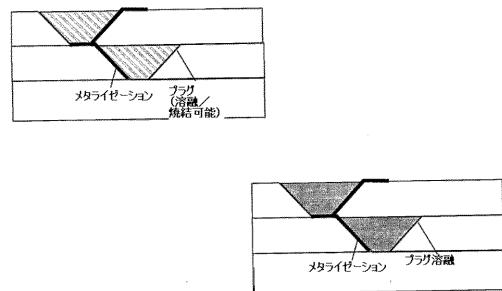

次に図81および82を参照すると、本発明（図81）と上述したIBMの米国特許NO.6,355,501（図82）で開示される方法との比較が示される。図82（IBM）は、BO×層上のSOI装置を示す。メタライゼーションは、Z方向、すなわち、SOI装置の上部および底部での垂直の直通結合のみにおいて提供される。 30

#### 【0175】

特に、本発明については、エッジ相互接続は、示されるように提供され、上記のように、全体の処理ステップを減少して拡張装置効率を提供し、診断および拡張されかつ簡略相互接続のような改良された機能を許容する。

#### 【0176】

特定の実施例において、サイズ（接触面積）、導電率（レデューシング固有抵抗）またはその両方を増加させることによって、本願明細書において記載されるウェーハ・スケールまたはチップ・スケールがスタックされた素子の相互接続を強化することは、望ましい。 40

#### 【0177】

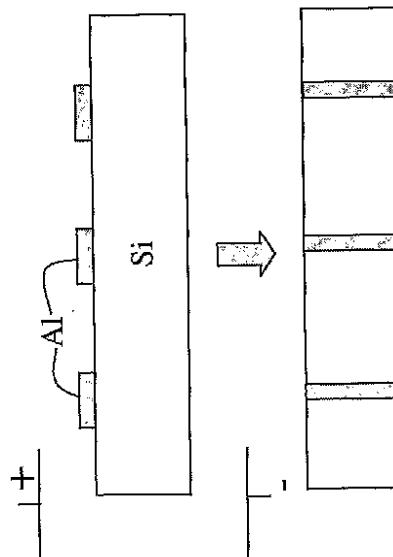

次に図83を参照すると、エッジ相互接続導電率を強化する一実施例が示される。一般に、イオン注入はメタライゼーション層の（例えば下の）領域の過剰なドープ（n<sup>++</sup>またはp<sup>++</sup>）を提供する。このようなn<sup>++</sup>またはp<sup>++</sup>ドープは、従来技術において周知である。したがって、このように提供される相互接続は、例えば、エッジが露出した導体を結合するため全体の導電率を強化する。このステップは、メタライゼーションの前または後、および、一般に、メタライゼーションを有する回路部を含む素子層が除去される前に、（または個々の素子が除去される前に）に起こることができる。

#### 【0178】

相互接続、特に直通相互接続を形成する他の方法において、熱電気移行処理が、使われることができる。熱電式移行ができるアルミニウムまたは他の適切な伝導性の金属は、シリコン層の上に堆積する。上昇した温度（例えば200以上）で電界が適用されると、アルミニウムは、伝導性の経路を提供する基板を通じて移行する。このプロセスは、少なくとも厚さ最高10マイクロメートル（移行方向）の直通相互接続を形成するために用いることができる。熱電式移行処理は、素子層の上に形成される回路部の直通の相互接続を残して、多層基板の素子層で実行される。

## 【0179】

あるいは、バルク性層への素子層の選択的な結合の前に、層は熱電式移行を受けることができる。

10

## 【0180】

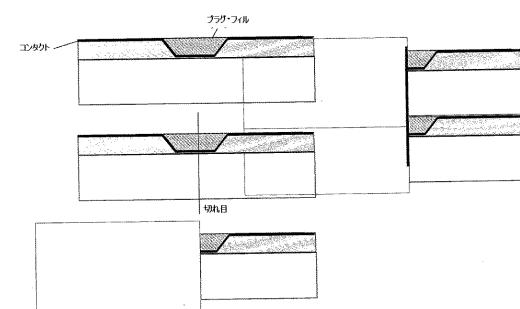

図88を参照すると、接触面積および導電率を強化するプラグ充填法が示される。例えば、優先エッティングのための一般に45°角の先細エッティングが基板において形成される。導体は、基板の上部全体に形成され、先細エッティングされた領域を横切る。小さい角（より好ましくは、60°未満で、さらに好ましくは45°未満）が導体の機械的な故障の可能性を最小化するために要求されることに注意する。

## 【0181】

先細エッティングされた領域は、それから適切な伝導性の材料でプラグ充填される。

## 【0182】

この先細エッティング部分は、以下に明らかになるように、好ましくはエッジ・ダイに位置する。

20

## 【0183】

プラグは、伝導性のプラグ材料および導体を露出させて、切れ目に沿って切断される。いくつかの層は、スタッカされかつエッジが結合され、それによって、接触抵抗は、伝導性のプラグ部の存在によりかなり最小化される。

## 【0184】

バイアホールは、形成されたメタライゼーションへのアクセスのために（例えば好ましくは約45°の先細エッティング）エッティングされることができる。バイアホールは、溶融可能または焼結可能な伝導性の材料によって充填される。

30

## 【0185】

図89を参照する。現在の方法で形成される直通相互接続が記載される。x-y平面上において延長するメタライゼーションはエッジ結合として延長することができることに注意する。先細バイアホールは、より低層においてエッティングされる。メタライゼーションはその中に形成され、バイアは溶融可能または焼結可能な材料で満たされるプラグである。次の層は、第1層の上に形成される。先細バイアホールは、上部層においてエッティングされる。メタライゼーションは最上層の上に形成され、バイアは溶融可能または焼結可能な材料で満たされるプラグである。

## 【0186】

一実施例において、伝導性のプラグ材料は、層がスタッカされると、焼結または溶解される。これは整列結合すなわち、一時的な結合でない、接続が接触すると除去されず、常に唯一の不变な結合として役立つ十分な結合強さでない結合にさらに役立つことができる。

40

好ましくは、溶融可能または焼結可能な導電材料は、好ましくは融解または、伝導性のプラグ材料を溶解または焼結するために適切な他の結合である最終的な結合ステップまで溶解または焼結しない。融解および伝導性の溶融／焼結の後、または、融解および伝導性の溶融／焼結の前に重なった素子が顧客に提供されることができる。

## 【0187】

1つまたはそれ以上エッジ相互接続を提供することによって、上述したIBM米国特許NO.6,355,501にて説明されたように、直通相互接続のみと比較すると、直通相互接続で実行可能ではない様々な追加的な特徴が提供されることがある。

50

## 【0188】

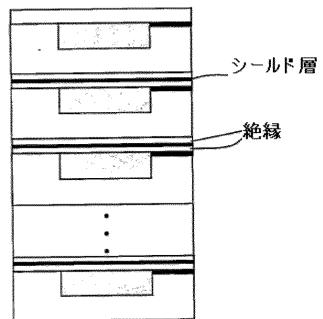

例えば、図65を参照すると、シールド層が隣接する層の間で提供されることがある。これは、回路部分の層間の交差ノイズを妨げる。

## 【0189】

直通結合では、ノイズは1つの層から次の層へ放射する。これは、垂直にスタックされた回路の周知の問題である。本発明の好適な実施例がエッジ接合に依存するので、シールド層が提供される。シールド層は、銅、タンゲステン、モリブデンまたは他の伝導性の材料のような材料で形成される。特定の実施例において、このシールド層は、熱を除去するためにさらに役立つ。シールド層および隣接したメタライゼーション層は、周知のように最適に断熱される。有益に、1つの層によって作成されるいかなるノイズも隣接層に伝達されない。これは、電源、アナログ、RF、デジタル、オプティカル、フォトニック、MEMS、微小流体からなる有用な素子、および、有用な素子の前述のタイプの少なくとも1つからなる組合せの群から選択される組合せを含む混合垂直集積化回路にとって特に望ましい。

10

## 【0190】

シールド層は、クラッド層を形成するように光学的に結合された回路においてさらに使われることができる。このシールド層はまた、従来技術で周知のように極端な高速および極端な広いバンド幅伝送線を作成するために接地面として役立つことができる。

20

## 【0191】

IBM米国特許NO.6,355,501は、その中の方法が直通結合のみを教示するので、このようなシールド層を含まないということに注意する。

20

## 【0192】

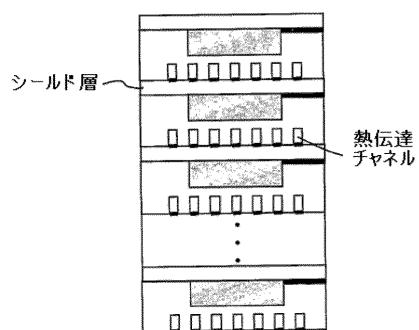

図66を参照すると、熱散逸を可能にするため、チャネルが層の間で提供されることがある。熱除去のためのチャネルは、熱除去のための流体（液体または気体）を担持することができる。

30

## 【0193】

例えば、冷却のため層を通じて流動させるため、チャネルは受動的な空気または他の分離した冷却流体を許容することができる。あるいは、微小流体ポンプまたは他の装置は、目立たない層として提供された空気または他の任意の冷却流体に含まれることができる。一般に、この議論のために、発明の多重層構造において、微小流体素子は、追加的に多層基板に製造されると理解される。相互接続およびバイアホールが微小流体素子の溝、井およびチャネルのための類似した電気機能に役立つと理解される。電気または光学制御装置を必要としたいくつかの動電学的な微小流体素子を除いて、大部分の微小流体素子は、集積化された回路製作において一般に使用される製造技術でのマイクロスケール構造からなる機械的な素子である。したがって、本願明細書において使われるよう、当業者は、相互接続、導体、電極およびバイアホールのような用語が、微小流体素子の場合のポート、溝、井およびマイクロチャネルを指すことができるということを理解する。MEMS装置および微小流体素子の両方のために、所望の素子の一連の細い水平なスライスへの分解がなければならない。一般に所望の層厚は、2から10ミクロンの間にある。これらのスライスの各々は、多くのMEMSまたは微小流体の周知のウェーハ加工技術のうちの1つを用いてシリコン・ウェーハ上に作成される。MEMSまたは微小流体スライスがウェーハの上面に作成されるならば、スライスは、ウェーハから離れるように剥離され、MEMSまたは微小流体構造を作成する他のスライスの上にスタックされる。この連続した剥脱およびスタックを通じて、複合内部構造体および形状を有し、高さ1センチメートルまでのMEMSまたは微小流体手段が作成されることがある。

40

図67を参照すると、これらのチャネルは、熱散逸をさらに助ける熱伝導性の部分（すなわち溶着金属）を含むことができる。あるいは、これらのチャネルは、例えば、上述した米国特許NO.6,355,976にて説明されたように、ワッフル状の構造として形成されることができる。

50

## 【0194】

次に図 6 8 を参照すると、各々の回路部と関連しているチャネルまたは他の熱伝導性の部分は、それがハンドラによって維持される場合、素子層の下側の上に形成されることができる。

#### 【 0 1 9 5 】

これらのチャネルは、上記の通り、回路部および導体の形成後に形成されることがある。シールド層は、図 6 6 および 6 7 に示された構造を形成するため、任意にこれらのチャネル上に直接形成されることがある。

#### 【 0 1 9 6 】

あるいは、シールドおよび / または熱伝導性の部分は、バルク性基板への素子層の選択的な結合の前に素子層の下側の上に形成されることがある。

10

#### 【 0 1 9 7 】

さらに、シールドおよび / または熱伝導性の部分は、図 6 4 - 6 6 に示される構造を形成するため、整列配置され、スタックされ、結合される 1 つまたはそれ以上分離した層として形成されることがある。

#### 【 0 1 9 8 】

もう 1 つの実施例では、チャネルは、バルク性基板への素子層の選択的な結合の前に形成されることがある。例えば、上記の通り、弱い結合領域を形成する 1 つの処理技術は、弱い結合領域 5 の表面のエッチングを含む。

#### 【 0 1 9 9 】

このエッチング・ステップの間、柱 9 は表面 1 A ( 図 8 )、2 A ( 図 9 ) または 1 A および 2 A の両方との上の弱い結合領域 5 において定義される。

20

#### 【 0 2 0 0 】

柱は、柱を残した選択エッチングによって定義されることがある。柱の形状は、三角形、ピラミッド型、矩形、半球状、または他の適切な形状である可能性がある。あるいは、柱は伸ばされる、またはエッチングされた領域に置かれることがある。上述した他の処理技術は、層 1 ( 図 1 2 )、2 ( 図 1 3 ) において弱い結合領域 5 に、例えばエッチング、機械加工または両方 ( 使用される材料に次第で ) によって形成されたボイド領域 1 0 ( 図 1 2 および 1 3 ) の介在物を含む。したがって、第 1 の層 1 が第 2 の層 2 に接合する場合、続いて起こる剥離を容易にする強い結合領域 6 と比較すると、ボイド領域 1 0 は結合を最小化する。

30

#### 【 0 2 0 1 】

柱およびボイド領域の両方の選択的な結合の目的のため、結合される材料の結合表面領域がより少ないので、弱い結合領域 5 の全体の結合強さは、強い結合領域 6 での結合よりも ( 訳注 \* 7 ) 非常に弱い。熱散逸のために、これらの柱またはボイド領域もまた、チャネルを定義する。任意に、これらのチャネルは、上記の通り、その中に堆積する熱伝導材料を含むことができる。

#### 【 0 2 0 2 】

図 6 5 - 6 7 のこれらの特徴が上述した IBM 米国特許 N O . 6 , 3 5 5 , 5 0 1 の教示に従う直通コネクタを用いて事実上形成されることがないことに注意する。

40

上記の通り、導体は適切な伝導材料を回路部と使用可能に電気または光学接触して置くことによって形成されることがある。加えてまたは代替的に、導体は選択的に接合された素子層を形成するプロセスにおいて、本質的に形成されることがある。

#### 【 0 2 0 3 】

上記の通り、強い結合領域を形成する処理技術の 1 つは、表面 1 A ( 図 2 ) または 1 A および 2 A の両方との弱い結合領域 5 で、1 つまたはそれ以上の金属領域 8 の使用を含む。

#### 【 0 2 0 4 】

例えば、Cu、Au、Pt、または、その組合せまたは合金を含むがそれらに限定されない金属は、弱い結合領域 5 に置かれる。層 1 および 2 が結合すると、弱い結合領域 5 は、弱く結合される。強い結合領域は、処理されていないままであり、( ここにおいて、結

50

合強さの差は、弱い結合層 5 および強い結合領域 6 に関して弱い結合比に対する必要な強い結合を提供する) または、強い凝着を促進するため、上記に記載された、または下記のように処理されることがある。

#### 【 0 2 0 5 】

伝導層が素子層の弱い接合側面で予め形成されて、回路部の処理の準備ができる。特定の実施例において、回路部は予め形成された伝導層を接触させるために十分な深さに形成されることがある。特定の他の実施例において、予め形成された伝導層は、次のレベルの導体の少なくとも一部として役立つことができる。所望の伝導パターン(訳注\*8)を形成するため、予め形成された伝導層が残される、または、エッティングされることはいうまでもない。

10

#### 【 0 2 0 6 】

あるいは、素子層の下側で、弱い結合の目的のためのメタル層を形成する代わりに、複数の処理技術が所望のパターンの伝導層においてメタル層を形成するために用いることができる。さらに、メタル層は 1 つまたはそれ以上他の処理技術の前に形成されることがある。

#### 【 0 2 0 7 】

他の実施例では、スタックの分離した層は、相互接続のために提供されることがある。この層は、使用可能な状態で、メッキされた(絶縁)エッジ・ワイアの必要を最小化する一方で、輻輳を避けるため、経路選択およびプリッジングを可能にする。例えば、本願明細書において記載されるように、その層が輻輳する層である場合、図 6 2 の水平な(x 方向)関係は層内部で形成されることがある。本願明細書において記載される様々な方法は、記載されたように、ウェーハ・スケールにおいて好ましくは実行される。しかしながら、多数の特徴がチップ・スケール上の垂直に集積化されたチップ製造のために非常に有用であることは、予測される。

20

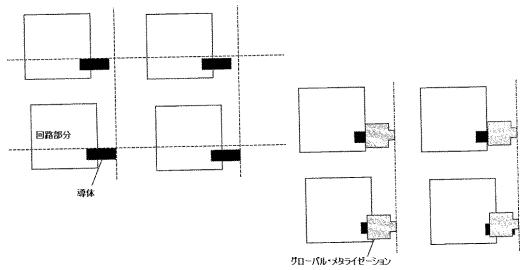

#### 【 0 2 0 8 】

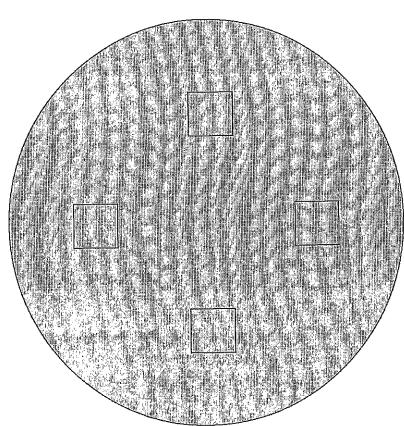

次に図 6 9 を参照すると、複数の選択的に接合された回路形成領域(白で示された)を有する選択的に接合された多層基板が表される。明確にするため、ほんの少数の典型的な回路領域だけが示され、100 個代または 1000 個代の回路部が単一ウェーハに提供されることでできることに注意する。選択的に接合された多層基板の残りの陰影をつけられた部分は、上記を記載されたように、強い結合によって一般に結合される。図 7 0 は、この一連の選択的に接合された回路部分の側面図を示す。これらの強い結合領域は、処理および/または剥脱の間、回路または素子部の構造的整合性を維持するため、一般に強い結合領域の堀に似ている。選択的に接合された回路部を(例えば、回路処理の後に)除去するため、図 7 1 に概略的に示されるように、また、上記の通りの剥離技術で各々の回路部は除去されることができる。SOI チップを提供するため、上記の通り、素子層はその中に WB または WB および SB 領域の両方で BOX 層を有することができることに注意する。いくつかのスタックされた層の整列は、周知の整列法によって達成されることがある。上述した IBM 米国特許 NO. 6,355,501 に記載されるように、光学整列が使われ、それによって、隣接層(例えば、透過的領域と関連した)上の基準マークは、周知の光学的手段を用いて互いに整列される。その参考文献も、自己整列プラグをその方法において開示し、それによって、機械的な相互接続(例えば、本願明細書において示される図 5 3 - 5 6 に関連して)が使用される。

30

40

#### 【 0 2 0 9 】

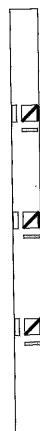

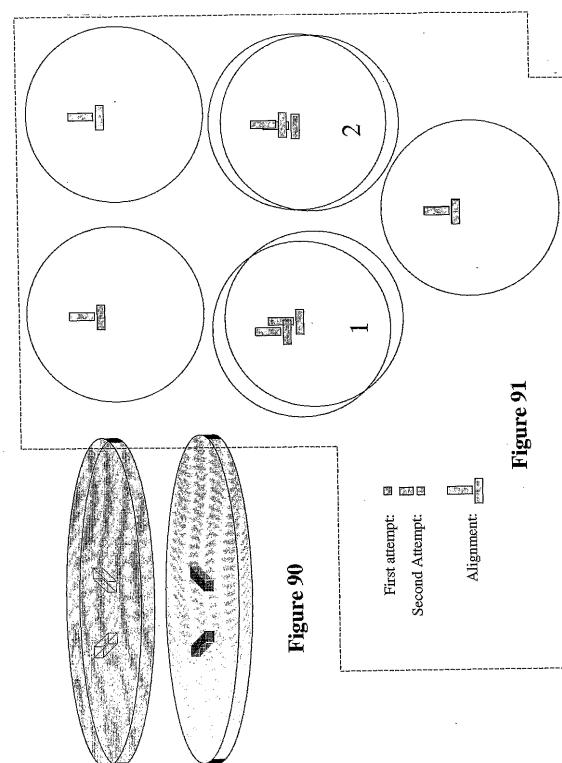

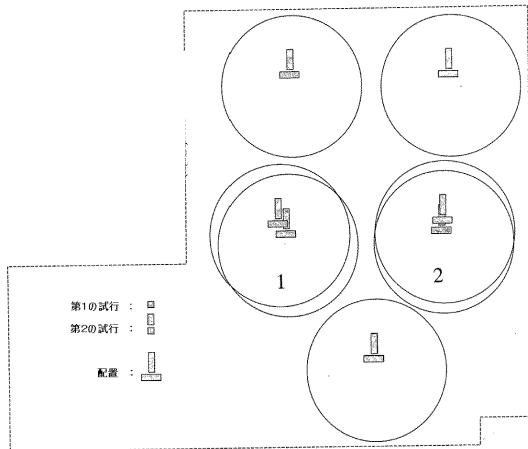

もう 1 つの実施例では、図 9 0 を参照すると、他の機械的な整列方法が、素子層ウェーハ・スタッキングと連携した使用が提供される。機械的な突出またはポストは 1 つの層に提供され、受容孔は他の層に提供される。それらが機械的に適合した場合、整列は達成される。

#### 【 0 2 1 0 】

さらにもう 1 つの実施例では、整列は上述した米国特許 NO. 6,355,976 において開示される方法で実行されることがある。

50

## 【0211】

そこに図示されるように、固定された基準が整列ステーションで使われ、層は基準との比較で整列され、UVで硬化可能な接着材が適用され、および、層は前にスタックされた層（または基板）上にスタックされ、累積誤差の積重ねを誘発する前の層の基準マークと比較して、固定された基準点に基づいて正確な整列を維持する。各々の層がスタックされると、紫外線光は適用される。

## 【0212】

複数の層を整列配置する方法およびシステムは、整列配置される層の投影された画像を利用する、そこにおいて、投影された画像は、整列配置される層またはスタックから離れた整列基準に合わせることができる、このことにより上記したエラー増幅を誘発する中間層整列を除去する。10

## 【0213】

この方法は、第1層の機械的な基板への配置を含む。第1層および機械的な基板との間に、好適な実施例で、低粘性接着材が含まれる。この低粘性接着材は、（例えば、紫外線に露出されると）、好ましくは重合可能であり、任意にこの接着材は、分解可能である。ここにおいて、代わりの接着剤は、本願明細書において記載されるステップによって形成された後、永続的に多層を共に結合するために用いることができる。

## 【0214】

システムは、第1層に関して45°の角で一般に整列配置される偏光反射器をさらに含む。光の供給源は、偏光反射器の方へ向けられ、かつ、第1層の方へ向けられる。加えて、1/4波長位相制動機は偏光反射器と第1層との間で配置される。この1/4波長位相制動機は随意であり、分極状態は1/4波長位相制動機によって逆転するので、反射器から反射される偏光は、続いて層1から反射することができ、偏光反射器を通じて伝達することができる。20

## 【0215】

層1は、1つまたはそれ以上の整列マークをさらに含む。これらの整列マークはエッチングされた領域、層に適用された材料、形成された領域、または他の周知の整列マークであることができる。偏光または偏光されない光が偏光反射器の方へ伝達される場合、光は、これらの整列マークから反射し、特定の実施例において、1/4波長位相制動機を通じて戻り、整列マークの位置の画像を投影するため、続いて偏光反射器を通過する。30

## 【0216】

整列マークの位置の画像は、整列基準と比較される。この整列基準は、第1層上の整列マークに対応する整列マークを含む。第1層が適切に配置されている場合、例えば、コンパレータで測定されるので、さらなる動作は必要とされない。しかしながら、層が整列配置されない場合、光は、コンパレータまたはディテクタで検出される整列基準を通過し、偏光反射器で反射される反射光からの整列基準の整列マークが整列配置されるまで、適切なX-Y-S subsystemのシステムが、第1層をx方向、y方向および/または角方向に移すために役立つ。検出回路が空値を検出する（すなわち、第1層からの光が整列参照上の整列マークと整列する）場合、層は整列配置する。

## 【0217】

あるいは、整列マークは、光が反射しないように偏光され、特定の偏光の波長は、層の残りのマークされない部分から反射するものが選択される。したがって、整列基準上の整列マークの位置以外のすべての部分で光が反射される場合、空値は達成される。40

## 【0218】

好みの実施例において、空値検出器またはコンパレータは、自動整列プロセスが達成されるように使用可能な状態でX-Y-S subsystemに連結する。すなわち、空値検出器が光を検出する場合、空値が検出されるまで、X-Y-S subsystemは調整される。

## 【0219】

さらに代替実施例において、整列が正しい場合空値を検出する代わりに、例えば、光は整列基準の開口または透過的部分（使用する光に関して）を通じて提供される整列マーク50

に対応して伝達されることができる。ここにおいて、光は整列が適正である場合のみ通過する。

#### 【0220】

記載されたプロセスは、第2層、第3の層などのためにN番目の層により反復されることが可能。投影システムの1つの代替物は、走査プロセスを含み、それによって、整列基準への反射が適正なソフトウェアでまたは他のコンパレータで処理することができる反射されたレーザー光線によって、表面は走査される。これは、周知のフーリエ光学および他の走査および検出システムの使用を含むことができる。

#### 【0221】

このシステムの重要な利点は、整列基準が一定に残る、または、整列およびスタッキング動作を通じて公知であるので、先の層（複数）のエラーのためのエラーが除去されることである。N層は、個別に整列基準にすべて合わせられ、したがって、N層のスタックを有する所望の最終生成物は、適当に整列される。この方法で、先の層に関して整列配置されることに対して個々の層の各々が周知または一定の参照に関して整列配置されるので、最大の正確さが達成されることがある。したがって、最悪のケースで、整列は、N層まで各々増加されるエラーに対して単一のエラーのために外れてしまうので、最大の正確さが達成されることがある。

#### 【0222】

N層が整列配置でスタックされた場合、それらは、上記した接着材によって共に接合され、および上述のようにそれらの接着材はまた、分解されかつ他の接着材に置き換えられる。

#### 【0223】

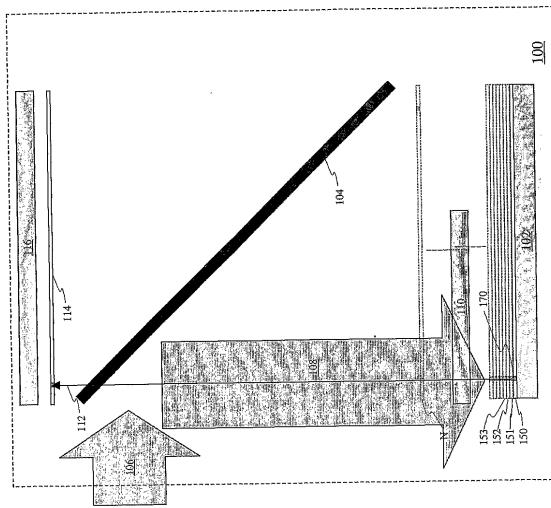

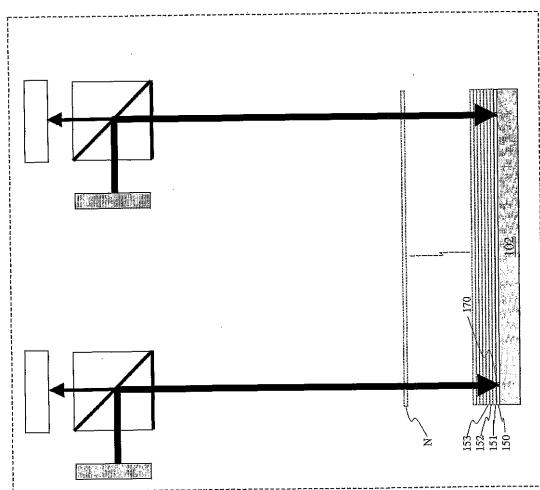

図72を参照すると、例示的なシステムおよび方法が記載される。方法は、機械的な基板102上への整列マーク170を含む第1層150の配置を含む。整列マーク170は、点、線、カーブ、形状、または、堆積、エッティング等により層の上または内部に形成された他のマークから構成することができる。さらに記載されるように、整列マーク170は一般に特定の偏光を反射する。

#### 【0224】

システムは、一般に、第1層150に関して45°で整列配置される偏光反射器104をさらに含む。光源106は、偏光反射器104の方へ向けられ、偏光108は、第1層150上の整列マーク170の方へ向けられる。加えて、1/4波長位相制動機110は、偏光反射器104と第1層150との間で配置される。この1/4波長位相制動機110は、偏光状況が1/4波長位相制動機110によって逆転すると、反射器104から反射された偏光108が、続いて整列マーク170から後部112を反射し、偏光反射器104を通じて伝達することを可能にする。

#### 【0225】