**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                       |                             |

|---------------------------------------------------------------------------------------|-----------------------------|

| (51) Int. Cl. <sup>6</sup><br>G02F 1/136                                              | (45) 공고일자<br>1999년06월01일    |

| (21) 출원번호<br>10-1996-0005055                                                          | (11) 등록번호<br>10-0188113     |

| (22) 출원일자<br>1996년02월28일                                                              | (24) 등록일자<br>1999년01월11일    |

| (73) 특허권자<br>삼성전자주식회사 김광호<br>경기도 수원시 권선구 매단동 416번지                                    | (65) 공개번호<br>특 1997-0062781 |

| (72) 발명자<br>이규수<br>경기도 수원시 팔달구 인계동 557-7번지<br>김동규<br>경기도 수원시 권선구 권선동 권선2차아파트221동 401호 | (43) 공개일자<br>1997년09월12일    |

| (74) 대리인<br>김원호, 최현석                                                                  |                             |

**심사관 :** 강해성

**(54) 액정 표시 장치**

**요약**

본 발명은 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트선의 배선에 관한 것이다. 행렬로 형성되어 있는 다수의 게이트선 및 데이터선, 세 개의 단자를 가지고 있으며, 한 단자는 상기 게이트선과 연결되어 있고 다른 한 단자는 상기 데이터선과 연결되어 있는 트랜지스터, 상기 트랜지스터의 나머지 한 단자와 연결되어 있으며 행렬 방향으로 형성되어 있는 다수의 화소 전극, 상기 화소 전극 중 1번 화소행의 화소 전극의 전압을 유지하기 위한 유지 축전기를 형성하기 위해, 상기 1번 화소행의 인접 위치에 상기 1번 화소 행을 중심으로 상기 1번 게이트선과 대응하는 0번 게이트선 및 -1번 게이트선을 포함하고 있으며, 상기 0번 게이트선의 분지에도 다른 번 게이트선 분지와 마찬가지로 게이트 전극이 형성되어 있고, 게이트 전극의 상부에는 트랜지스터 및 화소 전극이 형성되어 있다. 상기 -1번 게이트 선은 상기 0번 게이트 선의 인접 위치에 형성되어 있어 컬러 필터기판의 공통 전극과 연결되어 있거나, 오픈 시켜 플로팅된 상태로 만들어 줄 수 있다.

**대표도**

**형세서**

[발명의 명칭]

액정 표시 장치

[도면의 간단한 설명]

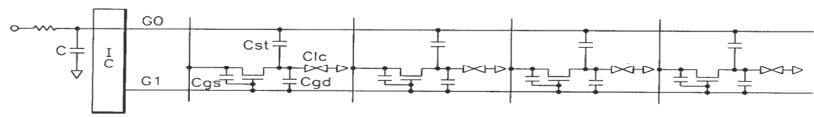

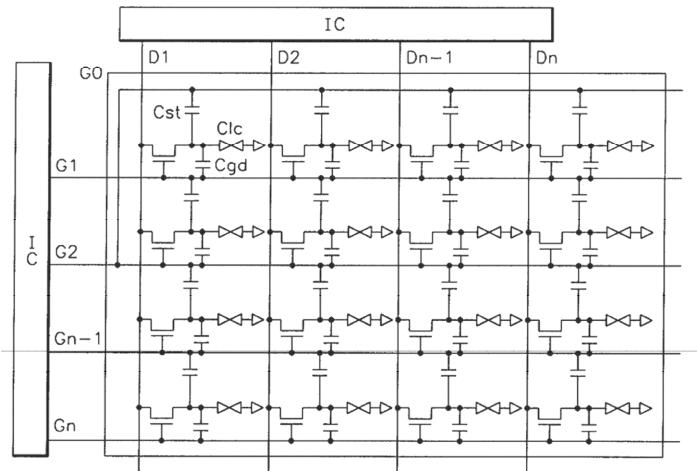

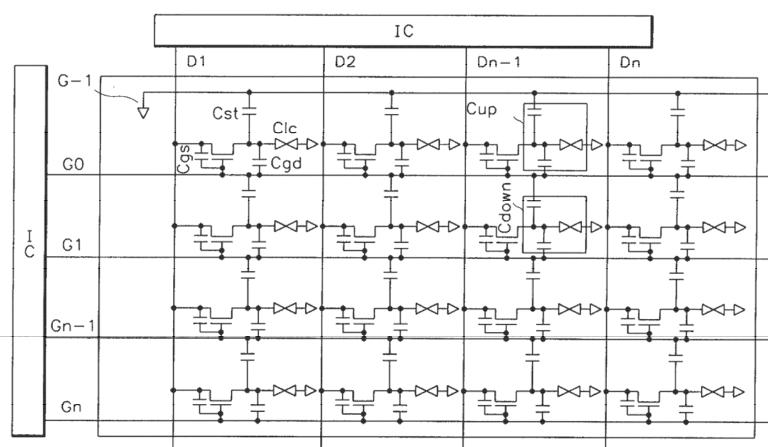

제1도는 종래의 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트선의 배선을 나타낸 회로도이고, 제2도는 종래의 다른 액정 표시 장치용 박막 트랜지스터 기판에 형성되어 있는 0번 게이트선의 배선을 나타낸 회로도이고,

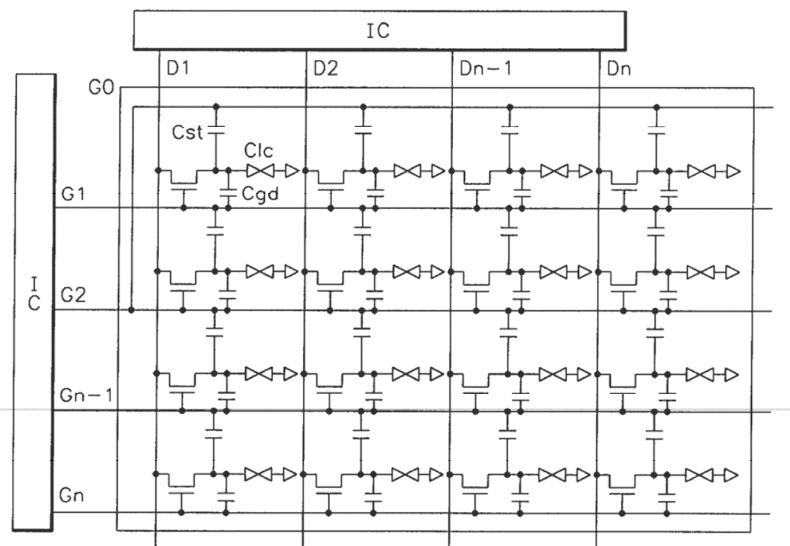

제3도는 본 발명의 제1 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판이 0번 게이트선의 배선을

나타낸 회로도이고,

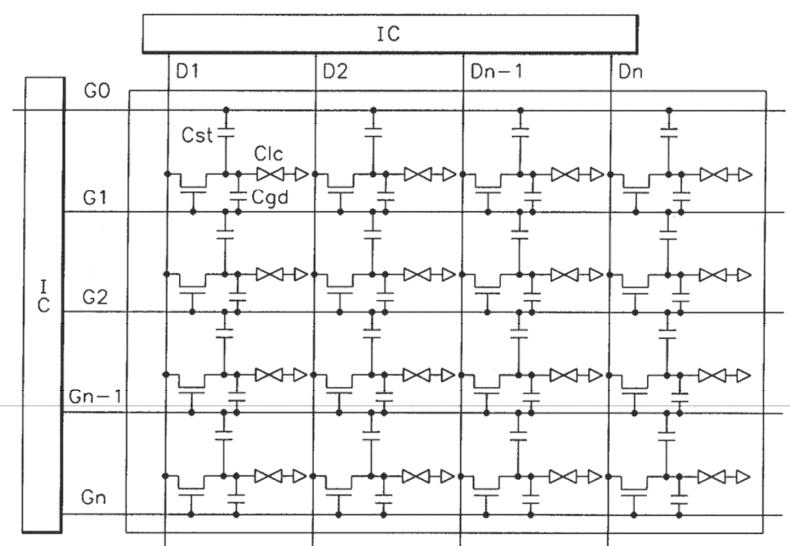

제4도는 본 발명의 제2 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트선의 배선을 나타낸 회로도이다.

#### [발명의 상세한 설명]

본 발명은 액정 표시장치에 관한 것으로서, 더욱 상세히 말하자면, 액정 표시장치용 박막 트랜지스터 기판의 0번 게이트선의 배선에 관한 것이다.

일반적으로 액정 표시장치는, 박막 트랜지스터와 화소전극으로 이루어진 화소 단위가 행렬의 형태로 다수 개가 형성되어 있으며, 게이트선 및 데이터선이 각각 화소 단위의 행과 열을 따라 형성되어 있는 액정 표시 장치의 상부 기관인 박막 트랜지스터 기판, 그리고 공통 전극이 형성되어 있는 액정 표시 장치의 하부 기판인 컬러 필터 기판, 그리고 그 사이에 봉입되어 있는 액정 물질을 포함하고 있다.

박막 트랜지스터 기판의 게이트 전극은 게이트선을 통해 게이트 구동부로부터 게이트 구동 신호를 전달 받아 반도체층에 채널을 형성시킨다. 이에 따라 데이터 구동부로부터의 데이터 신호가 데이터 선을 통해 소스 전극에 전달되어, 반도체층과 드레인 전극을 통하여 화소 전극에 전달된다.

이와 같은 액정 표시 장치의 박막 트랜지스터 기판에는 화소 전극에 인가된 전압을 일정 시간동안 유지하기 위하여 유지 축전기(storage capacitor)가 형성되어 있으며, 이 유지 축전기는 다음 화소 정보가 들어올 때까지 현재의 화소 정보를 그대로 유지 시킨다.

제1도는 종래의 액정 표시장치용 박막 트랜지스터 기판의 0번 게이트선의 배선을 나타낸 회로도이다.

제1도를 참고로 하여, 종래의 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트선의 배선 구조를 설명한다.

다수의 게이트선( $G_0, G_1, G_2, \dots, G_n$ )이 행 방향으로 형성되어 있고, 다수의 데이터선( $D_1, D_2, \dots, D_n$ )이 열 방향으로 형성되어 있다. 박막 트랜지스터의 한 단자는 게이트선( $G_0, G_1, G_2, \dots, G_n$ )과 연결되어 있으며, 다른 한 단자는 데이터선( $D_1, D_2, \dots, D_n$ ) 단자와 연결되어 있으며, 나머지 한 단자는 화소 전극에 연결되어 있다. 화소 전극은 데이터 선( $D_1, D_2, \dots, D_n$ )에 연결되어 있으며 행렬 방향으로 형성되어 있다. 1번 화소행( $n_1$ )의 화소전극의 유지 축전기( $C_{st1}$ )는 0번째 게이트선( $G_0$ )과 임의의  $N$ 번 게이트선과 연결하여 형성한다.

즉, 종래의 유지 축전기는 제1도에 도시한 바와 같이, 1번 화소행( $n_1$ )의 유지 축전기( $C_{st1}$ )의 경우는, 0 번째 게이트선( $G_0$ )과 임의의  $N$ 번 게이트선과 연결하거나, 또는 패널 외부에서 PCB를 통해 연결하는 방법을 사용한다.

이러한 방법은, 외부에서 따K로 0번 게이트선에 신호를 인가해 줄 필요가 없는 장점이 있으나, 0번 게이트선이 연력되어 있는 임의의  $n$ 번 게이트선에서 RC값이 증가되어 신호를 왜곡시켜 화질을 저하시키는 문제점이 발생한다.

제2도는 종래의 다른 액정 표시 장치용 박막 트랜지스터 기판에 형성되어 있는 0번 게이트선의 배선을 나타낸 회로도이다.

제2도를 참고로 하여, 종래의 다른 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트선의 배선 구조를 설명한다.

다수의 게이트선( $G_0, G_1, G_2, \dots, G_n$ )이 행 방향으로 형성되어 있고, 다수의 데이터선( $D_1, D_2, \dots, D_n$ )이 열 방향으로 형성되어 있다. 박막 트랜지스터(TFT)의 한 단자는 게이트선( $G_0, G_1, G_2, \dots, G_n$ )과 연결되어 있으며, 다른 한 단자는 데이터선( $D_1, D_2, \dots, D_n$ )과 연결되어 있으며, 나머지 한 단자는 화소전극에 연결되어 있다. 화소 전극은 데이터선( $D_1, D_2, \dots, D_n$ )에 연결되어 있으며 행렬 방향으로 형성되어 있다. 1번 화소행( $n_1$ )의 화소전극의 유지 축전기( $C_{st1}$ )는 패널 외부에서 구동부의 더미라인을 이용해 0번 게이트선( $G_0$ )에 컬러 필터 기판의 공통 전극( $V_{com}$ )을 연결하여 사용한다.

즉, 제2도에서 도시한 바와 같이, 종래의 다른 유지 축전기는, 1번 화소행( $n_1$ )의 유지 축전기( $C_{st1}$ )는 패널 외부에서 구동부의 더미라인을 이용해 0번 게이트선( $G_0$ )에 컬러 필터 기판의 공통 전극( $V_{com}$ )을 연결한다.

그러나 이러한 방법은 상기 제1도의 설명에서 보인 바와 같은, 0번 게이트선과 연결되어 있는 임의의  $n$ 번 게이트선의 저항의 증가와 같은 문제점을 극복할 수 있으나, 0번 게이트선에는 보조 용량( $C_{st}$ )이나 액정 용량( $C_{LC}$ )이 형성되어 있지 않으므로, 다른 게이트선과의 RC값의 차이로 인한 1번 게이트 선 결함(line defect)이 발생되어 화질을 저하시키는 문제점이 있다.

그러므로 본 발명의 목적은 이러한 종래 기술의 문제점을 해결하기 위한 것으로서, 전압을 일정하게 유지하고 화소 신호의 왜곡을 방지하는 액정 표시 장치를 제공하기 위한 것이다.

이러한 목적을 달성하기 위한 본 발명의 구성은, 행렬로 형성되어 있는 다수의 게이트선 및 데이터선, 세 개의 단자를 가지고 있으며, 한 단자는 상기 게이트선과 연결되어 있고 다른 한 단자는 상기 데이터선과 연결되어 있는 트랜지스터, 상기 트랜지스터의 나머지 한 단자와 연결되어 있으며 행렬 방향으로 형성되어 있는 다수의 화소 전극, 상기 화소 전극 중 1번 화소행의 화소 전극의 전압을 유지하기 위한 유지 축전기를 형성하기 위해, 상기 1번 화소행의 인접 위치에 상기 1번 화소행을 중심으로 상기 1번 게이트 선과 대응하는 0번 게이트선 및 -1번 게이트선을 포함하고 있으며, 상기 0번 게이트선의 분지에도 다른 번 게이트 분지와 마찬가지고 게이트 전극이 형성되고 있고, 게이트 전극의 상부에는 트랜지스터 및 화소 전극이 형성되어 있다.

이때, 상기 -1번 게이트 선은 상기 0번 게이트선의 인접 위치에 형성되어 있어 컬러 필터 기판의 공통 전극과 연결되어 있거나, 오픈시켜 플로팅된 상태로 만들어 줄 수 있다.

이러한 목적을 달성하기 위한 본 발명의 다른 구성은, 행렬로 형성되어 있는 다수의 게이트선 및 데이터선, 세 개의 단자를 가지고 있으며, 한 단자는 상기 게이트선과 연결되어 있고 다른 한 단자는 상기 데이터선과 연결되어 있는 트랜지스터, 상기 트랜지스터의 나머지 한 단자와 연결되어 있으며 행렬 방향으로 형성되어 있는 다수의 화소 전극, 상기 화소 전극 중 1번 화소행의 화소 전극의 전압을 유지하기 위한 유지 축전기를 형성하기 위한, 상기 1번 화소행의 인접위치에 상기 1번 화소행을 중심으로 상기 1번 게이트선과 대응되도록 형성되어 있는 0번 게이트선을 포함하고 있으며, 상기 0번 게이트선의 외부에 상기 0번 게이트선의 RC값을 외부에서 자유로이 조절할 수 있게하는 가변 저항부를 포함하고 있다.

첨부한 도면을 참고로 하여, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 본 발명의 실시예를 상세하게 설명한다.

제3도는 본 발명의 제1 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트 선의 배선을 나타낸 회로도이다.

다수의 게이트선( $G_0, G_1, G_2, \dots, G_n$ )이 행 방향으로 형성되어 있고, 다수의 데이터선( $D_1, D_2, \dots, D_n$ )이 열 방향으로 형성되어 있다. 박막 트랜지스터(TFT)의 한 단자는 게이트선( $G_0, G_1, G_2, \dots, G_n$ )과 연결되어 있으며, 다른 한 단자는 데이터선( $D_1, D_2, \dots, D_n$ )과 연결되어 있으며, 나머지 한 단자는 화소 전극에 연결되어 있다. 화소 전극은 데이터선( $D_1, D_2, \dots, D_n$ )에 연결되어 있으며 행렬 방향으로 형성되어 있다. 또한 1번 화소행의 인접 위치에 상기 1번 화소행을 중심으로 1번 게이트선( $G_1$ )과 대응하는 0번 게이트 선( $G_0$ ) 및 -1번 게이트선( $G_1$ )을 포함하고 있으며, 상기 0번 게이트선( $G_0$ )의 분지에 다른 번 게이트선과 마찬가지로 트랜지스터 및 화소 전극을 형성되어 있어, 1번 화소행의 화소 전극의 유지 축전기( $C_{st}$ )를 형성한다.

또한 -1번 게이트 선을 형성하여 0번 게이트선( $G_0$ )의 보조 용량( $C_{st}$ )을 연결할 수 있도록 하였다.

제4도는 본 발명의 제2 실시예에 따른 액정 표시 장치용 박막 트랜지스터 기판의 0번 게이트선의 배선을 나타낸 회로도이다.

다수의 게이트선( $G_0, G_1, G_2, \dots, G_n$ )이 행 방향으로 형성되어 있고, 다수의 데이터선( $D_1, D_2, \dots, D_n$ )이 열 방향으로 형성되어 있다. 박막 트랜지스터(TFT)의 한 단자는 게이트선( $G_0, G_1, G_2, \dots, G_n$ )과 연결되어 있으며, 다른 한 단자는 데이터선( $D_1, D_2, \dots, D_n$ )과 연결되어 있으며, 나머지 한 단자는 화소 전극에 연결되어 있다. 화소 전극은 데이터선( $D_1, D_2, \dots, D_n$ )에 연결되어 있으며 행렬 방향으로 형성되어 있다. 또한 1번 화소행의 인접 위치에 상기 1번 화소행을 중심으로 1번 게이트선( $G_1$ )과 대응하는 0번 게이트선( $G_0$ )을 포함하고 있으며, 상기 0번 게이트 선( $G_0$ )의 외부에 상기 0번 게이트선( $G_0$ )의 RC값을 외부에서 자유로이 조절할 수 있게 하는 가변 저항부( $R$ )를 포함하고 있다.

전단 게이트 방식에서 0번 게이트선에 보조 용량( $C_{st}$ ), 액정 용량( $C_{LC}$ ), 게이트와 드레인 간의 용량( $C_{gd}$ )을 형성하기 위한 액정 표시장치의 박막 트랜지스터 기판의 배선 구조를 설명한다.

제3도에 도시한 바와 같이, 하나의 화소에 있어서 0번 게이트선에 연결되어 있는 커패시터의 총합을 수식으로 나타내면 다음과 같다.

$$C_{total} = C_{up} + C_{down} + C_{cross}$$

$$\text{단, } \frac{1}{C_{up}} = \frac{1}{C_{gd}} + \frac{1}{(Clc + Cst)} + C_{gs}$$

$$\text{단, } \frac{1}{C_{down}} = \frac{1}{Cst} + \frac{1}{(Clc + Cgd)}$$

단,  $C_{gs}$ 는 게이트와 소스간의 용량임.

단, Cross = 게이트선과 데이터선 사이의 캐퍼시턴스

제1도 및 제2도에 도시한 바와 같이, 종래의 1번 화소행의 유지 용량의 형성 방법은  $C_{up}$ 이 형성되지 않아,  $C_{total} = C_{down} + C_{cross}$ 와 같다.

일반적으로  $C_{up}$ 의 크기는  $C_{total}$ 의 10%정도를 차지하므로 종래의 방법에 있어서 0번 게이트선( $G_0$ )의 커퍼시턴스는 다른 게이트선에 비해 10%정도 작다고 할 수 있다.

이는 0번 게이트선( $G_0$ )에 인가되는 신호의 지연이 다른 게이트 선에 비해 10%정도 적다는 것을 의미한다.

이로인해 0번 게이트선( $G_0$ )에 인가되는 신호의 스위칭 시간이 다른 신호와 일치하지 않게 되어 희미한 선결함이 나타난다.

본 발명에서는 제3도에 도시한 바와 같이, 0번 게이트선( $G_0$ )에도 하른 게이트선과 마찬가지로  $C_{up}$ 을 형성하였다. 또한 0번 게이트 선( $G_0$ )에  $C_{up}$ 을 형성하기 위하여 -1번 게이트 선( $G_1$ )을 형성하여 0번 게이트

선(G0)의 보조용량( $C_{st}$ )을 연결할 수 있도록 하였다.

0번 게이트 선(G0)에 싱호를 인가해 주기 위해 게이트 구동부의 더미 라인과 0번 게이트 선(G0)을 연결하여 패널 외부에서 공통 전극(Vcom)이나 Voff를 인가해 줄 수 있도록 하였다.

-1번 게이트 선(G-1)은 패널 내부에서 공통 전극(Vcom) 전압과 연결하거나 오픈시켜 플로팅(floating)된 상태로 구동되어진다.

제4도에 도시한 바와 같이, 0번 게이트 선(G0)에 트랜지스터 및 화소 전극을 형성하지 않고 패널 외부에서 RC 회로(RC)를 구성하여 이를 통해 0번 게이트선에 신호를 인가 할 수 있다. 즉, 0번 게이트 선의 RC 값을 외부에서 자유로이 조절할 수 있다. 한편, 제3도에서 도시한 바와 같은 방법과 제4도에서 도시한 바와 같은 방법을 병행하여 사용할 수 있다.

그러므로 본 발명은 화소 용량의 충전 시간 증가로 인해 충전 특성을 개선할 수 있어 대형화되고 고정세화된 패널 적용시 효과가 크다.

### (57) 청구의 범위

#### 청구항 1

행렬로 형성되어 있는 다수의 게이트선 및 데이터선, 세 개의 단자를 가지고 있으며, 한 단자는 상기 게이트선과 연결되어 있고 다른 한 단자는 상기 데이터선과 연결되어 있는 트랜지스터, 상기 트랜지스터의 나머지 한 단자와 연결되어 있으며 행렬 방향으로 형성되어 있는 다수의 화소 전극, 상기 화소 전극 중 1번 화소행의 화소 전극의 전압을 유지하기 위한 유지 축전기를 형성하기 위해, 상기 1번 화소행의 인접 위치에 상기 1번 화소 행을 중심으로 상기 1번 게이트 선과 대응하는 0번 게이트선 및 -1번 게이트선을 포함하고 있으며, 상기 0번 게이트선의 분지에도 다른 번 게이트선 분지와 마찬가지로 게이트 전극이 형성되어 있고, 게이트 전극의 상부에는 트랜지스터 및 화소 전극이 형성되어 있는 액정 표시 장치.

#### 청구항 2

제1항에 있어서, 상기 -1번 게이트선은 상기 0번 게이트선의 인접위치에 형성되어 있어 컬러 필터 기판의 공통 전극과 연결되어 있거나, 오픈시켜 플로팅된 상태로 만들어 줄 수 있는 액정 표시 장치.

#### 청구항 3

행렬로 형성되어 있는 다수의 게이트선 및 데이터선, 세 개의 단자를 가지고 있으며, 한 단자는 상기 게이트선과 연결되어 있고 다른 한 단자는 상기 데이터선과 연결되어 있는 트랜지스터, 상기 트랜지스터의 나머지 한 단자와 연결되어 있으며 행렬방향으로 형성되어 있는 다수의 화소 전극, 상기 화소 전극 중 1번 화소행의 화소 전극의 전압을 유지하기 위한 상기 1번 화소행의 인접 위치에 상기 1번 화소행을 중심으로 상기 1번 게이트선과 대응되도록 형성되어 있는 0번 게이트선, 상기 0번 게이트선의 외부에 상기 0번 게이트선의 RC값을 외부에서 자유로이 조절할 수 있게 하는 가변 저항부를 포함하고 있는 액정 표시 장치.

#### 청구항 4

제3항에서, 상기 0번 게이트선의 분지에 형성되어 있는 트랜지스터 및 화소 전극을 더 포함하는 액정 표시 장치.

#### 청구항 5

제3항 또는 제4항에서, 상기 0번 게이트선의 인접한 위치에 형성되어 있는 -1번 게이트선을 더 포함하는 액정 표시 장치.

### 도면

도면1

도면2

도면3

## 도면4