(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6732468号

(P6732468)

(45) 発行日 令和2年7月29日(2020.7.29)

(24) 登録日 令和2年7月10日(2020.7.10)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4N 5/378 (2011.01) | HO4N 5/378   |

| HO4N 5/374 (2011.01) | HO4N 5/374   |

| HO4N 9/07 (2006.01)  | HO4N 9/07 A  |

| HO4N 1/028 (2006.01) | HO4N 1/028 C |

請求項の数 17 (全 26 頁)

(21) 出願番号 特願2016-26970 (P2016-26970)

(22) 出願日 平成28年2月16日 (2016.2.16)

(65) 公開番号 特開2017-147549 (P2017-147549A)

(43) 公開日 平成29年8月24日 (2017.8.24)

審査請求日 平成31年2月14日 (2019.2.14)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

(72) 発明者 小倉 正徳

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、

保持回路と、

出力信号線と、を有する光電変換装置であって、

前記保持回路は、複数の第1の保持部を各々が含む複数のグループを有し、前記複数のグループの各々は、前記複数の列のうちの対応する1列に設けられており、1つのグループに属する前記複数の第1の保持部は、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を並行して保持するように構成されており、

前記保持回路は、複数の第2の保持部を各々が含む複数の第2のグループを更に有し、前記複数の第2のグループの各々は、前記複数の列のうちの対応する1列に設けられており、

前記複数の第1の保持部のそれぞれは、第1の容量値の第1の容量素子を含み、

前記複数の第2の保持部のそれぞれは、前記第1の容量値よりも大きい第2の容量値の第2の容量素子を含み、

前記光電変換装置は、前記複数のグループの前記複数の第1の保持部に保持された前記複数の画素の前記画素信号のうち、同色の前記光学フィルタを有する画素の前記画素信号

を、前記複数の第2のグループのうちの対応する前記第2のグループに並列に転送し、前記複数の第2のグループの各々に保持された前記画素信号を前記出力信号線に連続的に読み出す読み出し回路を更に有する

ことを特徴とする光電変換装置。

【請求項2】

前記出力信号線の電位をリセットするリセット回路と、前記出力信号線に接続された増幅回路と、前記増幅回路から出力される前記画素信号を保持する第3の保持部を有し、

前記読み出し回路は、前記複数の画素の前記画素信号を前記出力信号線に連続的に転送する際に、前記画素信号を前記出力信号線に読み出す読み出し期間と、前記出力信号線の電位をリセットするリセット期間とを繰り返し実施し、

前記第3の保持部は、前記読み出し期間の間に前記増幅回路から出力される前記画素信号を選択的に保持する

ことを特徴とする請求項1記載の光電変換装置。

【請求項3】

前記読み出し回路は、前記複数の画素の前記画素信号を保持する前記複数の第1の保持部が画素の前記光学フィルタの色に応じて規則的に配列されるように、前記画素アレイから前記複数の第1の保持部に前記複数の画素の前記画素信号を転送するように構成されている

ことを特徴とする請求項1又は2記載の光電変換装置。

【請求項4】

複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、

保持回路と、

出力信号線と、を有する光電変換装置であって、

前記保持回路は、複数の第1の保持部を各々が含む複数のグループを有し、前記複数のグループの各々は、前記複数の列のうちの対応する1列に設けられており、1つのグループに属する前記複数の第1の保持部は、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を並行して保持するように構成されており、

前記光電変換装置は、前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を前記出力信号線に連続して読み出す読み出し回路と、前記出力信号線の電位をリセットするリセット回路と、前記出力信号線に接続された増幅回路と、前記増幅回路から出力される前記画素信号を保持する第3の保持部と、を更に有し、

前記読み出し回路は、前記複数の画素の前記画素信号を前記出力信号線に連続的に転送する際に、前記画素信号を前記出力信号線に読み出す読み出し期間と、前記出力信号線の電位をリセットするリセット期間とを繰り返し実施し、

前記第3の保持部は、前記読み出し期間の間に前記増幅回路から出力される前記画素信号を選択的に保持する

ことを特徴とする光電変換装置。

【請求項5】

複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、

保持回路と、

出力信号線と、を有する光電変換装置であって、

前記保持回路は、複数の第1の保持部を各々が含む複数のグループを有し、前記複数のグループの各々は、前記複数の列のうちの対応する1列に設けられており、1つのグループに属する前記複数の第1の保持部は、前記光学フィルタの色が互いに異なる複数の画素

10

20

30

40

50

から読み出された前記画素信号を並行して保持するように構成されており、

前記光電変換装置は、前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を前記出力信号線に連続して読み出す読み出し回路を更に有し、

前記読み出し回路は、前記複数の画素の前記画素信号を保持する前記複数の第1の保持部が画素の前記光学フィルタの色に応じて規則的に配列されるように、前記画素アレイから前記複数の第1の保持部に前記複数の画素の前記画素信号を転送するように構成されている

ことを特徴とする光電変換装置。

#### 【請求項6】

前記保持回路は、複数の第2の保持部を各々が含む複数の第2のグループを更に有し、

前記複数の第2のグループの各々は、前記複数の列のうちの対応する1列に設けられており、

前記読み出し回路は、前記複数のグループの前記複数の第1の保持部に保持された前記複数の画素の前記画素信号のうち、同色の前記光学フィルタを有する画素の前記画素信号を、前記複数の第2のグループのうちの対応する前記第2のグループに並列に転送し、前記複数の第2のグループの各々に保持された前記画素信号を前記出力信号線に連続的に読み出すように構成されている

ことを特徴とする請求項4又は5記載の光電変換装置。

#### 【請求項7】

前記複数の第1の保持部のそれぞれは、第1の容量値の第1の容量素子を含み、

前記複数の第2の保持部のそれぞれは、前記第1の容量値よりも大きい第2の容量値の第2の容量素子を含む

ことを特徴とする請求項6記載の光電変換装置。

#### 【請求項8】

前記保持回路は、複数のバッファ回路を更に有し、

前記複数のバッファ回路の各々は、前記複数のグループのうちの1つの前記グループの出力と前記複数の第2のグループのうちの1つの前記第2のグループの入力との間に設けられている

ことを特徴とする請求項1、2、3、6及び7のいずれか1項に記載の光電変換装置。

#### 【請求項9】

複数の前記出力信号線を有し、

前記読み出し回路は、複数の前記出力信号線に同色の前記光学フィルタを有する画素の前記画素信号を並列に読み出すように構成されている

ことを特徴とする請求項1乃至8のいずれか1項に記載の光電変換装置。

#### 【請求項10】

前記読み出し回路は、前記複数の画素の前記画素信号を、前記複数のグループに同時に転送するように構成されている

ことを特徴とする請求項1乃至9のいずれか1項に記載の光電変換装置。

#### 【請求項11】

1列の画素の前記光学フィルタは、互いに異なる色を1つずつ含み、1行の画素の前記光学フィルタの色が規則的に繰り返し配列されている

ことを特徴とする請求項1乃至10のいずれか1項に記載の光電変換装置。

#### 【請求項12】

前記読み出し回路は、1列に配された複数の行の複数の画素の前記画素信号を、前記画素アレイから前記複数のグループのうちの対応する1つのグループに並列に転送する

ことを特徴とする請求項1乃至11のいずれか1項に記載の光電変換装置。

#### 【請求項13】

複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれと前記複数の列のそ

10

20

30

40

50

れぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、複数の第1の保持部を各々が含み、各々が前記複数の列のうちの対応する1列に設けられた複数のグループと、複数の第2の保持部を各々が含み、各々が前記複数の列のうちの対応する1列に設けられた複数の第2のグループと、を有し、前記複数の第1の保持部のそれぞれが第1の容量値の第1の容量素子を含み、前記複数の第2の保持部のそれぞれが前記第1の容量値よりも大きい第2の容量値の第2の容量素子を含む、光電変換装置の駆動方法であって、

前記画素アレイの対応する1列の、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を、前記複数のグループの各々が並行して保持するステップと、

前記複数のグループの前記複数の第1の保持部に保持された前記複数の画素の前記画素信号のうち、同色の前記光学フィルタを有する画素の前記画素信号を、前記複数の第2のグループのうちの対応する前記第2のグループに並列に転送するステップと、

前記複数の第2のグループの各々に保持された前記画素信号を出力信号線に連続的に読み出すステップと

を有することを特徴とする光電変換装置の駆動方法。

#### 【請求項14】

複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、複数の第1の保持部を各々が含み、各々が前記複数の列のうちの対応する1列に設けられた複数のグループと、出力信号線と、前記出力信号線の電位をリセットするリセット回路と、前記出力信号線に接続された增幅回路と、前記増幅回路から出力される前記画素信号を保持する第3の保持部と、を有する光電変換装置の駆動方法であって、

前記画素アレイの対応する1列の、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を、前記複数のグループの各々が並行して保持するステップと、

前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を連続して読み出すステップと、を有し、

前記複数の画素の前記画素信号を前記出力信号線に連続的に転送する際に、前記画素信号を前記出力信号線に読み出す読み出し期間と、前記出力信号線の電位をリセットするリセット期間とを繰り返し実施し、

前記読み出し期間の間に前記増幅回路から出力される前記画素信号を前記第3の保持部に選択的に保持する

ことを特徴とする光電変換装置の駆動方法。

#### 【請求項15】

複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、複数の第1の保持部を各々が含む複数のグループと、を有し、前記複数のグループの各々が前記複数の列のうちの対応する1列に設けられた光電変換装置の駆動方法であって、

前記画素アレイの対応する1列の、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を、前記複数のグループの各々が並行して保持するステップと、

前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を連続して読み出すステップと、を有し、

前記保持するステップでは、前記複数の画素の前記画素信号を保持する前記複数の第1の保持部が画素の前記光学フィルタの色に応じて規則的に配列されるように、前記画素ア

10

20

30

40

50

レイから前記複数の第1の保持部に前記複数の画素の前記画素信号を転送することを特徴とする光電変換装置の駆動方法。

【請求項16】

対象物の画像を読み取る画像読み取り装置であって、

前記対象物に光を照射する発光部と、

前記対象物により反射された光を受光して電気信号に変換する請求項1乃至12のいずれか1項に記載の光電変換装置と

を有することを特徴とする画像読み取り装置。

【請求項17】

請求項16記載の画像読み取り装置と、

前記画像読み取り装置により取得した信号に基づき画像を形成する画像形成部と

を有することを特徴とする画像形成装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置及びその駆動方法に関する。

【背景技術】

【0002】

複写機やマルチファンクションプリンタ等の原稿読み取り装置のカラー原稿読み取り手段として、CMOSイメージセンサやCCDイメージセンサ等の光電変換装置を用いたものが知られている。特許文献1、特許文献2及び特許文献3には、R、G、Bの光学フィルタによりカラー原稿を色分離して画像情報を取得する光電変換装置が記載されている。

【0003】

特許文献1、特許文献2及び特許文献3に記載の光電変換装置では、主走査方向に複数列の画素が配置され、R画素、G画素、B画素が周期的に配置されている。副走査方向には3行分の画素が配列され、R画素、G画素、B画素が周期的に配列されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭62-49765号公報

30

【特許文献2】特開平08-116402号公報

【特許文献3】特開平02-250560号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1、特許文献2及び特許文献3に記載の光電変換装置において、主走査方向に沿って順番に画素の信号を読み出すと、R画素、G画素、B画素の信号が順番に読み出されることになる。R画素、G画素、B画素のそれぞれの信号の電位は、読み取るカラー原稿にもよるが、互いに異なることが多い。例えば、R画素の信号の電位が高く、G画素の信号の電位が低い場合を想定すると、電位の高いR画素の信号を読み出し後に読み出される電位の低いG画素の信号は、真値よりも高い電位になることがある。このように、R画素、G画素、B画素の信号を順番に読み出すと、前に読み出した異なる色の画素の信号の影響を受け、言わば画素信号の電気的な混色を生じることがあった。電気的な混色が生じると、取り込んだ画像を再生する際に色再現性が低下することになる。

【0006】

本発明の目的は、異なる色の画素から取得した画素信号間における電気的な混色を防止しうる光電変換装置及びその駆動方法を提供することにある。

【課題を解決するための手段】

【0007】

本発明の一観点によれば、複数の行及び複数の列に渡って配され、各々が画素信号を出

50

力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、保持回路と、出力信号線と、を有する光電変換装置であって、前記保持回路は、複数の第1の保持部を各々が含む複数のグループを有し、前記複数のグループの各々は、前記複数の列のうちの対応する1列に設けられており、1つのグループに属する前記複数の第1の保持部は、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を並行して保持するように構成されており、前記保持回路は、複数の第2の保持部を各々が含む複数の第2のグループを更に有し、前記複数の第2のグループの各々は、前記複数の列のうちの対応する1列に設けられており、前記複数の第1の保持部のそれぞれは、第1の容量値の第1の容量素子を含み、前記複数の第2の保持部のそれぞれは、前記第1の容量値よりも大きい第2の容量値の第2の容量素子を含み、前記光電変換装置は、前記複数のグループの前記複数の第1の保持部に保持された前記複数の画素の前記画素信号のうち、同色の前記光学フィルタを有する画素の前記画素信号を、前記複数の第2のグループのうちの対応する前記第2のグループに並列に転送し、前記複数の第2のグループの各々に保持された前記画素信号を前記出力信号線に連続的に読み出す読み出し回路を更に有する光電変換装置が提供される。

また、本発明の他の一観点によれば、複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、保持回路と、出力信号線と、を有する光電変換装置であって、前記保持回路は、複数の第1の保持部を各々が含む複数のグループを有し、前記複数のグループの各々は、前記複数の列のうちの対応する1列に設けられており、1つのグループに属する前記複数の第1の保持部は、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を並行して保持するように構成されており、前記光電変換装置は、前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を前記出力信号線に連続して読み出す読み出し回路と、前記出力信号線の電位をリセットするリセット回路と、前記出力信号線に接続された增幅回路と、前記増幅回路から出力される前記画素信号を保持する第3の保持部と、を更に有し、前記読み出し回路は、前記複数の画素の前記画素信号を前記出力信号線に連続的に転送する際に、前記画素信号を前記出力信号線に読み出す読み出し期間と、前記出力信号線の電位をリセットするリセット期間とを繰り返し実施し、前記第3の保持部は、前記読み出し期間の間に前記増幅回路から出力される前記画素信号を選択的に保持する光電変換装置が提供される。

また、本発明の他の一観点によれば、複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、保持回路と、出力信号線と、を有する光電変換装置であって、前記保持回路は、複数の第1の保持部を各々が含む複数のグループを有し、前記複数のグループの各々は、前記複数の列のうちの対応する1列に設けられており、1つのグループに属する前記複数の第1の保持部は、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を並行して保持するように構成されており、前記光電変換装置は、前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を前記出力信号線に連続して読み出す読み出し回路を更に有し、前記読み出し回路は、前記複数の画素の前記画素信号を保持する前記複数の第1の保持部が画素の前記光学フィルタの色に応じて規則的に配列されるように、前記画素アレイから前記複数の第1の保持部に前記複数の画素の前記画素信号を転送するように構成されている光電変換装置が提供される。

また、本発明の他の一観点によれば、複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、複数の第1の保持部を各々が含み、各々が前記複数の列のうちの対応する1列に設けられた複数のグループと、複数の第2の保持部を各々が含み、各々が前記複数の列のうちの対応する1列に設けられた複数の第2のグループと、を有し、前記複数の第1の保持部のそれぞれが第1の容量値の第1の容量素子を含み、前記複数の第2の保持部のそれぞれが前記第1の容量値よりも大きい第2の容量値の第2の容量素子を含む、光電変換装置の駆動方法であって、前記画素アレイの対応する1列の、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を、前記複数のグループの各々が並行して保持するステップと、前記複数のグループの前記複数の第1の保持部に保持された前記複数の画素の前記画素信号のうち、同色の前記光学フィルタを有する画素の前記画素信号を、前記複数の第2のグループのうちの対応する前記第2のグループに並列に転送するステップと、前記複数の第2のグループの各々に保持された前記画素信号を出力信号線に連続的に読み出すステップとを有する光電変換装置の駆動方法。

10

また、本発明の他の一観点によれば、複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、複数の第1の保持部を各々が含み、各々が前記複数の列のうちの対応する1列に設けられた複数のグループと、出力信号線と、前記出力信号線の電位をリセットするリセット回路と、前記出力信号線に接続された増幅回路と、前記増幅回路から出力される前記画素信号を保持する第3の保持部と、を有する光電変換装置の駆動方法であって、前記画素アレイの対応する1列の、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を、前記複数のグループの各々が並行して保持するステップと、前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を連続して読み出すステップと、を有し、前記複数の画素の前記画素信号を前記出力信号線に連続的に転送する際に、前記画素信号を前記出力信号線に読み出す読み出し期間と、前記出力信号線の電位をリセットするリセット期間とを繰り返し実施し、前記読み出し期間の間に前記増幅回路から出力される前記画素信号を前記第3の保持部に選択的に保持する光電変換装置の駆動方法が提供される。

20

また、本発明の他の一観点によれば、複数の行及び複数の列に渡って配され、各々が画素信号を出力する複数の画素を含む画素アレイであって、前記複数の画素の各々は、光学フィルタと、前記光学フィルタを透過した光を光電変換する光電変換部とを有し、前記複数の行のそれぞれと前記複数の列のそれぞれとに、前記光学フィルタの色が互いに異なる画素が配された画素アレイと、複数の第1の保持部を各々が含む複数のグループと、を有し、前記複数のグループの各々が前記複数の列のうちの対応する1列に設けられた光電変換装置の駆動方法であって、前記画素アレイの対応する1列の、前記光学フィルタの色が互いに異なる複数の画素から読み出された前記画素信号を、前記複数のグループの各々が並行して保持するステップと、前記複数のグループの各々から、同色の前記光学フィルタを有する画素の前記画素信号を連続して読み出すステップと、を有し、前記保持するステップでは、前記複数の画素の前記画素信号を保持する前記複数の第1の保持部が画素の前記光学フィルタの色に応じて規則的に配列されるように、前記画素アレイから前記複数の第1の保持部に前記複数の画素の前記画素信号を転送する光電変換装置の駆動方法が提供される。

30

### 【発明の効果】

#### 【0009】

本発明によれば、各行及び各列のそれぞれにおいて、互いに色の異なる光学フィルタを各々が有する複数の画素を含む画素アレイを有する光電変換装置において、異なる色の画

40

10

20

30

40

50

素から取得した画素信号間の電気的な混色を防止することができる。これにより、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。

【図面の簡単な説明】

【0010】

【図1】本発明の第1実施形態による光電変換装置の構成を示す概略図である。

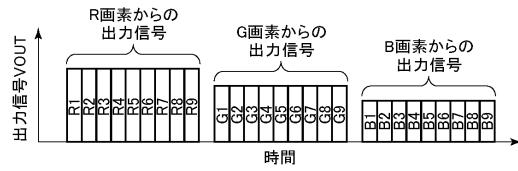

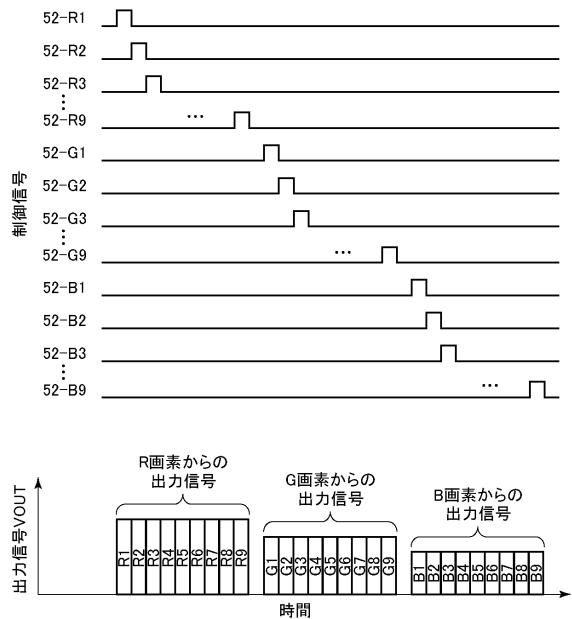

【図2】本発明の第1実施形態による光電変換装置の信号出力のタイミングを示す図である。

【図3】比較例による光電変換装置の信号出力のタイミングを示す図である。

【図4】本発明の第2実施形態による光電変換装置の構成を示す概略図である。

【図5】本発明の第2実施形態による光電変換装置の構成例を示す回路図である。 10

【図6】本発明の第2実施形態による光電変換装置の信号出力のタイミングを示す図である。

【図7】本発明の第3実施形態による光電変換装置の構成を示す概略図である。

【図8】本発明の第3実施形態による光電変換装置の信号出力のタイミングを示す図である。

【図9】本発明の第4実施形態による光電変換装置の構成を示す概略図である。

【図10】本発明の第5実施形態による画像読み取り装置の構成を示すブロック図である。

。

【発明を実施するための形態】

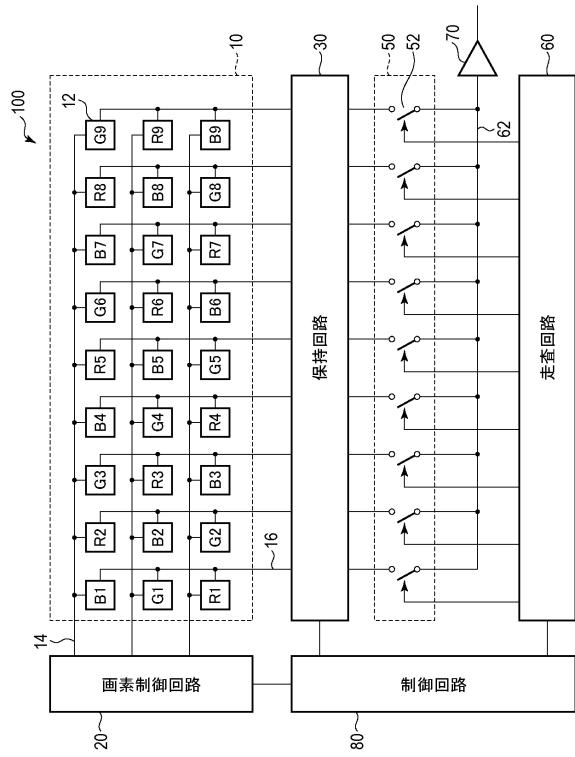

【0011】

<第1実施形態>

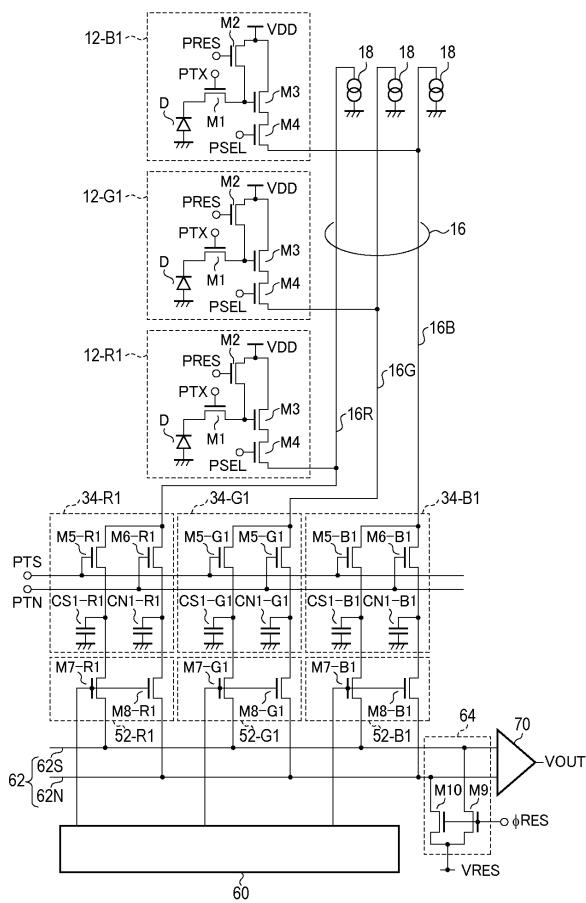

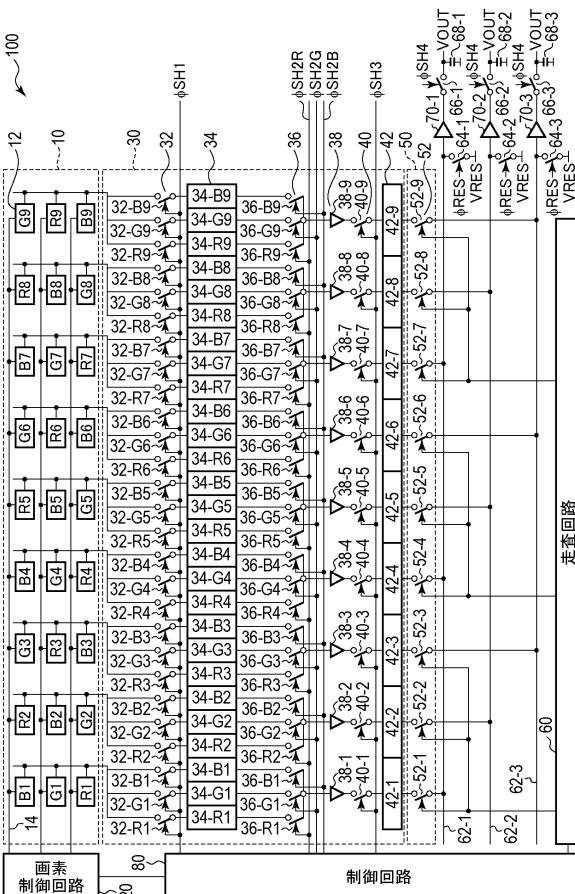

本発明の第1実施形態による光電変換装置について、図1乃至図3を用いて説明する。図1は、本実施形態による光電変換装置の構成を示す概略図である。図2は、本実施形態による光電変換装置の信号出力のタイミングを示す図である。図3は、比較例による光電変換装置の信号出力のタイミングを示す図である。

【0012】

はじめに、本実施形態による光電変換装置の構造について、図1を用いて説明する。

【0013】

本実施形態による光電変換装置100は、図1に示すように、画素アレイ10、画素制御回路20、保持回路30、スイッチ回路50、走査回路60、読み出しアンプ70、制御回路80を含む。 30

【0014】

画素アレイ10は、複数の行及び複数の列に渡って配された複数の画素12を含む。本明細書では、図1における横方向を行方向、水平方向或いは主走査方向と表記し、図1における縦方向を列方向、垂直方向或いは副走査方向と表記するものとする。複数の画素12は、赤色(R)の波長領域の光を透過する光学フィルタを上面に配したR画素と、緑(G)の波長領域の光を透過する光学フィルタを上面に配したG画素と、青色(B)の波長領域の光を透過する光学フィルタを上面に配したB画素とを含む。図1には、便宜的に、光学フィルタの色(R, G, B)と列番号を表す数字との組み合わせからなる符号を、各画素12に付している。例えば、「G5」と表記されている画素12は、第5列に位置するG画素を意味している。本明細書において特定の画素12を示すときは、当該符号を用いて「画素12-G5」のように表記することがある。また、後述するスイッチ32, 36, 40, 52や保持部34, 42等についても同様に、対応する画素12の色を表す記号(R, G, B)や列を表す番号を付記した符号で表記することがある。 40

【0015】

画素アレイ10の各1列には、入射光に応じた画素信号を出力する総ての種類の画素12、ここでは、光学フィルタが互いに異なる色の画素12、R画素、G画素及びB画素が、少なくともとも1つずつ含まれる。すなわち、R画素、G画素及びB画素の3種類の画素12を含む画素アレイ10においては、図1に示すように、少なくとも3つの行が含まれる。画素アレイ10の各1行についても同様に、入射光に応じた画素信号を出力する総 50

ての種類の画素 12 が規則的に繰り返し配列されている。図 1 の例では、各行に、R 画素、G 画素、B 画素、R 画素、…、の順番で繰り返し画素 12 が配置されている。すなわち、R 画素、G 画素、B 画素は、いわゆる点順次配列とされている。画素アレイ 10 の列数は、主走査方向に必要な幅や解像度等に応じて適宜決定される。図 1 には簡略化のために 3 行 × 9 列の画素アレイ 10 を示しているが、実際には更に多数の列が設けられる。

#### 【0016】

画素アレイ 10 の各行には、行方向に延在して、制御信号線 14 が配されている。制御信号線 14 は、行方向に並ぶ画素 12 に共通の信号線をなしている。制御信号線 14 は、画素制御回路 20 に接続されている。制御信号線 14 は、典型的にはそれぞれが複数の信号線を含む。画素制御回路 20 は、各画素 12 から信号を読み出す際に、画素 12 内の読み出し回路を駆動するための制御信号を各制御信号線 14 に供給する。10

#### 【0017】

画素アレイ 10 の各列には、列方向に延在して、対応する列の画素 12 に接続された垂直出力線バス 16 が配されている。垂直出力線バス 16 は、画素 12 の画素信号を出力するための出力信号線である。垂直出力線バス 16 のそれぞれは、列方向に並ぶ画素 12 のそれぞれに対応する複数の垂直出力線を含む。例えば、図 1 の例のように 3 行からなる画素アレイ 10 の場合、垂直出力線バス 16 は、3 つの画素 12 に個別に接続された 3 本の信号線を含む。なお、本実施形態の光電変換装置は、画素アレイ 10 から行順次で画素信号を読み出す構成とすることもでき、その場合は、垂直出力線バス 16 は列方向に並ぶ 3 つの画素 12 に共通の 1 本の垂直出力線であってもよい。20

#### 【0018】

垂直出力線バス 16 には、保持回路 30 が接続されている。保持回路 30 は、少なくとも、画素アレイ 10 の全ての画素 12 から出力される画素信号を一時に保持するために必要な数の複数の保持部を含む。それぞれの保持部は、画素 12 から出力される光電変換信号（S 信号）とリセット信号（N 信号）とを別々に保持できるように構成してもよい。

#### 【0019】

保持回路 30 は、スイッチ回路 50 を介して水平出力線 62 に接続されている。水平出力線 62 は、保持回路 30 の保持部に保持された画素信号を出力するための出力信号線である。スイッチ回路 50 には、走査回路 60 が接続されている。スイッチ回路 50 は、走査回路 60 により制御されるスイッチ 52 を含む。水平出力線 62 には、読み出しアンプ 70 が接続されている。これにより、走査回路 60 によりスイッチ回路 50 のスイッチ 52 を制御し、保持回路 30 の保持部に保持された画素信号を、水平出力線 62 を介して読み出しアンプ 70 に連続的に出力できるようになっている。30

#### 【0020】

画素制御回路 20、保持回路 30、走査回路 60 には、これらの動作やそのタイミングを制御する制御回路 80 が接続されている。なお、制御回路 80 は、必ずしも光電変換装置に設けられている必要はない。光電変換装置は、画素制御回路 20、保持回路 30、走査回路 60 等を制御するための制御信号を外部の制御回路から受信する手段を有する構成としてもよい。

#### 【0021】

次に、本実施形態による光電変換装置の駆動方法について、図 1 及び図 2 を用いて説明する。40

#### 【0022】

まず、画素制御回路 20 から、制御信号線 14 を介して各行の画素 12 に、画素 12 内の読み出し回路を駆動する制御信号を出力する。これにより、各画素 12 からは、光電変換により生成された信号電荷に基づく画素信号が、垂直出力線バス 16 を介して保持回路 30 に出力される。このようにして、画素アレイ 10 から、全列全行の画素 12 の画素信号を保持回路 30 へ同時に読み出す（並列読み出し）。なお、全列全行の画素 12 の画素信号は、必ずしも並列読み出しする必要はなく、行毎に順次読み出すようにしてもよい（行順次読み出し）。行順次読み出しと比較した並列読み出しのメリットとしては、複数行

の画素 12 からの信号の読み出しを高速にできる点が挙げられる。

**【0023】**

次いで、保持回路 30 では、画素アレイ 10 から出力された画素信号に対して必要に応じて所定の電気的な処理を実施し、総ての画素 12 からの画素信号をそれぞれ独立して保持部に保持する。総ての画素 12 から読み出された画素信号、すなわち、光学フィルタの色が互いに異なる画素から読み出された画素信号は、それぞれが互いに並行して保持部に保持されることになる。保持回路 30 における所定の電気的な処理としては、例えば、各画素の画素信号を所定の保持部に保持するための切り替え処理や、画素信号を増幅するための増幅処理等の処理が挙げられる。

**【0024】**

保持回路 30 に保持された画素信号は、走査回路 60 からの制御信号に応じてスイッチ回路 50 のスイッチ 52 が順次動作することで、水平出力線 62 に順次読み出される（シリアル読み出し）。水平出力線 62 に出力された画素信号は、読み出しアンプ 70 で所定の電気的な処理を施された後に読み出される。読み出しアンプ 70 における所定の電気的な処理としては、画素信号を増幅するための増幅処理や、光電変換信号からのリセット信号の減算処理等が挙げられる。

**【0025】**

本実施形態による光電変換装置の駆動方法では、保持回路 30 に保持された画素信号を、画素 12 の種類毎に水平出力線 62 に連続して読み出す。例えば、まず、各列の R 画素の画素信号を水平出力線 62 に連続的に順次読み出す。次に、各列の G 画素の画素信号を水平出力線 62 に連続的に順次読み出す。次に、各列の B 画素の画素信号を水平出力線 62 に連続的に順次読み出す。

**【0026】**

その結果、読み出しアンプ 70 からは、例えば図 2 に示すように、同じ色の画素 12 の画素信号（出力信号 VOUT）が連続して読み出されることになる。同じ色の画素 12 の画素信号を連続して読み出すことにより、読み出しアンプ 70 から出力される信号の電位の変動を小さく抑えることが期待できる。これにより、直前に読み出した画素 12 の画素信号の影響による画素信号の変動を抑制することができる。特に、例えば図 2 に示すように、R 画素の画素信号と、G 画素の画素信号と、B 画素の画素信号との間の信号レベルの差が大きい場合、同じ色の画素 12 の画素信号を連続して読み出すことの効果は大きい。

**【0027】**

仮に、例えば図 3 に示すように、R 画素、G 画素及び B 画素の画素信号の信号レベルの差が大きい場合において、画素 12 の画素信号を行単位で読み出す場合を想定する。この場合、異なる色の画素 12 の画素信号が連続して読み出しアンプ 70 から読み出されることになる。例えば、画素 12 - R 1 の画素信号を読み出した後には、画素 12 - G 2 の画素信号が読み出される。画素 12 - R 1 の画素信号を読み出した後、画素 12 - G 2 の画素信号を読み出す前には、通常、水平出力線 62 をリセットするリセット動作が行われる。しかしながら、水平出力線 62 のリセットが不十分であると、次に読み出される画素 12 - G 2 の画素信号は、画素 12 - R 1 の画素信号の影響を受けて、真値よりも高い電位となることがある。同じように、画素 12 - B 3 の画素信号は、画素 12 - G 2 の画素信号の影響を受けて、真値よりも高い電位となることがある。また、画素 12 - B 2 の画素信号の後に読み出される画素 12 - R 3 の画素信号は、画素 12 - B 2 の画素信号の影響を受けて、真値よりも低い電位となることがある。その結果、異なる色の画素 12 からの画素信号の影響を受けて次に読み出す画素 12 の画素信号の信号レベルが変化する現象、言わば電気的な混色が生じることとなる。そして、取り込んだ画像を再生する際には、色再現性が低下するという不具合が生じる。このような電気的な混色は、読み出しアンプ 70 の応答性に依存するものであり、主走査方向の読み出しレートが高くなるにつれて顕在化する。

**【0028】**

この点、本実施形態による光電変換装置の駆動方法では、各列の同じ色の画素 12 の画

10

20

30

40

50

素信号を連続的に読み出すので、前述したような電気的な混色が生じることはなく、また、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。

#### 【0029】

このように、本実施形態によれば、各行及び各列に異なる色の画素をそれぞれ含む画素アレイを有する光電変換装置において、異なる色の画素から取得した画素信号間の電気的な混色を防止することができる。これにより、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。

#### 【0030】

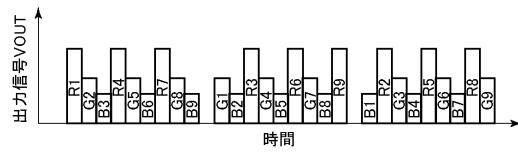

##### <第2実施形態>

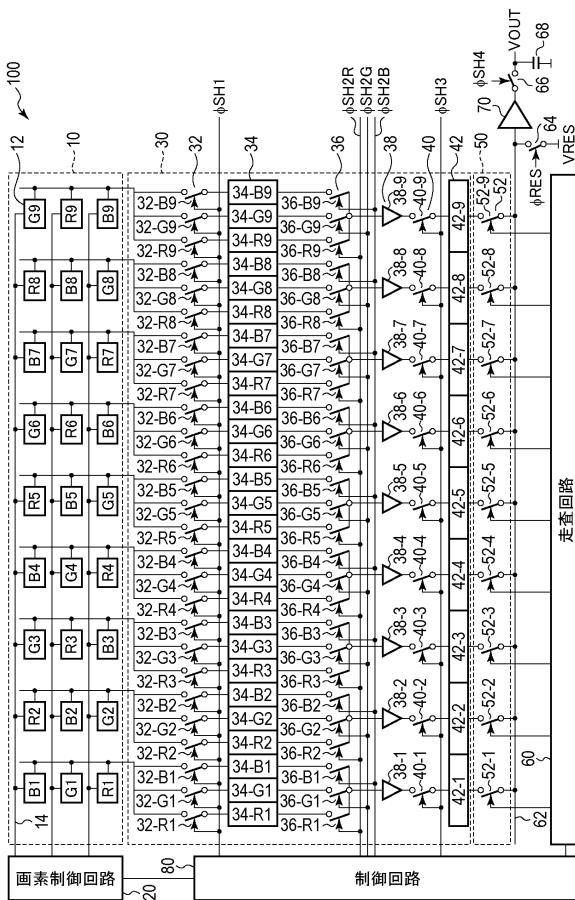

本発明の第2実施形態による光電変換装置及びその駆動方法について、図4乃至図6を用いて説明する。図4は、本実施形態による光電変換装置の構成を示す概略図である。図5は、本実施形態による光電変換装置の構成例を示す回路図である。図6は、本実施形態による光電変換装置の信号出力のタイミングを示す図である。図1乃至図3に示す第1実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

10

#### 【0031】

はじめに、本実施形態による光電変換装置の構造について、図4及び図5を用いて説明する。

#### 【0032】

本実施形態による光電変換装置の基本的な構成は、図1に示す第1実施形態による光電変換装置と同様である。本実施形態による光電変換装置は、以下の点において第1実施形態による光電変換装置とは相違している。

20

#### 【0033】

保持回路30は、画素アレイ10の各列に対応して、それぞれ複数の保持部34を有している。各列に対応して設けられた複数の保持部34は、当該列に配置された複数の画素12にそれぞれ対応している。例えば、図4において画素アレイ10の第1列に着目すると、3つの行の画素12-R1, 12-G1, 12-B1に対応して、保持部34-R1, 34-G1, 34-B1がそれぞれ設けられている。保持部34-R1は、画素12-R1から出力される画素信号を保持するための保持部である。保持部34-B1は、画素12-B1から出力される画素信号を保持するための保持部である。保持部34-G1は、画素12-G1から出力される画素信号を保持するための保持部である。

30

#### 【0034】

保持回路30には、R画素の画素信号を保持する保持部34-Rと、G画素の画素信号を保持する保持部34-Gと、B画素の画素信号を保持する保持部34-Bとが、規則的に繰り返し配置されている。図4の例では、R画素の画素信号の保持部34-R、G画素の画素信号の保持部34-G、B画素の画素信号の保持部34-Bが、この順番で繰り返し配置されている。

#### 【0035】

また、スイッチ回路50は、複数の保持部34のそれぞれと水平出力線62との間に設けられた複数のスイッチ52を有している。例えば、図4において画素アレイ10の第1列に着目すると、保持部34-R1と水平出力線62との間にスイッチ52-R1が設けられている。また、保持部34-G1と水平出力線62との間にスイッチ52-G1が設けられている。また、保持部34-B1と水平出力線62との間にスイッチ52-B1が設けられている。複数のスイッチ52の接続状態は、走査回路60から出力される制御信号によって制御される。また、水平出力線62とVRES電圧線との間には、スイッチ64が設けられている。

40

#### 【0036】

本実施形態による光電変換装置の画素アレイ10、保持回路30、スイッチ回路50は、例えば図5に示す回路により構成することができる。図5には、各部の構成要素について、第1列に対応する部分を抜き出して示している。

50

## 【0037】

画素 12 - R1, 12 - G1, 12 - B1 は、それぞれ、フォトダイオード D、転送トランジスタ M1、リセットトランジスタ M2、増幅トランジスタ M3 及び選択トランジスタ M4 を有している。フォトダイオード D は、光学フィルタを透過した光を光電変換することで電荷を生成する光電変換部である。

## 【0038】

フォトダイオード D のアノードは接地電圧線に接続され、フォトダイオード D のカソードは転送トランジスタ M1 のソースに接続されている。転送トランジスタ M1 のドレインは、リセットトランジスタ M2 のソース及び増幅トランジスタ M3 のゲートに接続されている。転送トランジスタ M1 のドレイン、リセットトランジスタ M2 のソース及び増幅トランジスタ M3 のゲートの接続ノードは、フローティングディフュージョン部（以下、「FD 部」と表記する）を構成する。リセットトランジスタ M2 のドレイン及び増幅トランジスタ M3 のドレインは、電源電圧線（電圧 VDD）に接続されている。増幅トランジスタ M3 のソースは、選択トランジスタ M4 のドレインに接続されている。10

## 【0039】

転送トランジスタ M1 のゲートには、画素制御回路 20 から図示しない転送ゲート信号線を介して、転送トランジスタ M1 の駆動用の転送ゲート信号 PTX が供給される。リセットトランジスタ M2 のゲートには、画素制御回路 20 から図示しないリセット信号線を介して、リセットトランジスタ M2 の駆動用のリセット信号 PRES が供給される。選択トランジスタ M4 のゲートには、画素制御回路 20 から図示しない選択信号線を介して、選択トランジスタ M4 の制御用の選択信号 PSEL が供給される。転送ゲート信号線、リセット信号線及び選択信号線は、図 4 の制御信号線 14 のそれぞれに含まれる。20

## 【0040】

垂直出力線バス 16 は、垂直出力線 16R, 16G, 16B を含む。垂直出力線 16R は、画素 12 - R1 の選択トランジスタ M4 のソースに接続されている。垂直出力線 16G は、画素 12 - G1 の選択トランジスタ M4 のソースに接続されている。垂直出力線 16B は、画素 12 - B1 の選択トランジスタ M4 のソースに接続されている。垂直出力線 16R, 16G, 16B の一端は、それぞれ、電流源 18 に接続されている。

## 【0041】

保持部 34 - R1, 34 - G1, 34 - B1 は、それぞれ、トランジスタ M5, M6 と容量素子 CS1, CN1 を含む。また、スイッチ 52 - R1, 52 - G1, 52 - B1 は、それぞれ、トランジスタ M7, M8 を含む。30

## 【0042】

保持部 34 - R1 及びスイッチ 52 - R1 を例にして説明すると、トランジスタ M5 - R1, M6 - R1 のドレインは、垂直出力線 16R の他端に接続されている。トランジスタ M5 - R1 のゲートには、制御回路 80 から、制御信号 PTS が供給される。トランジスタ M6 - R1 のゲートには、制御回路 80 から、制御信号 PTN が供給される。トランジスタ M5 - R1 のソースは、容量素子 CS1 - R1 の一方の端子と、トランジスタ M7 - R1 のドレインとに接続されている。容量素子 CS1 - R1 の他方の端子は、接地電圧線に接続されている。トランジスタ M7 - R1 のソースは、水平出力線 62S に接続されている。トランジスタ M6 - R1 のソースは、容量素子 CN1 - R1 の一方の端子と、トランジスタ M8 - R1 のドレインとに接続されている。容量素子 CN1 - R1 の他方の端子は、接地電圧線に接続されている。トランジスタ M8 - R1 のソースは、水平出力線 62N に接続されている。トランジスタ M7 - R1, M8 - R1 のゲートは、走査回路 60 に接続されている。保持部 34 - G1, 34 - B1、スイッチ 52 - G1, 52 - B1 についても同様である。40

## 【0043】

スイッチ 64 は、トランジスタ M9, M10 を含む。トランジスタ M9, M10 のドレインは、VRES 電圧線に接続されている。トランジスタ M9 のソースは、水平出力線 62S に接続されている。トランジスタ M10 のソースは、水平出力線 62N に接続されて50

いる。トランジスタM9, M10のゲートには、制御回路80から、制御信号RESが供給される。スイッチ64は、水平出力線62S, 62Nの電位をリセットするためのリセット回路を構成する。

#### 【0044】

次に、本実施形態による光電変換装置の駆動方法について、図4乃至図6を用いて説明する。

#### 【0045】

まず、画素制御回路20から制御信号線14を介して画素12にハイレベルの転送ゲート信号PTX及びリセット信号PREを出力し、転送トランジスタM1及びリセットトランジスタM2をオンにする。これにより、各画素12のフォトダイオードDに、転送トランジスタM1及びリセットトランジスタM2を介して電源電圧が印加され、フォトダイオードDの電位がリセットされる。フォトダイオードDのリセット動作を行った後、転送ゲート信号PTX及びリセット信号PREをローレベルとし、フォトダイオードDを電源電圧から切り離す。これにより、フォトダイオードDでは、入射光量に応じた信号電荷の蓄積動作が開始する。

10

#### 【0046】

所定の蓄積時間が経過した後、画素制御回路20から制御信号線14を介して画素12にハイレベルのリセット信号PREを出力し、リセットトランジスタM2をオンにする。これにより、FD部にリセットトランジスタM2を介して電源電圧が印加され、FD部の電位がリセットされる。FD部のリセット動作を行った後、リセット信号PREをローレベルとし、FD部を電源電圧から切り離す。これにより、FD部のリセット動作が完了する。

20

#### 【0047】

次いで、画素制御回路20から制御信号線14を介してハイレベルの選択信号PSELを出力し、各画素12の選択トランジスタM4をオンにする。増幅トランジスタM3は、選択トランジスタM4を介して電流源18からバイアス電流が供給された状態となり、ソースフォロワ回路を構成する。これにより、垂直出力線バス16には、FD部のリセット電圧に応じた信号(リセット信号)が、選択トランジスタM4を介して出力される。この際、制御信号PTNをハイレベルとしてトランジスタM6をオンすることで、垂直出力線バス16から出力されるリセット信号が容量素子CN1に保持される。

30

#### 【0048】

次いで、画素制御回路20から制御信号線14を介してハイレベルの転送ゲート信号PTXを出力し、転送トランジスタM1をオンにする。これにより、フォトダイオードDにおいて生成され、蓄積されていた信号電荷が、転送トランジスタM1を介してFD部に転送される。これにより、FD部は、FD部に転送された信号電荷の量及びFD部の容量に応じた電圧をリセット電圧に重畠した電圧となる。これにより、垂直出力線バス16には、FD部に転送された信号電荷の量に応じた信号(光電変換信号)が、選択トランジスタM4を介して出力される。この際、制御信号PTSをハイレベルとしてトランジスタM5をオンすることで、垂直出力線バス16から出力される光電変換信号が容量素子CS1に保持される。

40

#### 【0049】

このようにして、画素アレイ10から全列全行の画素12の画素信号を保持回路30へ同時に並列に読み出し、全ての画素12の画素信号をそれぞれ独立して保持部34に保持させる。例えば、画素アレイ10の第1列に着目すると、画素12-R1から出力された画素信号は、保持部34-R1に保持される。画素12-G1から出力された画素信号は、保持部34-G1に保持される。画素12-B1から出力された画素信号は、保持部34-B1に保持される。他の画素12から出力された画素信号についても同様に、当該画素12に対応する保持部34に保持される。

#### 【0050】

なお、全ての画素12の画素信号は、必ずしも同時に読み出す必要はなく、例えば、行

50

毎に順次読み出すようにしてもよい。この場合、画素制御回路 20 は、垂直走査回路として機能しうる。また、保持部 34 の前段に増幅回路を挿入し、増幅回路で増幅した画素信号を保持部 34 で保持するようにしてもよい。

#### 【0051】

保持回路 30 の保持部 34 に保持された画素信号は、走査回路 60 からの制御信号に応じてスイッチ回路 50 のスイッチ 52 が所定の順序で動作することで、水平出力線 62 に順次読み出される。まず、走査回路 60 からスイッチ 52 にハイレベルの制御信号を出力し、トランジスタ M7, M8 をオンにすることで、容量素子 CS1, CN1 に保持されている信号を水平出力線 62S, 62N にそれぞれ読み出す。次いで、制御信号 RES により、トランジスタ M9, M10 を駆動し、水平出力線 62S, 62N の電位を電圧 VRES にリセットする。この一連の動作を、各保持部 34 に対して順次、繰り返し行うことで、総ての画素 12 からの信号を水平出力線 62S, 62N に連続的に出力することができる。10

#### 【0052】

水平出力線 62S に出力された光電変換信号及び水平出力線 62N に出力されたリセット信号に対しては、読み出しアンプ 70 において差分処理が実施される。これにより、読み出しアンプ 70 からは、光電変換信号とリセット信号との差分信号である出力信号 VOUT が outputされる。読み出しアンプ 70 により電変換信号とリセット信号との差分演算を行うことにより、画素部の増幅トランジスタ M3 の閾値電圧などの特性バラツキに起因するノイズ信号を相殺することができ、S/N 比の高い出力信号を得ることができる。20

#### 【0053】

ここで、本実施形態による光電変換装置の駆動方法では、保持回路 30 に保持された画素信号を読み出す際に、画素 12 の種類毎に画素信号を連続して読み出す。

#### 【0054】

図 6 は、走査回路 60 からスイッチ 52 の制御ノードに出力される制御信号のタイミング図の一例である。各制御信号には、対応するスイッチ 52 の符号を付してある。これら制御信号は、ハイレベルのときに対応するスイッチ 52 がオンとなり、ローレベルのときに対応するスイッチ 52 がオフとなる。

#### 【0055】

まず、R 画素の画素信号が連続的に水平出力線 62 に読み出されるように、スイッチ 52 - R1, 52 - R2, 52 - R3, …, 52 - R9 を順次オンにする。次に、G 画素の画素信号が連続的に水平出力線 62 に読み出されるように、スイッチ 52 - G1, 52 - G2, 52 - G3, …, 52 - G9 を順次オンにする。次に、B 画素の画素信号が連続的に水平出力線 62 に読み出されるように、スイッチ 52 - B1, 52 - B2, 52 - B3, …, 52 - B9 を順次オンにする。なお、R 画素、G 画素、B 画素を読み出す順番は、図 6 の例に限定されるものではなく、任意に選択することができる。30

#### 【0056】

その結果、読み出しアンプ 70 からは、例えば図 6 に示すように、同じ色の画素 12 の画素信号が連続して読み出されることになる。これにより、第 1 実施形態において説明したように、画素信号の電気的な混色を防止し、また、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。40

#### 【0057】

また、保持回路 30 に全画素の画素信号を R 画素、G 画素、B 画素の順に規則的に保持することで、スイッチ 52 を駆動する順番の制御を簡素化することができる。

#### 【0058】

R 画素、G 画素、B 画素が異なる行に割り振られた線順次配列のカラーラインセンサでは、行毎に読み出しを実施することで同じ色の画素の画素信号を連続して読み出すことはできる。しかしながら、本実施形態の光電変換装置のような色配列が点順次配列のカラーラインセンサでは、色配列が線順次配置のカラーラインセンサと同じ読み出し順にしようとすると、ラインセンサの出力信号の A/D 変換後に信号の順番を並べ替える処理が必要で50

ある。そのために、多くのメモリが必要であるとともに、信号を並べ替える処理に時間を要する。

#### 【0059】

この点、本実施形態の光電変換装置では、スイッチ回路50における簡単なスイッチ操作によって、多くのメモリや信号を並べ替える処理を必要とすることなく、同じ色の画素12の画素信号を連続して読み出すことができる。

#### 【0060】

また、本実施形態による光電変換装置では、1つの水平出力線62のチャンネルで同じ色の画素12の画素信号を連続して読み出すことができる。また、R、G、Bに応じた3色分のチャンネルを備えなくてもよい。その結果、回路規模の縮小化、低消費電力化が可能となる。10

#### 【0061】

このように、本実施形態によれば、各行及び各列に異なる色の画素をそれぞれ含む画素アレイを有する光電変換装置において、異なる色の画素から取得した画素信号間の電気的な混色を防止することができる。これにより、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。

#### 【0062】

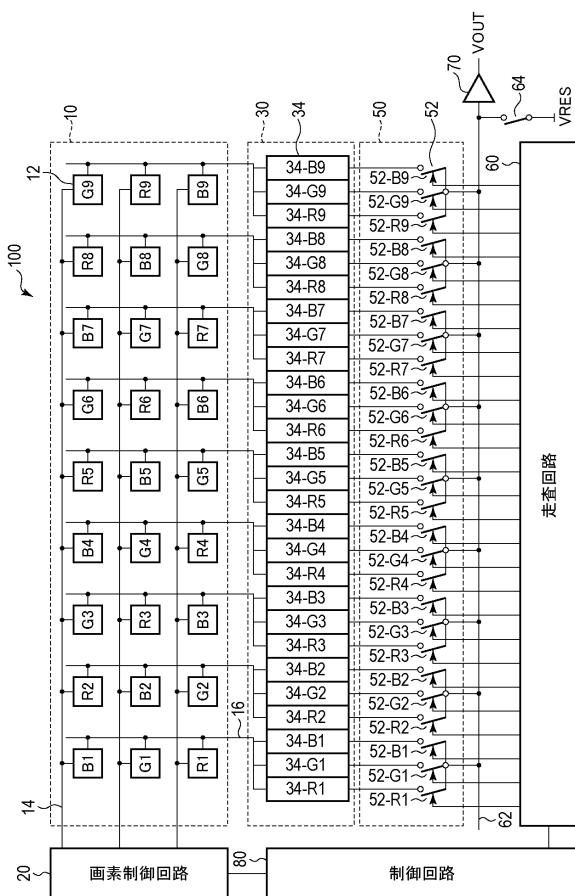

##### <第3実施形態>

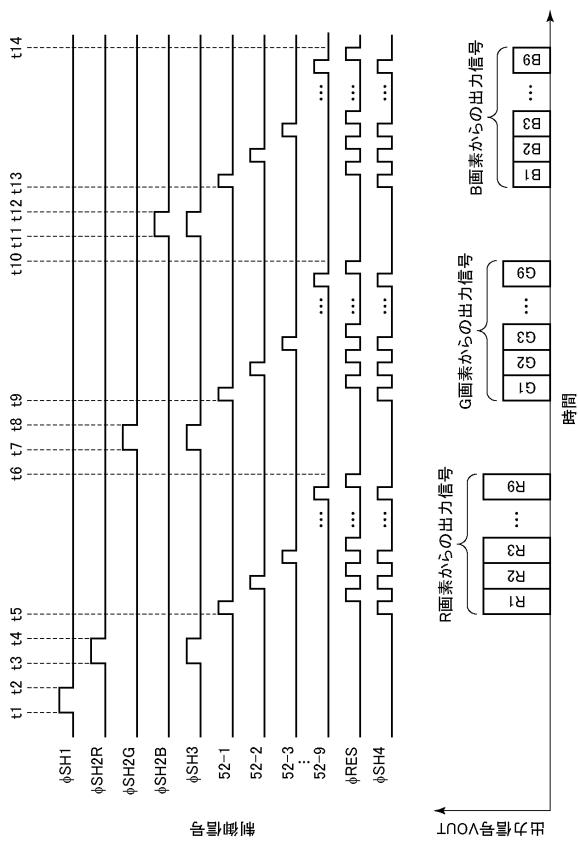

本発明の第3実施形態による光電変換装置及びその駆動方法について、図7及び図8を用いて説明する。図7は、本実施形態による光電変換装置の構成を示す概略図である。図8は、本実施形態による光電変換装置の信号出力のタイミングを示す図である。図1乃至図6に示す第1及び第2実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。20

#### 【0063】

はじめに、本実施形態による光電変換装置の構造について、図7を用いて説明する。

#### 【0064】

本実施形態による光電変換装置の基本的な構成は、図1に示す第1実施形態による光電変換装置と同様である。本実施形態による光電変換装置は、以下の点において第1実施形態による光電変換装置とは相違している。

#### 【0065】

保持回路30は、画素アレイ10の各列に対応して、それぞれ、複数のスイッチ32、複数の第1の保持部34、複数のスイッチ36、バッファ回路38、スイッチ40、第2の保持部42を有している。また、スイッチ回路50が、画素アレイ10の各列に対応して、スイッチ52をそれぞれ有している。30

#### 【0066】

各列に対応して設けられた複数のスイッチ32、複数の保持部34及び複数のスイッチ36のそれぞれは、当該列に配置された複数の画素12にそれぞれ対応している。

#### 【0067】

例えば、図7において画素アレイ10の第1列に着目すると、画素12-R1, 12-G1, 12-B1に対応して、スイッチ32-R1, 32-G1, 32-B1がそれぞれ設けられている。また、画素12-R1, 12-G1, 12-B1に対応して、第1の保持部34-R1, 34-G1, 34-B1がそれぞれ設けられている。また、また、画素12-R1, 12-G1, 12-B1に対応して、スイッチ36-R1, 36-G1, 36-B1がそれぞれ設けられている。40

#### 【0068】

スイッチ32-R1は、画素12-R1と第1の保持部34-R1との間に設けられている。スイッチ32-G1は、画素12-G1と第1の保持部34-G1との間に設けられている。スイッチ32-B1は、画素12-B1と第1の保持部34-B1との間に設けられている。スイッチ32-R1, 32-G1, 32-B1は、それぞれの制御ノードに入力される制御信号SH1により制御され、例えば、制御信号SH1がハイレベル50

のときにオン状態となり、制御信号 S H 1 がローレベルのときにオフ状態となる。制御信号 S H 1 は、制御回路 8 0 やその他の制御回路から出力される。なお、スイッチ 3 2 は、保持部 3 4 の一部を構成するスイッチ、例えば図 5 のトランジスタ M 5 , M 6 により構成してもよい。

#### 【 0 0 6 9 】

スイッチ 3 6 - R 1 は、第 1 の保持部 3 4 - R 1 とバッファ回路 3 8 - 1 との間に設けられている。スイッチ 3 6 - G 1 は、第 1 の保持部 3 4 - G 1 とバッファ回路 3 8 - 1 との間に設けられている。スイッチ 3 6 - B 1 は、第 1 の保持部 3 4 - B 1 とバッファ回路 3 8 - 1 との間に設けられている。スイッチ 3 6 - R 1 は、制御ノードに入力される制御信号 S H 2 R により制御され、例えば、制御信号 S H 2 R がハイレベルのときにオン状態となり、制御信号 S H 2 R がローレベルのときにオフ状態となる。スイッチ 3 6 - G 1 は、制御ノードに入力される制御信号 S H 2 G により制御され、例えば、制御信号 S H 2 G がハイレベルのときにオン状態となり、制御信号 S H 2 G がローレベルのときにオフ状態となる。スイッチ 3 6 - B 1 は、制御ノードに入力される制御信号 S H 2 B により制御され、例えば、制御信号 S H 2 B がハイレベルのときにオン状態となり、制御信号 S H 2 B がローレベルのときにオフ状態となる。制御信号 S H 2 R , S H 2 G , S H 2 B は、制御回路 8 0 やその他の制御回路から出力される。

#### 【 0 0 7 0 】

バッファ回路 3 8 - 1 は、スイッチ 4 0 - 1 を介して第 2 の保持部 4 2 - 1 に接続されている。スイッチ 4 0 - 1 は、制御ノードに入力される制御信号 S H 3 により制御され、例えば、制御信号 S H 3 がハイレベルのときにオン状態となり、制御信号 S H 3 がローレベルのときにオフ状態となる。制御信号 S H 3 は、制御回路 8 0 やその他の制御回路から出力される。

#### 【 0 0 7 1 】

第 2 の保持部 4 2 - 1 は、スイッチ回路 5 0 のスイッチ 5 2 - 1 を介して、水平出力線 6 2 に接続されている。第 2 の保持部 4 2 - 1 は、図 5 に示す第 1 の保持部 3 4 - R 1 等と同様の回路により構成することができる。スイッチ 5 2 - 1 は、走査回路 6 0 から出力される制御信号によって制御され、例えば、当該制御信号がハイレベルのときにオン状態となり、当該制御信号がローレベルのときにオフ状態となる。

#### 【 0 0 7 2 】

画素アレイ 1 0 の他の列に対応して設けられた複数のスイッチ 3 2 、複数の第 1 の保持部 3 4 、複数のスイッチ 3 6 、バッファ回路 3 8 、スイッチ 4 0 及び第 2 の保持部 4 2 についても同様である。

#### 【 0 0 7 3 】

R 画素の画素信号を保持する第 1 の保持部 3 4 - R 、 G 画素の画素信号を保持する第 1 の保持部 3 4 - G 及び B 画素の画素信号を保持する第 1 の保持部 3 4 - B は、第 2 実施形態の場合と同様、所定の順番で繰り返し配置されている。図 7 の例では、R 画素の画素信号の第 1 の保持部 3 4 - R 、 G 画素の画素信号の第 1 の保持部 3 4 - G 、 B 画素の画素信号の第 1 の保持部 3 4 - B が、この順番で繰り返し配置されている。

#### 【 0 0 7 4 】

また、水平出力線 6 2 と V R E S 電圧線との間には、制御信号 R E S により制御されるスイッチ 6 4 が設けられている。読み出しアンプ 7 0 の出力ノードには、制御信号 S H 4 により制御されるスイッチ 6 6 を介して、容量素子 6 8 が接続されている。スイッチ 6 4 , 6 6 は、例えば、制御信号 R E S , S H 4 がハイレベルのときにオン状態となり、制御信号 R E S , S H 4 がローレベルのときにオフ状態となる。制御信号 R E S , S H 4 は、制御回路 8 0 やその他の制御回路から出力される。

#### 【 0 0 7 5 】

次に、本実施形態による光電変換装置の駆動方法について、図 8 を用いて説明する。

#### 【 0 0 7 6 】

所定の露光期間が経過した後、時刻 t 1 において、制御信号 S H 1 がローレベルから

10

20

30

40

50

ハイレベルへと遷移してスイッチ 3 2 が総てオンとなり、それぞれの画素 1 2 がスイッチ 3 2 を介して対応する第 1 の保持部 3 4 に接続される。これにより、総ての画素 1 2 の画素信号が、対応する第 1 の保持部 3 4 にそれぞれ保持される。

#### 【 0 0 7 7 】

次いで、時刻  $t_2$ において、制御信号  $S_{H1}$  がハイレベルからローレベルへと遷移し、スイッチ 3 2 が総てオフとなる。

#### 【 0 0 7 8 】

次いで、時刻  $t_3$ において、制御信号  $S_{H2R}$  及び制御信号  $S_{H3}$  をローレベルからハイレベルへと遷移し、スイッチ 3 6 - R 及びスイッチ 4 0 をオンにする。これにより、各列の第 1 の保持部 3 4 - R が、スイッチ 3 6 - R、バッファ回路 3 8、スイッチ 4 0 を介して各列の第 2 の保持部 4 2 に接続される。そして、各列の第 1 の保持部 3 4 - R に保持されていた画素信号は、バッファ回路 3 8 で増幅された後に各列の第 2 の保持部 4 2 に保持される。10

#### 【 0 0 7 9 】

次いで、時刻  $t_4$ において、制御信号  $S_{H2R}$ ,  $S_{H3}$  がハイレベルからローレベルへと遷移し、スイッチ 3 6 - R, 4 0 が総てオフ状態となる。

#### 【 0 0 8 0 】

なお、時刻  $t_3$  から時刻  $t_4$  の期間において、制御信号  $S_{H2G}$ ,  $S_{H2B}$  はローレベル、すなわちスイッチ 3 6 - G, 3 6 - B はオフのままであり、G 画素及び B 画素の画素信号は、第 2 の保持部 4 2 には転送されない。つまり、第 2 の保持部 4 2 に転送される画素信号は、R 画素から出力された画素信号のみである。20

#### 【 0 0 8 1 】

次いで、時刻  $t_5$  から時刻  $t_6$  の期間において、第 2 の保持部 4 2 に保持されている各列の R 画素の画素信号を、水平出力線 6 2 に順次読み出す。具体的には、まず、走査回路 6 0 からの制御信号によってスイッチ回路 5 0 のスイッチ 5 2 をオンにして第 2 の保持部 4 2 に保持されている画素信号を水平出力線 6 2 に読み出す（読み出し期間）。水平出力線 6 2 に出力された画素信号は、読み出しアンプ 7 0 で所定の電気的な処理を施された後に出力され、保持部として機能する容量素子 6 8 に保持される。次いで、制御信号  $R_{ES}$  をハイレベルにしてスイッチ 6 4 をオンにし、水平出力線 6 2 をリセットレベルの電圧にリセットする（リセット期間）。読み出し期間及びリセット期間の一連の動作を、各列の第 2 の保持部 4 2 に対して順次行うことで、第 1 列から第 9 列までの R 画素の画素信号を連続的に読み出す。30

#### 【 0 0 8 2 】

時刻  $t_5$  から時刻  $t_6$  の期間において、制御信号  $S_{H4}$  の信号レベルは、制御信号  $R_{ES}$  の信号レベルに対して逆位相とすることが望ましい。すなわち、制御信号  $R_{ES}$  がハイレベルのときに制御信号  $S_{H4}$  はローレベルとし、制御信号  $R_{ES}$  がローレベルのときに制御信号  $S_{H4}$  はハイレベルとする。これは、読み出しアンプ 7 0 が容量素子 6 8 を駆動する負荷を減らして出力信号  $V_{OUT}$  のセトリング時間を短くするためである。

#### 【 0 0 8 3 】

読み出しアンプ 7 0 の出力ノードに容量素子 6 8 が接続された状態で水平出力線 6 2 のリセットを行うと、水平出力線 6 2 のリセット電圧を増幅した信号が容量素子 6 8 に保持されることになる。このため、画素信号を容量素子 6 8 に保持する際には、容量素子 6 8 のリセット電圧レベルの電圧を画素信号レベルの電圧に書き換えることになる。40

#### 【 0 0 8 4 】

この点、本実施形態の駆動方法では、読み出しアンプ 7 0 で増幅された画素信号は容量素子 6 8 に保持されるが、スイッチ 6 4 がオンのときにはスイッチ 6 6 はオフであり、水平出力線 6 2 のリセット電圧を増幅した信号が容量素子 6 8 に保持されることはない。すなわち、容量素子 6 8 には、読み出しアンプ 7 0 で増幅された画素信号が選択的に保持される。そのため、容量素子 6 8 に保持されている R 画素の画素信号を次の列の R 画素の画50

素信号で書き換えると足り、リセット電圧レベルの電圧を画素信号レベルの電圧に書き換える場合と比較して、出力信号 VOUT のセトリング時間を短くすることができる。

#### 【0085】

また、水平出力線 62 には寄生容量が存在するため、水平出力線 62 のリセットには相応の時間を要する。仮に、水平出力線 62 に読み出されている画素信号をこのリセット動作でリセットしきれなくても、次に読み出される画素信号は同じ色の画素信号であるので、混色にはならず、色再現性が悪化することもない。

#### 【0086】

次いで、時刻  $t_7$ において、制御信号 SH2G 及び制御信号 SH3 をローレベルからハイレベルへと遷移し、スイッチ 36-G 及びスイッチ 40 をオンにする。これにより、各列の第 1 の保持部 34-G が、スイッチ 36-G、バッファ回路 38、スイッチ 40 を介して各列の第 2 の保持部 42 に接続される。そして、各列の第 1 の保持部 34-G に保持されていた画素信号は、バッファ回路 38 で増幅された後に各列の第 2 の保持部 42 に保持される。

#### 【0087】

次いで、時刻  $t_8$ において、制御信号 SH2G, SH3 がハイレベルからローレベルへと遷移し、スイッチ 36-G, 40 が総てオフ状態となる。

#### 【0088】

なお、時刻  $t_7$ から時刻  $t_8$ の期間において、制御信号 SH2R, SH2B はローレベル、すなわちスイッチ 36-R, 36-B はオフ状態のままであり、R 画素及び B 画素の画素信号は、第 2 の保持部 42 には転送されない。つまり、第 2 の保持部 42 に転送される画素信号は、G 画素から出力された画素信号のみである。

#### 【0089】

次いで、時刻  $t_9$ から時刻  $t_{10}$ の期間において、第 2 の保持部 42 に保持されている各列の G 画素の画素信号を、時刻  $t_7$ から時刻  $t_8$ の期間における各列の R 画素の画素信号の読み出し動作と同様にして、水平出力線 62 に順次読み出す。

#### 【0090】

次いで、時刻  $t_{11}$ において、制御信号 SH2B 及び制御信号 SH3 をローレベルからハイレベルへと遷移し、スイッチ 36-B 及びスイッチ 40 をオンにする。これにより、各列の第 1 の保持部 34-B が、スイッチ 36-B、バッファ回路 38、スイッチ 40 を介して各列の第 2 の保持部 42 に接続される。そして、各列の第 1 の保持部 34-B に保持されていた画素信号は、バッファ回路 38 で増幅された後に各列の第 2 の保持部 42 に保持される。

#### 【0091】

次いで、時刻  $t_{12}$ において、制御信号 SH2B, SH3 がハイレベルからローレベルへと遷移し、スイッチ 36-B, 40 が総てオフ状態となる。

#### 【0092】

なお、時刻  $t_{11}$ から時刻  $t_{12}$ の期間において、制御信号 SH2R, SH2G はローレベル、すなわちスイッチ 36-R, 36-G はオフ状態のままであり、R 画素及び G 画素の画素信号は、第 2 の保持部 42 には転送されない。つまり、第 2 の保持部 42 に転送される画素信号は、B 画素から出力された画素信号のみである。

#### 【0093】

次いで、時刻  $t_{13}$ から時刻  $t_{14}$ の期間において、第 2 の保持部 42 に保持されている各列の B 画素の画素信号を、時刻  $t_7$ から時刻  $t_8$ の期間における各列の R 画素の画素信号の読み出し動作と同様にして、水平出力線 62 に順次読み出す。

#### 【0094】

これにより、第 1 及び第 2 実施形態の場合と同様、同じ色の画素 12 の画素信号を連続して読み出すことができるので、異なる色の画素 12 の画素信号間の電気的な混色を抑制することができる。

#### 【0095】

10

20

30

40

50

また、本実施形態では、第1の保持部34に画素信号を読み出す際に、全画素の画素信号をR、G、Bの順に規則的に保持している。この動作では、総ての画素12の画素信号を並列的に同時に読み出すため、時間をかけて読み出しても、一の画素12の画素信号を読み出すのに要する時間、すなわちビットレートが大きく低下しない。図8の時刻t1～時刻t2の期間において時間をかけて第1の保持部34に画素信号を読み出して保持することで、第1の保持部34において、隣に異なる色の画素信号が保持されても電気的な混色を起こしにくい。

#### 【0096】

また、本実施形態の光電変換装置は、図7に示すように、保持回路30が、第1の保持部34と第2の保持部42とを有している。保持回路30が第1の保持部34及び第2の保持部42の2つの保持部を有することで、以下に説明する更なる効果を奏することができる。10

#### 【0097】

第2実施形態の光電変換装置は、図4に示すように、保持回路30が、1つの保持部34を有している。ここで、保持部34の保持手段は容量素子（図5の容量素子CS1, CN1）である。水平出力線62には、寄生容量が存在する。保持部34の容量素子の容量値をC1、水平出力線62の寄生容量の容量値をCp、保持部34の容量素子に保持された電圧をV1とすると、水平出力線62の電圧は、 $V_1 \times C_1 / (C_1 + C_p)$ となり、感度が低下する。感度低下を抑えるには、保持部の容量素子の容量値C1を大きくする必要がある。そのためには、第2実施形態による光電変換装置では、保持回路30が有する27個の保持部34の容量素子の容量値（面積）を総て大きくする必要がある。20

#### 【0098】

これに対し、本実施形態による光電変換装置では、9個の第2の保持部42の容量素子の容量値（面積）を大きくするだけでよい。第1の保持部34と第2の保持部42との間にはバッファ回路38が挿入されており、第1の保持部34から画素信号を読み出す際の感度の低下は生じない。そのため、本実施形態による光電変換装置では、第1の保持部34の容量素子の容量値は小さくすることができる。さらに、第2の保持部42の画素信号を水平出力線62に読み出す際のゲインの低下を抑えるために、第2の保持部42の容量素子の容量値は大きくする。その結果、第2実施形態と比較して、感度の低下を抑えつつ、保持回路30の面積を小さくすることができる。30

#### 【0099】

このように、本実施形態によれば、各行及び各列に異なる色の画素をそれぞれ含む画素アレイを有する光電変換装置において、異なる色の画素から取得した画素信号間の電気的な混色を防止することができる。これにより、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。

#### 【0100】

##### <第4実施形態>

本発明の第4実施形態による光電変換装置及びその駆動方法について、図9を説明する。図9は、本実施形態による光電変換装置の構成を示す概略図である。図1乃至図8に示す第1乃至第3実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。40

#### 【0101】

本実施形態による光電変換装置は、図9に示すように、水平出力線62以降が3チャンネル化されているほかは、図7に示す第3実施形態による光電変換装置と同様である。

#### 【0102】

すなわち、本実施形態による光電変換装置100は、図9に示すように、水平出力線62-1、読み出しアンプ70-1、スイッチ64-1, 66-1、容量素子68-1で構成される第1のチャンネルを有している。また、水平出力線62-2、読み出しアンプ70-2、スイッチ64-2, 66-2、容量素子68-2で構成される第2のチャンネルを有している。また、水平出力線62-3、読み出しアンプ70-3、スイッチ64-3

, 66 - 3、容量素子 68 - 3 で構成される第 3 のチャンネルを有している。

**【0103】**

第 2 の保持部 42 - 1, 42 - 4, 42 - 7 は、それぞれスイッチ 52 - 1, 52 - 4, 52 - 7 を介して、水平出力線 62 - 1 に接続されている。第 2 の保持部 42 - 2, 42 - 5, 42 - 8 は、それぞれスイッチ 52 - 2, 52 - 5, 52 - 8 を介して、水平出力線 62 - 2 に接続されている。第 2 の保持部 42 - 3, 42 - 6, 42 - 9 は、それぞれスイッチ 52 - 3, 52 - 6, 52 - 9 を介して、水平出力線 62 - 3 に接続されている。

**【0104】**

光電変換装置をこのように構成することで、各チャンネルからの信号出力を並列して行うことができる。例えば R 画素については、画素 12 - R1, 12 - R4, 12 - R7 の画素信号の読み出しと、画素 12 - R2, 12 - R5, 12 - R8 の画素信号の読み出しと、画素 12 - R3, 12 - R6, 12 - R9 の画素信号の読み出しとを並列に行うことができる。つまり、図 8 のタイミング図において、時刻 t5 ~ 時刻 t6 の期間、時刻 t9 ~ 時刻 t10 の期間、時刻 t13 ~ 時刻 t14 の期間を、それぞれ 1 / 3 に短縮することができる。また、水平出力線 62 - 1, 62 - 2, 62 - 3 に同時刻に読み出されている画素信号は、同色の画素 12 の画素信号となる。

10

**【0105】**

それぞれのチャンネルにおいて同じ色の画素 12 の画素信号が連続して読み出されたとしても、別のチャンネルで異なる色の画素 12 の画素信号が読み出されている場合には、チャンネル間で電気的な混色が生じる虞がある。

20

**【0106】**

しかしながら、本実施形態による光電変換装置では、それぞれのチャンネルでは同じ色の画素 12 からの画素信号が連続して読み出され、かつ、総てのチャンネルにおいて同時に同じ色の画素 12 からの画素信号が読み出される。したがって、水平出力線 62 - 1, 62 - 2, 62 - 3 の間ににおいて電気的な混色が生じることはなく、色再現性の低下を抑制することができる。

**【0107】**

このように、本実施形態によれば、各行及び各列に異なる色の画素をそれぞれ含む画素アレイを有する光電変換装置において、異なる色の画素から取得した画素信号間の電気的な混色を防止することができる。これにより、取り込んだ画像を再生する際の色再現性の低下を抑制することができる。

30

**【0108】**

< 第 5 実施形態 >

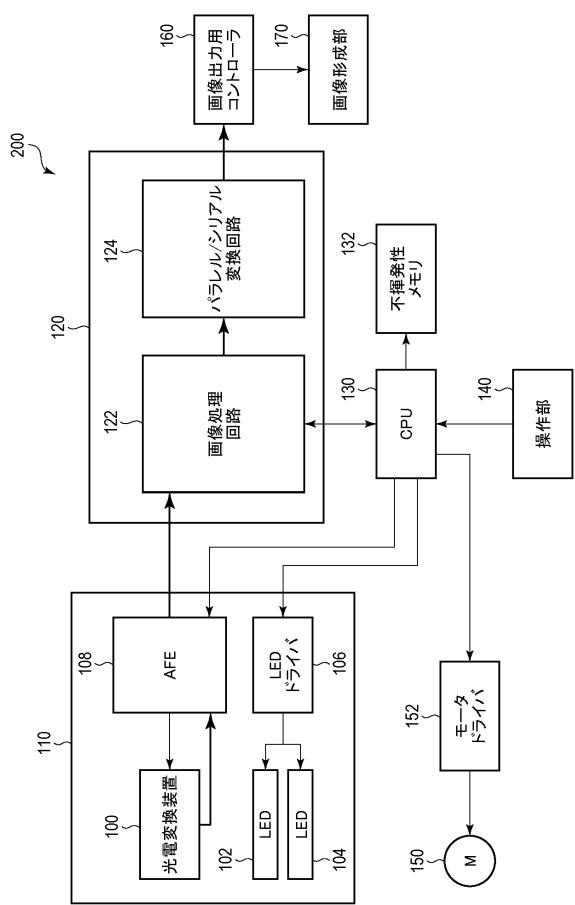

本発明の第 5 実施形態による画像読み取り装置及び画像形成装置について、図 10 を用いて説明する。

**【0109】**

本実施形態では、第 1 乃至第 4 実施形態による光電変換装置を適用した画像読み取り装置及び画像形成装置の一例を示す。画像読み取り装置及び画像形成装置としては、特に限定されるものではないが、例えば、複写機やマルチファンクションプリンタ等が挙げられる。ただし、第 1 乃至第 4 実施形態による光電変換装置は、本実施形態に示す画像読み取り装置及び画像形成装置に限らず、光電変換装置を含む種々の装置に適用可能である。

40

**【0110】**

本実施形態による画像読み取り装置 200 は、図 10 に示すように、読取部 110、画像処理部 120、CPU 130、不揮発性メモリ 132、操作部 140、モーター 150、モータードライバ 152、画像出力用コントローラ 160 を含む。読取部 110 は、光電変換装置 100、LED 102, 104、LED ドライバ 106、IC 108 を含む。画像処理部 120 は、画像処理回路 122、パラレル / シリアル変換回路 124 を含む。

**【0111】**

CPU 130 は、不揮発性メモリ 132 に格納された制御プログラムを読み出し、画像

50

読み取り装置 200 の全体の制御を行う。操作部 140 は、ユーザーがカラーコピーやモノクロコピー、両面コピーといったコピーモードの設定や、コピー開始の指示を入力するユーザーインターフェースである。

#### 【 0 1 1 2 】

LED ドライバ 106 は、CPU 130 からのタイミング信号を受け、発光部、すなわち白色の LED 102, 104 を発光させるための電流を供給する。これにより、LED 102, 104 は、画像の読み取り対象物（原稿）に光を照射する。光電変換装置 100 は、原稿から反射された光を受光し、光電変換により電気信号に変換し、入射した光量に応じたアナログ電圧信号を出力する。IC 108 は、光電変換装置 100 から出力されるアナログ電圧信号に対し、サンプルホールド処理、オフセット処理、ゲイン処理といったアナログ処理を行い、アナログ処理された電圧信号をデジタルデータ（以下、輝度データ）に変換する。IC 108 は、一般的に AFE (A n a l o g F r o n t E n d) と呼ばれる。なお、IC 108 の機能の一部或いは全部は、光電変換装置 100 に搭載してもよい。

#### 【 0 1 1 3 】

モーター 150 は、読み取り部 110 を副走査方向に移動させる。モータードライバ 152 は、CPU 130 からのタイミング信号を受け、モーター 150 を回転制御させるための励磁電流を供給する。

#### 【 0 1 1 4 】

画像処理回路 122 は、IC 108 から出力される読み取りデータに対して、シェーディング補正処理やフィルタ処理などの画像処理を施す。なお、画像処理を行うために必要となるフィルタの設定等は電源投入時に CPU 130 によって画像処理回路 122 内のレジスタに設定される。パラレル／シリアル変換回路 124 は、画像処理回路 122 からパラレルのデータとして出力される各種画像処理後の読み取りデータをシリアルデータに変換する。シリアルデータに変換された読み取りデータは、画像出力用コントローラ 160 に送信される。

#### 【 0 1 1 5 】

画像出力用コントローラ 160 に送信された読み取りデータは、画像形成部 170 に送られる。画像読み取り装置 200 と画像形成部 170 とにより、画像形成装置が構成される。公知の画像形成部 170 の一例としては、電子写真方式の画像形成部が挙げられる。電子写真方式の画像形成部 170 は、感光ドラムに形成された静電潜像をトナー像に現像し、紙などの記録媒体にトナー像を転写することで像形成を行う。これにより、画像形成装置は、画像読み取り装置 200 により読み込まれた画像を、画像形成部により記録媒体に形成することができる。

#### 【 0 1 1 6 】

第 1 乃至第 4 実施形態で説明したように、上記実施形態の光電変換装置は、異なる色の画素間における画素信号の電気的な混色を効果的に抑制する。したがって、上記実施形態の光電変換装置を用いることにより、混色のない良質の画像を取得しうる画像読み取り装置、色再現性に優れた画像形成装置を実現することができる。

#### 【 0 1 1 7 】

##### < 变形実施形態 >

本発明は、上記実施形態に限らず種々の変形が可能である。

#### 【 0 1 1 8 】

例えば、上記実施形態では、R 画素、G 画素、B 画素の 3 種類の画素 12 を含む画素アレイ 10 を有する光電変換装置について説明したが、色の組み合わせは必ずしも R, G, B に限られるものではない。また、画素 12 の種類は必ずしも 3 種類である必要はなく、4 種類等、必要に応じて適宜増減することができる。画素アレイ 10 の行数は、画素 12 の種類に応じて増減すればよい。また、画素アレイ 10 は、入射光に応じた画素信号を出力する画素以外の画素、例えばダミー画素等を含んでもよい。

#### 【 0 1 1 9 】

10

20

30

40

50

また、図5における画素12、保持部34、スイッチ52等の回路構成は、一例を示したものであり、適宜変更が可能である。例えば、画素12は、選択トランジスタM4を省略してもよい。

#### 【0120】

また、第3実施形態に示した、第2の保持部42から水平出力線62への読み出しのタイミング、水平出力線62のリセットのタイミング、読み出しアンプ70の出力のサンプルホールドのタイミングを、第1又は第2実施形態に適用してもよい。

#### 【0121】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

##### 【0122】

10 10 ... 画素アレイ

12 ... 画素

14 ... 制御信号線

16 ... 垂直出力線バス

20 ... 画素制御回路

30 ... 保持回路

32, 36, 40, 52, 64, 66 ... スイッチ

34, 42 ... 保持部

38 ... バッファ回路

50 ... スイッチ回路

60 ... 走査回路

62 ... 水平出力線

68 ... 容量素子

70 ... 読み出しアンプ

80 ... 制御回路

100 ... 光電変換装置

200 ... 画像読み取り装置

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 伊庭 潤

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 大室 秀明

(56)参考文献 特開2010-199710 (JP, A)

特開平08-116402 (JP, A)

特開2012-227590 (JP, A)

特開2010-103708 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L21/339

H01L27/14-27/148

H01L27/30

H01L29/762

H04N 1/024-1/036

H04N 5/30-5/378

H04N 9/04-9/11