(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4217614号

(P4217614)

(45) 発行日 平成21年2月4日(2009.2.4)

(24) 登録日 平成20年11月14日(2008.11.14)

(51) Int.Cl.

H04N 5/335 (2006.01)

H01L 27/14 (2006.01)

F 1

H04N 5/335

H01L 27/14Z

K

請求項の数 12 (全 11 頁)

(21) 出願番号 特願2003-517884 (P2003-517884)

(86) (22) 出願日 平成14年7月24日 (2002.7.24)

(65) 公表番号 特表2004-537904 (P2004-537904A)

(43) 公表日 平成16年12月16日 (2004.12.16)

(86) 國際出願番号 PCT/GB2002/003380

(87) 國際公開番号 WO2003/012794

(87) 國際公開日 平成15年2月13日 (2003.2.13)

審査請求日 平成17年7月5日 (2005.7.5)

(31) 優先権主張番号 0118678.2

(32) 優先日 平成13年8月1日 (2001.8.1)

(33) 優先権主張国 英国(GB)

(73) 特許権者 501297550

キネティック リミテッド

イギリス ロンドン エスタブリュー1イ

ー 6ピードイー バッキンガム ゲート

85

(74) 代理人 100082005

弁理士 熊倉 穎男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100074228

弁理士 今城 俊夫

(74) 代理人 100086771

弁理士 西島 孝喜

最終頁に続く

(54) 【発明の名称】 ランダムアクセス復号器

## (57) 【特許請求の範囲】

## 【請求項1】

少なくとも1つの復号器を備える読み取り回路であって、

前記各復号器は、複数の復号器回路素子、及び、前記復号器回路素子の各々に入力信号を与えるための手段を備え、前記各復号器回路素子は、固有の電子アドレス、及び二値データ出力を有し、個々の復号器回路素子の前記固有の電子アドレスが、前記与えられた入力信号と一致する時にのみ、その二値データ出力上にデータを出力し、前記複数の復号器回路素子の各々の前記固有の電子アドレスは、前記復号器回路素子の各々に電子的に書き込まれ、

画像アレイで使用するようにされ、かつ、

前記各復号器と関連付けられたシフトレジスタを更に備え、前記各復号器は、その長手方向の任意の点において、それと関連付けられた前記シフトレジスタに書き込むように配列された

ことを特徴とする読み取り回路。

## 【請求項2】

前記各復号器回路素子が、同じ配列で電気的に接続された等価な電気コンポーネントを含む

ことを特徴とする請求項1に記載の読み取り回路。

## 【請求項3】

二又はそれ以上の前記復号器回路素子が、物理的に同一の回路設計により形成された

ことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。

【請求項 4】

全ての前記復号器回路素子が、物理的に同一の回路設計により形成されたことを特徴とする請求項1又は2に記載の読み取り回路。

【請求項 5】

前記各復号器回路素子が、該各復号器回路素子に対し固有の電気アドレスが電子的に書き込まれるように、直列に接続された加算器コンポーネントを含むことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。

【請求項 6】

前記各復号器回路素子が、個々の復号器回路の前記固有の電気アドレスが前記与えられた入力信号と一致するかどうか、を判定する比較器コンポーネントを含むことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。 10

【請求項 7】

多数の行及び/又は列を有する画像アレイから、データを読み取るように配列されたことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。

【請求項 8】

画素素子の一次元アレイを備える画像アレイから、データを読み取るように配列されたことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。

【請求項 9】

行及び列のラインに沿って作動可能に接続された画素素子の二次元アレイ、を備える画像アレイから、データを読み取るように配列されたことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。 20

【請求項 10】

単一シリコンチップ上に製造された

ことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。

【請求項 11】

CMOS技術を使用して製造された

ことを特徴とする前記請求項のいずれか1項に記載の読み取り回路。

【請求項 12】

前記請求項のいずれか1項に記載の読み取り回路を有する赤外線検知器。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明はランダムアクセス復号器に関するものであり、特に画像アレイ読み取り回路において使用するためのランダムアクセス復号器に関するものである。

【背景技術】

【0002】

可視又は赤外線画像検出器のような多くのデバイスでは、検出器画素の二次元アレイから情報を読み取らなければならない。これは、二次元アレイの個々の画素から共通バス線へデータを伝送するための一連のスイッチを使用することにより遂行することができる。赤外線画像アレイで使用される画素素子の二次元アレイは普通、単一シリコン読み取りチップ上に行及び列読み取り回路と共に組み込まれる。各画素素子はまた、増幅器、ノイズフィルター等のような付加的な電子部品を含むこともできる。そのようなチップは典型的に、相補形金属酸化膜半導体(CMOS)技術を用いて製造される。 40

【0003】

画像検出器で一般的に使われる、行及び/又は列読み取り回路の一つの形式は、シフトレジスタである。シフトレジスタは典型的に、一連のフリップフロップ形式のシフトレジスタ素子から構成される。論理「1」が第一のシフトレジスタ素子に書き込まれると、次に各シフトレジスタ素子が、一連のクロックパルスにより順次イネーブルとなる。

【0004】

第一行目の最初の画素から第一行目の最後の画素までのデータを抽出し、次に後に続く各行においてこの処理を繰り返すことにより、行及び列シフトレジスタを内蔵する二次元アレイが読み取られる。このように、アレイ全体は、各ピクセルを通じて順番にラスターすることにより、連続的に読み取られる。シフトレジスタは連続的に作用するだけであるため、二次元アレイ内の画素に任意にアクセスすることができない。アレイ内の特定の部分又は「ウィンドウ」のみからのデータが関心のあるものである時、アレイ内のいずれの画素からも任意にデータを読み取ることができないことは不都合であり、特に大規模なアレイでは不都合である。

【0005】

行及び列読み取り回路の他の形式は復号器である。復号器は典型的に、一意の復号器回路素子を複数含み、かつ、これら復号器素子のどれもが要求どおりにアクセスされることができる。それゆえ復号器は、シフトレジスタと異なり、二次元アレイ内の如何なる画素への任意のアクセスも全く可能にする。

【0006】

既知の復号器の短所は、一意の復号器素子を複数設計する必要があることである。このような設計作業は時間がかかり、かつまた、非二進数であるアレイの大きさを使用する時には複雑なものとなる。また、各復号器素子において個別の設計を作成する必要があることは、読み取り回路を製造するコスト及び複雑さを増すことになる。例えば、一意の行及び列復号器回路素子を必要とすることは、既知のCMOS製造技術を使って作成できるアレイの大きさの最大値を制限する。

【0007】

赤外線検知器の応用例で使用される多重化技術のより詳細な検討については、ワシントン州ベーリングハムのSPIE光工学出版の、W.D.Rogatto著、電気光学部品 赤外線及び電気光学ハンドブック第3巻の第5章を見られたい。

【0008】

本発明の第一の側面によれば、復号器は、各々が固有の電子アドレス及びバイナリデータ出力を有する複数の復号器回路素子と、入力信号を復号器回路素子の各々に与えるための手段とを含み、各復号器回路素子の固有の電子アドレスが与えられた入力信号と一致する時にのみ、その復号器回路素子が自己のバイナリデータ出力上にデータを出力するようになった復号器であって、複数の復号器回路素子の各々の固有の電子アドレスが電気的に各復号器回路素子内に書き込まれることを特徴とする。

【0009】

各復号器回路素子を同じ配置で電気的に接続される等価な電気コンポーネントから構成することは、利点がある。言い換えれば、復号器回路素子とは、それらは全て同様に機能するようにする。

【0010】

二又はそれ以上の復号器回路素子を物理的に同一の回路設計から形成することが、好都合である。あるいは、全ての復号器回路素子を物理的に同一の回路設計から形成する。

【0011】

下記に述べるように、物理的に同一の復号器回路素子から成る復号器を有することは、復号器回路を設計することの複雑さを軽減し、かつまた、そのようなデバイスを製造する時に有利であることがわかる。

【0012】

更なる実施形態では、各復号器回路素子は加算器コンポーネントを含み、各復号器回路素子に対し固有の電気アドレスが電子的に書き込まれるように、各復号器回路素子の加算器コンポーネントは直列に接続される。

【0013】

加算器コンポーネントは、「+1」加算器、又は同様な機能を実行する何らかのデバイスとすることができます。加算器はまた、負の数(例えば「-1」)を加えることができるものでもよく、言い換えれば、減算形式の機能をも提供するようにすることもできる。

10

20

30

40

50

## 【0014】

各復号器回路素子は比較器コンポーネントを含み、各復号器回路素子の比較器コンポーネントは、個々の復号器回路の固有の電気アドレスが与えられた入力信号と一致するか否かを判定するようにすることが好都合である。

## 【0015】

本発明の第二の側面によれば、読み取り回路は、画素素子の一次元アレイと、復号器回路素子が該一次元アレイの各画素に接続された本発明の第一の側面による復号器とを含み、各画素素子に関連するデータは、その一次元アレイから如何なる順にでも読み取られることができ、かつ一又はそれ以上の出力信号バス上に出力されることができる。

## 【0016】

本発明の第三の側面によれば、読み取り回路は、行及び列の線に沿って作動的に接続された画素素子の二次元アレイを有しており、行及び列の線の各々に接続された行及び列復号器は、本発明の第一の側面による復号器を含み、各画素素子に関連するデータはそのアレイから如何なる順にでも読み取られることができ、かつ一又はそれ以上の出力信号バス上に出力されることができる。

## 【0017】

有利なことに、読み取り回路は、CMOS技術を使って都合よく単一シリコンチップ上で作られる。

## 【0018】

本発明の第四の側面によれば、赤外線検知器は、本発明の第二又は第三の側面による読み取り回路を含むことができる。

## 【0019】

(発明の詳細な説明)

以下、後の図面を参照して、ただ単に例として、本発明を説明することとする。

## 【0020】

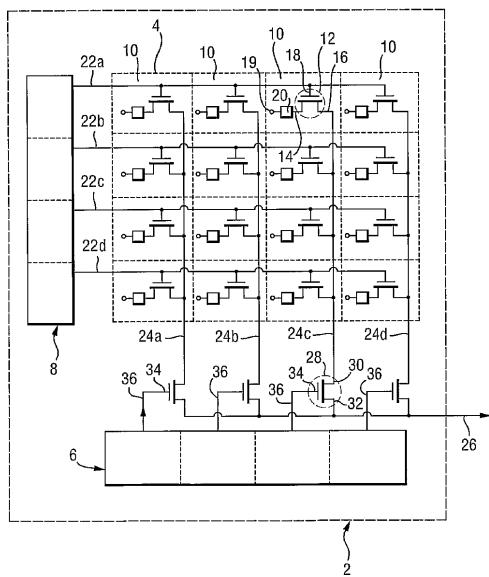

図1を参照すると、読み取り集積回路2は、画素素子10のアレイ4、列回路6、及び行回路8を含む。

## 【0021】

各画素素子10は、入力接続14、出力接続16、及びゲート接続18を有する画素MOSFETスイッチ12を含む。インジウムバンプのような相互接続19は、外部検知器のアレイ(示されていない)の画素が、さらに別の回路20を介して入力接続14に接続されることを可能にする。出力接続16は列バス線24に接続され、かつゲート接続18は行バス線22に接続される。各行バス線22は、行回路8の出力に接続される。

## 【0022】

当業者であれば、別の回路20が複数の異なる素子を含むことができることを認識するであろう。例えば、增幅器及び焦点面処理回路素子である。別の回路の実際の中身は、個別のアプリケーションによって異なるであろうが、それは本発明にとって重要ではない。

## 【0023】

各縦バス線24は、列MOSFETスイッチ28の入力接続30に接続される。各列MOSFETスイッチ28の出力接続32は出力バス線26に接続され、各ゲート接続34は列回路6からの出力36に接続される。

## 【0024】

作動において、画素の適切な行のゲート接続に電圧を与え、それと同時にまた適切な列スイッチのゲート接続に電圧を与えることにより、アレイ4上の画素10に存在するデータを出力バス線26上に出力することができる。それゆえ、画素に関連するデータのアクセスの容易さは、列回路6及び行回路8の特性によって定められる。

## 【0025】

図1を参照して説明する読み取り回路は一本の出力バス線36を含み、それゆえ、完全に直列なデータ出力を提供する、ということに注目すべきである。ある一定の画素からのデータが実際には異なるデータ出力バスに送られる可能性もあり、かつそれにより、一次並

10

20

30

40

50

列データ出力を提供する可能性もあるということを、当業者であれば認識するであろう。

【0026】

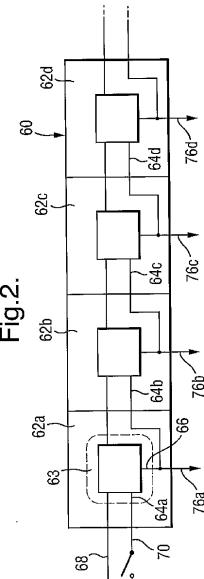

図2を参照すると、典型的な従来技術のシフトレジスタ60が示されている。

【0027】

シフトレジスタ60は、複数のシフトレジスタセル62a、b、c、d等を含む。各シフトレジスタセル62は、入力接続64及び出力接続66を有するD型ラッチ回路63を含む。第一のシフトレジスタセル62aの入力接続64は、シフトレジスタリセット線70に接続される。次に続くシフトレジスタセル62b、c、dの入力接続は、直前のシフトレジスタセルの出力接続に接続される。クロック線68はまた、シフトレジスタセル62の各々に、周期的なクロック信号を供給する。

10

【0028】

作動に際しては、リセット信号は、リセット線70を介して、第一のシフトレジスタセル62aの入力接続64aに与えられる。次にD型ラッチ回路は、1クロック周期の間、出力線76a上に論理「1」の出力を出す。そのクロック周期の最後に、論理「1」が第二のシフトレジスタセル62bの入力上に存在する(すなわち、第一のシフトレジスタセルの出力線76aの論理「1」)、そしてそれにより、次に続くクロック周期の間、論理「1」が出力76b上に現れ、それと同時に出力線76aは論理「0」の出力に戻る。このように、論理「1」は下げることができ、それによりシフトレジスタは順次イネーブル信号を提供する。

【0029】

図2を参照して説明するシフトレジスタの形式は、図1を参照して説明する集積回路2の中の行回路及び/又は列回路として使用することができる。シフトレジスタは集積回路として容易に実装されることができ、各シフトレジスタセルは、連鎖中の自己のいずれか一方のシフトレジスタセル及びクロック信号との单一接続を必要とするだけである。しかしながら、シフトレジスタは順次イネーブル方式で動作できるだけであるので、画像データを抽出するために、アレイ全体をラスター的に読み取らなければならない。それゆえシフトレジスタは、アレイのある決まった部分又は「ウィンドウ」のみを読む必要のあるアプリケーションには適していない。

20

【0030】

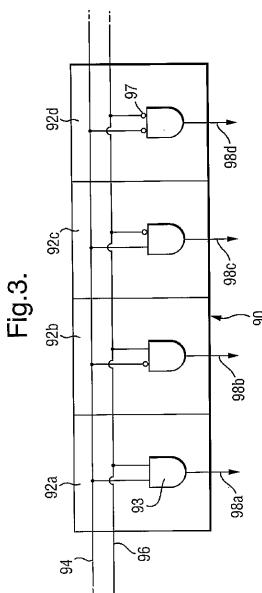

図3を参照すると、典型的な従来技術のランダムアクセス復号器90が示されている。

【0031】

復号器90は、各々がデジタルバス線94、96に接続される比較器93を有する、複数の単位セル92a、b、c、dを含む。復号器の各単位セル92は、「NOT」ゲート素子(例えば97)を含むことにより、一意にアドレス指定可能となる。適当なデジタル符号をバス線94、96に与えることにより、一つの単位セル(例えば92b)が、それに接続されている比較器の出力線(98b)上に論理「1」を出力することになり、その他の全ての比較器の出力線(98a、c、d)はローレベルに維持される。

30

【0032】

図3で与えられる例では、4つの単位セルを一意に識別するために、たった2本のバス線が要求されるだけである。しかしながら、単位セルの数が増えるにつれて、バス線の数もまた増えるであろう。例えば、もし256個の比較器セルが固有のアドレスを持つようなことがあれば、8本のバス線が要求されることになり、1024の固有のアドレスを提供するためには10本のバス線が必要とされることになる等である。

40

【0033】

図3を参照して説明するランダムアクセス多重化装置の形式は、図1を参照して説明した集積回路2の中の行及び/又は列回路として使用することができる。そのとき、アレイ上のいずれの画素に関連するデータにも全くランダムアクセスすることが可能であり、これにより、ディスプレイ上のウィンドウ又は個々の画素を、ディスプレイの他の部分よりも早い速度で更新することが可能となる。

【0034】

図3を参照して説明する従来技術のランダムアクセス復号器回路90の短所は、復号器の

50

各セルが一意の回路であることを必要とすることである。それゆえ、復号器の各セルについて個別仕様の回路設計が要求され、回路設計には時間がかかり、そのような設計は、非二進数のアレイサイズの場合に幾分複雑になることがある。

【0035】

容認できる性能を達成するためには、読み取り回路に関連する全ての回路を单一シリコンチップ上に収めることができが、一般的に望まれる。しかしながら、CMOS回路を複写するのに使用されるフォトマスクは典型的にサイズが制限され、それゆえ、製造されることのできる最大チップサイズもまた、それに応じて制限される。CMOS製造技術に関連するサイズ制限をある程度まで克服する様々な技術が当業者には知られており、かつそれにより、フォトマスクの大きさよりも大きい回路を製造することが可能である。

10

【0036】

製造されることのできるCMOS回路のサイズを増やすために、この分野で使用される技術の一例には、レチクル・ステッチがある。複数の異なる回路設計が、一又はそれ以上のフォトマスクの幾つかの異なる領域上に実装される。次いで、様々なマスク上に収められる様々な異なる回路設計の組み合わせにより、回路が单一シリコンチップ上で形成される。

【0037】

CMOS回路のサイズは、レチクル・ステッチ技術を使って増大することができるが、一つのフォトマスク上に搭載することのできる異なる回路設計の数には限りがある。様々な形式のCMOS製造装置を用いて使用することのできる異なるマスクの数もまた、制限される可能性があり、そしてそれはまた同様に、回路サイズの最大値、及び得られうる全体の複雑さも制限する。それゆえ、複雑な回路設計が実装される場合には、複数の回路設計を含む複数のマスクが要求されることになるので、各復号器セル回路について独自性が必要であることは、レチクル・ステッチCMOS技術を使ってデバイスを製造する時に不利になる。

20

【0038】

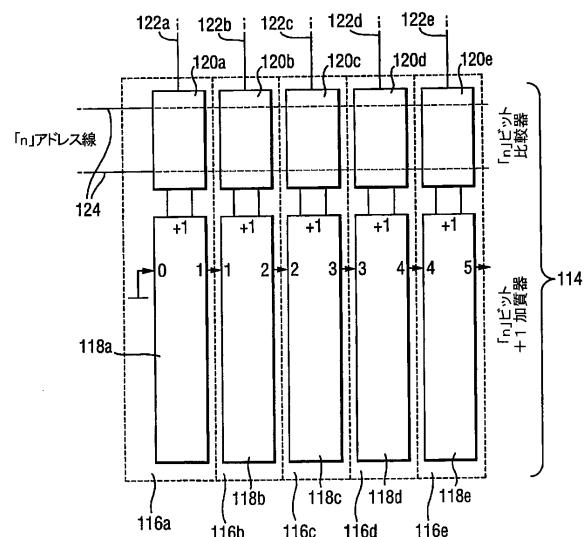

図4を参照すると、本発明によるランダムアクセス復号器114が示されている。ランダムアクセス復号器114は複数の復号器セル116を含み、復号器セル116の各々は、「+1」加算器118及び比較器120を含む。

【0039】

本発明による復号器114は、第一の「+1」加算器118aに「0」を与えることにより初期化される。次に第一加算器118aは、「0」入力に「1」を加え、第二の「+1」加算器118bにその結果である「1」を出力する。次に第二の「+1」加算器は、第一「+1」加算器の出力に「1」を加え、第三の「+1」加算器118cに「2」を出力する。このように、デバイスに電圧がかけられた時、各復号器セルは、「+1」加算器118に固有のデジタル数字を書き込まれる。

30

【0040】

デジタルアドレスバス124に与えられたどのデータも、各比較器120により、各「+1」加算器118に格納された固有のデジタル数字と比較される。デジタルアドレスバスに与えられたデジタル数字が格納されたデジタル数字と一致する場合には、論理「1」のイネーブル信号が、それに接続されている比較器出力線122上に出力され、その他の全ての比較器出力線はロー(low)レベルに維持される。

40

【0041】

復号器素子を作動させるために要求されたデジタルアドレスデータは、外部の(例えばオフチップ)デジタル番号作成手段から、「n」電気接続を介して、デジタルアドレスバス124の「n」アドレス線に与えることができる。あるいは、読み取り回路チップは、外部のデジタル番号作成手段から一つの電気接続を介して直列デジタルコードを受け取り、その信号を「n」アドレス線に並列に与えられる並列デジタルデータに変換する、直列-並列変換機を附加的に含むことができる。

【0042】

本発明による復号器は、図1を参照して説明した集積回路2の中の行及び/又は列回路として使用することができる。その場合には、アレイ上の任意の画素に関連するデータへの

50

完全なランダムアクセスが可能となり、ディスプレイのウィンドウ又は個々の画素が、ディスプレイの他の部分よりも早い速度で更新されることを可能にする。言い換えると、本発明による行及び列復号器を有する二次元アレイ内の画素は、どんな任意の順番にでもアクセスすることができる。

【0043】

従来技術の復号器とは異なり、本発明の各復号器セル114の設計は同一のものとすることができる。それゆえ、多重素子復号器を作り上げるために、一つの回路設計で複数回複製することができる。これは、復号器を設計するのに必要な時間及び労力を減らし、かつまた、非二進数の区切り点(ブレークポイント)を持つ復号器が要求される時、回路設計をより容易なものにする。

10

【0044】

各復号器素子の同一回路設計はまた、CMOSレチカル・ステッチ技術を使ってシリコン読み取りチップを製造する時にも、有利であることがわかる。複数の復号器素子を含む復号器回路設計は、フォトマスクの一つの領域上に形成され、次いで複数回複製して、單一シリコンチップ上に広い面積の復号器回路を作り上げることができる。このように、一つの読み取りチップを、従来技術の復号器回路設計を用いて可能なものより広い領域、及び多くの行及び/又は列を有するように、製造することができる。

【0045】

本発明による復号器はまた、従来技術のシフトレジスタ及び従来技術の復号器よりも消費電力が少ないという利点も有する。従来技術のシフトレジスタは、クロック信号の継続的な付与のため、かなりの電力を求めるものであり、そのうえ、従来技術の復号器素子を一意にアドレス指定可能にするために必要な電気回路は、本発明による復号器素子よりも多くの電力を消費する。低電力での動作は、特に冷却IR検知器システムにおいて有利であり、電力損失の減少により、読み取りチップに関連する不要な発熱効果が減少する。

20

【0046】

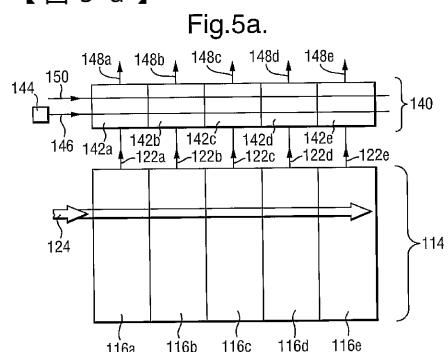

図5を参照すると、本発明による復号器を、その任意の長さの点でシフトレジスタを読み込むのにどのように使用できるかを示している。前の図面を参照して説明したコンポーネントと同じコンポーネントは、同じ参照番号が割り当てられている。

【0047】

図5aは、図4を参照して説明した復号器114及びシフトレジスタ140を示す。シフトレジスタ140は、各々が二値出力線148を有する多数のシフトレジスタセル142を含む。各シフトレジスタセル142はまた、復号器114の出力線122からリセット信号を受け取る能力もある。クロック144からのクロック信号はクロック線146を介して各シフトレジスタセル142に供給され、かつ二値制御信号は制御線150を伝わって供給される。

30

【0048】

作動に際しては、制御線150に与えられた二値制御信号は、シフトレジスタ140が順次イネーブル方式、又はデータ受信方式、のいずれで動作するのかを判定する。データ受信方式では、シフトレジスタ素子142が、復号器114の通信出力線122上にある如何なる信号も受け入れるように構成される。これにより、シフトレジスタ素子がクロックパルスの継続時間中にその二値出力線148上に論理「1」を出力するようにする復号器により、シフトレジスタ素子がリセットされることが可能となる。順次イネーブル方式では、シフトレジスタが、その長さにわたりイネーブル信号をクロック的に送る。この構成は、通常のシフトレジスタ動作(すなわち、図2を参照して説明した形式の順次イネーブル方式)の初期化、及びシフトレジスタに沿った任意の点での停止を可能にする。

40

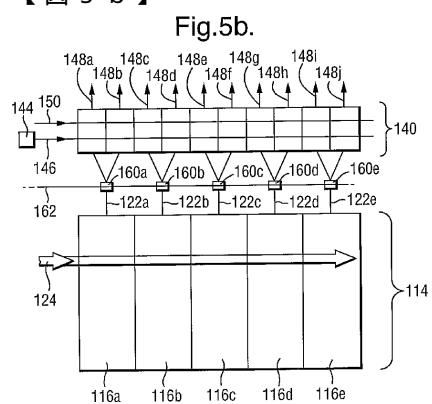

【0049】

図5bは、図5aを参照して説明した構成の代りとなる構成を示している。復号器114の各出力線122は、双方向スイッチ160を介して、二つのシフトレジスタ素子の一方に送られる。スイッチ制御線162は、どのシフトレジスタ素子が出力線122からデータを受け取るかを決定する二値データ信号を、各双方向スイッチ160に供給する。このように、デジタルアドレスバス124上に適切なデータを載せることにより特定の復号器素子を作動させ、かつ

50

スイッチ制御線162に適当なデータを与えることにより双方向スイッチ160が望ましい位置にあることを確実にすることによって、どのシフトレジスタ素子もリセットされることができる。

#### 【0050】

図5bの構成は、所定の数のシフトレジスタ素子に対し、少数の復号器素子を必要とするものである。これは、所定の数のシフトレジスタ素子をアドレス指定するのに必要な復号器素子の数を減らし、それゆえ要求される電子回路のサイズを小さくする。また、スイッチの補助線を復号器とシフトレジスタとの間に介在させることができ、それにより必要な復号器素子の数がさらに減ることが、当業者であればわかるであろう。しかしながら、仲介するスイッチの数の増加が回路設計の複雑さを増大させ、これにより、複数の繰り返された回路素子から回路を製造することができるという上述の利益が減少するであろうこともまた、当業者であれば認識するであろう。

10

#### 【0051】

それゆえ、読み取り回路が、本発明の復号器のみを使用する行及び列回路を含むことができ、或いは、シフトレジスタのような付加的なコンポーネントと組み合わされた復号器を含むものとすることができるということが分かるであろう。本発明の復号器を搭載する代替の読み取り回路の構成もまた、当業者には明白であろう。

#### 【0052】

当業者であれば、本発明による復号器の幅広い応用もまた認識するであろう。このような復号器は、画像アレイにおける読み取り回路を製造する時に使用される場合があるというだけでなく、データ記憶画素へのデータの読み取り及び/又は書き込み(例えば、ランダムアクセスメモリをアドレス指定すること)に使用される場合もある。ディスプレイ内の画素をアドレス指定するために、そのような復号器を使用することもまた可能である。実際に、このような復号器は、並列データの蓄積を直列に出力又は入力させが必要な任意のアプリケーションにおいて使用することもできる。

20

#### 【0053】

##### 例

図6を参照すると、CMOSレチクル・ステッチ技術を使用して製造された、シリコン読み取りチップの一部の顕微鏡写真が示されている。集積回路は、本発明による行及び列回路復号器に組み合わせた $1024 \times 768$ 画素のアレイを含む。

30

#### 【0054】

行及び列復号器素子は同一の回路設計に製造され、かつ図3を参照して説明した従来技術の復号器に匹敵する速さで、ランダムにアクセスすることができる。チップは、冷却赤外線検知器としての使用のためにアンチモン化インジウム(InSb)検知器アレイと併合されるように設計される。

#### 【図面の簡単な説明】

#### 【0055】

【図1】行及び列読み取り回路を内蔵する $4 \times 4$ の画像アレイを示す。

【図2】従来技術のシフトレジスタを示す。

【図3】従来技術の復号器の説明図である。

40

【図4】本発明による復号器を示す。

【図5】本発明の復号器及びシフトレジスタを含む読み取り回路を示す。

【図6】本発明による復号器を含むシリコン読み取りチップの一部の写真である。

【 図 1 】

Fig. 1.

【 図 2 】

【図3】

၃၇

【 図 4 】

Fig.4.

【図5a】

【図5b】

【図6】

Fig.6.

---

フロントページの続き

(72)発明者 ホリアー コリン ジョン

イギリス ウスター・シャー ダブリュアール 14 3ピーエス モルヴァーン セント アンド

リューズ ロード ケエックス ビルディング ルーム 04 キネティック モルヴァーン

審査官 小田 浩

(58)調査した分野(Int.Cl. , DB名)

H04N 5/335

H01L 27/14