## (12)发明专利

(10)授权公告号 CN 107667410 B

(45)授权公告日 2019.12.10

(21)申请号 201680028700.9

银英·肖李 刘学峰

(22)申请日 2016.05.21

(74)专利代理机构 北京律盟知识产权代理有限公司 11287

(65)同一申请的已公布的文献号

申请公布号 CN 107667410 A

代理人 张世俊

(43)申请公布日 2018.02.06

(51)Int.Cl.

(30)优先权数据

62/164,975 2015.05.21 US

H01J 1/304(2006.01)

15/160,505 2016.05.20 US

H01J 1/308(2006.01)

(85)PCT国际申请进入国家阶段日

H01J 1/34(2006.01)

2017.11.17

H01L 27/148(2006.01)

(86)PCT国际申请的申请数据

H01L 31/105(2006.01)

PCT/US2016/033669 2016.05.21

H01L 31/107(2006.01)

(87)PCT国际申请的公布数据

(56)对比文件

W02016/187603 EN 2016.11.24

US 6201257 B1,2001.03.13,

(73)专利权人 科磊股份有限公司

US 2014291493 A1,2014.10.02,

地址 美国加利福尼亚州

US 2014034816 A1,2014.02.06,

(72)发明人 勇-霍·庄 约翰·费尔登

US 5363021 A,1994.11.08,

US 6220914 B1,2001.04.24,

审查员 丁钰丰

权利要求书3页 说明书16页 附图11页

## (54)发明名称

包括在具有硼层的硅衬底上的场发射极阵列的光阴极

## (57)摘要

一种光阴极利用一体地形成于硅衬底上的场发射极阵列FEA来增强光电子发射，且利用直接安置在所述FEA的输出表面上的薄硼层来阻止氧化。所述场发射极是通过具有安置成二维周期性图案的各种形状(例如，角锥体或经修圆晶须)的突出部形成，且可经配置而以反向偏置模式操作。任选栅极层经提供以控制发射电流。任选第二硼层形成于经照射(顶部)表面上，且任选抗反射材料层形成于所述第二硼层上。在相对的所述经照射表面与所述输出表面之间产生任选外部电位。通过特殊掺杂方案且通过施加外部电位而形成n型硅场发射极与p-i-n光电二极管膜的任选组合。所述光阴极形成传感器及检验系统的部分。

## 1. 一种光电阴极,其包含:

硅衬底,其具有相对的第一表面及第二表面且包括多个一体式场发射极突出部,每一所述场发射极突出部具有一体地形成于所述硅衬底上的固定部分且从所述第二表面延伸到尖端部分,及

大体上纯硼层,其气密地安置在至少每一所述场发射极突出部的所述尖端部分上,

其中所述光电阴极不包括低功函数材料,借此通过所述尖端部分离开所述光电阴极的电子仅通过所述大体上纯硼层;及

其中所述硅衬底进一步包含掺杂剂,所述掺杂剂经配置使得在所述光电阴极的操作期间,每一所述场发射极突出部作为场发射极以反向偏置模式操作。

2. 根据权利要求1所述的光电阴极,其中所述多个场发射极突出部在所述第二表面上布置成二维周期性图案。

3. 根据权利要求1所述的光电阴极,其中所述大体上纯硼层具有处于大约1nm到5nm的范围内的厚度。

4. 根据权利要求1所述的光电阴极,其中每一所述场发射极突出部包含角锥体形结构。

5. 根据权利要求1所述的光电阴极,其中每一所述场发射极突出部包含圆锥体形结构及圆晶须形结构中的一者。

6. 根据权利要求1所述的光电阴极,其进一步包含至少一个栅极结构,所述至少一个栅极结构安置在所述第二表面上方且邻近于所述多个场发射极突出部中的至少一者的所述尖端部分定位并且与所述尖端部分间隔开。

7. 根据权利要求1所述的光电阴极,其进一步包含直接安置在所述硅衬底的所述第一表面上的第二大体上纯硼层。

8. 根据权利要求7所述的光电阴极,其进一步包含安置在所述第二大体上纯硼层上的抗反射层。

9. 根据权利要求1所述的光电阴极,其进一步包含经配置以跨越所述硅衬底施加外部电位差的导电结构。

10. 根据权利要求3所述的光电阴极,

其中所述第一表面完全安置在所述硅衬底的p掺杂区域上,且所述第二表面及所述多个场发射极突出部完全安置在所述硅衬底的n掺杂区域上,且

其中所述p掺杂区域及所述n掺杂区域经配置以形成p-i-n光电二极管,当跨越所述硅衬底施加至少100伏特的外部电位差时,所述p-i-n光电二极管在雪崩倍增条件下操作。

11. 根据权利要求1所述的光电阴极,其中所述硅衬底包括p型梯度扩散区域,所述p型梯度扩散区域从所述第一表面朝向所述第二表面延伸,使得所述p型梯度扩散区域在接近所述第一表面定位的所述硅衬底的部分中比在远离所述第一表面安置的所述硅衬底的部分中具有更高p型掺杂剂浓度。

12. 一种传感器,其用于响应于被引导到所述传感器的接收表面上的光子而产生电信号,所述传感器包含:

光电阴极,其邻近于所述接收表面而安置且经配置以响应于所述光子通过所述接收表面且进入所述光电阴极中而发射光电子,所述光电阴极包括:

硅衬底,其具有相对的第一表面及第二表面且包括多个一体式场发射极突出部,每一

所述场发射极突出部具有一体地形成于所述硅衬底上的固定部分且从所述第二表面延伸到尖端部分,及

大体上纯硼层,其气密地安置在至少每一所述场发射极突出部的所述尖端部分上;及其中所述硅衬底进一步包含经植入掺杂剂,所述经植入掺杂剂经配置使得在所述光电阴极的操作期间,每一所述场发射极突出部作为场发射极以反向偏置模式操作;

检测装置,其具有面对所述光电阴极的所述第二表面的检测表面,所述检测装置经配置以检测由所述光电阴极发射的所述光电子,且经配置以响应于所述所检测到的光电子而产生所述电信号;及

壳体,其可操作地连接于所述光电阴极与所述检测装置之间,使得所述检测装置的所述检测表面通过介入间隙区域与所述光电阴极分离,所述介入间隙区域在所述大体上纯硼层的暴露的外表面与所述检测装置的所述检测表面之间完全延伸。

13. 根据权利要求12所述的传感器,其中所述多个场发射极突出部在所述第二表面上布置成二维周期性图案。

14. 根据权利要求12所述的传感器,其中所述大体上纯硼层具有处于大约1nm到5nm的范围内的厚度。

15. 根据权利要求12所述的传感器,其中所述传感器包含图像增强器、电子轰击电荷耦合装置EBCCD及光电信增管中的一者。

16. 根据权利要求12所述的传感器,其中每一所述场发射极突出部包含圆锥体形结构及圆晶须形结构中的一者。

17. 根据权利要求12所述的传感器,其中每一所述场发射极突出部包含角锥体形结构。

18. 根据权利要求12所述的传感器,其进一步包含放置在与所述场发射极尖端大致相同高度处的至少一个栅极层。

19. 根据权利要求12所述的传感器,其进一步包含直接安置在所述硅衬底的所述第一表面上的第二大体上纯硼层。

20. 根据权利要求19所述的传感器,其进一步包含直接安置在所述第二大体上纯硼层上的抗反射层。

21. 根据权利要求20所述的传感器,其中所述传感器的所述接收表面包含抗反射材料的外表面。

22. 根据权利要求12所述的传感器,其中所述接收表面包含安置在窗的第一表面上的抗反射材料层,且所述硅衬底安置在所述窗的相对第二表面上。

23. 根据权利要求12所述的传感器,其中所述检测装置包含第二硅衬底且包括直接安置在所述第二硅衬底的所述检测表面上的硼层。

24. 一种检验系统,其包含:

照射源,其经配置以发射经引导光子;

传感器,其经配置以检测经重新引导光子;及

光学系统,其经配置以将所述经引导光子从所述照射源导引到样本,且将经重新引导光子从所述样本导引到所述传感器,

其中所述传感器包含:

光电阴极,其经配置以响应于所述经重新引导的光子而发射光电子,所述光电阴极包

括：

硅衬底，其具有相对的第一表面及第二表面且包括多个一体式场发射极突出部，每一所述场发射极突出部具有一体地形成于所述硅衬底上的固定部分且从所述第二表面延伸到尖端部分，及

大体上纯硼层，其气密地安置在至少每一所述场发射极突出部的所述尖端部分上且具有背对所述硅衬底的暴露的外表面；及

其中所述硅衬底进一步包含经植入掺杂剂，所述经植入掺杂剂经配置使得在所述光电阴极的操作期间，每一所述场发射极突出部作为场发射极以反向偏置模式操作；及

检测装置，其具有通过间隙与所述光电阴极分离的检测表面以使得所述间隙在所述大体上纯硼层的所述暴露的外表面与所述检测表面之间完全延伸，所述检测装置经配置以检测由所述光电阴极发射的所述光电子，且经配置以响应于所述所检测到的光电子而产生电信号。

25. 根据权利要求24所述的检验系统，其中所述传感器包含图像增强器、电子轰击电荷耦合装置EBCCD及光电倍增管中的一者。

## 包括在具有硼层的硅衬底上的场发射极阵列的光电阴极

### [0001] 优先权申请

[0002] 本申请案主张2015年5月21日提出申请的标题为“包括在具有硼层的硅衬底上的场发射极阵列的光电阴极 (PHOTOCATHODE INCLUDING FIELD EMITTER ARRAY ON A SILICON SUBSTRATE WITH BORON LAYER)”的美国临时专利申请案62/164,975的优先权,且所述美国临时专利申请案以引用的方式并入本文中。

### [0003] 相关申请案

[0004] 本申请案与标题为“光电倍增管、图像传感器以及使用PMT或图像传感器的检验系统 (Photomultiplier Tube, Image Sensor, and an Inspection System Using a PMT or Image Sensor)”且由庄 (Chuang) 等人在2014年3月5日提出申请的美国专利申请案14/198,175 (公开为2014/0291493) 有关,且与标题为“包括具有硼层的硅衬底的光电阴极 (Photocathode Including Silicon Substrate with Boron Layer)”且由庄 (Chuang) 等人在2013年7月22日提出申请的美国专利申请案13/947,975 (公开为2014/0034816) 有关。这两个申请案以引用的方式包括于本文中。

### 技术领域

[0005] 本发明一般来说涉及结合半导体晶片、光罩或光掩模检验系统一起使用的低光感测检测器(传感器),且更明确地说涉及在用于此类检验系统的所述传感器中利用的光电阴极。

### 背景技术

[0006] 光电阴极是通常用于光检测装置(例如光电倍增管、图像增强器及电子轰击CCD (EBCCD))中的带负电荷电极。光电阴极包含光敏化合物,当被光量子(光子)撞击时,由于光电效应所述光敏化合物响应于每一所吸收光子而产生一个(或多个)电子。现代光电阴极中所使用的光敏化合物通常包含碱金属,这是因为其低功函数允许电子从光电阴极容易地逸出以供由主机图像传感器装置的其它结构检测。例如GaAs及InGaAs的化合物半导体还用于制造光电阴极,尤其用于制造红外线敏感装置。过去已制造硅光电阴极,但硅光电阴极未发现有显著商业用途,这是因为尽管硅在俘获光时是高效的,但所产生电子中的极少电子能够从硅逸出,从而导致低总体效率。

[0007] 光电阴极一般来说划分为两个广泛群组:透射光电阴极及反射光电阴极。透射光电阴极通常形成于面对待测量的光源的窗的表面(例如,玻璃)上,且离开光电阴极的电子通过光电阴极的输出表面以供检测(即,电子移动远离光源)。反射性光电阴极通常形成于不透明金属电极基极上,其中光进入“经照射”表面且电子从同一“经照射”表面离开。尽管反射光电阴极简化了下文所论述的光电阴极厚度与敏感性之间的一些权衡,但其不适合用于例如图像增强器及EBCCD装置的成像装置中(尽管其可适合用于一些光电倍增管配置中)。因此,在下文论述中,术语“光电阴极”仅是指透射光电阴极,除非另有规定。

[0008] 光电阴极通常形成或安装在适合主机传感器的壳体(例如,真空管)上,且所述传

感器壳体经定位使得经照射表面面对目标光源(即,使得光电阴极定位于光源与主机传感器的电子-测量结构之间)。当光子被光电阴极吸收时,平均约50%的所产生电子将朝向光电阴极的经照射侧行进(即,面对光源、光子穿过其进入光电阴极的侧)。另外50%的光电子将行进到光电阴极的输出表面,且如果所述光电子具有充足能量,那么其将被朝向传感器的电子-测量结构发射。当从光电阴极的输出表面发射电子时,其通常将通过主机传感器内的电场朝向阳极加速,从而产生指示一或多个光子的俘获的对应可测量电压或电流。

[0009] 光电倍增管是包括光电阴极、阳极及一系列倍增极(电极)的真空光电管,其中每一倍增极均比其前一者处于相继更正电位,使得阳极处于高于上一倍增极的电位的正电位。从光电阴极发射的光电子通过光电阴极-倍增极电场加速且通常将撞击倍增极,此致使发射多个次级电子,所述次级电子通过后续倍增极-倍增极电场加速。几乎所有这些次级电子均将撞击另一倍增极且产生更多电子。最终,电子将通常在通过多个倍增极的多个放大级之后到达阳极。因此,每当光子被吸收且沿正确方向发射光电子时,光电倍增管均产生电流脉冲(即,电荷)。由于所产生电荷等于许多电子上的电荷,因此当增益足够高时可产生高于电子器件的噪声水平的电荷。因此,光电倍增管可为对电磁光谱的紫外线、可见及近红外线范围内的光的极其敏感的检测器。这些检测器将由入射光产生的电流在多个倍增极级中倍增多达一亿倍,从而使得(举例来说)当光的入射通量极低时能够检测个别光子。

[0010] 图像增强器是另一类型的真空管传感器装置,其利用磷光体来增加光学系统中的所检测到光的强度以便促进(举例来说)低光过程的视觉成像或用于将例如近红外线或短波红外线的非可见光源转换成可见光源。在典型图像增强器中,从光电阴极发射的光电子朝向涂覆有磷光体的透明阳极加速,使得光电子以高能量(通常约1keV到约20keV)撞击所述磷光体,从而致使所述磷光体产生许多光子。在一些图像增强器中,微通道板放置在光电阴极与磷光体之间以便从每一光电子产生多个次级电子。甚至在不具有微通道板的情况下,还可针对每一所吸收光子而在图像增强器的输出处产生多个光子。经发射光子通过光学器件(例如光纤束或透镜)经引导到图像传感器。由于每一所吸收光子可产生许多输出光子,因此可检测并测量极低光水平,在一些情况下甚至可能是单光子。

[0011] EBCCD是以类似于图像增强器的方式操作的另一传感器。替代作为输出的磷光体屏幕,使用例如CCD的图像传感器来检测从光电阴极发射且通过电场加速的电子。在EBCCD中,通常使用约2kV或更多的电位差在光电阴极与CCD之间产生电场,借此由光电阴极发射的光电子被加速且以高能量撞击CCD,从而在CCD内侧产生多个电子,所述多个电子接着被俘获。由于针对经检测的每一光子产生多个电子,因此CCD的读出及暗噪声不如原本对光子的直接检测重要。如与图像增强器相比,EBCCD避免用以将光从磷光体转移到图像传感器所需的光学器件的成本,且还避免由那些光学器件导致的图像分辨率的降级。

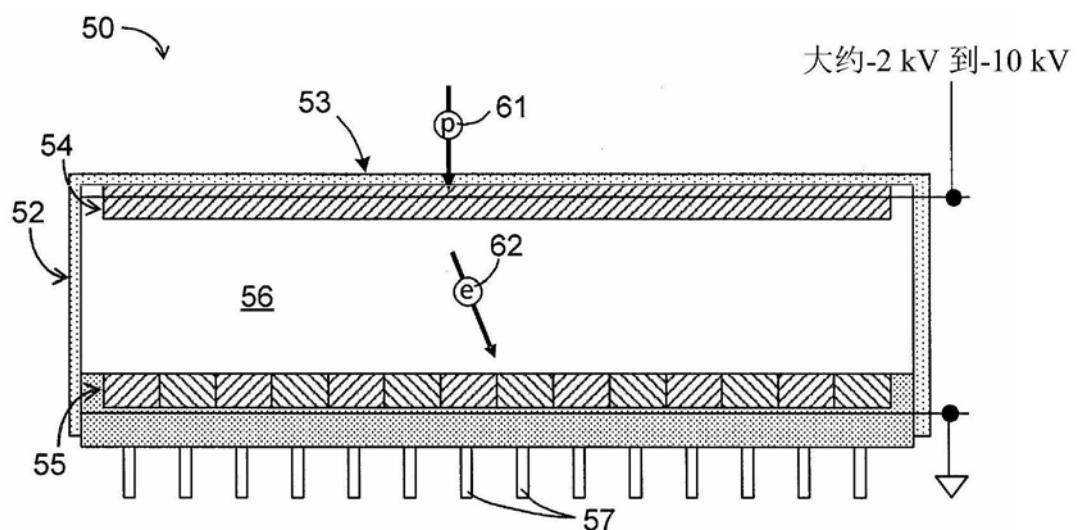

[0012] 图12展示常规EBCCD 50,EBCCD 50包含:壳体52,其包括窗53;光电阴极54,其安置在窗53的内侧表面上;及电荷耦合装置(CCD)55,其安置在壳体52的下部端处,使得光电阴极54通过真空间隙56与CCD 55分离。通过将相对于CCD 55的电压为负的电压施加到光电阴极54而在所述光电阴极与所述CCD之间产生电场。传入光子61穿过窗53进入且被光电阴极54吸收,从而致使产生光电子。当光电子62具有充足能量以穿过光电阴极54的输出侧逸出(即,在图中向下)时,其进入间隙区域56。由于CCD55相对于光电阴极54处于通常2kV或更多的正电位,因此光电子62被朝向CCD 55加速,使得其实现大于约2keV的能量,借此光电子通

常将在CCD 55内侧产生多个电子。在CCD 55内侧产生的电子接着经发射(例如,通过引脚57)到处理系统(未展示),所述处理系统经配置以产生相关联图像或与所检测到的光电子相关联的其它资料。

[0013] 现有技术光电阴极需要在与吸收光子及发射光电子相关联的冲突要求之间作出艰难权衡。良好光电阴极需要具有在所关注波长处吸收光子的高概率,及从所述所吸收光子产生一个(或多个)光电子的高概率。良好光电阴极还需要具有由所吸收光子产生的任何光电子从光电阴极逸出的高概率。较厚光电阴极增加入射光子将被吸收的概率,但还增加所得经发射光电子在其逸出之前将重新组合(即,损失)的概率。更具体来说,重新组合通常发生在形成光电阴极的材料中的缺陷或杂质处,因此光电子必须穿过光电阴极材料行进的距离越长,其将遇到缺陷或杂质且经重新组合的概率越大。材料必须具有低功函数,这是因为仅具有接近于或大于所述功函数的能量的光电子具有合理逸出概率。

[0014] 通常针对相对窄范围的波长而使光电阴极最佳化。举例来说,UV波长在半导体工业中对于检测半导体晶片上的小粒子及缺陷尤其有用,这是因为一般来说从小粒子散射的光的量(除其它因素外)取决于粒子或缺陷大小对波长的比率。大部分光电阴极材料强烈吸收UV光。针对UV波长最佳化的现有技术光电阴极通常需要为薄的,这是因为将接近于经照射表面而吸收UV光子。如果光电阴极并非薄的,那么光电子可具有从光电阴极的输出表面逸出的低概率。通常仅在光电阴极的面对磷光体或图像检测器的侧上逸出的光电子将产生输出信号。针对UV波长最佳化的此薄光电阴极通常将在可见及红外线波长处具有不良敏感性,这是因为在较长波长处的显著部分入射光子将在不吸收的情况下通过光电阴极。

[0015] 现有技术光电阴极的另一限制是经发射光电子的能量随所吸收光的波长变化且在UV光子被吸收时可为数eV。由于光电子经发射的方向是随机的,因此此电子能量导致沿水平方向的信号的散布。此外,所述散布将随所吸收光子的波长而变化,对于较短波长所述散布是较大的。在厚光电阴极中,光电子通常将在被发射之前经历多次碰撞且将更可能具有接近于通过光电阴极的温度确定的能量的能量(即,电子更可能经热化)。然而,当电子在光电阴极内经历多次碰撞时,其可能由于现有技术光电阴极材料的表面内及/或上的高缺陷水平而重新组合且损失。因此,将以大体上降低的敏感性为代价而达到减少的能量散布(大部分入射光子将不再产生信号)。

[0016] 单晶体(单晶)硅将出现以克服刚刚描述的许多缺点。硅吸收比约 $1.1\mu\text{m}$ 短的所有波长。硅晶体可以极高纯度及极少晶体缺陷生长。高质量单晶硅中的电子的重新组合寿命可为许多微秒,在最佳质量材料中甚至是数百微秒。此类较长重新组合寿命允许在远离表面许多微米处产生的电子能够以低重新组合概率迁移到表面。

[0017] 然而,尽管其有许多优点,但用于商业用途的硅基光电阴极的开发被两个主要缺点阻止。

[0018] 硅的一个缺点是硅具有相对大的功函数(大约4.8eV,艾伦(Allan)及戈贝利(Gobelli),“原子级清洁硅的功函数、光电阈值及表面状态(Work Function, Photoelectric Threshold, and Surface States of Atomically Clean Silicon)”,物理学评论(Physical Review),第127卷第1期,1962年,第150页到158页),所述相对大的功函数对通过光子的吸收产生的光电子的发射不利。材料的功函数是处于费米(Fermi)能级的电子与处于真空能级的电子(即,已从材料逸出的电子)之间的能量差。硅的相对大能带间

隙意指经热化电子无法从硅逸出。甚至接近于硅的表面吸收的UV光子还不形成较多光电流,这是因为光电子不具有用以逸出的足够能量。举例来说,6.5eV的光子能量形成具有约3eV的能量的光电子(这是因为在此波长处直接吸收比间接吸收更可能发生)。具有约3eV的能量的光电子由于硅功函数而不能够从硅逸出。

[0019] 关于硅用作光电阴极材料的第二更严重问题是硅极易在其表面上形成自然氧化物。甚至在真空中,自然氧化物也将最终形成,因为存在于真空中的少量氧与水将与硅的表面反应。硅与二氧化硅之间的界面具有缺陷(由悬空键所致),其中电子重新组合的概率是极高的。此外,二氧化硅的能带间隙是大的(约8eV),从而形成高于电子逸出必须克服的功函数的额外势垒,即使氧化物极薄(极平滑硅表面上的自然氧化物通常为约2nm厚)也是如此。可通过移除自然氧化物且在高温(例如大约900°C到1000°C)下生长热氧化物来减小硅与氧化物界面处的缺陷密度。当生长到约1.5nm到2nm的厚度时,此层可为稳定的。然而,甚至良好质量热氧化物在其与硅的界面处也具有显著缺陷密度(通常10<sup>9</sup>到10<sup>11</sup>个缺陷/cm<sup>2</sup>),且即使可克服功函数,氧化物的高能带间隙与接近于2nm的最小厚度组合仍对电子逸出提供显著势垒。薄氮化硅层可用于阻止在硅上生长自然氧化物层,但缺陷的密度在硅与氮化硅界面处比在硅与二氧化硅界面处高,且氮化硅的能带间隙(约5eV)对于阻止大部分电子从表面逸出是足够大的。出于这些原因,从未发现硅作为光电阴极的显著商业用途。

[0020] 因此需要一种克服现有技术的限制中的一些或所有限制的光电阴极。

## 发明内容

[0021] 本发明针对于一种光电阴极结构,所述光电阴极结构包括:多个场发射极突出部,其一体地形成(经图案化)于单晶或多晶硅衬底的输出表面上;及大体上纯硼(第一)层,其气密地形成于至少所述场发射极突出部的尖端(自由端)部分上。将一体式场发射极突出部引入到所述输出表面上可通过利用当所述突出部充当场发射极时产生的场增强而规避硅衬底的相对高功函数,此在所述衬底经受所施加电场时发生,所述所施加电场是足够高(强)的以减小硅-真空界面上的电位势垒,使得光电子可在所述尖端部分处穿隧穿过此势垒(量子-机械穿隧)。可通过考虑到由于场发射极所致的场增强因子的福勒-诺得海姆(Fowler-Nordheim)理论的经修改版本来估计所得发射电流密度(R.·福勒(R.Fowler)及L.·诺得海姆(L.Nordheim),“强电场中的电子发射(Electron emission in intense electric fields)”,伦敦皇家协会会刊A(Proceedings of the Royal Society of London A),第119卷,第781期,1928年5月,第173页到181页)。此外,通过形成所述大体上纯硼层使得其气密密封所述场发射极突出部的至少所述尖端部分,所述场发射极输出表面的氧化大体上被完全阻止,借此避免在常规方法中遇到的对电子逸出的显著势垒。因此,通过产生包括一体地形成于单晶体硅衬底上且由大体上纯硼层气密地保护的场发射极突出部的光电阴极,本发明提供具有有益质量的硅(即,亚1μm波长吸收、高纯度/低缺陷材料及长电子重新组合时间)同时避免先前阻止硅基光电阴极的广泛商业用途的不利方面的光电阴极。

[0022] 任选地利用各种常规半导体处理技术来使根据本发明产生的光电阴极的性能最佳化。举例来说,硅衬底优选地是具有介于约10nm到约100μm的范围内的厚度的基本上无缺陷单晶(单晶体)硅,其中所述厚度部分地取决于待俘获的光的波长。在优选实施例中,所述

硅衬底包括具有经最佳化的掺杂水平的(例如,经植入n型)掺杂剂,使得当所述光电阴极经受适当外部电场时,每一场发射极突出部作为场发射极在反向偏置模式中起作用。所述场发射极突出部是通过蚀刻或以其它方式使所述硅衬底图案化而形成,使得部分硅材料形成具有一体地连接到输出表面的相对宽基极部分的一体式结构,且在所述输出表面上延伸至少100nm的高度距离到达相对窄尖端(自由端)部分。在一个实施例中,为促进最佳场发射极操作,每一场发射极突出部的基极部分具有约100nm的最小直径/宽度尺寸且尖端部分具有约200nm(且更优选地大约100nm或更小)的最大直径/宽度尺寸。在示范性实施例中,使用标准CMOS制作技术制作场发射极突出部(例如,通过PECVD将二氧化硅或氮化硅掩模材料沉积在平坦衬底表面上,使用已知光学光刻技术使所述掩模图案化,且接着透过所述掩模中的开口蚀刻所述硅衬底以形成所述场发射极突出部),使得所述场发射极突出部在所述硅衬底的所述输出表面上布置成二维阵列图案。优选地使用高温沉积过程(例如,介于约600°C与800°C之间),以产生具有介于1nm到5nm(优选地约2nm到3nm)的范围内的厚度的无针孔硼层的方式在清洁、平滑硅上形成硼层,借此所述硼层通过可靠地气密密封所述硅衬底的整个输出表面免受氧化而规避硅的氧化问题。在替代实施例中,所述场发射极突出部是使用各种突出结构形状形成,例如圆晶须(具有圆形尖端的圆柱形柱)、圆锥体或角锥体。上文所提及的各种技术及特征可单独地或组合地使用以增强光电阴极性能。

[0023] 根据本发明的各种替代特定实施例,额外层及结构用于进一步增强发明性光电阴极结构的有益质量。在一些实施例中,一个或数个栅极结构(控制电极)安置在输出表面上且放置在场发射极尖端部分的高度处或稍微低于所述高度以便实现对发射电流的快速及准确控制。在一些实施例中,第二硼层(第三层)形成于硅衬底的经照射(第一)表面上以进一步阻止可减少光子吸收的氧化物及缺陷。在另一实施例中,抗反射材料层(第四层)安置在第二硼层(第三层)上以进一步增强光子吸收。在一些实施例中,金属或导电框架或栅格及电压源用于在硅衬底的经照射表面与输出表面之间产生外部电位差以便致使电子优先地朝向所述输出表面移动。在一些实施例中,光电阴极包括n型硅场发射极与p-i-n光电二极管结构的组合,当在所述衬底的所述经照射表面与所述输出表面之间施加高电压(例如,大约数十或几百伏特)时,所述组合在雪崩倍增条件下操作。此雪崩增益增强有效量子效率且因此改进光电阴极的性能。在其它实施例中,硼(或另一p型掺杂剂)穿过所述经照射表面扩散到所述硅衬底中以形成p型掺杂区域以形成驱动电子远离所述经照射表面(电子可在其处重新组合且损失)的电位梯度。

[0024] 根据替代特定实施例,本发明的发明性光电阴极结构经并入到各种传感器结构中以提供呈现优越低光感测能力的传感器。除光电阴极(其邻近于传感器的接收表面而定位)之外,这些传感器结构还包括具有检测表面的检测装置(例如,CCD或CMOS图像传感器),所述检测表面面对光电二极管的输出表面且通过介入间隙与所述衬底的输出表面上的硼层间隔,其中所述检测装置用于检测穿过所述光电阴极的所述输出表面发射的光电子,且用于产生指示光电子的俘获的电信号。在一些传感器实施例中,所述传感器结构是在所述光电阴极的顶部上可(或可不)具有窗的电子轰击电荷耦合装置(EBCCD)。在本发明的其它实施例中,所述传感器是在所述光电阴极的顶部上可(或可不)具有窗的图像增强器。在本发明的其它实施例中,所述传感器是在所述光电阴极的顶部上可(或可不)具有窗的光电倍增管。

[0025] 在一些传感器实施例中,第二硼层形成于光电阴极的经照射表面上以阻止所述经照射表面上的氧化物形成,且抗反射材料层提供于所述第二硼层上方以改进光子俘获效率。在这些实施例中的一些实施例中,所述抗反射材料层安置在窗与所述光电阴极之间,但在其它实施例中,所述抗反射材料层还用作传感器的接收表面(即,所述传感器在所述光电阴极的所述经照射表面上方不具有窗),此进一步增加通过所述传感器的光子俘获效率。在于所述光电阴极的所述经照射表面上方包括窗的其它传感器实施例中,抗反射材料层提供于所述窗上以改进光子俘获效率。

[0026] 在本发明的一些实施例中,包括本发明的光电阴极的传感器还包括在其接收表面(即,面对所述光电阴极的所述检测装置的表面)上具有额外硼层的硅基检测装置。举例来说,在其中所述传感器是电子轰击CCD(EBCCD)且所述检测装置是CCD(其通常形成于硅衬底上)的情形中,在制作期间硼层直接形成于CCD的接收表面上以通过阻止在所述CCD的接收表面上形成二氧化硅层来改进所述传感器的电子俘获效率。在其它实施例中,所述传感器包括CMOS检测器(即,替代CCD),且额外硼层形成于所述CMOS检测器的接收表面上。

[0027] 在本发明的其它实施例中,包括发明性光电阴极的传感器用于晶片、光罩或光掩模检验系统中。明确地说,发明性系统包括:照射源(例如,激光系统),其用于将光发射到样本/晶片上;一或多个传感器(例如,光电倍增管、图像增强器或EBCCD),其利用本文中所描述的发明性光电阴极中的任一者来检测通过样本/晶片或由样本/晶片反射的光子;及相关联光学系统,其用于将光/光子从所述照射源导引到所述样本(晶片、光罩或光掩模)且从所述样本导引到所述传感器。

## 附图说明

[0028] 在附图的各图中以实例方式而非以限制方式图解说明本发明,在附图中:

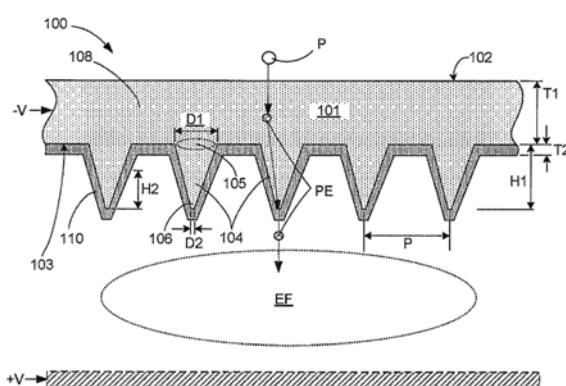

[0029] 图1是图解说明根据本发明的经简化一般化实施例的包括形成于硅衬底上的场发射极阵列的光电阴极的横截面侧视图;

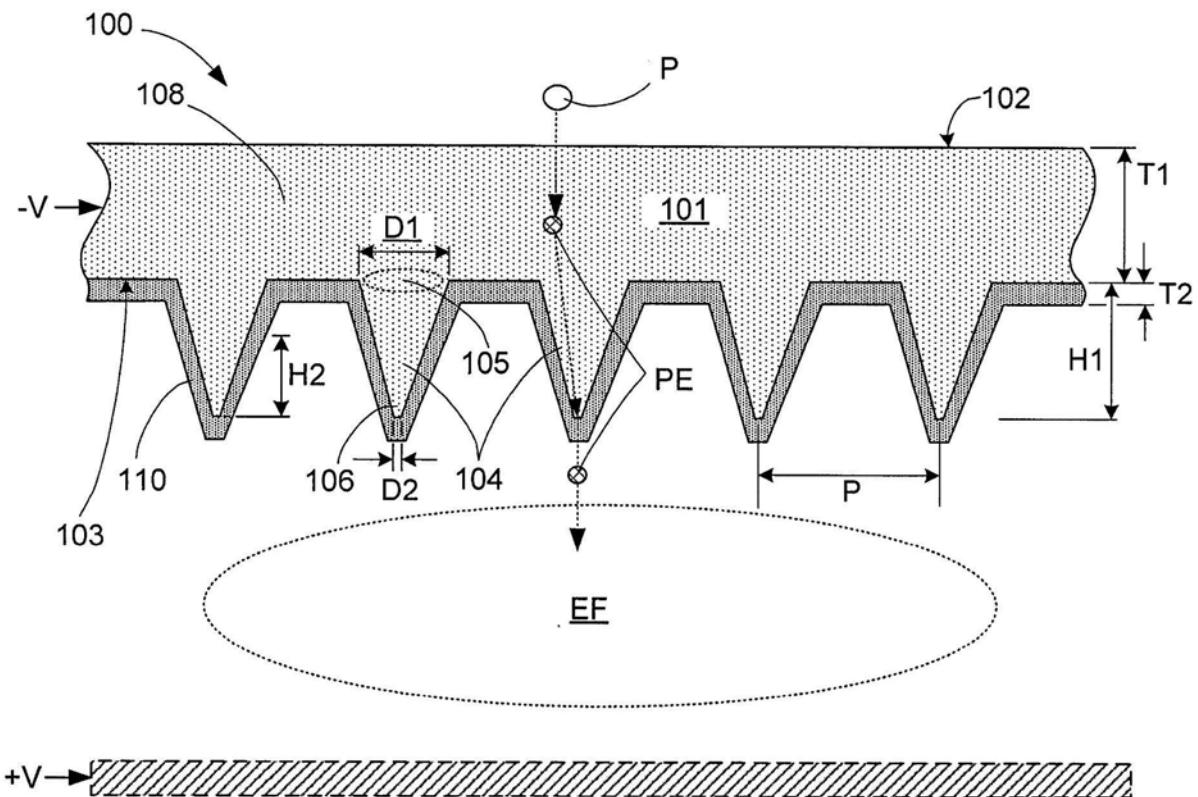

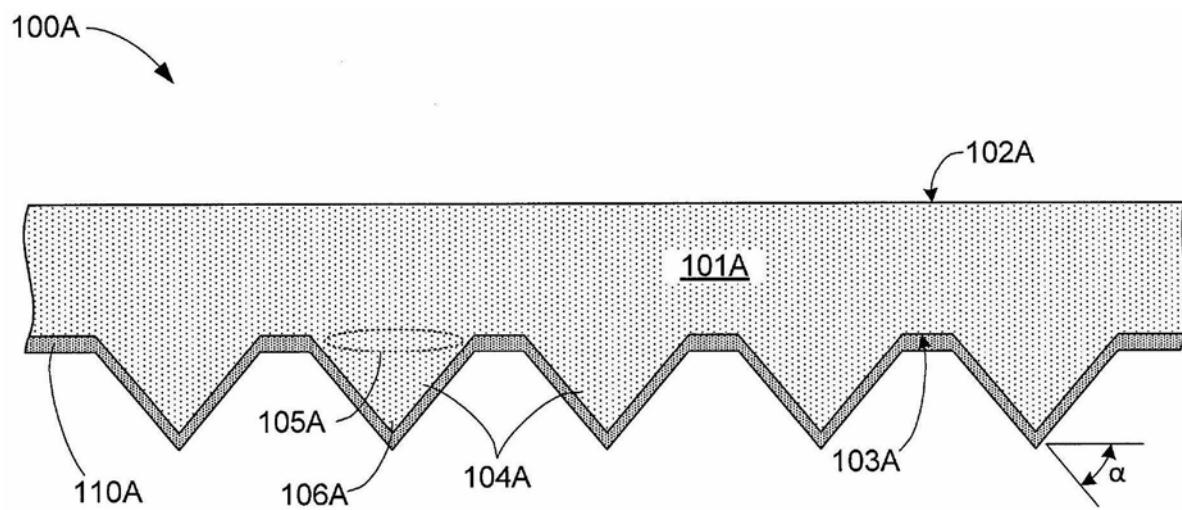

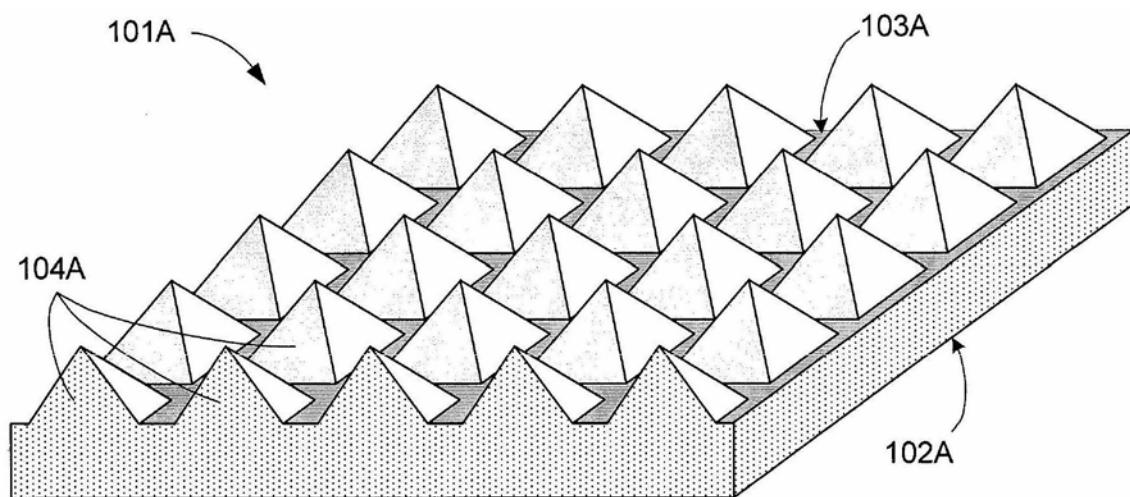

[0030] 图2A及2B是展示根据本发明的第一特定实施例的硅光电阴极的经放大部分横截面侧视图及部分透视图;

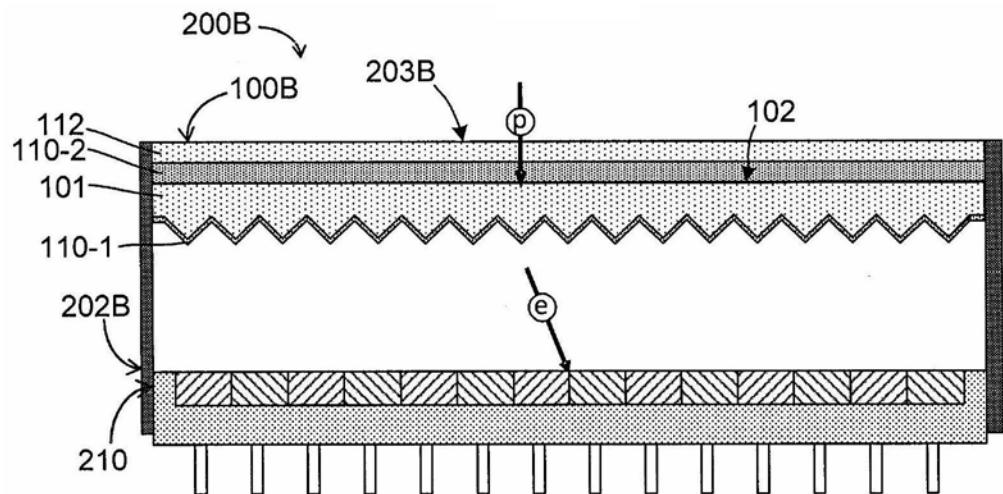

[0031] 图3是图解说明根据本发明的另一示范性特定实施例的光电阴极的经放大部分横截面侧视图;

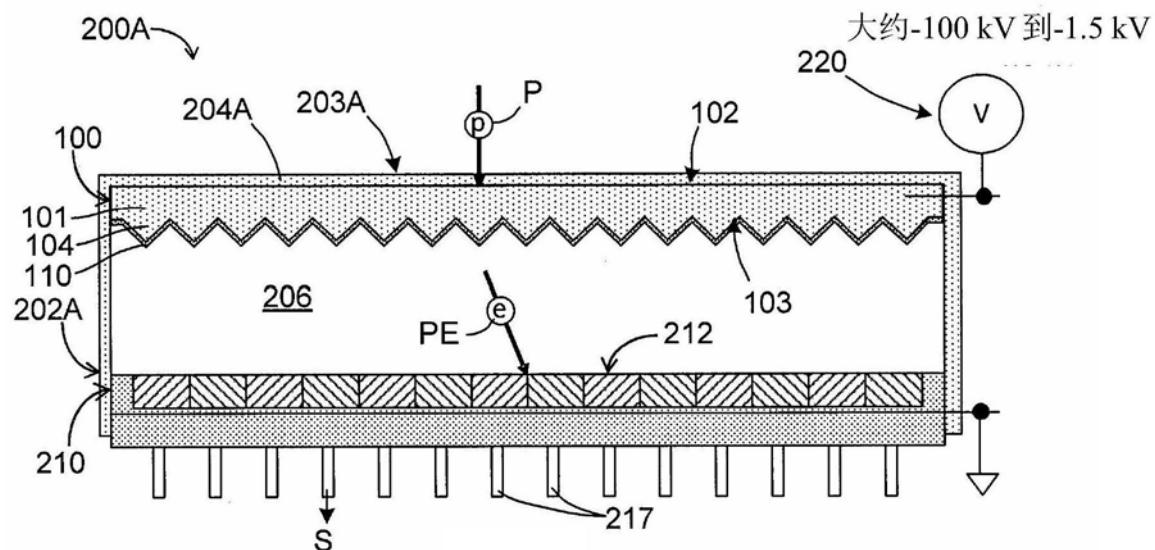

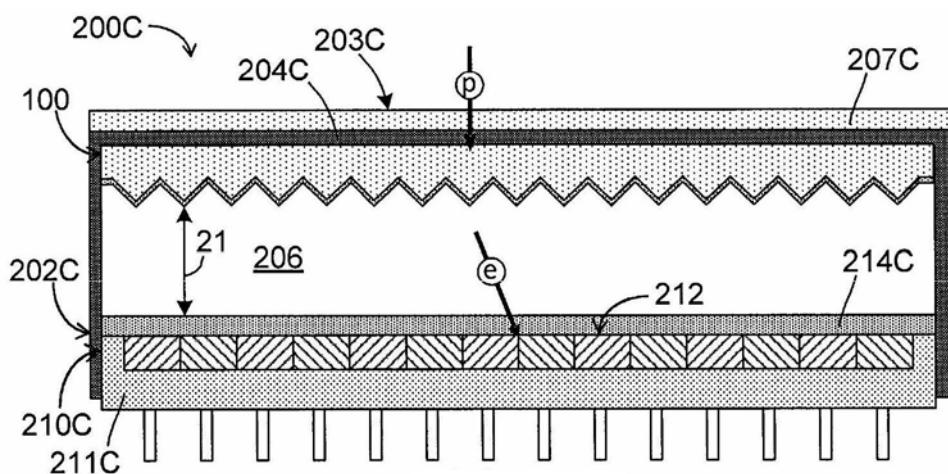

[0032] 图4A、4B、4C、4D、4E及4F是展示根据本发明的额外示范性特定实施例的光电阴极的横截面图;

[0033] 图5是图解说明在根据本发明形成的光电阴极的硅衬底内侧的示范性电子能量水平的能量图式;

[0034] 图6A、6B及6C是图解说明根据本发明的替代特定实施例的包括光电阴极的示范性传感器的横截面侧视图;

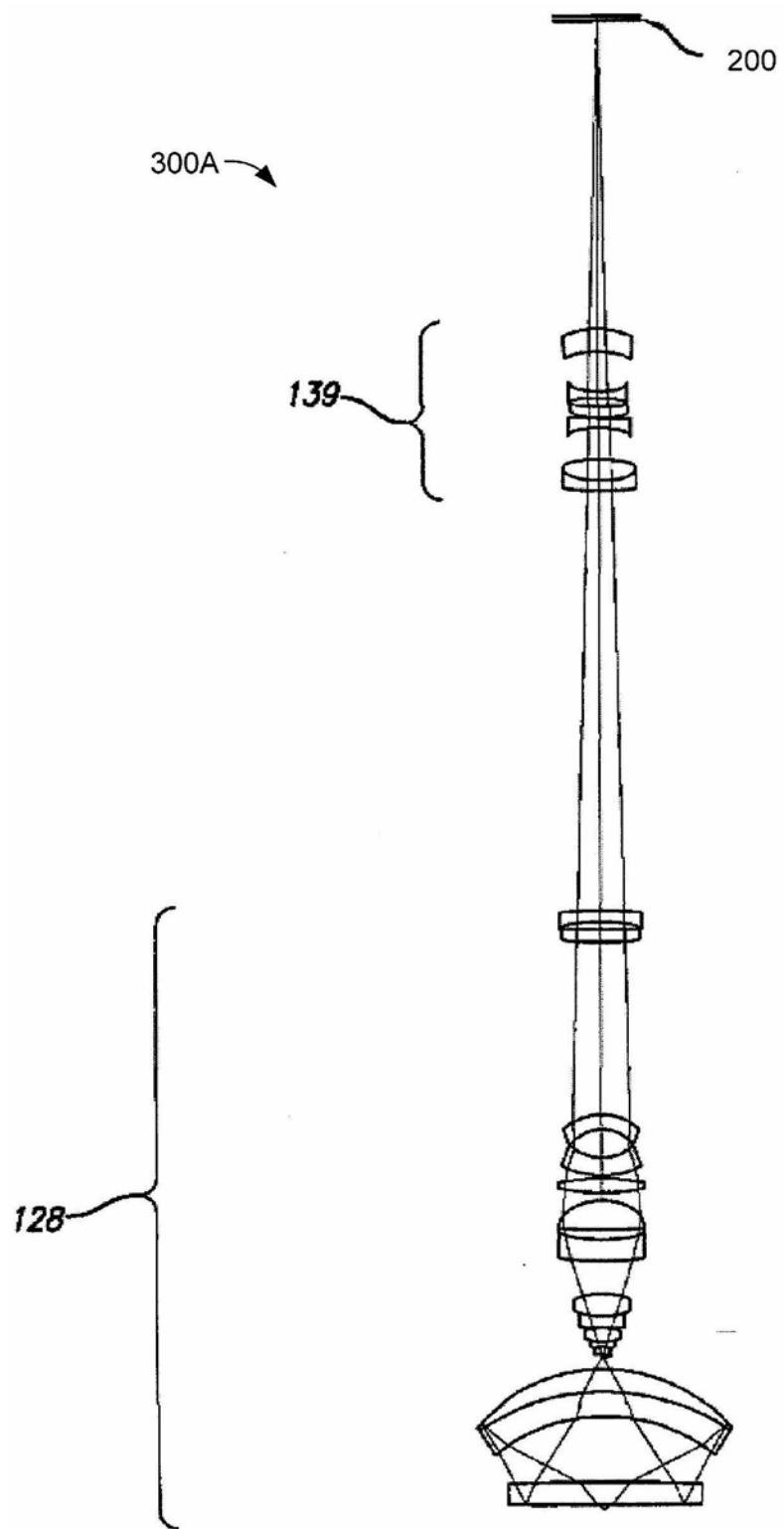

[0035] 图7是展示根据本发明的另一实施例的检验系统的简化图式;

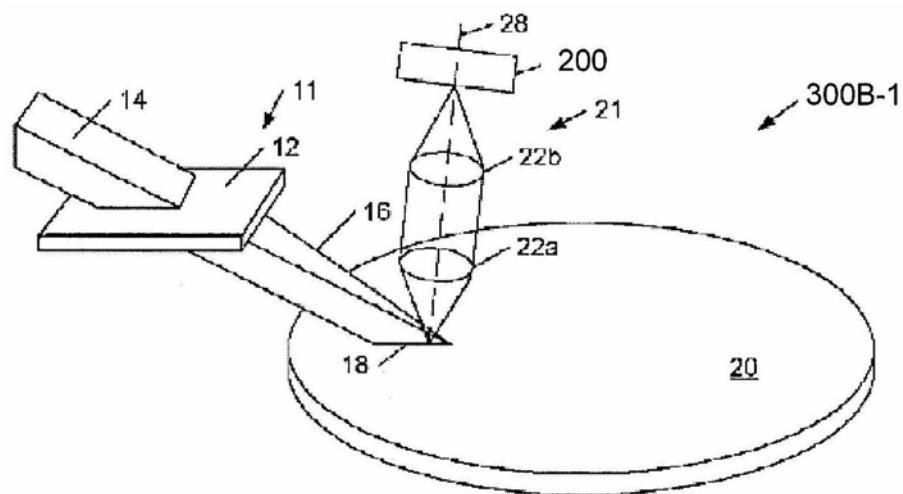

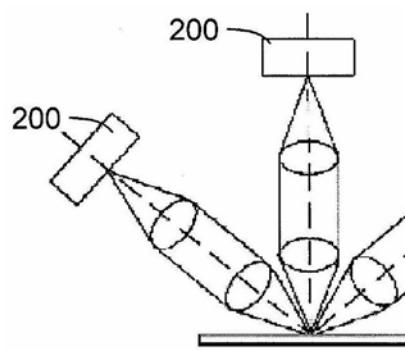

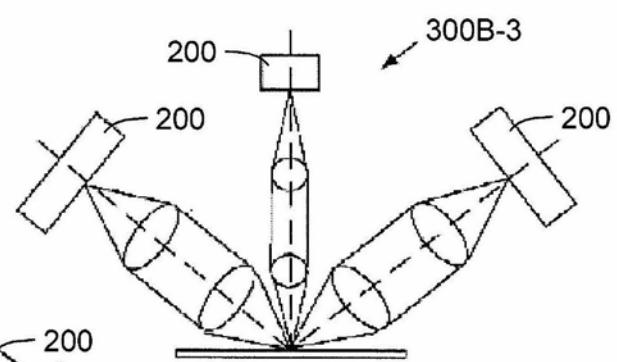

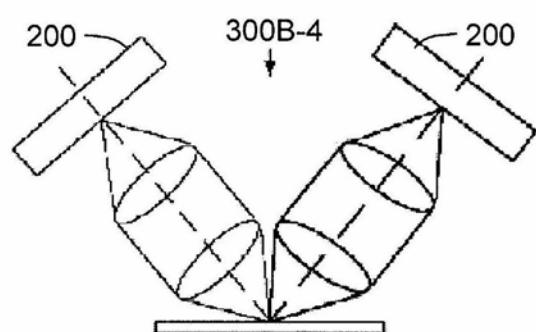

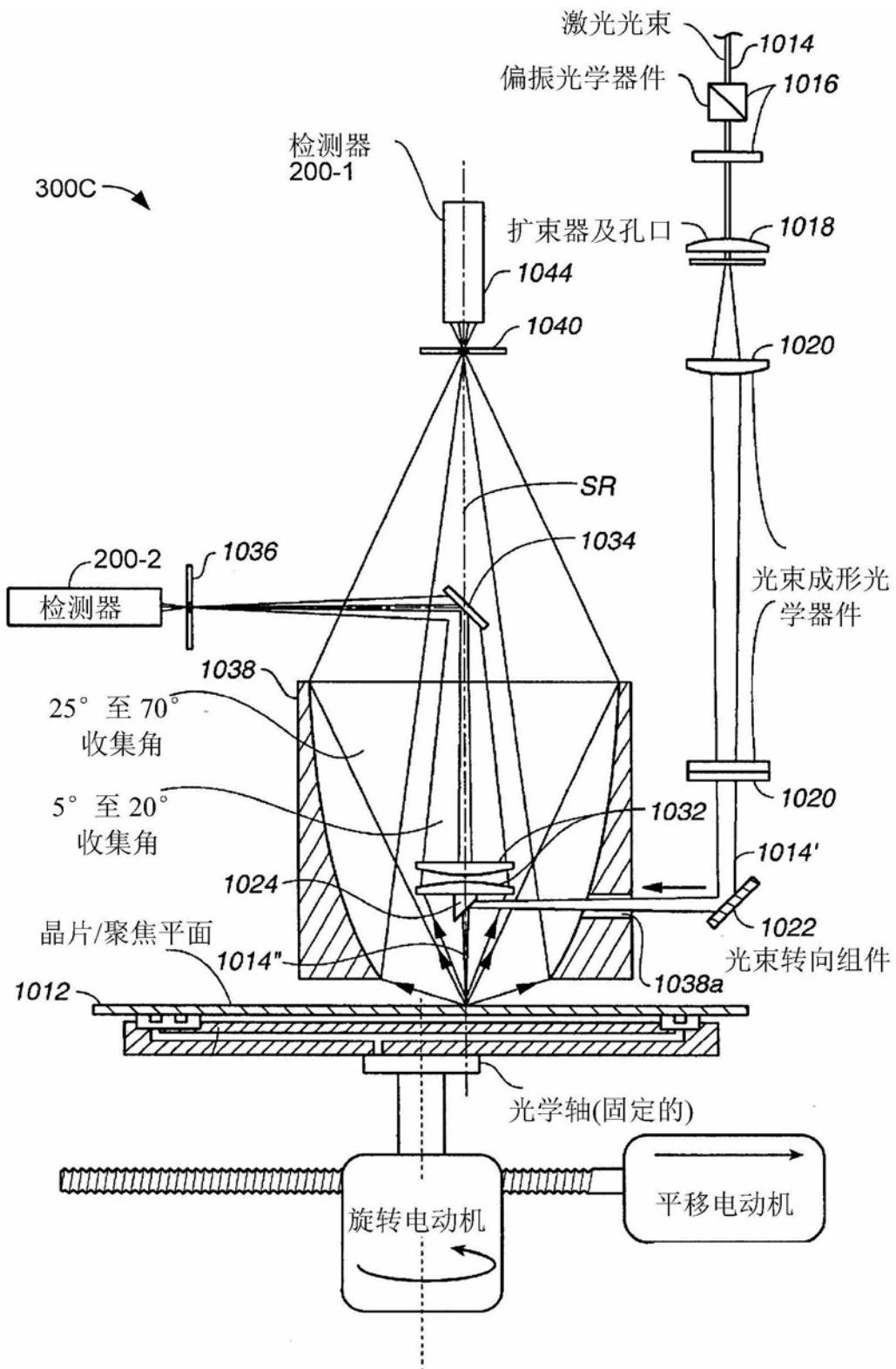

[0036] 图8A、8B、8C及8D是展示根据本发明的额外实施例的检验系统的简化图式;

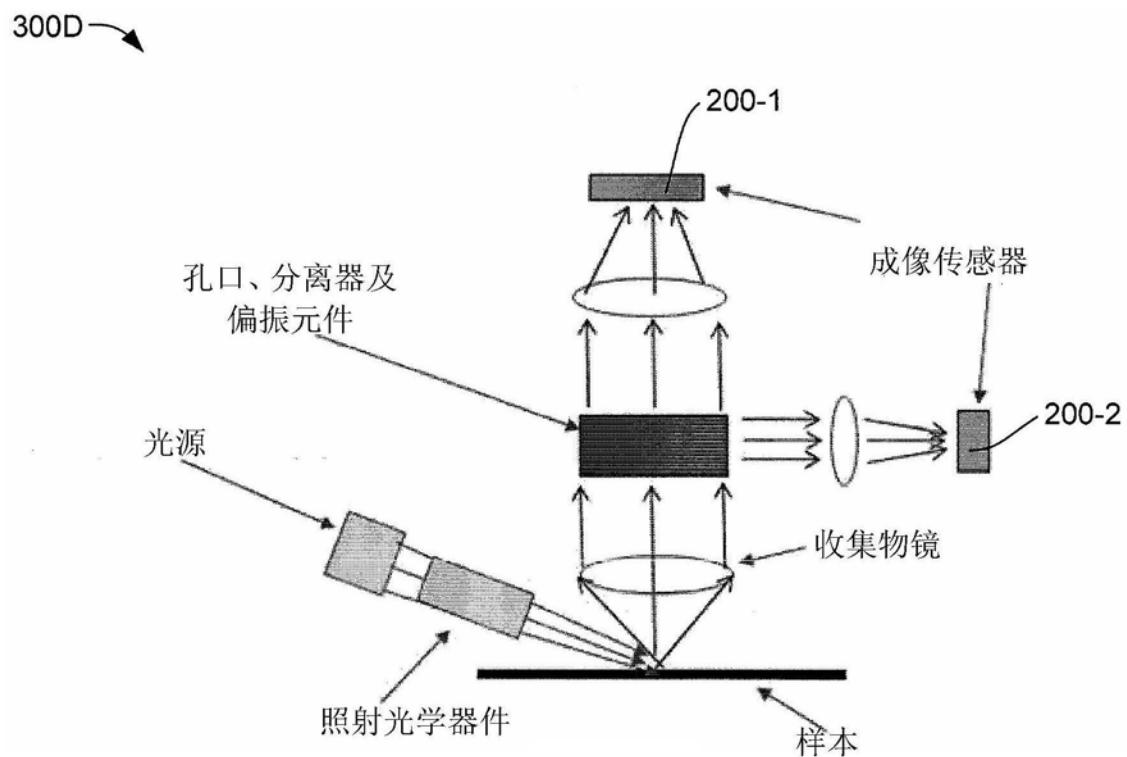

[0037] 图9是展示根据本发明的另一实施例的另一检验系统的简化图式;

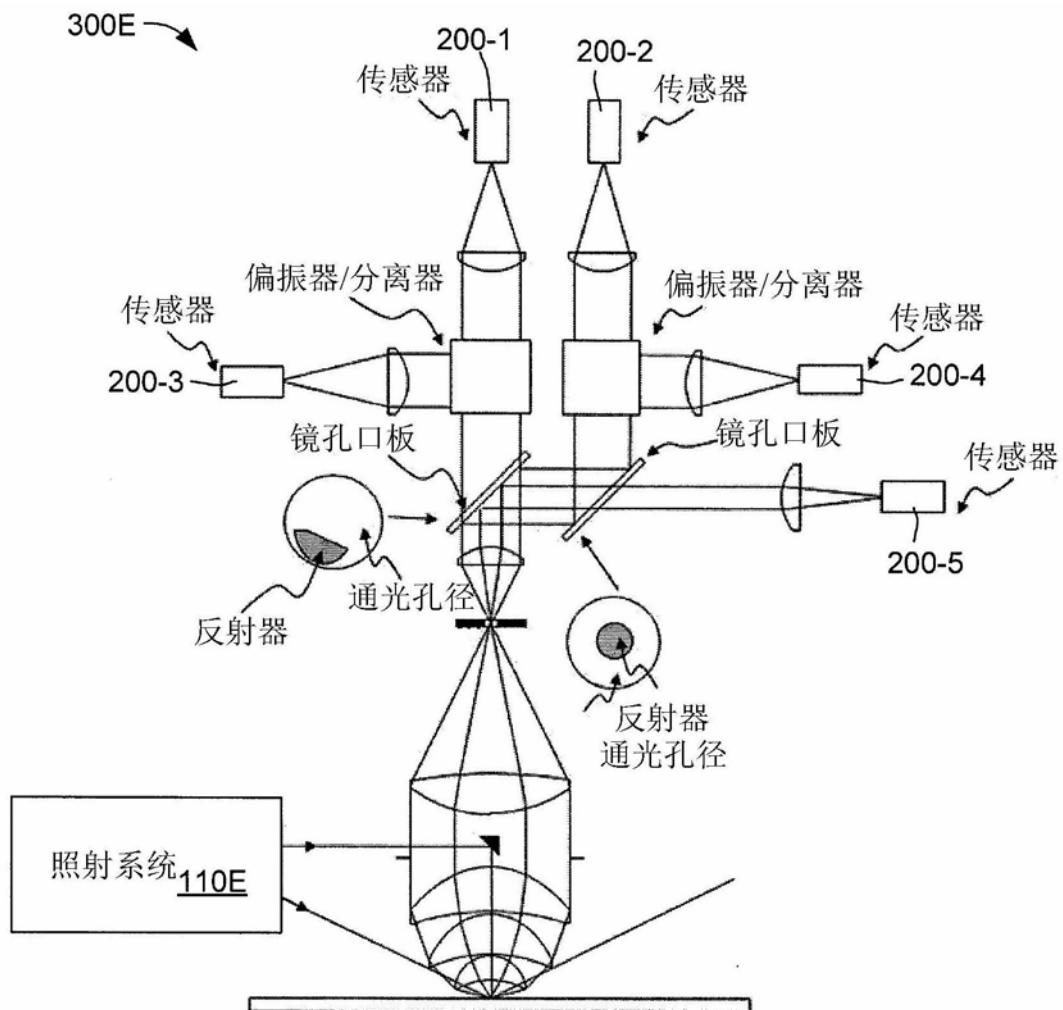

[0038] 图10是展示根据本发明的另一实施例的另一检验系统的简化图式;

[0039] 图11是展示根据本发明的另一实施例的另一检验系统的简化图式;且

[0040] 图12是图解说明常规传感器的横截面侧视图。

### 具体实施方式

[0041] 本发明涉及用于半导体检验系统的低光传感器的改进。呈现以下描述以使所属领域的技术人员能够制造并使用本发明,如在特定申请案及其要求的上下文中提供。如本文中所使用,例如“顶部”、“底部”、“上方”、“下方”、“上部”、“向上”、“下部”、“在下面”及“向下”等方向术语打算出于描述目的提供相对位置,且并不打算指定绝对参考系。所属领域的技术人员将容易明了对优选实施例的各种修改,且本文中所定义的一般原理可适用于其它实施例。因此,本发明并不打算限于所展示及所描述的特定实施例,而欲赋予与本文中所揭示的原理及新颖特征一致的最宽广范围。

[0042] 图1以横截面图图解说明根据本发明的一般化实施例的光电阴极100。光电阴极100大体来说包括:硅衬底101,其具有面向上经照射(顶部/第一)表面102及相对面向下输出(底部/第二)表面103;场发射极突出部104阵列,其一体地形成于输出表面103上(即,图案化成部分硅材料且由部分硅材料形成)且从输出表面103延伸;及大体上纯硼层110,其气密地安置在输出表面103上、在场发射极突出部104上方。在此布置的情况下,光电阴极100类似于常规光电阴极而操作,这是因为当经恰当定位时,所述光电阴极经受适当电场EF,穿过经照射(上部)表面102进入硅衬底101的光子P被吸收且形成光电子PE,所述光电子PE接着穿过输出表面103而发射。根据本发明的方面,输出表面103可操作地经配置使得当电场EF存在时,场发射极突出部104充当场发射极阵列(FEA),此大大增加在衬底101中产生的给定光电子PE将从输出表面103发射的概率。根据另一方面,硼层110用于保护场发射极突出部104免受氧化,此促进光电阴极100的可靠长期操作。此外,本发明发明者已确定,硼大体上对低能量电子是透明的,从而使硼成为用于硅基光电阴极的理想气密密封材料。

[0043] 根据实际实施例,优选地使用单晶硅(即,硅的单晶体)来实施硅衬底101,所述单晶硅在小于约 $10^{19}\text{cm}^{-3}$ 的掺杂水平处是经p型掺杂的(即,含有p型掺杂剂108),即约 $0.005\Omega\text{cm}$ 或更高的电阻率。由于少数载子寿命及扩散长度随增加的掺杂剂浓度而降低,因此当硅极薄(例如薄于约 $1\mu\text{m}$ )时,可使用高于约 $10^{19}\text{cm}^{-3}$ 的掺杂剂浓度,然而当硅厚于约 $1\mu\text{m}$ 时,低于约 $10^{19}\text{cm}^{-3}$ 的掺杂剂浓度可为优选的。在其它实施例中,硅衬底101包含多晶硅(polycrystalline silicon或multi-crystalline silicon)。取决于光电阴极的既定波长操作范围,硅的厚度可介于约10nm与约100 $\mu\text{m}$ 之间。硅衬底101呈现大约1.1eV的能带间隙,因此具有短于大约 $1.1\mu\text{m}$ 的真空波长的光被吸收。硅衬底101的1.1eV能带间隙是间接的,因此光谱的红色及红外线部分中的波长的吸收是弱的。硅衬底101还具有大约3.5eV的直接能带间隙,因此其强烈吸收深UV波长。取决于对光电阴极100的既定用途,硅衬底101具有处于大约20nm到大约100 $\mu\text{m}$ 的范围内的厚度T1。举例来说,为促进吸收光谱的红外线部分中的光子的高概率,硅衬底101形成有约 $10\mu\text{m}$ 或数十 $\mu\text{m}$ 的厚度T1。另一选择为,为吸收UV波长,硅衬底101形成有处于几十nm到约100nm的范围内的厚度T1。在实际实施例中,硅衬底101具有约 $1\mu\text{m}$ 的厚度T1以便吸收在从真空UV到接近可见光谱的红端的大约670nm的波长范围内的至少85%未经反射入射光子。当硅衬底101包含使用已知技术以极低密度的晶体缺陷及高纯度生长的单晶(单晶体)结构时,在硅衬底101内侧产生的光电子具有数十或数百微秒( $\mu\text{s}$ )的潜在寿命。另外,单晶体结构致使光电子损失其过量能量中的许多能量且部分地或大体

上以低重新组合概率而热化。

[0044] 根据优选实际实施例,使用标准CMOS制作技术在硅衬底101上制作场发射极突出部104。每一场发射极突出部104具有一体地连接到输出表面103的相对宽基极部分105,且所述场发射极突出部在输出表面103上面延伸至少100nm的高度距离H1到达相对窄尖端(自由端)部分106。在一个实施例中,为促进最佳场发射极操作,每一场发射极突出部104的基极部分105具有约100nm的最小直径/宽度尺寸D1,且尖端部分106具有200nm(且更优选地大约100nm或更小)的最大直径/宽度尺寸D2。在制作期间,二氧化硅或氮化硅可用作掩模材料且通过(举例来说)PECVD而沉积,且光学光刻可用于图案化。干蚀刻(例如RIE、ICP及ECR)及湿蚀刻两者可用于形成布置成二维周期性图案(例如,如在图2B中所描绘,下文所论述)的场发射极突出部阵列。影响场发射极性质的重要参数是发射极突出部104之间的间隔(间距)P。已知,紧密间隔的发射极由于导致个别发射极之间的不充分电场穿透的屏蔽效应而减小场增强因子。因此,为使场遮蔽效应最小化且为使场发射电流密度最佳化,经垂直对准发射极之间的距离应介于其高度的大约两倍与大约20倍之间(举例来说,参见R. • 瑟巴恩(R.Serbun)、B. • 博恩曼(B.Bornmann)、

[0045] A. • 纳维茨基(A.Navitski)、C. • 普罗莫斯伯杰(C.Prommesberger)、C. • 莱格(C.Langer)、F. • 达姆斯(F.Dams)、G. • 米勒(G.Müller)及R. • 沙伊纳(R.Scheiner),“集成式真空微电子装置的单B掺杂Si尖的稳定场发射及均匀尖阵列的线性电流比例缩放(Stable field emission of single B-doped Si tips and linear current scaling of uniform tip arrays for integrated vacuum microelectronic devices)”,真空科学与技术学报B(Journal of Vacuum Science and Technology B),第31卷,第2期,2013年,第02B101页)。举例来说,当场发射极突出部具有等于500nm的标称高度H1时,间隔P应介于大约1μm与大约10μm之间。

[0046] 根据本发明的另一方面,场发射极经配置而以反向偏置模式操作(如在p-n二极管中),其中由于发射极表面处的高电场而产生耗尽层。在此实施例中,接近场发射极突出部104的尖端的区域可在所述突出部的形成之前或之后掺杂有n型掺杂剂(例如磷或砷)。场发射在所施加电场足够高以减小硅-真空界面上的电位势垒,使得电子可穿隧穿过此势垒(量子-机械穿隧)时发生。在其中电子浓度是通过局部掺杂水平及电位确定的半导体中,可将场发射极设定为处于反向偏置模式。可通过考虑到由于场发射极所致的场增强因子的福勒-诺得海姆理论的经修改版本来估计发射电流密度。

[0047] 根据本发明的另一方面,硼层110包含大体上纯硼,所述硼层直接安置在输出表面103上,使得场发射极突出部104的至少尖端部分106被气密密封。如本文中所使用,短语“大体上纯硼”意指具有95%或更高的纯度的硼,且短语“直接在…上”结合硼与硅界面打算意指除可在Si/B界面处形成的可能SiB<sub>x</sub>薄层(即,几个单层)之外,不存在将场发射极突出部104的输出表面与硼层110分离的连续介层(例如,氧化物或SiN<sub>x</sub>层)。还注意,短语“直接在…上”不排除在硼及硅的一些部分之间存在可在硼层110的形成之前或期间不经意地形成的不连续氧化物分子或斑点。在一个实施例中,使用由F. • 萨鲁比(F.Sarubbi)等人在“针对受控纳米深度p+n结形成的a硼层在硅上的化学气相沉积(Chemical Vapor Deposition of a-Boron Layers on Silicon for Controlled Nanometer-Deep p+n Junction Formation)”(电子材料杂质(Journal of Electronic Materials),第39卷,第2

期, (2010年2月) 第162页到173页, ISSN 0361-5235) 中教示的技术在高温下(即, 在高于大约500°C, 优选地介于约600°C与800°C之间的温度下)于清洁平滑硅上生长大体上纯硼层110, 使得硼形成具有处于大约1nm到5nm(优选地大约2nm到3nm)的范围内的厚度T2的无针孔涂层。如萨鲁比等人在所引用参考文献的163页上所阐释, 通过(举例来说)在沉积硼之前进行湿清洁、后续接着原位热氢清洁而从硅移除所有自然氧化物是重要的。硼的较低温度沉积也是可能的, 但涂层可为较不均匀的, 且可需要厚于2nm的涂层以确保其是无针孔的。以此方式形成大体上纯硼层110的优点是当经施加到清洁硅表面时, 所得无针孔硼涂层用作阻止在下伏硅表面上形成自然氧化物的气密密封。如本文中所使用, 短语“气密地安置”意指以上文所陈述的方式形成硼层110, 且短语“至少在尖端部分上”意指气密地安置的硼涂层沿着每一场发射极突出部104从尖端部分106延伸至少距离H2, 其中距离H2是总突出部高度H1的至少10%。在优选实施例中, 硼层110气密地安置在整个输出表面103上方。如先前所描述, 二氧化硅层具有高能带间隙且甚至薄层还可阻挡显著部分电子离开硅。因此, 硼层110允许甚至具有低能量的电子在操作期间离开尖端部分106。现有技术装置不可避免如铯或氧化铯的低功函数碱金属或碱金属氧化物材料的使用。尽管此项技术中已知碱金属层可通过在输出表面处形成负电子亲和性装置而降低光电阴极输出表面的功函数, 但在特定使用时间之后, 此层随着碱金属离开输出表面而变得较薄。通过将大体上纯硼层110气密地安置在输出表面103上, 光电阴极100的所得场发射极阵列规避此限制且尖锐尖端的场发射极突出部104提供场增强及较多发射电流。另外, 现有技术装置不可避免在硅与低功函数材料之间形成二氧化硅界面层, 即使当经涂覆时硅层不含氧化物也是如此。即, 在于硅上不具有防渗无针孔保护层的情况下, 氧将最终迁移到硅表面且形成氧化物层。在输出表面103上提供气密地安置的大体上纯硼层110的优点是甚至极薄(例如, 1nm)无针孔硼层也是防渗氧的且保护硅免受氧化。在输出表面103上提供具有处于1nm到5nm范围内的厚度的气密地安置的大体上纯硼层110的另一优点是硅-与-硼界面处的缺陷的密度及界面陷阱通常低于硅-与-二氧化硅界面处, 因此大体上纯硼层110还用于减少在电子可被发射之前用以在表面处进行重新组合所损失的电子的部分。

[0048] 根据替代特定实施例, 场发射极突出部104是使用在输出表面103上布置成二维周期性图案的各种几何形式(例如圆晶须、圆锥体或角锥体)实施。

[0049] 图2A及2B描绘光电阴极100A, 所述光电阴极包括具有平坦输入(上部)表面102A的衬底101A, 一体地形成于相对输出表面103A上的角锥体形场发射极突出部104A阵列, 及以上文所描述的方式气密地安置在输出表面103A上的大体上纯硼层110A。每一场发射极突出部104A包含角锥体形结构, 所述角锥体形结构包括从相对宽固定(基极)部分105A延伸到相对窄尖端(自由端)部分106A的四个成角度壁。在一个实施例中, 场发射极突出部104A的角锥体形状是通过各向异性蚀刻的硅衬底101而实现, 优选地使得蚀刻过程产生具有接近于54.7°的倾斜角 $\alpha$ 的场发射极突出部104A(即, 这是因为所述倾斜角对应于单晶硅中的(100)与(111)平面的相交点)。尽管邻近角锥体形场发射极突出部104A经描绘为通过相对平坦输出(下部)表面103的窄区段分离, 但在其它实施例中, 可通过进一步蚀刻硅直到邻近角锥体形结构的外围边缘彼此邻接而消除这些窄平坦区段(即, 输出表面103A大体上完全包含场发射极突出部104A)。尽管图2B将场发射极突出部阵列描绘为定位于方形栅格上, 但所述突出部可位于不同栅格图案上, 例如位于六边形栅格上。

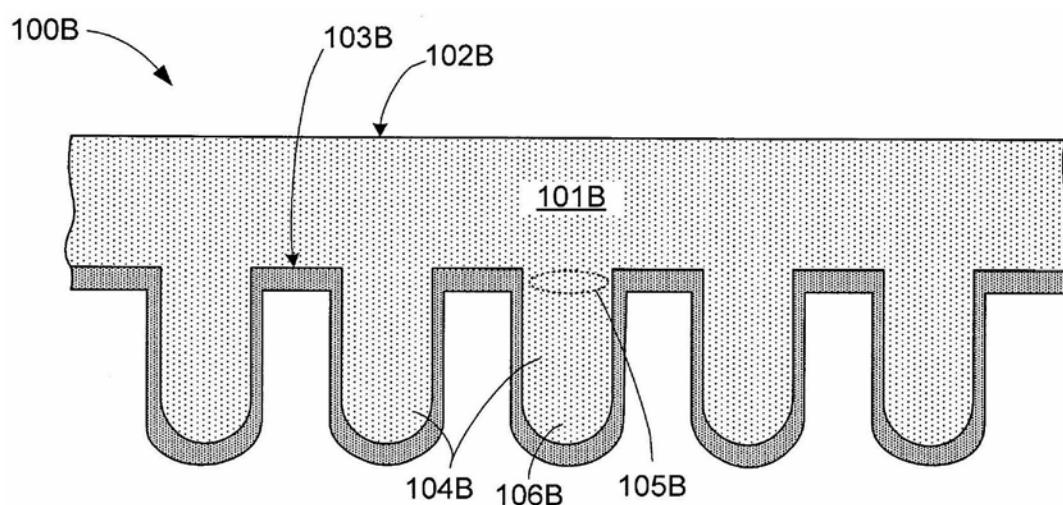

[0050] 图3描绘光电阴极100B,所述光电阴极包括具有平坦输入(上部)表面102B的衬底101B,一体地形成于相对输出表面103B上的经间隔开场发射极突出部104B阵列,及气密地安置在输出表面103B上的大体上纯硼层110B。在此实施例中,场发射极突出部104B形成为具有大致圆形基极部分105B及大体上圆柱形中心部分的圆晶须,所述圆柱形中心部分远离输出表面103B延伸到圆尖端部分106B。在替代实施例中,突出部104B的大体上圆柱形中心部分可成角度以形成优选地具有零度或近零度半角的圆锥体形结构。已知,与具有大于零度的半角的圆锥体或角锥体相比,圆晶须或具有近零度半角的圆锥体提供更高场增强(举例来说,参见T.・内海(T.Utsumi),“真空微电子学:什么是新奇和令人激动的(Vacuum microelectronics:What's new and exciting)”,电气及电子工程师学会电子装置会刊(IEEE Transactions on Electron Devices),第38卷,第10期,1991年,第2276页到2283页)。可利用所属领域的技术人员已知的干蚀刻技术(例如RIE、ECR及ICP)来制作圆晶须场发射极突出部104B。

[0051] 图4A到4F图解说明根据本发明的各种替代实施例的发明性光电阴极,在所述替代实施例中利用额外层及结构以进一步增强上文所描述的发明性光电阴极结构的有益质量。所图解说明示范性实施例并不打算是穷尽性的,且包括下文所描述的额外层与结构的组合的光电阴极经理解为可能的。

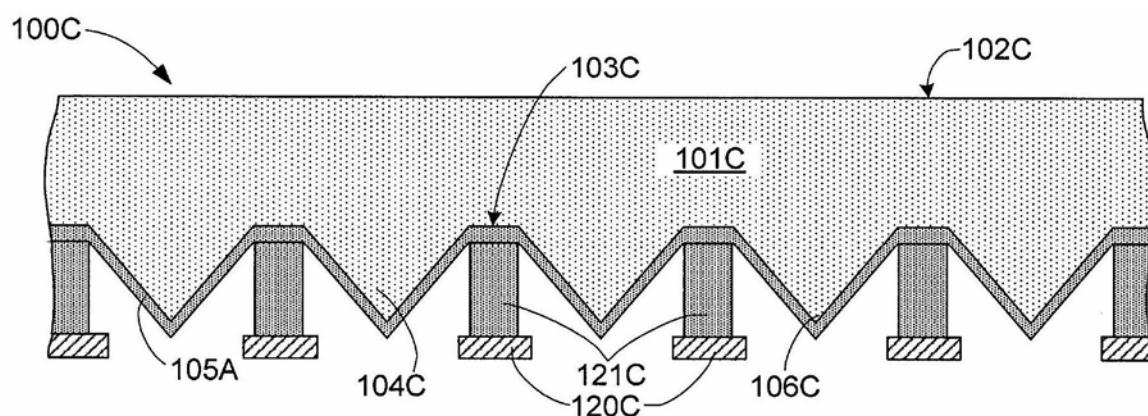

[0052] 图4A以横截面图图解说明光电阴极100C,所述光电阴极包括具有平坦输入表面102C的硅衬底101C,安置在相对输出表面103C上的场发射极突出部104C阵列,及安置在输出表面103C上、在场发射极突出部104C上方的硼层110C。光电阴极100C不同于先前所描述实施例之处在于连续栅极或控制电极120C经放置为与场发射极突出部104C的尖端部分106C大致齐平且通过电介质结构121C附接到输出表面103。在操作期间,使用相对于衬底的介于约10V与100V之间的控制电压来操作栅极120C以实现对来自场发射极突出部104C的发射电流的快速及准确控制。相对于衬底101C的正提取电压可施加到栅极120C以增强发射,且相对于衬底的负电压可经施加以抑制发射,如果需要。可通过标准CMOS制作技术制作栅极120C及电介质结构121C栅极层。在所描绘实施例中,栅极120C形成为三极管配置中(即,所有栅极120C均安置在仅一个栅极层中)。在其它实施例(未展示)中,可利用两个或多于两个栅极层。

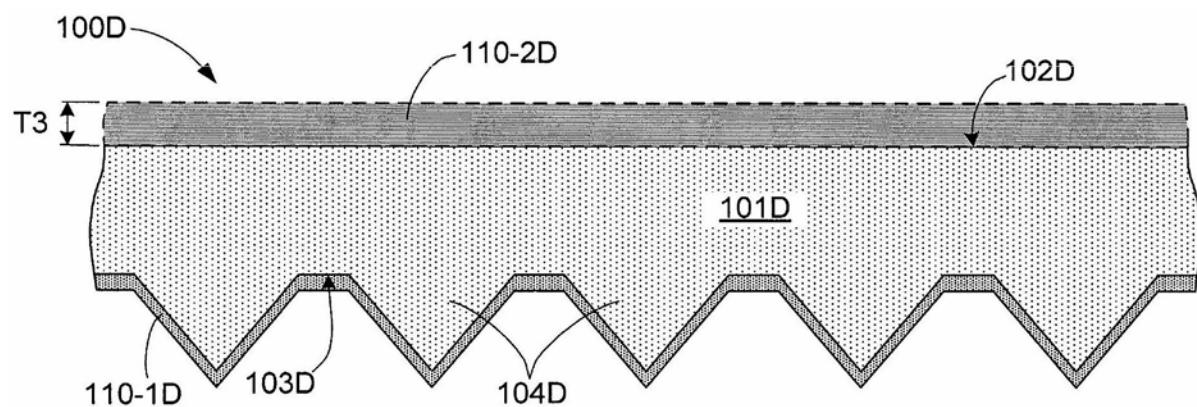

[0053] 图4B描绘光电阴极100D,所述光电阴极包括具有平坦输入表面102D的硅衬底101D,安置在相对输出表面103D上的场发射极突出部104D阵列,及以上文所描述的方式安置在输出表面103D上、在场发射极突出部104D上方的(第一)硼层110-1D。另外,光电阴极100D包括形成于硅衬底101D的面向上输入(经照射)表面102D上的第二硼层110-2D。硼层110-1D及110-2D两者参考硼层110的形成(参见图1)而使用上文所描述的技术形成于衬底101D上。尽管硼通过形成具有大约5nm或更小的厚度T3的第二硼层110-2D而确实在UV波长处吸收,但仅小部分入射光子被吸收。此外,由于硼是硅中的p型掺杂剂,因此第二硼层110-2D的存在将趋向于驱动光电子远离经照射表面102D,此用于通过减小电子在经照射表面102D处重新组合的可能性而改进光电阴极100D的效率。可通过在表面102D处的极浅层中植入p型掺杂剂而实现类似结果。因此,在替代实施例(未展示)中,经照射表面102D不含残留硼,且硼(或另一p型掺杂剂)经植入或扩散到经照射表面102D下面的硅衬底101D中。即,尽管硼层110-2D可用于阻止在经照射表面102D上形成氧化物,但经照射表面102D上的氧化物

涂层的存在不需使光电阴极100D的量子效率显著地降级,且在适当选择氧化物厚度的情况下,可有用地减小经照射表面102D在所关注波长下的反射性。

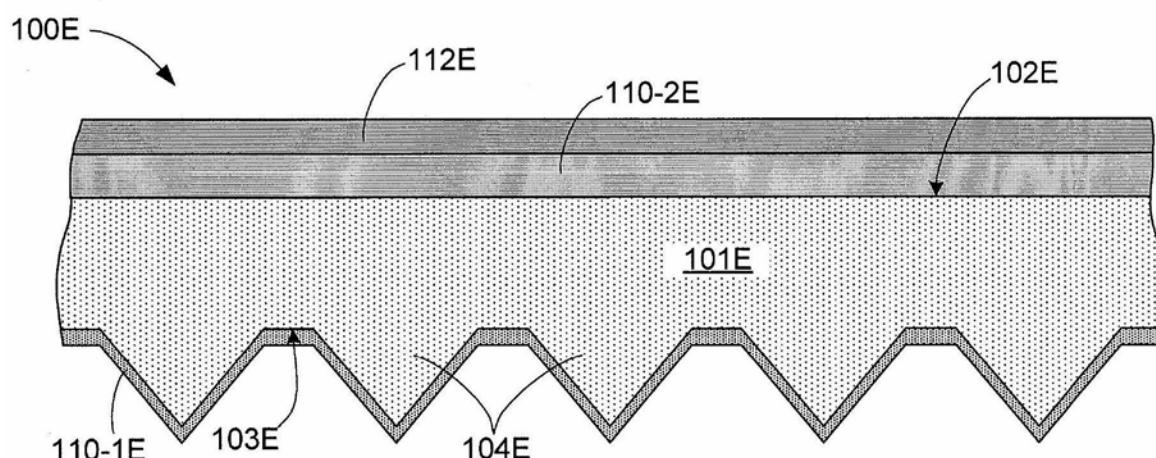

[0054] 图4C描绘光电阴极100E,所述光电阴极包括具有平坦输入(经照射)表面102E的硅衬底101E,安置在相对输出表面103E上的场发射极突出部104E阵列,安置在输出表面103E上、在场发射极突出部104E上方的下部(第一)硼层110-1E,及安置在经照射表面102E上的上部(第二)硼层110-2E,这些均以上文所描述的方式形成。光电阴极100E不同于先前所论实施例,因为其进一步包括安置在上部硼层110-2E上的一或多个抗反射涂层112E。在示范性特定实施例中,抗反射涂层112E是使用对UV及深UV抗反射层有用的材料(包括(但不限于)二氧化硅、氮化硅、氟化镁及二氧化铪)形成。对于在UV波长处需要高量子效率的光电阴极来说,在经照射表面处及接近经照射表面的缺陷的密度及经陷获电荷必须保持为低,这是因为UV光子是接近经照射表面而吸收。如上文所提及,直接涂覆于硅衬底的经照射表面上的任何电介质材料将在所述表面处及在所述电介质的块体内形成缺陷及经陷获电荷,且将使光电阴极的量子效率降级(尤其对于接近于所述表面吸收的深UV波长来说)。通过首先形成上部硼层110-2E作为薄无针孔层(例如,大约2nm到5nm),经照射表面102E保持大体上不含缺陷及经陷获电荷,且光电阴极100D包括由抗反射涂层112E提供的经增强高量子效率。上部硼层110-2E还可至少部分地遮蔽硅衬底101E免受安置在抗反射涂层112E上方的任何额外层中的经陷获电荷。

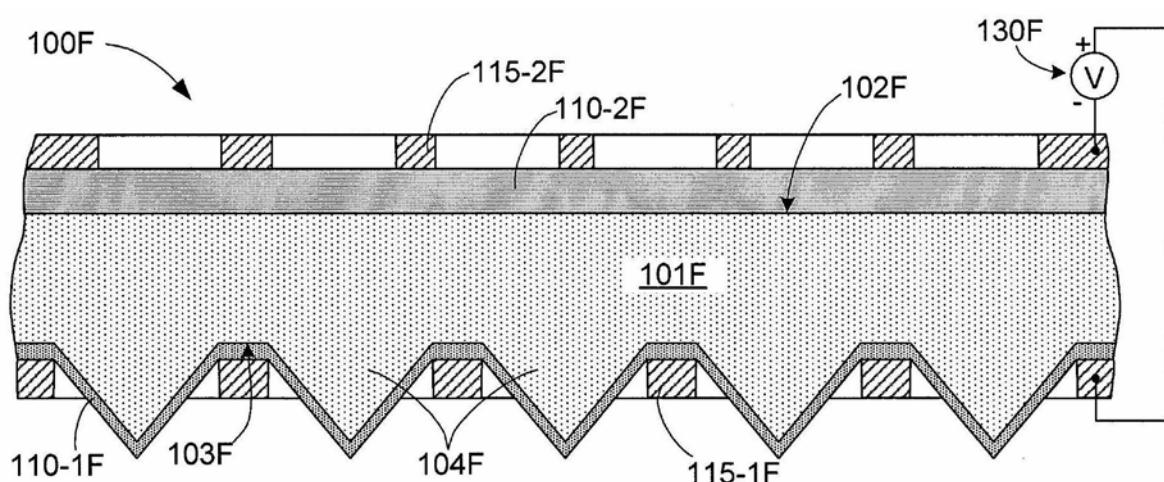

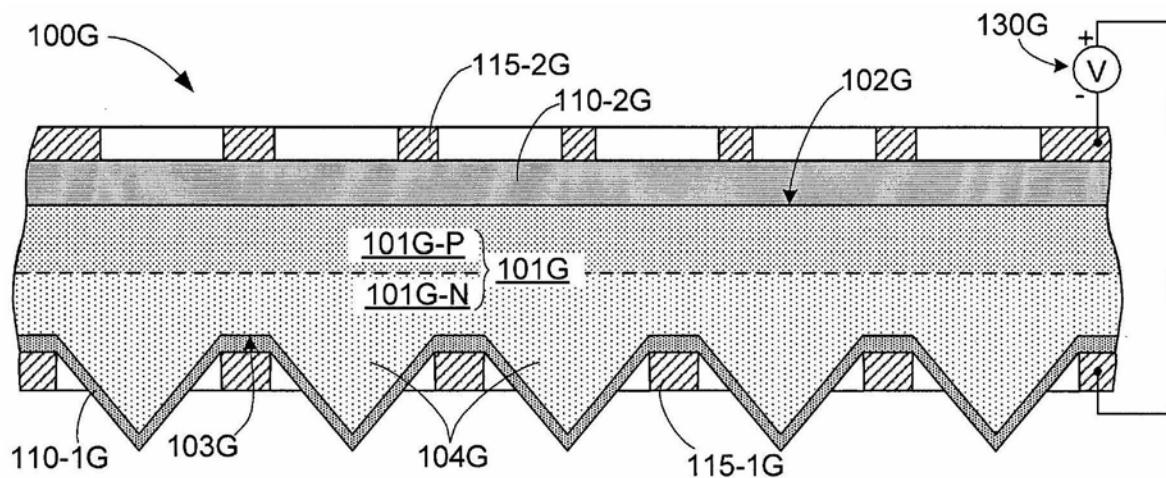

[0055] 图4D描绘光电阴极100F,所述光电阴极包括具有平坦输入(经照射)表面102F的硅衬底101F,安置在相对输出表面103F上的场发射极突出部104F阵列,安置在输出表面103F上、在场发射极突出部104F上方的下部(第一)硼层110-1F,及安置在经照射表面102F上的上部(第二)硼层110-2F,此等全部均以上文所描述的方式形成。光电阴极100F不同于先前实施例之处在在于光电阴极100F包括分别安置在衬底101F的相对侧上的导电结构115-1F及115-2F,当连接到适当外部电压源130F时,导电结构115-1F及115-2F促进跨越硅衬底101F施加外部电位差以便致使在光电阴极100F的操作期间在硅衬底101F中产生的光电子优先地朝向输出表面103F移动。在替代特定实施例中,导电结构115-1F及115-2F包含围绕衬底101F的外围边缘安置的金属边界,或分别安置在下部硼层110-1F及上部硼层110-2F上以确保到衬底101F的相对表面的良好电连接的经稀疏安置金属栅格。由于形成衬底101F的经高度掺杂硅是弱导体,因此在经照射表面102F与输出表面103F之间产生适合电位差(例如,小于大约5V)用于产生穿过输出表面103F的较高光电子流。

[0056] 图4E描绘光电阴极100G,所述光电阴极包括具有平坦输入(经照射)表面102G的硅衬底101G,安置在相对输出表面103G上的场发射极突出部104G阵列,安置在输出表面103G上、在场发射极突出部104G上方的下部(第一)硼层110-1G,及安置在经照射表面102G上的上部(第二)硼层110-2G,此等全部均以上文所描述的方式形成。光电阴极100G不同于先前实施例之处在在于使用已知技术处理硅衬底101G以使其包括p掺杂区域101G-P及n掺杂区域101G-N,所述p掺杂区域及所述n掺杂区域经配置使得经照射表面102G完全安置在p掺杂区域101G-P上且输出表面103G(包括场发射极突出部104G)完全安置在n掺杂区域101G-N上。注意,p掺杂区域101G-P在衬底101G内部邻接n掺杂区域101G-N以形成p-i-n光电二极管结构,且注意,n掺杂区域101G-N致使场发射极突出部104G在光电二极管100G的操作期间实施n型硅场发射极。另外,利用类似于上文参考图4D所描述的导电结构的导电结构115-1G及

115-2G来确保跨越衬底101G的相对表面的外部电压源130G的良好电连接。在此布置的情况下,当源130G在经照射表面102G与输出表面103G之间施加高电压电位(例如,大约几十到数百伏特)时,n型硅场发射极及p-i-n光电二极管结构在雪崩倍增条件下操作。此雪崩增益增强有效量子效率且因此改进光电阴极100G的性能。

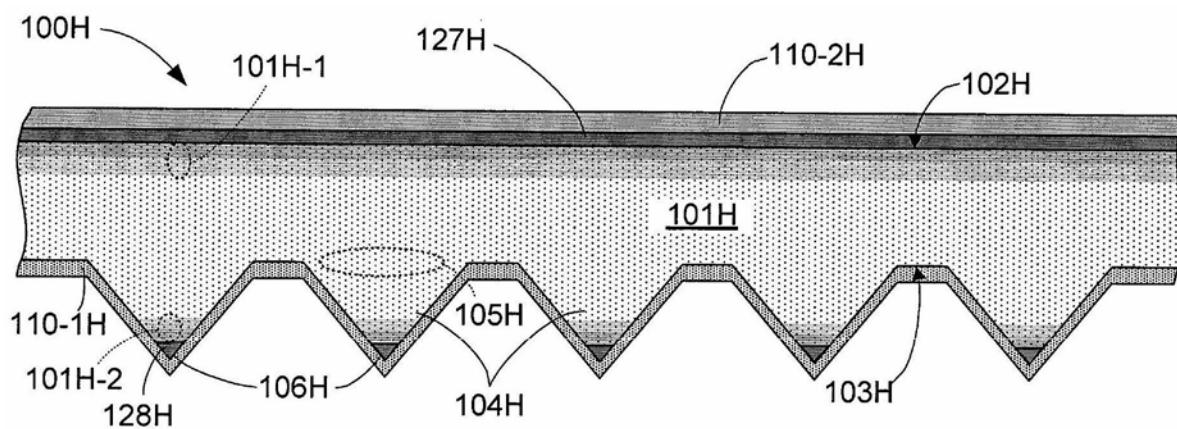

[0057] 图4F描绘光电阴极100H,所述光电阴极包括具有平坦输入(经照射)表面102H的硅衬底101H,安置在相对输出表面103H上的场发射极突出部104H阵列,安置在输出表面103H上、在场发射极突出部104H上方的下部(第一)硼层110-1H,及安置在经照射表面102H上方的上部(第二)硼层110-2H,此等全部均以上文所描述的方式形成。光电阴极100H不同于先前实施例之处在于p型掺杂剂及n型掺杂剂从经照射表面102H及输出表面103H中的一者或两者以产生梯度掺杂区段101H-1及101H-2的方式扩散到衬底101H中,所述梯度掺杂区段邻近硅表面具有相对高掺杂浓度且远离所述表面具有相对轻掺杂浓度。梯度掺杂区段101H-1及101H-2经配置以朝向突出部104H的尖端106H引导(偏置)在硅衬底101H内产生的光电子。在所图解说明实施例中,通过在经照射表面102H与上部硼层110-2H之间形成薄硅化硼层127H而产生梯度掺杂区段101H-1。此布置致使来自硅化硼层127H的一些硼穿过经照射表面102H扩散到硅衬底101H中以形成p型梯度扩散区域101H-1,所述p型梯度扩散区域在接近经照射表面102H的部分中比在安置在衬底101H中、距经照射表面102H更远的部分中具有更高p型掺杂剂浓度(如通过阴影区所指示),借此形成将趋向于驱动电子远离经照射表面102H而到衬底101H中的电位梯度。在省略经照射表面上的硼层的本发明的实施例中,p型掺杂剂(例如硼)从经照射表面植入或扩散到硅中以便形成梯度扩散区域101H-1。类似地,极薄(一个或若干单层)硅化硼层128H形成于场发射极突出部104H的尖端部分106H与下部硼层110H-1之间,借此一些硼扩散一短距离到硅中以形成梯度扩散区域101H-2(通过阴影所指示)。在一些实施例中,梯度扩散区域101H-2可包含其它p型或n型掺杂剂,所述掺杂剂经植入到硅中以便修改接近突出部104H的尖端部分106H的电场梯度。

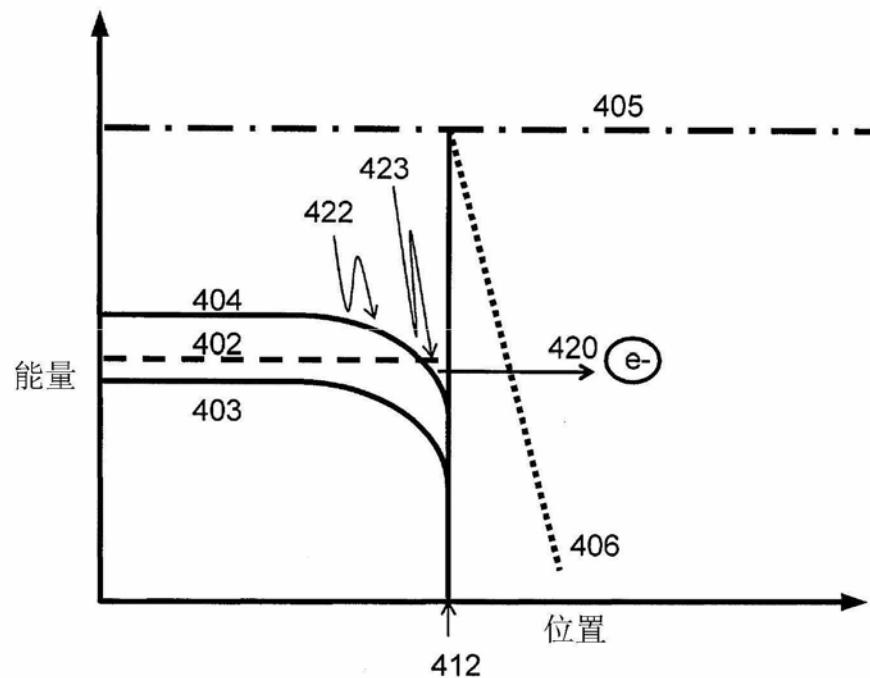

[0058] 图5是图解说明根据上文所描述的实施例形成的示范性发明性光电阴极的电子场发射的示范性能量图式。垂直方向表示能量。注意,此图并非按比例的,所述图经变形且一些方面经夸大以便更清楚地图解说明光电阴极的关键方面。虚线402表示光电阴极内的费米能级。线403表示半导体内的价带的顶部。线404表示传导带的底部。传导带的底部与价带的顶部之间的差被称为能带间隙。对于硅来说,能带间隙是大约1.1eV,但能带间隙在掺杂剂浓度为高处减小。点虚线405表示真空能量水平。真空区域中的小虚线406表示具有位于大距离(例如大于数微米的距离)处的阳极(未展示)的场发射极的电位分布。通过标记412指示场发射极突出部的尖端的位置。

[0059] 光电阴极的经照射表面(未展示)是从明确掺杂或从来自表面硼涂层(未展示,这是因为如果存在,那么所述表面硼涂层仅为几nm厚)的硼的扩散,或从所述两者的组合而经重p掺杂的。由于接近表面的重p型掺杂,因此费米能级刚刚超过价带的顶部。举例来说,对于高的硼掺杂水平来说,费米能级与价带的顶部之间的间隙可小到大约0.05eV。随着掺杂剂浓度远离表面而降低,费米能级与价带的顶部之间的间隙增加,从而致使传导带及价带远离表面而向下弯曲,如通过箭头420所指示。

[0060] 当通过吸收光子而形成自由电子时,所述电子将处于传导带中。所述电子最初以大约等于光子能量与能带间隙之间的差的能量而形成。在硅中,过量能量通常迅速损失,使

得电子迅速达到接近于传导带的底部的能量。由于传导带中的向下斜率接近于经照射表面,因此接近所述表面形成的任何电子均将迅速移动远离所述表面且不可能在存在于经照射硅表面上或接近经照射硅表面的任何缺陷处重新组合。由于深UV光子极可能在几nm经照射硅表面内被吸收,因此深UV波长处的光电阴极的高量子效率通过接近表面的此掺杂剂轮廓而变得可能。

[0061] 可通过众所周知的福勒-诺得海姆穿隧来描述来自硅场发射极的场发射。与所施加电场相比,发射极尖端处的局部场是通过场增强因子而增强。当外部电场穿透到半导体中时,近表面区域中的载子浓度改变,且传导带404及价带403两者在发射极表面处弯曲,如通过标记422所指示。

[0062] 如果通过足以使传导带404的底部低于费米能级402的能量弯曲传导带,那么在如423处所描绘的下沉中收集电子。收集的最高填充能级与费米能级402一致,此贯穿半导体的块体保持恒定。当电子朝向光电阴极表面412移动时,外部场使电子加速且允许电子以足以具有高逸出概率的能量到达表面412。

[0063] 对于例如 $10^7$ V/cm的高静电偏置场来说,p型场发射极的传导带将在表面处退化,且在p型内部与n型表面之间形成其中费米能级402位于能隙的中间的耗尽区域。此导致此区域中的电子及空穴的最小浓度,此类似于经反向偏置p-n接面的情形。

[0064] 在基于硅的现有技术光电阴极中,将在硅表面上存在薄氧化物层。即使仅约2nm厚,此氧化物也表示对试图逸出的任何电子的巨大势垒。二氧化硅的能带间隙为大约8eV。此大能带间隙导致传导带中的局部峰值,所述局部峰值比硅内的传导带高数eV。光电阴极表面上的硼层阻挡氧或水到达硅表面且阻止生长氧化物层,因此实现高效光电阴极。

[0065] 图6A到6C是展示根据替代特定实施例的各种传感器结构的简化横截面图,其中传感器实施例中的每一者包括根据上文所陈述的实施例中的至少一者的发明性光电阴极结构,借此提供可(举例来说)用于半导体检验系统中的具有优越低光感测能力的传感器。尽管图6A到6C中所展示的经简化传感器结构与EBCCD型传感器一致,但应理解,所描绘传感器结构还可适用于其它传感器结构(例如,图像增强器及光电倍增管传感器)。

[0066] 图6A以横截面图解说明根据本发明的第一传感器实施例的传感器200A。传感器200A大体来说包括上文所描述的硅光电阴极100,检测装置210(例如,CCD或CMOS图像传感器),及壳体202A,所述壳体可操作地连接于光电阴极100与检测装置210之间,使得检测装置210的检测表面212通过介入间隙区域206与光电阴极100的下部硼层110分离。光电阴极100邻近于传感器200A的接收表面203A安置且经布置使得经照射表面102背对检测装置210,借此将光电阴极100定向以接收辐射(例如,光子P)且跨越介入间隙区域206将光电子PE发射到检测装置210。如上文参考图1所陈述,光电阴极100是通过具有一体地形成于(例如,单晶)硅衬底101的输出(第二)表面103上的发射极突出部104及安置在输出表面103上的硼(第一)层110而表征。类似于大部分CCD及CMOS图像传感器装置,检测装置210包括用于检测光电子PE的感测结构及用于响应于所检测到的光电子而产生电信号S(例如,通过一或多个输出引脚217)的电路。

[0067] 根据所图解说明实施例的方面,光电阴极100接合到或以其它方式气密密封到不导电或高度电阻性玻璃或陶瓷窗204A,所述窗结合壳体202A的侧壁及其它部分形成其内部被抽空(即,间隙区域206大体上填充有真空)的包络层。在一个特定实施例中,通过围绕光

电阴极100的边缘安置的二氧化硅层而形成窗204A与光电阴极100之间的接合。在一些实施例中,光电阴极100的硅衬底101可为几十微米到几百微米厚。此类厚度足够强以在光电阴极的顶部上不具有任何窗的情况下耐受来自外部的大气压力。适合于在形成窗204A时使用的材料包括熔融硅石、石英、氧化铝(蓝宝石)、氟化镁及氟化钙。

[0068] 根据第一传感器实施例的另一方面,传感器200包括导电结构(例如,类似于上文参考图4D及图4E所描述的栅格结构),所述导电结构可操作地安置在光电阴极100及检测装置210上或邻近于光电阴极100及检测装置210而安置,使得当适合电压供应器220可操作地耦合到传感器200A时,电场在光电阴极100与检测装置210之间产生,所述电场用于将从光电阴极发射的电子112朝向检测装置210加速到间隙区域206中。在一些实施例中,如上文参考图4D及图4E所阐释,光电阴极100的输出表面103通过第二电压源(未展示)而相对于照射表面102保持处于正电位。当辐射(光子)被吸收时,光电阴极100发射电子,且发射到间隙区域206中的光电子朝向检测装置210加速,这是因为光电阴极100D通过电压源220而相对于检测装置210保持处于负电位。在优选实施例中,由电压源220产生的电位差处于大约100V到大约1500V的范围内。

[0069] 图6B展示根据第二传感器实施例的传感器200B,所述传感器包括光电阴极100D,形成于(第二)硅衬底211C上的检测装置210B(例如,CCD或CMOS图像传感器),及将光电阴极100B维持于距检测装置210B固定距离处的壳体202。如上文参考图4C所描述,光电阴极100D是通过包括直接安置在硅衬底101的经照射(第一)表面102上的第二硼层(第三层)110-2及安置在第二硼层110-2上的抗反射材料(第四)层112而表征。在此实施例中,壳体202B不包括安置在光电阴极100上面的窗,因此通过抗反射材料(第四)层112的外(上部)表面而形成传感器200B的接收表面203B。因此,归因于无由于通过窗的反射或吸收所致的损失,传感器200B具有比有窗的传感器更敏感(即,能够检测较低量的光)的优点。如此,传感器200B呈现从近红外线波长到X射线波长的相对高敏感性。

[0070] 图6C展示根据第三传感器实施例的传感器200C,所述传感器包括光电阴极100及形成于(第二)硅衬底211C上的硅基检测装置210C(例如,CCD或CMOS图像传感器),所述硅衬底以类似于上文参考图6A所描述的方式紧固到壳体202C。

[0071] 根据第三传感器实施例的方面,壳体202C包括安置在光电阴极100上方的上部窗部分204C,且抗反射材料层207C形成于窗204C上以便改进通过传感器200C进行的光子俘获。在替代实施例中,额外抗反射材料层(未展示)安置在光电阴极100与窗204C之间(即,使用(举例来说)上文参考图4C所描述的光电阴极100D来实施光电阴极100)。

[0072] 根据第三传感器实施例的另一方面,使用上文参考光电阴极100所描述的技术在图像传感器210C的检测(上部)表面212上直接形成(第三)硼涂层214C以实现通过图像传感器210C的电子(其从光电阴极100发射)的高效吸收。在优选实施例中,光电阴极100与图像传感器210C之间的间隙距离G介于大约100μm与大约1mm之间。由于硼涂层214C改进针对低能量电子的图像传感器210C的效率,因此可使用比现有技术装置中典型的低的加速电压及比其小的间隙。更低加速电压及更小间隙的优点是传感器的空间分辨率得以改进且响应时间得以减少(即,最大操作频率得以增加)。硅光电阴极内的光电子的热化还改进图像传感器的空间分辨率。

[0073] 在本发明的其它实施例中,晶片、光罩或光掩模检验系统包括:照射源(例如,激光

系统),其用于将光(光子)发射到样本/晶片上;传感器(例如,光电信增管、图像增强器或EBCCD),其利用上文所描述的发明性光电阴极中的任一者来检测通过样本/晶片或由样本/晶片反射的光子;及相关联光学系统,其用于将光/光子从所述照射源导引到所述样本(晶片、光罩或光掩模)且从所述样本导引到所述传感器。这些实施例的实例在图6到10中展示。

[0074] 图7展示具有暗场及明场检验模式的检验系统300A的关键组件。由系统300A利用的光学器件包含高数值孔径大视场物镜128、用于设定或调整放大率的镜筒透镜139,及检测器200,所述检测器并入有根据上文所描述的实施例中的任一者构造的光电阴极。当在暗场模式中操作时,检测器200在类似于图6A到6C中的任一者中所展示的布置的EBCCD或图像增强器布置中并入有发明性光电阴极。关于此检验系统的其它方面的更多细节可存在于美国专利7,345,825中,所述美国专利以其全文引用的方式并入本文中。

[0075] 图8A到8D图解说明根据本发明的其它示范性实施例的并入有发明性光电阴极的暗场检验系统的方面。在图8A中,检验系统300B-1通过光14照射线18,光14通过包含透镜或镜12的光学器件11到正被检验的晶片或光掩模(样本)的表面20上。收集光学器件21使用例如22a及22b的透镜及/或镜将经散射光从所述线引导到传感器200。收集光学器件的光学轴28并不在线18的照射平面中。在一些实施例中,轴28大致垂直于线18。传感器200是并入有(举例来说)根据图6A、6B及6C中的任一者中所图解说明的实施例的发明性光电阴极的阵列传感器,例如线性阵列传感器。图8B、8C及8D图解说明多个暗场收集系统(分别是300B-2、300B-3及300B-4)的替代布置,所述暗场收集系统并入有结合例如图8A中所展示的线照射的线照射的具有发明性光电阴极的检测器200。此类检验系统的更多细节可存在于美国专利7,525,649中,所述美国专利以其全文引用的方式并入本文中。美国专利6,608,676(其还以其全文引用的方式并入本文中)还描述适合于未经图案化或经图案化晶片的检验的线照射系统。

[0076] 图9展示根据本发明的另一示范性实施例的并入有发明性光电阴极的未经图案化晶片检验系统300C。来自激光器1014的光借助于偏振光学器件1016、光束成形光学器件1020以及例如1022及1024的转向镜而引导到晶片1012。通过例如1038及1032的镜及透镜收集从晶片散射的光且将所述光发送到并入有根据上文所描述的实施例中的任一者构造的光电阴极的检测器200-1及200-2。在一些实施例中,检测器200-1及200-2包含并入有发明性光电阴极的光电信增管。关于未经图案化晶片检验系统的更多细节可存在于美国专利6,271,916中,所述美国专利以其全文引用的方式并入本文中。

[0077] 图10展示根据本发明的另一替代实施例的泛光照射晶片检验系统300D。通过离轴光源照射晶片(样本)的一区。从晶片散射的光通过收集物镜收集,通过一或多个孔口、分离器及偏振器且接着经引导到一或多个图像传感器200-1及200-2,所述一或多个图像传感器并入有根据上文所描述的实施例中的任一者构造的光电阴极。在一些实施例中,图像传感器200-1及200-2包含并入有发明性光电阴极的EBCCD或图像增强器。此检验系统的更多细节可存在于罗曼诺夫斯基(Romanovsky)等人的标题为“晶片检验(Wafer Inspection)”的共同拥有且同在申请中的美国专利申请案第13/544,954号(公开为2013/0016346)中,所述美国专利申请案以其全文引用的方式并入本文中。在此类检验系统实施例中,晶片优选地在检验期间连续移动。本发明的此实施例中所使用的图像传感器可有利地并入有以下各项中所描述的技术中的任一者:标题为“使用EBCCD检测器的电子轰击电荷耦合装置及检验系

统 (Electron-Bombarded Charge-Coupled Device And Inspection Systems Using EBCCD Detectors)”的共同拥有且同在申请中的美国专利申请案第13/710,315号(公开为2013/0148112),及标题为“使用脉冲式照明来高速获取移动图像的方法及设备 (Method and apparatus for high-speed acquisition of moving images using pulsed illumination)”的共同拥有且同在申请中的美国专利申请案第14/096,911号(公开为2014/0158864),所述美国专利申请案两者均以其全文引用的方式并入本文中。

[0078] 图11展示根据本发明的另一替代实施例的晶片检验系统300E。检验系统300E包括通过所图解说明光学系统提供不透明照射及大体上法向照射的照射子系统110E,检验系统300E收集经散射光且穿过各种孔口及偏振分束器将所述光引导到多个传感器200-1到200-5,所述传感器并入有根据上文所描述的实施例中的任一者的发明性光电阴极。晶片检验系统300E及可有利地使用并入有本文中所揭示的光电阴极的检测器的晶片检验系统的其它方面的更多细节可存在于由赵 (Zhao) 等人在2011年12月7日提出申请的标题为“晶片检验 (Wafer Inspection)”的且以引用的方式并入本文中的美国专利申请案13/822,281中。

[0079] 现有技术图像增强器及电子轰击CCD必须在敏感性与光谱频带宽度之间进行折衷。在最好的情况下,良好敏感性仅针对窄波长范围是可能的。通过使得能够使用硅作为光电阴极,本发明允许在较宽波长范围内的高敏感性。此外,由于发明性光电阴极的高效率及高电流发射,因此图像增强器、光电倍增管及电子轰击CCD在一些实施例中可以较低加速电压操作,此继而改进装置寿命且增加最大操作频率及/或空间分辨率。

[0080] 现有技术硅光电阴极在每一表面上具有氧化物层,此阻碍光电子的逸出且导致低效率。通过在硅的输出表面上形成硼层允许电子更容易地逸出,从而导致更高效率。表面上的场发射极阵列进一步增强效率。

[0081] 组合发明性光电阴极与经硼涂覆CCD或CMOS图像传感器的图像传感器呈现光电阴极中的较高量子效率与经硼涂覆CCD的增加的敏感性组合。

[0082] 并入有具有发明性光电阴极的检测器的暗场检验系统具有不可运用常规图像及光传感器实现的高效率、极低噪声水平与高速操作的组合。

[0083] 尽管已关于一些特定实施例描述本发明,但所属领域的技术人员将清楚本发明的发明性特征还可适用于其它实施例,所有所述实施例均打算归属于本发明的范围内。

图1

图2A

图2B

图3

图4A

图4B

图4C

图4D

图4E

图4F

图5

图6A

图6B

图6C

图7

图8A

图 8B

图 8C

图 8D

图9

图10

图11

图12现有技术