(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6199876号

(P6199876)

(45) 発行日 平成29年9月20日(2017.9.20)

(24) 登録日 平成29年9月1日(2017.9.1)

(51) Int.Cl.

F 1

B 41 J 2/14 (2006.01)

B 41 J 2/045 (2006.01)B 41 J 2/14 6 1 1

B 41 J 2/14 3 0 1

B 41 J 2/045

請求項の数 17 (全 17 頁)

(21) 出願番号 特願2014-542936 (P2014-542936)

(86) (22) 出願日 平成24年11月23日 (2012.11.23)

(65) 公表番号 特表2015-501740 (P2015-501740A)

(43) 公表日 平成27年1月19日 (2015.1.19)

(86) 國際出願番号 PCT/GB2012/052914

(87) 國際公開番号 WO2013/076510

(87) 國際公開日 平成25年5月30日 (2013.5.30)

審査請求日 平成27年11月13日 (2015.11.13)

(31) 優先権主張番号 1120228.0

(32) 優先日 平成23年11月23日 (2011.11.23)

(33) 優先権主張国 英国(GB)

(73) 特許権者 511270653

インカ・デジタル・プリンターズ・リミテッド

イギリス国ケンブリッジシャー・シービー

1・3ジェイエス, ケンブリッジ, コール

ドハムズ・レーン 515

(74) 代理人 100116850

弁理士 廣瀬 隆行

(74) 代理人 100165847

弁理士 関 大祐

(72) 発明者 クリア, ハミルトン ブキャナン

イギリス国, シービー1・3ジェイエス

ケンブリッジシャー, ケンブリッジ, コー

ルドハムズ・レーン 515, インカ・デ

ジタル・プリンターズ・リミテッド内

最終頁に続く

(54) 【発明の名称】 インクジェットプリントヘッドのドライバ回路および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

インクの滴を噴出するためにプリントヘッド(10)に繰り返し電圧を印加するための駆動回路であって、前記プリントヘッドは、各々が個別のキャパシタンスを有する複数のノズル流路を有し、

前記駆動回路は、

少なくとも1つのノズル流路の前記キャパシタンスを所望の動作電圧まで充電するための電流用の充電経路を提供するために、第1のインダクタ(L1)を介して、前記プリントヘッドの駆動接続部を電力供給部(V1)の第1の接続に結合するように接続された第1の切り替え素子(S1)と、

前記少なくとも1つのノズル流路の前記キャパシタンスを所望のパルス間電圧まで放電するための電流用の放電経路を提供するために、第2のインダクタ(L2)を介して、前記プリントヘッドの駆動接続部を前記電力供給部(V1)の第2の接続に結合するように接続された第2の切り替え素子(S2)と、を備える、

駆動回路であって、

前記駆動回路は、前記第2のインダクタ(L2)と前記電力供給部の前記第1の接続との間に接続された第3の切り替え素子(S3)を備え、

前記駆動回路は、一方向のみの電流の流れを可能にし、前記第2のインダクタ(L2)と前記電力供給部の前記第1の接続との間に直列に接続された、第3の回路素子(D3)を備える、

10

20

駆動回路。

**【請求項 2】**

前記所望の動作電圧は、前記電力供給部の電圧より高い、

請求項 1 に記載の駆動回路。

**【請求項 3】**

前記駆動回路は、一方向のみの電流の流れを可能にし、前記第 1 のインダクタ (L 1) と前記プリントヘッドの駆動接続部との間に直列に接続された、第 1 の回路素子 (D 1) を備える、

請求項 1 または 2 に記載の駆動回路。

**【請求項 4】**

前記駆動回路は、一方向のみの電流の流れを可能にし、前記第 2 のインダクタ (L 2) と前記プリントヘッドの駆動接続部との間に直列に接続された、第 2 の回路素子 (D 2) を備える、

請求項 1 から 3 のいずれかに記載の駆動回路。

**【請求項 5】**

前記駆動回路は、前記第 1 のインダクタ (L 1) と前記電力供給部の前記第 2 の接続との間に接続された第 4 の切り替え素子 (S 4) を備える、

請求項 1 から 4 のいずれか一項に記載の駆動回路。

**【請求項 6】**

前記駆動回路は、一方向のみの電流の流れを可能にし、前記第 1 のインダクタ (L 1) と前記電力供給部の前記第 2 の接続との間に直列に接続された、第 4 の回路素子 (D 4) を備える、

請求項 1 から 5 のいずれか一項に記載の駆動回路。

**【請求項 7】**

前記駆動回路は、一方向のみの電流の流れを可能にし、前記第 2 のインダクタ (L 2) と前記電力供給部の前記第 2 の接続との間に直列に接続された、第 5 の回路素子 (D 5) を備える、

請求項 1 から 6 のいずれか一項に記載の駆動回路。

**【請求項 8】**

前記駆動回路は、略完全にオンと完全にオフとの直接的な切り替えを提供するための前記切り替え素子 (S 1、S 2、S 3、S 4) 用の波形を駆動するための制御配置 (90) を備え、前記オンとオフとの切り替えの時間は、電流が前記第 1 のインダクタ (L 1) に流れる時間に基づいて、所望の駆動電圧を提供するように、選択される、

請求項 1 から 7 のいずれか一項に記載の駆動回路。

**【請求項 9】**

前記制御配置 (90) は、所望の電圧に基づいて、前記第 4 の切り替え素子 (S 4) が使用されるブーストモードとノーマルモードとを切り替えるように配置され得る、

請求項 5 に従属する 請求項 8 に記載の駆動回路。

**【請求項 10】**

プリントヘッド駆動端子 (30) が、複数のノズル流路への電力供給部に接続され、前記ノズル流路は、電流戻り経路 (50) に接続され、前記複数のノズル流路の各々は、それぞれのノズル切り替え素子 (S n 1、S n 2、S n 3、S n 4) と直列に接続される、

請求項 8 または 9 のいずれか一項に記載の駆動回路。

**【請求項 11】**

前記ノズル流路の前記電流戻り経路は、第 2 の電力供給接続 (60) に結合される、

請求項 10 に記載の駆動回路。

**【請求項 12】**

前記制御配置は、個々のノズル切り替え素子についての情報に基づいて噴射しているノズル流路の数、または、所与の駆動パルスのためのアクティブなノズル流路の数の計測に依存して、前記駆動回路を調節するように配置される、

10

20

30

40

50

請求項 10 または 11 のいずれか一項に記載の駆動回路。

【請求項 13】

前記駆動回路は、駆動出力における少なくとも 1 つのインダクタを有し、前記駆動回路は、アクティブなノズルの数に伴う負荷キャパシタンスの変化を減じるために、前記プリントヘッド (10) および駆動端子にわたって並列な少なくとも 1 つの補償コンデンサ (Cc1、Cc2、Cc3) を有する、

請求項 1 から 12 のいずれか一項に記載の駆動回路。

【請求項 14】

複数の個々に切り替えられるノズル流路に、請求項 1 に記載の駆動回路を介して、駆動電力パルスを供給する方法であって、

10

前記方法は、

a ) 所与の駆動パルスのためにアクティブであることが期待されるプリントヘッドの前記ノズル流路の数の計測を決定するステップと、

b ) ノズル流路のキャパシタンスの変化を補償するために前記駆動回路が前記駆動パルスを発生させるために前記駆動回路に制御パラメータを提供するステップと、を備える、方法。

【請求項 15】

c ) 前記駆動回路用のタイミング信号を調節するステップをさらに備える、

請求項 14 に記載の方法。

【請求項 16】

d ) 測定されたノズル流路電圧に基づいて前記タイミング信号を調節するステップをさらに備える、請求項 15 に記載の方法。

20

【請求項 17】

請求項 1 に記載の駆動回路であって、

各々がキャパシタンスを有する前記プリントヘッド用の補償回路をさらに含み、

前記複数のノズル流路が、共通の駆動接続に接続されると共に、個々のノズル制御切り替え素子と直列に接続されており、前記補償回路は、アクティブなノズル流路の数の変化に伴う駆動回路に提示される全キャパシタンスの変化を減じるために前記駆動接続に接続された補償キャパシタンス配置を備える、

駆動回路。

30

【発明の詳細な説明】

【技術分野】

【0001】

インクジェットプリンタのためのプリントヘッドは典型的に、圧電性である。圧電素子はキャパシタンスを有し、インク滴を噴出するために固有回路抵抗によって所望の電圧までこのキャパシタンスを急速に充電および放電する際、エネルギーが典型的に消散する。これらの問題は、著しい電力が消散する高速で高容量のプリントヘッドにおける問題であり、エネルギーの浪費と冷却の問題の両方を招く。プリントヘッドの大きなアレイを駆動するシステムにおいて、この電力の消散は、エネルギーを提供するための大きなDC電力供給と無駄な熱を消散させるための大きなヒートシンクとを必要とする、著しいものであり得る。

40

【背景技術】

【0002】

単一のピエゾアクチュエータのような容量性負荷を駆動するための誘導性エネルギー回収回路が、Efficient Charge Recovery Method for Driving Piezoelectric Actuators with Quasi-Square Waves by Domenico Campolo, Metin Sitti, and Ronald S. Fearing (IEEE Trans. On Ultrasonics, Ferroelectrics, And Fre

50

quency Control, Vol. 50, No. 1, January 2003)において説明されている。

電気理論において周知であるように、エネルギーは(電流が流れることに応じてエネルギーを蓄積する)インダクタとコンデンサとの間でリサイクルされ得るので、圧電素子のための駆動回路にインダクタンスを組み込むことが提案されている。しかしながら、理論上の回路が実際的なプリントヘッドに適用される場合、問題が生じることが分かる。所望の急速な充電および放電を、望ましくないリングングなしに達成することには問題が多く、パルス繰り返しレートが悪影響を受け得る(プリンタにおいて、言い換えると、解像度の減少または印刷時間の増加ということになる)。また、プリントヘッドにおいて、インダクタを追加することは、プリントヘッド電圧が変動し得るので、印刷の均一性を減じ得ることが分かる。10

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Efficient Charge Recovery Method for Driving Piezoelectric Actuators with Quasi-Square Waves by Domenico Campolo, Metin Sitti, and Ronald S. Fearing (IEEE Trans. On Ultrasonics, Ferroelectrics, And Frequency Control, Vol. 50, No. 1, January 2003)

【発明の概要】

【0004】

本発明は、インクの滴を噴出するためにプリントヘッドに繰り返し電圧を印加するための駆動回路を提供し、このプリントヘッドは、それぞれのキャパシタンスを各々が有する複数のノズル流路を有し、この駆動回路は、少なくとも1つのノズル流路のキャパシタンスを所望の動作電圧まで充電するための電流用の充電経路を提供するために、第1のインダクタを介して、電力供給部の第1の接続にプリントヘッドの駆動接続を結合するよう接続された第1の切り替え素子と、上記少なくとも1つのノズル流路のキャパシタンスを所望のパルス間電圧まで放電するための電流用の放電経路を提供するために、第2のインダクタを介して、第2の接続にプリントヘッドの駆動接続を電力供給部の結合するために接続された第2の切り替え素子と、を備える。30

【0005】

充電および放電フェーズのための別個のインダクタとともに別個の切り替え素子を提供することにより、抵抗損失におけるエネルギーの消散なしに高いパルス繰り返しレートが達成され得ることが分かっている。別個のインダクタは充電および放電フェーズの重複を可能にすることことができ、各々がより正確に制御され得る。単一のインダクタを有する回路の変化の1つの原因是、蓄積されるエネルギーが、ヘッドのキャパシタンスの変化に部分的に起因して、パルス間で不定な状態であり得るからであることが分かっている。充電および放電のための別個のインダクタにより、既知の状態の充電経路を有することがより容易である。インダクタのペアのこの使用は、より高いパルス繰り返し周波数の達成を可能にし、寄生キャパシタンスが存在する際のより安定した動作を可能にしながら、電圧パルスのタイミングのより高い柔軟性を提供する。明らかであるように、インダクタのペアのこの使用は、他の圧電装置のための制御回路に適用され、同一の利点から利益を得ることができる。40

【0006】

インダクタは、充電および放電について異なり得る、所望の傾きの時間を与えるために、異なる値のものであることができ、プリントヘッドの物理的特性に合わせられ得る。さらに、インダクタとコンデンサとの相互作用が、コンデンサを電力供給電圧より高い電圧まで充電することを可能にできるが、それは充電回路が電圧二倍器として機能し得るから50

であり、これは別個の電圧昇圧回路の必要を回避する。一例に過ぎないが、約90ボルトの典型的なプリントヘッド駆動電圧は、48ボルトのバス電圧から直接発生させられることができる。

#### 【0007】

一実施形態において、回路は、供給レールの電圧より高い、持続した電圧を発生させることができる。1つの実現では、一方向のみの電流の流れを可能にする回路素子が、電圧二倍器の動作を容易にするために、第1のインダクタとプリントヘッド駆動接続との間に直列に接続される。この回路素子は、電流遮断装置の役割を果たし、ダイオードとして回路に実装され得る。この装置は、充電経路の電流が少なくとも1つのノズル流路のキャパシタンスへと流れることを可能にする。電流遮断装置の使用は回路に、(供給レール電圧より低い電圧がいくつかの実現において実際には発生させられ得るが)回路の供給レール電圧より高い、容量性負荷での電圧を持続することを可能にさせる。

10

#### 【0008】

ダイオードが特に、電流遮断機能を実現するのに有利であり得る。特に、ダイオードは、特別な制御を必要とせず、その低い寄生キャパシタンスは、回路の効率的な動作を可能にし得る。しかしながら、トランジスタまたはFETといった他の電流遮断素子もまた、いくつかの実現において使用されることができる。

#### 【0009】

第2のダイオードのような一方向のみの電流の流れを可能にするさらなる回路素子が、好ましくは、第2のインダクタからの逆方向の電流の流れを抑止するために、第2のインダクタとプリントヘッド駆動接続との間に直列に接続される。第2のダイオードは、放電経路の電流が少なくとも1つのノズル流路のキャパシタンスから流れ出ることを可能にする。

20

#### 【0010】

好ましくは、駆動回路はさらに、第2のインダクタと電力供給部の第1の接続との間に接続された第3の切り替え素子を備える。これは、第2のインダクタに蓄積されたエネルギーのためのフライバック電流経路を可能にし、それにより効率を向上させる。

#### 【0011】

第3のダイオードのような一方向のみの電流の流れを可能にする追加の回路素子が、好ましくは、フライバック動作を容易にするために、第2のインダクタと第1の電力供給接続との間に直列に接続される。第3のダイオードは、放電経路の電流が第1の電力供給接続に流れ戻ることを可能にする。

30

#### 【0012】

好ましくは、駆動回路はさらに、第1のインダクタと電力供給部の第2の接続との間に接続された第4の切り替え素子を備える。これは、エネルギーを蓄積するために第1のインダクタに(増大した)電流を流すことによりブーストを提供して、電力供給電圧の2倍より高い電圧へのブーストを達成するために、使用されることがある。

#### 【0013】

第4のダイオードのような一方向のみの電流の流れを可能にする追加のさらなる回路素子が、好ましくは、ブースト動作を容易にするために、第1のインダクタと第2の電力供給接続との間に直列に接続され、第1のスイッチが開かれた場合に電流が流れることを可能にして、接地基準を提供する(第2の電力供給接続が接地または他の電位であるとみなされると仮定する)。第4のダイオードは、電流が第2の電力供給接続から第1のインダクタに流れることを可能にする。

40

#### 【0014】

第5のダイオードのような一方向のみの電流の流れを可能にする追加のさらなる回路素子が、好ましくは、より高い電圧からの放電動作を容易にするために、第2のインダクタと第2の電力供給接続との間に直列に接続され、第2のインダクタにおける電流が第1の電力供給接続に流れることを可能にする。第5のダイオードは、電流が第2の電力供給接続から第2のインダクタに流れることを可能にする。

50

## 【0015】

切り替え素子は、トランジスタ、特に電界効果トランジスタ、であることができる。好ましくは、制御配置が、略完全にオンと完全にオフとの直接的な切り替えを提供するための切り替え素子のための駆動波形を提供し、オンとオフとの切り替え時間は、第1のインダクタに電流が流れる時間に基づいて、所望の駆動電圧を提供するように、選択される。

## 【0016】

第4の切り替え素子が提供される場合、制御配置は、所望の電圧に基づいて、第4の切り替え素子が使用されるブーストモードとノーマルモードとを切り替えるように、配置され得る。これは、選ばれた動作方式に基づくことができ、所与の電圧が両方のモードで達成可能であるが、一方のモードで動作するほうが、もう一方のモードで動作するより効率的である、ということが分かり得る。

10

## 【0017】

好ましくは、プリントヘッド駆動端子が、複数のノズル流路への電力供給部に接続され、このノズル流路は、典型的には第2の電力供給接続に結合される、戻り経路に接続され、複数のノズル流路の各々は、それぞれのノズル切り替え素子と直列に接続される。このように、電力回路が全てのノズル流路のために反復される必要はなく、ヘッド全体のための、またはさらにはいくつかのヘッドのための、1つの電力回路が存在することができ、ノズルの印刷は、ノズル切り替え素子によって制御される。ノズル切り替え素子は、より小型であることができ、ノズル切り替え素子における消散を減じるために、電力が駆動回路から駆動接続によって供給されていない時間においてのみ切り替わるように配置され得る。

20

## 【0018】

好ましくは、制御配置は、個々のノズル切り替え素子についての情報に基づいて噴射しているノズル流路の数、または、所与の駆動パルスのためのアクティブなノズル流路の数の計測に依存して、駆動回路を調節するように配置される。これは、合計キャパシタンスの変化に影響を受けない均一な印刷の達成を可能にし得る。この特徴は、所与のパルスのためのアクティブなノズル流路の数の計測に基づいて駆動回路のパラメータを調節する手段によって特徴付けられる、複数の個々に切り替えられるノズル流路に駆動電力パルスを供給するように配置された、プリントヘッド用の駆動回路において、独立して提供され得る。

30

## 【0019】

好ましくは、駆動回路は、駆動出力における少なくとも1つのインダクタを有し、駆動回路は、アクティブなノズルの数に伴う負荷キャパシタンスの変化を減じるために、プリントヘッドおよび駆動端子にわたって並列な少なくとも1つの補償コンデンサを有する。それは単にプリントヘッドを駆動するために必要とされる電力を増加させるに過ぎないから、これは、ノーマルな回路では、反直観的であろう。しかしながら、インダクタと共にそれが存在することは、タイミングを安定させる利点を提供し、それは、この欠点より重要である。

## 【0020】

関連する態様において、本発明は、所与の駆動パルスのためにアクティブであることが期待されるプリントヘッドのノズル流路の数の計測を決定することと、ノズル流路キャパシタンスの変化を補償するために駆動パルスを発生させる回路に制御パラメータを提供することと、を提供する。

40

## 【0021】

関連する態様において、調節の動的な範囲を減じるために、本発明は、キャパシタンスを各々が有する複数のノズル流路を有するプリントヘッド用の補償回路を提供し、複数のノズル流路が、共通の駆動接続に、および個々のノズル制御切り替え素子と直列に、接続され、この回路は、アクティブなノズル流路の数の変化に伴う駆動回路に提示される全キャパシタンスの変化を減じるために駆動接続に接続される、補償キャパシタンス配置を備える。

50

## 【0022】

補償キャパシタンス配置は、全てのノズル流路がアクティブである場合の合計ヘッドキャパシタンスの略3分の1のキャパシタンスを有する固定コンデンサであり得る。加えて、またはあるいは、補償キャパシタンス配置は、駆動端子に1つの切り替え素子を介してまたはそれぞれの切り替え素子を介して結合された1つ以上の追加のキャパシタンスを含むことができ、制御手段が、アクティブなノズル流路の数に基づいて全キャパシタンスの変化を減じるように追加のキャパシタンスを切り替えるために提供され得る。追加のキャパシタンスは、二進数的な関係で配置されることができ、例えば、最大および最小プリントヘッドキャパシタンス間の差の約2分の1である1つのキャパシタンス、4分の1である1つ、および8分の1である1つが、3つのみのキャパシタンスによって約12%まで動的な変化を減じるし、4つ目は約6%を与える。10

## 【0023】

プリントヘッド用の駆動回路がパルス電圧を制御するための調節可能なパラメータを有するさらなる態様では、好ましくは制御配置が、実際のノズル流路電圧を測定し、測定に基づいてパラメータを調節するために、提供される。これは、測定された電圧に基づいてタイミング値を調節することにより、第1の態様の回路によって最も有利に達成される。最も好ましくは、調節は、電圧の計測とアクティブなノズル流路の数の計測との両方にに基づいて行われる。

## 【0024】

一実施形態において、実際のパルス電圧の測定が、プリントヘッドによって提示される負荷とは無関係に所望の一定のパルス電圧を達成するためにタイミング係数を調節するために、使用され得る。いくつかの状況において、特にプリントヘッドにおけるクロストークに起因して、所与の駆動電圧について、滴の質量および滴の速度は、プリントヘッドから噴射されている液滴の数に依存し得る。したがって、いくつかの実施形態において、制御システムは、発生させるパルス電圧を噴射されている液滴の数の既知の(一定でない)関数に設定するために使用され得る。このように、回路は、プリントヘッド内のクロストークの影響をある程度補償することができる。20

## 【0025】

印刷において、基板上に印刷される滴の光学濃度は、キーとなるファクターであり得、イメージスキャナがこれを測定するために使用され得る。したがって、一定の電圧または一定の滴の質量を目的とするよりもむしろ、本願のシステムは、プリントヘッドにおいて噴射しているノズルの数とは無関係の一定のインク濃度を目的とするために、いくつかの実現において使用され得る。このシステムはまた、電圧の変化、滴の質量、およびインク濃度を許容誤差内に維持するように配置されることができ、したがって、これらの変数のうちの1つ、またはこれらの変数のうちの1つより多い変数の組み合わせの関数が、制御されることができる。30

## 【0026】

明らかであるように、各態様の好ましい特徴は、他の態様とともに適用されることができ、方法の態様は、対応する装置、例えば論理または回路として、提供されることができ、その逆も同様である。40

## 【0027】

本発明のさらなる特徴および利点が、例としておよび添付の図面に関連付けられて与えられる以下の詳細な説明から、よりよく理解されるであろう。

## 【図面の簡単な説明】

## 【0028】

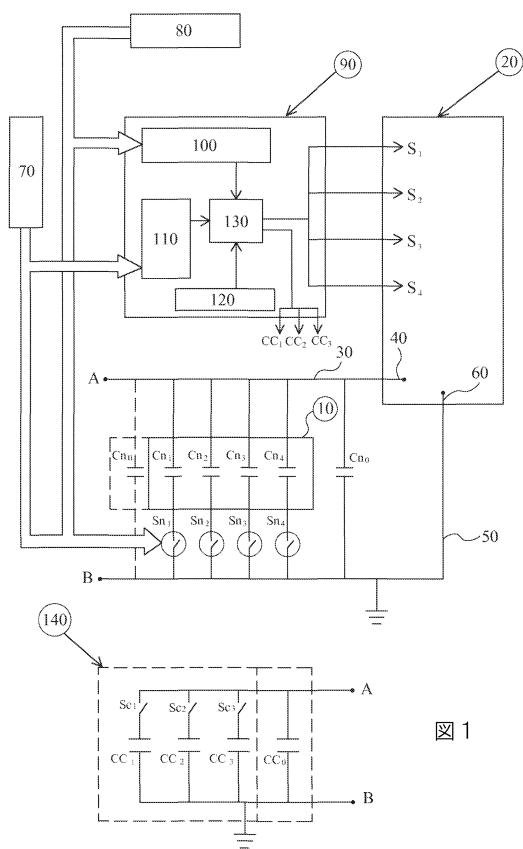

【図1】プリントヘッドに電圧を印加するための回路の概略図である。

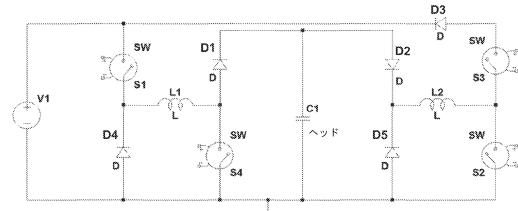

【図2】パルス発生回路の簡略化された概略図である。

【図3】プリントヘッドのノズル流路のキャパシタンスを充電する図2の回路を示す図である。

【図4】接地に対し、供給電圧の2倍より高く充電する図2の回路を示す図である。50

【図5】供給に対し、供給電圧の2倍より高く充電する図2の回路を示す図である。

【図6】供給の2倍より高いパルス電圧によって放電する図2の回路を示す図である。

【図7】供給の2倍より低いパルス電圧によって放電する図2の回路を示す図である。

【図8】「リング」を回避するためのインダクタからのエネルギーの消散を示す図である。

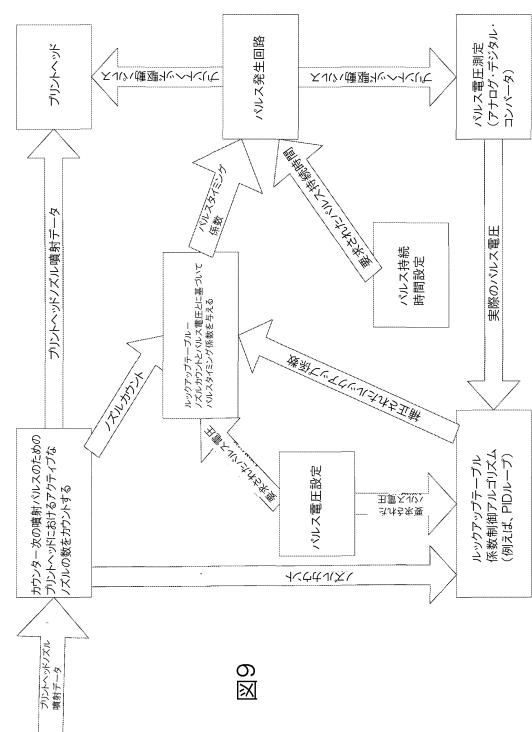

【図9】フィードバックシステムの流れ図である。

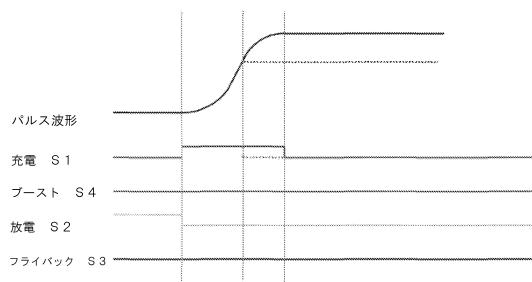

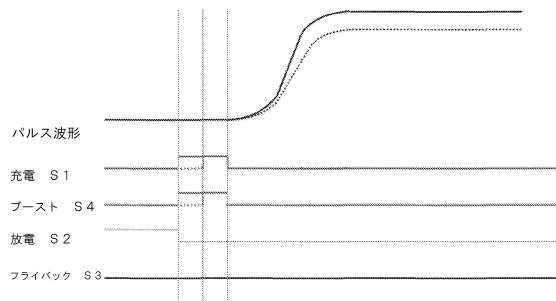

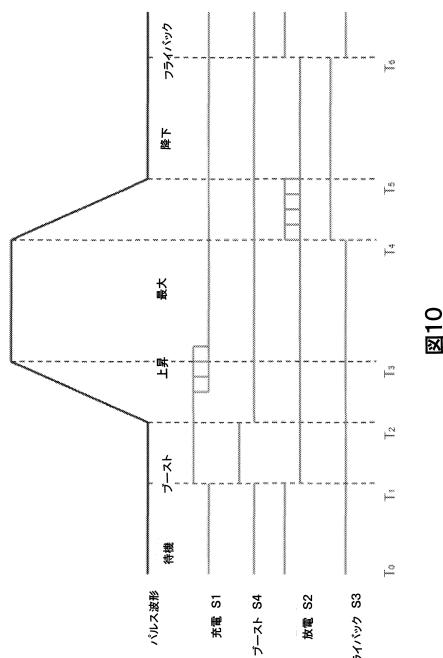

【図10】駆動回路の48ボルト動作の実施例の切り替えタイミング関係を示す図である。

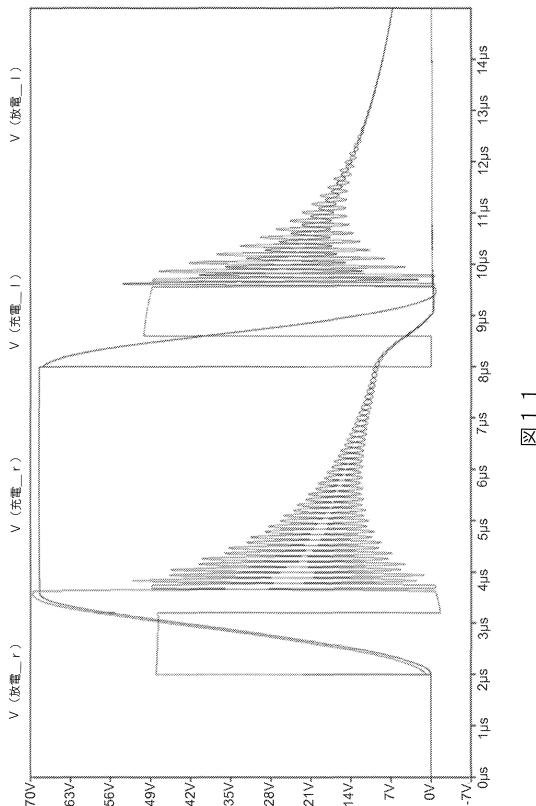

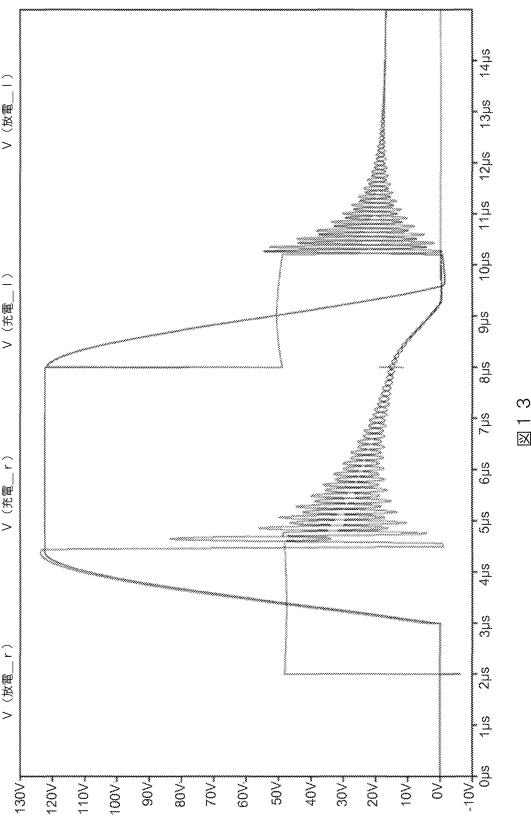

【図11】(2×HTパルス10n + 10n負荷より低い)放電電圧波形を示す図である。

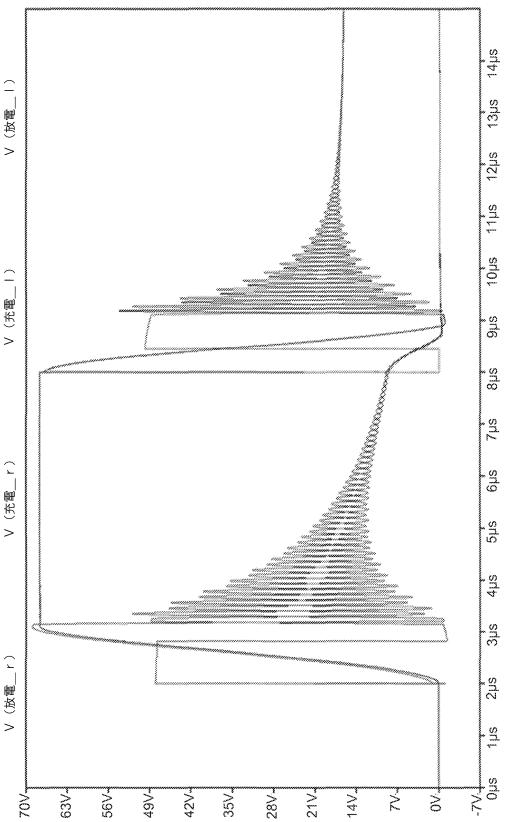

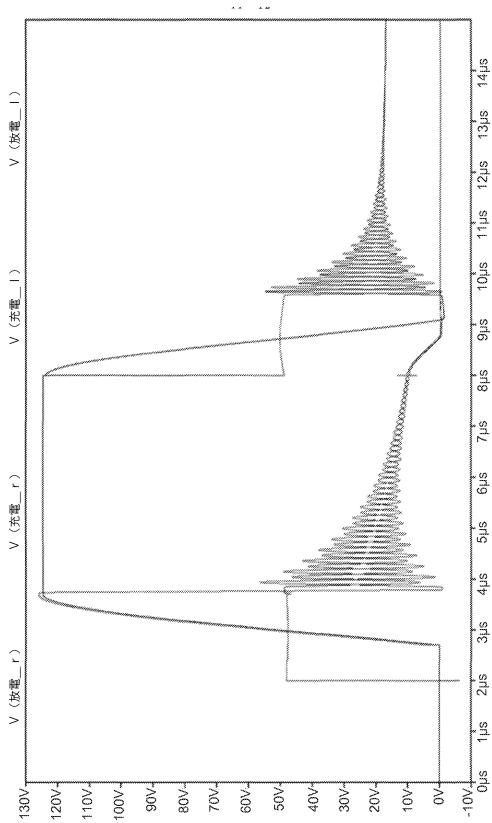

【図12】(2×HTパルス10n負荷より低い)放電電圧波形を示す図である。

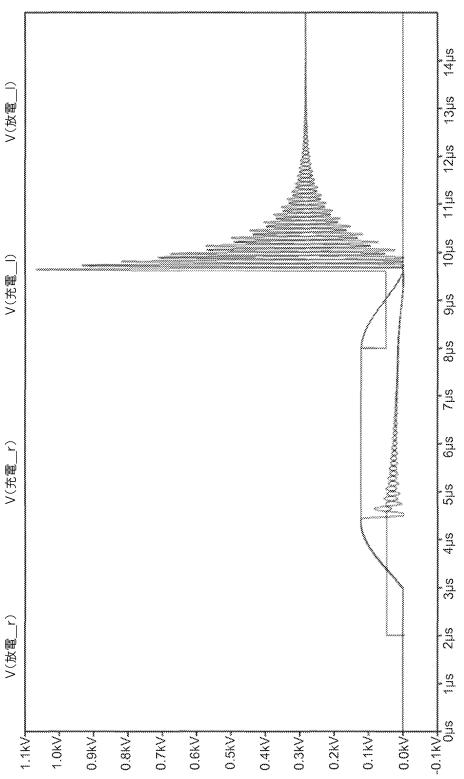

【図13】(2×HTパルス、10n + 10n負荷より高い)放電電圧波形を示す図である。

【図14】(2×HTパルス10n負荷より低い)放電電圧波形を示す図である。

【図15】フライバック信号の早期終了時に生じる放電電圧波形を示す図である。

【発明を実施するための形態】

【0029】

図1を参照すると、インクの滴を噴出するためにプリントヘッド10に繰り返し電圧を印加するための制御または駆動回路の概略図が示されている。プリントヘッドは、インクの滴を噴出するために、図2に示すように、パルス発生回路20によって繰り返し電圧を印加される、それぞれのキャパシタンスCn1、Cn2、Cn3、Cn4...Cnnを各々が有する複数のノズル流路を有する。プリントヘッドは、ノズル流路にわたって並列に示されたそれ独自の固有キャパシタンスCn0を有する。プリントヘッド駆動端子30が、パルス発生回路20からの第1の電力供給接続40にノズル流路を接続する。ノズル流路は、パルス発生回路20への第2の電力供給接続60に電流戻り経路50によって接続される。各ノズル流路は、印刷データソース70およびタイミングデータソース80によって制御される、それぞれのノズル切り替え素子Sn1、Sn2、Sn3、Sn4...Snと直列に接続される。

【0030】

駆動回路は、パルス発生回路20における切り替え素子S1、S2、S3、S4用の波形を駆動するための制御配置90を備える。制御配置は、印刷データソース70およびタイミングデータソース80からデータを受け取る。タイミングデータは、タイミング発生器100によって処理される。印刷データは、印刷データに基づいて任意の1つの時間にアクティブなノズル流路をカウントするためのカウンタ110によって処理される。制御配置は、ノズル流路への所望の電力供給の表を記憶するメモリチップ120を有する。論理130は、パルス発生回路20における切り替え素子S1、S2、S3、S4を駆動するために、タイミング発生器100、カウンタ110、およびルックアップメモリ120から情報を供給される。

【0031】

開発において、駆動回路はまた、固定の補償コンデンサCc0と並列に接続された1つ以上のアクティブに切り替えられる補償コンデンサCc1、Cc2、Cc3を有する補償回路140を備える。各補償コンデンサは、制御配置90によって制御されるそれぞれの切り替え素子Sc1、Sc2、Sc3と直列に接続される。補償回路は、端子AおよびBを介してプリントヘッド10と並列に接続される。固定の補償コンデンサは、全てのノズル流路がアクティブである場合の合計ヘッドキャパシタンスの約3分の1のキャパシタンスを有する。アクティブなノズル流路の数に依存してキャパシタンスを切り替えることにより、全キャパシタンスの変化が減じられることができる。キャパシタンスは、二進数的な大きさで配置されることができ、補償コンデンサCc1は、補償コンデンサCc0の2分の1であることができ、補償コンデンサCc2は、補償コンデンサCc1の2分の1であることができ、補償コンデンサCc3は、補償コンデンサCc2の2分の1であり得る

10

20

30

40

50

ので、変化は約 10 % に減じられ得る。

【0032】

パルス発生回路の動作が、図 2 ~ 9 を参照して説明される。

【0033】

図 2 を参照すると、パルス発生回路の簡略化された概略図が示されている。スイッチが、電力レール、プリントヘッドキャパシタンス、およびインダクタ間の電流の流れを制御する。

【0034】

プリントヘッドキャパシタンス C 1 の充電または放電を結果としてもたらす、さまざまな切り替えシーケンスが、図 3 ~ 5 を参照してここで説明される。

10

【0035】

特に図 3 を参照すると、第 1 の切り替え素子 S 1 を閉じることは、第 1 のインダクタ L 1 および第 1 のダイオード D 1 を介してプリントヘッドキャパシタンス C 1 を充電する。そのような回路は、図 3 に実線で示すように、DC 供給電圧の 2 倍に近いコンデンサでの電圧を発生させることができる。しかしながら、第 1 のインダクタ L 1 からプリントヘッドキャパシタンス C 1 へのエネルギーの共鳴移動が完了する前に第 1 の切り替え素子 S 1 を開くことにより、図 3 に破線で示すように、この電圧までの任意の電圧が発生させられることができる。

【0036】

特に図 4 を参照すると、回路がどのように、接地電位に対し、供給電圧の 2 倍より高く充電するかが示されている。第 1 の切り替え素子 S 1 および第 4 の切り替え素子 S 4 が、同時に閉じられ、第 1 のインダクタ L 1 を通る電流を時間とともに線形的に増加させる。インダクタの充電時間が長ければ長いほど、より多くのエネルギーがインダクタの磁場に蓄積される。第 1 および第 4 の切り替え素子 S 1 および S 4 が同時に開回路にされた場合、第 1 のインダクタ L 1 からプリントヘッドキャパシタンス C 1 へのエネルギーの部分的な共鳴交換が存在し、よってそれを、第 4 のダイオード D 4 によって確立される接地基準に対し高く充電する。達成される電圧は、供給レール電圧の倍数であり、乗数は、充電時間を  $(L_1 * C_1)$  で割ったものとほぼ等しい。より短い充電時間の結果は、図 4 の破線によって示される。

20

【0037】

特に図 5 を参照すると、回路がどのように、接地電位に対し、供給電圧の 2 倍より高く充電するかが示されている。第 4 の切り替え素子 S 4 を開いた後に第 1 の切り替え素子 S 1 を閉じたままにしておくことにより、コンデンサは、図 4 に示すように、電圧がここでは（第 1 の切り替え素子 S 1 によって）供給レールに対し確立されることを除き、先の説明と同様の手法で充電される。したがって、以前より高い電圧が同一のインダクタ充電時間のために確立され、これは、より効率的な動作をもたらす。実際には、上記スキームの組み合わせが、広い範囲の出力電圧を与えるために使用され得る。プリントヘッドキャパシタンス C 1 の放電が、図 6 および図 7 を参照して以下に説明される。

30

【0038】

特に図 6 を参照すると、回路がどのように、供給の 2 倍より高いパルス電圧によって放電するかが示されている。第 3 の切り替え素子 S 3 が閉じられた場合、電流は、プリントヘッドキャパシタンス C 1 から、第 2 のダイオード D 2 、第 2 のインダクタ L 2 、および第 3 のダイオード D 3 を介して、供給レールに流れる。初期パルス電圧が十分に高い場合、コンデンサでの電圧が供給レール電圧へと減じられる時までに、インダクタ L 2 において確立された電流は、図 6 に示すように、電圧をゼロへと減じながら、コンデンサから残りの電荷を得るのに十分に高くなる。この時点で第 2 のインダクタ L 2 において依然として流れている任意の電流は、第 5 のダイオード D 5 および第 3 のダイオード D 3 を介して供給レールに流れる。実際的な回路では、この方法は、パルス電圧が供給電圧より少なくとも 2.7 倍高い場合に働く。

40

【0039】

50

特に図7を参照すると、回路がどのように、供給の2倍より低いパルス電圧によって放電するかが示されている。パルス電圧による放電は供給の2倍より低い。第2の切り替え素子S2が閉じられた場合（この時点で切り替え素子S3を閉じることが好都合である）、電流は、プリントヘッドキャパシタンスC1から、第2のダイオードD2、第2のインダクタL2、および第2の切り替え素子S2を介して、接地電位に流れ始める。十分な電流が第2のインダクタL2において流れている場合、第2の切り替え素子S2はオフにされ得る。この時点で、この時点で、電流はここで、プリントヘッドキャパシタンスC1が完全に放電されて0ボルトになるまで、プリントヘッドキャパシタンスC1から、第2のダイオードD2、第2のインダクタL2、第3の切り替え素子S3、および第3のダイオードD3を介して、供給レールに流れれる。この時点で第2のインダクタL2において依然として流れている任意の電流は、図7によって示すように、第5のダイオードD5および第3のダイオードD3を介して供給レールに流れれる。

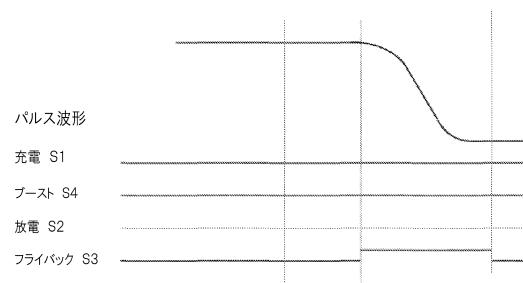

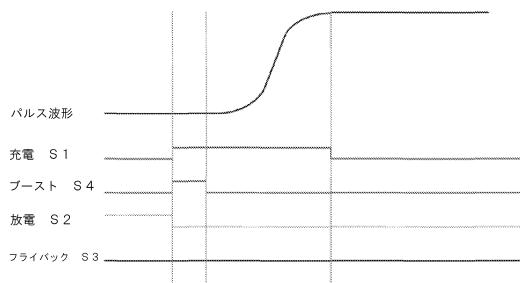

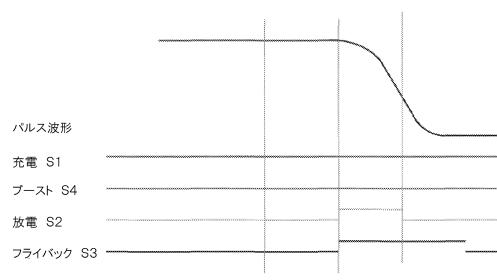

#### 【0040】

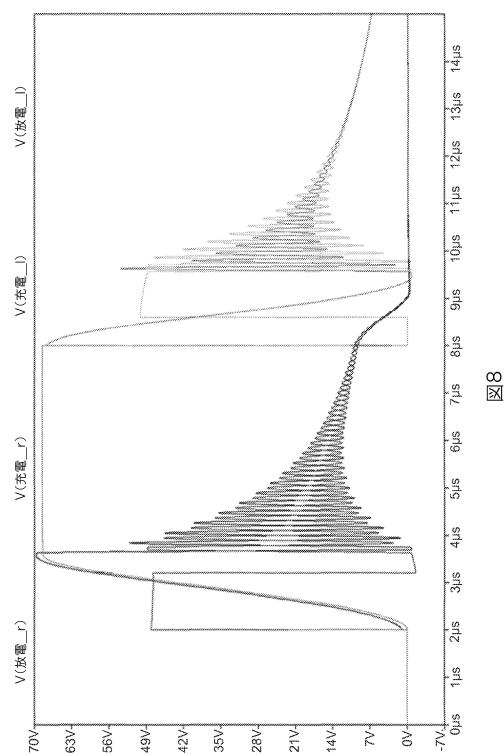

図8を参照して、デュアル・インダクタ・トポロジーの利点が説明される。インダクタの放電の後、電流がゼロになる時点では、インダクタにわたって、また任意の関連付けられた浮遊キャパシタンス（例えば、インダクタにおける巻線間キャパシタンスまたは半導体スイッチにおけるキャパシタンス）にわたって、電圧が存在することが多い。スイッチの動作がインダクタを有効に開回路のままにしておく場合には、インダクタにわたる電圧の「リングング」が、インダクタと浮遊キャパシタンスとの間の共鳴エネルギー移動に起因して生じ得る。インダクタの一貫した充電を達成するために、それは、インダクタが次に充電される前にこのエネルギーが完全に消散し得る場合、有用である。デュアル・インダクタ・トポロジーは、一方のインダクタにおける完全な電流の放電と振動の減衰を、他方のインダクタがコンデンサと供給レールとの間で電流をアクティブに移動させている間に、可能にする。

#### 【0041】

デュアル・インダクタ・トポロジーのさらなる利点は、インダクタL2がコンデンサC1から供給レールに電荷を移動させるために使用されているのと同一の時間に、インダクタL1が電流によって充電され得ることである。したがって、第1のインダクタL1からプリントヘッドキャパシタンスC1を、それが第2のインダクタL2へと放電（して寄生振動の減衰を可能に）した直後に、充電することが可能である。このように、ほぼ正弦曲線に見える制限的な波形による、非常に高いパルス繰り返しレートが達成されることができる。

#### 【0042】

第3の利点は、パルス立ち上がり立ち下がり時間が回路コンポーネントのLC時間定数によって決定されることである。充電および放電インダクタのための異なる値のインダクタを使用することによって、異なるパルス立ち上がりおよび立ち下がり時間を設定することができる。

#### 【0043】

現実のプリントヘッドにおいて、提示されるキャパシタンスは、インクを噴射しているピエゾ流路の数に伴って増加する。したがって、N個のピエゾ流路が噴射している場合の負荷キャパシタンスのためのより現実的なモデルは、 $C_1 = C_0 + N^* C_n$ である[ここで、 $C_0$ は、駆動回路でのケーブルおよび任意の固定のコンデンサに起因する一定のキャパシタンスであり、 $C_n$ は、単一のピエゾ流路のキャパシタンスである]。

#### 【0044】

全てのノズル流路がアクティブである場合のプリントヘッドのキャパシタンスの約3分の1の値を有する追加の負荷キャパシタンスを使用することにより、システムが動作しなくてはならない負荷の動的な範囲が、範囲 [ $C_0, 4^* C_0$ ]まで減じられる。この負荷キャパシタンスに蓄積された余分なエネルギーはコンデンサ放電サイクル中にほとんど回収されるので、余分な電力の消散の観点でのペナルティが許容可能である。以下に説明するように、アクティブに切り替えられる補償キャパシタンスが、さらに変化を減じ、二次

10

20

30

40

50

駆動回路とともに使用され得る。

【0045】

データに依存したキャパシタンスの結果として、パルス発生回路のための充電時間は、一貫した駆動電圧を達成するために、印刷されているデータに依存して変えられなくてはならない。これは、単純なカウンティング回路および充電時間のためのルックアップテーブルによりデジタルハードウェアにおいて達成されることができる。

【0046】

図9を参照すると、安定したパルス電圧を達成するためのフィードバックシステムの流れ図が示されている。発生させられたパルス電圧は、DCレール電圧、充電インダクタンス、負荷キャパシタンス、および充電時間に関連するものとして示されてきた。これらの値、特に有効負荷キャパシタンスが、経時的に変化し得ること、またいくらかの温度依存性を示し得ることが知られている。したがって、所望のパルス電圧を達成するために、パルス回路の動作全体を通してインダクタ充電時間に対する精細な調節を行うことが必要であり得る。これは、発生させられた電圧を測定し、それを所望の電圧と比較することによって達成され得る。任意の誤差は、制御アルゴリズム（例えば、PIDサーボループ）への入力として使用され得、それは、電圧の誤差に基づいてインダクタ充電時間を補正する。

10

【0047】

この典型的で非限定的な応用例における図2の回路コンポーネントのための値は、以下のとおりである。

20

【0048】

インダクタ ( $L_1$  および  $L_2$ ) = 典型的には  $10 \sim 50 \mu H$

コンデンサ ( $C_1$ ) = 約  $10 nF$  (どのノズル流路も噴射していない) ~  $40 nF$  (全てのノズル流路が噴射している)

立ち上がりおよび立ち下がり時間 = 約  $1 \mu s$

パルス持続時間 =  $3 \sim 6 \mu s$  の範囲内

パルスとパルスの間隔 =  $10 \mu s$  から  $1 ms$  まで、およびそれを超える

供給電圧 =  $24 V$  または  $48 V$  であるが、任意の供給電圧が可能

パルス電圧 = 典型的には  $60 V \sim 120 V$  の範囲内だが、それは、いくつかのプリントヘッドではより低い  $25 V \sim 35 V$  の範囲内であり得る

30

図10～14を参照して、以下は、典型的な駆動回路の48ボルト動作の実施例である。

特に図10を参照すると、以下の表による切り替えタイミング関係が示されている。

【0049】

【表1】

| 状態     | 時間             | アクティブな配置、コメント                                                                                                                                                                                                    |

|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 待機     | $T_0 \sim T_1$ | S2、出力クランプ機能                                                                                                                                                                                                      |

| ブースト   | $T_1 \sim T_2$ | S1およびS4、パルス電圧 $> \approx 1.7 \times HT$ である。0uSであり得る。                                                                                                                                                            |

| 上昇     | $T_2 \sim T_3$ | S1、インダクタが負荷を駆動しながら充電および放出する                                                                                                                                                                                      |

| 最大     | $T_3 \sim T_4$ | この時間はパルスの長さに寄与する                                                                                                                                                                                                 |

| 降下     | $T_4 \sim T_5$ | S3およびいくらかS2が確認の必要あり                                                                                                                                                                                              |

| フライバック | $T_5 \sim T_6$ | S3のみ。S2はオフでなくてはならず、そうでなければ、回収されたエネルギーが失われ、インダクタの放電時間が大幅に延長される。期間 $T_4 \sim T_6$ は典型的に、全てのエネルギーがソースに戻されることを保証するために、 $T_1 \sim T_3$ より長く、そうでなければ潜在的に、危険なフライバック電圧が生じ、それは、最終的に回路を破壊する。同様に、S2がオフになる場合、S3はオンでなければならない。 |

| 待機     |                | S2、出力クランプとして                                                                                                                                                                                                     |

40

50

図11を参照すると、以下の表の切り替えタイミングによる（ $2 \times \text{HTパルス } 10\text{n} + 10\text{n}$ 負荷より低い）放電電圧波形が示されている。

【表2】

| 名称 | 機能        | 遅延  | オン   | 単位 | コメント                      |

|----|-----------|-----|------|----|---------------------------|

| S1 | L1の充電     | 2.0 | 1.2  | uS |                           |

| S4 | L1の接地     |     |      |    | 必要なし                      |

| S2 | L2の接地     | 8.0 | 0.6  | uS | 負荷に戻ってきて0ボルトに戻っていくことを確認する |

| S3 | L2のフライバック | 8.0 | >1.6 | uS |                           |

10

図12を参照すると、以下の表の切り替えタイミングによる（ $2 \times \text{HTパルス } 10\text{n}$ 負荷より低い）放電電圧波形が示されている。

【表3】

| 名称 | 機能        | 遅延  | オン   | 単位 | コメント                      |

|----|-----------|-----|------|----|---------------------------|

| S1 | L1の充電     | 2.0 | 0.82 | uS |                           |

| S4 | L1の接地     |     |      |    | 必要なし                      |

| S2 | L2の接地     | 8.0 | 0.45 | uS | 負荷に戻ってきて0ボルトに戻っていくことを確認する |

| S3 | L2のフライバック | 8.0 | >1.1 | uS |                           |

20

図13を参照すると、以下の表の切り替えタイミングによる（ $2 \times \text{HTパルス}、 10\text{n} + 10\text{n}$ 負荷より高い）放電電圧波形が示されている。

【表4】

| 名称 | 機能        | 遅延  | オン   | 単位 | コメント                                        |

|----|-----------|-----|------|----|---------------------------------------------|

| S1 | L1の充電     | 2.0 | >2.5 | uS |                                             |

| S4 | L1の接地     | 2.0 | 1.1  | uS | $2 \times \text{HT}$ を超えて得られるインダクタにおける余分な電荷 |

| S2 | L2の接地     |     |      |    | 必要なし*                                       |

| S3 | L2のフライバック | 8.0 | >2.3 | uS |                                             |

30

図14を参照すると、以下の表の切り替えタイミングによる（ $2 \times \text{HTパルス } 10\text{n}$ 負荷より低い）放電電圧波形が示されている。

【表5】

| 名称 | 機能        | 遅延  | オン   | 単位 | コメント                                        |

|----|-----------|-----|------|----|---------------------------------------------|

| S1 | L1の充電     | 2.0 | >1.7 | uS |                                             |

| S4 | L1の接地     | 2.0 | 0.7  | uS | $2 \times \text{HT}$ を超えて得られるインダクタにおける余分な電荷 |

| S2 | L2の接地     |     |      |    | 必要なし*                                       |

| S3 | L2のフライバック | 8.0 | >1.6 | uS |                                             |

40

上記実施形態は、本発明の例示的な例として理解されるべきである。本発明のさらなる実施形態が想定される。任意の一実施形態に関連して説明された任意の特徴は、単独で、または説明された他の特徴と組み合わせられて、使用され得ること、また、任意の他の実

50

施形態の、または任意の他の実施形態の任意の組み合わせの、1つ以上の特徴と、組み合わせられて使用され得ること、が理解されるべきである。さらに、上述されていない均等物および変形例もまた、添付の請求項において定義される本発明の範囲から逸脱せずに用いられ得る。

【図1】

【図2】

図2

【図3】

図3

【図4】

図4

【図6】

図6

【図5】

図5

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

10

### 【図11】

11

## 【図12】

卷之二

### 【図13】

3

1

図

【図 1 4】

図 1 4

【図 1 5】

図 1 5

---

フロントページの続き

審査官 藏田 敦之

(56)参考文献 特開2001-129989 (JP, A)

特開2007-118307 (JP, A)

特開2008-023813 (JP, A)

特開2011-046030 (JP, A)

米国特許第06271618 (US, B1)

(58)調査した分野(Int.Cl., DB名)

B 41 J 2 / 01 - 2 / 215